Page 1

DR-6 05 T / E /TE1 / TE2

S e r v i c e M a n u a l

CONTENTS

• SPECIFICATIONS

1) General.......................................................................2

2) Transmitter.................................................................2

3) Receiver......................................................................2

• CIRCUIT DESCRIPTION

1) Frequency Configuration..........................................3

2) Receiver Sytem

3) Power Supply Circuit...............................................4

4) AF Signal Circuit......................................................5

5) Transmitter System..............................................5-6

6) PLL Circuit.................................................................6

7) Front CPU and Peripheral Circuit

8) Cross Band Repeater Circuit

9) Tone Burst Output Circuit........................................7

10) CTCSS Tone Encoder Circuit

11) CTCSS Tone Decoder Circuit

12) 9600bps Packet Circuit............................................8

13) Clone Circuit

14) CPUI/O Port........................................................9-10

• SEMICONDUCTOR DATA

1) AK2341 ...................................................................11

2) AN78L05M ............................................................12

3) AN8010M...............................................................12

4) AT24C16N-10SI-2.7 .............................................12

5) LA4425A ................................................................12

6) M64076GP ............................................................ 13

7) M57788 ..................................................................14

8) M67746 ..................................................................14

9) M68702H .............................................................. 14

10) MC3372VM ...........................................................15

11) MC7808CT

12) NJM4558 .............................................................16

13) RH5VA60AA ........................................................16

14) RN5VL25AA-T1 ...................................................16

15) TC4W53FU.............................................................17

16) Transistor,Diode and LED Outline Drawings

17) LCD Connection ...................................................18

• EXPLODED VIEW

1) LCD Assembly

2) VHF Unit Assembly.................................................20

3) UHF Unit Assembly.................................................21

...................................................3-4

...........................

..................................

.................................

.................................

............................................................8

............................

........................................................19

.............................. 15

......

17

• PARTS LIST

VHF MAIN Unit......................................................22-23

UHF MAIN Unit......................................................24-26

FRONT CPU Unit................................................. 26-27

VHFVCO Unit......................................................27-28

UHFVCO Unit.............................................................28

TCXO Unit................................................................... 28

Mechanical Parts.........................................................28

PCB Unit......................................................................28

SP Unit......................................................................... 28

Packing........................................................................ 28

7

7

8

8

• ADJUSTMENT

1) Required Test Equipment................................29-30

2) UHF PLL Adjustment.............................................30

3) UHF RX Adjustment..............................................31

4) UHF TX Adjustment................................................32

5) VHF PLL Adjustment............................................33

6) VHF RX Adjustment...............................................33

7) VHF TX Adjustment............................................... 34

8) Adjustment Points.................................................. 35

• PC BOAD VIEW

1) VHF Main Unit Side A............................................36

2) VHF VCO Unit Side A

3) UHF Main Unit Side A

4) UHFVCO Unit Side A............................................ 37

5) VHF Main Unit Side B............................................38

6) VHFVCO Unit Side B............................................ 38

7) UHF Main Unit Side B............................................39

8) UHFVCO Unit Side B............................................ 39

9) Front Unit Side A ................................................... 40

10) Front Unit Side B ................................................... 40

11) TCXO Unit ..............................................................40

• SCHEMATIC DIAGRAM

1) CPU Unit............................................................41-42

2) VHF Main Unit T/E............................................43-44

3) VHF Main Unit TE1fTE2..................................45-46

4) UHF Main Unit T/E........................................... 47-49

5) UHF Main UnitTE1fTE2 .................................49-50

6) VHF PLL-VCO Unit..........................................51 -52

7) UHF PLL- VCO Unit.........................................51 -52

8) TCXO Unit........................................................51-52

• BLOCK DIAGRAM......................................................53-54

............................................

............................................37

36

A L IN C O , inc

Page 2

SPECIFICATIONS

1) General

Frequency Rage:

(Version T)

(Version E)

(Version TE1)

(Version TE2)

Modulation:

Antenna Impedance:

Supply Voltage:

Ground:

Current Consumption

Frequency Stability:

Dimensions (Body only):

Weight:

Cannel

VHF BAND 136.000-

UHF BAND

VHF BAND

UHF BAND 430.000 - 439.995MHz

VHF BAND 136.000-

UHF BAND 400.000 -

VHFBAND

UHF BAND

F3E (FM)

50Q

13.8 Volts DC

Negative

VHF TX 50W: 11.5A max. (T/E), 35W: 11 .OA max. (TE1/TE2)

UHFTX 35W: 10.0A max.

RX 1.2A max.

±1 Oppm max.

140(W)mm x 40(H)mm x 176(D)mm

1.1kg

VHF: 51 / UHF: 51 total 102

173.995MHz

144.000-

420.000 -

147.995MHz (TX)

470.000MHz

430.000 ~449.995MHz

144.000-

145.995MHz

173.995MHz

420.000MHz (RX/TX)

136.000-

173.995MHz

450.000 - 470.000MHz

(RX)

(RX)

(TX)

(RX/TX)

(RX/TX)

(RX/TX)

(RX/TX)

(RX/TX)

2) Transmitter

Output Power:

Modulator:

Spurious Emission:

Max. Deviation:

Mod. Distortion (@60% mod.):

Microphone Impedance:

VHF BAND High: 50W / Low: approx. 5W (T/E)

High: 35W/Low: approx. 5W (TE1/TE2)

UHF BAND High: 35W/Low: approx. 5W

Reactance modulation

-60dB max.

±5kHz

3% max. (300 to 3000Hz)

2k£2

3) Receiver

Rx System:

Intermediate Frequency:

Sensitivity (12dB SINAD):

Selectivity:

Squelch Sensitivity:

AF Output (@5% distortion):

Speaker Output Impedance:

Note: Specifications are subject to change without notice or obligation.

Specifications guaranteed in the amateur band only. (T/E)

Double Superheterodyne

VHF: First: 21.7MHz/Second: 450kHz

UHF: First: 30.85MHz / Second: 455kHz

Main band: -16dBn (0.16^V) or less

-6dB: 12kHz min.,-60dB: 28kHz max.

-20dB^ (0.1 (xV) or less

2W or more (

8 C i

8Q load)

Page 3

CIRCUIT DESCRIPTION

1) Frequency Configuration

• VHF and UHF bands have each PLL independently, and 2 IF systems are

provided. Therefore 2 bands can be received simultaneously.

• The received signal of VHF band is mixed with the first local oscillator signal and

converted into the first IF of 21.70M Hz. Then the resulting signal is mixed with the

second local oscillator signal of 21.25MHz and converted into 450kHz.

• The received signal of UHF band is mixed with the first local oscillator signal and

converted into the first IF of 30.85kMHz. Then the resulting signal is mixed with

the second local oscillator signal of 30.395MHz and converted into 455kHz.

2) Receiver System

1. Receiver Circuit

The received signal from the antenna is passed through the duplexer (the circuit

consists of low-pass filter for VHF and high-pass filter for UHF), and divided into

the signals of VHF and UHF.

1-1 144M Band Receiver Circuit

After the received signal from the duplexer is passed through the band-pass filter

via the antenna switch (D5, D6), the signal is amplified at RF amplifier Q11. The

unwanted signal of the amplified signal is eliminated by the band-pass filter

consisting of 3 varicaps. Next the signal is mixed with the first local oscillator

signal at the first mixer Q12, and converted to the first IF. The unwanted signal is

attenuated by the crystal filter circuit. Then the signal is fed to IC2 Pin16 after

being amplified at IF amplifier Q7. In this IC2 the signal is mixed with the second

oscillator signal and converted to the second IF, then it is output from Pin3. The

output signal is attenuated the unwanted signal by the ceramic filter, and input

again from IC2 Pin5. Next the signal is passed through the limiter amplifier and

demodulated in the quadrature detection circuit of IC2 to be output from Pin9 as

AF signal.

1-2 430M Band Receiver Circuit

The received signal from the duplexer is passed through the antenna switch

(D206, D207), and amplified in the RF amplifier Q 211. The amplified signal is

attenuated the unwanted signal by the helical filter L218. The signal is amplified in

RF amplifier Q212 and attenuated the unwanted signal again by the helical filter

L219, then it is mixed with the first local oscillator signal at the first mixer Q 213 and

converted to the first IF. The unwanted signal is attenuated by the crystal filter

circuit. Then the signal is fed to IC202 Pin16 after being amplified at IF amplifier

Q214. In this IC202 the signal is mixed with the second oscillator signal and

converted to the second IF, then it is output from Pin3. The output signal is

attenuated the unwanted signal by the ceramic filter, and input again from IC202

Pin5. Next the signal is passed through the limiter amplifier and demodulated in

the quadrature detection circuit of IC202 to be output from Pin9 as AF signal.

Page 4

2. S (Signal) Meter Circuit

3. Squelch Circuit

VHF:

The S meter signal DC voltage which is output from IC2 Pin13 is supplied to IC401

Pin10 via Trim, pot VR1, then it is digitized by A/D converter to be indicated on

LCD as the S meter.

UHF:

The S meter signal DC voltage which is output from IC202 Pin 13 is supplied to

IC401 Pin5 via Trim, pot VR202 then it is digitized by A/D converter to be indicated

on LCD as the S meter.

VHF Squelch Circuit:

The AF signal which is output from IC2 Pin9 is input to Pin10. Only the noise is

amplified by the active filter in IC2 and output from Pin11, then amplified by the

noise amplifier Q6. The amplified noise is rectified to DC voltage by D2 and input

to CPU IC401 Pin9 via Trim, pot VR2. In the IC the input voltage and the settled

voltage by the squelch knob are compared to work the squelch ON/OFF. When

the squelch is open, the squelch signal "H" is output from IC401 Pin41 and LED

D401 (green) lights.

UHF Squelch Circuit:

The AF signal output from IC202 Pin9 is input to Pin 10. Only the noise is amplified

by the active filter in IC2 and output from Pin11, then amplified by the noise

amplifier Q206. The amplified noise is rectified to DC voltage by D202 and input to

CPU IC401 Pin5 via Trim, pot VR201. In the IC the input voltage and the settled

voltage by the squelch knob are compared to work the squelch ON/OFF. When

the squelch is open, the squelch signal "H" is output from IC401 Pin13 and LED

D402 (green) lights.

3) Power Supply Circuit

1. VHF Power Supply Switch Circuit and Unlock Circuit

Jn the receiving mode, "H" is output from PLL shift register IC501 Pin16 according

to the serial data from CPU, and Q17 and Q16 are turned ON, then 8V is added to

8RV line. In the transmitting mode, just same as the receiving mode, "H" is output

from IC501 Pin17, and Q19 and Q 18 are turned ON, then 8V is added to 8TV line.

When PLL is unlocked, the unlock switch Q21 is turned ON because "H" is output

from UL terminal of PLL-VCO unit. Then 8TV switch Q19 is turned OFF. Conse

quently, as 8TV line does not work, the unit does not transmit when PLL is un

locked.

2. UHF Power Supply Switch Circuit and Unlock Circuit

In the receiving mode, "H" is output from PLL shift register IC601 Pin16 according

to the serial data from CPU, and Q217 and Q218 are turned ON, then 8V is added

to 8RV line. In the transmitting mode, just same as the receiving mode, "H" is

output from IC601 Pin17, and Q220 and Q219 are turned ON, then 8V is added to

8TV line. When PLL is unlocked, the unlock switch Q222 is turned ON because

"H" is output from UL terminal of PLL-VCO unit. Then 8TV switch Q220 is turned

4

Page 5

4) AF Signal Circuit

1. VHFAF Signal

2. UHF AF Signal

OFF. Consequently, as 8TV line does not work, the unit does not transmit when

PLL is unlocked.

The AF signal which is output from IF unit IC2 Pin9 is made the AF frequency

characteristics 3kHz or below by the de-emphasis circuit (consisting of R19, C18,

R13, C10, R12 and C9), then amplified by AF preamplifier Q3. Besides the

amplified signal is made the AF frequency characteristics 300Hz or more by the

de-emphasis circuit (consisting of C5, R8, C4, R3, C3). The de-emphasized AF

signal ROV is muted and after the signal is adjusted by volume VR401, added to

AF power amplifier IC3 Pinl and amplified to drive the speaker.

The AF signal which is output from IF unit IC202 Pin9 is made the AF frequency

characteristics 3kHz or below by the de-emphasis circuit (consisting of R226,

C213, R222, C2 11, R221 and C210), then amplified by AF preamplifier Q203.

Besides the amplified signal is made the AF frequency characteristics 300Hz or

more by the de-emphasis circuit (consisting of C207, R210, C206, R207, C205).

The de-emphasized AF signal ROU is muted and after the signal is adjusted by

volume VR402, added to AF power amplifier IC3 Pin 1 and amplified to drive the

speaker.

3. AF Mute Circuit

VHF:

When the squelch is turned ON and there is no input signal, the output control

signal of the microcomputer IC401 Pin42 turns ON double mute switches Q2 and

Q4, then the input signal of audio power amplifier IC3 is cut to mute the speaker

output.

UHF:

When the squelch is turned ON and there is no input signal, the output control

signal of the microcomputer IC401 Pin19 turns ON double mute switches Q204

and Q233, then the input signal of audio power amplifier IC3 is cut to mute the

speaker output.

5) Transmitter System

1. Modulator Circuit VHF/UHF

After the voice is converted into the electric signal by the microphone, the signal is

led to the microphone amplifier Q401 to be amplified. The microphone amplifier

includes the pre-emphasis circuit. The amplified voice signal is added to the IDC

circuit of operational amplifier IC203 and limited the band width. Each frequency

deviation can be adjusted in VR3 (VHF) or VR204 (UHF). The signal is added to

varicap of VHF/UHF VCO unit for reactance modulation.

Page 6

2. Drive/PA Amplifier Circuit

VHF:

The transmit signal from VCO of VHF band is amplified by the younger amplifiers

Q9, Q10, then input to the power module IC1. The signal amplified to the desired

level in IC1, is passed through the low-pass filter, antenna switch, and low-pass

filter in duplexer to attenuate the second and third harmonics enough, then

supplied to the antenna.

UHF:

The transmit signal from VCO of VHF band is amplified by the younger amplifiers

Q208, Q209, Q 210 then input to the power module IC201. The signal amplified to

the desired level in IC201, is passed through the low-pass filter, antenna switch,

and low-pass filter in duplexer to attenuate the second and third harmonics

enough, then supplied to the antenna.

3. APC circuit

VHF:

A part of output power from low-pass filter is detected by Diodes D7 and D8, and

converted to DC. The detection voltage is passed through the APC circuit of UHF

side (Q229, Q228, Q227), then it controls the APC voltage supplied to the younger

amplifier Q10 and the power module IC1 to fix the output power.

6) PLL Circuit

1. PLL Synthesizer Circuit

UHF:

A part of output power from low-pass filter is detected by Diodes D208 and D209,

and converted to DC. The detection voltage is passed through the APC circuit of

UHF side (Q229, Q228, Q227), then it controls the APC voltage supplied to the

younger amplifier Q210 and the power module IC201 to fix the output power.

VHF and UHF bands have their own units isolatedly. The sub unit is packed in a

hard shield case so as not to be influenced by the circumstances. The crystal X2:

21.25M Hz is oscillated in IC501 (VHF), and the output is fed to IC601 (UHF) via

buffer Q13. The reference oscillating frequency (X2) is divided inside IC501 and

IC601 to gain the reference frequency of 5kHz or 6.25kHz. The comparison

frequency is divided by the pulse swallow system PLL IC501 and IC601 after VCO

output is amplified in Q505 (VHF) and Q604 (UHF). In the result, the PLL synthe

sizer which has 5, 10,12.5, 15 ,20, 25, 30 and 50kHz steps is obtained.

The reference frequency of 21.25MHz is passed through the buffer of IC501 and

output from Pin 1 XBO, then input to IC2 Pin1 as VHF (144MHz band) 2nd local

oscillator.

*As for TE1 and TE2, reference frequency of 21 ,25MHz is oscillated in X901:

TCXO unit and fed to IC501 (VHF).

Page 7

2. V-VCO Circuit

The desired frequency is oscillated directly in Colpitts oscillating circuit consisting

of FET Q502. VCO control voltage is added to the varicaps D502 and D503 to

tune the oscillating frequency. While receiving RXV becomes "H", and Q501 and

D501 are turned ON to shift the oscillating frequency.

3. U-VCO Circuit

The desired frequency is oscillated directly in Colpitts oscillating circuit consisting

of FET Q601. VCO control voltage is added to the varicaps D602 and D603 to

tune the oscillating frequency.

7) Front CPU and Peripheral Circuit

1. Microphone Key Input Circuit

PTT key:

Soon after the switch on the microphone (PTT) is turned ON, "L" level is input to

CPU IC401 directly.

UP/DOW N key:

Soon after this switch is turned ON, the voltage is generated by the resistors that

are connected to keys and supplied to IC401 Pin4 then A/D converted in CPU.

2. Lighting Circuit

When the power is turned ON, the voltage which is stabilized to 10.5V at Q405 and

D407 is supplied to LMP401 and LMP402 to turn ON the lamp.

3. Reset and Backup Circuit

When the power is turned ON, "L" level of approximately 2jis or more is output

from IC403 OUT (equipped with reset function), then "H" level is output to reset

CPU IC401. When the power is turned OFF, IC405 output (BU) becomes "L" level

and the transceiver goes into the backup mode. The contents of the memory is

written on E2PROM IC402 in the backup mode. Then IC403 (equipped with reset

function) becomes "L" level to reset the CPU.

4. Beep Sound Output Circuit

The square pulse is output from CPU IC401 Pin23 (BEEP), then it is integrated by

CR and input to AF amplifier without passing through Volume VR.

8) Cross Band Repeater Circuit (T, TE1, TE2)

When the Squelch of VHF side is opened in the Cross Band Repeater mode, the

AF signal ROV (VHF) is unmuted and amplified by IC203. The amplified modula

tion signal is added to modulation varicap of UHF VCO and transmitted from UHF

side. When the Squelch of UHF side is opened in the Cross Band Repeater mode,

the AF signal ROU (UHF) is unmuted and amplified by IC203. The amplified

modulation signal is added to modulation varicap of VHF VCO and transmitted

from VHF side.

Page 8

9) Tone Burst Output Circuit

When Down key is pressed while holding the PTT key down, the square pulse is

output from CPU IC401 Pin14 (B1750). It is amplified by IC203 after being

integrated by CR. The amplified signal is added to each VCO modulation varicap

to output.

10) CTCSS Tone Encoder Circuit

The mimic sine wave is output from IC401 Pin11. It is integrated by CR, and

converted to analogue wave to obtain 50 waves within 67.0~254.1. The tone is

added to VCO to output.

11) CTCSS Tone Decoder Circuit (EJ-24U)

In IC1 (VHF) or IC2 (UHF), a kind of tone frequency is settled by the serial data

selected from 50 kinds of frequencies within 67.0-254.1 Hz . While receiving the

voice and tone signals input from RAV (VHF) or RAU (UHF) are supplied to Pin1,

and tone signal only is selected at the low-pass filter in IC. When the signal is

accordance with the tone frequency which is settled by the serial data, "L" level is

output to TDV (VHF) or TDU (UHF) terminal. The "L" level signal is input to

IC401, Pin32 and Pin33, then the squelch is opened When the tone signal is not

accordance with the settled frequency, "H" level is output to the TDV (VHF) or

TDU (UHF) terminal. The "H" level signal is input to IC401, Pin32 and Pin33, then

the squelch is closed.

12) 9600bps Packet Circuit

In the 9600 packet mode, PTT is provided through the UART terminal of JK1 to

IC401 Pin22, then it is transmitted in "L" level. The modulation signal from TNC is

provided through 9600 PKT terminal of JK2. It is amplified and limited in Q29,

unmuted in Q26 and Q27, and the VCO is modulated, then transmitted. The

detection output of IF IC2 or IC202 is input to the signal switch IC4 via butter Q23

or Q235. The input V/U signal switches the input signal of IC4 according to the

signal from CPU IC401 Pin33. Then the MAIN band signal is output from Pin1 to

JK2.

13) Clone Circuit

In the Clone mode, the data which is output from IC401 Pin21 of Master unit is fed

to the IC401 Pin22 of the Slave unit through the UART terminal JK1 and connect

ing cable.

Page 9

14) CPU I/O Port

No.

Pin Name Function I/O Logic

Description

1

C1 C1

2 VL1

P67/AN7

3

4 P66/AN6

5 P65/AN5

P64/AN4

6

7 P63/SCLK22/AN3 BP1 I A/D

P62SCLK21/AN2 BP2 I

8

9 P61/SOUT2/AN1 SQV

P60/SIN2/AN0

10

11 P57/ADT/DA2

P56/DA1 MMUT

12

P55/CNTR1 SDU

13

14

P54/CNTR0

P53/RTP1

15

16 P52/RTP0

17

P51/PWM1

18 P50/PWM0

19 P47/SROY1

20 P46/SCLK1

P45/TXD TXD

21

P44/RXD RXD I

22

P43/S/TOUT BEEP

23

24

P42/INT2

P41/INT1

25

26 P40

P77

27

28 P76 MONI I/O L

29

P75

P74

30

P73 FUNC I

31

P72

32

P71

33

34

P70/INT0 BU

RESET

35

Xcin

36

37 Xcout xco

Xin

38

39 Xout XOUT

V1

v/u I A/D Key input (VHF/UHF/TOT key switch)

UP/DN I

SMU I A/D

SQU I A/D UHF side SQ noise voltage input

SMV I

TONE

B1750

DATU

CKU o Pulse UHF side PLL clock output

STPU o

PTT

MUTU

XMUT

ENC2 I

ENC1 I

UL

TP I

MHZ I

V/M I L Key input (VFO/MR switch)

TDV I L VHF CTCSS tone detection (when the tone is detected = "L")

TDU

RES I L

XC1

XIN

- -

- -

A/D Key input (UP/DOWN/CALL key switch)

A/D

I

o

o H Microphone mute OFF control output (TX="H")

o

I/O A/D/H Extension specification (when PSW is ON)/ Tone burst output

0 Pulse UHF side PLL data output

I

0 H

o L

o

0

I L PLL unlock input (L = unlock)

I/O

I

- -

- -

I

o

A/D VHF side SQ noise voltage input

A/D VHF side S meter voltage input

D/A

Pulse

Pulse

Pulse Clone data input (9600 packet = PTT input "L" = TX)

L/H

NC

LCD Power supply

UHF side S meter voltage input

Destination setting (T=5V, E=3.2V)

Extension specification

CTCSS tone output (50 waves)

H UHF Squelch signal output (When squelch is open = "H")

UHF side PLL reset output

L Key input (PTT)

UHF side AF signal mute control output ("H" = Mute is ON)

AF unmute output in cross band repeater mode (XBR = "L")

Clone data output

H Beep sound output

L Rotary encoder B input

L Rotary encoder A input

Trunking mode input (H = Trunking mode)

Key input (MONITOR) / 9600 mode (PTT ON = "L")

L Key input (MHz)

L

L Backup signal input ("L"=Backup)

-

-

key input (FUNC)

UHF CTCSS tone detection/RX switch in 9600 mode (VHF=L)

Reset signal input ("L"=Reset)

NC

NC

CPU clock input (4.1943MHz)

CPU clock output (4.1943MHz)

9

Page 10

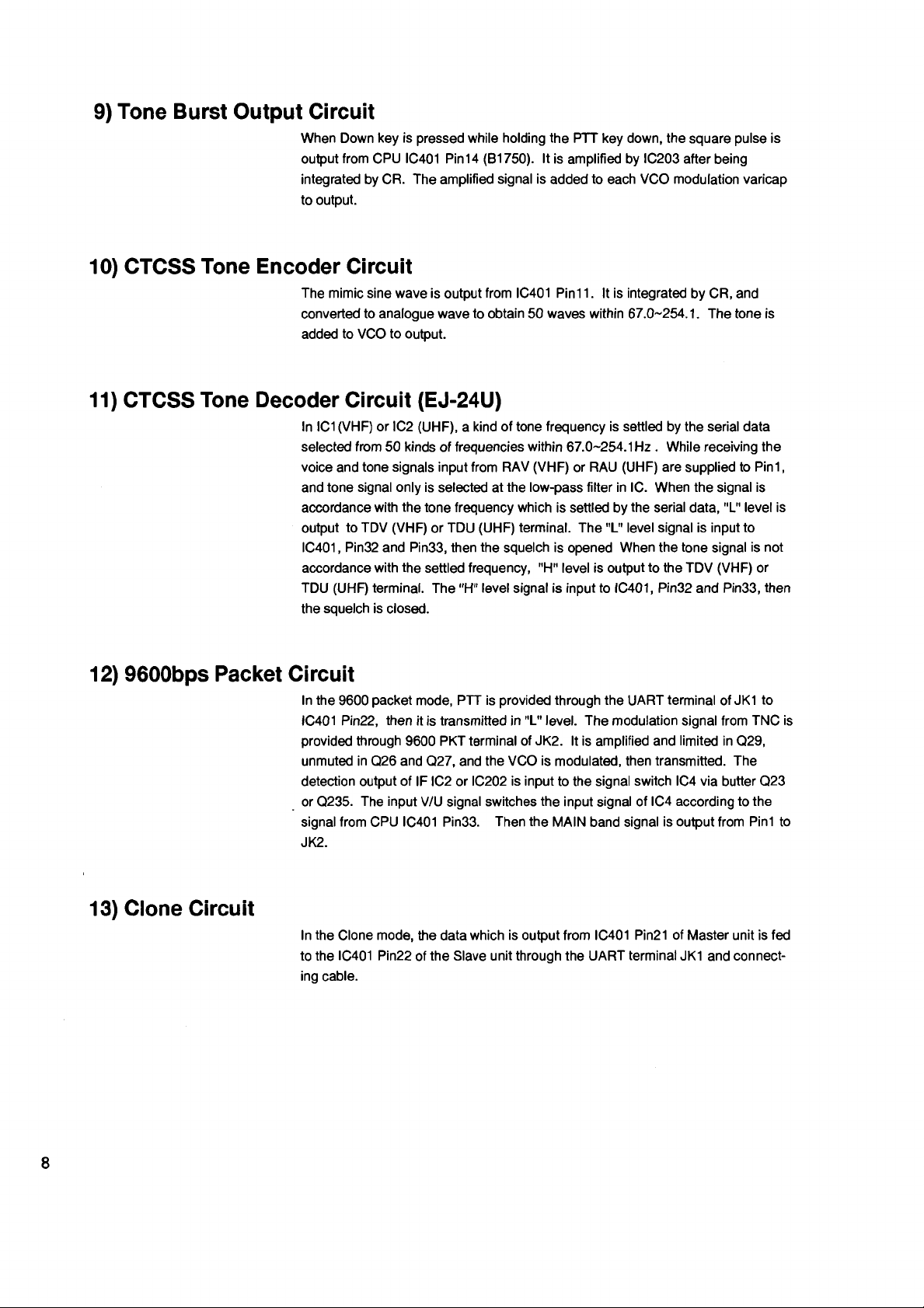

No. Pin Name

Vss GND

40

41 P27 SDV 0 H VHF squelch signal output (when squelch is open = "H")

P26 MUTV

42

P25

43

44 P24

45 P23

P22

46

P21 SDA I/O Pulse EEPROM data input/output

47

P20 LOW o

48

P17

49

50 P16 TID

51 P15/SEG39 SEG39

i i i i

i

90

SEGO

91 Vcc VCC

92 Vref AVCC

93 AVss GND

94 COM3 COM3

COM2 COM2 0

95

COM1

96

97 COMO COMO

98 VL3

VL2

99

C2

100

Function I/O Logic Description

- -

- -

STPV

DATV

CKV 0 Pulse VHF PLL/CTCSS clock output

SCL

STB2

SEGO

COM1 0

V3

V2

C2

0 Pulse VHF PLL reset output

0 Pulse VHF PLL/CTCSS data output

0

0 Pulse CTCSS UHF strobe signal output

I/O Pulse

0 H Segment output for LCD

o H Segment output for LCD

- -

- -

-

-

0

- -

- -

-

Pulse

H

GND

VHF AF signal mute control output (H=Mute is ON)

EEPROM clock output

Transmitting output switch ("H"=Low output)

CTCSS board detection/CTCSS VHF strobe signal output

i

5V Power supply

Reference power supply for A/D conversion

GND

-

NC

-

Common output 2 for LCD

-

Common output 1 for LCD

-

Common output 0 for LCD

-

Power supply for LCD

Power supply for LCD

NC

-

Page 11

SEMICONDUCTOR DATA

1) AK2341 (XA0239) EJ24u (option)

C T C S S E n c o d e r / D e c o d e r

Pin

Pin

Name

RXIN

TXIN

VDD

XIN

XOUT

VSS -

TLINP

TLINN I

TLINO

BIAS

I/O

I RX Signal Input

I TX Audio Input

0

-

I Crystal Terminal (3.6864MHz)

Crystal Terminal (3.6864MHz)

0

I Strobe for Serial Data

I Serial Data

I

I DCS Input

I Tone Detection Level Adjust Input

I

RX Tone Signal Reference Input

0

o

I

I

No.

1

2 RXINO 0 AMP2 Output

3 TXINO 0

4

5 RXOUT 0

6

TXOUT

7

8

9

10 STB

11

SDATA

12 SCLK

13 DCS

DETOUT0Tone Detection Output (Detect: Low)

14

15

16 DREF

17

18

19

20 RXTONE 0 RX Tone Signal Output

21 TXTONE

22 AGNDIN

23 AGND 0 Analog Ground Output

24

Function

AMP1 Output

RX Audio Output

TX Audio Output

Power Supply (1.8 - 5.5V)

Serial Clock

Ground

RX Tone Signal Input

AMP3 Output

TX Tone Signal Output

Analog Ground Input

Bias Input

RXIN

RXINO n z

TXINO

TXIN

RXOUT

TXOUT

VDD

XIN

XOUT c =

STB

SDATA

SCLK

nz

n z

c z

c z

1 =

c =

1 =

n z

> =

n z

1

2

3

4

5

>

10

11

12

*

fO

CO

6

7

8

9

24

23

22

21

20

19

18

17

16

15

14

13

= □

= □

ZZI

ZZI

ZD

= □

ZZI

ZD

= □

Z D

1=]

ZZI

BIAS

AGND

AGNDIN

TXTONE

RXTONE

TLINO

TLINN

TLINP

DREF

VSS

DETOUT

DCS

Block Diagram

J 3. 6864 MHz

Page 12

2) AN78L05M (XA0238)

5 V V o lt a g e R e g u la to r

3) AN8010M (XA0119)

V o lt a g e R e g u l a to r

Test Circuit

u u u

Output Common Input

A N 8 0 1 0 M

u u u

Output Common Input

A N 7 8 L 0 5 M

4) AT24C16N-1 OSI-2.7 (XA0368)

1 6 K b it s C M O S S e ria l E E P R O M

AO

A1 IZZ 2

A2 C Z

GND

1 =

■ =

1

3

4

>

H

N>

O

_k

o>

z

8

7 = □ TEST

6

5

= l

ZD

Vcc

SCL

SDA

5) LA4425A (XA0410)

5 W A u d io P o w e r A m p lif i e r s

Pin Nam e

AO to A 2 Addres s inputs

SD A

SC L

Te s t

NC N o conne ctio n

Serial D ata

Se rial Clock

Test Input {GN D or Vcc )

Function

12

1 2 3 4 5

Page 13

6) M64076GP (XA0352)

Dual PLL Synthesizer

XB o

SI

C P S

RS T

Vc c

Fini

Lo c k l

PD1

VT1

VF

1

C

2 19

c

3 18

□

4

c

5

c

6

c

7

c

8

c

9

c

10

c

Equivalent Circuit

Fin2 0

2

o>

o

o>

O

“O

GND

20

□

Xin

□

Xout

□

17□OP2

16□OP 1

15□Fin2

Lock 2

14

□

13□PD 2

12□VT 2

11

GND

□

Pa ramet er S ym bol

Pow e r s upp ly vo lta ge

LPF sup ply voltage

Lo c a l oscillator input leve l

Lo c a l os cillator input fre quen cy

Xin input le vel

Xin input freq uen c y

— Data latch (17bit)

Local 2

programmable divider

Cond ition Min.

Vcc

Vin

Fin

Vxin

Fxin

Fin-8 0 ~520MH z

Vin =-10d Bm

VF - ■ 9 12

Fin -80-52 0M H z

Vcc-2 .7~5.5 V

Vin»-20 ~ -4d B m

Vcc-2.7 -5 . 5 V

Vcc- 2 .7 ~5 . 5V

Fx in=1 0 -25MH z

Sin e w a v e

Vçc- 2 .7 ~5 . 5V

Vx in-0 .4 ~ 1 .4 V p -p

Ty p. Ma x. Unit

2.7

-

-20

-

80 - 520

0.4

- 1.4

10

-

5.5

-4

dBm

M H z

Vp -p

25 MHz

V

V

Data latch (16bit)

Reference frequency 2

programmable divider

Reference frequency 1

programmable divider

............I.......

Data latch (16bit)

Local 1

programmable divider

I ~

"— Data latch (17bit)

' — Data latch (6bit)

"

GND

13

Page 14

7) M57738LR (XA0447)

M57788MR (XA0313)

M57788HR (XA0448)

U H F F M 3 5 W R F P o w e r M o d u le

S' O

D

o

p

O

il

5 c

t'i

o s

8 ) M67746 (XA0412)

1 4 4 - 1 4 8 M H z 6 0 W

R F P o w e r M o d u l e

D

M57788MR

5 4 3 2 1

>*

*5 .

o 2

a

D

? !

TO

Q g

I I

iT ©

S) 0)

¿3 ^

w a

CM W

o |

Q E

iS >*

<0 Q.

V) D

(13

a

V)

M67746

12 3 4

O

Q

ID C-

.§* >-c

” & E

« 5 m

>

3 CM

Q |

I I

iT

C-

4_, (Q

5 c

t i

o s

<Q

If

^ s

c l o

£ 52- - u > &

I f

3 s

Q .O

C '«i’

§

S

c

c

T3

c

Supply voltage

D

O

6

Total current

Input power

Output power Po

Operation case temperature

Storage temperature

f=430~450MHz, Vcc1<13.5V, Zg»ZI=50ii

Supply voltage Vcc 17

Total current

o

Input power Pin(max)

Output power

Operation case temperature

Storage temperature Tstg

Zg=ZI=50£i

Ratings

Ratings

Symbol

Vcc

Icc

Pin

Tc(op)

Tstg

Symbol Ratings

Icc 20

Po(max)

Tc(op)

Ratings

17.0

12

0.8

50

-30—i-110

-40—1-110

600

70

-30 to+110

-40 to+110

Unit

V

A

W

W

°C

°C

Unit

V

A

mW

W

°C

°C

14

9) M68702H (XA0444)

1 5 0 - 1 7 5 M H z 6 0 W

R F P o w e r M o d u le

T3

c

3

D

M68702H

12 3 4

>

0 ^

Q OJ

0)

S? ^ «

jS ^ c

I f

3 O

” & E

Q .O

C CO

1 3 *

3 OJ o

V) y - CD

O -s

O g

? !

il £

■5

CL

■5

O

T3

C

Supply voltage

o

c

5

n

c

E

©

Total current

6

Input power

Output power

Operation case temperature

Storage temperature

Zg=ZI=50£i

Ratings

Symbol

Vcc

Icc 20

Pin(max) 600

Po(max) 75

Tc(op) -30 to+110

Tstg

Ratings

17

-40 to+110

Unit

V

A

mW

W

°C

°C

Page 15

10) MC3372VM (XA0343)

L o w P o w e r F M IF

Equivalent Circuit

(1 6 )

---------

(15 >

Sq uelch Trigg er

Oscillator — » Mixer

(! )— H d)— © — © — ¿>

4k

Filter A m p

------

& — ® -

Crystal O s c .

Crystal O s c . nz

Mixer Output

Vc c nz

Lim iter Input

De cou p ling

Lim iter Output

Qua d Input

Ta=25°C

Parameter Pin No.

Max. supply voltage

4

Symbol Ratings Unit

Vcc 2.4-9.0 Vdc

RF input voltage 16 Vrf 0.005-10 mVrms

RF input frequency 16

Oscillator input voltage

IF frequency

1

-

Limiter amplifier input voltage 5 Vif

Filter amplifier input voltage 10

Squelch input voltage

Mute sink current

Temperature range

12

14

-

Frf

0.1-100 MHz

Vlocal 80-400 mVrms

Fif 455

0-400

Vfa

Vsq

0.1-300

0or2

Isq 0.1-30

kHz

mVrms

mVrms

Vdc

mA

TA -30-+75

1

l=

2

3 14

c :

4

i= 5

6 11

cz

7

c=

8 9

c=

°C

15

13

12

10

= ]

=1

=1

= •

=3

= □

Mixer Input

GND

Mute

M ete r drive

Sq uelch Input

Filter Output

Filter Input

De m odu lator

Output

11) MC7808CT (XA0082)

8 V V o l t a g e R e g u la to r

Test Circuit

O

78L08

Page 16

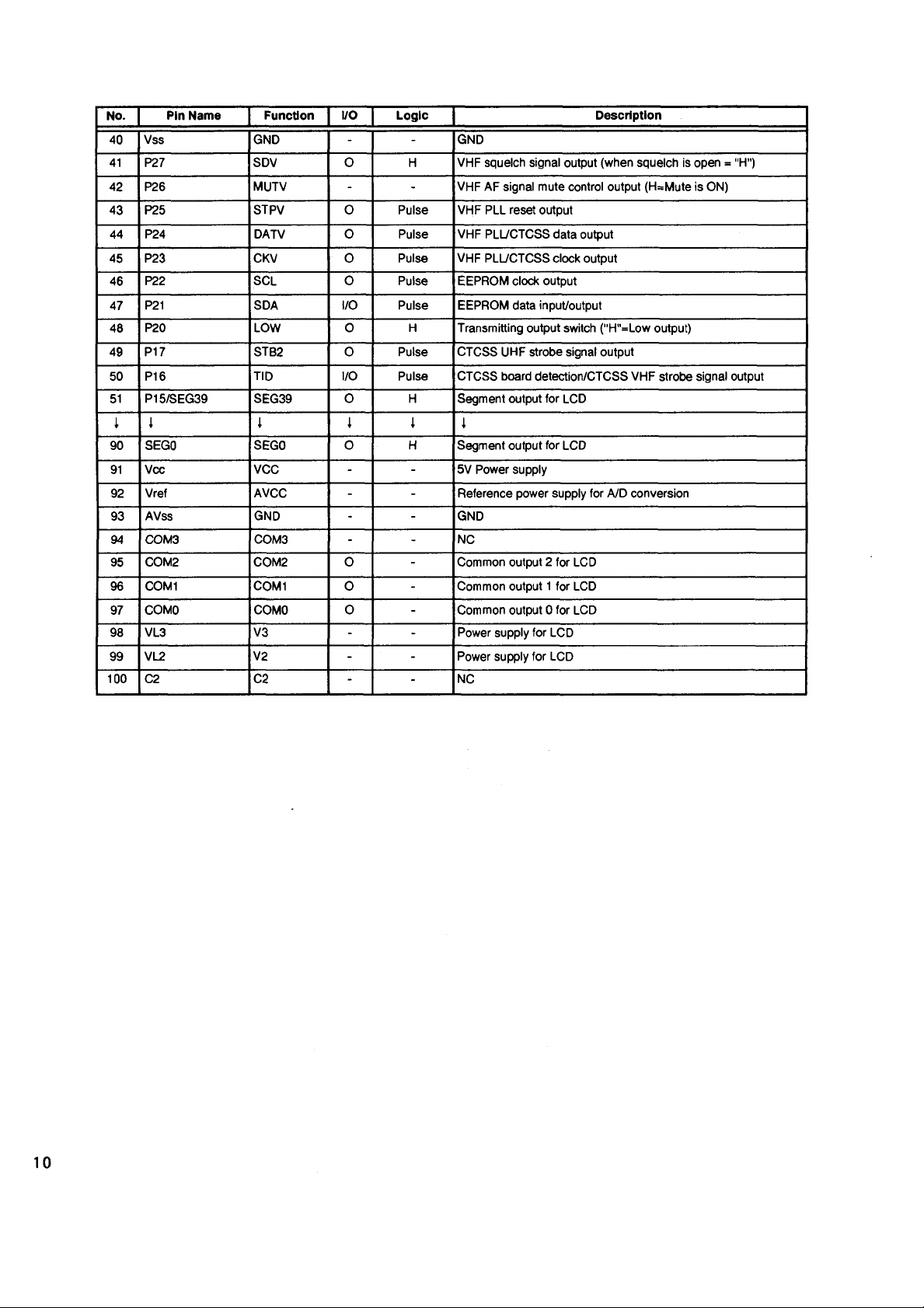

12) NJM4558 (XA0097)

O p e ra t io n a l A m p lif ie r s

13) RH5VA60AA (XA0315)

C - M O S V o l t a g e D e te c t o r

Equivalent Circuit

VD D r

................................................................

- o

OUT

A Output [

A -Input [

A +lnput I

V- [

1 A \

2

Â

3 6

4 5

h 7

8

V+

IB Output

B -Input

B + Input

14) RN5VL25AA-T1 (XA0309)

C - M O S V o lt a g e D e t e c t o r

Equivalent Circuit

VD D r......................................................................

(* >

Vr ef

VSS

u u u

OUT VDD VSS

©

R H 5 V A 6 0 A A

OUT

O

u u u

VSS

©

OUT VDD VSS

R L 5 V L 2 5 A A

16

Page 17

15) TC4W53FU (XA0348)

M u l t i p l e x e r /D e m u lt ip le x e r

F u n c t i o n T a b le

Control input

INH

L

L

* Don't Care

ON channel

A

L

H

*

chO

ch 1

NONE

COMMON

INH

VEE

VSS 4

1

2

3

16) Transistor, Diode and LED Outline Drawings

T o p V ie w

•

4^

U l

03 6

~n

8

7

I]H

17

Page 18

17) LCD Connection

No.

COM.3

1

COM.3

COM.2

COM.1 No. COM.3

2 COM.2 27

3 COM.1 28

4

(R)ISQLI

5

(R) 50

(R)CD

(R) 75 (R) 25

6 10c 10b

7

10g 10a 10d

8 10e 10f

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

9c 9b

9g

9e

8c

eg

B e 8f

7 c 7b

7g

7e

14c

14g

14b

14a

14e

13c

13b 6f

13g 13a 13d

13e

13f

LOW F

(L) 50

(L) 75 (L) 25

9a

9f

8b

8a 8d 38

7a

7f

14f

(H) I I I

(G) I I I

@ .

( n i l l

9d

(D .

(E )« //

(R) □

(R) E l

7d

7a

6bcg

14d

6e

(R)IMAINI

(D) I I I

COM.2 COM.1

26

29

30

31 4e 4f

5c

5g

5e 5f

4c

4g

5b

(C)///

5a 5d

© .

4b

<B) / / /

4a 4d

© .

32 3c 3b (a x n

33

34

35

36

37

3g

3e

2c

2g

2e 2f

12c

39

12g

40 12e

41 1 1 c

42

110

43 11e

3a 3d

(L) I SOL I

3 1

2b

(u m

2a

(L) □

12b

(L) E l

12a 12d

12f

1bc

11b

11a

11f

11 d

(L)IMAIN I

2d

ifg

Page 19

Page 20

2) VHF Unit Assembly

fc

Page 21

T S0 130

A: AV0002

B: AW0001

C: AA0050

D: AB0008

E: AV0004

Torque=4kg-f*cm

Torque=4kg*f*cm

Torque=4kg*f*cm

Torque=4kg*f*cm

Torque=4kg-f*cm

Page 22

PARTS LIST

M < * 0 © ' J W W W S ( i) M - * 0 ( 0 # ,,J OÎ() !o iS u ÎO-‘ 0 ( D 0 1 S O ) W A W M - * 0 < Û Œ ' IO > W A W M - , 0

iOOOOOOOOOOOO

mmcccccccccc

;§ sg ëë ëë ëë|| |

iMinwfoîniov’ ê Îi o5 (^

cc c c cccc cccc c ccc fnc c cS ccc c w c ccc c g c

g8g88888gg88gSSg88|g§8888§88§||§

o o o o o o o o o o m o o o o o o g o o o g o o o o o m g o g m o

3,3,3,2,3,ZZZ3,3,®ZZZZZ?2Z2ZZZZZZZyzZZsji

■o' -o' -o' -o' -5 -o ■© ■o -o -o a ’o ’o'o'o'5'o'o'o'o'o'o'o'o'o'o'o Q tj tj Û ^

--

----------------------------------

-----

-----------

flüflfiwwwwwwww**-«

^-lOOOOOOOriOOOOOOOopppoP

OOOOOOOr<OOOOOOOè

...................I......................

oooo oo ooo oo ogo ooo

I.

s S

z7

o2.

Note: Versioni-TE1, Verston2-TE2 Note: Versk>M»TEl, Vers»n2«TE2

o o o o o o o

8 § g 8 6 2 8

OOOOOOOOOOOOOOQO

cccccc cc ccm c wcc w

O O O O O O O

Z 2 Z Z Z Z I

T3 ï TJ T3 ü 'D Î

O O O O O O O

922222 2992

0)0 0)0)9 0)0090)

0)CDQ)ODQ)Q)(SQ)QJQ)Q(p

I I I I I I I I I I

is§§§§sg8gsgsgggs§§gg§gQgsggsg 8 8 8

/T10000000000

fz zz z z z zz z z

oooSoHOOHoooooooooooooooooopopppi.pg.i.

at • *• . • n» ........................................................................................................................ o o o

o2 ^ 2 2 y 22222

fngQg§Ogg®2 ®

s 2 I e e I

p op o ro ® —

> -* c -* -* >

î ï s ï ï L

I 1 S 1 1 S !

>>>>>>>>>>

o o o o o o

c c c c c c

m m m m m m

i S 2 P i s

fi S o fo C 10

O O -j "J w w

o o o o o o o g o o o o g g g o o g o g g g g g g g g g g g g g

s^ saKssïslISsiisfeSës^ g sKSëîiS K sys

O O O p O O

ooooooooo

cc ccc ccc c

..............

ëëëë ~

5 o> -» -»

■Nj Ü1 -sj «o

■o,ç■o■o■o,D■o■o■o,o■

&

I

00000000000000000000000000000000000

w w c ç m m c ç ç ç ç ç w ç c ç c ç H S a c c c c c c c c c c c c c m

OHHOOOOHOOOOO

e s s e e e E s e e c E e æ e ^ B É É S g

O l zx D II )0 ] D ) -i IS C 0 IS D ia )N 0) y- ‘ 0)IS y( D

I I î i i S i lJ - - Si m i O

H lllii Siig Sa sis SiliS

XoooooKoooo’DtJoS

S Sr oM w Sy M in Ku io jo «^

^ 3 3 3 3 | 3 5* 3 3£ 3

> > i > > > > z > > > >

o o o

c c c

8 8 8 :

OOOOOOOOOOOOOOOOOOOOOp

zz z z z z zz zz z z zizz z z s z ? Î

■D 'O'S 'D'O 'O'O 'a' O'O 'O 'D'D 'D'D'O ^T J pT3 p W

oooooooo oo ooooo oo ooo

CCCCCCCCCCOCOPOCPPQO

ëë8 ëS ëëëSi$8Sg

O )MIO O)O )W (< )(< )O O0 )Oft O> ..

ü i- *u ci üi ü tu iC r w w 'jr oo ' CO ( D

22222222S2Sn

-* -‘ - i“i o»oig>Ô)o2on

ËË §§ s§is

S S îîi S Ïp p

ï ï î ï ï ë ï s *

sseSSÇSÇ®

¡ÎSïoôrOÎA

55 5qqCo

2

_* o

ro to

s yi ii

O O O

o o o o g g g o o g n g g g o o

8 8

ro ro

? “

>

OOOOOOOOOO

oàjCTJtncntntncncucn

-■OOli'W NO'^iw

OOQOOpOOOOO

® Z 9 ® <® Z Z $ ® Z

i o i 3 3. I o o i. 1 o

o * o’ Ô o o o c

O O O o

3JIOOOOD3JO

Biiiieei

s|SËËaa§

g w w i x g i l

P o J t P o P P o

T r j ï ï Î N r T M

“

J ^ S S ?

§ > > > > >

mm mm

lo

( û o os a iy > * ^ u ro

O) O) (D U (1)

8 8 2 g g

(Ü (A 09 M U

z7

oJB.

z2?

o2.

VHF MAIN Unit VHF MAIN Unit

O) o S 8 S -J

* *5 1 1 2

S s

lo lo K) K) b Kj m

C E C C

o « ot s

01 ui u 10 -* o

Q O O O O O O O O O O O O O

Bf

o-* ->-k-‘ uu u Ë ^ < n > 6 u

•£ -* -* -i r‘ tn oiai(n aiuiaiü> cn

cBWN io roMmmm oniino""

gffgggggggggggggfgfü

$ 2 . 2 .

^ -1 (o n n

V *-» w w w ® S

ggggg I

s z s s z s s s

H 3 3 I 3 ? I 3

W W ^ w P W wt0

O O O ^ O O ^ Q

(i >W U(D ^U *^IO

(A in i» en i» inPtn

— jji'

pp p p p p“Tp0 ggg

boŒWOlŒOjP“ '

z z z z z

O O O O O

* Z Z 3 1 z .

■O- 'ü "O "6

OO O O

£ S S Î 2 88 2Q g 5

7? c_ c. >>>>>

pii i fIfI

e e

O (D

1

%

O O O O O

d Ç 5 5 S

g i 8 § 3

s g s s ê

i g

c_ c_ c_

OOOOOOOOOOQOOOO

S'S'S'ZZZZZZZZZ. ZZ. =:

,6’ '0',D -o '-o -o ,D ' 6 -O ‘O 'C 'O ,O 'of l

OHOOOOOOOOOOOOO

fi)........................................... . . . ^

i

000

e E 2

CD O D OD D Q

i s g i i i o i

8 S 8 8 S 8 8 8

2S|5

> 2 > > > Z >

O O O C7 O O

-< & u ro -< o

x x x x x x x x x x x x x x x

O O O O Q O Q O O Q O O Q O O

S g 2 2 2 2 2 S 8 8 8 S S S 2

io u i u u u u u û ^ 5 - ‘ V'^!;u

M i f Ô M t O f O O O O - W Î - O l O O )

? ?

I i i I i Î

0

ï W W W W M

^ co < < < <

ro £j) ro ^ M M

1

T, 01 v* cji tn tn

8

m T *0 "D "D

ï 5 ï 5

S i

E i

???5?

11 11

8

O O O O O O O

e

O O O g

X I I ®

Î I I Î

H .-I r* r* •T* C* *

m m fo m m m r

I I î

—* ro S

IO M S

e s S

i i ï i i

s g

5

S

¡6 ï

I

Z?

P®

22

Page 23

V HF MAI N Un it

Parts No.

as

Q1 XI0 0 9 5

0 2

XT0095 Transistor 2SC 4 081 T10 6R

03

XT0095 Transistor 2SC4081 T106R

04 XU0160

05 XU0174

XT0095

0 6

07 XT0124

0 8 XT0124

XT0048

09

XT0084

010

011

XE0013

012 XE0013

XT0095

013

XE0021 FE T

015

XT0017 Tra nsistor

016

017 XU0061 Transistor UN5211 -T X

018 XT0061

019 XU0061 Transistor U N 52 11 -T X

020 XU0180 Transistor

021 XU0061

022 XU0160

XT009 5 Tra nsistor

02 3

XU0160

025

026 XT0095

027 XU0179 Tran sistor

XU0180 Transistor UN52 13

028

XT0095 Transistor

029

030 XT0146

R1

RK3038 Ch ipR.

R2 RK3042

R3

RK3058

R4

RK3071 C h ipR.

RK303 4

R5

R6 RK3026

R7

RK3042

R8

RK3054

RK30 50

R9

RK3032 Chip R.

R10

R11 RK3071

R12 RK30 57

RK3054

R13

R14

RK3059 Ch ipR.

RK3041 Ch ip R.

R15

RK3041

R16

R17

RK3058 Ch tpR .

RK3030

R18

R19 RK3046 C h ipR .

R20 RK3038

R21 RK3050

RK3056 Chip R.

R22

R23 RK3038 Chip R.

RK3038

R24

R25 RK3043 Chip R.

Description

Transistor 2SC 408 1TT06R R 26

Transistor DTC3 63E KT146

Tra nsistor UN 5112-TX

Tra nsistor 2S C408 1T1 06R

Tra nsistor 2 S C 4215-Y(TE85L )

Transistor

Tra nsistor

Transistor 2SC2954-T1

FE T

FET

Tra nsistor

Tra nsistor

Transistor

Tra nsistor

Tra nsistor D T C 363E K T146

Transistor

Transistor

Chip R.

Chip R, ERJ3GSYJ4 73V

Chip R.

ChipR.

Chip R.

Chip R.

Chip R .

Chip R.

Chip R.

C ttp R .

Chip R.

ChipR.

Chip R. ERJ3GSYJ1 02V R74

Chip R.

Chip R.

Parts Name

2SC421 5*Y (T E 85L )

2S C 3 357T 1 RE

3SK18 4S-TX

3SK184S-TX

2SC4081T106R R38 RK3 026

2SK88 0GRTE 86L

2S A11 62YT E85

2SB11 32T10 0Q R 42

UN 5 2 Î3

UN 5211-T X

DT C36 3EK T146

2SC4081T106R

2SC4081T106R

UN 5114

2SC40 81T 106 R

2SC5 226 -4-TL R52 RK3042

ER J3G SYJ102V

ER J3GSYJ22 2V

ER J3GSYJ56 4V

ER J3G SYJ 471 V

ER J3G SYJ 101 V R59 RK3026 Chip R.

ER J3GSYJ22 2V

ER J3G SYJ 223V R61

ER J3GSYJ10 3V

ERJ3 GSY J331V

ER J3G SYJ 564V

ERJ3 GSY J393V

ERJ3 GSY J223V R67

ER J3G SYJ563V

ÊR J3GSYJ18 2V

ER J3G SYJ 182V

ER J3GSYJ47 3V

ERJ3 GSY J221V R72

ER J3G SYJ472V

ERJ3 GSY J103V

ER J3G SYJ333V

ER J3GSYJ10 2V R77

ER J3G SYJ102V

ER J3GSYJ27 2V

Ref.

Ver.

I*

Parts No.

No.

RK30 56 Ch ip R.

R27

RK30 50 Chip R.

R28 RK3066

R29 RK3038 Chip R. ERJ3G SYJ 102 V

R30

RK30 62

R31

RK30 38

R32 RK3071 C hip R. ERJ3 G SYJ 564 V

R33

RK30 38

R34

RK30 26

R35 RK302 6

R3 6 RK30 45

R37

RK 30 38

R39 RK3038

RK30 38

R4 0

R41

RK30 45 Chip R.

RK30 14 Chip R.

RK3034

R43

R44

RK30 22 Ch ip R. ERJ 3GSY J47 0V

RK3034 Chip R. ERJ3G SYJ471V

R45

RK3043

R46

R47 RK010 7 C hip R.

RK3014

R47

RK40 26

R48

RK40 18 Chip R. ERJ-12YJ2 20 V

R49

R50 RK003 6

R51 R K3042 Chip R. ERJ3 GSYJ 222 V

RK3058

R53

RK3057 Chip R. ERJ 3GSY J39 3V

R53

R54 RK305 0

R55 RD0062U

RK30 26

R56

R58 RK3062

RK3062 Chip R. ERJ3GSYJ104V

R60

RK30 62

R62 RK3 062 Chip R. ERJ3 GSYJ104 V

R63 RK3052

RK3014 Chip R.

R65

R66 R K3042

RK30 26

R68 R K3060

RK30 37 Chip R.

R69

RK30 50

R70

R71 R K3050

RK 30 50

R73 RK3050

RK3041

RK 30 54

R75

R76 RK3046

RK3044

RK 301 8 Chip R. E R J3G S YJ2 20V

R78

R79

RK 30 62

Description Parts Name Ver

Chip R.

Chip R. E R J3G SYJ 104 V

Ch ip R. E R J3G S YJ10 2V

Chip R. E R J3G SYJ 102V

Chip R. E RJ3G SYJ 101V

Chip R. ERJ3G S YJ1 01V

Ch ip R.

Chip R.

Ch ip R.

Chip R.

Chip R.

Chip R.

Chip R.

Ch ip R.

Chip R.

Chip R. ERJ6G EYJ122V

Ch ip R.

Chip R. ERJ3GSYJ473V

Chip R. ERJ3GSY J10 3V

Carto n R.

Chip R.

Chip R . ERJ3GSYJ104V

Chip R.

Chip R .

Ch ip R.

Chip R .

Ch ip R.

Ch ip R. E RJ3 GSYJ10 3V

Ch ip R . E R J3G SYJ 103V

Ch ip R. E R J3G SYJ 103V

Ch ip R. E RJ3G SYJ 103V

Chip R. E RJ3GSY J182V

Ch ip R.

Chip R. ERJ3G S YJ472 V

Chip R. ERJ3GSY J33 2V

Ch ip R.

ER J3G S YJ3 33V

ER J3G SYJ 103 V

ER J3G SYJ 224 V

ER J3G S YJ3 92V

ER J3G S YJ1 02V

ER J3G SYJ 101V

ER J3G S YJ1 02V

ER J3G SYJ 102 V

ER J3G S YJ3 92V

ER J3G S YJ1 00V

ER J3G S YJ4 71V

ER J3G S YJ2 72V

ER J6GE Y 0R00 V

ER J3G SYJ 100 V

ERJ-12YJ101V

ER J3G SYJ 222V

ER D S2T 473A T

ER J3G SYJ101V

ER J3G S YJ1 01V

ER J3G SYJ 104V

ER J3G SYJ 153 V

ER J3G S YJ1 00V

ER J3G SYJ 222 V

ER J3G S YJ1 01V

ER J3G SYJ 103 V

ER J3G SYJ 821 V

ER J3G SYJ 223V

ER J3G SYJ 104V

T,E

U

T.E

U

No te: V e r sio ni«TE1f Ve r sion2« TE 2

Page 24

Ref.

Parts No.

No.

R81

RK 303 8

R82

RK30 50 C hip R.

R83

RK30 62

R84

RK3001 Chip R. ERJ3GSYO ROOV T.E R141

R84

RK3Q26

Rfl6

RK30 54 Chip R.

R87

RK30 58 Chip R. E R J3G SYJ 473V

R88

RK30 34 Chip R.

R89

RK30 62 C hip R.

R92

RK 30 26

RK 307 4

R9 3

R94

RK 30 26

R95 RK3038 Chip R. E RJ3GS YJ1Q2V

R96

RK30 38

R97

RK30 38

R98 RK3038

R99

RK01 05

R100

RK30 62

R101

RK 305 6 Chip R-

R102

RK 303 8

R103 RK3050 Ch ip R. E RJ3G SYJ 103 V

R104

RK30 26

R105 RK3026 Chip R. ERJ3G S YJ101 V

R106

RK 302 6 C hipR.

R107

RK30 70

R108

RK 30 42

R109

RK 305 8

R110 RK3038 Chip R.

RK 30 58

R111

RK 30 54

R112

R113

RK 305 0 Chip R. E RJ3GSY J103V

R114

RK 305 0

R115

RK 305 8

R116

RK3001

R118 RK3026 C N p R. ERJ3 G SYJ 101 V

R119 RK010 7 Chip R.

R120

RK3001

RK30 50

R120

R121 RK30 58

R122

RK 305 0 C hip R. E R J3G S YJ1 03V

R123

RK 012 8 Chip R. ERJ 6GEY J5R 6V

R124 RK0036 C hip R. ER J6G E YJ1 22V

R125 RK3058 ChipR. ERJ3G SYJ 473 V

RK3054

R126

R127

RK3031

R128 RK3069 Chip R. ERJ 3GSY J39 4V

RK30 44

R129

RK30 26

R130

R131 RK3042 Chip R. ERJ3G S YJ222 V

R132

RK3051

R133 RK3023

R133

RK3Q26 C N p R. ERJ3GS YJ1 01V

R134

RK30 74

R135

RK 3050 Chip R.

Description

ChipR .

Chip R . ERJ3G S YJ1 04V

Chip R. ERJ3GS YJ1 01V

Chip R.

ChipR.

Chip R. E R J3G SYJ 101 V

Chip R. E RJ3 G SYJ 102 V

Chip R.

Chip R.

Chip R.

Chip R. E R J3G SYJ 104V

Chip R.

Chip R. ERJ3GSY J10 1V X1

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. E RJ3 GSY J47 3V

Chip R.

Chip R. ERJ3GSYOROOV

C N p R .

Chip R. E R J3G SYJ 473V

Chip R.

CN p R.

Chip R. ERJ3 GSYJ33 2V

Chip R. E RJ3 G SYJ 101 V

Chip R .

Chip R.

Chip R.

Parts Name

ERJ3G SYJ 102 V

ER J3G SYJ 103V

ER J3G S YJ2 23V

ER J3G SYJ 471V R144

ER J3G SYJ 104 V

ER J3G SYJ 101V

ER J3G S YJ1 05V T,E R147

ER J3G SYJ 102V

ERJ3G SYJ 102 V

ER J6G E YJ2 R 2V

ERJ3G SYJ 473 V

ER J3G SYJ 102V V R4

ER J3G SYJ 101V

ER J3G SYJ474V S D0034

ER J3G SYJ 222 V

ER J3G S YJ4 73V

ER J3G SYJ 102 V

ER J3G SYJ 473 V

ER J3G SYJ 223V

ER J3G SYJ 103V

ERJ3GSYOROOV

ER J6G S Y0R 0 0V

ERJ3G SYJ 103 V

ER J3G SYJ 223V

ER J3G SYJ271V

ER J3G SYJ 123V

ER J3G SYJ 560V T,E

ER J3G SYJ 105 V

ER J3G SYJ 103V

Ref.

Ver.

15

T.E

T.E

1.2

E.1,2

1.2

1,2

1,2

T.E

15

15

Parts No.

No.

R137

RK 301 8 C N p R .

R138 RK3046

R139

RK3050

RK3054 Chip R.

R142

RK30 48

R142

RK3053

R143

RK1998

RK3042 Chip R.

RK 305 4

R145

R146

RK3057 CN p R. ER J3GSYJ393V

RK11 07 C h ipR.

TC1 C T 001 2 Trim . C. C T Z10A W

TH1

XS00 30

VR1

RH 0108

VR 2 RH0104 Trim. Pot

VR 3

RH 01 06 Trim. Pot EVM 1YSX 5 0B04

RH 01 04 Trim. Pot EVM 1YSX50 BE4

XK00 03 Discriminator

X2

XQ0 081

Y1 T Z0049

Y2 TZ 0049

Description

CN p R.

CN p R.

Ch ip R.

Ch ip R.

Chip R.

Chip R .

Therm istor

Trim. P ot

Crystal

Spring

V HF MAIN Unit

Parts Name Ver.

ER J3 GSYJ220 V

ERJ3GSYJ472 V

ERJ3GSYJ103 V

ERJ3GSYJ223 V

ERJ3 GSY J682V

ER J3GSYJ18 3V

MC R50JZHJ2R 2E

ERJ3GSYJ222 V

ERJ3GSYJ2 23V

ER J8G EY0R 00V

NTC CM16084LH 223KC T,E

EV M1Y SX5 0B15

EVM1Y SX50B E4

CDBM 450C7

38CHT 2 155M H z T .E

Earth S pring DR130

Silicon Dumper

Silicon Dumper

T.E

15

15

15

T,E

CO

CM

15

15

Not e: Ve r sfc>nl-TE1, Ver sion 2-TE 2

Page 25

UH F M AIN Unit

Ref.

Parts No.

No.

C201

CU 30 47 Chip C.

C2Q2

CU 9018

C203

CU 9018

C204

CE0312 Electrolytic C.

C205 CU3044

C206

CU 3044 Chip C.

C207

CU 8035 Chip C. C 20 12B1E 393K

C208 CE0 312

C209 CU8034

C210 CU3041

C211

CU 3049 Chip C. C 160 8JB 1E1 53KT-A

C212

CU8042 Chip C . C20 12J B1C 104KT-A

C213

CU3035 Chip C . C16 08JB1 H10 2KT-A

C214

CU3023 Chip C .

C215

CU 3023

C216 CU3035

C217 CU3047 Chip C.

C218 CU8Û42

CS00 65

C219

CU3Q47

C220

C221 CU3Û51 Chip C .

C222 CE0312 Electrolytic C.

C223

CU 3059 Chip C.

C224 CU3022

C225 CU3059

C226 CU3Q59

C227

CU 3010

C228 CU3007 Chip C .

C229 CU3018 Chip C .

C230 CU3005

C231 CU3011 Chip C.

C232

CU 3035

C233

CU 3035

C234

CU 3035 Chip C. C l608 J B t H l02K T -A

CU 3035

C235

C236 CU3004 Chip C.

C237 CU3035

C238 CU3015

C239

CU 3035

C240 CU3011

C241

CU 3035

C242

CU 3035

CU 3035

C243

C244 CU 3035

C245 CU3 03 5 Chip C. C160 8JB 1H1 02KT-A

C247 CU 3 011

CU 3004

C248

C249

CU 3035 Chip C. C 1 6 0 8JBtH t02K T -A

CU 3035

C250

C251 C U3035 Chip C. C160 8JB1 H1Q2K T-A

C252 CU3004

C252 CU 3003 C hip C.

C2 53 CE0 315 Electrolytic C.

Description

Parts Name

UHF MAIN Unit

Chip C .

Chip C . C 3216J B1C105MT-N

Chip C.

Electrolytic C.

Chip C. C 2012X7R1E 333K

Chip C. C 160 8JB1H332 KT-A

Chip C . C 1608C H 1H1 01JT-A

Chip C .

Chip C. C 2012JB1C 104 KT-A

Chip TantaJ

Chip C. C 1608JB1H 103 KT-A

Chip C .

Chip C. C 160 8JF1E104ZTA

Chip C.

Chip C.

Chip C. C 160 8CH 1H04 0CT -A

Chip C. C 1608JB1H 102 KT-A

Chip C .

Chip C .

Chip C.

Chip C.

Chip C.

Chip C.

Ch ip C.

Chip C.

Ch ip C.

Chip C. C16 08JB1 H10 2KT-A

Chip C. C16 08C H 1H10 0CT -A

Chip C.

Chip C. C 16 08JB1 H10 2KT-A

Chip C. C160 8CH1H0 30CT-A

C1608JB1H 103KT -A

C321 6JB1C 105MT-N

EC EV1C A100R

C1 608JB 1H562K T-A

C1608JB 1H5 62KT-A

EC EV1 C A10 0R

C16Û8 CH1H101JT-A

C1608J B1H 102KT -A

C16Q8J B1H103K T-A

TM C SA1D 684M T R

C1608J B1E22 3KT -A

EC EV1C A100R

C l 608JF1E104ZTA

C16Û 8C H1H 820JT-A

C1 608JF 1E1 04Z TA

C16 0 8 C H 1H090C T-A

C160 8CH1 H060CT-A

C16 0 8 C H 1H390JT-A

C1608CH1H 100C T-A

C160 8JB 1H1 02KT-A

C1608JB 1H1 02KT-A

C 16 0 8CH1H030CT-A

C 1608JB1 H102KT-A

C1608CH 1H220J T-A

C 1608JB1 H102KT-A

C 160 8 C H 1H10OCT -A

C160 8J8 1H1 02KT-A

C1608JB1H 102KT -A

C1608J B1H 102KT -A

C 16 08C H1H030CT -A

C 160 8 C H 1HQ20CT-A 2

EC E V1CA 4 70P #

Ref.

Ver.

T.E.1

Parts No.

No.

C255 CU3023

CE 0312

C256

C257 CU3031 C h i pC . C16Q 8J81H471K T-A

CU3031

C258

CC5051 Ceram ic C.

C259

C259 CC 505 0 Ceramic c .

CC504 9 C eramic C.

C259

C260

CU 303 5

C262 CC 505 5

CU 300 2

C263

C2B4 CU3003

C265 CC505 8

CC 5 059 C era m ic C. RCC05SL 120J-L46AE

C265

C266 CU3002

CU 3003 Chip C.

C267

C268 CC50 5 6

C269 CC50 5 5

C269 CC50 56 Ceram ic C.

CC 5057 Cer amic C.

C269

CC 5054 Cer amic C.

C269

CC5054 C eramic C.

C270

CC 506 0

C271

CC 507 3

C272

C273 CC50 50 Ceram ic C.

C274 CU3004 C hip C.

CU 3004

C275

CU 303 5 Chip C. C16 08JB1H102KT-A

C278

CU 303 5

C279

CU 303 5 Chip C.

C280

CU30Q2 Chip C .

C281

CU 303 5 C hip C.

C282

CU 3035 Chip C. C1608JB1 Hi 02KT-A

C283

CU 302 3

C284

CU 303 5 C hip C.

C285

C286 CU303 5

C287 C U 306 4

CU 300 3

C287

C287 CU30 02

C288 CU30 12

CU 301 7

C289

CU 303 5 C h ipC.

C290

CU 303 5

C291

CU 303 5

C292

CU 3 035

C293

CU 3017

C293

C293 CU3011

C294 CU3064

CU 3035

C295

C296 CU30 35

C297 CU3011

CU 3035

C298

C300

CU 3035

CU 8042

C301

CU3Q51

C302

Description

Chip C.

Electrolytic C. EC E V1CA 100 R

Chip C .

Chip C.

Ce ram ic C.

Chip C.

Chip C.

Ce ram ic C.

Chip C.

Ceram ic C.

Ce ram ic C.

Ce ram ic C.

Ce ram ic C.

Chip C . C 1608C H 1H 030CT-A

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C. C l 608JB 1E 223KT-A

C16 08CH1H 101 JT-A

C1608JB1H 471KT-A

RCC05SL030C-L46AE

RC C05SL0 20C-L46 AE E

RC C 05SL0 10C -L 46AE

C1608JB1 H102KT-A

RCC05SL070C-L46AE

C1608CH1H01OCT-A

C160 8CH 1H0 20CT-A

DD05 -979SL100 D500

C1608CH1H 010CT -A

C1 6 08CH 1H020CT-A

RCC05SL080D-L46AE

RCC0 5SL07 0D-L46A E T

RCC0 5SL08 0D-L46A E E

RCC05SL090D-L46AE

RCC05SL060C-L46AE 2

RC C 05SL060C -L 46AE

RCC05SL150J-L46A E

RCC06SL56 0J-L 46AU

RC C 05SL020C -L 46AE

C16 08CH1H030CT -A

C1608J B1H102KT-A

C1608 JB1 H 102KT-A

C1 608CH1H010C T-A

C1608JB1 HI 02KT-A

C16 0 8CH1H 101 JT-A

C1608JB1H 102KT-A

C1608JB1 HI 02KT-A

C 1608C H 1H 1R5CT-A

C1608CH 1H020C T-A 1

C1608CH1H01 OCT-A 2

C 16 08CH 1H 120CT-A

C î 60 8CH1H330JT-A

C1 608JB1H 102KT-A

C 16 08JB1H 102KT-A

C1608JB1 H102KT-A

C1608JB1H102KT-A

C16 08CH1H330JT-A

C16 0 8CH1H 100CT-A

C1 608 CH1 H1R5CT-A

C1608J B1H102K T-A

C1608J B1H102K T-A

C 1608C H 1H 100CT -A

C1608 JB1 H 102KT-A

C16 08J B1H 102KT-A

C201 2JB1C 104KT-A

Parts Name

Ver.

T

1.2

T.E.2

1

1

E

E

T.E

1.2

T.E

1

2

E

Not e: Versi on ! sTE I, Vers i on 2»TE 2

Page 26

Ref.

Parts No.

No.

C3Q3 CU 8034 C h ipC. C2 Q12X7R 1E3 33KT-A

C304

CU 7002 Chip C.

C3 05 CU3 047

C306

CU 3019

C3 07

CU 8042

C308 C U 30 47 C hip C.

C309 CU3 019 Chip C. C1608 CH1H 470JT-A

C310

CE0312 Electrolytic C.

C311 CU 3035

CEQ312

C312

C313 CU3 028 C hip C. C16 08CH1H 271 JT-A C372 CU9018

C314

CU 3039

C3 15

CS02 37

C316

CU 3035 Chip C. C 160 8JB1H 102 KT-A C 376 CU30 35

C317

CU 3035

C3t8

CU 3035

C320

CU 3035

C321

CE03 15

C322

CU 3035

C323 CU 3035

C324 CU 3035

C328 CU3035

C329 CE 0374 Electrofytic C.

C330 CU 303 5

CU 3025

C331

C331 C U 3019 Ch ip C. C16 0 8 C H 1H470JT-A

C332

CU 3035

C333 CU 3035

C334

CU 3035 Chip C. C1608JB1 HI 02KT-A

CE 037 4

C335

C336 CU 304 7 Chip C. C1608 JB1 H103KT-A

C337

CU 304 7 Chip C. C1608JB1 H10 3KT-A 0201 X 001 3 6

C338

CE0312

CU 304 7 C hip C.

C339

C3 40 C U 303 5 Chip C. C1608JB1 H10 2KT-A

C341

CE 0316

C342

CU 3035 C hip C.

C343

CU 3035 C hip C.

C344

CS 0049 Chip TantaJ TMCSA1 C 105M T R 02 08 X D0250

CS0 061 Ch ip TantaJ

C345

C346 CU3 035 Chip C. C 1608J B1H102KT -A

C347

CU 3035 Chip C. C16 08JB1H102KT-A D212 XD0230

C348

CU 3035

CS0049

C349

CE 0380

C350

C351 CU3035 Chip C. C l 608JB1H102KT-A 0216

C352

CU 3035

C353 CU 3035

C3 54

CU 303 5 C hip C.

C355

CU 3035 Chip C.

C3 56 CU3 035

C3 57 CU3 035

CU 3035

C358

C359 CU 303 5

Description

Chip C. C16 08JB1H103KT -A C362 CU3002

Chip C. C 1608C H1H470JT-A

Chip C.

Chip C .

Electrolytic C. E CEV1 C A10 0R C370 CS023 7 Chip Tantal

Chip C. C 1608JB1H 222 KT-A

Chip Tantal TMC M A 1 A475 M TR C375 CU 3 035

Chip C. C l 608J B1H 102KT-A

Chip C. C 16 08JB1 H10 2KT-A C3 87

Chip C. C 16 08JB1 H10 2KT-A

Electrolytic C. E C E V1CA 47 0P

Chip C.

Chip C. C1608JB 1H102KT-A

Chip C. C1608JB 1H1 02KT-A

Chip C. C1608JB 1H1 02KT-A

Chip C.

Chip C. C 1 6 08CH1H151JT-A T,E C396 C E 0315 Electrolytic C. EC EV1C A 4 70P

Chip C. C 1608J B1H 102 KT-A

Chip C.

Electrolytic C.

Electrolytic C.

Electrolytic C.

Chip C.

Chip Tantal T M C SA1C 1 05MTR

Electrolytic C. CED SM1C 152M 0215

Ch ip C. C 1608J B1H 102KT -A

Ch ip C.

Ch ip C. C1608JB1H 102KT-A

Ch ip C.

Chip C.

Chip C.

Parts Name Ver.

T 1C 2C31 N 2ACG 0 30C

C2Q1 2JB1C 10 4K T-A

C16Q 8J B1H10 3K T-A C 36 5 CU30 35

EC EV1C A100R

C1608JB1 H l 02KT-A C369

C160 8JB 1H1 02KT-A

16 C V 1 00BS C393 CU3035

C160 8JB 1H1 02KT-A

C1608JB1 HI 02KT -A

16CV 100BS CN2Q3 UE0043 C onn ector

ECEV1 C A10 0R

C160 8JB 1H1 03KT-A

EC E V1EA 4R7R

C1 608JB 1H102KT -A

C1608JB1H 102KT -A

TM C SA1V22 4 M TR

C160 8JB1H 102KT-A

C160 8JB 1H1 02KT-A

C160 8JB 1H1 02KT-A FL201

C1608JB 1H 102KT-A FL202

C1608J B1H 102KT -A

C1608J B1H 102KT -A

C t 608JB1H 102KT-A

Ref.

Parts No. Description Parts Name

No.

C360 CS 0 328 Chip Tantal

T,E,1

1.2

1,2

CU 303 5 C hip C.

C361

CE0312

C363

C364

CU3031

CU 303 5 C hip C. C 1608JB 1H102K T-A

C366

C368 CU30 35

CU 305 9 C hip C.

C373 CU 303 5 Chip C.

C386

CU 3035

CS0 216

CC 504 9

C389

C389 CC505 0

C390

CU 3014 Chip C.

C390

CU 3019 Chip C.

C391 CU3035

CU 3035 Chip C.

C392

C394

CU 3035 C h ipC . C1608JB1 H I 02KT-A

C399

CU 3035

C3 45

CS0063 Ch ip Tantal TM C S A1V 1 0 4 M T R

UE0224

CN201

CN20 2

UE02 28

D202 XD 0250 O iod e MA7 42-T X

D203 XD0141 D iod e

D204

XD 0257

D205 XD0254 Diode 1SS355 TE -17

X0001 3 Diode MI407

D206

D207

XD0301

D209 XD0250

D211 XD0230

D213 X D 0230 O iode DAN 202U T106

D214

XD 0274

XD 0254

XD 0254

0217 XD0 25 4

XC 0016

XF00 14Z

IC201 XA0313

XA0447 IC M5778 8L R 1

IC201

LC201

XA 0448

UH F MAIN Unit

EC ST0J Y685 R

Chip C.

Electrolytic C. ECEV 1CA1 00R

Ch ip C.

Chip C.

Ch ip C.

Chip C.

Ch ip C .

Chip C.

Ch ip C .

Ch ip Tantal

Ceramic C. RCC 05SL010C-L46AE

Cer am ic C.

Ch ip C.

Ch ip C.

Chip C .

Co nnector

Co nnector

Diode D TZ5 .1A TT11

Diode

Oiod e 1SV268

Diod e

Diod e M A742-TX

Oiod e

Oiod e D AN2 02U T106

Oiod e

Diod e 1SS355 T E-17

Diode 1SS355 T E-17

Oiode 1SS355 T E-17

Filter

Filter

IC M57788M R

IC M5778 8HR

C160 8JB1H 10 2KT-A

C1 608 CH1H01OCT-A

C1608JB1 H47 1KT-A

C l 608JB1 H l 02K T-A

C1608JB1 H10 2KT-A

C1 608JF 1E104 ZTA

TM C M A1A4 75MTR

C3216J81C 105 MT-N

C160 8JB1H 10 2KT-A

C160 8JB1H 10 2KT-A

C160 8JB1H 10 2KT-A

C1608JB1H 102KT -A

TM CMB1 A106MTR

RC C05 SL0 20C -L 46A E 1

C1608C H1H 180 JT-A T.E

C1608C H1H 470 JT-A 1.2

C1 608J 81H 102KT-A

C 1608JB 1H 102K T-A

C1608JB1H102KT-A

C1608JB1 H10 2KT-A

19PS^JE

28 5084 00 9 000 808

PI22A02M

1SV237 TE 8 5R

RN73 1V TE -17

MA 742-TX

DAN202U T106

DSA3A1

CF W S 455E

30.850M HZ 3OM1509A

Ver.

1,2

T,E,2

T.E

E

T.E

2

No te: Vers i o nl-TE1 , Ver s i o n2- T£2

CSJ

Page 27

UH F M AIN Un it

Ref.

Parts No.

No.

XA0343

IC202

XA0097

IC203

IC205 XA0119

IC206 XA 00 82

UE0257 Con nector

JK201

UA0040 A Con nec to r

JK202

QC0061

1201

1202 QC00 59

QC 00 59

1203

L204

QK A 2 5 0 Coil

OK A 150

L205

L206 QKA5 5E

1207 QKA95D Coil MR 3.0 9 .5T 0.6

L208 0K A 2 5 0 Coil

L209

OK A15 E Coil

L210 QKA1 5E

1211 QKA15 E Co«

QK A15E

L212

L213

QK A15 E

L214

QK A12E

L215 0K A 1 2 E

QC 03 98 Chip C oil

L216

L217 ÛC 039 8

QA0113 Coil

L218

QA0114 Coil

L218

L218 QA012 8 CoiJ

L218

0 A 0129

L219 Q A0113

1219 QA0 11 4 Coil

L219 QA01 28

0 AO129

L219

QC 00 60

L220

ÛC 0059

L220

1220 ÛC 0057

00 0 0 6 2 Chip Coil

L221

1999

QC00 43

ÛC 0048

L223

QC04 02

L227

XU0061 Tra nsistor UN5211-TX

0201

02 02 X T0095 Tra nsistor

02 03

XT009 5

02 04

XT0095

02 05 X U0174

02 06

XT0095

02 0 7

XT0125

02 0 8 X T0146

02 09 XT0048

XT008 4 Tra nsistor 2SC2954 -T1

02 1 0

0211 XE0013

02 1 2

XE0022

XE0013 FET 3SX 1 84S TX

02 1 3

Description Parts Name Ver.

\c

iC

IC

IC

Chip Coil

Chip Coil

Chip Coil NL 322 522 T -022J

Coil MR3 .0 1.5T0 .6 0 2 2 7

Coil

Coil

Coil

C o «

Coil

Coil

Chip Coil

Coil ÛA0 129

Coil

Coil

Coil QA 0129

Chip Coil

Chip Coil

Chip Coil

Chip Coil

Chip Coil

Chip Coil

Transistor

Transistor

Transistor

Transistor

Transistor

Transistor

Transistor

FET 3SK 184 STX

FET

MC33 72VM-EL

NJM4 558 M T t

AN 8010M-(E 1)

MC 780 8CT

A30 -30190-15

R-B2 .0 ’ 0.2Mplug15A

NL322522T-0 33J

NL322522T-022J 0 2 2 4 XU0054

MR 3.0 2 .5 T 0 .6

MR 3.0 5.5T 0.8

MR 3.0 2 .5T 0 .6

MR 3.0 1.5T0.8

MR 3.0 1.5T0.8 0233 X U0160

MR 3.0 1.5T 0.8

MR 3.0 1.5 T0.8 0 2 3 5

MR 3.0 1.5T0.8

MR 3.0 1.25 T 0.8 E

MR3.01.2 5 T 0.8 E

LON1A15 NJ0 4

LQN1A15 NJ0 4

KE-07319 T R205

KE-07320 E

ÛA 012 8

KE-0731 9

KE-07320 E

QA012 8 1

NL32252 2T-027J

NL32252 2T-022J

NL322522T-015J 2

NL32252 2T-039J R216 RK3030 Chip R.

NL322522T-2R 2J R217 RK304 2 Chip R.

NL322522T-100J R218

LQN1A39NJ 04

2SC4081 T106R R222

2SC4081 T106R

2SC4081 T106R R224

UN 51 12 -TX

2SC4081T106R R226

2SC4245Y(TE 8 5L) R227

2SC5226-4-TL R228

2SC 3357T1 RË

2SK1 577

Parts No.

r

02 1 4 X T 012 5

02 1 6 XU0 16 Û Transistor

XU0061

02 1 7

XT006 1

02 1 8

02 1 9 XT0061 Transistor

XU0061

02 2 0

XU0180

0221

XU0061

Q225»

02 23

XU0028

02 2 5 XU00 46

XU0061 Tra nsistor

02 2 6

XT 011 2

XT0037

02 2 8

02 2 9 X T 009 4

02 3 0

XT 012 6

0231 XT0095

02 3 4

XU 0 180

XT 009 5

R201 RK3055 Chip R.

RK30 60

R202

R203

RK30 58

R204

RK30 38

RK30 38 Chip R.

RK30 42

R206

1 R207

2 R208

T

2 R212 RK3042 Chip R.

T,E

1 R214

RK 305 8

RK3071

RK 303 4

R209

RK 305 4

R210

RK 303 3 C hip R,

R211

R213 RK3066

RK30 26 Chip R. ERJ3G SYJ 101V

RK30 50

R215

RK3041

RK30 58

R219

RK 305 0 C hip R.

R220

RK30 57 C hip R.

R221

RK30 54 C hip R.

RK30 50 C hip R.

R223

RK 305 0 C hip R.

R225 RK3038

RK30 46

RK30 66

RK30 50

RK 305 6

R229

RK 30 38

R230

R231 RK 3043

RK 30 38

R232

R233 RK3055

Description

Transistor

Transistor UN5 211-TX

Transistor

Transistor UNS211 -T X

Transistor

Transistor

Transistor FM C 2

Transistor

Transistor XN11 1M-TX

Transistor

Transistor

Transistor

Transistor

Transistor

Transistor

Transistor

Transistor

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ3 GSYJ 473 V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ 3GS YJ1 02V

Chip R. ERJ3GSY J33 3V

Parts Name

2S C424 5Y(TE85 L)

DT C36 3EK T146

2SB1132T10QQ

2SB1132T 100 Q

UN 5213-TX

UN 6211-TX

XN1213-TX

UNS211-T X

2SB1 292F

2S C 2412 K T 146R

2S A15 76T106R

2SB1 302 S-TD

2SC4 081 T106R

DT C 363E K T 146

UN 5213-TX

2SC4081T106R

ER J3GSYJ27 3V

ER J3G S YJ6 83V

ER J3G SYJ 473 V

ER J3G SYJ 102V

ER J3G SYJ 102V

ER J3G SYJ 222 V

ER J3G SYJ 564V

ER J3G SYJ 471V

ER J3G SYJ 223V

ER J3G SYJ 391V

ERJ3G SYJ 222 V

ER J3G SYJ334V

ER J3G SYJ103V

ER J3G SYJ 221V

ER J3G SYJ 222V

ERJ3G SYJ 182 V

ER J3G SYJ 473V

ER J3G SYJ 103V

ER J3G SYJ393V

ER J3G SYJ 223 V

ER J3G SYJ 103V

ER J3G SYJ103V

ER J3G SYJ 102V

ER J3G SYJ 472V

ER J3G SYJ 224V

ER J3G SYJ 103 V

ER J3GSYJ33 3V

ER J3GSYJ10 2V

ER J3G SYJ 272V

No t e: V e r sio n1» TEl , Vers i on 2= TE2

Page 28

Ref.

Parts No. Description

No.

R234 RK3 038

R235 RK3 062

R2 36

RK30 42

R2 37 . RK30 50

R2 38 RK3 030

R239 RK 304 2 C hip R. ERJ 3GS YJ222V

RK 304 2 Chip R. E R J3G S YJ2 22V

R2 40

R241

RK 30 42

RK 304 4 C hipR. ERJ 3GS YJ332V

R242

R2 43 RK305Q

R244

RK 303 6

R2 45 RK3001 Chip R. ERJ3GSYOROOV

R246 RK3Q22

R247 RK3050

RK 303 8

R248

R250 R K3036

R251 RK3030 Chip R. E R J3G SYJ 221V

R252 RK 303 4 C hip R. ERJ 3GS YJ4 71V

R253 RK0 107

R2S4

RK 401 8

R2 55 RK4 026

RK00 44

R2 56

R257

RKQ128

R258 RK 004 4

R259 RK 010 7

R260 RK3 058

R261 RK30 42

R262 RK 3042 C hip R.

RD 0069U

R263

R264

RK 305 6

R265

RK30 26

R2 66 RK3026

R267

RK3001

R267 RK3026 C hip R. ERJ 3GS YJ101V

R268 RK3018

RK30 54

R272

R273

RK30 38

R274

RK3001

R275 RK 302 6

R276 RK3032

R277 RK 3022

R278 RK3036

R279

RK 307 0

R280 RK3 030

RK 302 6

R281

R282

RK 3058 C hip R.

R283

RK 306 3

R284

RK 30 52

RK 305 4

R285

RK 306 2 C hip R. E R J3G SYJ 104 V

R286

R287

RK3001

R288

RK 303 8

R289

RK30 69

R2 90

RK30 42

Chip R.

Chip R.

Chip R. E RJ3GSY J222V

Chip R .

Chip R. ERJ3GSY J22 1V R 295

Chip R . ER J3G SYJ 222V

Chip R. E RJ3GSY J103V R3Û0 R K 304 6

Chip R . ERJ3GSY J102V

Chip R . ERJ3GSY J470V R 303 RK3 042

Chip R.

Chip R. ERJ 3GSY J10 2V R305

Chip R. ERJ 3GS YJ681V R306

Chip R.

Chip R.

Chip R.

Chip R. ERJ6GE YJ3 92V R312

Chip R. ERJ 6GE YJ5 R6V

Chip R. ERJ6GE Y J392V

Chip R.

Chip R .

Chip R. ERJ 3GS YJ2 22V R317 RK305 4