Page 1

Agilent HDMP-3001

Ethernet over SONET Mapper IC

Device Specification

Data Sheet

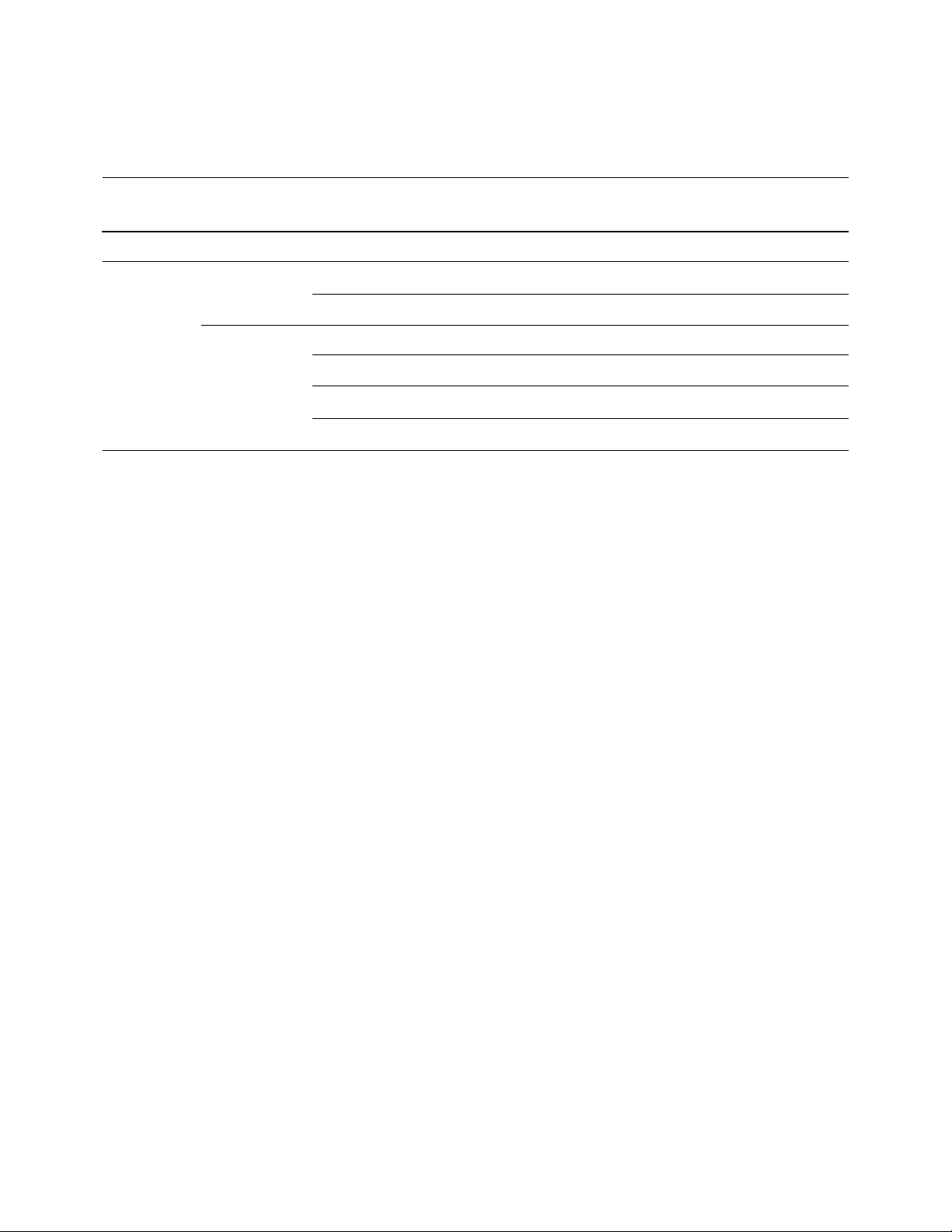

Table of Contents

1. Introduction............................................................................................... 5

1.1 Internal Functional Blocks .............................................................. 5

1.2 HDMP-3001 Features List ................................................................ 5

1.3 Applications ....................................................................................... 6

1.4 Benefits............................................................................................... 6

1.5 Interfaces............................................................................................ 6

1.6 Data Processing................................................................................. 6

2. Pinout ......................................................................................................... 7

2.1 Pin Assignments ................................................................................ 7

2.2 Pin Descriptions ................................................................................ 8

2.3 I/O Buffer Types .............................................................................. 16

3. Functional Description .......................................................................... 17

3.1 Introduction ..................................................................................... 17

3.2 Interface Descriptions.................................................................... 17

3.2.1 Microprocessor Interface ....................................................... 17

3.2.2 MII Management Interface .................................................... 17

3.2.3 EEPROM Interface .................................................................. 17

3.2.4 MII Interface............................................................................. 17

3.2.5 SONET/SDH Interface............................................................. 18

3.3 Initialization ..................................................................................... 18

3.3.1 Hardware reset......................................................................... 18

3.3.2 Software Reset ......................................................................... 18

3.3.3 Software State Machine Reset ............................................... 18

3.4 Bit Order........................................................................................... 18

3.4.1 GFP Mode ................................................................................. 18

3.4.2 LAPS Mode ............................................................................... 19

3.5 Performance Monitoring................................................................ 19

3.6 Test.................................................................................................... 20

3.6.1 Loopbacks................................................................................. 20

3.6.2 JTAG .......................................................................................... 21

3.7 Interrupts.......................................................................................... 21

3.7.1 Interrupt Driven Mode ........................................................... 21

3.7.2 Polled Mode.............................................................................. 21

3.7.3 Interrupt Sources..................................................................... 21

3.7.4 APS_INTB ................................................................................. 22

3.8 Data Processing............................................................................... 22

3.8.1 LAPS Processing ...................................................................... 22

3.8.2 GFP Processing........................................................................ 23

Page 2

3.9 SONET/SDH Processing................................................................. 24

3.9.1 Transmit SONET/SDH Processing Overview ...................... 24

3.9.2 Receive SONET/SDH Processing Overview ........................ 25

3.9.3 Transmit SONET/SDH Processing Details........................... 25

3.9.4 Receive SONET/SDH Processing Details............................. 30

4. Application Information ........................................................................ 38

4.1 Chip setup and configuration ........................................................ 38

4.1.1 EEPROM Detection................................................................. 38

4.2 Configurations ................................................................................. 38

4.2.1 PHY and MAC mode ................................................................ 38

4.2.2 SDH and SONET mode ........................................................... 38

4.2.3 LAPS and GFP mode ............................................................... 38

4.2.4 INT Pin Configuration............................................................. 38

4.3 Firmware and System Design Information ................................. 40

4.3.1 Board level pull-ups and pull-downs.................................... 40

4.3.2 Motorola MPC860 Microprocessor Interface ...................... 40

4.3.3 MII Interface............................................................................. 41

4.3.4 EEPROM Interface .................................................................. 41

5. Register Definitions............................................................................... 42

5.1 MII Management Register Map .................................................... 42

5.2 Chip Register Map........................................................................... 44

5.3 SONET/SDH Transmit Registers................................................... 56

5.4 SONET/SDH Receive Registers..................................................... 61

5.5 Ethernet Transmit Registers ......................................................... 79

5.6 Ethernet Receive Registers ........................................................... 88

6. Package Specification .......................................................................... 104

7. Electrical and Thermal Specifications............................................... 107

7.1 Technology..................................................................................... 107

7.2 Maximum Ratings ......................................................................... 107

7.3 Thermal Characteristics............................................................... 107

7.4 DC Characteristics........................................................................ 108

7.5 AC Electrical Characteristics ...................................................... 108

7.5.1 General AC Specifications.................................................... 108

7.5.2 MII Specifications.................................................................. 109

8. Timing Diagrams.................................................................................. 110

8.1 Microprocessor Bus Timing - Write Cycle................................. 110

8.2 Microprocessor Bus Timing - Read Cycle ................................. 111

8.3 Microprocessor Bus Timing Table. ............................................ 112

8.4 Line Interface Receive and Transmit Timing............................ 112

8.5 TOH Interface E1/E2/F1 Transmit Timing................................. 113

8.6 TOH Interface E1/E2/F1 Receive Timing................................... 114

8.7 DCC Interface Transmit Timing.................................................. 114

8.8 DCC Interface Receive Timing.................................................... 115

8.9 JTAG Interface Timing ................................................................. 115

8.10 Reset specification..................................................................... 116

8.11 MII Timing................................................................................... 116

8.12 MDIO Port Timing...................................................................... 117

8.13 EEPROM Port Timing ................................................................ 118

8.14 In Frame Declaration................................................................. 118

9. Applicable Documents ......................................................................... 124

2

Page 3

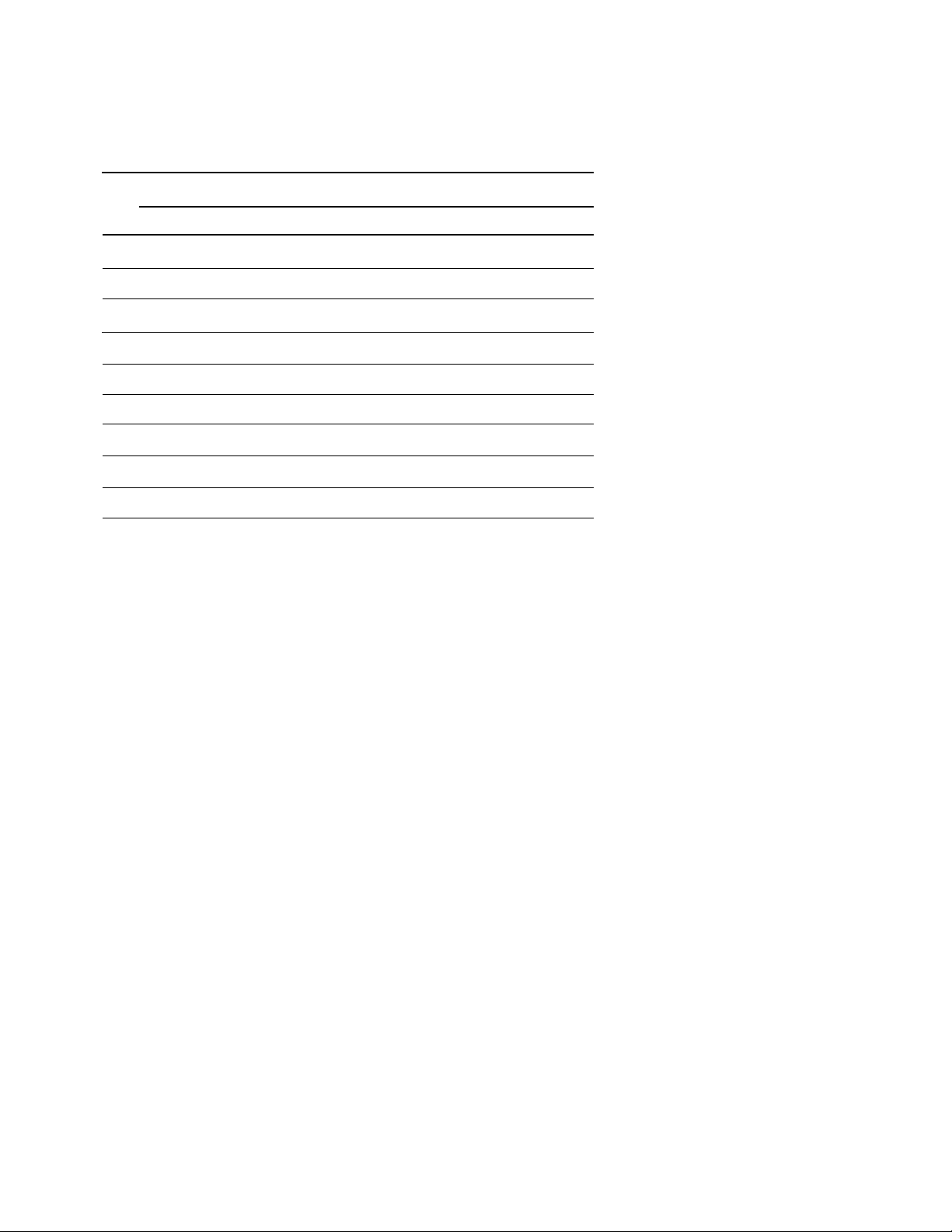

List of Figures

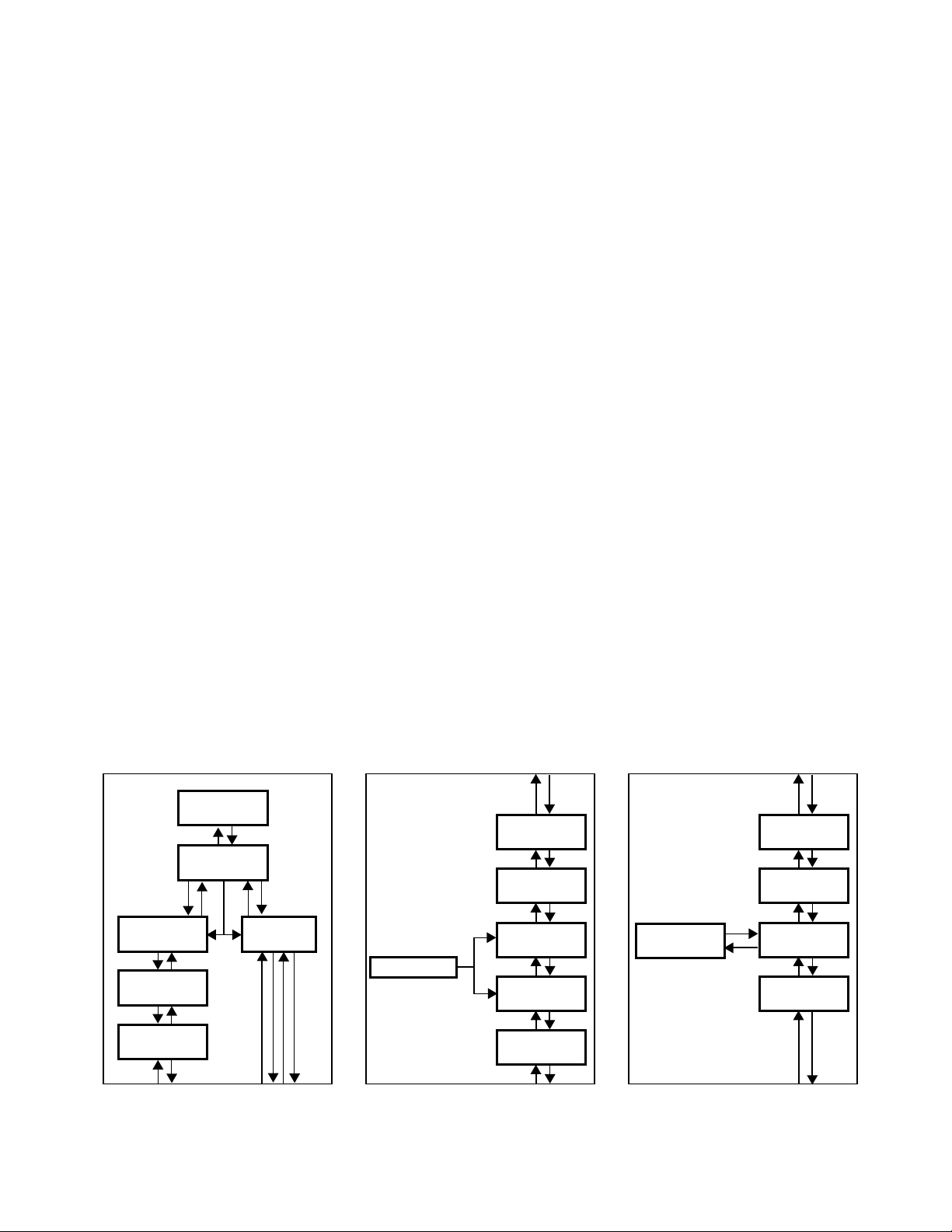

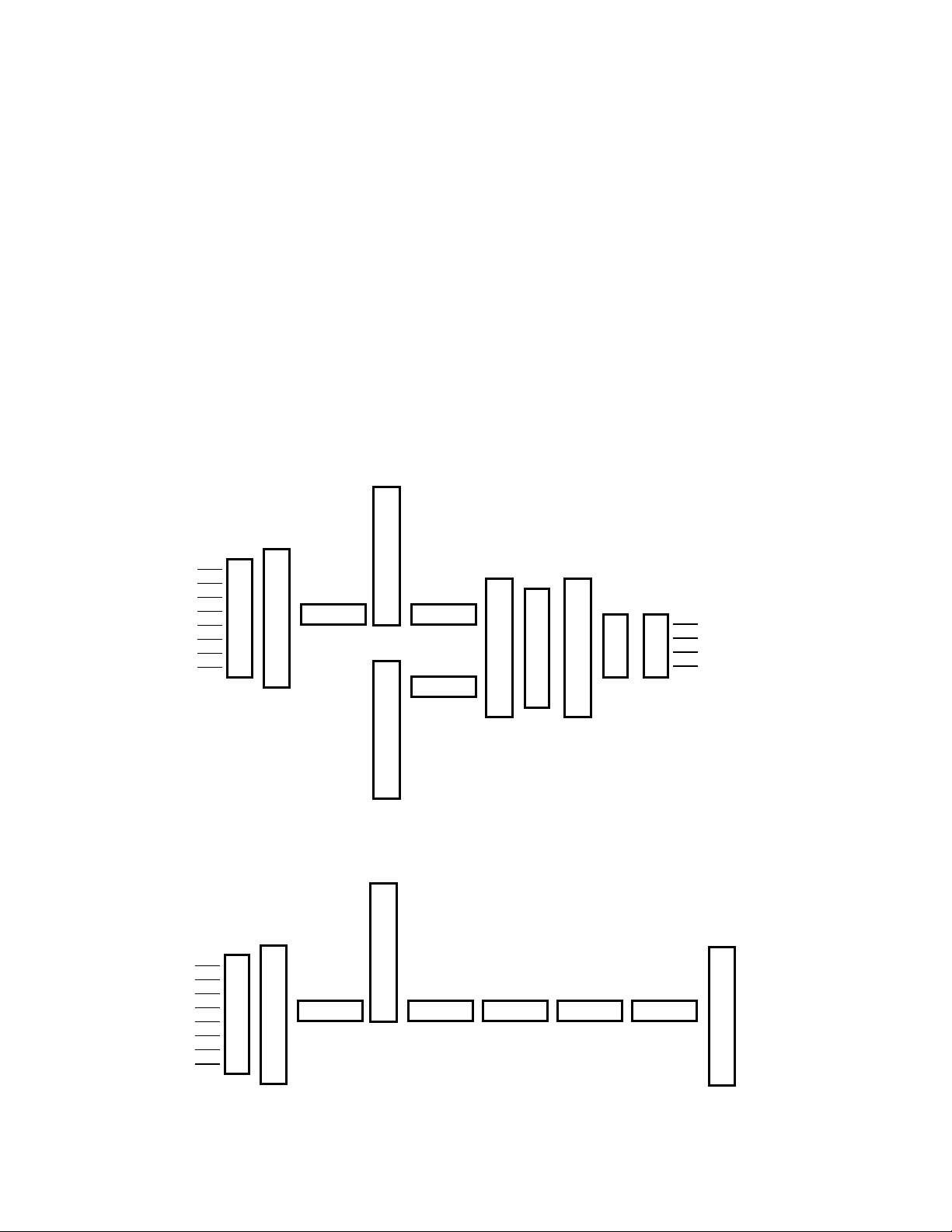

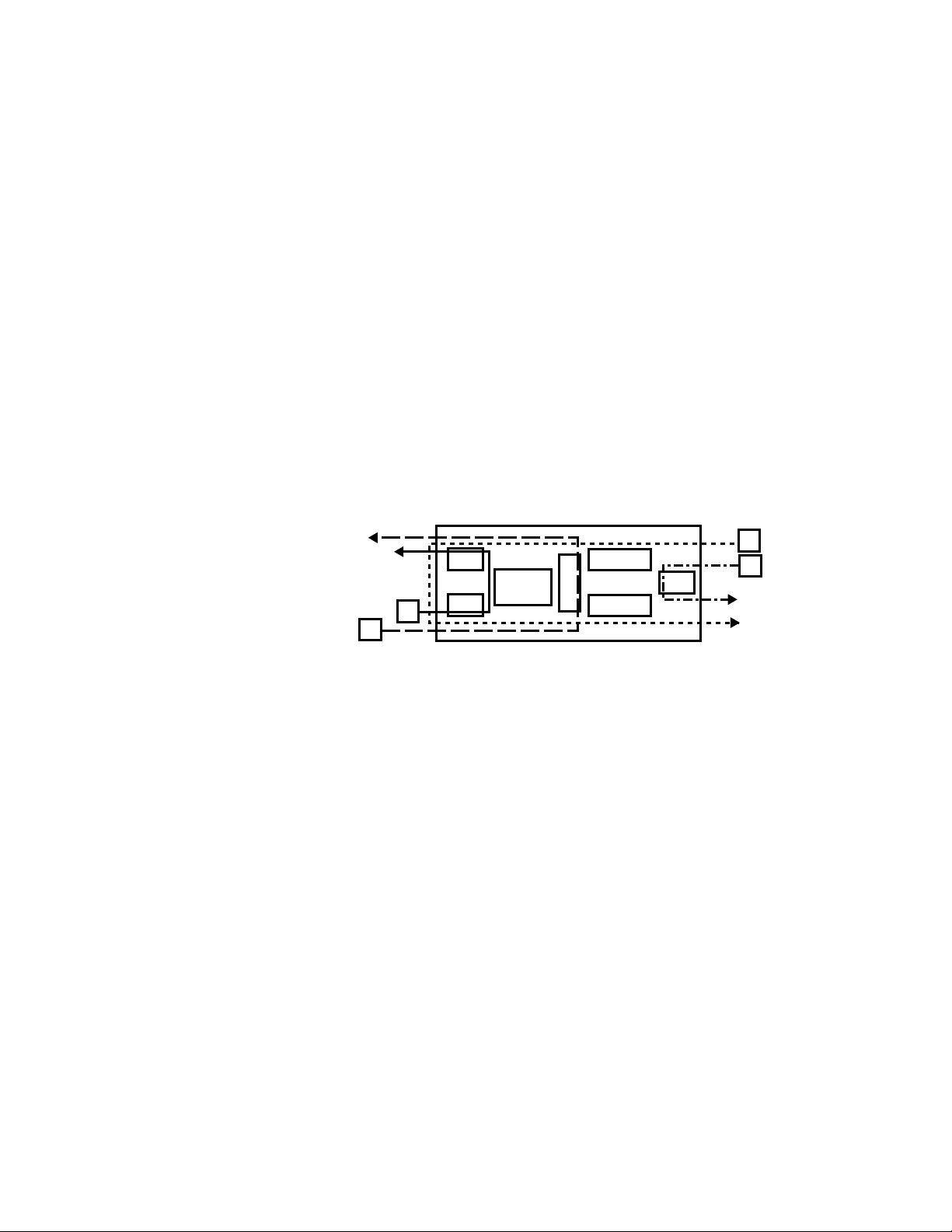

Figure 1. Functional Block Diagram ......................................................... 5

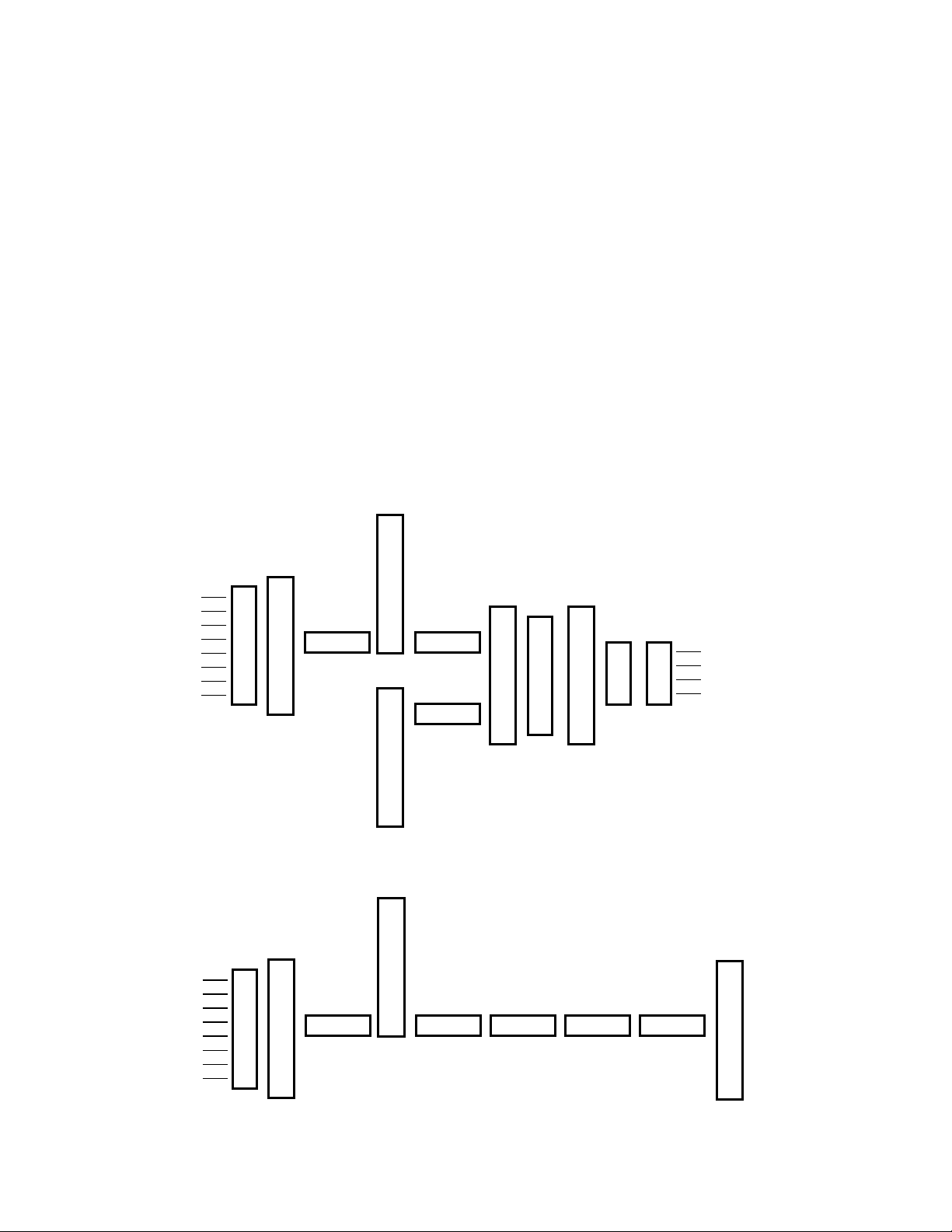

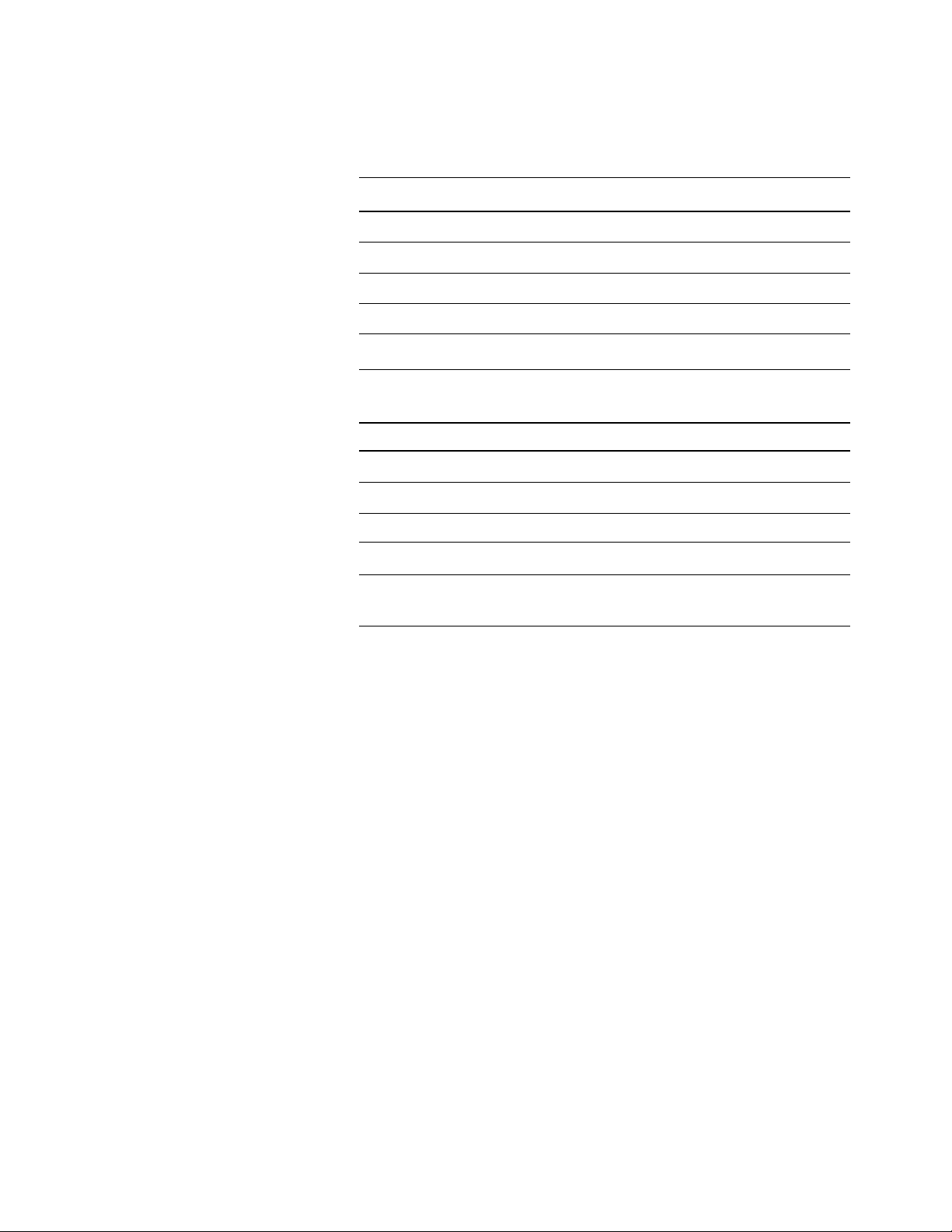

Figure 2. HDMP-3001 applications ............................................................6

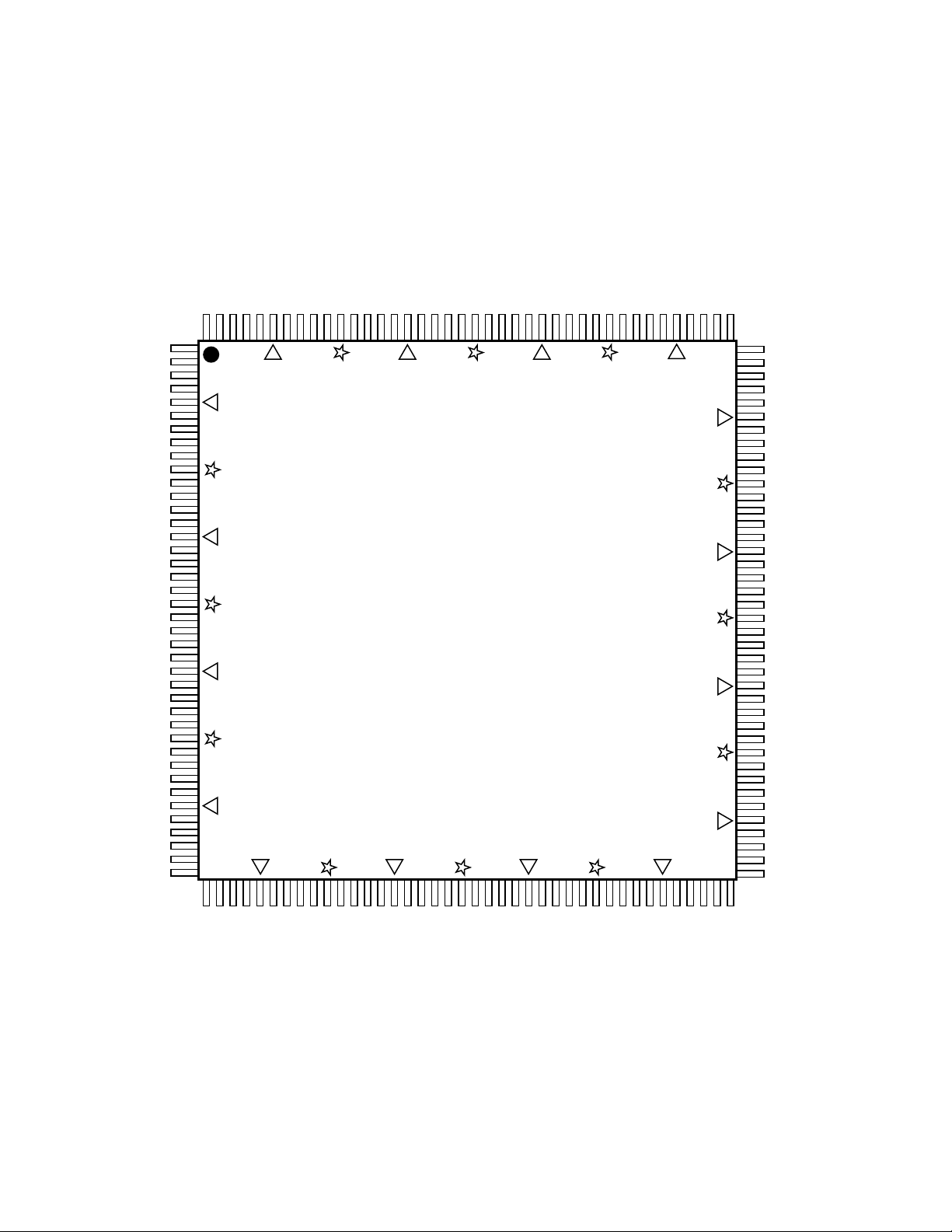

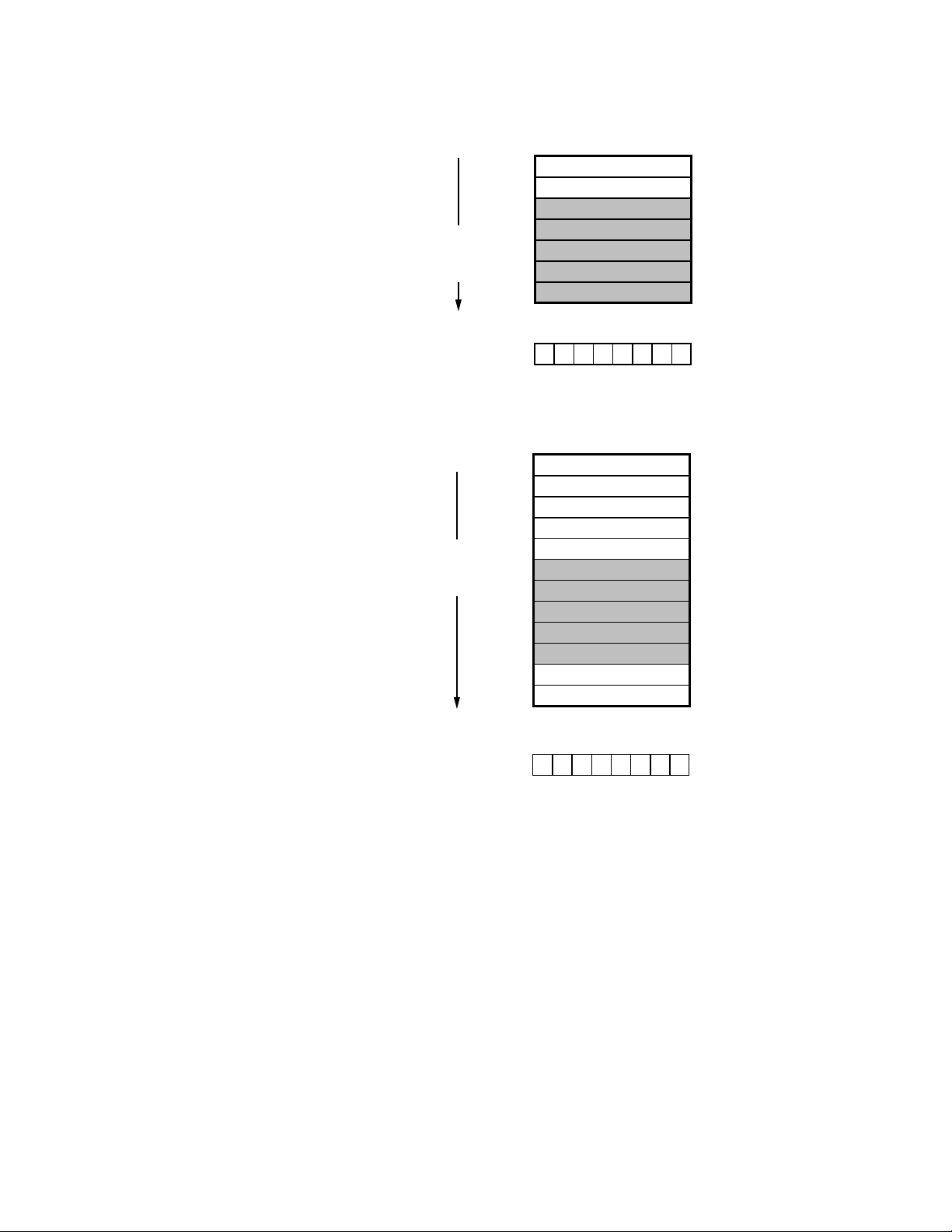

Figure 3. HDMP-3001 pin assignments .....................................................7

Figure 4. GFP Payload Bit Order ............................................................. 18

Figure 5. GFP FCS Bit Order....................................................................18

Figure 6. LAPS Payload Bit Order ...........................................................19

Figure 7. LAPS FCS Bit Order .................................................................. 19

Figure 8. Loopbacks ..................................................................................20

Figure 9. An Ethernet MAC frame ........................................................... 22

Figure 10. The format of a LAPS frame with a MAC payload..............22

Figure 11. The GFP frame......................................................................... 24

Figure 12. The structure of the SONET STS-3c SPE and SDH VC-4... 25

Figure 13. STS-3c SPE or VC-4 Structure ...............................................25

Figure 14. Pointer Byte Fields.................................................................. 29

Figure 15. Pointer Processing ..................................................................33

Figure 16. Pointer tracking algorithm..................................................... 33

Figure 17. Functional block of SONET framer scrambler ................... 36

Figure 18. HDMP-3001 connecting to a MAC......................................... 38

Figure 19. HDMP-3001 connecting to a PHY.......................................... 38

Figure 20. Mode = 00, O/D (Default) ...................................................... 39

Figure 21. Mode = 01, O/S.........................................................................39

Figure 22. Mode = 10, Always Enabled, Active-0 ..................................39

Figure 23. Mode = 11, Always Enabled, Active-1 ..................................39

Figure 24. Package Marking ...................................................................104

Figure 25. Top View of Package ............................................................ 104

Figure 26. Bottom View of Package ......................................................105

Figure 27. Side View of Package........................................................... 105

Figure 28. Detailed View of Pin ............................................................. 105

Figure 29. Microprocessor Write Cycle Timing................................... 110

Figure 30. Microprocessor Read Cycle Timing ................................... 111

Figure 31. Line Interface Transmit Timing...........................................112

Figure 32. Line Interface Receive Timing.............................................113

Figure 33. TOH Interface E1/E2/F1 Transmit Timing......................... 113

Figure 34. TOH Interface E1/E2/F1 Receive Timing...........................114

Figure 35. DCC Interface Transmit Timing .......................................... 114

Figure 36. DCC Interface Receive Timing ............................................ 115

Figure 37. JTAG Interface Timing ......................................................... 115

Figure 38. MII timing as defined by IEEE 802.3 ..................................116

Figure 39. In Frame Declaration............................................................ 118

Figure 40. Out of Frame Declaration ................................................... 119

Figure 41. Loss of Frame Declaration/Removal ..................................119

Figure 42. Line AIS and Line RDI Declaration/Removal ....................119

Figure 43. Transmit Overhead Clock and Data Alignment ................ 120

Figure 44. Receive Overhead Clock and Data Alignment ..................121

Figure 45. Transmit Data Link Clock and Data Alignment ................ 122

Figure 46. Receive Data Link Clock and Data Alignment .................. 123

3

Page 4

List of Tables

Table 1. Line Side Interface Pins Description........................................... 8

Table 2. MII Interface Pins Description..................................................... 9

Table 3. Transport Overhead Pins Description ...................................... 10

Table 4. Microprocessor Interface Pins Description ............................. 12

Table 5. JTAG Interface Pins Description ............................................... 13

Table 6. Two-Wire EEPROM Interface Pins Description...................... 14

Table 7. Miscellaneous Pins Description................................................. 14

Table 8. Buffer types .................................................................................. 16

Table 9. JTAG pins...................................................................................... 21

Table 10. JTAG instructions supported ................................................... 21

Table 11. Path RDI bit values .................................................................... 27

Table 12. STS-3c/STM-1 TOH/SOH ........................................................... 28

Table 13. Pointer Processing..................................................................... 34

Table 14. Pointer Tracking ........................................................................ 34

Table 15. INT Pin Configuration ............................................................... 39

Table 16. Pin Connections – MPC860 ...................................................... 40

Table 17. Pin Connections – MII Interface. ............................................. 41

Table 18. MII Management Register Map ................................................ 42

Table 19. HDMP-3001 Register Map ......................................................... 44

Table 20. G1 values ..................................................................................... 59

Table 21. STS-3c/STM-1 Configuration for

RX_FRAME_POSITION [3:0] .......................................................... 64

Table 22. Package Dimensions ............................................................... 106

Table 23. Absolute Maximum Ratings ................................................... 107

Table 24. Operating Conditions .............................................................. 107

Table 25. Thermal Performance ............................................................. 107

Table 26. DC Electrical Characteristics................................................. 108

Table 27. Power Dissipation.................................................................... 108

Table 28. Clock requirements and switching characteristics............. 108

Table 29. MII AC Specification................................................................ 109

Table 30. Timing of microprocessor bus ............................................... 112

Table 31. MII signal clocking................................................................... 117

Table 32. EEPROM Interface Timing Parameters................................ 118

This IC was jointly developed with Wuhan Research Institute of Post and Telecommunications

4

Page 5

1. Introduction

The Agilent HDMP-3001 is a

highly integrated VLSI device that

provides mapping of Ethernet encapsulated packets into STS-3c

payloads. The HDMP-3001 supports full-duplex processing of

SONET/SDH data streams with

full section, line, and path overhead processing. The device

supports framing pattern,

scrambling/descrambling, alarm

signal insertion/detection, and bit

interleaved parity (B1/B2/B3)

processing. Serial interfaces for

SONET/SDH TOH overhead bytes

are also provided. The HDMP3001 provides a line side interface

that operates at 155.52 Mb/s (8-bit

bus at 19.44 MHz). For Ethernet

applications a system interface

operating at 25 MHz is provided.

LAPS (Link Access Procedure –

SDH) support includes framing,

transparency processing, 32-bit

FCS processing, and self- synchronous scrambling/descrambling

(X43 +1). The HDMP-3001 also

provides GFP (Generic Framing

Procedure) support which includes framing, 32-bit FCS

processing, 16-bit HEC processing, and self-synchronous

scrambling/descrambling

(X43 +1).

1.1 Internal Functional Blocks

See the Figure 1 block diagram.

1.2 HDMP-3001 Features List

• Full Duplex Fast Ethernet

(100 Mb/s) over SDH/SONET

(OC-3c/STM-1).

• Handles the source and sink of

SONET/SDH section, line, and

path layers, with E1, E2, F1

and D1-D12 overhead interfaces in both transmit and

receive directions.

• Implements the processing of

STS-3c/STM-1 data streams

with full duplex mapping of

LAPS or GFP frames into

SONET/SDH payloads.

• Self-synchronous scrambler/

descrambler implementing

(X43 +1) polynomial for LAPS/

GFP frames.

• Link-level scrambling function

to improve operational

robustness.

• Monitors link status when

mapping MAC frame into

SONET/SDH SPE. Statistics of invalid frames are also

provided.

• Device control, configuration,

and status monitoring by

either an 8-bit external

microprocessor interface or an

MII management interface.

• Compliant with SONET/ SDH

specifications ANSI T1.105,

Bellcore GR-253-CORE and

ITU G.707.

• Provides IEEE 1149.1 JTAG

test port.

• Supports internal loopback

paths for diagnostics.

• Packaged in a 160 pin PQFP.

• Typical power dissipation

250 mW.

8 BITS AT

19.44 MHz TO

TRANSCEIVER

PARALLEL

INTERFACE

TO

LINE

8 BITS AT

19.44 MHz FROM

TRANSCEIVER

Figure 1. Functional Block Diagram

5

8-BIT GENERIC

E1, E2, F1 AND DCC

TOH OVERHEAD

INSERT

TX FRAMER

TOH MONITOR POH MONITOR

RX FRAMER

TOH OVERHEAD

EXTRACT

E1, E2, F1 AND DCC

MICROPROCESSOR BUS

MICROPROCESSOR

SPE/VC

GENERATOR

POINTER

PROCESSOR

INTERFACE

X43 + 1

SCRAMBLER

X43 + 1

DESCRAMBLER

ETHERNET

MANAGEMENT BUS

MDIO INTERFACE EEPROM INTERFACE

LAPS/GFP

FRAME

PROCESSOR

PERFORMANCE

MONITOR

LAPS/GFP

FRAME

PROCESSOR

GPIO REGISTER

16 GENERAL

PURPOSE PINS

STANDARD 2-WIRE

EEPROM BUS

TX FIFO

ETHERNET

INTERFACE

RX FIFO

JTAG TEST

ACCESS PORT

TEST DATA

4 BITS AT

25MHz

MII

TO

SYSTEM

4 BITS AT

25MHz

Page 6

• Implemented in 0.25 micron

AGILENT

FIBER OPTICS

SERDES

WITH CDR

AGILENT

HDMP-3001

SWITCH

FABRIC

MICROPROCESSOR

ETHERNET

PHYs

MDIO BUS

OC-3c PORT ETHERNET PORTS

PORT ON ETHERNET SWITCH

LINE CARD OF SONET ADM

ETHERNET

PHY

AGILENT

HDMP-3001

ADM

EEPROM

SERDES

WITH CDR

AGILENT

FIBER OPTICS

DROP SIDE - 100 MBIT/S

FULL-DUPLEX ETHERNET

OC-48/12

SONET RING

MICROPROCESSOR

STAND ALONE DSU/CSU

ETHERNET

PHY

AGILENT

HDMP-3001

SONET SERDES

WITH CDR

AGILENT

FIBER OPTICS

100 MBIT/S

FULL-DUPLEX ETHERNET

OC-3c

CMOS with 1.8 V core, 3.3 V I/O

power and LVCMOS

compatible I/Os.

• Provides a 16-bit general purpose I/O (GPIO) register.

• Device power-up initialization

optionally through 2-wire

EEPROM interface.

• Configurable by hardware to

be connected to either a PHY

or a MAC from the system

connectivity viewpoint.

1.3 Applications

• Multi-Service Ethernet

Switches.

• Enhanced Services SONET/

SDH Add/Drop Multiplexers

(ADMs).

• DSU/CSUs.

1.4 Benefits

• Allows LANs to be interconnected over leased OC-3c

lines, thereby extending a LAN

to multiple sites.

• Ethernet switches in each LAN

can be connected together directly which reduces cost and

complexity.

• Enables Transparent LAN

Services which, unlike POS

solutions, do not require

WAN access routers.

1.5 Interfaces

• System interface is a 25 MHz

IEEE 802.3 full-duplex, 100

Mb/s Ethernet MII port that

connects to either a PHY or a

MAC.

• Line side SERDES interface is

8-bit parallel data operating at

19.44 MHz. SONET/SDH

framer is compliant to

specifications ANSI T1.105 and

ITU G.707.

• Serial data channels for add

and drop of SONET overhead

bytes E1, E2, F1 and DCC.

• 8-bit microprocessor

interface allows direct

connection to the Motorola

MPC860.

• IEEE 802.3 MDIO management

interface.

• Standard 2-wire EEPROM

interface for optional boot-up

configuration.

• Provides 16-bit General

Purpose I/O (GPIO) register.

• Provides standard five-pin

IEEE 1149.1 JTAG test port.

1.6 Data Processing

• Complies to the GFP (Generic

Framing Procedure) draft

specification, revision 2, of

ANSI T1X1.5 and implements

both the null and linear header

options.

• Complies to the LAPS (Link

Access Procedure – SDH)

specification X.86 of ITU.

• Optional self-synchronous

X43 +1 scrambling of the

payload.

Figure 2. HDMP-3001 Applications

6

Page 7

2. Pinout

2.1 Pin Assignments

DGND

RX_SDCC_CLK

RX_FRAME_SFP

DVDD

RX_LDCC_DATA

RX_LDCC_CLK

RX_SDCC_DATA

GND

DGND

RX_OOF_OUT

RX_LAIS_OUT

RX_8K_CLK

RX_LOS

NO CONNECT

RX_LOF_OUT

TX_DATA[0]

TX_DATA[1]

TX_DATA[2]

VDD

GND

DGND

DVDD

TX_DATA[3]

TX_DATA[4]

TX_DATA[5]

TX_DATA[6]

TX_DATA[7]

VDD

DGND

TX_SONETCLK

TX_8K_CLK

TX_E1E2F1_CLK

TX_E2_DATA

TX_E1_DATA

TX_F1_DATA

VDD

TX_FRAME_SFP

TX_LDCC_DATA

TX_LDCC_CLK

GND

GND

VDD

NO CONNECT

TRSTB

TMS

TDO

TCK

TDI

GPIO[0]

DGND

DGND

GPIO[1]

GPIO[2]

GPIO[3]

GPIO[4]

GPIO[5]

GPIO[6]

GPIO[7]

DVDD

DGND

GND

VDD

RX_FRAME_IN

RX_SONETCLK

RX_DATA[0]

RX_DATA[1]

RX_DATA[2]

RX_DATA[3]

RX_DATA[4]

BUSMODE1

GND

RX_DATA[5]

RX_DATA[6]

RX_DATA[7]

RX_E1E2F1_CLK

RX_F1_DATA

RX_E2_DATA

RX_E1_DATA

DVDD

DGND

DGND

155

5

10

15

20

25

30

35

45

150

50

145

55

140

60

135

65

130

70

125

115

110

105

100

95

90

85

75

DVDD

TX_SDCC_CLK

TX_SDCC_DATA

LOC_RX

LOC_TX

MDC

MDIO

P_TX_ER_M_RX_ER

GND

DGND

P_TX_EN_M_RX_DV

P_TXD_M_RXD[0]

P_TXD_M_RXD[1]

P_TXD_M_RXD[2]

P_TXD_M_RXD[3]

P_TX_CLK_M_RX_CLK

P_RX_ER_M_TX_ER

VDD

GND

DGND

DVDD

P_RX_DV_M_TX_EN

P_RXD_M_TXD[0]

P_RXD_M_TXD[1]

P_RXD_M_TXD[2]

P_RXD_M_TXD[3]

P_RX_CLK_M_TX_CLK

SCL

VDD

DGND

SDA

SYS_25M_CLK

BUSMODE0

INT

RSTB

CSB

APS_INTB

VDD

GND

VDD

GND

GPIO[9]

GPIO[8]

GPIO[11]

GPIO[10]

Figure 3. HDMP-3001 Pin Assignments

7

GPIO[13]

GPIO[12]

DGND

GPIO[14]

VDD

RDYB

GPIO[15]

WRB

RDB

ADDR[1]

ADDR[0]

DVDD

ADDR[2]

GND

CPU_CLK

VDD

ADDR[4]

ADDR[3]

ADDR[6]

ADDR[5]

ADDR[8]

ADDR[7]

D[0]

DGND

GND

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

DVDD

DGND

Page 8

2.2 Pin Descriptions

Table 1. Line Side Interface Pins Description

Signal name Pin # Type(I/O) Signal description

RX_DATA[0] 25 I RECEIVE DATA: Byte-wide STS-3c data input stream.

RX_DATA[1] 26 RX_DATA [7] is the MSB, and RX_DATA [0] the LSB.

RX_DATA[2] 27 Data is sampled on the rising edge of RX_SONETCLK.

RX_DATA[3] 28

RX_DATA[4] 29

RX_DATA[5] 32

RX_DATA[6] 33

RX_DATA[7] 34

RX_FRAME_IN 23 I RECEIVE FRAME INDICATOR: Frame position indication signal is

active high and indicates the SONET frame position on the RX_

DATA [7:0] bus. Sampled on the rising edge of RX_SONETCLK.

Only used when RX_FRAME_INH is set, otherwise tie this pin low.

RX_LAIS_OUT 153 O RECEIVE LINE ALARM INDICATION SIGNAL OUTPUT:

Receive line alarm indication signal will be set high if a binary

“111” pattern is received for the number of consecutive frames

programmed into the K2_CONSEC register. RX_LAIS_OUT will

be cleared if a binary “111” pattern is not received for the

number of consecutive frames programmed into the

K2_CONSEC register.

RX_LOF_OUT 149 O RECEIVE LOSS OF FRAME OUTPUT:

RX_LOF_OUT is set high when there is a loss of frame indication.

If RX_OOF_OUT is active continuously for 24 consecutive frames

(3 ms), the RX_LOF bit is set high. Once RX_LOF is set, it remains

high until RX_OOF_OUT is inactive continuously for 3 ms.

RX_LOS 147 I RECEIVE LOSS OF SIGNAL: RX_LOS should be used to indicate

to the framer that there is no signal present from the optical

receiver. The signal’s default is active high, but can be set to

active low by programming RX_LOS_LEVEL = 1.

RX_OOF_OUT 152 O RECEIVE OUT OF FRAME OUTPUT: RX_OOF_OUT is set high when

there is an out of frame indication. An out of frame condition occurs

when five consecutive erroneous framing patterns specified

in the A1 or A2 bytes have been received.

RX_SONETCLK 24 I RECEIVE SONET CLOCK: RX_SONETCLK is the receive

input clock from the line side, and provides timing for the

receive data bus and frame position indication inputs.

This clock should be 19.44 MHz ± 20 ppm.

TX_DATA[0] 145 O TRANSMIT DATA: Byte-wide STS-3c data output stream.

TX_DATA[1] 144 TX_DATA [7] is the MSB, TX_DATA [0] is the LSB. Data is

TX_DATA[2] 143 updated on the rising edge of TX_SONETCLK.

TX_DATA[3] 138

TX_DATA[4] 137

TX_DATA[5] 136

TX_DATA[6] 135

TX_DATA[7] 134

(continues)

8

Page 9

Signal name Pin # Type(I/O) Signal description

TX_FRAME_SFP 125 O TRANSMIT FRAME POSITION OUTPUT INDICATOR: Frame position

indication signal is active high and indicates the SONET frame

position on the TX_DATA [7:0] bus. Updated on the rising edge of

TX_SONETCLK. This signal is also used for the outer board to start

sending the first bit (MSB) of the serial data E1, E2, F1, SDCC,

and LDCC.

TX_SONETCLK 133 I TRANSMIT SONET CLOCK: TX_SONETCLK is the transmit output

clock to the line side, and provides timing for the transmit data

bus and frame position indication outputs. This clock should be

19.44 MHz ± 20 ppm.

LOC_TX 115 O Loss of SONET_TX clock.

LOC_RX 116 O Loss of SONET_RX clock.

Table 2. MII Interface Pins Description

Signal name Pin # Type(I/O) Signal description

SYS_25M_CLK 88 I Drives the two MII clocks in PHY mode, TX_CLK and

RX_CLK. It is also used to monitor the TX_SONETCLK

and RX_SONETCLK.

The requirement for this clock is 25 MHz ±100 ppm.

P_TX_CLK_M_RX_CLK 104 I/O (Int. PU) PHY mode: transmit clock output. Derived from

SYS_25M_CLK.

MAC mode: receive clock input. Nominally 25 MHz.

P_TXD_M_RXD[0] 108 I PHY mode: transmit data nibble.

P_TXD_M_RXD[1] 107 MAC mode: receive data nibble.

P_TXD_M_RXD[2] 106

P_TXD_M_RXD[3] 105

P_TX_EN_M_RX_DV 109 I PHY mode: transmit data enable.

MAC mode: receive data valid.

P_RX_CLK_M_TX_CLK 93 I/O (Int. PU) PHY mode: receive clock output. Derived from

SYS_25M_CLK.

MAC mode: transmit clock input. Nominally 25 MHz.

P_RXD_M_TXD[0] 97 O (T/S) PHY mode: receive data nibble.

P_RXD_M_TXD[1] 96 MAC mode: transmit data nibble.

P_RXD_M_TXD[2] 95

P_RXD_M_TXD[3] 94

P_RX_DV_M_TX_EN 98 O (T/S) PHY mode: receive data valid.

MAC mode: transmit data enable.

P_RX_ER_M_TX_ER 103 O (T/S) PHY mode: receive error.

MAC mode: transmit error.

P_TX_ER_M_RX_ER 112 I PHY mode: transmit error.

MAC mode: receive error.

9

(continues)

Page 10

Signal name Pin # Type(I/O) Signal description

MDIO 113 I/O MII management input/output serial data. When this interface

is unused, connect this pin high. If HDMP-3001 is attached

to a MAC via the mechanical interface specified in IEEE 802.3,

clause 22.6, an external pull-up of 1.5 kohm ± 5% is required.

MDC 114 I MII management clock, up to 2.5 MHz. When this interface is

unused, connect this pin high.

Table 3. Transport Overhead Pins Description

Signal name Pin # Type(I/O) Signal description

RX_E1_DATA 38 O RECEIVED E1 DATA: Local orderwire channel data byte

(E1) received from the line side.

RX_E2_DATA 37 O RECEIVED E2 DATA: Express orderwire channel data byte

(E2) received from the line side.

RX_F1_DATA 36 O RECEIVED F1 DATA: Maintenance channel data byte (F1)

received from the line side.

RX_E1E2F1_CLK 35 O RECEIVED E1/E2/F1 DATA REFERENCE CLOCK: A

64 kHz clock reference output for E1/E2/F1 data. The MSB of

the E1/E2/F1 bytes appears in the first 64 kHz clock cycle

after a rising edge of RX_FRAME_SFP.

RX_FRAME_SFP 158 O RECEIVE FRAMER START-OF-FRAME INDICATION: This signal is

nominally 8 kHz and is high during the first row of overhead

of the received frame. The RX_FRAME_SFP signal is also used

for byte alignment of the received E1/E2/F1 data outputs. This

is a SFP (Start-of-Frame-Pulse) indicating the SONET frame

position on the RX_DATA [7:0] bus.

RX_LDCC_DATA 154 O RECEIVED LINE DCC DATA: Drop output for received

Line Data Communications Channel (DCC).

RX_LDCC_CLK 155 O RECEIVED LINE DCC REFERENCE CLOCK : A gapped 576 kHz clock

reference for Line DCC data. The RX_LDCC_DATA outputs are

updated on the falling edge of RX_LDCC_CLK.

RX_SDCC_DATA 156 O RECEIVED SECTION DCC DATA: Drop output for received Section

Data Communications Channel (DCC).

RX_8K_CLK 146 O 8kHz RECEIVE CLOCK: A general purpose 8kHz buffered clock

derived from RX_SONETCLK which may be used for external

clock reference purposes.

RX_SDCC_CLK 157 O RECEIVED SECTION DCC REFERENCE CLOCK : A gapped 192 kHz

clock reference for Section DCC data. The RX_SDCC_DATA outputs are updated on the falling edge of RX_SDCC_CLK.

(continues)

10

Page 11

Signal name Pin # Type(I/O) Signal description

TX_E1_DATA 126 I TRANSMIT E1 DATA: Local orderwire channel data byte

(E1) to be inserted by the HDMP-3001 into the outgoing

SONET data stream.

TX_E2_DATA 127 I TRANSMIT E2 DATA: Express orderwire channel data byte

(E2) to be inserted by the HDMP-3001 into the outgoing

SONET data stream.

TX_F1_DATA 128 I TRANSMIT F1 DATA: Maintenance channel data byte (F1)

to be inserted by the HDMP-3001 into the outgoing SONET

data stream.

TX_E1E2F1_CLK 129 O TRANSMIT E1/E2/F1 DATA REFERENCE CLOCK: A 64 kHz clock

reference output for E1/E2/F1 data to be inserted by the

HDMP-3001 into the outgoing SONET data stream.

TX_LDCC_DATA 123 I TRANSMIT LINE DCC DATA: Input for the Line Data

Communications Channel (DCC) to be inserted by the HDMP-3001

into the outgoing SONET data stream.

TX_LDCC_CLK 124 O TRANSMIT LINE DCC REFERENCE CLOCK: A 576 kHz clock

reference for Line DCC data to be inserted by the

HDMP-3001 into the outgoing SONET data stream. The

TX_LDCC_DATA inputs are sampled on the falling edge of

TX_LDCC_CLK.

TX_SDCC_DATA 117 I TRANSMIT SECTION DCC DATA: Input for the Section

Data Communications Channel (DCC) to be inserted into the

outgoing SONET data stream from the HDMP-3001.

TX_SDCC_CLK 118 O TRANSMIT SECTION DCC REFERENCE CLOCK:

A 192 kHz clock reference for Section DCC data to be inserted

by the HDMP-3001 into the outgoing SONET data stream. The

TX_SDCC_DATA inputs are sampled on the falling edge of

TX_LDCC_CLK.

TX_8K_CLK 132 O 8kHz TRANSMIT CLOCK: A general purpose 8kHz

buffered clock derived from TX_SONETCLK which may be

used for external clock reference purposes.

11

Page 12

Table 4. Microprocessor Interface Pins Description

Signal name Pin # Type(I/O) Signal description

ADDR[0] 56 I ADDRESS BUS: Allows host microprocessor to perform

ADDR[1] 57 register selection within the HDMP-3001.

ADDR[2] 58

ADDR[3] 63

ADDR[4] 64

ADDR[5] 65

ADDR[6] 66

ADDR[7] 67

ADDR[8] 68

APS_INTB 83 O (O/D) APS INTERRUPT: Active-low output triggered by an APS

event. APS_INTB is an open-drain output which is in a high

impedance state when inactive.

When used, this pin needs an external pull-up.

BUSMODE0 87 I/O BUS INTERFACE MODE:

BUSMODE1 30

BUSMODE1, BUSMODE0 = 00 -> Motorola MPC860 mode

BUSMODE1, BUSMODE0 = 01 -> Reserved

BUSMODE1, BUSMODE0 = 10 -> Reserved

BUSMODE1, BUSMODE0 = 11 -> Reserved

Both pins are latched at reset and are also used as test outputs in

test mode. In normal applications, tie these pins low.

CPU_CLK 60 I CPU CLOCK: Used in Motorola MPC860 mode.

CSB 84 I CHIP SELECT: Active-low chip select.

D[0] 69 I/O I/O DATA BUS: Allows transfer of data between host

D[1] 72 microprocessor and the HDMP-3001.

D[2] 73 Refer to microprocessor application notes on the usage of

D[3] 74 board level pull-ups.

D[4] 75

D[5] 76

D[6] 77

D[7] 78

12

(continues)

Page 13

Signal name Pin # Type(I/O) Signal description

INT 86 O (T/S) INTERRUPT: Configurable interrupt output. Refer to

Table 18 for a detailed description of how INT is configured.

In open-drain configurations, an external pull-up is required.

In open-source configurations, an external pull-down is

required.

To prevent undesired interrupts before configuration is

complete, microprocessors with an active-high interrupt pin

should have a pull-down and those with an active-low interrupt

pin, a pull-up.

RDB 55 I READ ENABLE: Active low.

RDYB 53 I/O READY: RDYB is an active-low output to acknowledge the

end of data transfer. This pin is briefly driven to its inactive state

before being tristated.

Refer to microprocessor application notes for board pull-up

requirements.

RSTB 85 I RESET: Active low input to reset the HDMP-3001.

WRB 54 I WRITE ENABLE: Active low.

Table 5. JTAG Interface Pins Description

Signal name Pin # Type(I/O) Signal description

TCK 7 I TEST CLOCK: JTAG input clock used to sample data on the

TDI and TDO pins. Should be tied high when the JTAG interface

is not in use.

TDI 8 I (Int PU) TEST DATA IN: Input pin for serial data stream to be sent to

HDMP-3001. TDI is sampled on the rising edge of TCK.

TDO 6 O TEST DATA OUT: Output pin for serial data stream sent

from the HDMP-3001. TDO is sampled on the falling edge of` TCK.

TMS 5 I (Int. PU) TEST MODE SELECT: Controls the operating mode of the

JTAG interface. TMS is sampled on the rising edge of TCK.

TRSTB 4 I (Int. PU) TEST PORT RESET: Active low input used to reset the

JTAG interface.

13

Page 14

Table 6. Two-Wire EEPROM Interface Pins Description

Signal name Pin # Type(I/O) Signal description

SCL 92 I/O EEPROM bus clock. If no EEPROM is present, connect this pin

to ground.

Refer to EEPROM application notes for board pull-up requirements.

SDA 89 I/O EEPROM bus data. If no EEPROM is present, connect this pin

to ground.

Refer to EEPROM app notes for board pull-up requirements.

Table 7. Miscellaneous Pins Description

Signal name Pin # Type(I/O) Signal description

GPIO[0] 9 I/O (int. PU) GENERAL PURPOSE I/O: The GPIO register allows the

GPIO[1] 12 user to define each grouping (GPIO [0, 1], GPIO [2, 3], GPIO [4, 5],

GPIO[2] 13 GPIO[6, 7], GPIO [8, 9], GPIO [10, 11], GPIO [12, 13],

GPIO[3] 14 GPIO [14, 15] ) as either input or output bits. These bits can

GPIO[4] 15 be used for functions such as LED control or user-defined

GPIO[5] 16 input control.

GPIO[6] 17

GPIO[7] 18

GPIO[8] 43

GPIO[9] 44

GPIO[10] 45

GPIO[11] 46

GPIO[12] 47

GPIO[13] 48

GPIO[14] 49

GPIO[15] 52

NO CONNECT 3, 148 These pins should be left unconnected.

GND 1, 21, 31, Logic GROUND: These pins should be connected to the logic

41,61, 71, ground plane.

81, 101,

111, 121,

141, 151

(continues)

14

Page 15

Signal name Pin # Type(I/O) Signal description

DGND 10, 11, 20, Driver GROUND: These pins should be connected to the I/O

40, 50, ground plane.

70, 80,

90, 100,

110, 120,

130, 140,

150, 160

VDD 2, 22, Logic POWER: These pins should be connected to the 1.8 V

42, 51, power supply for logic.

62, 82,

91, 102,

122, 131,

142

DVDD 19, 39, Driver POWER: These pins should be connected to the 3.3 V

59, 79, power supply for I/O.

99, 119,

139, 159

Note:

I = Input, O = output, T/S = Tristateable output, O/D = Open-drain output, and Int. PU = Internal pull-up.

15

Note: All unused inputs must be tied off to their inactive states. No input pins

should be left floating.

Page 16

2.3 I/O Buffer Types

This section lists the types of some particular I/Os used in the HDMP-3001 chip.

Table 8. Buffer types

Buffer Type I/O Name Comment

O/D APS_INTB Need external P/U

Output

TS P_RXD_M_TXD[0] Controlled by the “Isolate MII” register bit

Output P_RXD_M_TXD[1]

P_RXD_M_TXD[2]

P_RXD_M_TXD[3]

P_RX_DV_M_TX_EN

P_RX_ER_M_TX_ER

INT See INT Pin Configuration Section

RDYB Uses a T/S output buffer and logically drives high before output buffer is

released or tristated

Input TMS, TRSTB, TDI

w/

Internal P/U

Bidirectional

P_TX_CLK_M_RX_CLK

w/

Internal P/U

for input

mode

P_RX_CLK_M_TX_CLK

SDA P/U can be disabled if there is an external P/U

SCL

GPIO [15:0]

Note:

All of the internal P/Us are normally enabled, and they can be disabled through the JTAG port, with the exception of SCL and SDA.

The pullups on these two pins can be disabled using controls from register 0x003 bits [5:4].

16

Page 17

3. Functional Description

3.1 Introduction

The HDMP-3001 performs fullduplex mapping of Ethernet

frames into a SONET STS-3c /

SDH STM-1 payload using the

LAPS or GFP protocol. All

SONET/SDH framing functions

are included. A TOH

interface provides direct add/drop

capability for E1, E2, F1, and both

Section and Line DCC channels.

SONET or SDH mode is selected

during initial configuration.

By default, the HDMP-3001 operates in LAPS mode. LAPS is a

HDLC-compatible protocol. The

LAPS transmit processing includes packet framing,

inter-frame fill, payload scrambling (X43 +1), transparency

processing (byte stuffing) and 32bit CRC generation. The receive

LAPS processing provides for the

extraction of LAPS frames, transparency removal, descrambling,

header and FCS checking.

The HDMP-3001 can also be configured to operate in GFP mode.

The GFP transmit processing includes the insertion of framed

packet framing, idle frame insertion, payload scrambling (X43 +1)

and 32-bit CRC generation. The

receive GFP processing provides

for the extraction of GFP frames,

descrambling, header and FCS

error checking.

A robust set of performance

counters and status/control registers for performance monitoring

via the external microprocessor

or MDIO is provided.

The SONET/SDH line side consists of an 8-bit parallel interface

which operates at 19.44 MHz.The

device is typically connected to a

parallel-to-serial converter, which

is in turn connected to an optical

transceiver for interfacing to a

fiber. The Ethernet interface is a

standard MII interface which operates at 25 MHz (4-bit). Only 100

Mb/s full-duplex operation is supported, i.e. collisions are not

supported. This device can be

controlled through either a microprocessor port or a two-wire

MDIO (MII Management)

port. The complete register map

can be accessed from both these

ports. Additionally, the initial configuration can be automatically

downloaded from an EEPROM

which is useful in designs without

on-board intelligence.

3.2 Interface Descriptions

3.2.1 Microprocessor Interface

The interface consists of eight

data bits, nine address bits, three

control signals and one acknowledge signal. Through this

interface the HDMP-3001 internal

register map can be accessed.

Only one of the microprocessor,

MII Management or EEPROM

ports can be active at any one

time. Hence, in the rare cases

where more than one port is used,

care has to be taken not to have

more than one port active simultaneously.

3.2.2 MII Management Interface

The MII Management interface is

a standard port for Ethernet PHYs

and is defined in the IEEE 802.3

specification. It is a two wire interface that allows access to

thirty-two sixteen-bit data registers. These are defined in the MII

Management memory map. Sixteen of the data registers are

defined by the IEEE specification

and sixteen are left for vendor

specific purposes. Two of the vendor specific registers in the

HDMP-3001 are used to enable

access to the internal chip registers through indirect addressing.

One of the vendor specific registers is used to shadow the

frequently polled master alarm

register.

3.2.3 EEPROM Interface

This port operates in master mode

only, i.e. the HDMP-3001 cannot

be accessed through this port.

One use of this port is to configure the chip in stand-alone

applications. Another use is to

assign unique PHY addresses to

cascaded HDMP-3001 ICs when

they are controlled through the

MDIO port.

If enabled, this port is automatically activated after reset to load

the HDMP-3001 configuration

from an EEPROM. The complete

address space of the HDMP-3001,

511 to 0, is filled with the data

from EEPROM addresses 511 to 0.

EEPROMs like Philips’

PCF8594C-2, Fairchild’s

NM24C02U or Atmel’s AT24C04

are supported. The EEPROM device address should be set to zero.

The SCL clock rate is just under

100 kHz. It takes a little under 300

ms for the EEPROM to load, so

during this time the microprocessor and MII Management ports

must stay inactive.

3.2.4 MII Interface

This interface is a 100 Mb/s fullduplex Ethernet MII interface as

defined by IEEE 802.3. It operates

at 25 MHz. At power-up the MII

Isolate bit in the register map is

active, which sets all output pins

in this interface to high impedance

and ignores all MII inputs.

17

Page 18

3.2.5 SONET/SDH Interface

This interface is 8 bits wide and

runs at 19.44 MHz. The Serial

SONET/SDH overhead channels

are clocked in and out of the IC

through low-speed serial ports.

3.3 Initialization

3.3.2 Software Reset

Software resets are functionally

equivalent to hardware resets.

There are two identical software

resets, one in the microprocessor

register map and one in the MII

register map. Both resets are selfcleared in less than 10 µs.

3.4 Bit Order

3.4.1 GFP Mode

The bit order for the MII nibbles

through the HDMP-3001 chip is

shown in Figure 4. The order in

which the FCS bits are transmitted is shown in Figure 5.

3.3.1 Hardware reset

The HDMP-3001 hardware reset,

RSTB, is asynchronous and must

be active for at least 200 SONET

clock cycles (>10 µs) with stable

power.

PINS

TX_DATA[7]

TX_DATA[6]

TX_DATA[5]

TX_DATA[4]

TX_DATA[3]

TX_DATA[2]

TX_DATA[1]

TX_DATA[0]

7

6

X

7

S

C

R

F = FIRST

L = LAST

F

7 6 5 4 3 2 1 0

[7] [0]

5

4

3

2

1

0

3.3.3 Software State Machine Reset

This reset should always be active

when the chip is configured. Only

when the configuration is completed should the state machine

reset be cleared to begin normal

operation.

X

4

3

S

C

R

C

R

C

G

E

N

F

7 6 5 4 3 2 1 0

F

7 6 5 4 3 2 1 0

L

L

7

6

M

5

G

F

P

I

I

4

3

I

2

/

1

F

0

L

F

0

1

2

3

LSN

MSN

L

PINS

4

5

6

7

TXD0

TXD1

TXD2

TXD3

Figure 4. GFP Payload Bit Order

PINS

TX_DATA[7]

TX_DATA[6]

TX_DATA[5]

TX_DATA[4]

TX_DATA[3]

TX_DATA[2]

TX_DATA[1]

TX_DATA[0]

7

6

5

4

3

2

1

0

Figure 5. GFP FCS Bit Order

18

X

7

S

C

R

F

7 6 5 4 3 2 1 0

[7] [0]

X

4

3

S

C

R

L

F

7 6 5 4 3 2 1 0

31

X

24

X

7 6 5 4 3 2 1 0

23

X

16

X

7 6 5 4 3 2 1 0

15

X

8

X

7 6 5 4 3 2 1 0

7

X

C

L

R

C

0

G

X

E

N

Page 19

3.4.2 LAPS Mode

In LAPS mode the FCS is calculated LSB first and the FCS sum is

transmitted in reversed bit order

within each byte. See Figure 6 and

Figure 7.

3.5 Performance Monitoring

For performance monitoring purposes, the HDMP-3001 contains a

number of delta bits, event bits

and error counters.

Delta bits are set by the HDMP3001 when a monitored parameter

changes state. The delta bit then

stays high until the controller

PINS

TX_DATA[7]

TX_DATA[6]

TX_DATA[5]

TX_DATA[4]

TX_DATA[3]

TX_DATA[2]

TX_DATA[1]

TX_DATA[0]

7

6

X

7

S

C

R

F = FIRST

L = LAST

F

7 6 5 4 3 2 1 0

[7] [0]

5

4

3

2

1

0

clears the bit. If a clear occurs simultaneously with a parameter

state change, the delta bit remains

set. Delta bits are indicated by a

_D suffix.

When LATCH_CNT in register

0x001 is written from a 0 to a 1, it

produces a pulse on an internal

signal, LATCH_EVENT.

All the internal performance

monitoring counter blocks are

comprised of a running error

counter and a holding register

that presents stable results to the

controller. The counts in all of the

X

4

3

S

C

R

C

R

C

G

E

N

F

7 6 5 4 3 2 1 0

F

0 1 2 3 4 5 6 7

L

L

7

6

M

5

L

4

A

P

3

S

2

/

1

F

0

L

running counters are latched into

the hold registers and the running

counters are cleared when a pulse

occurs on LATCH_EVENT.

To prevent missing a count that

occurs when latching occurs, a

counter is set to one, rather than

zero, if the clear signal is simultaneous with an increment. After

being latched, the results are held

to be read by the microprocessor.

The running counters will stop at

their maximum value rather than

roll over to zero.

F

L

PINS

TXD0

4

0

I

1

I

2

I

3

LSN

MSN

TXD1

5

TXD2

6

TXD3

7

Figure 6. LAPS Payload Bit Order

PINS

TX_DATA[7]

TX_DATA[6]

TX_DATA[5]

TX_DATA[4]

TX_DATA[3]

TX_DATA[2]

TX_DATA[1]

TX_DATA[0]

7

6

5

4

3

2

1

0

Figure 7. LAPS FCS Bit Order

19

X

F

7

S

[7] [0]

C

R

7 6 5 4 3 2 1 0

X

4

3

S

C

R

L

F

7 6 5 4 3 2 1 0

24

X

31

X

7 6 5 4 3 2 1 0

16

X

23

X

7 6 5 4 3 2 1 0

8

X

15

X

7 6 5 4 3 2 1 0

0

X

C

L

R

C

7

G

X

E

N

Page 20

Summary delta event bits provide

a consolidated view of the various

individual delta event bits,

grouped either by function or

SONET tributary. Summary delta

events are therefore a function of

the other delta events bits in the

register maps. The summary bits

are read only, and will only be

cleared when all delta event bits

that contribute to them are

cleared.

The summary bits are O/R'd together to form the HDMP-3001

interrupt outputs, INTB and

APS_INTB. The contribution of

any of these bits to the summary

interrupts can be deleted by setting the corresponding mask bit.

3.6 Test

3.6.1 Loopbacks

Several loopbacks are provided

for test purposes, as shown in

Figure 8:

• Loopback 1:

SONET_R_TO_R_LOOPL,

requires STS-3c/STM-1 mode

with TX_SONETCLK =

RX_SONETCLK.

• Loopback 2:

SONET_R_TO_T_LOOP,

requires STS-3c/STM-1 mode

with TX_SONETCLK =

RX_SONETCLK.

• Loopback 3: Loopback done

on the board level.

• Loopback 4:

MII_T_TO_R_LOOP, only

supported in PHY mode, i.e.

when the HDMP-3001 drives

the MII clocks.

The loopback modes are selected

by programming register bits in

the register map. For details

please refer to the description of

register 0x001.

In SONET loopback mode

SONET_R_TO_T_LOOPL, the

data received on the RX_DATA

pins is routed straight to the

TX_DATA pins. The data is not

processed by the chip. In SONET

loopback mode

SONET_R_TO_T_LOOP, the data

received on the RX_DATA pins is

processed by the line side receive

circuitry. After the framer the

1

2

Figure 8. Loopbacks

TX TX_LAPS

OVERHEAD

RX

F

I

F

O

data is looped back to the line

side transmit circuitry, from

where it is sent out on the

TX_DATA pins.

The Ethernet loopback mode can

be enabled by setting register bit

MII_LOOPBACK_MODE. In

loopback mode, the MII RX interface and MII TX interface are

used together to route the MAC

frames from the MAC device back

to the MAC device. That is, the

MAC frames under test are received from the MAC device

through the MII TX interface.

Then, the MAC frames are not

processed and are sent directly to

the MII RX interface.

THIRD LOOPBACK

3

OUTSIDE CHIP

4

MII

RX_LAPS

20

Page 21

3.6.2 JTAG

The HDMP-3001 supports the

IEEE 1149.1 Boundary Scan standard. The Test Access Port

consists of 5 pins as defined in

Table 10. Signals TDI, TMS and

TRSTSB are all pulled up to logic

one when not driven.

Table 9. JTAG pins

Signal Name Description

TDI Signal input to the TAP controller

TMS TAP controller state machine control

TCK TAP controller clock

The HDMP-3001 TAP supports the

mandatory EXTEST, SAMPLE/

PRELOAD, and BYPASS instructions along with the optional

CLAMP and HIGHZ instructions.

The instructions and their

opcodes are listed in Table 11.

The TAP generates a two-phase

non-overlapping clock to control

the boundary scan chain based

upon the input signal TCK. The

TAP controller is optimized to

work at 10 MHz.

3.7 Interrupts

The microprocessor interface can

be operated in either an interrupt

driven or a polled mode. In both

modes, the HDMP-3001 register

bit SUM_INT can be used to determine whether or not changes have

occurred in the state of monitoring registers.

3.7.1 Interrupt Driven Mode

In an interrupt driven mode, the

SUM_INT_MASK bit should be

cleared. This allows the INT output to become active. In addition,

the RX_APS_INT_MASK bits of

the receive side should be cleared

(to logic zero). This allows the

APS_INTB output to become active (logic zero). If an interrupt

occurs, the microprocessor can

first read the summary status registers to determine the class(es)

of interrupt source(s) that is active, and then read the specific

registers in that class(es) to determine the exact cause of the

interrupt.

TRSTB Asynchronous TAP reset

TDO Scan output from TAP

Table 10. JTAG instructions supported

Instruction Opcode Description

EXTEST 00 Board Level Interconnection Testing

SAMPLE/ PRELOAD 02 Snapshots of Normal Operation

BYPASS FF Normal Chip Operation

HIGHZ 08 Outputs in High Impedance State

CLAMP 04 Holds Values from Boundary-Scan

Chain to Outputs

3.7.2 Polled Mode

The SUM_INT_MASK and

RX_APS_INT_MASK bits should

be set to logic 1 to suppress all

hardware interrupts and operate

in a polled mode. In this mode,

the HDMP-3001 outputs INT and

APS_INTB are held in the inactive

(logic one) state.

Note that the SUM_INT_MASK

and RX_APS_INT_MASK bits do

not affect the state of the register

bits SUM_INT and RX_APS_INT.

These bits can be polled to determine if further register

interrogation is needed.

3.7.3 Interrupt Sources

The interrupt sources are divided

into four groups. Each group can

be masked and each interrupt

source within the group can be

individually masked.

TOH_D_SUM group indicates

that at least one of the delta signals below is unmasked and set.

RX_LOS_D, RX_OOF_D,

RX_LOF_D, RX_LAIS_D,

RX_LRDI_D, RX_K1_D,

K1_UNSTAB_D,

RX_K2_D, J0_OOF_D

PTR _D_SUM group indicates

that at least one of the delta signals below is unmasked and set.

RX_PAIS_D, RX_LOP_D

PATH_D_SUM group indicates

that at least one of the delta signals below is unmasked and set.

RX_PLM_D, RX_UNEQ_D,

RX_G1_D, RX_C2_D, J1 _AVL,

J1_OOF_D

21

Page 22

EOS_D_SUM group indicates

that at least one of the delta signals below is unmasked and set.

NEW_RX_MIN_ERR,

NEW_RX_MAX_ERR,

NEW_RX_OOS_ERR,

NEW_RX_FORM_DEST_ERR,

NEW_RX_FIFO_UR_ERR,

NEW_RX_FIFO_OF_ERR,

NEW_RX_FCS_HEC_ERR,

NEW_TX_FIFO_UR_ERR,

NEW_TX_FIFO_OF_ERR,

NEW_TX_ER_ERR,

NEW_TX_MII_ALIGN_ERR

3.7.4 APS_INTB

RX_APS_INT interrupt message

for APS (K1 and K2) indicates that

at least one of the RX_K1_D,

RX_K2_D, K1_UNSTAB_D is one

and the corresponding mask bits

and RX_APS_INT_MASK are zero.

3.8 Data Processing

The LAPS and GFP TX Processing

refers to the encapsulation of the

MAC (Media Access Control)

frames coming from the MII (Media Independent Interface, see

IEEE 802.3 specification) into the

LAPS/GFP frames, which are then

sent to the Line Side Interface

(SONET/SDH). Figure 9 shows an

Ethernet MAC frame, and Figure

10 a LAPS frame with a MAC payload.

3.8.1 LAPS Processing

The Transmit LAPS Processor

provides the insertion of packetbased information into the STS

SPE. It provides packet encapsulation, FCS field generation,

inter-packet fill and scrambling.

The Transmit LAPS Processor

performs the following functions:

• Encapsulates packets within

an LAPS frame. Each packet is

encapsulated with a start flag

(0x7E), a 32-bit FCS field,

Address, Control and SAPI

PREAMBLE

START OF FRAME DELIMITER

DESTINATION ADDRESS (DA)

OCTETS WITHIN

FRAME ARE

TRANSMITTED FROM

TOP TO BOTTOM

MSB

Figure 9. An Ethernet MAC frame

MSB

MSB

MSB

MSB

OCTETS WITHIN

FRAME ARE

TRANSMITTED FROM

TOP TO BOTTOM

Figure 10. The format of a LAPS frame with a MAC payload

MSB

MSB

MSB

fields, and an end of field flag

(0x7E). All fields except the

start flag can be disabled

through configuration.

• Optional self-synchronous

transmit payload scrambler

(X43 +1 polynomial).

• Transparency processing

(octet stuffing for Flags &

Control Escape). Byte stuffing

occurs between start and end

of field flags. Stuffing replaces

SOURCE ADDRESS (SA)

LENGTH/TYPE

MAC CLIENT DATA

FCS

BIT 7 BIT 0

FLAG (0x7E)

ADDRESS (0x04)

CONTROL (0x03)

SAPI MSB (0xFE)

SAPI LSB (0x01)

DESTINATION ADDRESS (DA)

SOURCE ADDRESS (SA)

LENGTH/TYPE

MAC CLIENT DATA

FCS OF MAC

FCS OF LAPS

FLAG (0x7E)

BIT 8 BIT 1

each byte within a frame that

matches the flag or control

code bytes with a two-byte

sequence.

• Provides the ability to insert

FCS errors for testing under

SW control.

• Provides for selectable

treatment of FIFO underflow.

A FIFO underflow condition

occurs when a TX FIFO empty

occurs prior to the end of a

7 OCTETS

1 OCTET

6 OCTETS

6 OCTETS

2 OCTETS

46 - 1500 OCTETS

4 OCTETS

LSB

1 OCTET

LSB

1 OCTET

LSB

1 OCTET

LSB

1 OCTET

LSB

1 OCTET

LSB

6 OCTETS

6 OCTETS

2 OCTETS

46 - 1500 OCTETS

4 OCTETS

4 OCTETS

LSB

LSB

MAC

FRAME

1 OCTET

22

Page 23

packet. When this occurs an

interrupt is generated. The

packet can be ended via

generation of an FCS error, via

an abort sequence, or via “fill”

bytes inserted in the gap,

depending upon a software

configurable escape code.

• Maintains performance

monitor counters.

3.8.1.1 FCS Polynomial for LAPS

Processing

The HDMP-3001 supports CRC-32

Frame Check Sequence (FCS)

generation and checking. The

polynomial used to generate and

check the FCS is

X32 + X26 + X23 + X22 + X16 + X

12

+ X11 + X10 + X8 + X7 + X5 + X4 +

X2 + X + 1.

The FCS field is calculated over

all bits of the Address, Control,

Payload, Information and Padding

fields, not including any octets

inserted for transparency. This

does not include the Flag Sequences nor the FCS field itself.

The CRC generator and checker

are initialized to all ones. Upon

completion of the FCS calculation

the FCS value is ones-complemented. It is this new value that is

inserted in the FCS field.

3.8.1.2 LAPS Scrambling

Scrambling is performed to protect the SONET/SDH line against

malicious users deliberately sending packets to cause long

run-lengths of ones or zeros or

replicating the SONET/SDH framing bytes. In the transmit

direction an X43 +1 scrambler

scrambles all SPE payload data.

In the receive direction, a self-synchronous X43 +1 descrambler

recovers the scrambled data.

3.8.2 GFP Processing

The Transmit GFP Processor provides the insertion of packetbased information into the STS

SPE. It provides packet encapsulation, FCS field generation,

inter-packet fill and scrambling.

The GFP Processor performs the

following functions:

• Counts the Ethernet frame

length.

• Calculates the payload length

field, (PLI).

• Performs XOR with values as

shown in Figure 11.

• Generates and sends cHEC

and XOR (Figure 11).

• Sends programmable TYPE

values.

• Generates and sends tHEC.

• Sends programmable DP, SP,

and SPARE.

• Generates and sends eHEC.

• Generates and sends optional

FCS.

3.8.2.1 FCS Polynomial for GFP

Processing

The HDMP-3001 supports CRC-32

Frame Check Sequence (FCS)

generation and checking. The

polynomial used to generate and

check the FCS is

X32 + X26 + X23 + X22 + X16 + X

12

+ X11 + X10 + X8 + X7 + X5 + X4 +

X2 + X + 1.

The FCS field is calculated over

the GFP payload, excluding all

headers. The CRC generator and

checker are initialized to all ones.

Upon completion of the FCS calculation the FCS value is

ones-complemented. It is this new

value that is inserted in the FCS

field.

3.8.2.2 HEC Polynomial for GFP

Processing

The following polynomial is used

for generating and checking the

HECs:

X16 + X12 + X5 + 1

An HEC is calculated over each

header. The initial value of the

CRC registers is zero and the HEC

is not inverted before being sent.

23

Page 24

NOTE: ‘+’ IN THE DIAGRAM BELOW IS AN EXCLUSIVE OR FUNCTION

MSB PLI '+' 0xB6 NUMBER OF BYTES IN THE GFP PAYLOAD

LSB PLI '+' 0xAB

MSB cHEC '+' 0x31

NON-SCRAMBLED

LSB cHEC '+' 0xE0

MSB TYPE PROGRAMMABLE

LSB TYPE PROGRAMMABLE

MSB tHEC

LSB tHEC

DP PROGRAMMABLE SP PROGRAMMABLE

SPARE

MSB eHEC

LSB eHEC

+ 1)

43

OCTET TRANSMISSION ORDER

SCRAMBLED (X

MSB FCS[31:24] 1) 32-BIT CRC POLYNOMIAL

FCS[23:16] 2) ON PRE-SCRAMBLED DATA

FCS[15:8] 3) COVERS THE GFP PAYLOAD DATA ONLY

LSB FCS[7:0]

BIT TRANSMISSION ORDER

Figure 11. The GFP frame

3.8.2.3 GFP Scrambling

Scrambling is performed to protect the SONET/SDH line against

malicious users deliberately sending packets to cause long

run-lengths of ones or zeros or

replicating the SONET/SDH framing bytes. In the transmit

direction an X43 +1 scrambler

scrambles all SPE payload data

except core headers. In the receive direction, a

self-synchronous X43 +1

descrambler recovers the

scrambled data.

PROGRAMMABLE

MAC PAYLOAD

64-1522 BYTES

3.9 SONET/SDH Processing

The HDMP-3001 performs standard

STS-3c/STM-1 processing for both

the transmit and receive directions. In the transmit direction, the

LAPS/GFP packets are encapsulated into the SONET/SDH SPE/

VC. The POH and TOH/SOH are

inserted, and the resulting STS signal is transmitted in byte wide

format to a parallel to serial

converter and then to a fiber optic

transceiver.

CORE HEADER

TYPE HEADER

HEADER

EXTENDED

GFP PAYLOAD DATA

FCS (OPTIONAL)

In the receive direction the process is reversed. The byte wide

STS signal is received, the HDMP3001 locates the frame and TOH/

SOH, interprets the pointer, terminates the TOH/SOH and POH,

extracts the SPE/VC, and then extracts the LAPS/GFP packets from

the SPE/VC payload. The LAPS/

GFP frames are then processed

and passed on to an appropriate

link layer device via the MII system interface.

3.9.1 Transmit SONET/SDH Processing Overview

The Transmit SONET/SDH Processor provides for the

encapsulation of LAPS/GFP packets into the SPE/VC. It then

inserts the appropriate POH and

TOH/SOH and outputs the final

STS signal to a parallel to serial

converter. The processor performs the following functions:

• Multiplexes LAPS/GFP packets

from the system interface with

Path Overhead (POH) bytes

that it generates to create the

SPE for SONET or VC for SDH.

• Supports the following POH

bytes: Path Trace (J1), Path

BIP-8 (B3), Signal Label (C2),

and Path Status (G1). Other

POH bytes are transmitted as

fixed all zeros.

• Performs AIS and Unequipped

signal insertion.

• TOH/SOH generation,

including:

• Frame bytes, A1A2

• Section Trace, J0

• Section Growth, Z0

• Section BIP-8, B1

• Orderwire, E1, E2

• Section User Channel, F1

• Data Communications

Channel, D1-D12

24

Page 25

• Pointer Bytes, H1, H2, H3

• BIP-96/24, B2

• APS bytes, K1, K2

• Synchronization Status, S1

• Line/MS REI, M1

• Transmits undefined TOH/SOH

as fixed all zeros.

• Scrambles payload using

SONET/SDH frame

synchronous descrambler,

polynomial (X7 + X6 +1).

3.9.2 Receive SONET/SDH Process-

ing Overview

The Receive SONET/SDH Processor provides for the framing of the

STS signal, descrambling, TOH/

SOH monitoring including B1 and

B2 monitoring, AIS detection,

pointer processing, and POH

monitoring. The Receive SONET/

SDH Processor performs the following functions:

• SONET/SDH framing, [A1

A2] bytes are detected and

used for framing. Provides

OOF and LOF indicators

(single event and second

event).

• Descrambles payload

using SONET/SDH frame

synchronous descrambler,

polynomial (X7 + X6 +1).

• Monitors incoming B1 bytes

and compares them to

recalculated BIP-8 values.

Provides error event

information.

• Monitors incoming B2 bytes

and compares them to

recalculated BIP-96/24 values.

Provides error event

information.

• Monitors K1 and K2 bytes,

which are used for sending

Line/MS AIS or RDI, and for

APS signaling.

• Monitors the four LSBs of

received S1 bytes for

consistent values in

consecutive frames.

• Monitors the M1 byte to

determine the number of B2

errors that are detected by the

remote terminal in its received

signal.

• Outputs the received E1, F1,

and E2 bytes and two serial

DCC channels, SDCC (D1-D3)

and LDCC (D4-D12).

• Examines the H1-H2 bytes to

establish the state of the

received pointer (Normal,

LOP, AIS). If the pointer state

is normal, the first H1H2 bytes

are read to determine the

start of the SPE/VC.

• Monitors POH bytes J1, B3, C2,

and G1 for errors or changes in

state.

• Monitors/captures J1 bytes. In

SONET applications, captures

64 consecutive J1 bytes and in

SDH applications looks for a

repeating 16 consecutive J1

byte pattern.

• Monitors C2 bytes for

verification of correct

tributary types. The tributary

is checked for five consecutive

frames with identical C2 byte

values.

• Monitors G1 for REI-P and

RDI-P.

• Monitors incoming B3 bytes

and compares them to

recalculated BIP-8 values.

Provides error event

information.

3.9.3 Transmit SONET/SDH

Processing Details

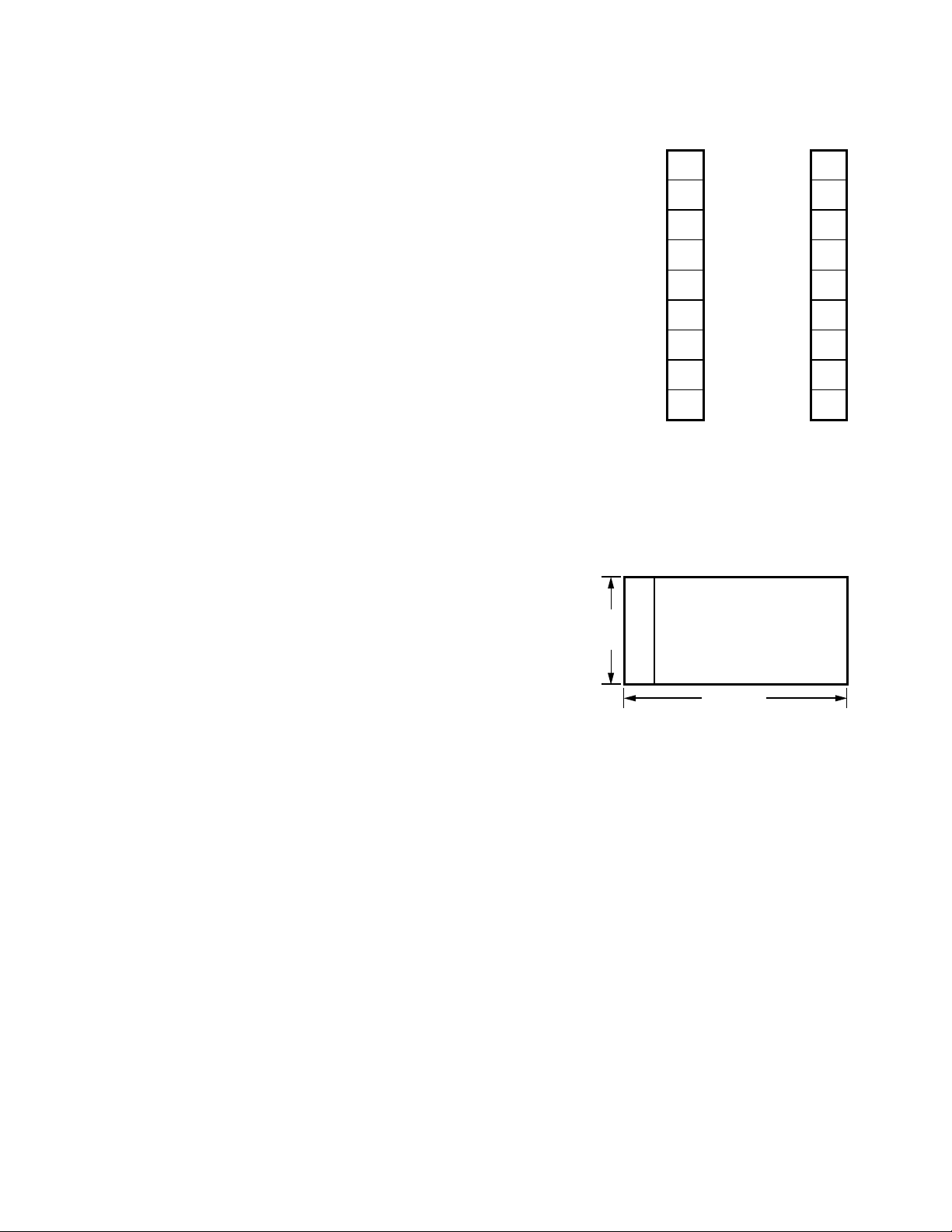

3.9.3.1 SPE/VC Structure

The first column of the SPE/VC is

the POH. The ordering of these

nine bytes is shown in Figures 12

and 13 for SONET and SDH.

SONET POH

Figure 12. The structure of the SONET STS-3c

SPE and SDH VC-4

9 ROWS

Figure 13. STS-3c SPE or VC-4 Structure

J1

B3

C2

G1

F2

H4

Z3

Z4

Z5

PAYLOAD CAPACITY (2340 BYTES)

POH 9 BYTES

261 COLUMNS

SDH POH

J1

B3

C2

G1

F2

H4

F3

K3

N1

25

Page 26

3.9.3.2 POH

There are nine bytes of path overhead. The first byte of the path

overhead is the path trace byte,

J1. Its location with respect to the

SONET/SDH TOH/SOH is indicated by the associated STS/AU

pointer. The following sections

define the transmitted values of

the POH bytes. Where the byte

names differ between SONET and

SDH, the SONET name is listed

first.

3.9.3.2.1 Path Trace (J1)

The HDMP-3001 can be programmed to transmit either a

16-byte or a 64-byte path trace

message in the J1 byte. The messages are stored in

TX_J1[63:0]_[7:0]. In SDH mode,

the J1 byte is transmitted repetitively as the 16-byte sequence in

TX_J1[15]_[7:0] down to

TX_J1[0]_[7:0]. Otherwise, the

64-byte sequence in

TX_J1[63]_[7:0] down to

TX_J1[0]_[7:0] is transmitted.

(The 16-byte sequence is used in

the SDH mode, and the 64-byte

sequence in the SONET mode.)

3.9.3.2.2 Path BIP-8 (B3)

The Bit Interleaved Parity 8 (BIP-

8) is transmitted as even parity

(normal) if register bit B3_INV =

0. Otherwise, odd parity (incorrect) is generated. The BIP-8 is

calculated over all bits of the previous SPE/VC (including the POH)

before scrambling and placed into

the B3 byte of the current SPE/VC

before scrambling. By definition

of BIP-8, the first bit of B3 provides parity over the first bit of all

bytes of the previous SPE/VC, the

second bit of B3 provides parity

over the second bit of all bytes of

the previous SPE/VC, etc.

the SPE/VC. The provisioned

value, TX_C2[7:0], is inserted into

the generated C2 bytes.

3.9.3.2.4 Path Status (G1)

The receive side monitors B3 bit

errors in the received SPE/VC.

The number of B3 errors detected

in each frame (0 to 8) is transferred from the receive side to the

transmit side for insertion into the

transmit path status byte, G1, as a

Remote Error Indication. If register bit PREI_INH = 0, the bits are

set to the binary value (0000

through 1000, indicating between

0 and 8) equal to the number of

B3 errors most recently detected

by the Receive Side POH monitoring block. Otherwise, they are set

to all zeros.

Path RDI. Bit 5 of G1 can be used

as a Path/AU Remote Defect Indication, RDI-P, or bits 5, 6, and 7 of

G1 can be used as an enhanced

RDI-P indicator. The values transmitted in bits 5, 6, and 7 of G1 are

taken either from the TX_G1[2:0]

registers (if PRDI_AUTO = 0), or

the HDMP-3001 automatically

generates an enhanced RDI signal

(if PRDI_AUTO = 1 and

PRDI_ENH = 1), or a one bit RDI

signal (if PRDI_AUTO = 1 and

PRDI_ENH = 0). The values transmitted in bits 5, 6, and 7 of G1 are

shown in Table 11.

If PRDI_AUTO = 1, the values

shown above are transmitted for a

minimum of 20 frames. Once 20

frames have been transmitted

with the same value, the value

corresponding to the current state

of the defect indication values

listed in Table 1 will be transmitted. Bit 8 of G1 (the LSB) is

unused, and it is set to zero.

are transmitted as all zeros. These

include the path user channel

(F2), the position indicator (H4),

the path growth/user channel (Z3/

F3), the path growth/path APS

channel (Z4/K3), and the tandem

connection monitoring (Z5/N1)

bytes.

3.9.3.2.6 SONET/SDH Frame

Generation

The SONET/SDH frame generator

creates an STS-3c/STM-1 by generating the Transport (Section)

Overhead (TOH/SOH) bytes, filling the payload with bytes from

SPE/VC, and scrambling all bytes

of the SONET/SDH signal except

for the first row of TOH/SOH

bytes.

3.9.3.2.7 Frame Alignment

HDMP-3001 does not support

frame alignment in the transmit

direction.

3.9.3.2.8 Payload Generation

The SONET or SDH payload is

normally filled with bytes from

the SPE/VC. The J1 byte of the

SPE/VC is placed into column 10

of row 1.

3.9.3.2.3 Signal Label (C2)

The signal label byte indicates the

composition, e.g. LAPS or GFP, of

26

3.9.3.2.5 Other POH Bytes

The remaining POH bytes are not

supported by the HDMP-3001 and

Page 27

Table 11. Path RDI bit values

PRDI_AUTO PRDI_ENH RX_PAIS RX_UNEQ RX_PLM G1 Bits 5, 6, and 7

RX_LOP

0 x x x x TX_G1[2:0]

101 x x 100

0x x000

1 1 x x 101

01 x110

00 1010

00 0001

3.9.3.2.9 POH AIS Generation

Normal generation of SONET/

SDH payload is suspended during

transmission of the Line (Multiplex Section or MS) Alarm

Indication Signal, LAIS, or the

Path (Administrative Unit or AU)

AIS signals, PAIS. AIS is generated if:

• TX_LAIS or TX_PAIS = 1. In

addition the entire payload

(9396 or 2349 bytes) is filled

with all ones.

• LOF is detected.

• Bits 6 - 8 of K2 are all ones.

• The pointer bytes H1, H2 are

all ones.

3.9.3.2.10 Unequipped Generation

Unless AIS is active, unequipped

SPE/VC (all SPE/VC bytes are

filled with all zeros) is generated

if TX_UNEQ = 1.

3.9.3.3 TOH/SOH Generation

The SONET TOH bytes are generally the same as the SDH SOH

bytes. The following sections define the values generated for all

TOH/SOH bytes. Where the byte

names differ between SONET and

SDH, the SONET names are listed

first. Entries that are blank in

Table 15 are SONET undefined or

SDH non-standardized reserved

bytes. The HDMP-3001 fills these

bytes with all zeros. The Z1 and

Z2 bytes are non-standardized reserved bytes for STM-1.

3.9.3.3.1 TOH/SOH AIS Generation

Normal generation of TOH/SOH

bytes is suspended during transmission of LAIS or PAIS. If

TX_LAIS = 1, the first three rows

of the TOH/SOH are generated

normally, but the remainder of the

TOH/SOH as well as all SPE/VC

bytes are transmitted as all ones

bytes. If TX_PAIS = 1, all rows of

the TOH/SOH are generated normally, except for the pointer bytes

in row four. The H1, H2, and H3

bytes as well as all SPE/VC bytes

are transmitted as all ones.

3.9.3.3.2 Frame Bytes (A1 and A2)

The frame bytes are normally generated with the fixed patterns:

• A1: 1111_0110 = F6

• A2: 0010_1000 = 28

3.9.3.3.3 Section Trace/Regenerator

Section Trace (J0)

Over periods of 16 consecutive

frames, the HDMP-3001 continuously transmits the 16-byte