Page 1

YASNAC J50 PC SYSTEM

INSTRUCTIONS

CNC SYSTEM FOR TURNING APPLICATIONS/ MACHINING CENTERS

Upon receipt of the product and prior to initial operation, read these instructions

thoroughly, and retain for future reference.

‘iAsuAvv14

TOE-C843-1 2.1 B

Page 2

1. OUTLINE 1

2. BLOCK DIAGRAM 1

3. SPECIFICATIONS 2

3.1 FUNDAMENTAL SPECIFICATIONS 2

3.2 PROGRAM FUNCTIONS 2

3.3 MACRO INSTRUCTIONS 2

3.4 INPUT/OUTPUT SPECIFICATIONS 2

PROCEDURES FOR SEQUENCE

4.

PROGRAM PREPARATION 4

5. ADDRESS NUMBER AND ADDRESS MAP 5

ADDRESS NUMBER 5

5.1

5.2 ADDRESS MAP AND DISPLAY SYMBOL 5

5.3 1/0LIST AND SEQUENCE LADDER 12

SEQUENCE CONTROL METHOD 13

6.

6.1 DIFFERENCES IN OPERATION 13

6.2 SCANNING TIME (PROCESSING TIME) 13

6.3 MEMORY CAPACITY OF SEQUENCE

PROGRAM 14

PC INSTRUCTIONS 15

7.

PRELIMINARY KNOWLEDGE 15

7.1

7.2

TYPES OF INSTRUCTIONS AND LISTS 15

INSTRUCTIONS FOR RELAYS 19

7.3

7.4

INSTRUCTIONS FOR TIMERS 22

7.5

INSTRUCTIONS FOR REGISTERS 22

7.6

CONTROL INSTRUCTIONS 30

MACRO INSTRUCTIONS 31

7.7

SEQUENCE PROGRAM EXAMPLE 43

8.

8.1

SERIES CONNECTION 43

PARALLEL CONNECTION 43

8.2

SERIES AND PARALLEL CONNECTION 43

8.3

MASTER CONTROL RELAY APPLICATIONS 44

8.4

9.2

SEQUENCE PROGRAM EDITOR (JDUO1) 46

9.3

CONNECTING SEQUENCE PROGRAM

EDITOR 46

EDIT SYSTEM OPERATOR’S STATION 47

9.4

FUNCTION MODE OF EDIT SYSTEM 48

9.5

HOW TO ENTER EDITING SYSTEM MODE 49

9.6

EDITING MODE (MODE 1) 50

9.7

9.8

LIST TAPE INPUT/OUTPUT MODE (MODE 2) 54

P-ROM WRITER MODE (MODE 3) 57

9.9

PARAMETER MODE (MODE 4) 59

9.10

PC DATA TABLE EDIT MODE (MODE 5) 62

9.11

ADDRESS CHECK MODE (MODE 6) 62

9.12

RETURN TO NC SYSTEM MODE (MODE 4) 64

9.13

9.14

OPERATING PROCEDURE 65

10. SEQUENCE PROGRAM

OFFLINE EDITING SYSTEM 67

OUTLINE OF OFFLINE EDITING SYSTEM 67

10.1

10.2 SOURCE FILE 68

10.3 COMPILER 70

10.4 LINKER 71

10.5 CHANGING INTO ROM 72

10.6 JSD LADDER SOURCE CONVERTER 73

10.7 LIST OF ERROR MESSAGES AND

WARNING MESSAGES 73

10.8 NOTES 73

APPENDIX 1

1/0 LIST FOR YASNAC J50L

(FOR LATHES) 74

APPENDIX 2

LIST FOR YASNAC J50M

1/0

(FOR MACHINING CENTERS) 85

APPENDIX 3

LIST OF INTERNAL RELAYS, REGISTERS

FOR YASNAC J50L/J50M 101

SEQUENCE PROGRAM ONLINE

9.

EDITING SYSTEM 45

BLOCK DIAGRAM OF SEQUENCE

9.1

PROGRAM EDIT SYSTEM 45

APPENDIX 4

CONVERSION TABLE OF DECIMAL AND

HEXADECIMAL NOTATION 123

Page 3

INDEX

Subject

A

ADDRESS CHECK MODE (MODE 6) . . . 4 . . . . . . . . . . . . . . . . .9...9.12 . ...62

ADDRESS MAPANDDISPLAY SYMBOL . . . . .. -....- . .-....5.....5.2 . . . . 5

ADDRESS NUMBER. O.... . . . . . . . . . . . . . . . . . . . . . . . ...5.....5.1 . ...5

,ADDRESS NUMBERANDADDRESS MAP . . . . . . . . . . . . . . . . . . 5 . . . . . . . . . . . . . . 5

APPENDIX 1 I/OLISTFORYASNACJ50L

(FORLATHES) . ..o+. o+.... . . . . . . . . . . . . . . . . . .. APPENDIx 1 . . . . . . . . . 74

APPENDIX21/O LISTFORYASNAC J50M

(FOR MACHINING CENTERS).. . . . . . . . . . . . . . . . . . . .. APPENDIX 2 . . . . . . . . . . 85

APPENDIX 3LISTOF INTERNAL RELAYS, REGISTERS

FoRYAsNAcJ50L/J50M.. . . . . . . . . . . . . . . . . . . . . .. APPENDIX3 . . . . . . . . ..101

APPENDIX 4CONVERSION TABLE OFDECIMALAND

HEXADECIMAL NOTATION. . . . . . . . . . . . . . . . . . . . . . ..APPENDIX4 . . . . . . . . . . 123

B

BLOCKDIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...2... . . . . . . . . . . . 1

BLOCK DIAGRAMOFSEQUENCE PROGIWMEDITSYSTEM . . . . . . 9 . . . . . 9.1 . . . . 45

c

CHANGING INTOROM . . . . .......~........... . . . . ...10.....10.5 . ...72

CAMPIER .,. SAC....... . . . . . . . . . . . . . . . . . . . . . ...10.....10.3 . ..-70

Compiler Checking Items. . . . . . . . . . . . . . . . . . . . . . . . . ...10.....10.3.3 . ...71

Compiler Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...10.....10.3.1 . ...70

CONNECTING SEQUENCE PROGRAM EDITOR . c . 0 . . . . 0 0 . . 0 . 9 . . 0 . . 9.3 ~. . . 46

CONTROL INSTRUCTIONS.. . . . . . . . . . . . . . . . . . . . . . . . ...7.....7.6 . ...30

D

DIFFERENCES IN OPERATION . . . . . . . . . . . . . . . . . . .. -.. . <6.....6.1 . ...13

E

EDIT SYSTEM OPERATORS STATION . . . . .. C..... . . . . . ...9.....9.4 . ...47

EDITING MODE (MODE 1). . . . . . . . . . . . . . . . . . . . . . . . ...9.....9.7 . ...50

Editing ofPCDataTables . . . . . . . . . . . . . . . . . . . . . . . . ...9.....9.11.1 . ...62

Error ListofCompile . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...10.....10.3.2 . ...70

Execution Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...10.... . 10.1.2 . ...67

F

Format ofSourceFile . . . . . . . . . . . . . . . . . . . . . . . . . . . ...10.....10.2.1 . ...68

FUNCTION MODEOFEDITSYSTEM. . . . . . . . . . . . . . . . . . . . . .9.....9.5 . ...48

FUNDAMENTAL SPECIFICATIONS . . . . . . . . . . . . . . . . . . . ., ..3.....3.1 . . . . 2

H

HOWTOENTER EDITING SYSTEM MODE . . . . . . . . . . . . . . . . . 9 . . . . . 9.6 . ...49

I

I/OLISTANDSEQUENCELADDER. . . . . . . . . . . . . . . . . . . . . .5. .<..5.3 . ..”12

INPUT/OUTPUTSPECIFICATIONS. . . . . . . . . . . . . . . . . . . . ...3.....3.4 . . . . 2

INSTRUCTIONS FORREGISTERS . . . . . . . . . . . . . . . . . . . . ...7..... 7.5 .“””22

INSTRUCTIONS FORRELAYS . . . . . . . . . . . . . . . . . . . . . . ...7.....7.3 .“””19

INSTRUCTIONS FORTIMERS . . . . . . . . . . . . . . . . . . . . . . ...7..... 7.4 “-””22

J

JSDLADDER SOURCE CONVERTER . . . . . . . . . . . . ..O---O ““IO. O””” 1O..6 ‘“””73

L

Line Connection . . . . . . . . . . . . . . . . . . . . . . . . . . ..”” ”.. ”10..”” “10.5.2. .””72

LINKER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..10 .” >--10.4 “’”-71

Linker Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 10”” ””” 10.4.2 ““’”71

Linker Output File..... . . . . . . . . . . . . ...””” .“”””. ”” .10” ”.”” 10.4.3 ““””72

LIST OFERRORMESSAGES AND WARNING MESSAGES - . “ - “ “ “ 10 “ “ “ “ o 10.7 “ “ “ > 73

LISTTAPEINPUT/OUTPUTMODE (MODE2)”””.””....OC”. .“ 9“”””” 9.8 ““””54

M

MACRO INSTRUCTIONS . . . . .--.-””...”.””””-” ““” ”””” 3””” ””3.3 ““””2

MACRO INSTRUCTIONS.. . . . . . . . . . . . . . . ...4 ‘o oooo. oo7. -4””7.7 ““””31

MASTER CONTROL RELAYAPPLICATIONS ‘“ -. --”” ”””” O”””” 8“”-o. 8.4 ““””44

MDIWrite Operation on Sequence Program. . . . “ . . ““ “ “ ““ “ “ “ “ 9 .- . “ “ 9.7.2 “ “ “ “ 52

MEMORY CAPACITY OFSEQUENCE PROGRAM O.. -”o”o o-o ‘.. 6...”” 6.3 “’””14

N

NOTES . . . . . . . . . . . . . . . . . . . . . . . . . ...””” .“”””. ”””lO. ””. ”10.8 ““””73

o

Object Data and Linker Processing ......o”””.””””””. .. ”. 10”” ”” .10.4.1 ““””71

Operation Environment”.” ‘.-””-”””””-””””””” ““” ”” ”” 10”” ””” 10.1.1 ‘“””67

OPERATING PROCEDURE.. ...<..”..”””””””.”. ““” ”.”” 9.”. ””9.14 ““..65

OUTLINE .0000 OOC” O.’.. “$. .O. O-”.-””””””-””” “oolo-””o.oo-o””o-el

Outline ofExecution File Processing ““””.””...””.”-.”” .o-10.””..10.1.3 ““”.67

OUTLINE OFOFFLINEEDITING SYSTEM .“””””” ”.”” ””. .””10. .“” .10.1 .“67

Outline of Operation .”... .“...””.””””””.”.” “.” ”” ”” lo”””. -10.1.A ““””67

Chapter Section Page

Page 4

INDEX (Cent’d)

Subject

P P-ROM Format Tape Input/c) utput Function ( ~ , m )

P-ROMWRITER M0DE(M0DE3) . . . . . . . . . . . . . . . .

PAWLLEL CONNECTION . . . . . . . . . . . . . . . . . . . . . .

PARAMETER MODE (MODE 4)... . . . . . . . . . . . . . . . .

PC DATA TABLE EDIT MODE.. .................

PC INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . .

PRELIMINARY KNOWLEDGE. . . . . . . . . . . . . . . . . .

PROCEDURES FOR SEQUENCE PROGRAM PREPARATION .

PROGRAM FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . .

R Reading-in, Punch-out, and Verify a P-ROM Format Tape

(IN, OUTand VERoperations) . . . . . . . . . . . . . . . . . . .

REIWRN TO NC SYSTEM MODE (MODE 4) . . . . . . . . . . .

S SCANNING TIME (PROCESSING TIME) . . . . . . . . ~ . . . .

Selection of PROM Writer... . . . . . . . . . . . . . . . . . . .

SEQUENCE CONTROL METHOD . . . . . . . . . . . . . . . . .

Sequence Program Editing . . . . . . . . . . . . . . . . . . . . .

SEQUENCE PROGRAM OFFLINE EDITING SYSTEM . . . . .

SEQUENCE PROGRAM ONLINE EDITING SYSTEM . . 0 . . .

SEQUENCE PROGRAM EDITOR (JDUO1) . . . . . . . . . . ~ .

SEQUENCE PROGRAM EXAMPLE . . . . . . . . . . . . . . . .

SERIES AND PARALLEL CONNECTION . . . . . . . . . . . . .

SERIES CONNECTION . . . ..-. . . . . . . . . . . . . . . . .

SOURCE FILE . . . . .. O...... . . . . . . . . . . . . . .

SOURCE FILES . . . . .. O..... . . . . . . . . . . . . . .

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . .

T TYPES OF INSTRUCTIONS AND LISTS . 0 . . . . . . . . . . . .

W When NC Unit Entered SD Mode from Offline State . . . . .

When NC Unit Entered SD Mode from Online State . . . . .

When NC Unit is in Offline State (System No.6 + SD MODE) c , . . 9 . . . . . 9.6.1 . . . ~ 49

When NC Unit is in Online State (System No.4 + SD MODE) . . . . 9 . . . . . 9,6.2 . . . . 49

Chapter Section

. . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . .

. . . . . .

. . . . . . . . . . .

. . . . . .

. . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . .

. . . .

. . . . . .

. . . . . . . . . . .

. . . . . .

. . . . . .

. . . . . . . . . . .

. . . . . .

. . . . . . . . . . .

. . . . . .

. . . . . .

. . . . . .

. . . . . .

. . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . .

9

9

8

9

9

. . . . . . . . . .

7

7

4 . . . . . . . . . . .

3

9

9

6

. .10.....10.5.1 . ...72

6.. .’ . . . . . . ..”13

9

10..............67

9..............45

9

. . . . . . . . . . . . . .

8

8

8 . . ...8.1 . ...43

10 . . ...10.2 . ...68

10 . ...10.2.2 . ...68

3 ., . . . . . . . . ...2

7

9

9

9.7.3

9.9

8.2

9.10

9.11

7.1

3.2

9.11.2 . . . 62

9.13 ..64

6.2 . ...13

9.7.1 “ . . . 50

9.2 . ...46

8.3 . ...43

7.2 . ..15

9.13.1 . . . . 64

9.13.2 . . . . 64

. . . .

. . . .

. . .

. . .

. . . .

. . . .

. . . .

. . . .

. . . .

Page

53

57

. 43

. 59

62

15

15

4

2

43

...

111

Page 5

1. OUTLINE

1. The programmable controller (called PC hereafter) for

YASNAC J50L/J50M stands between the standard

YASNAC NC unit and the machine tool. It facilitates

the compact and efficient utilization of the sequence

control required by the machine tool through the software.

2. Sequence program editing of PC can be performed efficiently with CRT”; NC and JSD modes are easily

changed and selected.

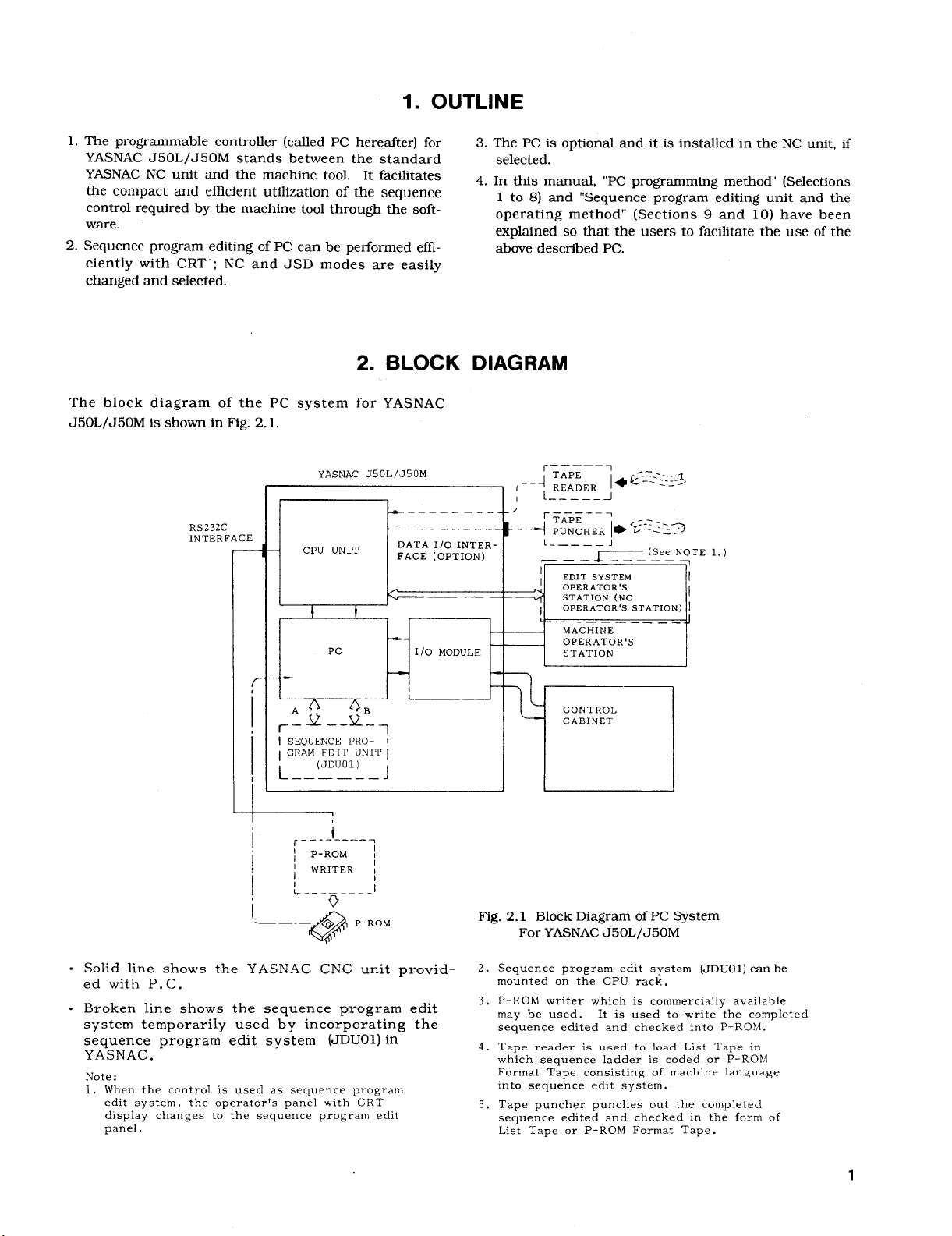

2. BLOCK DIAGRAM

The block diagram of the PC system for YASNAC

J50L/J50M is shown in Fig. 2.1.

YASNAC J50L/J50M

——_ ___ ___ _/

RS232C

INTERFACE

CPU UNIT

n-”-” ----- ‘,

DATA 1/0 lNTER FAcE (OPTION)

3. The PC is optional and it is installed in the NC unit, if

selected.

4. In this manual, “PC programming method” (Selections

1 to 8) and “Sequence program editing unit and the

operating method” (Sections 9 and 10) have been

explained so that the users to facilitate the use of the

above described PC.

~–———–7

,--4

~=:: j

——-—

- +’ %;~HERj* f5~23

L_____J

r :D’= ~y~TEM

● c5’’$~-3

_~_(See NOTE 1.)

1

I

1/0 MODULE

r

-k----n

Solid line shows

ed with P.C.

Broken line shows the sequence program edit

sYstern temporarily used by incorporating the

sequence program edit system (JDUO1) in

YASNAC.

Note:

1. When the control is used as sequence program

edit system, the operator’s panel with CRT

display changes to the sequence program edit

panel.

the YASNAC CNC unit provid-

‘M~CHINE

OPERATOR’S

STATION

—————

J

Fig. 2.1 Block Diagram of PC System

For YASNAC-J50L/J50M

Sequence program edit system (JDUO1) can be

2.

mounted on the CPU rack.

P-ROM writer which is commercially available

3.

may be used.

sequence edited and checked into P-ROM.

4.

Tape reader is used to load List Tape in

which sequence ladder is coded or P-ROM

Format Tape consisting of machine language

into sequence edit system.

5,

Tape puncher punches out the completed

sequence edited and checked in the form of

List Tape or P-ROM Format Tape.

It is used to write the completed

Page 6

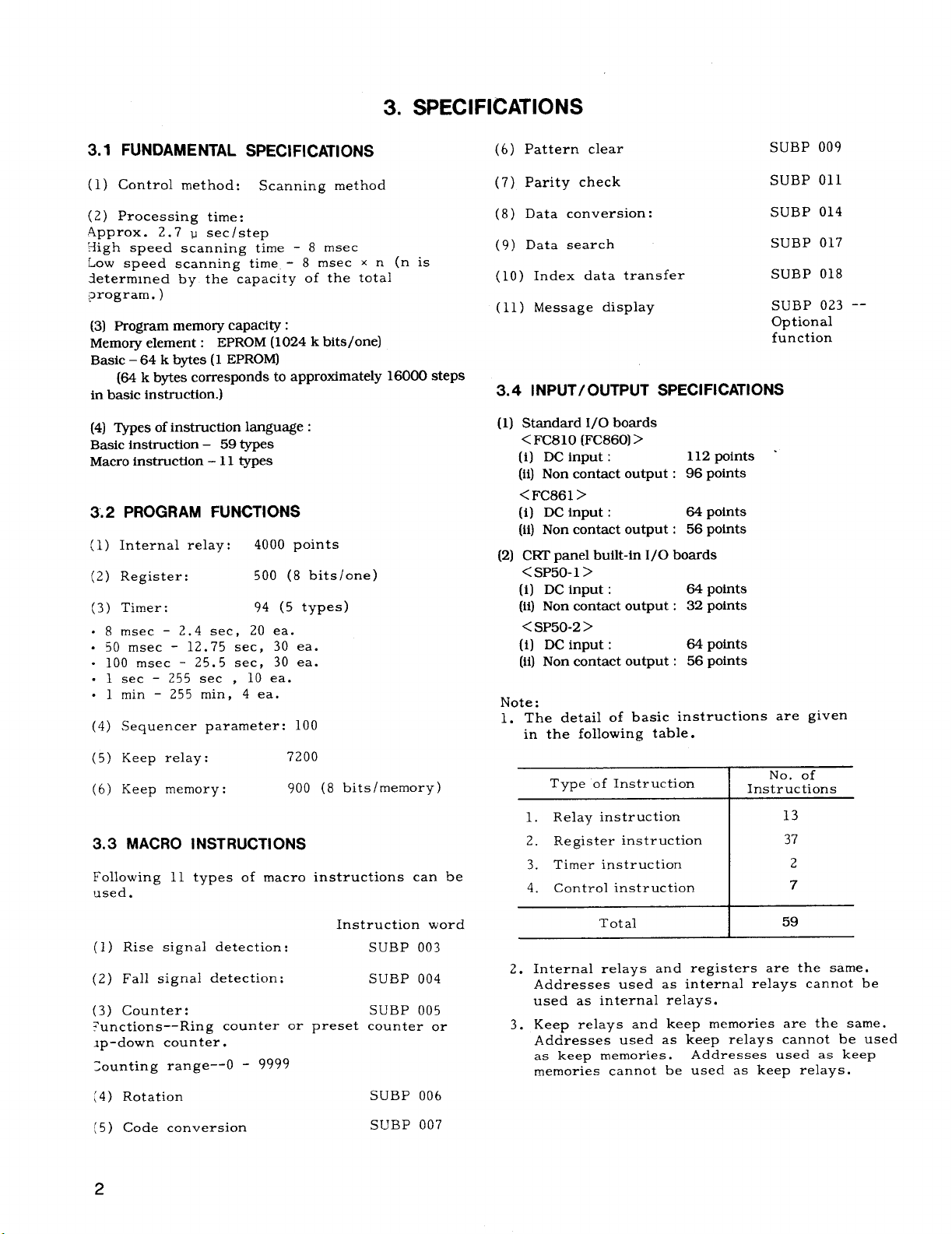

3. SPECIFICATIONS

3.1 FUNDAMENTAL

Control method:

(1)

(2) Processing time:

Approx. 2.7 l.i seclstep

qigh speed scanning time - 8 msec

Low speed scanning time - 8 msec x n (n is

determined by the capacity of the total

program. )

(3) Program memory capacity :

Memory element :

Basic – 64 k bytes (1 EPROM)

(64 k bytes corresponds to approximately 16000 steps

in basic instruction.)

(4) Types of instruction language:

Basic instruction – 59 types

Macro instruction – 11 types

PROGRAM FUNCTIONS

3.2

Internal relay:

(1)

(2) Register:

(3) Timer:

. 8 msec - 2.4 see, 20 ea.

.

50 msec - 12.75 see, 30 ea.

. 100 msec - 25.5 see, 30 ea.

.1

sec –

.1

min

(4)

Sequencer parameter: 100

Keep relay:

(5)

Keep memory:

(6)

3.3

Following 11 types of macro instructions can be

used.

255 sec , 10 ea.

- 255 rein, 4 ea.

MACRO INSTRUCTIONS

SPECIFICATIONS

Scanning method

EPROM (1024 k bits/one)

4000 points

500 (8 bits/one)

94 (5 types)

7200

900 (8 bits/memory)

(6) Pattern clear

(7) Parity check

(8) Data conversion:

(9) Data search

(10) Index data transfer

(11) Message display

3.4

lNPUT/OUTPUT SPECIFICATIONS

(1) Standard 1/0 boards

< FC81O (FC860) >

(i) DC input:

(ii) Non contact output : 96 points

< FC861 >

(i) DC input:

(ii) Non contact output: 56 points

(2) CRT panel built-in 1/0 boards

< SP50-1 >

(i) DC input:

(ii) Non contact output : 32 points

< SP50-2 >

(i) DC input:

(ii) Non contact output : 56 points

Note:

1. The detail of basic instructions are given

in the following table.

Type of Instruction

Relay instruction

1.

2. Register instruction

3. Timer instruction

4. Control instruction

112 points ‘

64 points

64 points

64 points

SUBP 009

SUBP 011

SUBP 014

No. of

Instructions

I

I

SUBP 017

SUBP 018

SUBP 023 -Optional

function

13

37

2

7

Instruction word

(1) Rise signal detection:

(2) Fall signal detection:

(3) Counter:

?unctions--Ring counter or preset counter or

lp-down counter.

Zounting range --O - 9999

Rotation

[4)

Code conversion

(5)

SUBP 003

SUBP 004

SUBP 005

SUBP 006

SUBP 007

2

Tot al

Internal relays and registers are the same.

2.

Addresses used as internal relays cannot be

used as internal relays.

Keep relays and keep memories are the same.

3.

Addresses used as keep relays cannot be used

as keep memories.

memories cannot be used as keep relays.

I

Addresses used as keep

59

Page 7

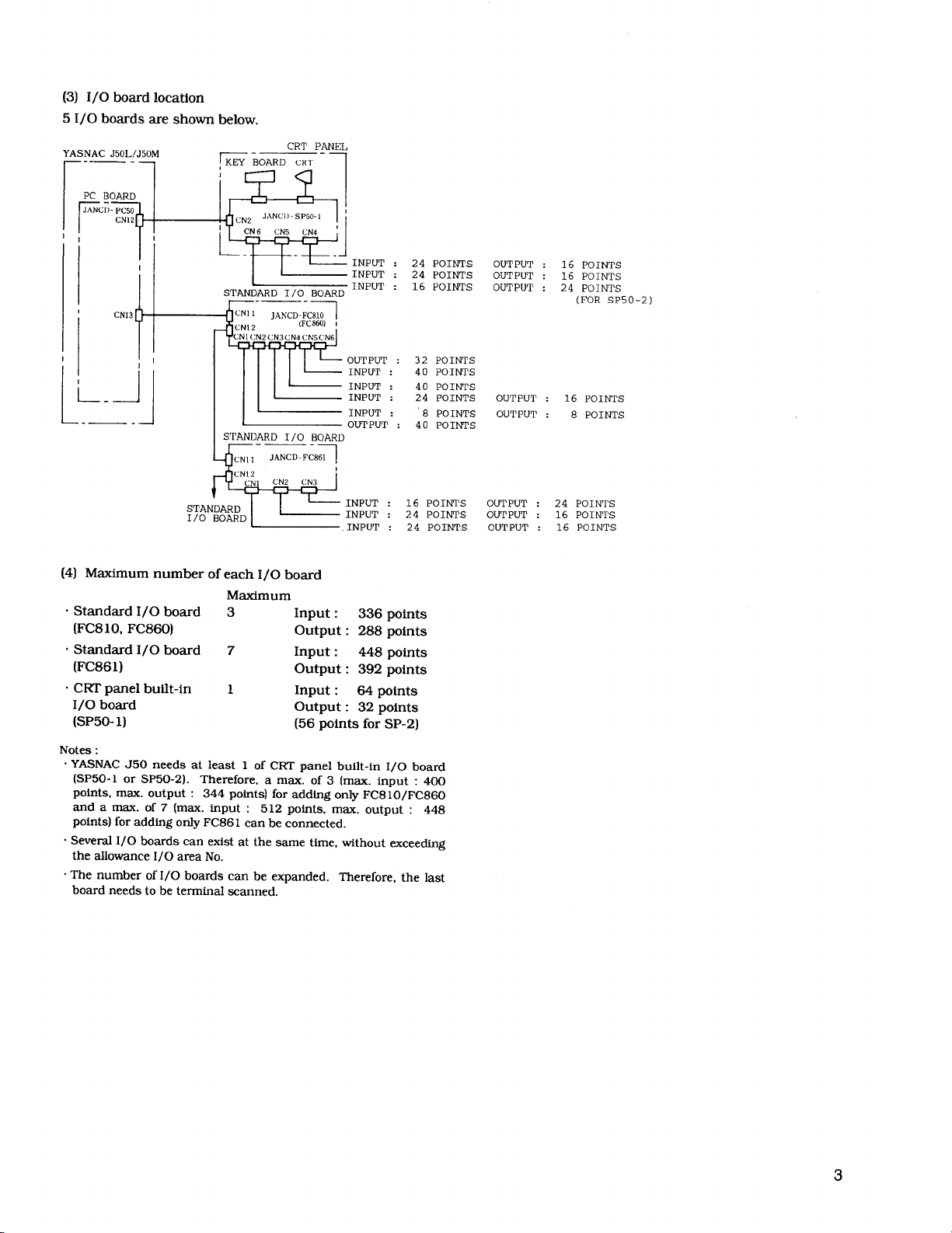

(3) 1/0 board location

5 1/0 boards are shown below,

YASNAC J50L/J50M

-.—.7

r-=

PC BOARD

JANcI)-PCVI

CNIZ

G

CRT PANEL

;OARD CRT -1

I

CN13

!

L--

J

..— - --l

STANDARD I/O BOARD

CNICN2CN3CN40+5CN6

(FCMJO) I

~

STANDARD 1/0 BOARD

-—-

JANCD-FC861

LNI 1

L5-

rub-d

(4) Maximum number of each 1/0 board

Maximum

“ Standard 1/0 board 3

(FC81O, FC860)

. Standard 1/0 board 7

(FC861)

“ CRT panel butlt-in 1

1/0 board

(SP50- 1)

Input :

Output : 288 points

Input :

Output : 392 points

Input :

Output : 32 points

(56 points for SP-2)

1

INPUT :

INPUT :

INPUT :

OUTPUT :

INPUT :

INPUT :

INPUT :

INPUT :

OUTPIJT ;

336 points

448 points

64 points

24 POINTS OUTPUT :

24 POINTS

16 POINTS

32 POINTS

40 POINTS

40 POINTS

24 POINTS OUTPUT :

8 POINTS

40 POINTS

OUTPUT :

OUT PUT :

OUTPUT :

16 POINTS

16 POINTS

24 POINTS

(FOR SP50-2 )

16 POIITI’S

8 POINTS

Notes :

YASNAC J50 needs at least 1 of CRT panel built-in 1/0 board

.

(SP50-1 or SP50-2). Therefore, a max. of 3 (max. input : 400

points,max.output: 344 points)for adding onlyFC810/FC860

and a max. of 7 (max. input : 512 points, max. output : 448

points)foraddingonfyFC861can be connected.

. Several1/0boardscan exist atthe same time,withoutexceeding

the allowance1/0area No.

.The numberof 1/0boards can be expanded. Therefore,the last

board needsto be terminalscanned.

3

Page 8

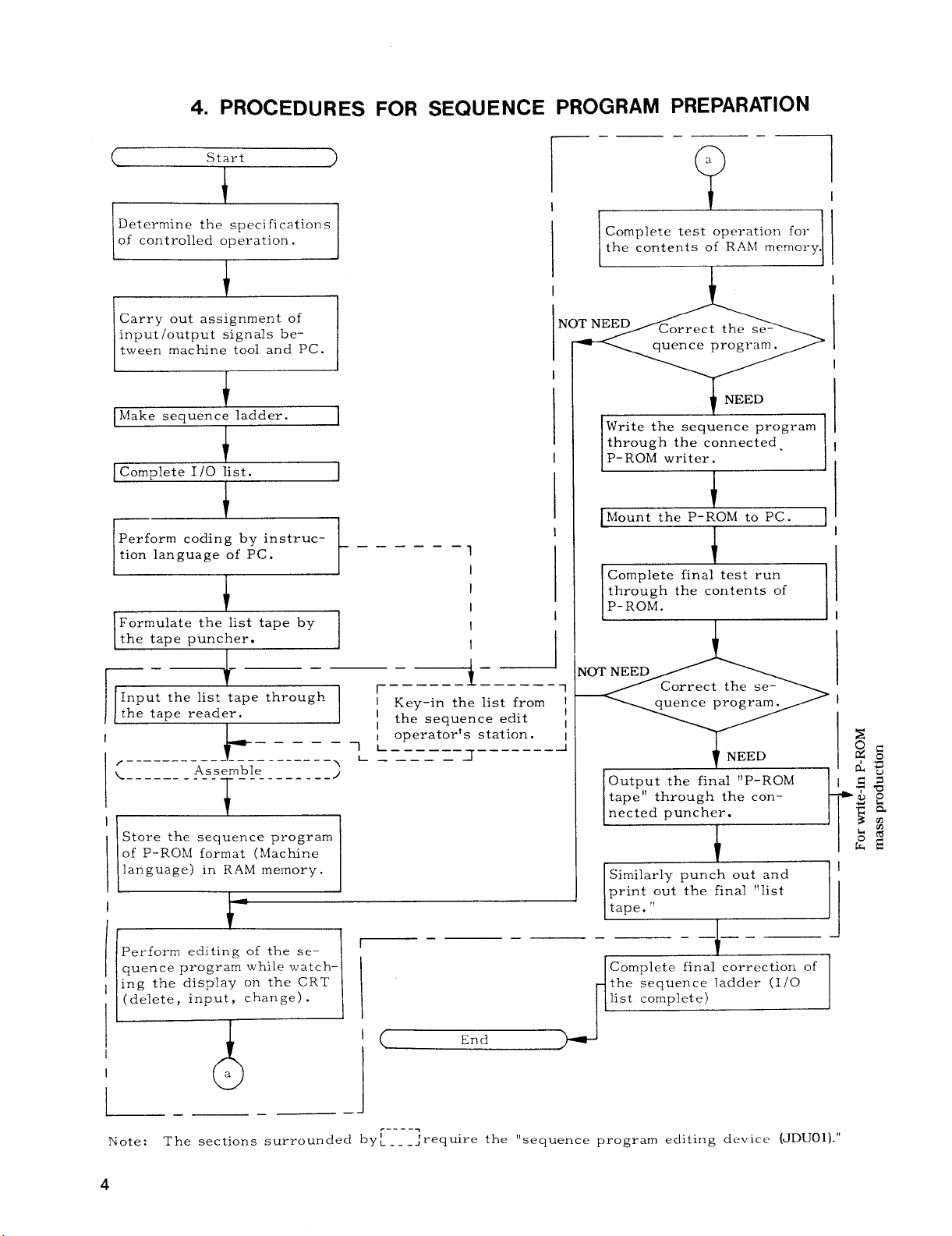

4. PROCEDURES

c

Determine the specifications

controlled operation .

of

L

I I

\Carry out assignment of ]

input loutput signals be–

tween machine tool and PC.

Start

I

I

i

FOR

)

SEQUENCE PROGRAM PREPARATION

,_. - —

a

Q

I

I

I

Complete test operation for

+,

i

NEED

I

I I

==+-

-+=

Perform coding by instruc-

tion language of PC.

Formulate the list tape by

the tape puncher.

T-4- -

Input the list tape through

the tape reader.

I

,— -—----- .-- .-—-- _______ \

Store the sequence program

of P-ROM format (Machine

language) in RAM memory.

1

lF-

7

—.— .—

.——

.

t

I

–1

I

I

I

I

I

-—~---l

~______ A__. __-7

I Key–in the list

! the sequence edit ,

1

operator’s station.

T ~______ .__. _.. __J

L ——— -—

-1

from I

Write the sequence program

through the connected,

I

I

P-ROM writer.

I

Mount the P-ROM to PC.

1

I

Complete final test run

through the contents of

P-ROM.

I

I

1 I

I

I

I I ——

Perform editing of the se-

quence program while watch-

ing the display on the CRT

(delete, input, change) . ,

(

I

— .

1

Note: The sections surrounded by~ .- -;req~re the

a

u

—— —

i

J

End

—

IComplete final correction of I

the sequence ladder (1/0

*

I

“sequence program editing device

- –+– -

I

(JDUO1).”

J

I

Page 9

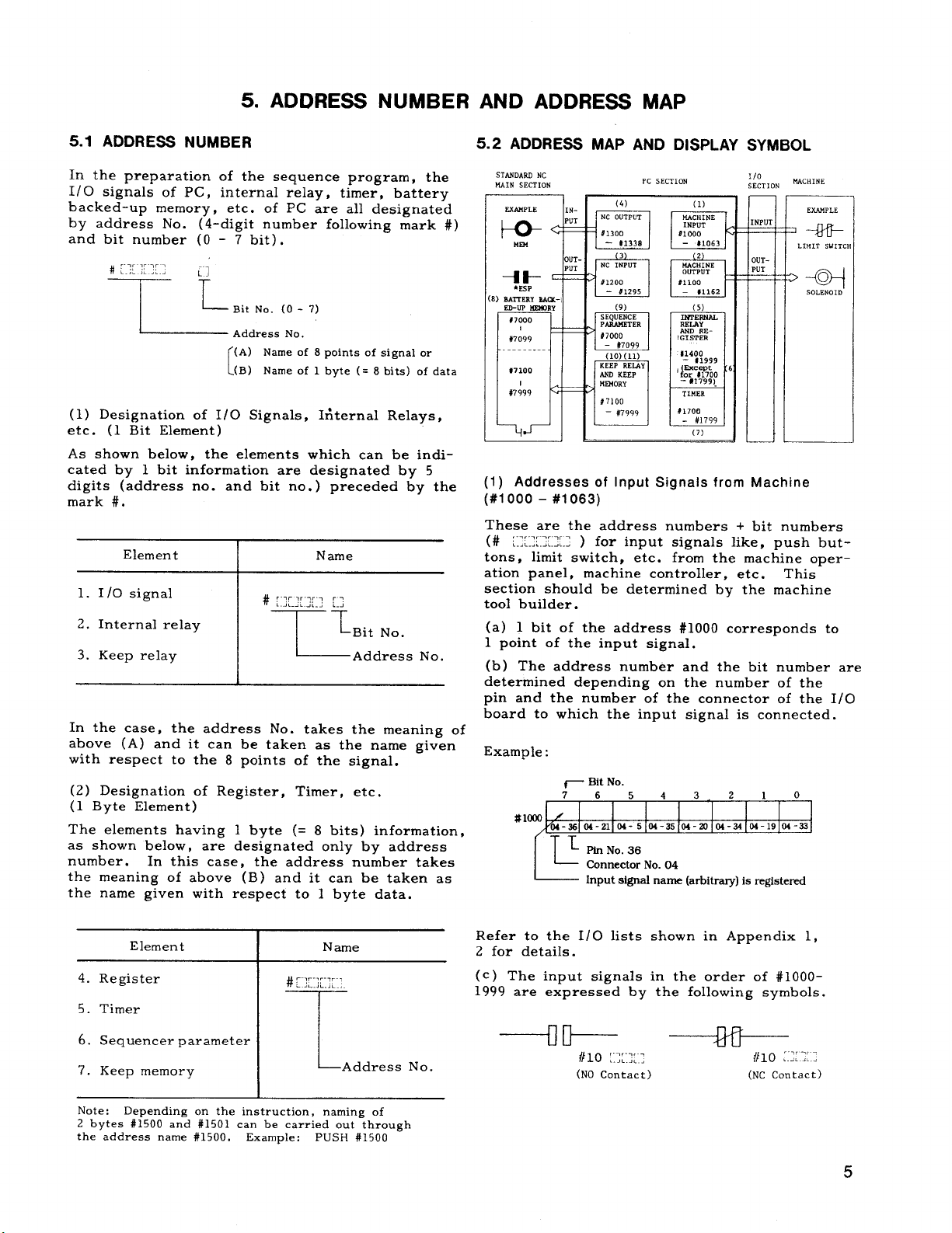

5. ADDRESS NUMBER AND ADDRESS MAP

5.1 ADDRESS NUMBER

In the preparation of the sequence program, the

1/0 signals of PC, internal relay, timer, battery

backed-up memory, etc. of PC are all designated

by address No. (4-digit number following mark #)

and bit number (O - 7 bit) .

I

~ Address No.

(1) Designation of 1/0 Signals, IfiternaI Relays,

etc. (1 Bit Element)

As shown below, the elements which can be indi-

cated by 1 bit information are designated by 5

digits (address no. and bit no. ) preceded by the

mark #.

Element

1. I/0 signal

2. Internal relay

3. Keep relay

In the case,

above (A) and it can be taken as the name given

with respect to the 8 points of the signal.

(2) Designation of Register, Timer, etc.

(1 Byte Element)

The elements having 1 byte (= 8 bits) information,

as shown below,

number.

In this case, the address number takes

the meaning of above (B) and it can be taken as

the name given with respect to 1 byte data.

-Bit No. (O - 7)

(A) Name of 8 points of signal or

(B) Name of 1 byte (= 8 bits) of data

[

,..,.,..,.;

L

Name

T

Bit No.

Address No.

I

# ,-..,,,,7 :;

the address No. takes the meaning of

are designated only by address

5.2 ADDRESS MAP AND DISPLAY SYMBOL

STANDARD Nc

MAIN SECTION

F+EEIm

+& ‘ ~

1) 8ATTE4YB/Lx-,

ED-UP ~RY

#7000

1

#7099

#7100

#7:99

e =

I

OUT-

,

~

>

>

~c ;;:”T

#lZoo

- #1295

(9)

SEQUENCE

PABAMETER

#7000

– #7099 -

(10)(11)

KEEP REMY

AND KEEP

MQIORY

#7100

– #7999

pc 5EcT10N

rl

!GISTER

,(Except

#1700

1

2

K4~:;E

#1100

– #1162

(5)

IfWE9NAL

RELAY

AND RE-

11400

– #1999

fOr#1700

- #1799[

TIMER

- #1799

(7)

1/0

SECTION

wu

—

—

UTUT

.

.

—

MACHINE

EXAMPLE

~+HF

LIMIT SWITC

‘w

SOLENOID

(1) Addresses of Input Signals from Machine

(#1000 - #1063) These are the address numbers + bit numbers

(# ,-.-.,7 ..,.

......... ...... ) for input signals like, push but-

tons, limit switch, etc. from the machine oper–

ation panel, machine controller, etc.

This

section should be determined by the machine

tool builder.

(a) 1 bit of the address #1000 corresponds to

1 point of the input signal.

(b) The address number and the bit number are

determined depending on the number of the

pin and the number of the connector of the 1/0

board to which the input signal is connected.

Example:

~ BitNo.

76543,21 0

# 1000

04-3SIQ4-21104-51M-35[M- miM-MIM-19]M-w

L PlnNo. 36

l-!

ConnectorNo.04

Inputslgmdname(arbitrary)is registenxl

Element

4. Register

I

Name

# ~,r-,,-,r,

. .L.,L.,L.,

5. Timer

T

6. Sequencer parameter

7. Keep memory

I

1

Depending on the instruction, naming of

Note:

2 bytes #1500 and #1501 can be carried out through

the address name #1500, Example:

I

~A&essNo,

PUSH #1500

Refer to the 1/0 lists shown in Appendix 1,

2 for details.

(c) The input signals in the order of #1000-

1999 are expressed by the following symbols.

5

Page 10

5.2 ADDRESS MAP AND DISPLAY SYMBOL

(Cent’d)

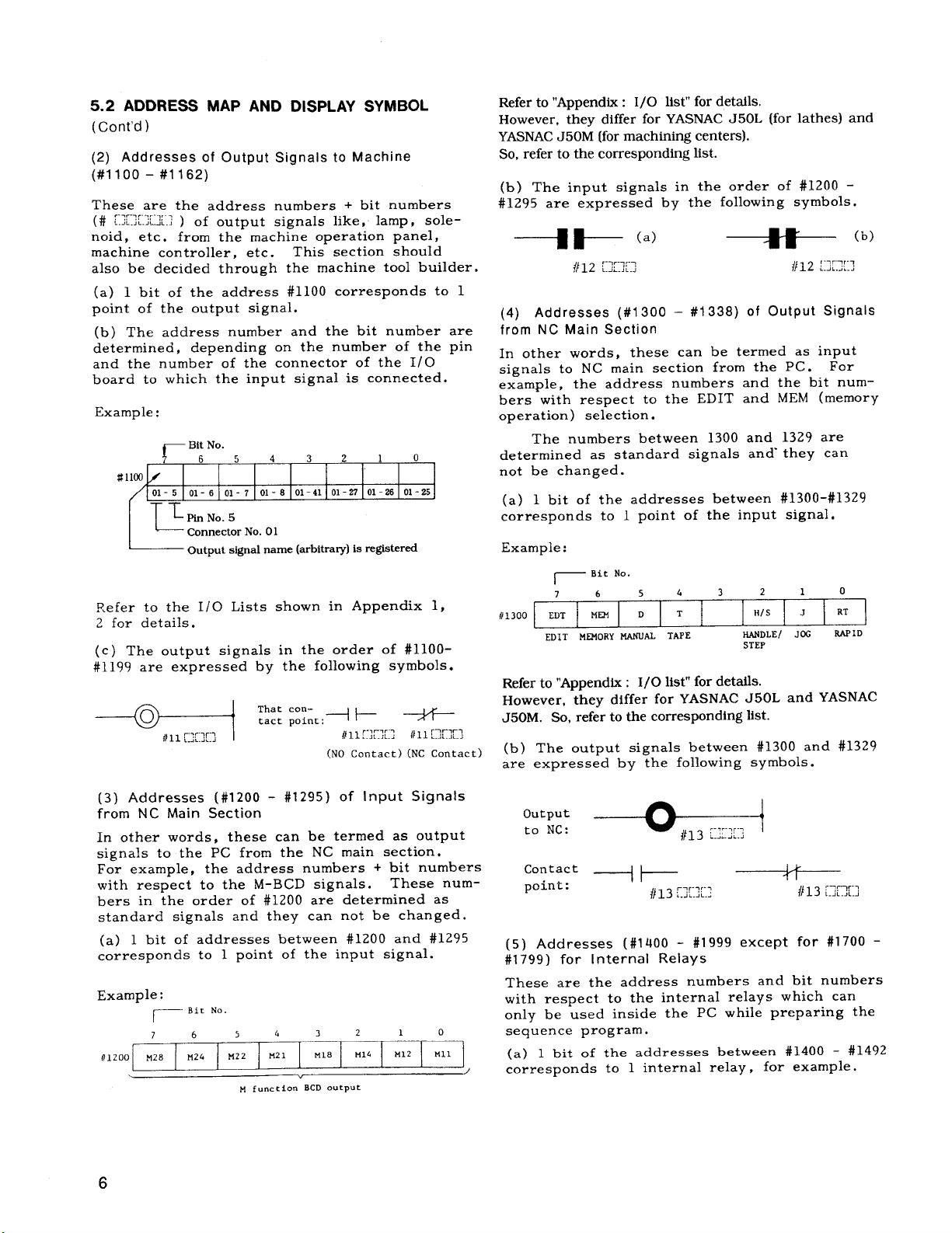

(2) Addresses of Output Signals to Machine

(#1100 - #1162)

These are the address numbers + bit numbers

(# rfi[~d[.~ ) of output signals like, lamp, solenoid, etc.

machine controller, etc.

from the machine operation panel,

This section should

also be decided through the machine tool builder,

(a) 1 bit of the address #1100 corresponds to 1

point of the output signal.

(b) The address number and the bit number are

determined, depending on the number of the pin

and the number of the connector of the 1/0

board to which the input signal is connected.

Example:

- BitNo.

?6543210

#llw

01-5101-6101-7101-8101-41 101-27101-26101-25

~PinNo.s

ConnectorNo.01

Lk

Outputsignalname(arbitrary)is registered

Refer to the I /O Lists shown in Appendix 1,

2 for details.

(c) The output signals in the order of #1100 #1199 are expressed by the following symbols.

Refer to “Appendix: 1/0 list” for details.

However, they differ for YASNAC J50L (for lathes) and

YASNAC J50M (for machining centers).

So, refer to the corresponding list.

(b) The input signals in the order of #1200 #1295 are expressed by the following symbols.

_’+ fl— (a)

(4) Addresses (#1300 - #1338) of Output Signals

from NC Main Section

In other words, these can be termed as input

signals to NC main section from the PC.

For

example, the address numbers and the bit numbers with respect to the EDIT and MEM (memory

oPeration) Selection.

The numbers between 1300 and 1329 are

determined as standard signals and they can

not be changed.

(a) 1 bit of the addresses between #1300 -#1329

corresponds to 1 point of the input signal.

Example:

~ Bit No.

2 1

H/S J

RANDLE/ JOC

STEP

#1300

6 5

7

EDT MEM

ME210RYMANUAL TAPE

EDIT

4 3

T

D

Refer to “Appendix : 1/0 list” for details.

However, they differ for YASNAC J50L and YASNAC

J50M. So, refer to the corresponding list.

0

RT

RAPID

(3) Addresses (#1200 - #1295) of Input Signals

from NC Main Section

ln other words, these can be termed as output

signals to the PC from the NC main section.

For example, the address numbers + bit numbers

with respect to the M-BCD signals.

These num-

bers in the order of #1200 are determined as

standard signals and they can not be changed.

(a) 1 bit of addresses between #1200 and #1295

corresponds to 1 point of the input signal.

Example:

Bit No.

#lZoo

7

M28

6

M24

4 3

5

M21

U22

v

functionBCD output

M

M18

2 1 0

)412 Ml 1

M14

I

6

(b) The output signals between #1300 and #1329

are expressed by the following symbols.

(5) Addresses (#1400 - #1999 except for #1700 -

#1799) for Internal Relays

These are the address numbers and bit numbers

with respect to the internal relays which can

only be used inside the PC while preparing the

sequence program.

1/

(a) 1 bit of the addresses between #1400 - $1492

corresponds to 1

internal relay, for example.

Page 11

1/0 list example:

(c) In a register,

.

pression symbol.

examples of the symbols.

the address itself is the ex-

The following shows two

“l400-

(b) The number of usable internal relays are as

follows .

500 bytes

(c) The internal relay and its contact

expressed by the following symbol.

There is no limit for NO and NC contact Doints

until the program memory capacity is exceeded.

(d) Adressed used in register cannot be used as

internal relay.

(6] Addresses (#1400 - #1999 except for

#1700 - #1799) of Register

These are the address numbers with respect to

the 1 byte (= 8 bits) register for general

purpose use.

. .

register instruction or for the working addresses

of macro instructions.

(a) 1 address number

of 1 byte.

1/0 list example:

//1500

#1501

~ Write the internal relay

name (arbitrary)

x 8 bits = 4000 relays

point are

These registers are used for

corresponds to 1 register

4

Insert the name (arbitrary)

of the register

t-+l?l

b

(d) Addresses used in internal relay cannot be

used as register.

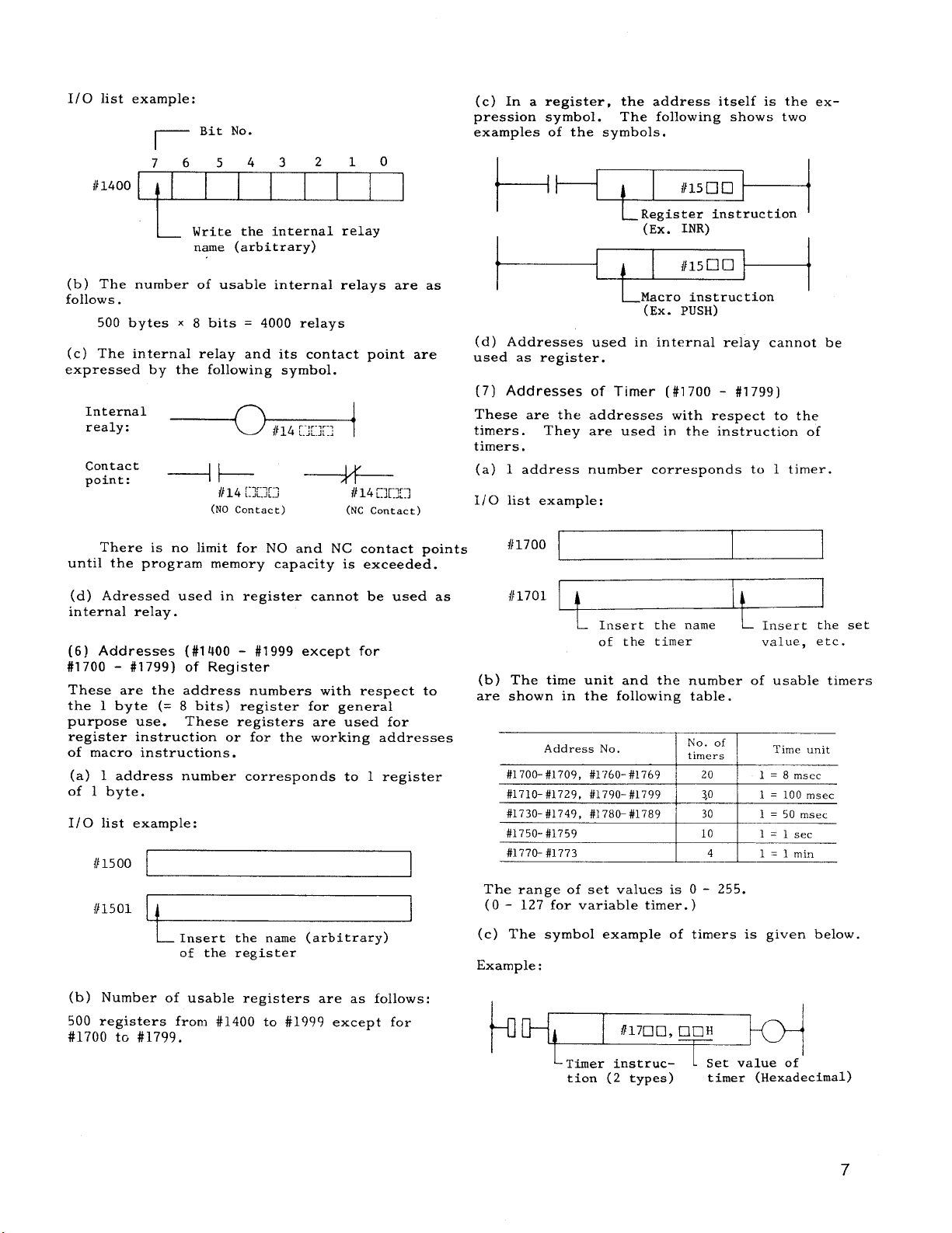

(7) Addresses of Timer (#1700 - #1799)

These are the addresses with respect to the

timers. They are used in the instruction of

timers.

(a) 1 address number corresponds to 1 timer,

1/0 list example:

#1700

//1701

(b) The time unit and the number of usable timers

are shown in the following table.

Address No.

#1700-#1709, #1’760-#1769

#1710-#1729, #1790-#1799

#1730-#1749, #1780-#1789

#1750-#1759

#1770-#1773

The range of set values is O- 255.

(O- 127 for variable timer.)

(c) The symbol example of timers is given below.

Example:

[fl

!

Insert the name Insert the set

of the timer

#15cJn

#15ncl

No. of

timers

I

!

I

20

3,0

30

10

4

<i

,t

J

value, etc.

Time unit

1 = 8 msec

1 = 100msec

1 = 50

msec

l=lsec

l=lmin

(b) Number of usable registers are as follows:

500 registers from #1400 to #1999 except for

#1700 tG #1799.

l-w1

LTimer instr~c- L set value of

tion (2 types)

#17Kln,DnH

I

timer (Hexadecimal)

7

Page 12

5.2 ADDRESS MAP AND DISPLAY SYMBOL

(Cent’d)

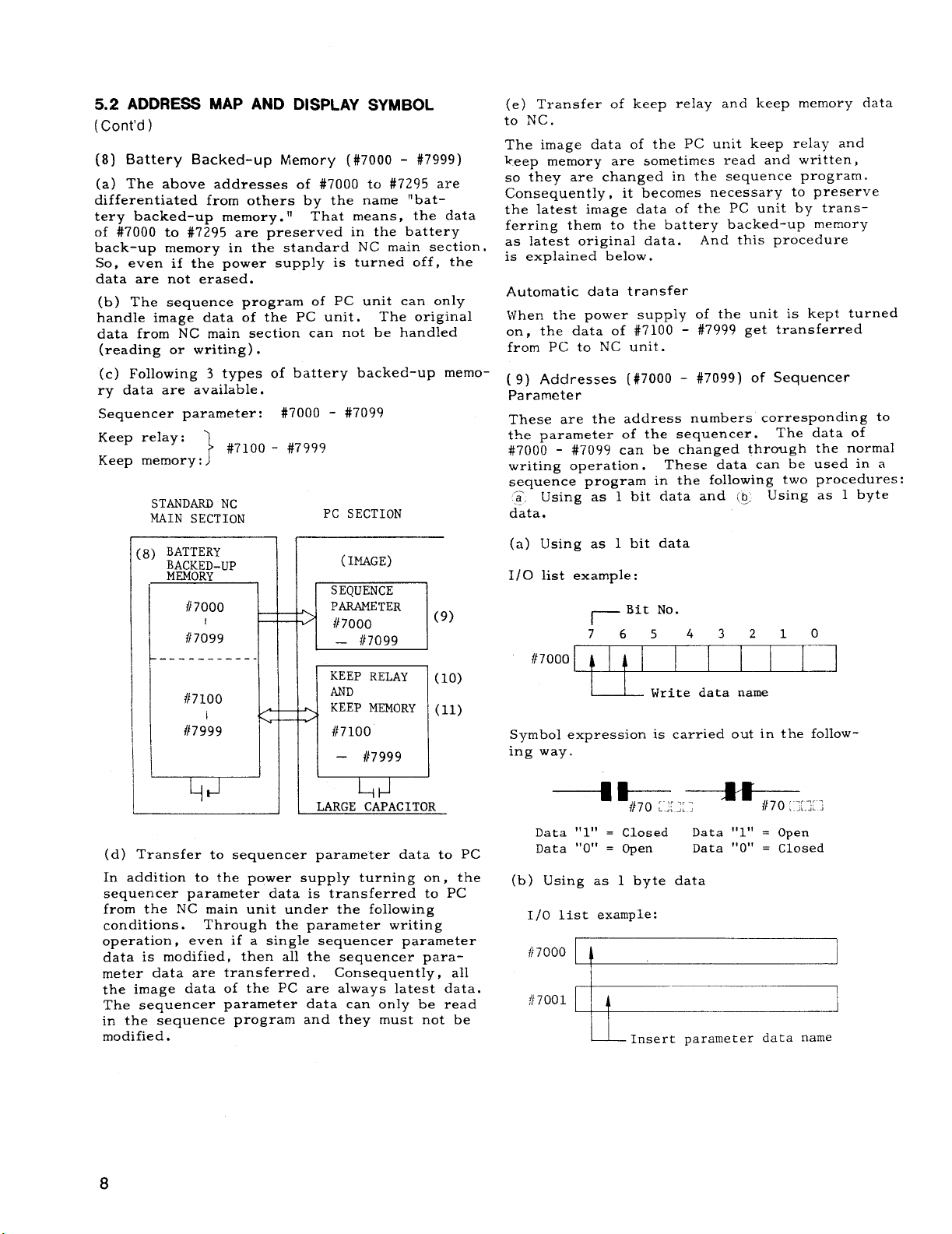

(8) Battery Backed-up Memory (#7OOO - #7999)

(a) The above addresses of #7ooO to #7295 are

differentiated from others by the name “bat-

tery backed-up memory. ”

of #7000 to #7295 are preserved in the battery

back-up memory in the standard NC main section.

So, even if the power supply is turned off, the

data are not erased.

(b) The sequence program of PC unit can only

handle image data of the PC unit.

data from NC main section can not be handled

(reading or writing).

(c) Following 3 types of battery backed-up memo-

ry data are available.

Sequencer parameter: #7000 - #7099

Keep relay:

Keep memory:J

STANDARD NC

MAIN SECTION

) BATTERY

BACKED-UP

MEMORY

I F

+-----------1

L

#7100- #7999

1

{/7000

#7;99

1

I

That means, the data

The original

PC SECTION

F

SEQUENCE

PARAMETER

#7000

P

&

KEEPMEMORY

#7100

H

(9)

(lo)

(11)

I-J

(e) Transfer of keep relay and keep memory data

to NC.

The image data of the PC unit keep relay and

keep memory are sometimes read and written,

so they are changed in the sequence program.

Consequently, it becomes necessary to preserve

the latest image data of the PC unit by transferring them to the battery backed-up memory

as latest original data.

is explained below.

Automatic data transfer

When the power supply

on, the data of #7100 from PC to NC unit.

(9) Addresses (#7000 -

Parameter

These are the address numbers corresponding to

the parameter of the sequencer.

#7000 - #7099 can be changed through the normal

writing operation.

sequence program

a~ Using as 1 bit

data.

(a) Using as 1 bit

1/0 list example:

r ‘it

76543210

#7000

Symbol expression is carried out in the follow-

ing way.

dtl

~ Write data name

And this procedure

of the unit is kept turned

#7999 get transferred

#7099) of Sequencer

The data of

These data can be used in a

in the following two procedures:

data and (~,

data

No.

Using as 1 byte

I

(d) Transfer to sequencer parameter data to PC

In addition to the power supply turning on, the

sequencer parameter data is transferred to PC

from the NC main unit under the following

conditions. Through the parameter writing

operation, even if a single sequencer parameter

data is modified, then all the sequencer parameter data are transferred.

the image data of the pC are always latest data.

The sequencer parameter data can only be read

in the sequence program and they must not be

modified.

8

Consequently, all

Data “l” = Closed

Data “O” = Open

(b) Using as 1 byte data

1/0 list example:

/7000

1A

UI~sert parameter data name

Data “l” =

Data “O” = Closed

Open

Page 13

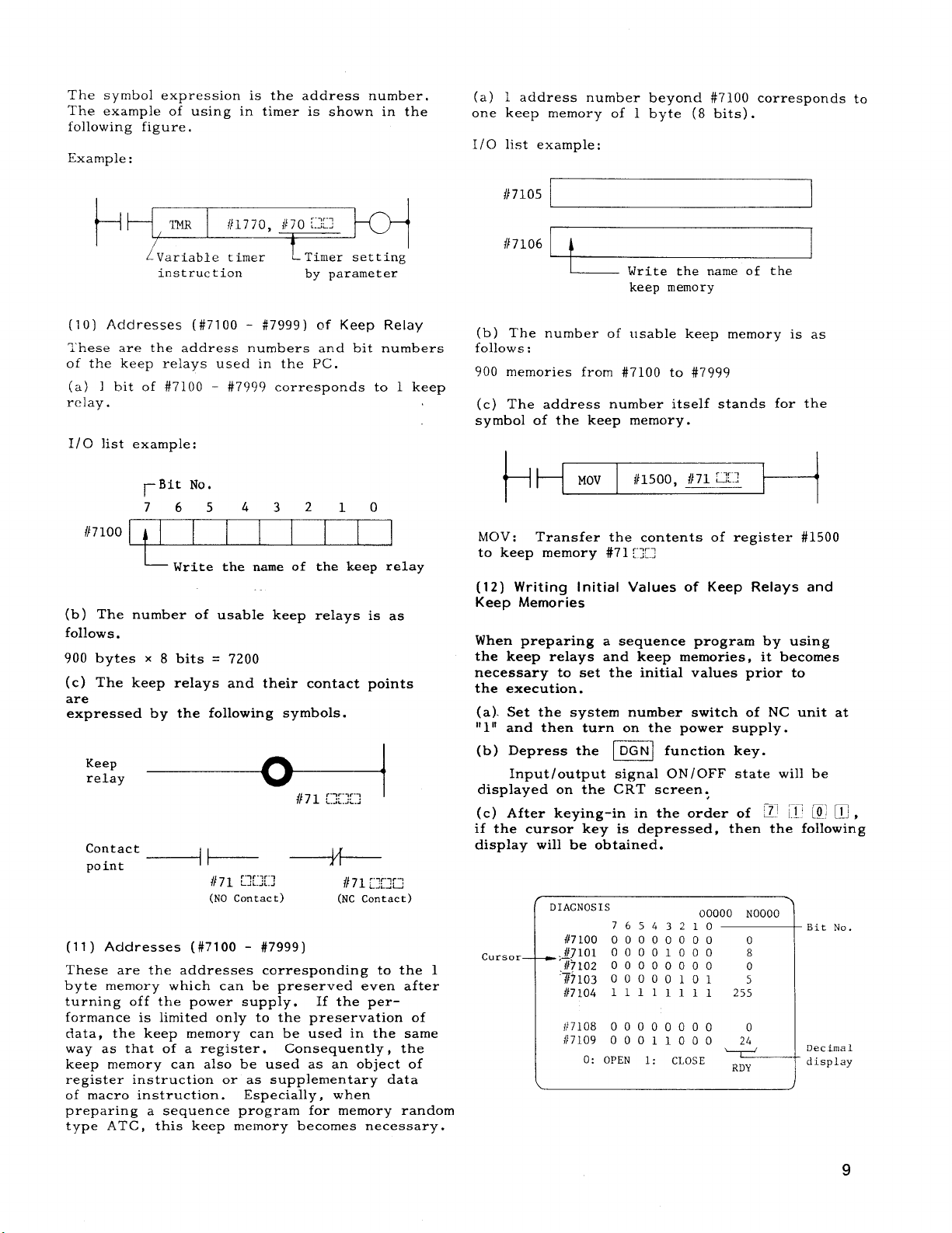

The symbol expression is the address number.

The example of using in timer is shown in the

following figure,

Example:

l177il, #70 ::7::

t+y~

Variable timer

instruct ion

Timer setting

by parameter

‘

I address number beyond #7100 corresponds to

(a)

one

keep memory of 1 byte (8 bits).

list example:

1/0

//71061 ~

~Write the name of the

keep memory

I

(10) Addresses (#7100 - #7999) of Keep Relay

These are the address numbers and bit numbers

of the keep relays used in the PC.

(a) I bit of #7100 - #7999 corresponds to 1 keep

relay.

1/0 list example:

➤Bit No.

7654321 0

“7100P==@===

‘Write the name of the keep relay

(b) The number of usable keep relays

follows .

900 bytes

(c) The keep relays and their contact

are

expressed by the following symbols.

x 8 bits = 7200

a’ ————0—+

is as

points

(b)

The number of usable kee~ memorv is as

follows :

900 memories from #7100 to #7999

(c) The address number itself stands for the

symbol of the keep memory.

MOV

l+ I‘1 ‘

MOV :

to keep memory #71zK~

(12) Writing Initial Values of Keep Relays and

Keep Memories

When preparing a sequence program by using

the keep relays and keep memories, it becomes

necessary to set the initial values prior to

the execution.

(a). Set the system number switch of NC unit at

11111and then turn on the power supPIY.

(b) Depress the [=1 function key.

displayed on the CRT screen:

(c) After keying-in in the order of ~~ [1 ‘@ ~,

if the cursor key is depressed, then the following

display will be o-btaine~.

Transfer the contents of register #1500

Input/output signal ON/OFF state will be

#1500, #713::

‘

(NO Contact)

(11) Addresses (#7100 - #7999)

These are the addresses corresponding to the 1

byte memory which can be preserved even after

turning off the power supply.

formance is limited only to the preservation of

data, the keep memory can be used in the same

way as that of a register, Consequently, the

keep memory can also be used as an object of

register instruction or as supplementary data

of macro instruction.

preparing a sequence program for memory random

type ATC, this keep meinory becomes necessary.

Especially, when

(NC Contact)

If the per-

Cursor

DIAGNOSIS

OPEN 1:

O:

76543210

#710000000000 o

I

;//710100001000 8

7710200000000 0

‘77103 OOOOO1O1 5

t

#710411111111

/710800000000 o

#710900011000

00000 NOOOO

255

CLOSE +2____

RDY

- Bit No.

Decimal

- display

9

Page 14

5.2 ADDRESS MAP AND DISPLAY SYMBOL

(Cent’d)

(d) Adjust addresses #7105 to #7294 for initial

condition setting by depressing the cursor.

(e) If the -] (insert) key is depressed,

the cursor will move in the right hand direction,

and will move to the 7th bit position of the

address.

(f) Keep on pressing the cursor key until it

becomes adjusted to the position of the decimal

display.

(g) Key-in the desired values (O - 255) for set-

ting initial condition and then depress the

key. The decimal display will get changed to

the presently keyed in value.

(h) If the

_ key is depressed, the cursor

will move to the left hand position #.

the setting of one address number is completed.

(i) Repeat steps (d) to (h) to write all the

desired initial values of the address numbers,

(j) Adjust the system number switch to “O. “

m

Thereby,

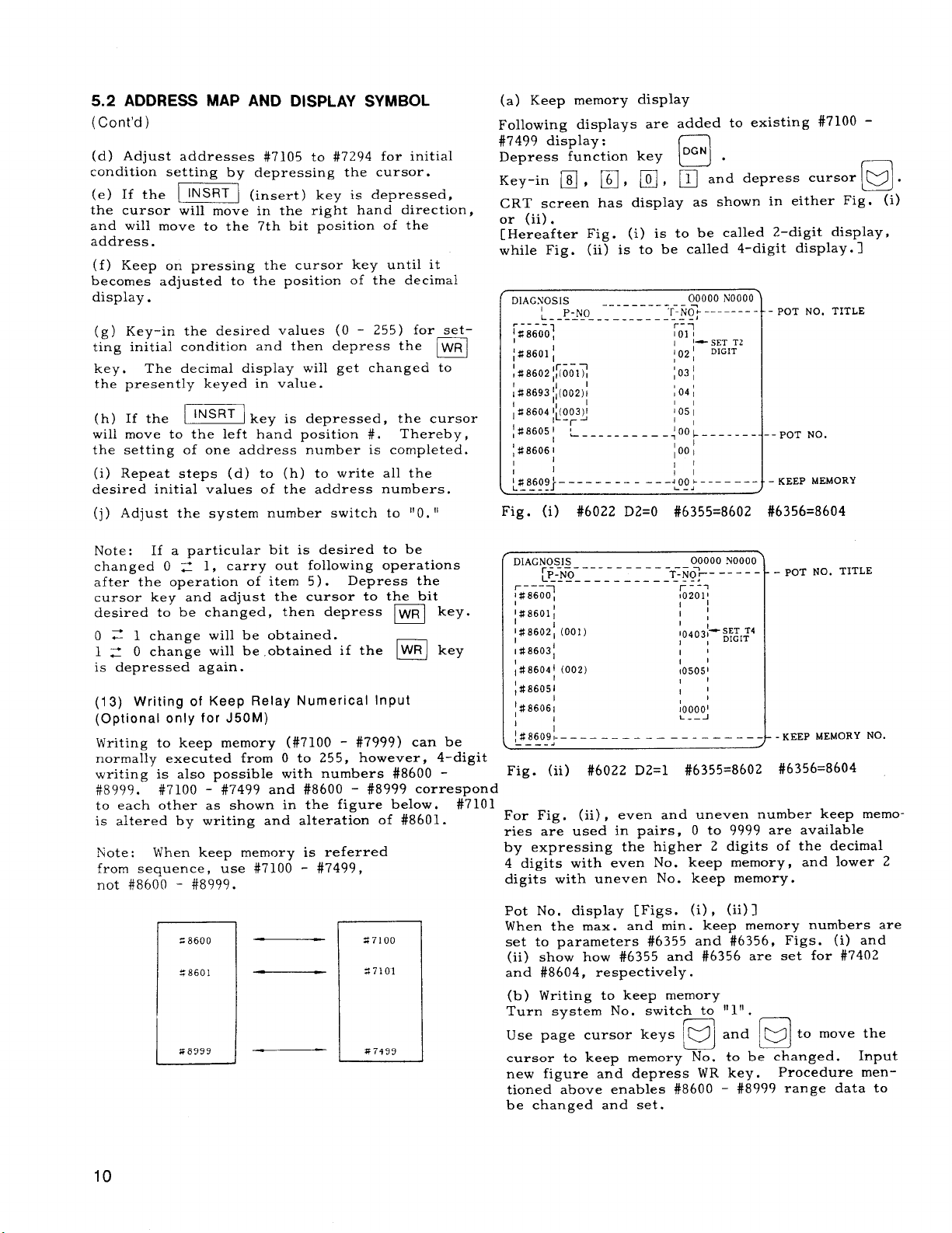

(a) Keep memory display

Following displays are added to existing #7100 #7499 display:

Depress function key

Key-in ❑ , ❑ , ❑ , ❑ and depress cursor ~ .

12GN

G

.

L-l

CRT screen has display as shown in either Fig. (i)

or (ii) .

[Hereafter Fig. (i) is to be called 2-digit display,

while Fig. (ii) is to be called 4-digit display. ]

DIAGNOSIS ._-_____= ._~OOOO ‘0000

‘L--~:N-O____-_____!-??: ‘--–---”

.--_:#8600:

:#8601:

1

;r--l

,#860211(001)1

h8693j(O02)~

;#86041fiO03)~ :05;

I -~-J 1

;#86051 ‘ loo;_______

;#8606 ;

1

I

L------- -—-1

I

r-l

1o11

1

!02:

;03;

,04;

la SET T~

DIGIT

Fig. (i) #6022 D2=0 #6355=8602

- POT NO, TITLE

.-POT NO.

- KEEP MEMORY

#6356=8604

Note:

If a particular bit is desired to be

changed O Z 1, carry out following operations

after the operation of item 5) .

Depress the

cursor key and adjust the cursor to the bit

desired to be changed, then depress ~ key.

0=

1 change will be obtained.

1:

0 change will be obtained if the ~ key

is depressed again.

(13) Writing of Keep Relay Numerical Input

(Optional only for J50M)

Writing to keep memory (#7100 - #7999)

can be

normallv executed from O to 255, however, 4-digit

writing’ is also possible with numbers #860”0 - -

#8999.

to each other as shown in the figure below.

#7100 - #7499 and #8600 - #8999 correspond

#7101

is altered by writing and alteration of #8601.

I’iote: When keep memory is referred

from sequence, use #7100 - #7499,

not #8600 – #8999.

Z8600

*71OO

I

$8601

37101

I

I

aa999

L

:

IT7499

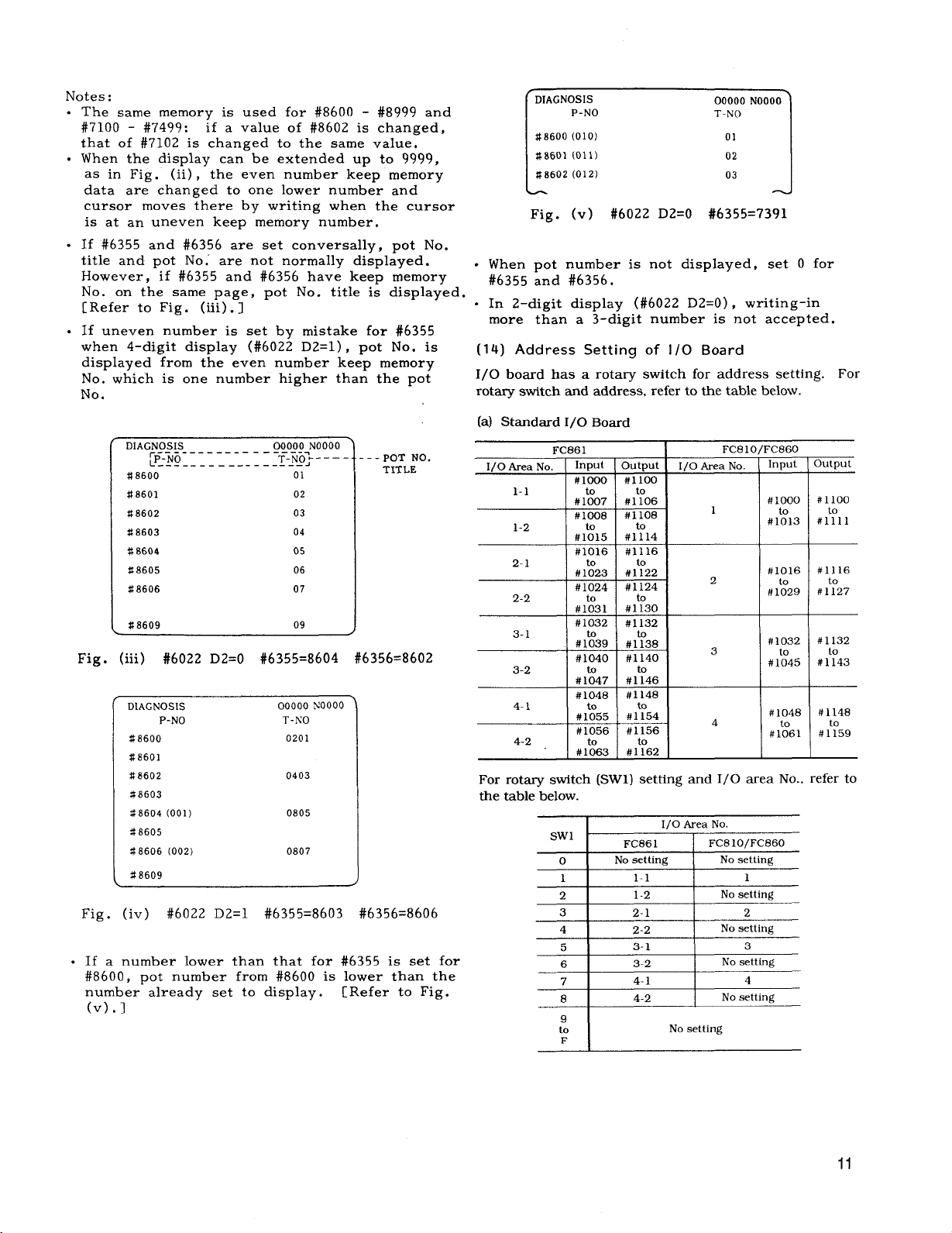

DIAGNOSIS

[:-:N]::__ _ ___ __T_-w.r - ‘- ‘- - -

----l#8600[

[#86011

1#8602~(001)

I#8603;

;#8604; (002)

j#86051

:#8606;

I

----- --- .-— ~

I

ltiNio91_____ –______ __ –--.___!-.

Fig. (ii) #6022 D2=1 #6355=8602

00000 NOooo

----

,,

!02011

I

II

I

,0403+SET T4

DIGIT

!,

t

I

II

105051

II

1;

,

100001

L-—J

POT NO. TITLE

-KEEP MEMORY NO.

#6356=8604

For Fig. (ii) , even and uneven number keep memories are used in pairs, O

to 9999 are available

by expressing the higher 2 digits of the decimal

4 digits with even No. keep memory, and lower 2

digits with uneven No. keep memory.

Pot No, display [Figs. (i) , (ii)]

When the max. and min.

set to parameters

#6355 and #6356, Figs. (i) and

keep memory numbers are

(ii) show how #6355 and #6356 are set for #7402

#8604, respectively.

and

(b) Writing to keep memory

Turn system No. switch to “ 1“ .

Use page cursor keys ~ and ~ to move the

cursor to keep memory No. to be changed. Input

new figure and depress WR key.

on

Procedure mentioned above enables #8600 - #8999 range data to

be changed and set.

10

Page 15

Notes:

.

The same memory is used for #8600 - #8999 and

#7100 - #7499: if a value of #8602 is changed,

that of #7102 is changed to the same value.

.

When the display can be extended up to 9999,

as in Fig. (ii), the even number keep memory

data are changed to one lower number and

cursor moves there by writing when the cursor

is at an uneven keep memory number.

.

If #6355 and #6356 are set conversally, pot No.

title and pot No.’ are not normally displayed.

However, if #6355 and #6356 have keep memory

No. on the same page, pot No. title is displayed,

[Refer to Fig. (iii).]

.

If uneven number is set by mistake for #6355

when 4-digit display (#6022 D2=1), pot No. is

displayed from the even number keep memory

No. which is one number higher than the pot

No.

DIAGNOSIS 00000 NOOOO

@~::____-____ T-_ N@+---

#8600

#8601

#8602

#8603

# 8604

#8605

#8606

#8609

Fig

. (iii) #6022 D2=0 #6355=8604 #6356=8602

-. ---— ------ .

01

02

03

04

05

06

07

09

-.

POT NO.

TITLE

r DIAGNOSIS

P-NO

?$8600(010)

?48601(011)

#8602 (012)

L

Fig.

(V) #6022 D2=0 #6355=7391

. When pot

#6355 and

● In 2-digit display (#6022 D2=O), writing-in

number is not displayed, set O for

#6356.

00000NOOOO

T-No

01

02

03

4

1

more than a 3-digit number is not accepted.

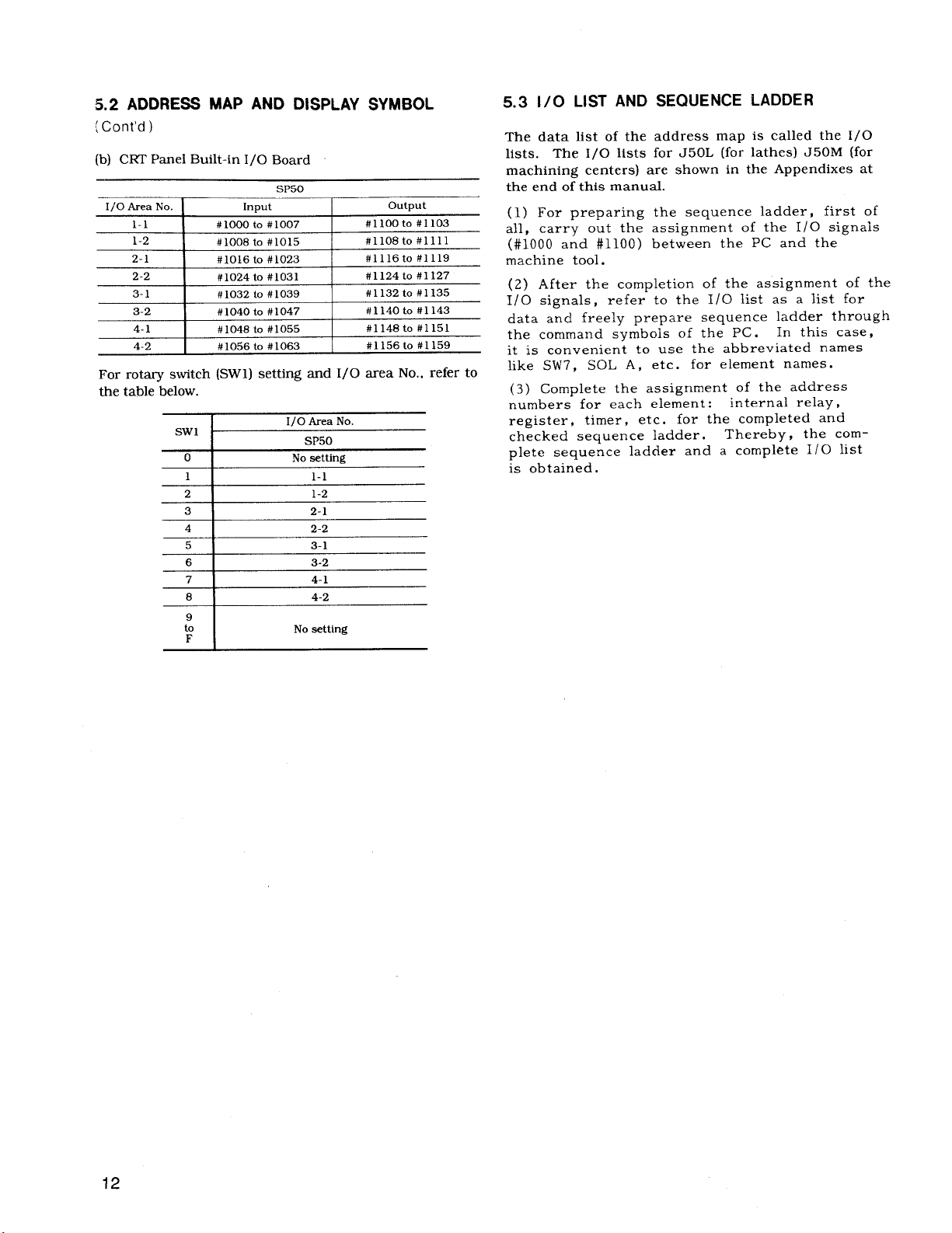

(14) Address Setting of 1/0 Board

1/0 board has a rotary switch for address setting. For

rotary switch and address, refer to the table below.

(a) Standard 1/0 Board

‘C660

FC810

1/0AreaNo.

1

2

Input

#1000

#1813

#1016

to

#1029

#1032

#1:45

3utput

#lloo

to

#1111

#1116

to

#1127

#1132

to

#1143

1/0

AreaNo.

1-1

1-2

2-1

2-2

FC861

Input

#1000 #lloo

to

#

1007 #1106

$1008

to

#lo15

#1016 #1116

to

#

1023 #1122

#1024

to

#lo31

#1032

output

to

#1108

to

#1114

to

#1124

to

#l130

#1132

DIAGNOSIS

P-NO

#8600

#8601

#8602

#8603

#8604 (001)

#8605

#8606 (002)

#8609

00000Noooo

T-NO

0201

0403

0805

0807

Fig. (iv) #6022 D2=1 #6355=8603 #6356=8606

.

If a number lower than that for #6355 is set for

#8600, pot number from #8600 is lower than the

number already set to display. [Refer to Fig.

(v). ]

#1046

#1061

#1148

to

to

#1159

For rotary switch (SW1) setting and 1/0 area No., refer to

the table below.

Swl

o

I

1

2

3

4

I

5

—

I

6 3-2

7

8

Q

:0

F

I

1/0Area No.

FC861

Nosetting

1-1

1-2

2-1 2

2-2

3-1

4-1

4-2

No setting

FC8lo/Fc860

Nosetting

1

setting

No

setting

No

3

No setting

4

No setting

11

Page 16

5.2 ADDRESS MAP AND DISPLAY SYMBOL

~Cont’d)

(b) CRT Panel Buik-in I/O Board

SP50

Area No.

1/0

1-1 #looo to #loo7

1-2

2-1

2-2

3-1

3-2

4-1

4-2

I

,

I

InDut

#1008 to #1015

#1016 to #1023

#1024to #1031

#1032 to #1039

#lo40 to #lo47

#1048 to #1055

#1056to #1063

For rotary switch (SW1) setting and 1/0 area No., refer to

the table below.

31 2-1

4

5

6

2-2

3-1

3-2

output

#lloot0#llo3

#l108to#llll

#ll16to#ll19

#l124t0#l127

#l132t0#l135

#l140t0#l143

#l148to#l151

#l156to#l159

5.3 I/0 LIST AND SEQUENCE LADDER

The data list of the address map is called the 1/0

The 1/0 lists for J50L (for lathes) J50M (for

lists.

machining centers) are shown in the Appendixes at

the end of this manual.

(1) For preparing the sequence ladder, first of

all, carry out the assignment

(#1000 and #1100) between the PC and the

machine tool.

(2) After the completion of the assignment of the

1/0 signals, refer to the 1/0 list as a list for

data and freely prepare sequence ladder through

the command symbols of the PC.

it is convenient to use the abbreviated names

like SW7, SOL A, etc. for element names.

complete the assignment of the address

(3)

numbers for each element:

register,

checked sequence ladder.

plete sequence ladder and a complete

timer, etc. for the completed and

;S obtained.

of the 1/0 signals

In this case,

internal relay,

Thereby, the com-

1/0 list

12

Page 17

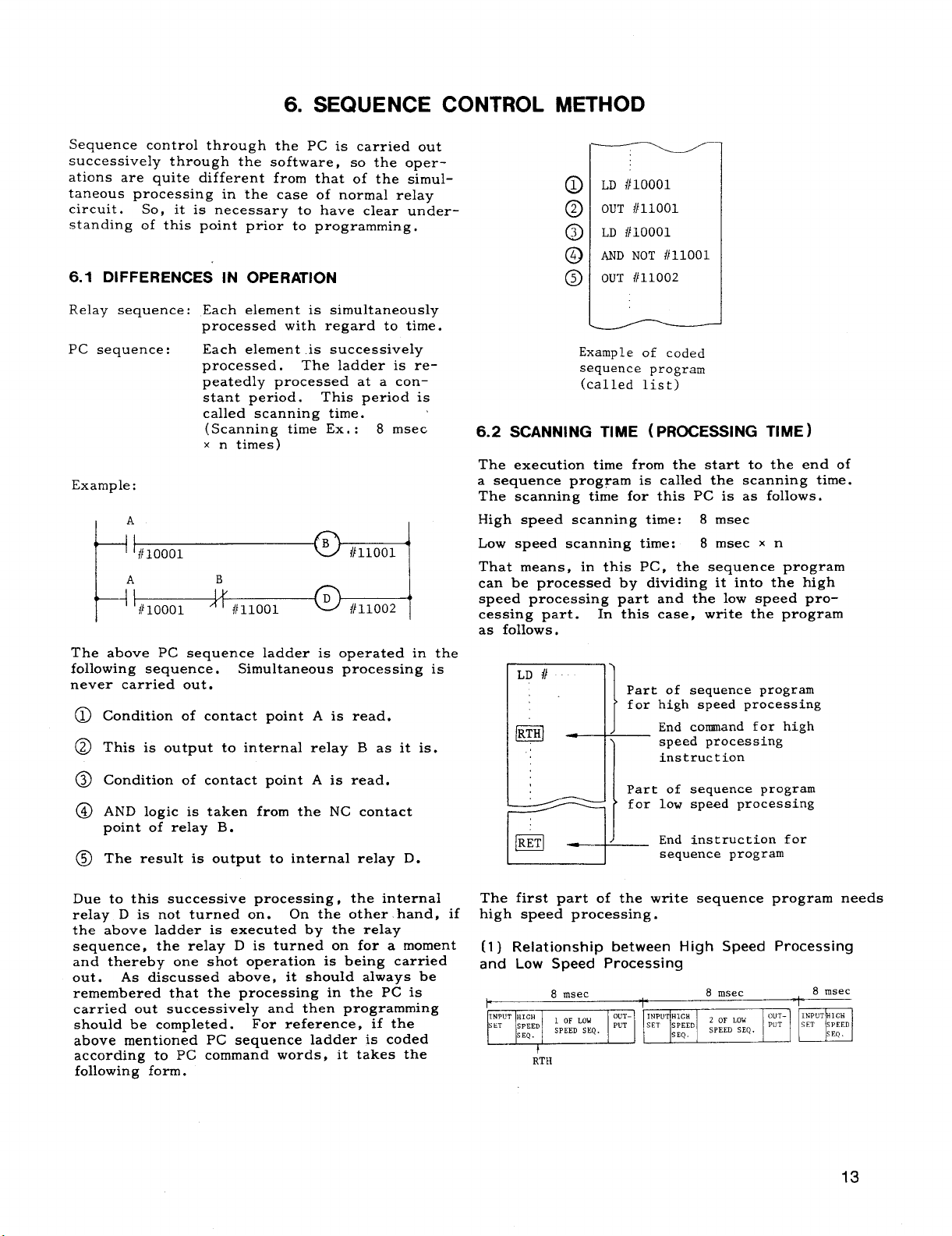

6. SEQUENCE CONTROL

Sequence control through the PC is carried out

successively through the software, so the operations are quite different from that of the simultaneous processing in the case of normal relay

circuit.

standing of this point prior to programming.

6.1

Relay sequence: Each element is simultaneously

PC sequence: Each element is successively

Example:

r:: ~

The above PC sequence ladder is operated in the

following sequence. Simultaneous processing is

never carried out.

So, it is necessary to have clear under-

DIFFERENCES IN OPERATION

processed with regard to time.

processed. The ladder is repeatedly processed at a con-

stant period.

called scanning time.

(Scanning time Ex, : 8 msec

X n times)

A

//10001

B

$

/}10001 /}11001

Condition of contact point A is read.

This is output to internal relay B as it is.

Condition of contact point A is read.

AND logic is taken from the NC contact

point of relay B.

The result is output to internal relay D.

This period is

B

#llool

D

#lloo2

LD //10001

OUT I11OO1

LD #10001

AND NOT #11001

OUT #11002

Example of coded

sequence program

(called list)

6.2 SCANNING TIME (PR~EssING TIME)

The execution time from the start to the end of

a sequence program is called the scanning time.

The scanning time for this PC is as follows.

High speed scanning time: 8 msec

Low speed scanning time: 8 msec

That means, in this PC, the sequence program

can be processed by dividing it into the high

speed processing part and the low speed processing part.

as follows.

71

@

:-IT

+!

In this case, write the program

Part of sequence program

for high speed processing

j Endcomnand forhigh

speed processing

instruct ion

Part of sequence program

for low speed processing

End instruction for

x n

E-.II#-‘equence program

Due to this successive processing, the internal

relay D is not turned on.

the above ladder is executed by the relay

sequence, the relay D is turned on for a moment

and thereby one shot operation is being carried

out .

remembered that the processing in the PC is

carried out successively and then programming

should be completed.

above mentioned PC sequence ladder is coded

according to PC command words, it takes the

As discussed above, it should always be

following form.

On the other hand, if

For reference, if the

The first part of the write sequence program needs

high speed processing. “ - -

(1) Relationship between High Speed Processing

and Low Speed Processing

i-

m~=

RTH

8 msec

1-

8 msec

1-

8 msec

13

Page 18

6.2 SCANNING TIME (PROCESSING TIME) (Cent’d)

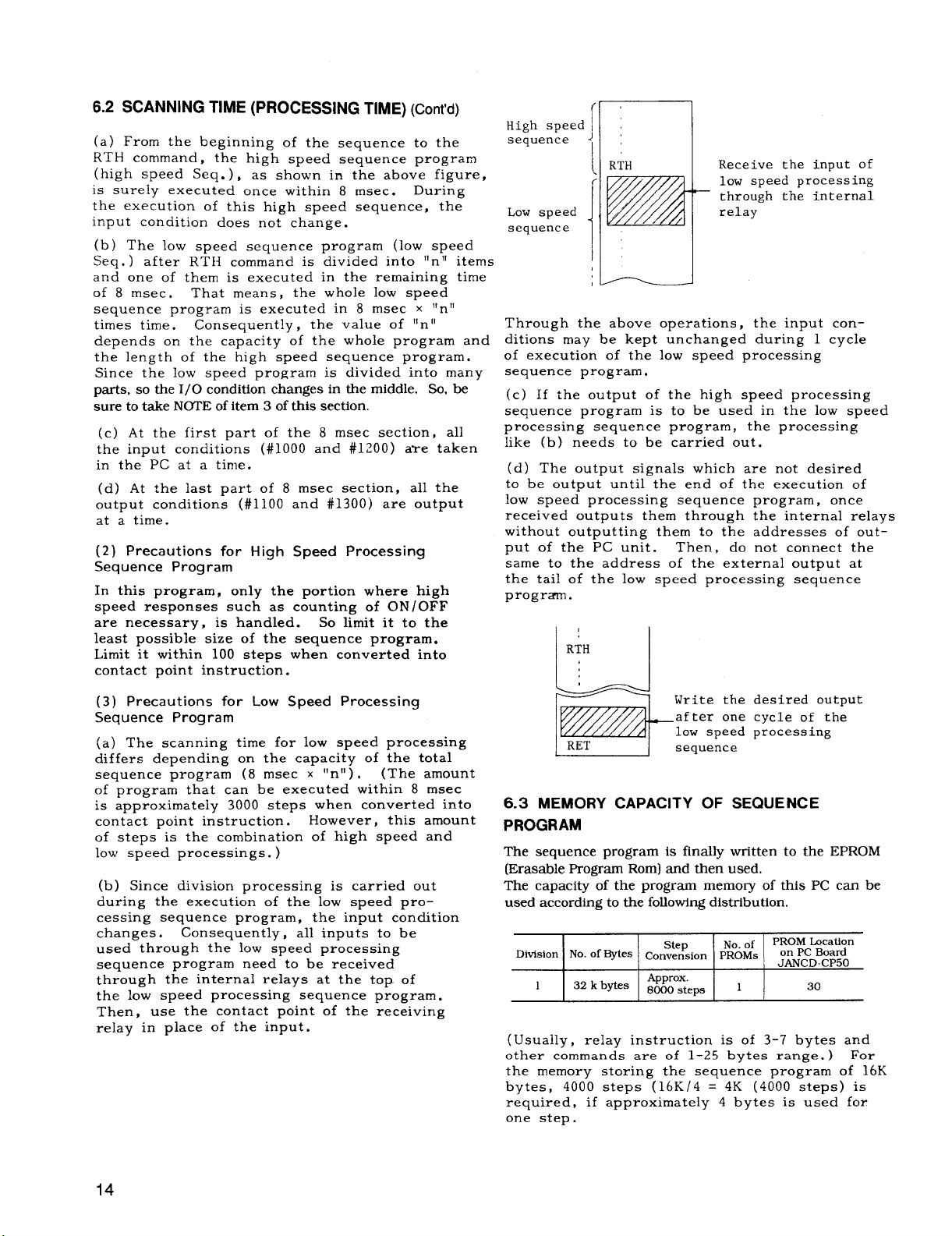

(a) From the beginning of the sequence to the

RTH command,

(high speed Seq.),

is surely executed once within 8 msec.

the execution of this high speed sequence, the

input condition does not change.

(b) The low speed sequence program (low speed

Sea.) after RTH command is divided into “n” items

and one of them is executed in the remaining time

of 8 msec.

sequence program is executed in 8 msec

times time. Consequently, the value of “n”

depends on the capacity of the whole program and

the length of the high speed sequence program.

Since the low speed program is divided into many

parts,sotheI/Oconditionchanges in the middle. So,be

sure totake NOTE ofitem3 ofthis section.

(c) At the first part of the 8 msec section, all

the input conditions (#1000 and #1200) aye taken

in the PC at a time.

(d) At the last part of 8 msec section, all the

output conditions (#1100 and #1300) are output

at a time.

(2) Precautions for High Speed Processing

Sequence Program

In this program, only the portion where high

speed responses such as counting of ON/OFF

are necessary, is handled. So limit it to the

least possible size of the sequence program.

Limit it within 100 steps when converted into

contact point instruction.

the high

That means, the whole low speed

speed sequence program

as shown in the above figure,

During

x “n”

High speed

sequence

RTH

Low speed

sequence

Through the above operations, the input conditions-may be kept ;nchanged during 1 cycle

of execution of the low speed processing

sequence program,

(c) If the output of the high speed processing

sequence program is to be used in the low speed

processing sequence program, the processing

like (b) needs to be carried out.

(d) The output signals which are not desired

to be output until the end of the execution of

low speed processing sequence program, once

received outputs them through the internal relays

without outputting them to the addresses of output of the PC unit.

same to the address of the external output at

the tail of the low speed processing sequence

program.

RTH

1’

I

Receive the input of

low speed processing

– through the internal

relay

Then, do not connect the

(3) Precautions for Low Speed Processing

Sequence Program

(a) The scanning time for low speed processing

differs depending on the capacity of the total

sequence program (8 msec

of program that can be executed within 8 msec

is approximately 3000 steps when converted into

contact point instruction.

of steps is the combination of high speed and

low speed processing. )

(b) Since division processing is carried out

during the execution of the low speed processing sequence program, the input condition

changes.

used through the low speed processing

sequence program need to be received

through the internal relays at the top of

the low speed processing sequence program.

Then, use the contact point of the receiving

relay in place of the input.

Consequently, all inputs to be

x “n”).

However, this amount

(The amount

Write the desired output

after one cycle of the

low speed processing

sequence

6.3 MEMORY CAPACITY OF SEQUENCE

PROGRAM

The sequence program is finally written to the EPROM

(Erasable Program Rem) and then used.

The capacity of the program memory of this PC can be

used according to the following distribution.

Division No. of Bytes c~nven~i~n pROMS

1 32 kbytes

(Usually, relay instruction is of 3-7 bytes and

other commands are of 1-25 bytes range. ) For

the memory storing the sequence program of 16K

bytes, 4000 steps (16 K/4 = 4K (4000 steps) is

required, if approximately 4 bytes is used for

one step.

Step

Approx.

8000steps

No.of

PROM Location

1

on

PCBoard

JANCD-CP50

30

14

Page 19

7. PC INSTRUCTIONS

This chapter explains the 61 type basic instructions and 11 type macro instructions that can be

used with this PC while describing their functions,

display symbols and coded lists.

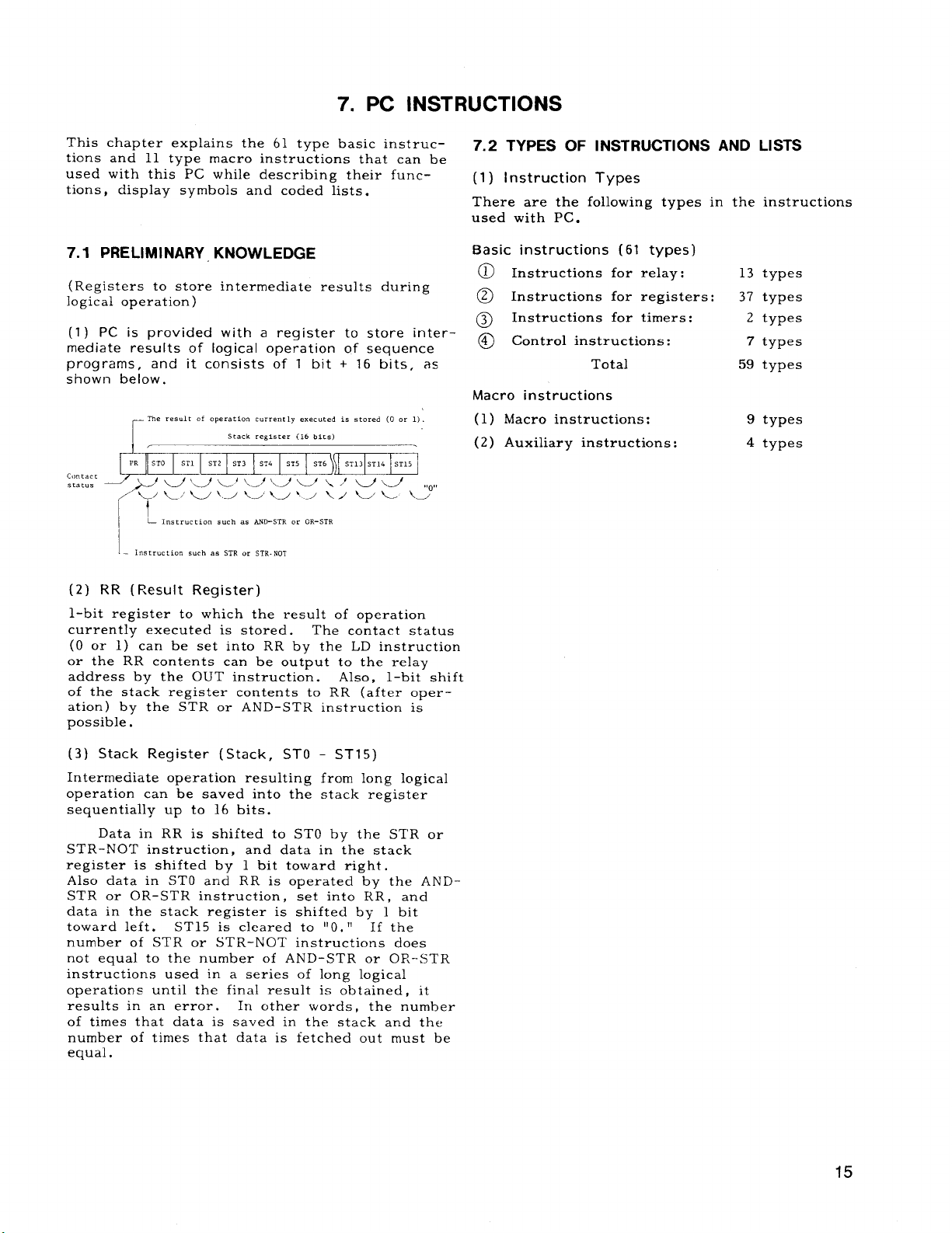

7.1 PRELIMINARY KNOWLEDGE

(Registers to store intermediate results during

logical operation )

(1) PC is provided with a register to store intermediate results of logical operation of sequence

programs,

and it consists of 1 bit + 16 bits, as

shown below.

~-

Th. T.SU1, .f operationcurrencly executed is stored (0 or 1)

L I.str.ctIon such .S AND-STRor OR-STR

i’

[- lns,rucrfonsuch ., STR ., STR.NOT

(2) RR (Result Register)

l-bit register to which the result of operation

currently executed is stored. The contact status

(O or 1) can be set into RR by the LD instruction

or the RR contents can be output to the relay

address by the OUT instruction.

Also, l-bit shift

of the stack register contents to RR (after oper–

ation) by the STR or AN D–STR instruction is

possible.

7.2 TYPES OF INSTRUCTIONS AND LISTS

(1) Instruction Types

There are the following types in the instructions

used with PC.

Basic instructions (61 types)

@) Instructions for relay:

13 types

@ Instructions for registers: 37 types

@) Instructions for timers:

@ Control instructions:

Total

2 types

7 types

59 types

Macro instructions

(1)

Macro instructions:

(2)

Auxiliary instructions:

9 types

4 types

(3) Stack Register (Stack, STO - ST15)

Intermediate operation resulting from long logical

operation can be saved into the stack register

sequentially up to 16 bits,

Data in RR is shifted to STO by the STR or

STR-NOT instruction, and data in the stack

register is shifted by 1 bit toward right .

Also data in STO and RR is operated by the ANDSTR or OR-STR instruction, set into RR, and

data in the stack register is shifted by 1 bit

toward left. ST15 is cleared to “O. “

If the

number of STR or ST R-NOT instructions does

not equal to the number of AN D–STR or OP.-STR

instructions used in a series of long logical

operations until the final result is obtained, it

results in an error. In other words , the number

of times that data is saved in the stack and the

number of times that data is fetched out must be

equal.

15

Page 20

7.2 TYPES OF INSTRUCTIONS AND LISTS (Cent’d )

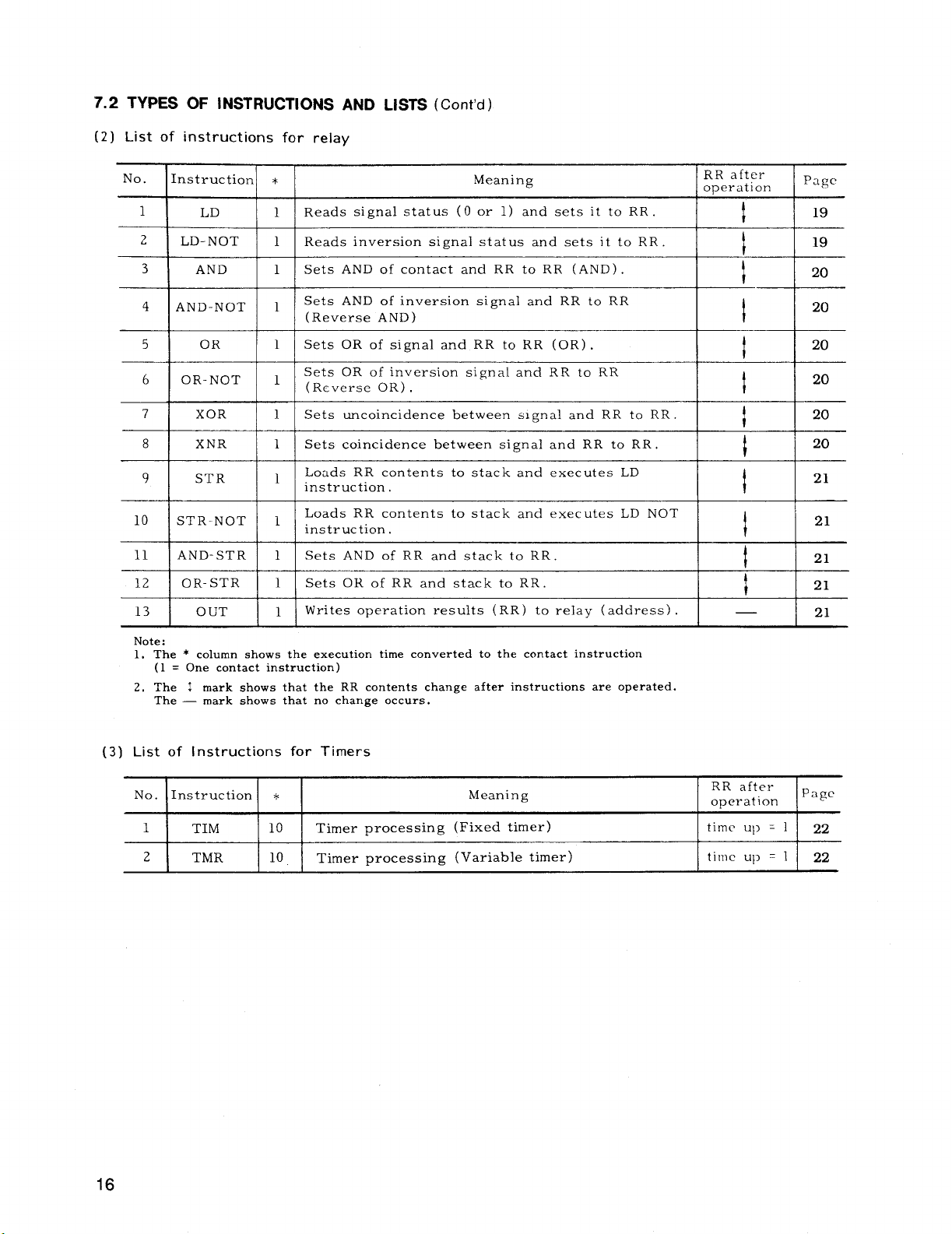

(2) List of instructions for relay

=7===

-+--b=-

+-+=

5

6

7 I XOR

8 I XNR

9

10 ST R-NOT

11 AN D-STR

12

=+=

13 I

Note:

1. The * column shows the execution time converted to the contact instruction

2, The $ mark shows that the RR contents change after instructions are operated.

OR

I

OR-NOT

I

STR

I

OR-STR

OUT

(1 = One contact instruction)

The — mark shows that no change occurs.

*

1

Reads signal status (0 or 1) and sets it to RR

I

Reads inversion signal status and sets it to RR

1

I

1 Sets

1

I

1

I

1

I

1

I

1

I

1

I

1

1

1

1

AND of contact and RR to RR (AND)

Sets AND of inversion signal and RR to RR

(Reverse AND)

Sets OR of signal and RR to RR (OR) .

Sets OR of inversion signal and RR to RR

(Reverse OR) .

Sets uncoincidence between signal and RR to RR .

Sets coincidence between signal and RR to RR.

Loads RR contents to stack and executes LD

instruction .

Loads RR contents to stack and executes LD NOT

instruction .

I

Sets AND of RR and stack to RR.

I

Sets OR of RR and stack to RR.

Writes operation results (RR) to relay (address) .

,

Meaning

RR after

operation

I 1

I

I

I 1 I

I

I

I 1 I

I I I

I

I

I

I

I 1 I

1

—

t ,

I

I

I

I

I

I

I

Page

19

19

20

20

20

20

20

20

21

21

21

21

21

(3) List of Instructions for Timers

Instruction * Meaning

No.

10 Timer processing (Fixed timer)

10

Timer processing (Variable timer)

16

1

2

TIM

TlvfR

RR after

operation

time up = 1 22

time up = 1 22

Page

Page 21

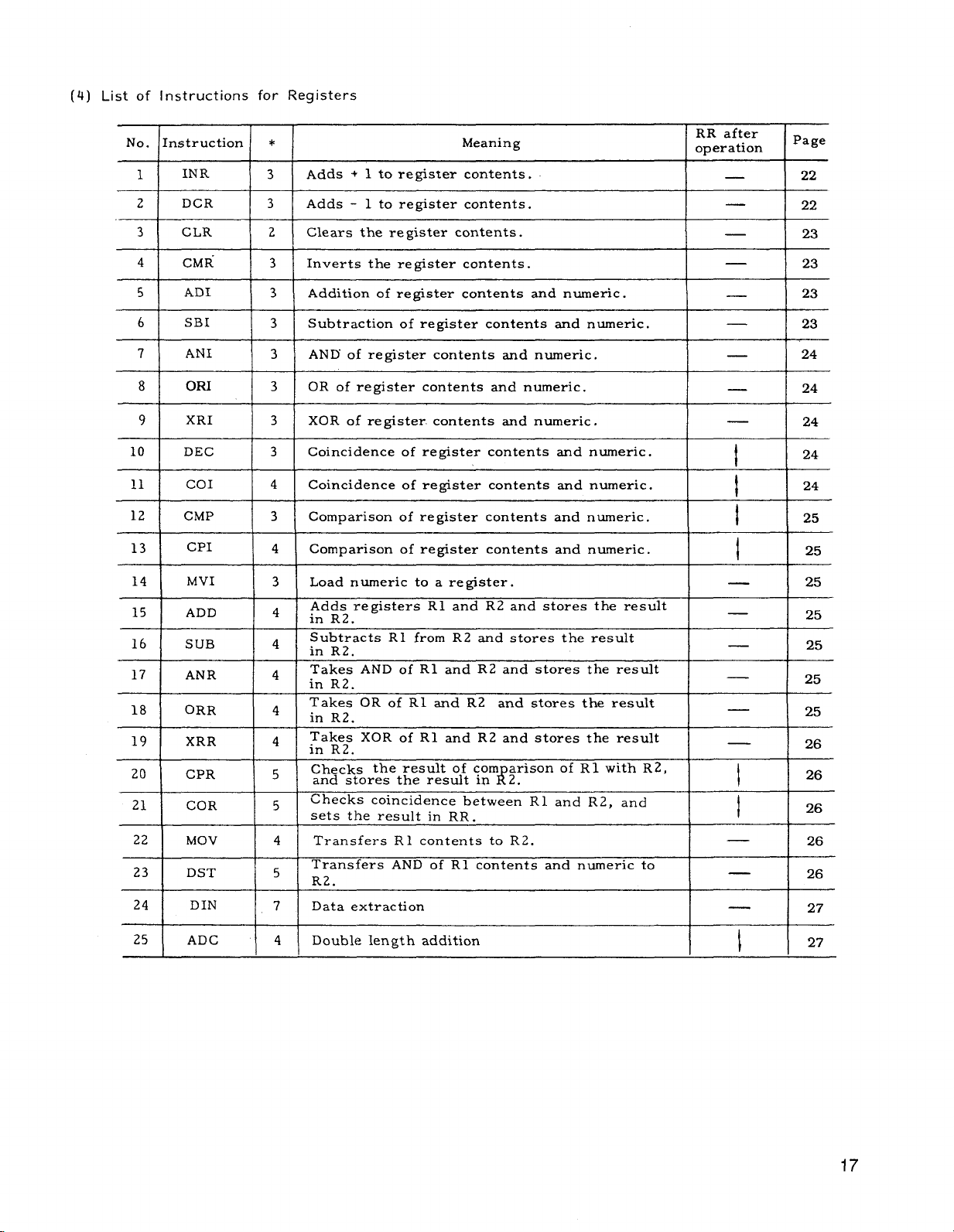

(4) List of Instructions for Registers

No. Instruction *

IN R

1

I

DCR

21

CLR \ 2 I Clears the register contents.

31

CMR I 3 I Inverts the register contents.

41

51

61

71

10 DEC 3 Coincidence of register contents and numeric.

11

12

13

14

15 ADD 4

16

17 AN R

18

19 XRR

20

21

22 I MOV

23 DST

24 I

ADI

SBI

‘N’ I 3 IANISO

8 OR1

9

XRI

COI

I

CMP

I

CPI

I

MVI

SUB

I

ORR

1 I 1

CPR

COR

DIN 1, 7 I Data extraction

I

Adds + 1 to register contents.

3

I

I

I 3 I Adds -1 to register contents.

I 3 I Addition of register contents and numeric.

] 3 I Subtraction of register contents and numeric. I –

f register contents and numeric,

3 OR of register contents and numeric.

3 XOR of register. contents and numeric.

4

I

I

I

I

[ ,

I 4 I Transfers R1 contents to R2.

I

Coincidence of register contents and numeric.

I

3IComparison of register contents and numeric.

4IComparison of register contents and numeric.

3 Load numeric to a register.

Adds registers R1 and R2 and stores the result

in R2.

Subtracts R1 from R2 and stores the result

4

in R2.

I

Takes AND of R1 and R2 and stores the result

4

in R2.

Takes OR of R1 and R2 and stores the result

4

in R2.

Takes XOR of R1 and R2 and stores the result

4

in R2.

Checks

5

I and stores the result in I?2.

Checks coincidence between R1 and R2, and

5

sets the result in RR.

Transfers AND of R1 contents and numeric to

5

R2.

the result of com arisen of R1 with R2,

Meaning

RR after

oDeration

I

—

I

l–

I –

l–

l–

I – H“

—

—

1

I 1

I

I

I

1

I

—

—

—

—

—

—

I

Page

22

I

I 22

123

I 23

I 23

I 23

24

24

24

24

I

25

I

I

I

t

25

2!5

25

25

25

26

I

I

l—

I

—

–127

I 26

25

26

26

26

25

ADC

I

4IDouble length addition

I

17

Page 22

7.2 TYPES OF INSTRUCTIONS AND LISTS ( Cent’d )

No.

:nstructio]

26

27

28

29

30 lNRW

31

32

34

35

36

37

ADDW

SUBW

MULW

DIVW

DCRW

CLRW

CORW

CPRW

MVIW

DSTW

*

Adds double length registers (wR2 and WR1) and

4

stores the result in WR2.

Subtracts WR1 from WR2 and stores the result in

4

WR2,

Multiplies double length register (WR2) with regis-

10

ter (Rl) and stores the result in WR2.

Divides double length re ister (WR2) by register

15

(Rl) and stores the resu t in WR2.

3 I Adds + 1 to double length register contents.

Adds - 1 to double length register contents.

3

Clears double length register contents.

3

233 CMRW

Inverts double length register contents.

1

Sets coincidence result of double length registers

3

(WR2 and WR1) to RR.

Sets comparison result of double length registers

3

(WR2 and WR1) to RR.

Loads numeric to double length register.

3

Transfers AND of double length register (WR1)

5

contents and numeric to doub–le len~th register

(WR2) .

Meaning

?

RR after

operation

H-

1s set to

RR “

“ 1“ when

overflow occurs.

*

—

I

—

1

I

I

I

1

I

Page

I

I

I

129

27

28

29

29

29

29

29

29

30

(5) List of Control Instructions

No. nstruction

1

2

3

4

5

6

7

NOP

MCR I 1 I Start of master control relay.

END 1

RET

RTI

SET

RTH

*

1 No-operation.

1 I

1 I Sequence program termination.

r m is set tO

1

I

1

1

‘-””1”

Meaning

End of master control relay.

and RET instruction is executed.

“ 1”

Sets RR to “ 1. “

High speed processing sequence program

termination.

RR after

operation

.—

1

Page

30

30

30

30

30

31

31

Page 23

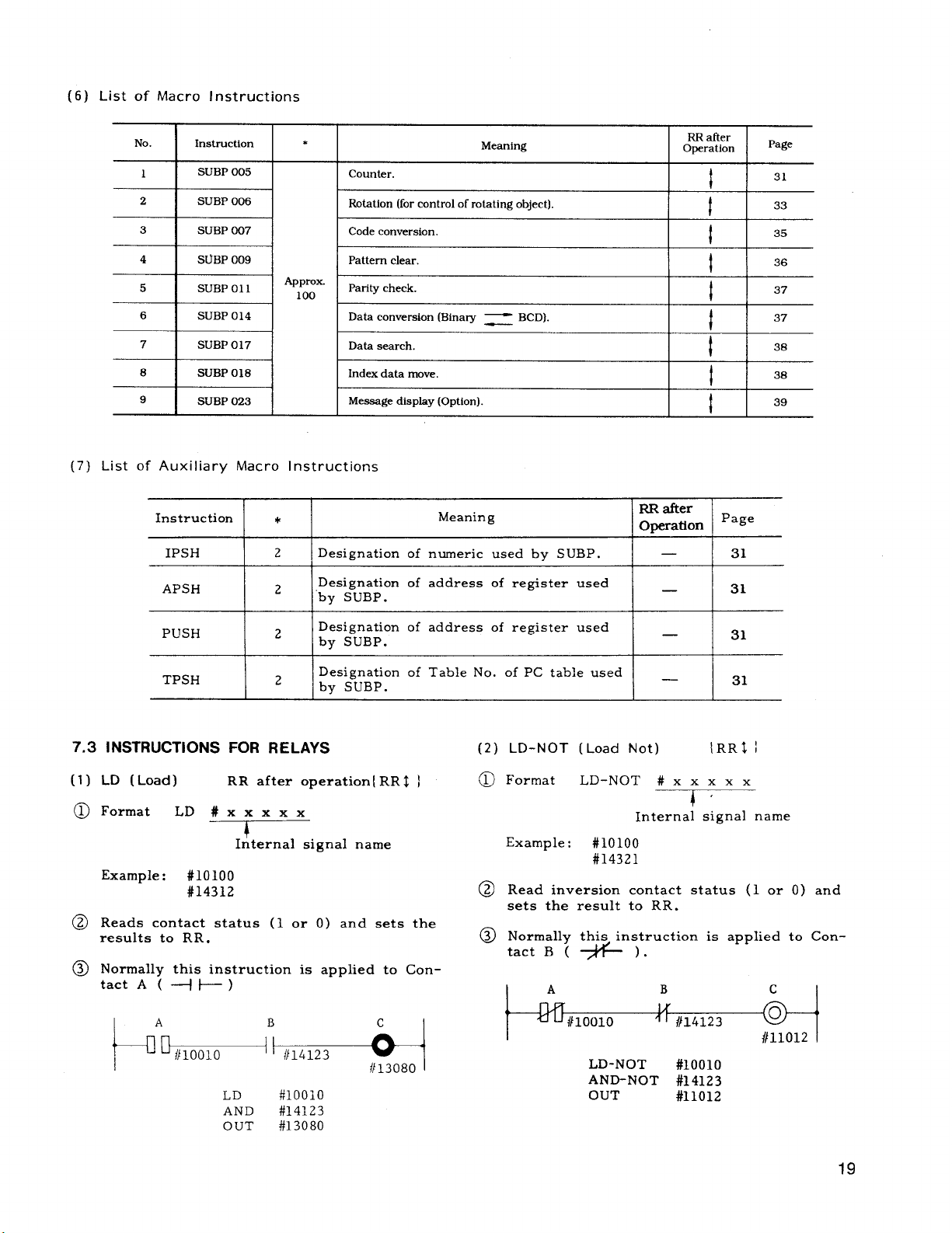

(6) List of Macro Instructions

No.

1

2

3

4

5

6

7

6

9

(7) List of Auxiliary Macro Instructions

Instruction

SUBP005

SUBP006

SU13P007 Codeconversion.

S~BP009

SUBP011

SUBP014 Dataconversion(Bina~

SUBP017 Datasearch.

SUBP018 Indexdatamove.

SUBP023

Instruction

IPSH

APSH

PUSH

I I

I

I

*

Approx.

100

*

Designation of numeric used by SUBP.

2

Designation of address of register used

2

“by SUBP.

Designation of address of register used

2

by SUBP.

Meaning

Counter.

Rotation(forcontrolofrotatingobject).

Patternclear.

Parttycheck.

— BCD).

MeaSagedispfay(Option).

Meaning

RR after

Operation

—

I

—

I

—

I

RRafter

Operation

1

1

1

1

1

t

1

1

I

‘age

[

I

I

Page

31

33

35

36

37

37

38

38

39

31

31

31

TPSH

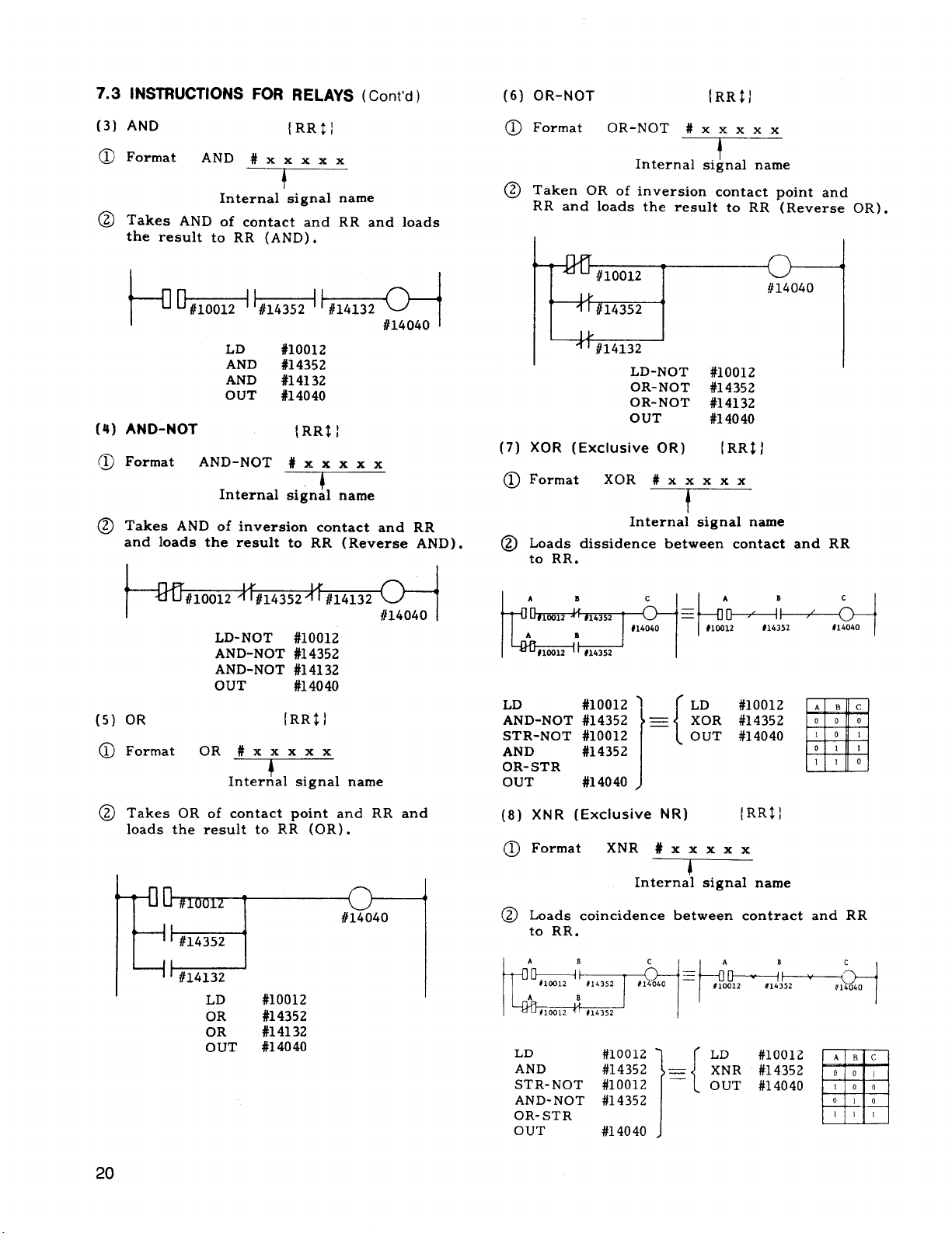

7,3 INSTRUCTIONS FOR RELAYS

LD ( Load)

Format

Example:

Reads contact status ( 1 or O) and sets the

results to RR.

Normally this instruction is applied to Contact

LD#xx xxx

#loloo

#14312

I

RR after operation{ RR $ I

!

Internal signal name

LD

AND

OUT

Designation of Table No. of PC table used _

2

by SUBP.

#loolo

#14123

#13080

31

I

4

1 #14123

#loolo

#llo12

IRRI }

,

c

& ‘

{/11012

LD-NOT (Load Not)

Format

Example:

Read inversion contact status ( 1 or O) and

sets the result to RR.

Normally this instruction is applied to Contact B ( ~Y~ ) .

+/}10010

LD-NOT#xx xxx

Internal signal name

#loloo

#14321

A

LD-NOT

AND-NOT #14123

OUT

B

1/

4

19

Page 24

7.3 INSTRUCTIONS FOR RELAYS (Cent’d )

(6)

OR-NOT

[RR$)

(3) AND

@ Format

@ Takes AND of contact and

the result to RR (AND).

(4) AND-NOT

@ Format

@) Takes AND of inversion contact and RR

and loads the result to RR (Reverse AND).

AND#x xxx

Internal signal

LD

AND

AND

OUT

AND-NOT # X X X X X

Internal signal name

{RR$I

+

#loo12

#14352

#14132

#14040

{RR$ ]

x

—

name

RR and loads

+

@ Format

@ Taken OR of inversion contact point and

RR and loads the result to RR (Reverse OR).

1’4;

(7) X(3R (Exclusive OR)

@ Format

@ Loads dissidence between contact and RR

to RR.

OR-NOT #xx xxx

Internal signal name

1

#14132

HI-NOT #10012

OR-NOT #14352

OR-NOT #14132

OUT

XOR#xx xxx

Internal signal name

t

#14040

t

{RR$j

lx lx

=Qfkoolz ‘1

(5) OR

@ Format

@ Takes OR of contact point and RR and

loads the result to Rk (OR).

E“”””

I

OR#xx xxx

#14352

#14132

I#14352 ~ t //14132

LD-NOT #10012

AND-NOT #14352

AND-NOT #14132

OUT

Internal signal name

!

#1

{RR1}

4040

~

LD

OR

OR

OUT #14040

#loo12

#14352

#14132

{/14040

#14040

0’

‘

I

XNR (Exclusive NR)

(8)

@ Format

@ Loads coincidence between contract and RR

—

to RR.

XNR#xx xxx

Internal signal name

4

{RR$}

20

Page 25

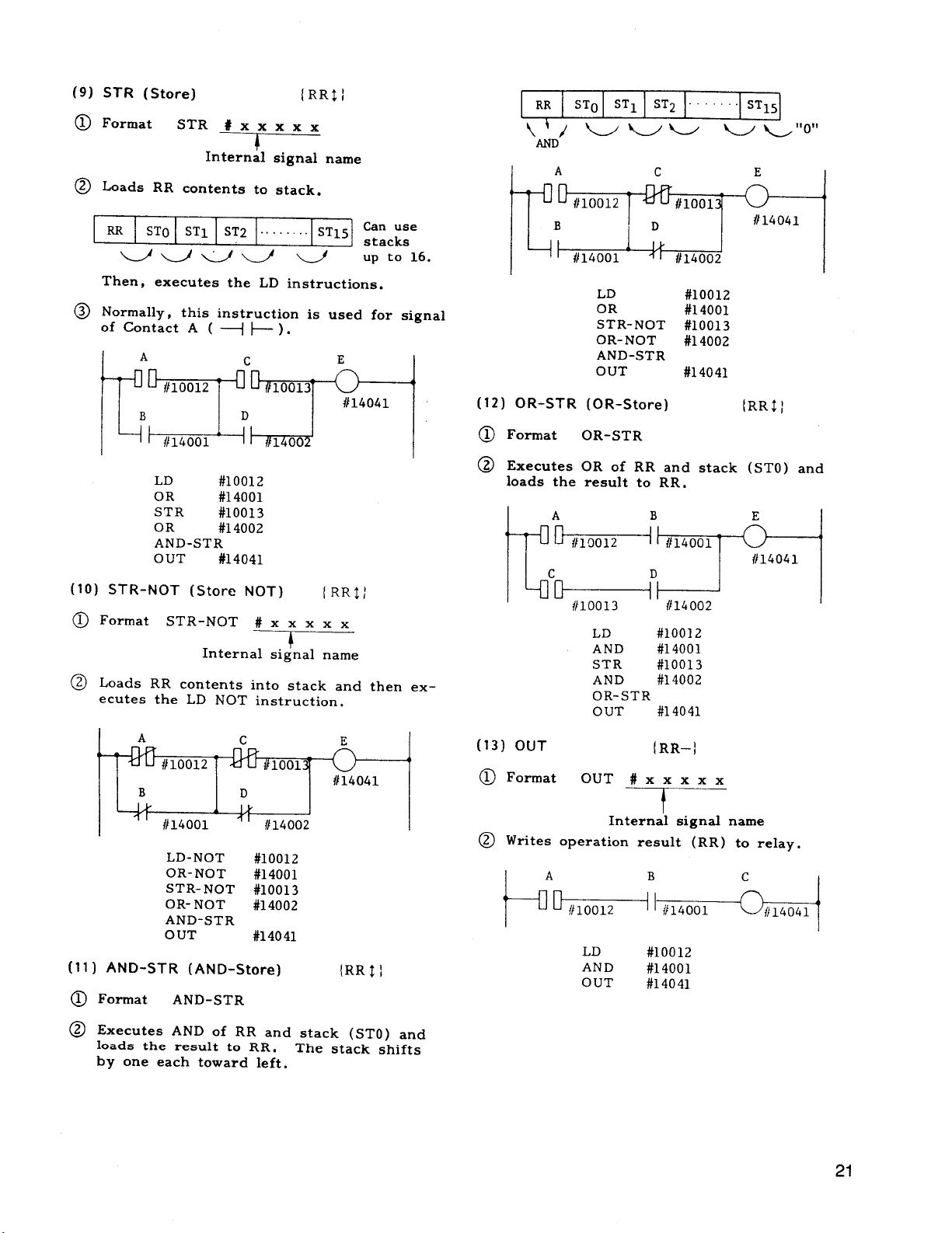

(9) STR (Store)

{RR$I

@ Format

@ Loads RR contents to stack.

RR

Utitiu u

Then, executes the LD instructions.

@ Normally, this instruction is used for signal

of Contact A ( ~ ~ ) .

1A

STR#xx xxx

Internal signal name

STO ST1

LD

OR

STR

OR

AND-STR

OUT

#loo12

#14001

#loo13

#14002

#14041

ST.2 .. . . .... ST15 ~aC;e

Up to 16.

c

E

I

1A

tl+~

II

(12) OR-STR (OR-Store)

Format

Executes OR of RR and stack (STO ) and

loads the result to RR.

/)10012 ] Jm/loo131

B

41

/)14001

LD

OR

STR-NOT #10013

OR-NOT

AND-STR

OUT

OR-STR

1A

{/19012

t---F’

c

I

ID

1

I,k’

41

#14002

#loo12

#14001

#14002

#14041

B E

‘-

I

I

{RR$;

E

#14041

1

I

I

(10) STR-NOT (Store NOT)

Format ST R-NOT # x x x x x

Internal signal name

Loads RR contents into stack and

ecutes the LD NOT instruction.

A

,

- #loo12 B

1>

L

/)14001

LD-NOT

OR-NOT

STR-NOT #10013

OR- NOT

AND-STR

OUT

) AND-STR (AND-Store)

Format

Executes AND of RR and stack (STO ) and

loads the result to RR.

by one each toward left.

AND-STR

c

{/10013’

D

1

II

’11

#14002

#loo12

#14001

#14002

#14041

{RR~;

E

{/14041

J

{RR$!

The stack shifts

then ex-

4I

I

I4h----iJl----J

(13) OUT

@ Format

@ Writes operation result (RR) to relay.

#loo13

LD

AND

STR

AND

OR-STR

OUT

OUT#xx xxx

Internal signal name

LD

AND

OUT

#14002

#loo12

#14001

#loo13

#14002

#14041

{RR–I

t

#loo12

#14001

#14041

21

Page 26

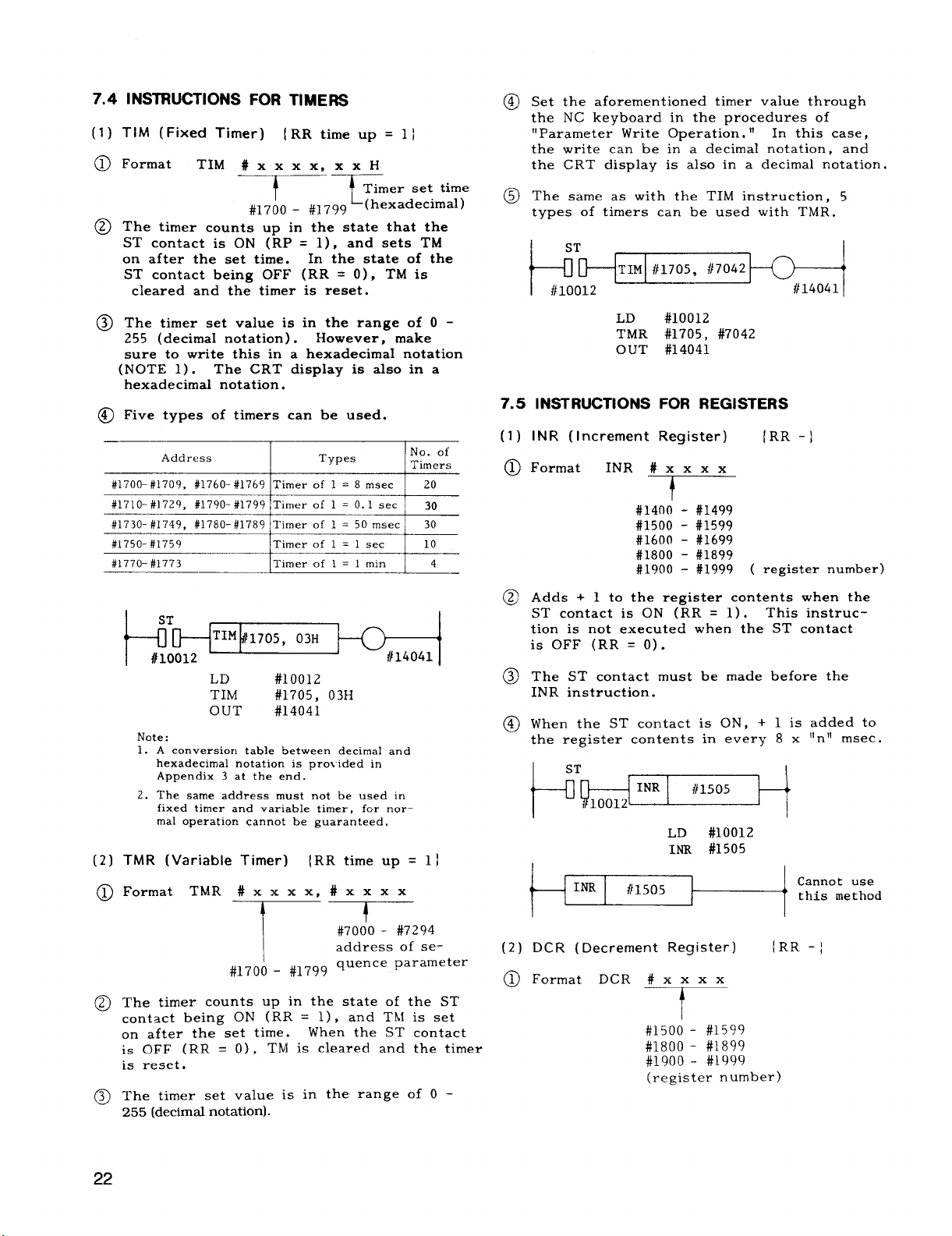

7.4 INSTRUCTIONS FOR TIMERS

(1) TIM

@ Format

(Fixed Timer) {RR time up = 1}

TIM#xxxx, xxH

Set the aforementioned timer value through

the NC keyboard in the procedures of

“Parameter Write Operation. “ In this case,

the write can be in a decimal notation, and

the CRT display is also in a decimal notation.

‘~~;::::::;

#1700 - #1799

@ The timer counts up in the state that the

ST contact is ON (RP = 1), and sets TM

on after the set time.

In the state of the

ST contact being OFF (RR = O), TM is

cleared and the timer is reset.

@) The timer set value is in the range of O -

255 (decimal notation). However, make

sure to write this in a hexadecimal notation

(NOTE 1).

The CRT display is also in a

hexadecimal notation.

@ Five types of timers can be used.

Address

#1700-#1709, #1760-#1769 Timer of 1 = 8 msec

#1710-#1729. #1790-#1799 \Timer of 1 = 0.1 sec / 30

#1730-#1749, #1780-#1789 \Timer of 1 = 50 msec \ 30

#1750-#1759

#1770-#1773 Timer of 1 = 1 min

I

Types

Timer of 1 = 1 sec 10

No. of

Timers

20

I

4

ST

TIM }1705, (J3H

#loo12

t+ ‘~ ~

LD

TIM

OUT

Note:

1. A conversion

hexadecimal notation is pro~ ided in

Appendix 3 at the end.

2. The same address must not be used in

fixed timer and variable timer, for nor-

mal operation cannot be guaranteed.

#loo12

#1705, 03H

#14041

table between decimal and

#14041

TMR (Variable Timer) {RR time up = 1 \

Format TMR#xxxx, # xxxx

~ T—

#7000 - #7294

1

#170A - #1799 q

address of se-

uence parameter

The timer counts up in the state of the ST

contact being ON (RR = 1) , and TM is set

on after the set time.

When the ST contact

is OFF (RR = O) , TM is cleared and the timer

is reset.

The timer set value

is in the range of O -

255 (decimal notation).

The same as with the TIM instruction, 5

types of timers can be used with TMR.

I

ST

TIM #1705, #7042

//10012

t+ 1

7.5 INSTRUCTIONS

(1)

INR (Increment

LD

TMR

OUT

#loo12

#1705, #7042

#14041

FOR REGISTERS

Register) {RR -j

Format INR#x xxx

#1400 - #1499

#1500 - #1599

#1600 - #1699

#1800 - #1899

regkter number)

Adds + 1

#1900 - #1999 (

to the register contents when the

ST contact is ON (RR = 1). This instruction is not executed when the ST contact

is OFF (RR = O).

The ST contact must be made before the

INR instruction.

the ST contact is ON, + 1 is added to

When

the register contents in every 8 x “n” msec.

ST

INR

#1505

LD #10012

INR #1505

Cannot use

(,

this method

DCR (Decrement Register)

Format DCR # x x x x

4

{RR -~

I

#1500 - #1599

#1800 - #1899

#1900 - #1999

(register number)

4I

Page 27

.... ..n -

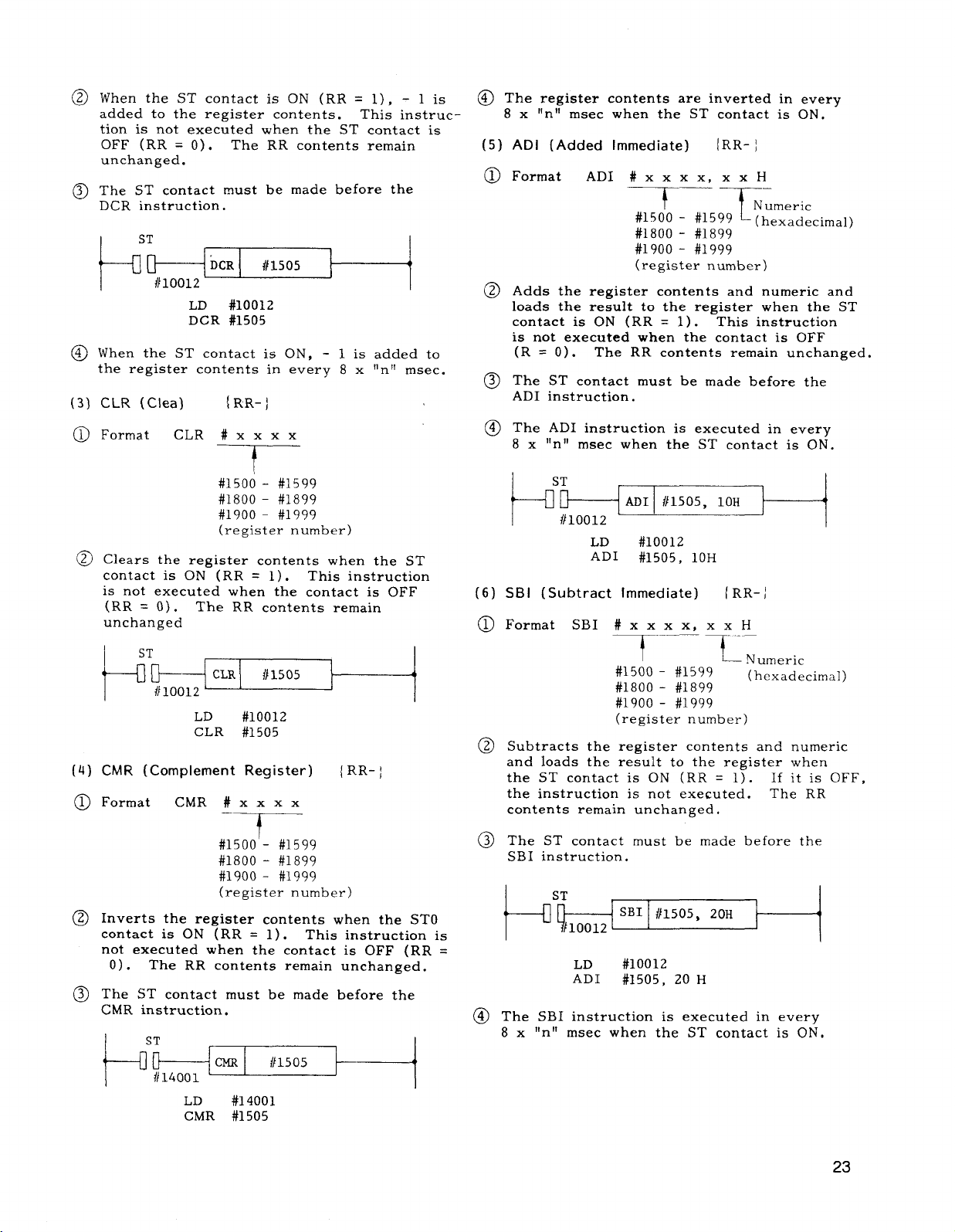

when the S1’ contact is

added to the register contents.

tion is not executed when the ST contact is

OFF (RR = o). The RR contents remain

unchanged.

The ST contact must be made before the

DCR instruction.

ST

DCR

b~ ‘-

When the ST contact is ON, - 1 is added to

the register contents in every 8 x ‘In!! msec.

CLR (Clea)

Format

Clears the register contents when the ST

contact is ON (RR = 1). This instruction

is not executed when the contact is OFF

(RR =

unchanged

//10012

LD #10012

DCR #1505

{RR-j

CLR#x xxx

#1500 - #1599

#1800 - #1899

#1900 - #1999

(register number)

o).

The RR contents remain

LD

CLR #1505

#loo12

CMR (Complement Register)

Format

Inverts the register contents when the STO

contact is ON (RR = 1) . This instruction is

not executed when the contact is OFF (RR =

o). The RR contents remain unchanged.

The ST contact must be made before the

CMR instruction.

P+ml

CMR#x xxx

ST

//14001

LD

CMR #1505

‘7

#1500 - #1599

#1800 - #1899

#1900 - #1999

(register number)

#14001

-.. ,—-. .

UN (KK = 1) , - 1 is

#1505

!

{RR-~

#1505

+--i

This instruc-

<1

@ The register contents are inverted in everv

8 x “n’~ msec when the ST contact is ON. ‘

AD I (Added Immediate)

Format ADI#xxxx, xxH

X5~;meric

#1800 - #1899

#1900 - #1999

(register number)

Adds the register contents and numeric and

loads the result to the register when the ST

contact is ON (RR = 1) . This instruction

is not executed when the contact is OFF

(R= O). The RR contents remain unchanged.

The ST contact must be made before the

AD I instruction.

The ADI instruction is executed in every

8 x “n” msec when the ST contact is ON.

ST

ADI #1505, 10H

1- ~f

SBI (Subtract Immediate)

Format SBI#xxxx, xx H

Subtracts the register contents and numeric

and loads the result to the register when

the ST contact is ON (RR = 1) . If it is OFF,

the instruction is not executed.

contents remain unchanged.

The ST contact must be made before the

SBI instruction.

t-+---+ 1-1

rhe SBI instruction is executed in every

) x “n” msec when the ST contact is ON,

#loo12

LD

AD1 #1505, 10H

_l–.-—

#1500 - #1599

#1800 - #1899

#1900 - #1999

(register number)

ST

)10012

AD I

SB1 #1505, 20H

LD

#loo12

#1505, 20 H

#loo12

1

{RR-;

(hexadecimal)

( RR-;

~...-

L ~umeric

(hexadecimal)

The RR

~

A

I

23

Page 28

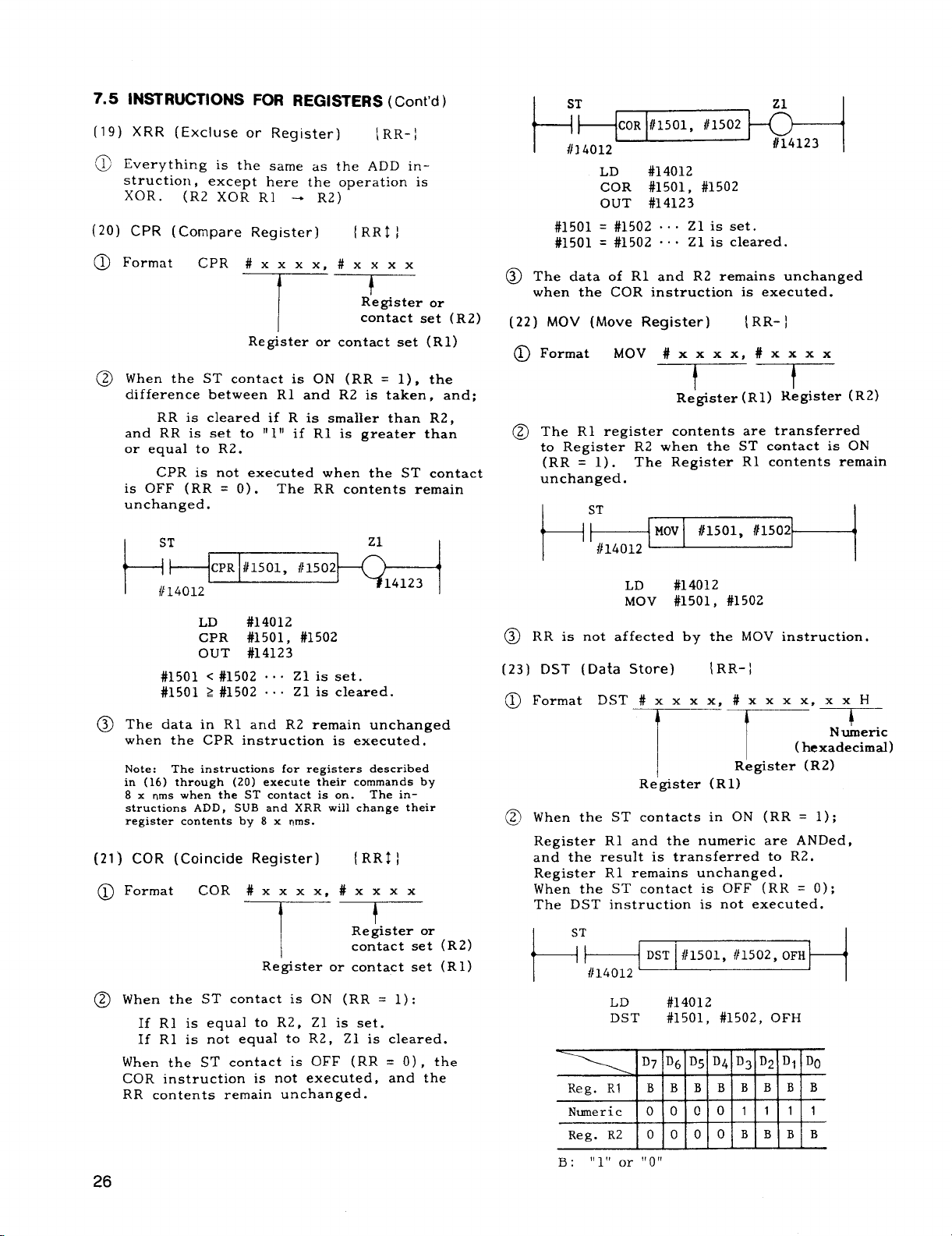

7.5 INSTRUCTIONS FOR REGISTERS

Cent’d )

(9)

XRI (Exclusive or Immediate)

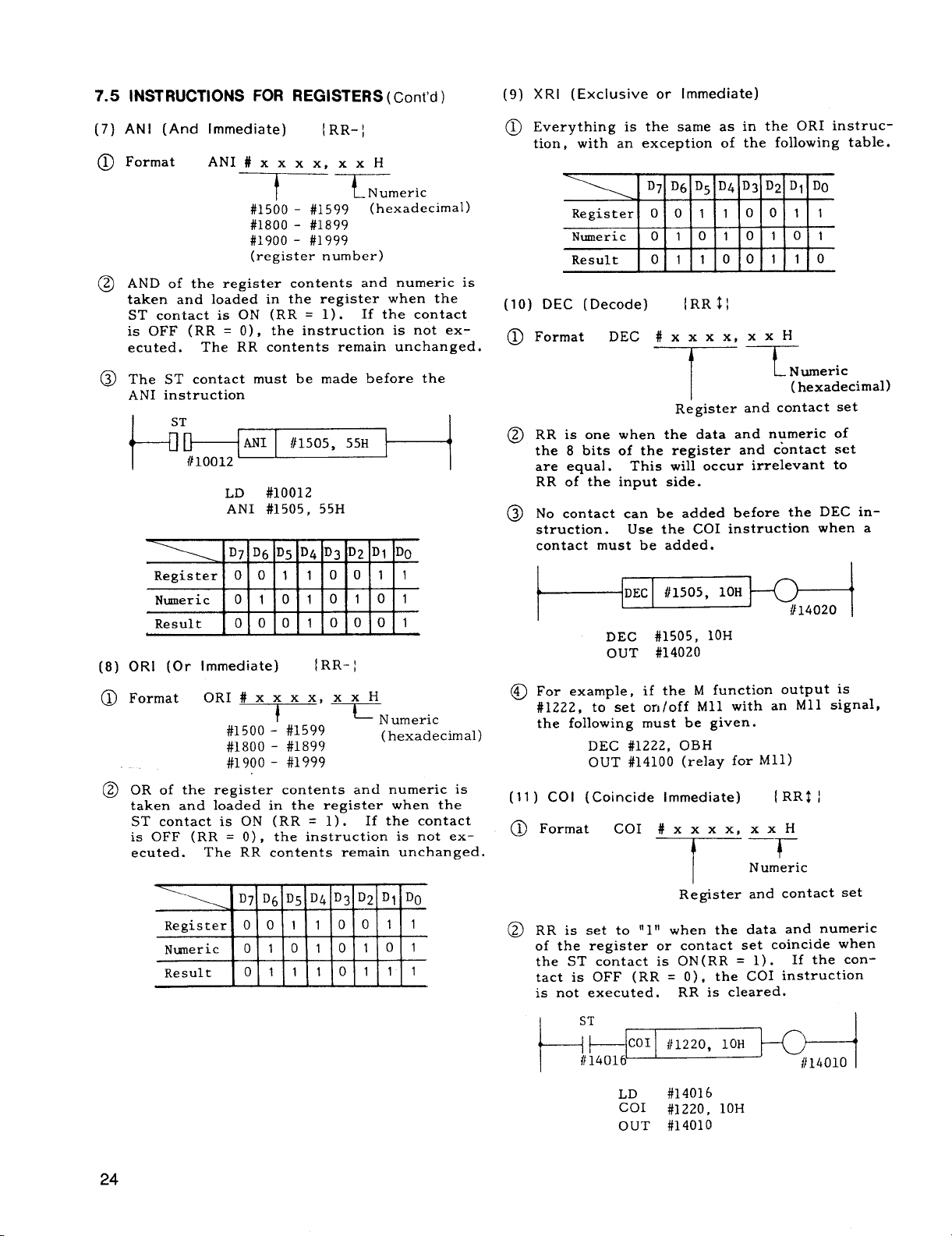

AN I (And Immediate)

Format

ANI#xxxx, xxH

— —

t

#1500 - #1599 (hexadecimal)

#1800 - #1899

#1900 - #1999

(register number)

of the register contents and numeric is

AND

taken and load~d in the register when the

ST contact is ON (RR = 1). If the contact

is OFF (RR = O) , the instruction is not ex-

ecuted.

The ST contact must be made before the

ANI instruction

t----- 1

Re~ister o 0 1

Numeric 1011 !01110111011

Result

ORI

Format

The RR contents remain unchanged.

ST

WI

#loo12

LD #10012

ANI #1505, 55H

D7 D6 D5 n). ln~ ln~ Inf Inn

0 001 0 O1o11

I

(Or Immediate)

ORI#xxxx, xxH

——

1

#1500 - #1599

#1800 - #1899

{RR-]

L. umeric

/}1505, 55H

t

tmT-tw-

IRR-1

!-

Numeric

(hexadecimal)

#1900 “ #1999

OR of the register contents and numeric is

taken and loaded in the register when the

ST contact is ON (RR = 1). If the contact

is OFF (RR = O) , the instruction is not ex–

ecuted.

-..

The RR contents remain unchanged.

‘.

D7 D6 D5

D4 D3 D2

D1 D()

@ Everything is the same as in the ORI instruc-

tion, with an exception of the following table.

D7 D6 D5 D4 D3 D2

Register o 0 1 1 0 0 1 1

Numeric o 1 0 1 0 1 0 1

Result o 1

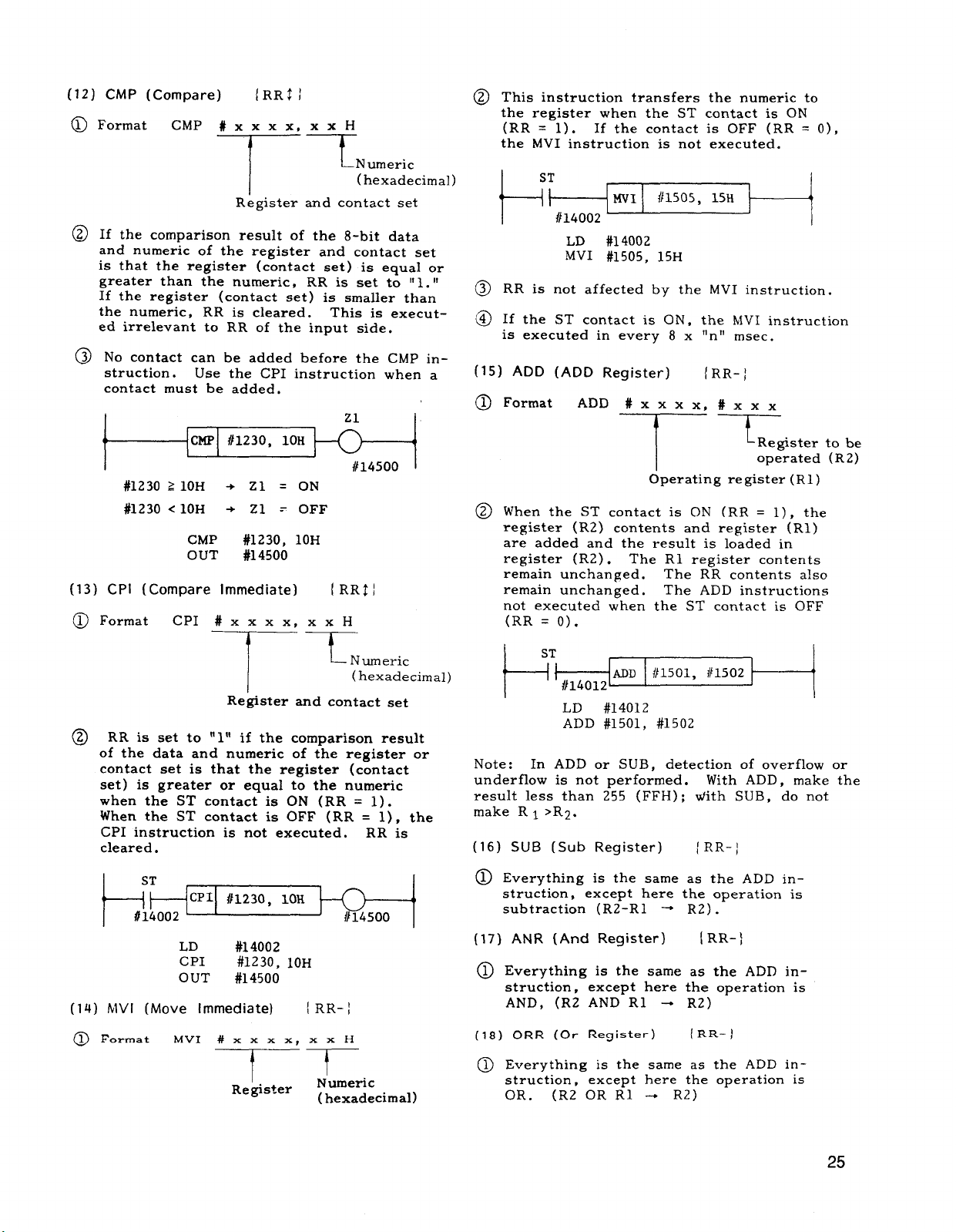

(10) DEC (Decode)

Format

d1

RR is one when the data and numeric of

the 8 bits of the register and contact set

are equal.

RR of the input side.

No contact can be added before the DEC instruction.

contact must be added.