Page 1

Virtex UltraScale+ FPGAs

GTM Transceivers

User Guide

UG581 (v1.0) January 4, 2019

Page 2

Revision History

Send Feedback

The following table shows the revision history for this document.

Revision History

Section

01/04/2019 Version 1.0

Initial Xilinx release. N/A

Revision Summary

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 2

Page 3

Table of Contents

Send Feedback

Revision History...............................................................................................................2

Chapter 1: Transceiver and Tool Overview.......................................................5

Introduction to the UltraScale Architecture.............................................................................5

Features........................................................................................................................................6

UltraScale+ FPGAs GTM Transceivers Wizard.......................................................................... 9

Simulation.................................................................................................................................. 10

Implementation.........................................................................................................................11

Chapter 2: Shared Features.....................................................................................12

Reference Clock Input/Output Structure............................................................................... 12

Reference Clock Selection and Distribution...........................................................................14

LCPLL...........................................................................................................................................18

Reset and Initialization............................................................................................................. 23

Power Down...............................................................................................................................45

Loopback.................................................................................................................................... 46

Dynamic Reconfiguration Port................................................................................................ 47

Digital Monitor...........................................................................................................................50

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 3

Chapter 3: Transmitter.............................................................................................. 54

TX Interface................................................................................................................................55

TX FEC......................................................................................................................................... 63

TX Buffer.....................................................................................................................................66

TX Pattern Generator................................................................................................................67

TX Polarity Control.....................................................................................................................71

TX Gray Encoder........................................................................................................................ 71

TX Pre-Coder.............................................................................................................................. 72

TX Fabric Clock Output Control............................................................................................... 73

TX Configurable Driver............................................................................................................. 77

Chapter 4: Receiver......................................................................................................84

RX Analog Front End................................................................................................................. 85

RX Equalizer............................................................................................................................... 87

Page 4

RX CDR........................................................................................................................................ 93

Send Feedback

RX Fabric Clock Output Control............................................................................................... 94

RX Margin Analysis....................................................................................................................98

RX Pre-Coder..............................................................................................................................99

RX Gray Encoder........................................................................................................................99

RX Polarity Control.................................................................................................................. 100

RX Pattern Checker................................................................................................................. 101

RX Buffer...................................................................................................................................104

RX FEC....................................................................................................................................... 106

RX Interface..............................................................................................................................113

Chapter 5: Board Design Guidelines................................................................ 117

Pin Description and Design Guidelines................................................................................ 117

Reference Clock....................................................................................................................... 120

GTM Transceiver Reference Clock Checklist........................................................................ 122

Reference Clock Interface...................................................................................................... 123

AC Coupled Reference Clock..................................................................................................124

Unused Reference Clocks.......................................................................................................125

Reference Clock Output Buffer..............................................................................................125

Reference Clock Power...........................................................................................................125

Power Supply and Filtering.................................................................................................... 125

PCB Design Checklist.............................................................................................................. 129

Appendix A: DRP Address Map of the GTM Transceiver in

UltraScale+ FGPAs.................................................................................................. 133

GTM_DUAL Primitive DRP Address Map...............................................................................133

Appendix B: Additional Resources and Legal Notices........................... 143

Xilinx Resources.......................................................................................................................143

Documentation Navigator and Design Hubs...................................................................... 143

Please Read: Important Legal Notices................................................................................. 144

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 4

Page 5

Chapter 1

Send Feedback

Transceiver and Tool Overview

Introduction to the UltraScale Architecture

The Xilinx® UltraScale™ architecture is the rst ASIC-class architecture to enable mul-hundred

gigabit-per-second levels of system performance with smart processing, while eciently roung

and processing data on-chip. UltraScale architecture-based devices address a vast spectrum of

high-bandwidth, high-ulizaon system requirements by using industry-leading technical

innovaons, including next-generaon roung, ASIC-like clocking, 3D-on-3D ICs, mulprocessor

SoC (MPSoC) technologies, and new power reducon features. The devices share many building

blocks, providing scalability across process nodes and product families to leverage system-level

investment across plaorms.

Virtex® UltraScale+™ devices provide the highest performance and integraon capabilies in a

FinFET node, including both the highest serial I/O and signal processing bandwidth, as well as

the highest on-chip memory density. As the industry's most capable FPGA family, the Virtex

UltraScale+ devices are ideal for applicaons including 1+ Tb/s networking and data center and

fully integrated radar/early-warning systems.

Virtex® UltraScale™ devices provide the greatest performance and integraon at 20 nm,

including serial I/O bandwidth and logic capacity. As the industry's only high-end FPGA at the

20 nm process node, this family is ideal for applicaons including 400G networking, large scale

ASIC prototyping, and emulaon.

Kintex® UltraScale+™ devices provide the best price/performance/wa balance in a FinFET

node, delivering the most cost-eecve soluon for high-end capabilies, including transceiver

and memory interface line rates as well as 100G connecvity cores. Our newest mid-range family

is ideal for both packet processing and DSP-intensive funcons and is well suited for applicaons

including wireless MIMO technology, Nx100G networking, and data center.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 5

Page 6

Chapter 1: Transceiver and Tool Overview

Send Feedback

Kintex® UltraScale™ devices provide the best price/performance/wa at 20 nm and include the

highest signal processing bandwidth in a mid-range device, next-generaon transceivers, and

low-cost packaging for an opmum blend of capability and cost-eecveness. The family is ideal

for packet processing in 100G networking and data centers applicaons as well as DSP-intensive

processing needed in next-generaon medical imaging, 8k4k video, and heterogeneous wireless

infrastructure.

Zynq® UltraScale+™ MPSoC devices provide 64-bit processor scalability while combining real-

me control with so and hard engines for graphics, video, waveform, and packet processing.

Integrang an ARM®-based system for advanced analycs and on-chip programmable logic for

task acceleraon creates unlimited possibilies for applicaons including 5G Wireless, next

generaon ADAS, and Industrial Internet-of-Things.

This user guide describes the UltraScale architecture GTM transceivers and is part of the

UltraScale architecture documentaon suite available at: www.xilinx.com/ultrascale.

Features

The GTM transceiver in the UltraScale+ FPGA is a high performance transceiver, supporng line

rates between 9.8 Gb/s and 58 Gb/s. Based on the available PLL divider conguraons in the

GTM transceivers, the following line rates are supported:

• PAM4 modulaon:

○ 58 Gb/s – 39.2 Gb/s

○ 29 Gb/s – 19.6 Gb/s

• NRZ modulaon:

○ 29 Gb/s – 19.6 Gb/s

○ 14.5 Gb/s – 9.8 Gb/s

The GTM transceiver is Xilinx’s rst PAM4 enabled transceiver that is highly congurable and

ghtly integrated with the programmable logic resources of the FPGA. The table below

summarizes the features by funconal group that support a wide variety of applicaons.

Table 1: GTM Transceiver Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 6

Group Feature

KP4 Reed-Solomon forward error correction (RS-FEC) for up to 2 x 58 Gb/s or 1 x 116 electrical and optical links

PCS

PRBS generator and checker

Programmable FPGA logic interface

Page 7

Chapter 1: Transceiver and Tool Overview

Send Feedback

Table 1: GTM Transceiver Features (cont'd)

Group Feature

LC tank oscillator PLL (LCPLL) for best jitter performance

Flexible clocking with one PLL per Dual (two channels)

Programmable TX output

PMA

Notes:

1. A dual is a cluster or set of two GTM transceiver channels. One GTM_DUAL primitive, one differential reference clock

TX FIR filter with de-emphasis controls

Continuous time linear equalizer (CTLE)

Decision feedback equalization (DFE)

Feed forward equalization (FFE)

pin pair, and analog supply pins. There is no channel primitive.

The GTM transceiver supports NRZ and PAM4

modulaon as well as the following protocols:

• 100GE CAUI2

• 100GE CAUI4

• 200GE CCAUI4

• 400GE (CDAUI8)

• 50GE LAUI

• 50GE LAUI2

• Ethernet AN/LT (auto negoaon/link training)

• OTU4

• Interlaken at 53.125 Gb/s, 25.78125 Gb/s, and 12.5 Gb/s

• CPRI at 48 Gb/s, 24 Gb/s, 12 Gb/s, and 10.1 Gb/s

The rst-me user is recommended to read High-Speed Serial I/O Made Simple, which discusses

high-speed serial transceiver technology and its applicaons. The Xilinx Vivado® IP catalog

includes an UltraScale+ FPGAs GTM Transceivers Wizard to automacally congure GTM

transceivers to support conguraons for dierent protocols and perform custom conguraons.

The GTM transceiver oers a data rate range and features that allow physical layer support for

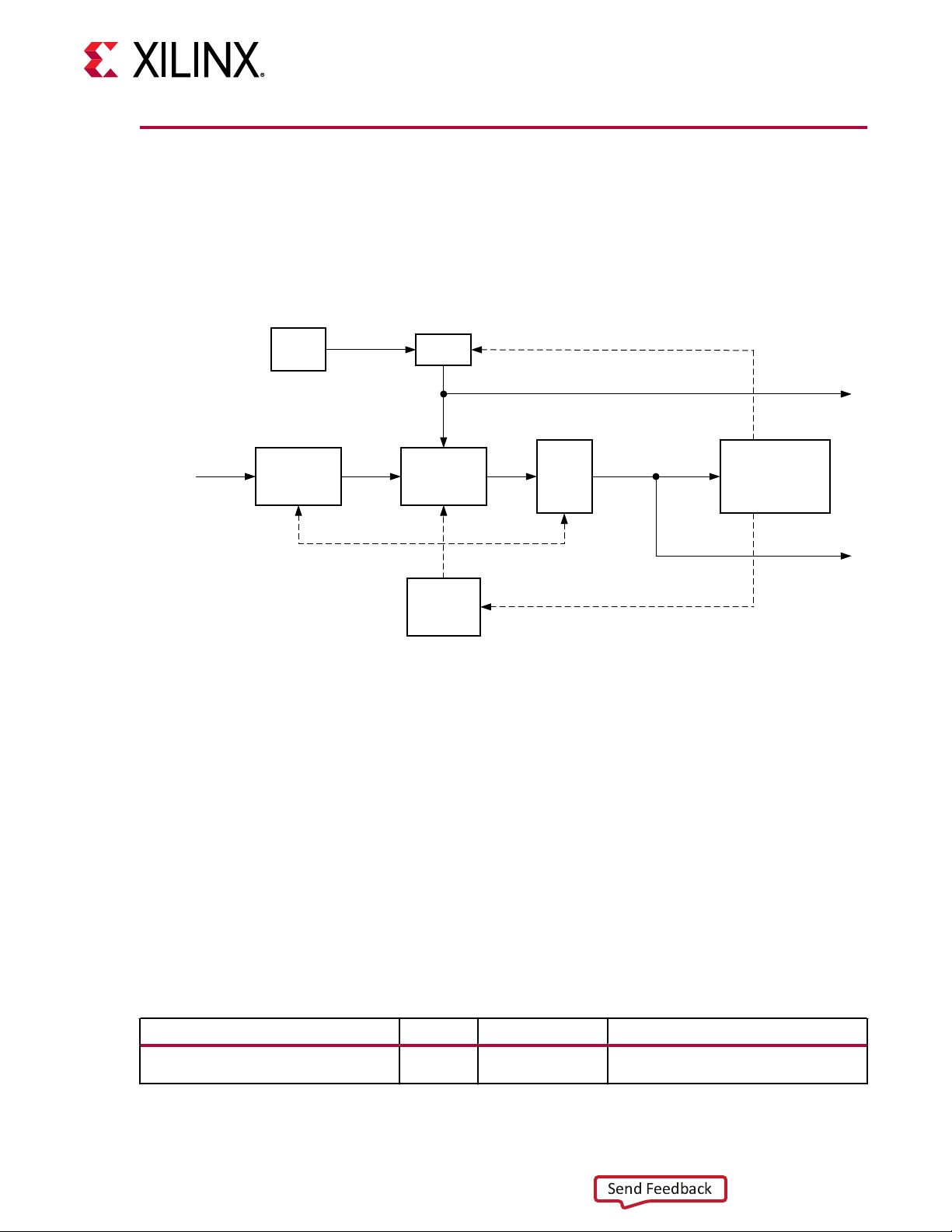

various protocols. The following gure illustrates the clustering of one GTM_DUAL primive.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 7

Page 8

IBUFDS_GTM /

Send Feedback

OBUFDS_GTM

REFCLK

Distribution

Chapter 1: Transceiver and Tool Overview

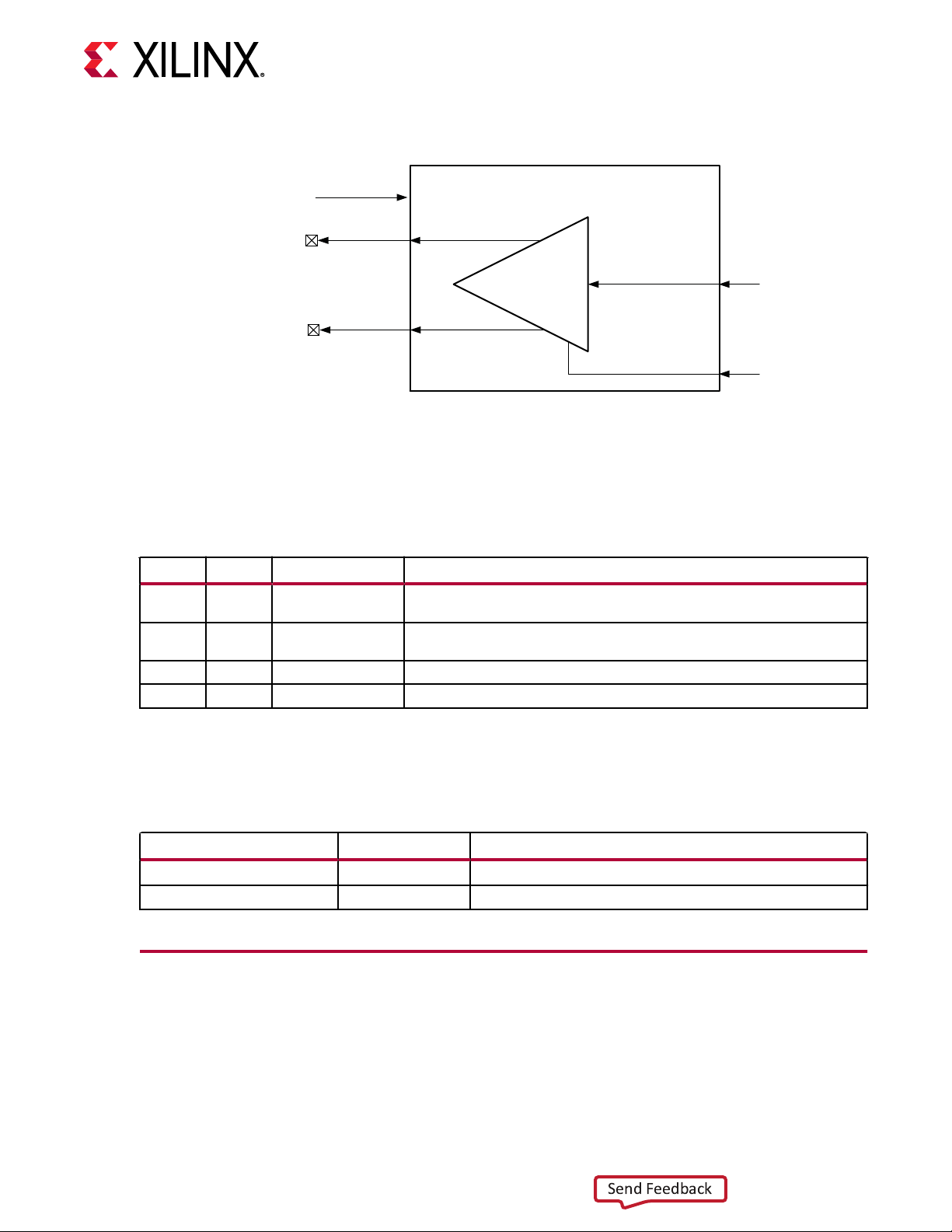

Figure 1: GTM Dual Configuration

GTM_DUAL

GTM Channel 0 (CH0)

TX

RX

LCPLL

GTM Channel 1 (CH1)

TX

RX

X20210-061418

The GTM_DUAL primive contains one LCPLL and two GTM channels. Contrary to other

UltraScale+ device transceivers such as the GTH and GTY transceivers, the GTM transceiver

does not contain channel/common primives. All channel ports and aributes are within the

GTM_DUAL primive. The following gure illustrates the topology of a GTM channel.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 8

Page 9

Driver

Send Feedback

TX

TX

Pre/

Pre2/

Post

Emp

PISO

Pre-Coder

Chapter 1: Transceiver and Tool Overview

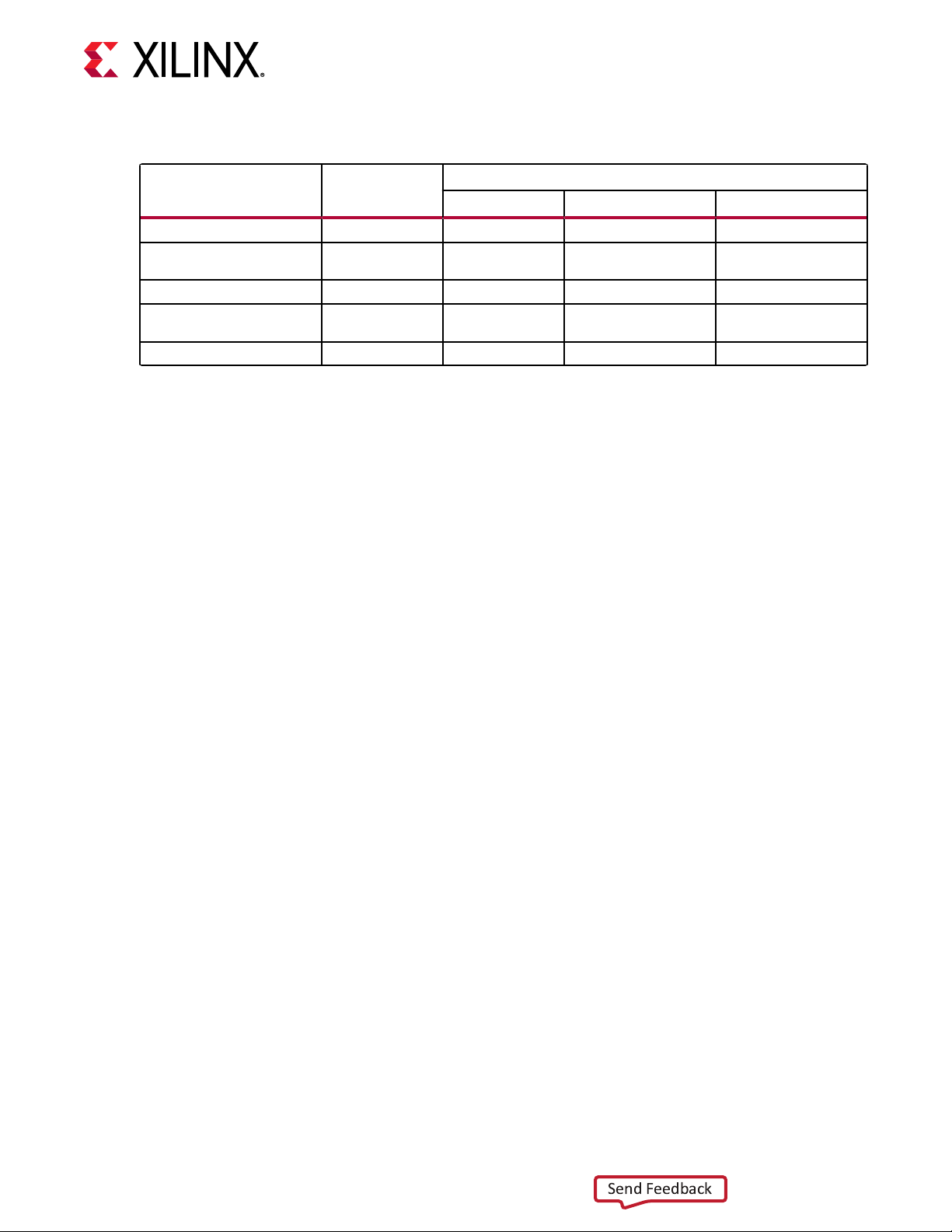

Figure 2: GTM Channel Topology

Pattern

Generator

Gray

Encoder

Polarity

FIFO

FEC

TX

Interface

RX PMA

TX PCS

To RX Parallel

Data (Near-End

PCS Loopback)

Pre-

Coder

RX PCS

Gray

Decoder

Polarity

PRBS

Checker

FIFO

FEC

RX EQ SIPOADC

DFE/

FFE

TX PMA

UltraScale+ FPGAs GTM Transceivers Wizard

From RX Parallel

Data (Far-End

PCS Loopback)

RX

Interface

X20211-052918

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 9

The UltraScale+ FPGAs GTM Transceivers Wizard (hereinaer called the Wizard) is the preferred

tool to generate a wrapper to instanate the GTM_DUAL. The Wizard is located in the IP catalog

under the IO Interfaces category.

RECOMMENDED

: Download the most recent IP update before using the Wizard. Details on how to

use this Wizard can be found in the UltraScale+ FPGAs GTM Transceivers Wizard LogiCORE IP Product

Guide (PG315).

Page 10

Chapter 1: Transceiver and Tool Overview

Send Feedback

Simulation

The simulaon environment and the test bench must fulll specic prerequisites before running

simulaon using the GTM_DUAL primives. For instrucons on how to set up the simulaon

environment for supported simulators depending on the used hardware descripon language

(HDL), see the latest version of the UltraScale+ GTM Transceivers Wizard LogiCORE IP Product

Guide (PG315) and Vivado Design Suite User Guide: Logic Simulaon (UG900).

The prerequisites for simulang a design with the GTM_DUAL primives are listed:

• A simulator with support for SecureIP models: SecureIP is an IP encrypon methodology.

SecureIP models are encrypted versions of the Verilog HDL used for implementaon of the

modeled block. To support SecureIP models, a simulator that complies with the encrypon

standards described in the Verilog language reference manual (LRM)—IEEE Standard for

Verilog Hardware Descripon Language (IEEE Std 1364-2005) is required.

• A mixed-language simulator for VHDL simulaon: SecureIP models use a Verilog standard. To

use them in a VHDL design, a mixed-language simulator is required. The simulator must be

able to simulate VHDL and Verilog simultaneously.

• An installed GTM transceiver SecureIP model

• The correct setup of the simulator for SecureIP use (inializaon le, environment variables).

• The correct simulator resoluon (Verilog).

Ports and Attributes

There are no simulaon-only ports on the GTM_DUAL primives. The GTM_DUAL primive has

aributes intended only for simulaon. The following table lists the simulaon-only aributes of

the GTM_DUAL primive. The names of these aributes start with SIM_.

Table 2: GTM_DUAL Simulation-Only Attributes

Attribute Type Description

SIM_RESET_SPEEDUP String If the SIM_RESET_SPEEDUP attribute is set to TRUE (default), an

SIM_DEVICE

String This attribute selects the simulation version to match different

approximated reset sequence is used to speed up the reset time for

simulations, where faster reset times and faster simulation times are

desirable. If the SIM_RESET_SPEEDUP attribute is set to FALSE, the

model emulates hardware reset behavior in detail.

versions of silicon. The default for this attribute is ULTRASCALE_PLUS.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 10

Page 11

Chapter 1: Transceiver and Tool Overview

Send Feedback

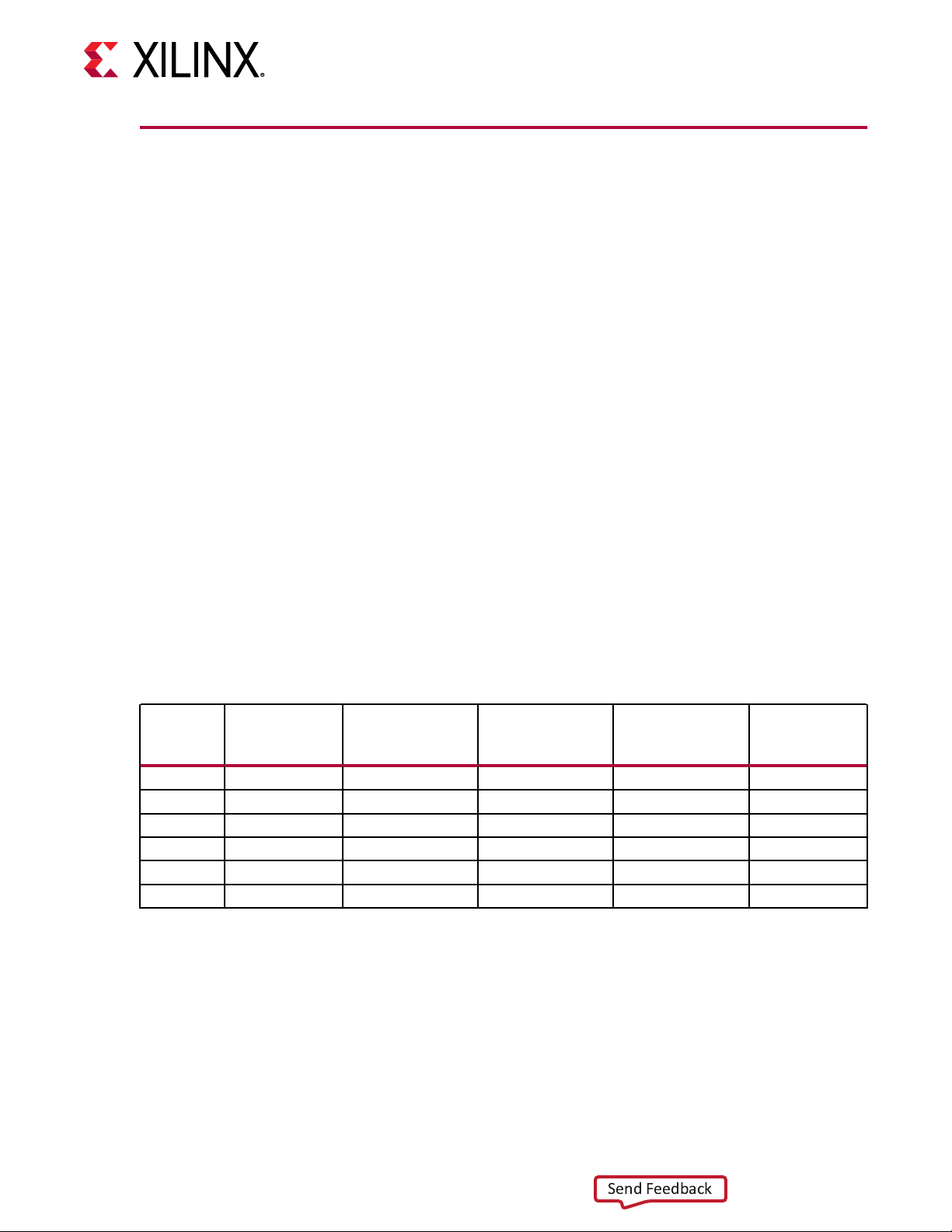

Implementation

It is a common pracce to dene the locaon of GTM transceiver Duals early in the design

process to ensure correct usage of clock resources and to facilitate signal integrity analysis during

board design. The implementaon ow facilitates this pracce through the use of locaon

constraints in the XDC le.

The posion of each GTM transceiver Dual primive is specied by an XY coordinate system that

describes the column number and the relave posion within that column. For a given device/

package combinaon, the transceiver with the coordinates X0Y0 is located at the lowest posion

of the lowest available bank.

There are two ways to create an XDC le for designs that ulize the GTM transceivers. The

preferred method is to use the UltraScale+ FPGAs GTM Transceivers Wizard. The Wizard

automacally generates XDC le templates that congure the transceivers and contain

placeholders for GTM transceiver placement informaon. The XDC les generated by the Wizard

can then be edited to customize operang parameters and placement informaon for the

applicaon.

The second approach is to create the XDC le manually. When using this approach, you must

enter both conguraon aributes that control transceiver operaon as well as the locaon

parameters. Care must be taken to ensure that all of the parameters needed to congure the

GTM transceiver are correctly entered. A GTM_DUAL primive must be instanated as shown in

the following gure.

Figure 3: One-Dual, Two-Channel Configuration (Reference Clock from the LCPLL)

GTM_DUAL

GTM Channel 0 (CH0)

TX

IBUFDS_GTM

LCPLL

GTM Channel 1 (CH1)

RX

TX

RX

X20212-061418

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 11

Each dual contains an LCPLL. Therefore, a reference clock can be connected directly to a

GTM_DUAL primive.

Page 12

Shared Features

Send Feedback

Reference Clock Input/Output Structure

The reference clock structure in the GTM transceiver supports two modes of operaon: input

mode and output mode. In the input mode of operaon, your design provides a clock on the

dedicated reference clock I/O pins that are used to drive the LCPLL. In the output mode of

operaon, the recovered clocks (RXRECCLK0 and RXRECCLK1) from any of the two channels

within the same Dual can be routed to the dedicated reference clock I/O pins. This output clock

can then be used as the reference clock input at a dierent locaon. The mode of operaon

cannot be changed during run me.

Chapter 2: Shared Features

Chapter 2

Input Mode

The reference clock input mode structure is illustrated in the following gure. The input is

terminated internally with 50Ω on each leg to MGTAVCC. The reference clock is instanated in

soware with the IBUFDS_GTM soware primive. The ports and aributes controlling the

reference clock input are ed to the IBUFDS_GTM soware primive.

Figure 4: Reference Clock Input Structure

MGTAVCC

GTREFCLKP

GTREFCLKN

CEB

I

IB

Nominal

50Ω

Nominal

50Ω

+

-

IBUFDS_GTM

MGTAVCC

/2

1'b0

Reserved

To GTREFCLK or

GTM_DUAL

2'b00

2'b01

2'b10

2'b11

To

HROW

O

ODIV2

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 12

REFCLK_HROW_CK_SEL

X20917-061418

Page 13

Chapter 2: Shared Features

Send Feedback

Ports and Attributes

The following table denes the reference clock input ports in the IBUFDS_GTM soware

primive.

Table 3: Reference Clock Input Ports (IBUFDS_GTM)

Port Dir Clock Domain Description

CEB In N/A This is the active-Low asynchronous clock enable signal for the clock buffer.

I In (pad) N/A These are the reference clock input ports that get mapped to GTREFCLKP.

IB In (pad) N/A These are the reference clock input ports that get mapped to GTREFCLKN.

O Out N/A This output drives the GTREFCLK signal in the GTM_DUAL software primitive.

ODIV2 Out N/A This output can be configured to output either the O signal or a divide-by-2

Setting this signal High powers down the clock buffer.

Refer to Reference Clock Selection and Distribution for more details.

version of the O signal. It can drive the BUFG_GT via the HROW routing. Refer

to Reference Clock Selection and Distribution for more details.

The following table denes the aributes in the IBUFDS_GTM soware primive that congure

the reference clock input.

Table 4: Reference Clock Input Attributes (IBUFDS_GTM)

Attribute Type Description

REFCLK_EN_TX_PATH 1-bit Reserved. This attribute must always be set to 1'b0.

REFCLK_HROW_CK_SEL 2-bit Configures the ODIV2 output port:

2'b00: ODIV2 = O.

2'b01: ODIV2 = Divide-by-2 version of O.

2'b10: ODIV2 = 1'b0.

2'b11: ODIV2 = Reserved.

REFCLK_ICNTL_RX

2-bit Reserved. Use the recommended value from the Wizard.

Output Mode

The reference clock output mode can be accessed via the OBUFDS_GTM soware primive. The

reference clock output mode structure for the OBUFDS_GTM primive is shown in the following

gure. The ports and aributes controlling the reference clock output are ed to the

OBUFDS_GTM soware primive.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 13

Page 14

Chapter 2: Shared Features

Send Feedback

Figure 5: Reference Clock Output Use Model for OBUFDS_GTM

MGTAVCC

GTREFCLKP

GTREFCLKN

O

OB

OBUFDS_GTM

From RXRECCLK0/1

of GTM_DUAL

I

CEB

X20877-061418

Ports and Attributes

The following table denes the ports in the OBUFDS_GTM soware primive.

Table 5: Reference Clock Output Ports (OBUFDS_GTM)

Port Dir Clock Domain Description

CEB In N/A This is the active-Low asynchronous clock enable signal for the clock buffer.

I In (pad) N/A Recovered clock input. Connect to the output port RXRECCLK0/1 of the

O In (pad) N/A Reference clock output port that gets mapped to GTREFCLKP.

OB Out N/A Reference clock output port that gets mapped to GTREFCLKN.

Setting this signal High powers down the clock buffer.

GTM_DUAL primitive.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 14

The following table denes the aributes in the OBUFDS_GTM soware primive that congure

the reference clock output.

Table 6: Reference Clock Output Attributes (OBUFDS_GTM)

Attribute Type Description

REFCLK_EN_TX_PATH 1-bit Reserved. This attribute must always be set to 1’b1.

REFCLK_ICNTL_TX 5-bit Reserved. Use the recommended value from the Wizard.

Reference Clock Selection and Distribution

The GTM transceivers in Virtex UltraScale+ FPGAs provide dierent reference clock input

opons. Clock selecon and availability is similar to the GTY transceivers in UltraScale+ devices,

but the reference clock selecon architecture supports only one LCPLL shared per Dual (two

GTM transceiver channels).

Page 15

Chapter 2: Shared Features

Send Feedback

From an architecture perspecve, a Dual contains a grouping of two GTM channels inside one

GTM_DUAL primive, one dedicated external reference clock pin pair, and dedicated reference

clock roung. The reference clock for a GTM_DUAL primive must also be instanated. For duals

operang at line rates lower than 16.3725 Gb/s (NRZ) and 32.7 Gb/s (PAM4), the reference clock

for a Dual can also be sourced from the Dual above via GTNORTHREFCLK or from the Dual

below via GTSOUTHREFCLK. For devices that support stacked silicon interconnect (SSI)

technology, the reference clock sharing via the GTNORTHREFCLK and GTSOUTHREFCLK ports

is limited within its own super logic region (SLR). Duals operang at line rates above

16.3725 Gb/s (NRZ) and 32.7 Gb/s (PAM4) should not source a reference clock from another

Dual.

See the UltraScale device data sheets (see hp://www.xilinx.com/documentaon) for more

informaon about SSI technology.

Reference clock features include:

• Clock roung for northbound and southbound clocks.

• Flexible clock inputs available for the LCPLL.

• Stac or dynamic selecon of the reference clock for the LCPLL.

The Dual architecture has two GTM transceivers, one dedicated reference clock pin pair, and

dedicated north and south reference clock roung. Each GTM dual has three clock pair inputs

available:

• One local reference clock pin pair, GTREFCLK.

• One reference clock pin pair for the Dual above, GTSOUTHREFCLK.

• One reference clock pin pair from the Dual below, GTNORTHREFCLK.

The gure below shows the detailed view of a reference clock mulplexer structure within a

single GTM_DUAL primive. The PLLREFCLKSEL port is required when mulple reference clock

sources are connected to this mulplexer. A single reference clock is most commonly used. In the

case of a single reference clock, connect the reference clock to the GTREFCLK ports and e the

PLLREFCLKSEL ports to 3’b001. The Xilinx soware tools handle the complexity of the

mulplexers and associated roung.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 15

Page 16

Chapter 2: Shared Features

Send Feedback

Figure 6: LCPLL Reference Clock Selection Multiplexer

0

1

2

3

4

5

6

7

GTM_DUAL

LCPLL

LCPLL Output CLK

X20897-061418

PLLREFCLKSEL

GTREFCLK

GTNORTHREFCLK

GTSOUTHREFCLK

GTGREFCLK2PLL

Single External Reference Clock Use Model

Each Dual has one set of dedicated dierenal reference clock input pins (MGTREFCLK[P/N])

that can be connected to the external clock sources. In a single external reference clock use

model, an IBUFDS_GTM must be instanated to use the dedicated dierenal reference clock

source. The following gure shows a single external reference clock connected to the LCPLL

inside the Dual. The user design connects the IBUFDS_GTM output (O) to the GTREFCLK ports

of GTM_DUAL.

Figure 7: Single External Reference Clock in a Dual

IBUFDS_GTM

GTM_DUAL

MGTREFCLKP

MGTREFCLKN

I

O

IB

GTREFCLK

X20898-061418

Note: The IBUFDS_GTM diagram in the above gure is a simplicaon. The output port ODIV2 is le

oang, and the input port CEB is set to logic 0.

The following gure shows a single external reference clock with mulple Duals connected. The

user design connects the IBUFDS_GTM output (O) to the GTREFCLK ports of the GTM_DUAL

primives. In this case, the Xilinx implementaon tools make the necessary adjustments to the

north/south roung as well as the pin swapping necessary to route the reference clock from one

Dual to another when required.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 16

Page 17

Chapter 2: Shared Features

Send Feedback

Figure 8: Single External Reference Clock with Multiple Duals

D(n+1)

GTM_DUAL

GTREFCLK

D(n)

GTM_DUAL

GTREFCLK

D(n-1)

GTM_DUAL

GTREFCLK

X20215-061418

MGTREFCLKP

MGTREFCLKN

IBUFDS_GTM

I

O

IB

Note: The IBUFDS_GTM diagram in the above gure is a simplicaon. The output port ODIV2 is le

oang, and the input port CEB is set to logic 0.

These rules must be observed when sharing a reference clock to ensure that jier margins for

high-speed designs are met:

• The number of Duals above the sourcing Dual must not exceed one.

• The number of Duals below the sourcing Dual must not exceed one.

• The total number of Duals sourced by an external clock pin pair (MGTREFCLKP/

MGTREFCLKN) must not exceed three Duals.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 17

The maximum number of Duals that can be sourced by a single clock pin pair is three (six

transceivers). Designs with more than three Duals require the use of mulple external clock pins

to ensure that the rules for controlling jier are followed. When mulple clock pins are used, an

external buer can be used to drive them from the same oscillator.

IMPORTANT

! Upon device conguraon, the clock output from the IBUFDS_GTM which takes inputs

from MGTREFCLKP and MGTREFCLKN can only be used as long as the GTPOWERGOOD signal has

already asserted High.

Ports and Attributes

The following table denes the clocking ports and aributes for the GTM_DUAL primive.

Page 18

Table 7: GTM_DUAL Clocking Ports

Send Feedback

Chapter 2: Shared Features

Port

PLLREFCLKSEL[2:0] In Async Input to dynamically select the input reference clock to the

GTGREFCLK2PLL In Clock Reference clock generated by the internal interconnect logic.

GTREFCLK In Clock External clock driven by IBUFDS_GTM for the LCPLL.

GTNORTHREFCLK In Clock Northbound clock from the Dual below.

GTSOUTHREFCLK In Clock Southbound clock from the Dual above.

PLLREFCLKLOST Out Async A High on this signal indicates that the reference clock to the

PLLREFCLKMONITOR Out Clock LCPLL reference clock selection multiplexer output.

Direct

ion

Clock

Domain

Description

LCPLL. Set this input to 3’b001 and connect to GTREFCLK when

only one clock source is connected to the PLL reference clock

selection multiplexer:

3’b000: Reserved.

3’b001: GTREFCLK selected.

3’b010: Reserved.

3’b011: GTNORTHREFCLK selected.

3’b100: Reserved.

3’b101: GTSOUTHREFCLK.

3’b110: Reserved.

3’b111: GTGREFCLK2PLL.

This input is reserved for internal testing purposes only.

phase frequency detector of the LCPLL is lost.

LCPLL

Each Dual contains one LC-based PLL, referred to as LCPLL, and cannot be shared with

neighboring Duals. The internal clocking architecture of the GTM Dual is shown in the following

gure.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 18

Page 19

REFCLK Distribution

Send Feedback

Chapter 2: Shared Features

Figure 9: Internal Dual Clocking Architecture

GTM_DUAL

GTM Channel 0 (CH0)

TX PMA

TX PCS

RX PMA

RX PCS

LCPLL

GTM Channel 1 (CH1)

TX PMA

TX PCS

RX PMA

RX PCS

X20900-061418

The LCPLL input clock selecon is described in Reference Clock Selecon and Distribuon. The

LCPLL outputs feed the TX and RX clock divider blocks, which control the generaon of serial

and parallel clocks used by the PMA and PCS blocks. The LCPLL is shared between the TX and

RX datapaths.

The gure below illustrates a conceptual view of the LCPLL architecture. The input clock can be

divided by a factor of M before it is fed into the phase frequency detector. The feedback divider

N determines the voltage-controlled oscillator (VCO) mulplicaon rao. For line rates below

28.1 Gb/s (NRZ) and 56.2 Gb/s (PAM4), a fraconal-N divider is supported where the eecve

rao is a combinaon of the N factor plus a fraconal part. The LCPLL output frequency depends

on the sengs of LCPLLCLKOUT_RATE. When LCPLLCLKOUT_RATE is set to HALF, the output

frequency is half of the VCO frequency. When it is set to FULL, the output frequency is the same

as the VCO frequency. A lock indicator block compares the frequencies of the reference clock

and VCO feedback clock to determine if a frequency lock has been achieved.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 19

Page 20

PLL

f

PLLClkout

= f

PLLClkin

*

N + FractionalDivider

M*LCPLLCLKOUT _ RATE

f

LineRate

= f

PLLClkout

*Modulation

FractionalDivider = N

SDM

+ 0. < FractionalPart >

FractionalPart

=

SDMDAT A

2

SDMW IDTH

Send Feedback

CLKIN

/M

Figure 10: Internal Dual Clocking Architecture

Lock

Indicator

Phase

Frequency

Detector

Charge

Pump

Loop

Filter

VCO

/2

Chapter 2: Shared Features

PLL

LOCKED

PLL

CLKOUT

/N-Fractional

LCPLLCLKOUT_RATE

The LCPLL VCO operates within 9.8 GHz—14.5 GHz. The Xilinx soware tool chooses the

appropriate LCPLL seng based on applicaon requirements. Equaon 2-1 shows how to

determine the PLL output frequency (GHz).

Equaon 2-2 shows how to determine the line rate (Gb/s).

Equaon 2-3 and Equaon 2-4 show how to determine the fraconal divider presented in

Equaon 2-1.

X20901-052418

The table below lists the allowable values.

Table 8: LCPLL Divider Settings

M LCPLL_REFCLK_DIV 1, 2, 3, 4

N PLLFBDIV[7:0] 16–160 (Integer only)

LCPLLCLKOUT_RATE LCPLLCLKOUT_RATE 1'b1: 1 (Full), 1'b0: 2 (Half)

Modulation See TX Configurable Driver 2 (NRZ), 4 (PAM4)

N

SDM

SDMDATA SDMDATA[SDMWIDTH – 1:0] Fractional part of fractional divider.

SDMWIDTH SDM_WIDTHSEL 16, 20, 24

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 20

Factor Attribute or Port Valid Settings

SDMDATA[SDMWIDTH + 1:SDMWIDTH] Integer part of fractional divider. (Two’s

complement) –2, –1, 0, 1

0 – (224 – 1)

Page 21

Ports and Attributes

Send Feedback

The following tables dene the LCPLL ports and aributes, respecvely.

Table 9: LCPLL Ports

Chapter 2: Shared Features

Port Direction

GTGREFCLK2PLL In Clock Reference clock generated by the internal interconnect

PLLFBCLKLOST Out PLLMONCLK A High on this signal indicates the feedback clock from the

PLLFBDIV[7:0] In Async PLL feedback divider selection. Actual feedback divider value

PLLLOCK Out Async This active-High LCPLL frequency lock signal indicates that

PLLMONCLK In Clock Stable reference clock for the detection of the feedback and

PLLPD

PLLREFCLKLOST Out PLLMONCLK A High on this signal indicates the reference clock to the

PLLREFCLKMONITOR Out Clock PLL reference clock selection multiplexer output.

PLLRESET In Async This port is driven High and then deasserted to start the

PLLRESETBYPASSMODE In Async Reserved. Tied Low.

PLLRESETDONE Out cfg_mclk Status signal that indicates when the PLL reset sequence is

PLLRESETMASK[1:0] In Async Bit 0 enables bit mask for PLL reset. Bit 1 enables bit mask

PLLRSVDIN[15:0] In Reserved Reserved. This port must be set to 0x0000.

PLLRSVDOUT Out Async Reserved.

BGBYPASSB In Async Reserved. This port must be set to 1’b1. Do not modify this

BGMONITORENB In Async Reserved. This port must be set to 1’b1. Do not modify this

BGPDB In Async Reserved. This port must be set to 1’b1. Do not modify this

BGRCALOVRD[4:0] In Async Reserved. This port must be set to 5’b11111. Do not modify

BGRCALOVRDENB In Async Reserved. This port must be set to 1’b1. Do not modify this

In Async An active-High signal powers down the LCPLL.

Clock

Domain

Description

logic. This input is reserved for internal testing purposes.

LCPLL feedback divider to the phase frequency detector of

the LCPLL is lost

is PLLFBDIV + 2. Valid values are from 14–158. (Actual divider

values are 160–160.)

the LCPLL frequency is within a predetermined tolerance.

The transceiver and its clock outputs are not reliable until

this condition is met.

reference clock signals to the LCPLL. The input reference

clock to the LCPLL or any output clock generated from the

LCPLL must not be used to drive this clock. This clock is

required only when using the PLLFBCLKLOST and

PLLREFCLKLOST ports. It does not affect the LCPLL lock

detection, reset, and power-down functions.

phase frequency detector of the LCPLL is lost.

LCPLL reset.

complete.

for PLL SDM reset.

value.

value.

value.

this value.

value.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 21

Page 22

Table 9: LCPLL Ports (cont'd)

Send Feedback

Chapter 2: Shared Features

Port Direction

RCALEN In Async Reserved. This port must be set to 1’b1. Do not modify this

SDMDATA[25:0] In Async Input to set the Fractional Divider. Bits [SDMWIDTH +

SDMTOGGLE In Async Reserved. Set to 1’b0.

Clock

Domain

Description

value.

1:SDMWIDTH] are the integer part of the divider in two’s

complement. Bits [SDMWIDTH – 1:SDMWIDTH] set the

fractional part of the divider.

Table 10: LCPLL Attributes

Attributes Type Description

BIAS_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

BIAS_CFG1 16-bit Reserved. Use the recommended value from the Wizard.

BIAS_CFG2 16-bit Reserved. Use the recommended value from the Wizard.

BIAS_CFG3 16-bit Reserved. Use the recommended value from the Wizard.

BIAS_CFG4 16-bit Reserved. Use the recommended value from the Wizard.

A_CFG 16-bit Reserved. Use the recommended value from the Wizard.

CRS_CTRL_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

CRS_CTRL_CFG1 16-bit Reserved. Use the recommended value from the Wizard.

DRPEN_CFG 16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

Bit Name Address Description

LCPLLCLKOUT_RATE [8] Sets the LCPLLCLKOUT_RATE factor either to provide full

LCPLL VCO frequency, or half of LCPLL VCO frequency at the

output:

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 22

1'b0: Half rate.

1'b1: Full rate.

PLL_CFG1

Bit Name Address Description

LCPLL_REFCLK_DIV [4:0] LCPLL reference clock divider M settings.

PLL_CFG2

PLL_CFG3 16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG4 16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG5 16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG6 16-bit Reserved. Use the recommended value from the Wizard.

16-bit Reserved. Use the recommended value from the Wizard.

5'b00000: Div by 2.

5'b00001: Div by 3.

5'b00010: Div by 4.

5'b10010: Div by 1.

Other values are not valid.

16-bit Reserved. Use the recommended value from the Wizard.

Page 23

Chapter 2: Shared Features

Send Feedback

Table 10: LCPLL Attributes (cont'd)

Attributes Type Description

SDM_CFG0[15:0] 16-bit Reserved. Use the recommended value from the Wizard.

Bit Name Address Description

SDM_WIDTHSEL [10:9] This attribute sets the denominator of the fractional part of

the feedback divider:

2'b00: 24 bits.

2'b01: 20 bits.

2'b10: 16 bits.

2'b11: Reserved.

SDM_CFG1

SDM_CFG2 16-bit Reserved. Use the recommended value from the Wizard.

SDM_SEED_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

SDM_SEED_CFG1 16-bit Reserved. Use the recommended value from the Wizard.

A_SDM_DATA_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

A_SDM_DATA_CFG1 16-bit Reserved. Use the recommended value from the Wizard.

16-bit Reserved. Use the recommended value from the Wizard.

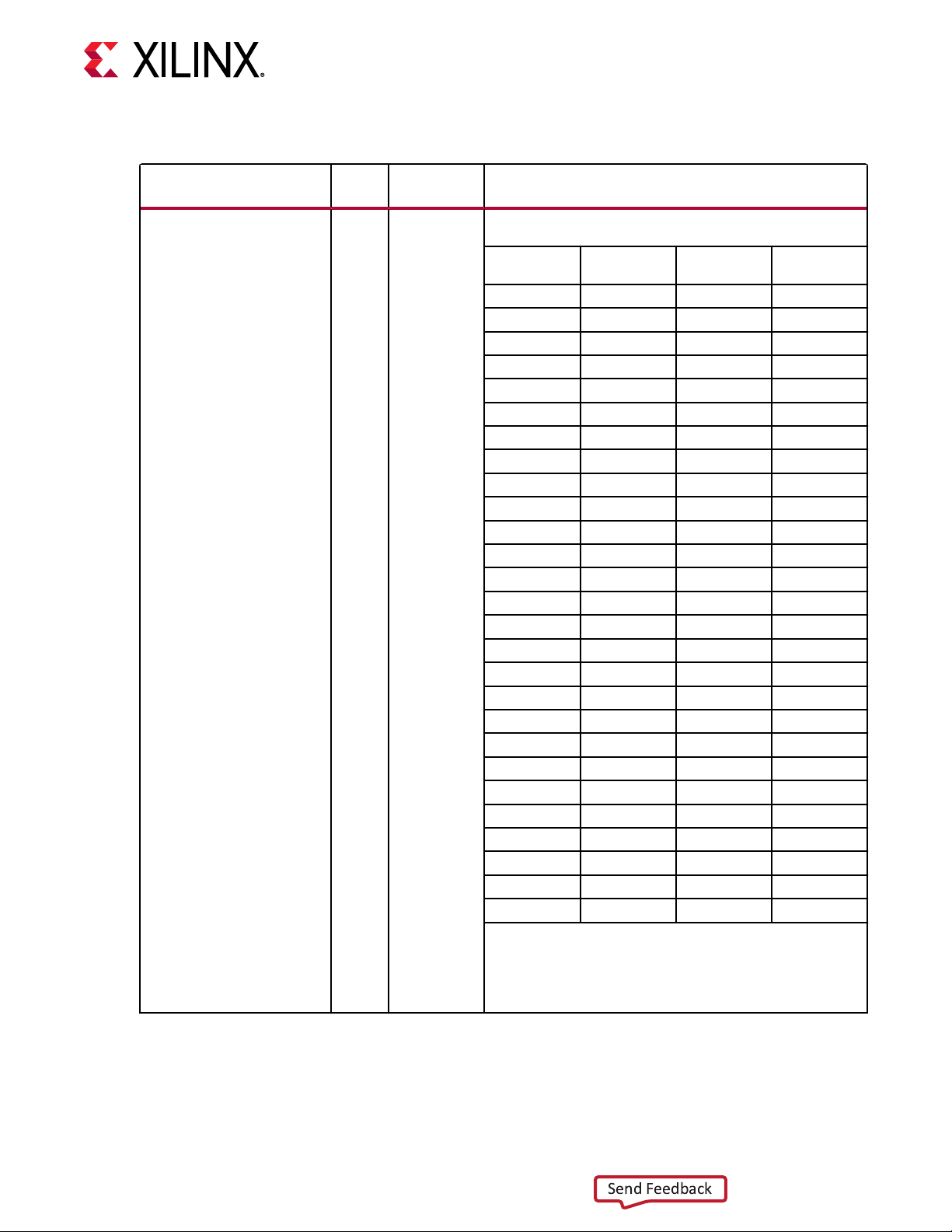

Reset and Initialization

The GTM transceiver must be inialized aer device power-up and conguraon before it can be

used. The GTM transmier (TX) and receiver (RX) can be inialized independently and in parallel

as shown in the following gure. The GTM transceiver TX and RX inializaon comprises three

steps:

1. Inializing the associated PLL driving TX/RX

2. Inializing the TX and RX datapaths (PMA + PCS)

The TX and RX in the GTM transceiver receive the clock through the LCPLL in the transceiver's

own Dual. In the power-on inializaon sequence, the LCPLL used by the TX and RX must be

inialized rst. The LCPLL used by the TX and RX is reset individually and its reset operaon

independent from TX and RX resets. The TX and RX datapaths must be inialized only aer the

associated LCPLL is locked.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 23

Page 24

Chapter 2: Shared Features

Send Feedback

Figure 11: GTM Transceiver Initialization Overview

After Configuration

LCPLL Reset

TX Initialization by

GTTXRESET

RX Initialization by

GTRXRESET

RXRESETDONETXRESETDONE

X20903-052818

The GTM transceiver TX and RX use a state machine to control the inializaon process. They

are paroned into a few reset regions. The paron allows the reset state machine to control

the reset process in a sequence that the PMA can be reset rst and the PCS can be reset aer

the asseron of the TXUSERRDY or RXUSERRDY. It also allows the PMA, the PCS, and

funconal blocks inside them to be reset individually when needed during normal operaon.

The GTM transceiver oers two types of reset: inializaon and component.

• Inializaon Reset: This reset is used for complete GTM transceiver inializaon. It must be

used aer device power-up and conguraon. During normal operaon, when necessary,

GTTXRESET and GTRXRESET can also be used to reinialize the GTM transceiver TX and RX.

GTTXRESET is the inializaon reset port for the GTM transceiver TX. GTRXRESET is the

inializaon reset port for the GTM transceiver RX. During inializaon reset,

TXRESETMODE and RXRESETMODE should be set to sequenal mode. All TX PMA, TX PCS,

RX PMA, and RX PCS component resets should be enabled by seng all required component

bits of TXPMARESETMASK, TXPCSRESETMASK, RXPMARESETMASK, and

RXPCSRESETMASK to High.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 24

• Component Reset: This reset is used for special cases and specic subsecon resets while the

GTM transceiver is in normal operaon. The component that is required to be reset is selected

by seng the associated bit within TXPMARESETMASK, TXPCSRESETMASK,

RXPMARESETMASK, or RXPCSRESETMASK to High. A TX component reset is triggered by

toggling the GTTXRESET port. An RX component reset is triggered by toggling the

GTRXRESET port. Separate component reset ports are available. For the TX, these are

TXCKALRESET, TXFECRESET, TXPCSRESET, and TXPMARESET. For the RX, these are

RXADAPTRESET, RXADCCLKGENRESET, RXBUFRESET, RXCDRFRRESET, RXCDRPHRESET,

RXDFERESET, RXDSPRESET, RXEYESCANRESET, RXFECRESET, RXPCSRESET,

RXPMARESET, and RXPRBSCSCNTRST.

Page 25

Chapter 2: Shared Features

Send Feedback

All reset ports described in this secon iniate the internal reset state machine when driven

High. The internal reset state machines are held in the reset state unl these same reset ports are

driven Low. These resets are all asynchronous. The guideline for the pulse width of these

asynchronous resets is one period of the reference clock, unless otherwise noted.

Note: Do not use reset ports for the purpose of power down. For details on proper power-down usage,

refer to Power Down.

Resetting Multiple Lanes and Quads

Reseng mulple lanes in a Dual or mulple Duals aects the power supply regulaon circuit.

Reset Modes

The GTM transceiver TX and RX resets can operate in two dierent modes: sequenal mode and

single mode.

• Sequenal mode: The reset state machine starts with an inializaon or component reset

input driven High and proceeds through all states aer the requested reset states in the reset

state machine, as shown in Figure 13 for the GTM transceiver TX or Figure 18 for the GTM

transceiver RX unl compleon. The compleon of sequenal mode reset ow is signaled

when (TX/RX)RESETDONE transions from Low to High.

• Single mode: The reset state machine only executes the requested component reset

independently for a predetermined me set by its aribute. It does not process any state aer

the requested state, as shown in Figure 13 for the GTM transceiver TX or Figure 18 for the

GTM transceiver RX. The requested reset can be any component reset to reset the PMA, the

PCS, or funconal blocks inside them. The compleon of a single mode reset is signaled when

(TX/RX)RESETDONE transions from Low to High.

The GTM transceiver inializaon reset must use sequenal mode. All component resets can be

operated in either sequenal mode or single mode. The GTM transceiver uses (TX/

RX)RESETMODE to select between sequenal reset mode and single reset mode. The following

table provides conguraon details that apply to both the GTM transceiver TX and GTM

transceiver RX. Reset modes have no impact on LCPLL reset. During normal operaon, the GTM

transceiver TX or GTM transceiver RX can be reset by applicaons in either sequenal mode or

single mode (GTM transceiver RX only), which provides exibility to reset a poron of the GTM

transceiver. When using either sequenal mode or single mode, (TX/RX)RESETMODE must be

set to the desired value of 50 ns before the asserons of any reset.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 25

Table 11:

GTM Transceiver Reset Modes Operation

Operation Mode (TX/RX)RESETMODE

Sequential Mode

Single Mode

2'b00

2'b11

Page 26

Table 12: GTM Transceiver Reset Modes Ports

Send Feedback

Port Direction Clock Domain Description

CH[0/1]_RXRESETMODE[1:0] In Async Reset mode port for RX.

2'b00: Sequential mode

(recommended).

2'b01: Reserved.

2'b10: Reserved.

2'b11: Single mode.

Chapter 2: Shared Features

CH[0/1]_TXRESETMODE[1:0]

In Async Reset mode port for TX.

2'b00: Sequential mode

(recommended).

2'b01: Reserved.

2'b10: Reserved.

2'b11: Single mode.

LCPLL Reset

The LCPLL must be reset before it can be used. Each GTM transceiver dual has dedicated reset

ports for its LCPLL. As shown in the gure, PLLRESET is an input that resets LCPLL. PLLLOCK is

an output that indicates the reset process is done. The guideline for this asynchronous PLLRESET

pulse width is one period of the reference clock. Aer a PLLRESET pulse, the internal reset

controller generates an internal LCPLL reset followed by an internal SDM reset. The me

required for LCPLL to lock is aected by a few factors, such as bandwidth seng and clock

frequency.

Figure 12: LCPLL Reset Timing Diagram

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 26

Table 13: LCPLL Reset Ports

Port Dir

PLLRESET In Async Active-High signal that resets the LCPLL.

PLLRESETMASK[1:0] In Async Reserved. Tied to 2’b11.

PLLRESETBYPASSMODE In Async Reserved. Tied Low.

PLLLOCK Out Async Active-High LCPLL frequency lock signal indicates that the

Clock

Domain

Description

LCPLL frequency is within a predetermined tolerance. The

GTM transceiver and its clock outputs are not reliable until

this condition is met.

Page 27

Chapter 2: Shared Features

Send Feedback

TX Initialization and Reset

The GTM transceiver TX uses a reset state machine to control the reset process. The GTM

transceiver TX is paroned into two reset regions, TX PMA and TX PCS. The paron allows TX

inializaon and reset to be operated only in sequenal mode, as shown in the gure below.

The inializing TX must use GTTXRESET in sequenal mode. Acvang the GTTXRESET input

can automacally trigger a full asynchronous TX reset. The reset state machine executes the

reset sequence, as shown in the gure below, covering the whole TX PMA and TX PCS. During

normal operaon, when needed, sequenal mode allows you to reset the TX from acvang

TXPMARESET and connue the reset state machine unl TXRESETDONE transions from Low

to High.

The TX reset state machine does not reset the PCS unl TXUSERRDY is detected High. Drive

TXUSERRDY High aer all clocks used by the applicaon including TXUSRCLK are shown as

stable.

Figure 13: GTM Transceiver TX Reset State Machine Sequence

GTTXRESET

High

Wait until

GTTXRESET from

High to Low

TXPMARESETMASK[0]

= 1?

No

TXPMARESETMASK[1]

= 1?

No

Wait for TXUSERRDY

= 1

Yes

Yes

TX CKCAL Reset

TX PMA Top Reset

TXPCSRESETMASK[0]

= 1?

No

TXPCSRESETMASK[1]

= 1?

No

TXRESETDONE High

Yes

Yes

TX FEC Reset

TX PCS Top Reset

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 27

X20905-060518

Page 28

Ports and Attributes

Send Feedback

The table below lists ports required by the TX inializaon process.

Table 14: TX Initialization and Reset Ports

Chapter 2: Shared Features

Port Dir

CH[0/1]_GTTXRESET In Async This port is driven High and then deasserted to start a TX reset

CH[0/1]_TXRESETMODE[1:0]

CH[0/1]_TXPMARESETMASK[1:0]

CH[0/1]_TXPCSRESETMASK[1:0] In Async TX PCS reset mask selection

CH[0/1]_TXUSERRDY In Async This port is driven High by the user application when TXUSRCLK

CH[0/1]_TXPMARESETDONE Out Async This active-High signal indicates TX PMA reset is complete.

CH[0/1]_TXRESETDONE Out TXUSRCLK This active-High signal indicates the GTM transceiver TX has

CH[0/1]_ TXCKALRESET In Async This port is driven High and then deasserted to start a single

CH[0/1]_ TXPMARESET In Async This port is driven High and then deasserted to start a single

CH[0/1]_ TXFECRESET In Async This port is driven High and then deasserted to start a single

CH[0/1]_ TXPCSRESET In Async This port is driven High and then deasserted to start a single

In Async Reset mode port for TX:

In Async TX PMA reset mask selection:

Clock

Domain

Description

sequence. The components to be reset are determined by

TXPMARESETMASK and TXPCSRESETMASK. In sequential mode,

the resets are performed sequentially. In single mode, the

resets are performed simultaneously.

2’b00: Sequential mode (recommended).

2’b01: Reserved.

2’b10: Reserved.

2’b11: Single mode.

Bit 1: TX PMA.

Bit 0: CKCAL.

Bit 1: TX PCS.

Bit 0: TX FEC.

is stable.

finished reset and is ready for use. This port is driven Low when

GTTXRESET goes High and is not driven High until the GTM

transceiver has completed all TX reset steps.

mode reset on TX CKCAL. The reset is not dependent on

TXRESETMODE or TXPMARESETMASK setting.

mode reset on TX PMA. The reset is not dependent on

TXRESETMODE or TXPMARESETMASK setting.

mode reset on TX FEC. The reset is not dependent on

TXRESETMODE or TXPCSRESETMASK setting.

mode reset on TX PCS. The reset is not dependent on

TXRESETMODE or TXPCSRESETMASK setting.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 28

Page 29

Chapter 2: Shared Features

Send Feedback

The following table lists aributes required by GTM transceiver TX inializaon. In general cases,

the reset me required by the TX PMA or the TX PCS varies depending on line rate. The factors

aecng PMA reset me and PCS reset me are the user-congurable aributes

TX_PMA_RESET_TIME, TX_PCS_RESET_TIME, TX_CKCAL_RESET_TIME, and

TX_FEC_RESET_TIME.

Table 15: TX Initialization and Reset Attributes

Attribute Type Description

CH[0/1]_RST_TIME_CFG0 16-bit Reserved.

Bit Name Address Description

TX_PCS_RESET_TIME [14:10] Represents the time duration to apply a TX PCS reset. Use

TX_PMA_RESET_TIME [9:5] Represents the time duration to apply a TX PMA reset. Use

TX_CKCAL_RESET_TIME [4:0] Represents the time duration to apply a TX CLKGEN reset.

CH[0/1]_RST_TIME_CFG1 16-bit Reserved.

Bit Name Address Description

TX_FEC_RESET_TIME [4:0] Represents the time duration to apply a TX CKCAL reset.

CH[0/1]_RST_LP_CFG0 16-bit Reserved.

Bit Name Address Description

TX_PCS_RESET_LOOP_ID [11:8] Reserved. Use the recommended value from the Wizard.

TX_PMA_RESET_LOOP_ID [7:4] Reserved. Use the recommended value from the Wizard.

TX_CKCAL_RESET_LOOP_ID [3:0] Reserved. Use the recommended value from the Wizard.

TX_FEC_RESET_LOOP_ID [15:12] Reserved. Use the recommended value from the Wizard.

CH[0/1]_RST_LP_ID_CFG1 16-bit Reserved.

Bit Name Address Description

TX_PCS_LOOPER_END_ID [15:12] Reserved. Use the recommended value from the Wizard.

TX_PCS_LOOPER_START_ID [11:8] Reserved. Use the recommended value from the Wizard.

TX_PMA_LOOPER_END_ID [7:4] Reserved. Use the recommended value from the Wizard.

TX_PMA_LOOPER_START_ID [3:0] Reserved. Use the recommended value from the Wizard.

CH[0/1]_RST_LP_CFG4 1-bit Reserved.

Bit Name Address Description

BYP_HDSHK_TX_PCS_RESET_LOOP [3] Reserved. Use the recommended value from the Wizard.

BYP_HDSHK_TX_CKCAL_RESET_LOOP [0] Reserved. Use the recommended value from the Wizard.

the recommended value from the Wizard. Must be a nonzero value when TXPCSRESETMASK[1] is High and

GTTXRESET initiates the reset process.

the recommended value from the Wizard. Must be a nonzero value when TXPMARESETMASK[1] is High and

GTTXRESET initiates the reset process.

Use the recommended value from the Wizard. Must be a

non-zero value when TXPMARESETMASK[0] is High and

GTTXRESET initiates the reset process.

Use the recommended value from the Wizard. Must be a

non-zero value when TXPMARESETMASK[0] is High and

GTTXRESET initiates the reset process.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 29

Page 30

Chapter 2: Shared Features

Send Feedback

GTM Transceiver TX Reset in Response to Completion of Configuration

The TX reset sequence shown in TX Inializaon and Reset is not automacally started to follow

global GSR. It must meet these condions:

1. TXRESETMODE must be set to sequenal mode.

2. GTTXRESET must be used.

3. All TXPMARESETMASK and TXPCSRESETMASK bits should be set to High.

4. GTTXRESET cannot be driven Low unl the associated PLL is locked.

5. Ensure that GTPOWERGOOD is High before releasing PLLRESET and GTTXRESET.

If the reset mode is defaulted to single mode, then you must:

1. Wait another 300–500 ns.

2. Assert PLLRESET and GTTXRESET following the reset sequence described in the following

gure.

RECOMMENDED: Use the associated PLLLOCK from the PLL to release GTTXRESET from High to

Low as shown in the gure. The TX reset state machine waits when GTTXRESET is detected High and

starts the reset sequence unl GTTXRESET is released Low.

Figure 14: GTM Transmitter Initialization after Configuration

GTM Transceiver TX Reset in Response to GTTXRESET Pulse in Full Sequential Reset

The GTM transceiver allows you to reset the enre TX completely at any me by sending

GTTXRESET an acve-High pulse. These condions must be met when using GTTXRESET:

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 30

1. TXRESETMODE must be set to sequenal mode.

2. All TXPMARESETMASK and TXPCSRESETMASK bits should be held High during the reset

sequence before TXRESETDONE is detected High.

Page 31

Chapter 2: Shared Features

Send Feedback

3. The associated PLL must indicate locked.

4. The guideline for this asynchronous GTTXRESET pulse width is one period of the reference

clock.

Figure 15: GTM Transmitter Reset after GTTXRESET Pulse in Full Sequential Reset

GTM Transceiver TX Component Reset

TX PMA and TX PCS can be reset individually. Component reset is enabled by seng the

appropriate TXPMARESETMASK and TXPCSRESETMASK bits along with TXRESETMODE and

then toggling GTTXRESET.

Driving GTTXRESET from High to Low starts the component reset process. All

TXPMARESETMASK and TXPCSRESETMASK bits along with TXRESETMODE must be held

constant during the reset process.

When TXRESETMODE is set to sequenal mode, the internal resets are toggled in sequence

depending on TXPMARESTMASK and TXPCSRESETMASK selecon. When TXRESETMODE is

set to single mode, the internal resets are toggled simultaneously depending on

TXPMARESETMASK and TXPCSRESTMASK selecon.

In sequenal mode, if the TX PCS is to be reset, TXUSERRDY must toggle to High prior to the

internal PCS reset signal being released allowing TX reset to be completed.

Direct single-reset ports TXPMARESET, TXCKALRESET, TXPCSRESET, and TXFECRESET are

available to perform single resets of the respecve TX components. When direct single-reset

ports are toggled, a single reset is performed regardless of TXPMARESETMASK,

TXPCSRESETMASK, and TXRESETMODE selecon. These ports must be held Low during any

sequenal or single resets driven by GTTXRESET.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 31

Page 32

Chapter 2: Shared Features

Send Feedback

Figure 16: GTM Transmitter Reset after GTTXRESET Pulse in Component Sequential

Mode

Figure 17: GTM Transmitter Reset after GTTXRESET Pulse in Component Single Mode

The following table lists the recommended resets for common situaons.

Table 16: Recommended Transmitter Resets for Common Situations

Situation

After power up and

configuration

After turning on a

reference clock to the

PLL being used

After changing the

reference clock to the

PLL being used

After assertion/

deassertion of PLLPD for

the PLL being used

Components to

be Reset

PLL, Entire TX

PLL, Entire TX

PLL, Entire TX

PLL, Entire TX

TXRESETMODE TXPMARESETMASK TXPCSRESETMASK

2'b00 2’b11 2’b11

2'b00 2’b11 2’b11

2'b00 2’b11 2’b11

2'b00 2’b11 2’b11

Recommended TX Reset Setting

1

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 32

Page 33

Chapter 2: Shared Features

Send Feedback

Table 16: Recommended Transmitter Resets for Common Situations (cont'd)

Situation

After assertion/

deassertion of TXPD

TX rate change TX PMA and TX PCS

TX parallel clock source

reset

Notes:

1. TXPCSRESETMASK[0] can be set to 0 if the FEC is bypassed.

Components to

be Reset

Entire TX

TX PCS 2'b00/2'b11

TXRESETMODE TXPMARESETMASK TXPCSRESETMASK

2'b00 2’b11 2’b11

2'b00 2’b11 2’b11

Recommended TX Reset Setting

2’b00 2’b11

After Power-up and Configuration

The PLL being used and the enre GTM TX require a reset aer conguraon. See GTM

Transceiver TX Reset in Response to Compleon of Conguraon.

After Turning on a Reference Clock to the LCPLL/ RPLL Being Used

If the reference clock(s) changes or the GTM transceiver(s) are powered up aer conguraon,

perform a full TX sequenal reset aer the PLL fully completes its reset procedure.

1

After Changing the Reference Clock to the PLL being Used

Whenever the reference clock input to the PLL is changed, the PLL must be reset aerwards to

ensure that it locks to the new frequency. Perform a full TX sequenal reset aer the PLL fully

completes its reset procedure.

After Assertion/Deassertion of PLLPD for the PLL being Used

When the PLL being used goes back to normal operaon aer power down, the PLL must be

reset. Perform a full TX sequenal reset aer the PLL fully completes its reset procedure.

After Assertion/Deassertion of TXPD[1:0]

Aer the TXPD signal is deasserted, perform a full TX sequenal reset.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 33

Page 34

Chapter 2: Shared Features

Send Feedback

TX Rate Change

When a rate change is performed, a full TX sequenal reset is required aer the rate aributes

have been updated.

TX Parallel Clock Source Reset

The clocks driving TXUSRCLK must be stable for correct operaon. Perform a TX PCS reset aer

the clock source re-locks.

RX Initialization and Reset

The GTM transceiver RX uses a reset state machine to control the reset process. Due to its

complexity, the GTM transceiver RX is paroned into more reset regions than the GTM

transceiver TX. The paron allows RX inializaon and reset to be operated in either sequenal

mode, as shown in the following gure, or single mode:

1. RX in Sequenal Mode: To inialize the GTM transceiver RX, RXRESETMODE must be set to

sequenal mode. The RX components that are required to be rest are determined by seng

the appropriate RXPMARESETMASK and RXPCSRESETMASK bits to High. The reset

sequence is then triggered by toggling GTRXRESET and then internal component resets are

triggered sequenally. The reset state machine executes the reset sequence as shown in the

following gure, covering the enre RX PMA and RX PCS. During normal operaon, the reset

state machine runs unl RXRESETDONE transions from Low to High.

2. RX in Single Mode: When the GTM transceiver RX is in single mode, RXRESETMODE must

be set to single mode. The RX components that are required to be rest are determined by

seng the appropriate RXPMARESETMASK and RXPCSRESETMASK bits to High. The reset

sequence is then triggered by toggling GTRXRESET and the internal component resets are

triggered simultaneously. In addion, RXADAPTRESET, RXADCCLKGENRESET,

RXBUFRESET, RXCDRFRRESET, RXCDRPHRESET, RXDFERESET, RXDSPRESET,

RXEYESCANRESET, RXFECRESET, RXPCSRESET, RXPMARESET and RXPRBSCNTRESET

pins are available to reset those components directly in single mode.

In either sequenal mode or single mode, the RX reset state machine does not reset the PCS

unl RXUSERRDY goes High. Drive RXUSERRDY High aer all clocks used by the applicaon,

including RXUSRCLK, are shown to be stable.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 34

Page 35

GTRXRESET

Send Feedback

High

Wait until

GTRXRESET from

High to Low

Chapter 2: Shared Features

Figure 18: GTM Transceiver RX Reset State Machine Sequence

RXPMARESETMASK[0]

= 1?

No

RXPMARESETMASK[1]

= 1?

No

RXPMARESETMASK[2]

= 1?

No

RXPMARESETMASK[3]

= 1?

No

Yes

Yes

Yes

Yes

RX PMA Top

Reset

RX ADC CLKGEN

Reset

RX DSP Reset

RX DFE Reset

Wait for

RXUSERRDY = 1

RXPCSRESETMASK[0]

= 1?

No

RXPCSRESETMASK[1]

= 1?

No

RXPCSRESETMASK[2]

= 1?

No

Yes

Yes

Yes

RX Eye Scan

Reset

RX FEC Reset

RX PCS Top Reset

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 35

RXPMARESETMASK[4]

= 1?

No

RXPMARESETMASK[5]

= 1?

No

RXPMARESETMASK[6]

= 1?

No

Yes

Yes

Yes

RX Adapt Reset

RX CDR PH Reset

RX CDR FR Reset

RXPCSRESETMASK[3]

= 1?

No

RXRESETDONE

High

Yes

RX PRBS Counter

Reset

X20906-053118

Page 36

Chapter 2: Shared Features

Send Feedback

Ports and Attributes

The following table lists the ports required by the GTM transceiver RX inializaon process.

Table 17: RX Initialization and Reset Ports

Port Dir

CH[0/1]_GTRXRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXRESETMODE[1:0]

CH[0/1]_RXPMARESETMASK[7:0]

In Async Reset mode port for RX:

In Async RX PMA reset mask selection:

Clock

Domain

Description

a RX reset sequence. The components to be reset are

determined by RXPMARESETMASK and

RXPCSRESETMASK. In sequential mode, the resets are

performed sequentially. In single mode, the resets

are performed simultaneously.

2’b00: Sequential mode (recommended).

2’b01: Reserved.

2’b10: Reserved.

2’b11: Single mode.

Bit 7: Reserved.

Bit 6: CDR FR.

Bit 5: CDR PH.

Bit 4: Adapt.

Bit 3: DFE.

Bit 2: DSP.

Bit 1: ADC CLKGEN.

Bit 0: RX PMA Top.

CH[0/1]_RXPCSRESETMASK[3:0]

CH[0/1]_RXUSERRDY

CH[0/1]_RXPMARESETDONE Out Async This active-High signal indicates RX PMA reset is

CH[0/1]_RXRESETDONE Out RXUSRCLK This active-High signal indicates the GTM transceiver

CH[0/1]_RXADAPTRESET

CH[0/1]_RXADCCALRESET In Async Reserved.

In Async RX PCS reset mask selection

Bit 3: PRBS counter.

Bit 2: RX PCS top.

Bit 1: FEC.

Bit 0: Eye Scan.

In Async This port is driven High by the user application when

RXUSRCLK is stable.

complete.

RX has finished reset and is ready for use. This port is

driven Low when GTRXRESET goes High and is not

driven High until the GTM transceiver has completed

all RX reset steps.

In Async This port is driven High and then deasserted to start

a single mode reset on RX adaptation. The reset is

not dependent on RXRESETMODE or

RXPMARESETMASK setting.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 36

Page 37

Table 17: RX Initialization and Reset Ports (cont'd)

Send Feedback

Chapter 2: Shared Features

Port Dir

CH[0/1]_RXADCCLKGENRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXBUFRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXCDRFRRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXCDRPHRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXDFERESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXDSPRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXEYESCANRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXFECRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXPCSRESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXPMARESET In Async This port is driven High and then deasserted to start

CH[0/1]_RXPRBSCNTRESET In Async This port is driven High and then deasserted to start

Clock

Domain

Description

a single mode reset on RX ADC CLKGEN. The reset is

not dependent on RXRESETMODE or

RXPMARESETMASK setting.

a single mode reset on RX buffer. The reset is not

dependent on RXRESETMODE or RXPCSRESETMASK

setting.

a single mode reset on CDR FR. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

a single mode reset on CDR PH. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

a single mode reset on DFE. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

a single mode reset on DSP. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

a single mode reset on eye scan. The reset is not

dependent on RXRESETMODE or RXPCSRESETMASK

setting.

a single mode reset on the FEC. The reset is not

dependent on RXRESETMODE or RXPCSRESETMASK

setting.

a single mode reset on the PCS top. The reset is not

dependent on RXRESETMODE or RXPCSRESETMASK

setting.

a single mode reset on the PMA top. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

a single mode reset on the PRBS counter. The reset is

not dependent on RXRESETMODE or

RXPCSRESETMASK setting.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 37

Page 38

Chapter 2: Shared Features

Send Feedback

The following table lists aributes required by GTM transceiver RX inializaon. In general cases,

the reset me required by the RX PMA or the RX PCS varies depending on line rate. The factors

aecng PMA reset me and PCS reset me are the user-congurable aributes

RX_PMA_RESET_TIME, RX_DFE_RESET_TIME, RX_ADAPT_RESET_TIME,

RX_DSP_RESET_TIME, RX_ADC_CLKGEN_RESET_TIME, RX_CDRFREQ_RESET_TIME,

RX_CDRPHASE_RESET_TIME, RX_PCS_RESET_TIME, RX_FEC_RESET_TIME,

RX_PRBS_RESET_TIME and RX_EYESCAN_RESET_TIME.

Table 18: RX Initialization and Reset Attributes

Attribute Type Description

CH[0/1]_RST_TIME_CFG2 16-bit Reserved. Use the recommended value from the

Bit Name Bit Field Description

RX_ADAPT_RESET_TIME [14:10] Reserved. Represents the time duration to apply an RX

RX_DSP_RESET_TIME

RX_ADC_CLKGEN_RESET_TIME

CH[0/1]_RST_TIME_CFG3

Bit Name Bit Field Description

RX_CDRFREQ_RESET_TIME [14:10] Reserved. Represents the time duration to apply an RX

RX_CDRPHASE_RESET_TIME

CH[0/1]_RST_TIME_CFG1

Bit Name Bit Field Description

RX_DFE_RESET_TIME [14:10] Reserved. Represents the time duration to apply an RX

RX_PMA_RESET_TIME

[9:5] Reserved. Represents the time duration to apply an RX

[4:0] Reserved. Represents the time duration to apply an RX

16-bit Reserved. Use the recommended value from the

[9:5] Reserved. Represents the time duration to apply an RX

16-bit Reserved. Use the recommended value from the

[9:5] Reserved. Represents the time duration to apply an RX

Wizard.

adapt reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[4] is High and GTRXRESET initiates

the reset process.

DSP reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[2] is High and GTRXRESET initiates

the reset process.

ADC CLKGEN reset. Use the recommended value from

the Wizard. Must be a non-zero value when

RXPMARESETMASK[1] is High and GTRXRESET initiates

the reset process.

Wizard.

CDR FR reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[5] is High and GTRXRESET initiates

the reset process.

CDR PH reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[6] is High and GTRXRESET initiates

the reset process.

Wizard.

DFE reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[3] is High and GTRXRESET initiates

the reset process.

PMA reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[0] is High and GTRXRESET initiates

the reset process.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 38

Page 39

Chapter 2: Shared Features

Send Feedback

Table 18: RX Initialization and Reset Attributes (cont'd)

Attribute Type Description

CH[0/1]_RST_TIME_CFG4 16-bit Reserved. Use the recommended value from the

Bit Name Bit Field Description

RX_PCS_RESET_TIME [14:10] Reserved. Represents the time duration to apply an RX

RX_FEC_RESET_TIME

RX_EYESCAN_RESET_TIME

CH[0/1]_RST_TIME_CFG5

Bit Name Bit Field Description

RX_PRBS_RESET_TIME [4:0] Reserved. Represents the time duration to apply a

CH[0/1]_RST_LP_CFG1

Bit Name Bit Field Description

RX_DSP_RESET_LOOP_ID [15:12] Reserved. Use the recommended value from the

RX_ADC_CLKGEN_RESET_LOOP_ID [11:8] Reserved. Use the recommended value from the

RX_DFE_RESET_LOOP_ID [7:4] Reserved. Use the recommended value from the

RX_PMA_RESET_LOOP_ID [3:0] Reserved. Use the recommended value from the

CH[0/1]_RST_LP_CFG2 16-bit Reserved. Use the recommended value from the

Bit Name Bit Field Description

RX_CDRFREQ_RESET_LOOP_ID [15:12] Reserved. Use the recommended value from the

RX_CDRPHASE_RESET_LOOP_ID [11:8] Reserved. Use the recommended value from the

RX_ADAPT_RESET_LOOP_ID [3:0] Reserved. Use the recommended value from the

[9:5] Reserved. Represents the time duration to apply an RX

[4:0] Reserved. Represents the time duration to apply an

16-bit Reserved. Use the recommended value from the

16-bit Reserved. Use the recommended value from the

Wizard.

PCS reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPCSRESETMASK[2] is High and GTRXRESET initiates

the reset process.

buffer reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPCSRESETMASK[1] is High and GTRXRESET initiates

the reset process.

eye scan reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPCSRESETMASK[0] is High and GTRXRESET initiates

the reset process.

Wizard.

PRBS counter reset. Use the recommended value from

the Wizard. Must be a non-zero value when

RXPCSRESETMASK[3] is High and GTRXRESET initiates

the reset process.

Wizard.

Wizard.

Wizard.

Wizard.

Wizard.

Wizard.

Wizard.

Wizard.

Wizard.

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 39

Page 40

Chapter 2: Shared Features

Send Feedback

Table 18: RX Initialization and Reset Attributes (cont'd)

Attribute Type Description