Page 1

Virtex-4 FPGA

www.BDTIC.com/XILINX

Embedded Tri-Mode

Ethernet MAC

User Guide

UG074 (v2.2) February 22, 2010

R

Page 2

R

www.BDTIC.com/XILINX

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development

of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the

Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise,

without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves

the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors

contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with

technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER

WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY

RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL

DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2004–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx

in the United States and other countries. PowerPC is a trademark of IBM Corp. and is used under license. All other trademarks are the

property of their respective owners.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com UG074 (v2.2) February 22, 2010

Page 3

Revision History

www.BDTIC.com/XILINX

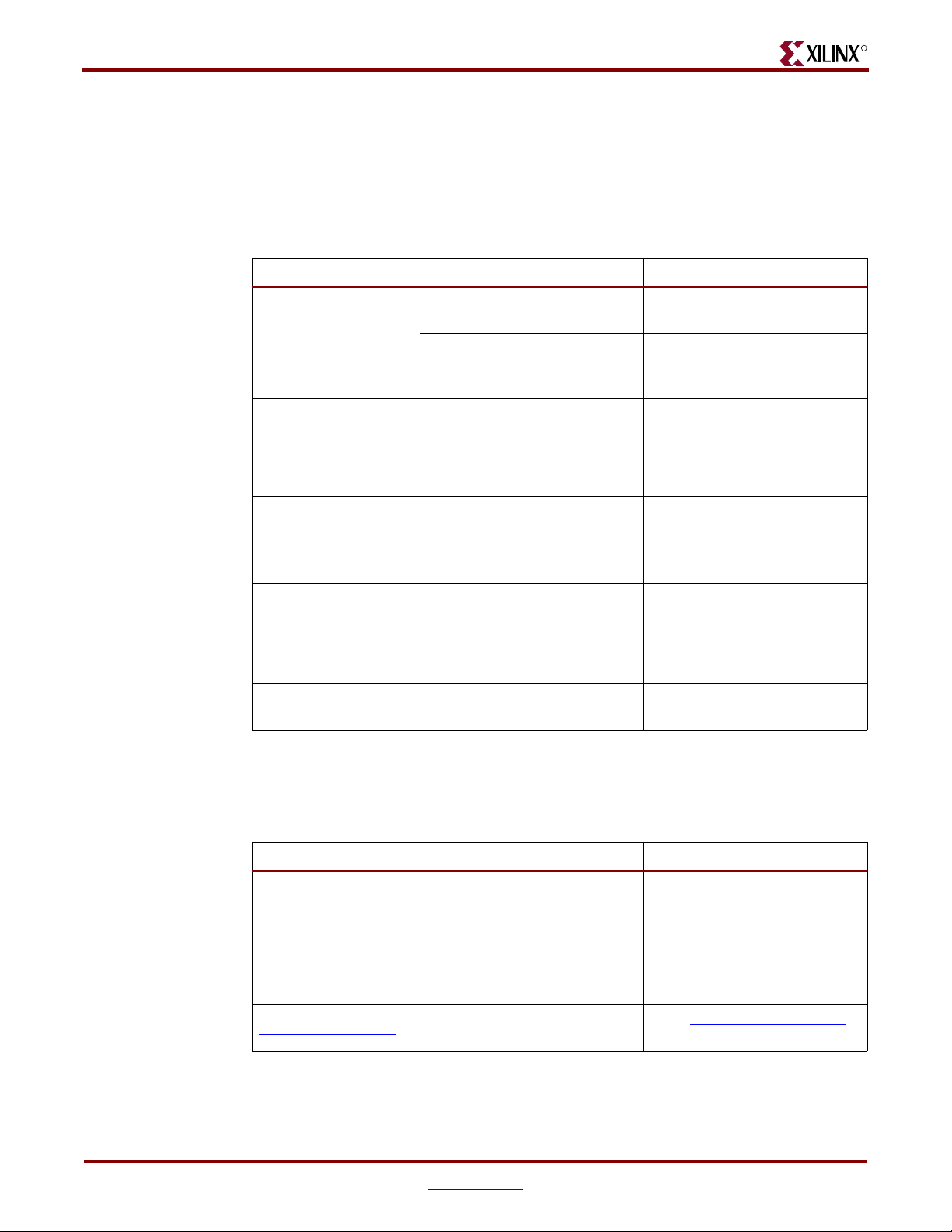

The following table shows the revision history for this document.

Date Version Revision

11/11/04 1.0 Initial Xilinx release.

07/05/05 1.1 In Chapter 2:

• Revised Tab l e 2-6 , pa g e 23, “Tie-Off Pins,” page 24, and Table 2-10, page 25.

In Chapter 3:

• Revised Ta bl e 3- 6 and Figure 3-5. Added information to “Normal Frame Transmission”.

Revised Figure 3-6, “Client Underrun”, Figure 3-7, and Figure 3-9.

• Added information to “Transmit (TX) Client – 16-bit Wide Interface,” page 43.

• Revised “SGMII/1000BASE-X PCS/PMA,” page 48 and Figure 3-18, page 49, Figure 3-19,

page 49, and Figure 3-21, page 50.

• Added information to “Flow Control Block,” page 57 and the “Flow Control

Implementation Example,” page 60.

• Revised Figure 3-32, page 59.

• Revised “Generic Host Bus,” page 70.

• Revised Table 3-17, page 73, and Table 3-20, page 76.

• Revised Table 3-22, page 78 through Table 3-31, page 83.

•Added “Connecting the MDIO to an External PHY” and Figure 3-49, page 96.

• Revised Ethernet MAC I/Os in Figure 3-55, page 97, Figure 3-60, page 103, Figure 3-65,

page 112, Figure 3-71, page 120, and Figure 3-75, page 128.

• Revised Figure 3-66, page 113.

• Added information to “Auto-Negotiation Interrupt,” page 145.

• Added information to “SGMII Standard,” page 146.

In Chapter 4:

• Revised sample code in “Interfacing to the Processor DCR,” page 150.

In Chapter 5:

•Replaced Figure 5-2, page 154 and Figure 5-3, page 156.

Added Appendix A, “Ethernet MAC Timing Model.”

07/20/05 1.2 Revised figures.

09/07/05 1.3 Corrected items from

“Miscellaneous Functions.” Updated pin 76 in Ta bl e 2 -9 . Revised Figure 3-56, Figure 3-57,

Figure 3-61, Figure 3-63, Figure 3-67, Figure 3-68, Figure 3-72, Figure 5-1, Figure 5-2, and

Figure 5-3. Added “Tri-Mode RGMII v1.3” in Chapter 3. Moved the “Using the DCR Bus as the

Host Bus”, “Description of Ethernet MAC Register Access through the DCR Bus”, and

“Address Code” sections to the “Host Interface” section.

UG074 (v2.2) February 22, 2010 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

version 1.1 and 1.2. Inserted eight new figures into Chapter 5,

Page 4

Date Version Revision

www.BDTIC.com/XILINX

02/07/06 1.4 In Chapter 2, “Ethernet MAC Architecture”:

• Added EMAC#CLIENTRXCLIENTCLKOUT to Tabl e 2 -2, p age 1 9.

In Chapter 5, “Miscellaneous Functions”:

•Corrected “Client RX Data/Control Interface,” page 55.

• Inserted new text to “Length/Type Field Error Checks,” page 52, “Tri-Mode RGMII v2.0,”

page 115, and “10/100/1000 SGMII Clock Management,” page 121.

• Edited waveforms in Figure 3-39, page 66.

• Added sections to Table 3-36, page 88.

•Added “Introduction to MDIO,” page 90, “MDIO Implementation in the EMAC,” page 92,

“Tri-Mode Operation with Byte PHY Enabled (Full-Duplex Only),” page 109, and

“1000BASE-X PCS/PMA (8-bit Data Client) Clock Management,” page 126.

• Added IDELAY component to Figure 3-61, Figure 3-62, Figure 3-63, and Figure 3-64.

• Revised the GT11 block in Figure 3-72 and Figure 3-73. Modified text in “10/100/1000

SGMII Clock Management,” page 121, “8-Bit Data Client,” page 129, and “16-Bit Data

Client,” page 130.

In Chapter 6, “Use Models”:

•Replaced “Interfacing to an FPGA Fabric-Based Statistics Block,” page 154 with new

content.

• Revised example code in “Writing to the PHY Registers Using MDIO,” page 153.

In Chapter 7, “Ethernet MAC Wrappers”:

• Added new text to “VHDL and Verilog CORE Generator Wrappers,” page 159.

•Added “Advanced Clocking,” page 155 and “Client Side Data Width,” page 157 options.

•Replaced “File Generation” with new content.

•Replaced Figure 5-1, page 153.

02/09/06 1.4.1 Cleaned up formatting issues. No content changes.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com UG074 (v2.2) February 22, 2010

Page 5

Date Version Revision

www.BDTIC.com/XILINX

11/11/06 1.5 • Book restructuring of Chapter 3 content:

•

Sections on Host, Client, and MDIO interfaces remain in Chapter 3, now called “Client, Host,

and MDIO Interfaces.”

• Pulled out section on Physical Interface to new Chapter 4, “Physical Interface.”

• Pulled out sections on Clock Frequency Support, Ethernet MAC Configuration, and Auto-

Negotiation Interrupt to new Chapter 5, “Miscellaneous Functions.”

• Globally changed all instances of PHYEMAC#TXD to EMAC#PHYTXD.

•Section “Features” in Chapter 1: Added full-duplex qualifier for SGMII support.

• Ta bl e 3- 3 0: Added EMAC1 registers IRSTATUS, IRENABLE, MIIMWRDATA, and

MIIMCNTL.

• Updated/corrected Figure 3-48, Figure 4-1, Figure 4-3, Figure 4-22, and Figure 4-24.

•Section “SGMII RX Elastic Buffer” added to Chapter 4, “Physical Interface.”

• Corrected section “1 Gb/s RGMII Clock Management” in Chapter 4.

•Section “10/100/1000 SGMII Clock Management” in Chapter 4: The external, high-quality

reference clock for the RocketIO transceiver changed from 125 MHz to 250 MHz. The GT11

clock schemes are simplified as shown in Figure 4-24.

•Section “1000BASE-X PCS/PMA (8-bit Data Client) Clock Management” in Chapter 4: The

GT11 clock schemes are simplified as shown in Figure 4-27.

•Section “1000BASE-X PCS/PMA Clock Management” in Chapter 4: The external, high-

quality reference clock for the 16-bit Data Client MGT changed from 125 MHz to 250 MHz.

The GT11 clock schemes are simplified as shown in Figure 4-28.

• Ta bl e 4- 1 3: Corrected 4.8:7 Pause, 10 and 11 (reversed)

•Section “MGT Elastic Buffer (Ring Buffer)” in Chapter 4: Corrected underflow/overflow

marks, and as a result corrected maximum frame size (Tab le 4 -4 ).

•Section “Transmit Clocking Scheme” in Chapter 5: Corrected description of inputs used to

generate client-side clock.

•Section “Reading the PHY Registers Using MDIO” in Chapter 6: Corrected decode address.

•Section “Writing to the PHY Registers Using MDIO” in Chapter 6: Corrected register

address for EMAC1 Management Configuration; corrected decode address.

• Chapter 7, “Using the Embedded Ethernet MAC” updated.

03/27/07 1.6 • Tab le 2 - 9: Removed Note (1).

• Ta bl e 2- 11 : Revised Note (1).

• Ta bl e 3- 5 : Removed exception from description of Length/Type Out of Range.

• Ta bl e 3- 2 0: Corrected default value for bit 31 (Promiscuous Mode Enable).

• Chapter 4: Multiple revisions in block schematic diagram figures.

• Chapter 4: Former section “1000BASE-X PCS/PMA (8-bit Data Client) Clock Management”

in Chapter 4 incorporated into

• Ta bl e 4- 3 : Consolidated “RISING” and “FALLING” RGMII signals into single signals with

revised descriptions. Added Note (1) to RGMII_TX_CTL_# and RGMII_RX_CTL_#.

UG074 (v2.2) February 22, 2010 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

section “8-Bit Data Client.”

Page 6

Date Version Revision

www.BDTIC.com/XILINX

08/20/07 1.7 • Replaced screen shots with updated images from v4.5 software.

• Ta bl e 2- 11 : Revised description of TIEEMAC#CONFIGVEC[63].

•Section “Length/Type Field Error Checks” in Chapter 3: Numerous textual revisions

throughout this section.

•Section “Receiving a PAUSE Control Frame” in Chapter 3: Last paragraph revised.

• Ta bl e 3- 9 : Revised definition of Receiver Configuration register bit [25] (LT_DIS).

• Figure 4-7 through Figure 4-10 and Figure 4-12 through Figure 4-16 and accompanying

text: Added IDELAY element to clock input.

• Figure 4-24: Corrected placement of BUFG to TXCLIENTCLKOUT.

• Made other typographical edits.

02/06/08 1.8 • Added conditions causing assertion of EMAC#CLIENTRXBADFRAME to “Frame

Reception with Errors,” page 53.

• Rewrote description of ALIGNMENT_ERROR bit in Tab l e 3-5 , pag e 70.

• Updated Figure 4-28, page 139.

•Added “Core Latency” in Appendix A.

08/13/08 1.9 • Corrected transposition error in the description column for bit [1] in Table 3-13, page 78

(values 0 and 1 were switched in second sentence).

• Corrected transposition error in the description column for bits 5.8:7 in Table 4-14, page 144

(values 01 and 10 were switched).

• Rewrote item number 1 for 1000BASE-X auto-negotiation summary (“Overview of

Operation,” page 151).

• Updated the link in the first bullet of “Global Buffer Usage,” page 165.

05/12/09 2.0 • Chapter 4:

In sections “1 Gb/s GMII Only,” page 107, “Tri-Mode Operation,” page 109, “Tri-

Mode Operation with Byte PHY Enabled (Full-Duplex Only),” page 110, “1 Gb/s

RGMII Clock Management,” page 115, “Tri-Mode RGMII v2.0,” page 117, and “Tri-

Mode RGMII v1.3,” page 120, changed the description of the method used to delay

the received clock (GMII_RX_CLK in case of GMII and RGMII_RXC in case of

RGMII) with respect to data. Original method described use of IDELAY and BUFG.

Revised method describes use of a DCM and BUFG.

In Figure 4-7, page 107, Figure 4-8, page 108, Figure 4-9, page 110, Figure 4-10,

page 111, Figure 4-12, page 115, Figure 4-13, page 116, Figure 4-14, page 118,

Figure 4-15, page 119, Figure 4-16, page 121, and “16-Bit Data Client,” page 139,

Replaced IDELAY block in clock path with DCM.

• Chapter 6:

“Simulation Models,” page 155: Removed description of SmartModels. Replaced

references to SmartModel with references to SecureIP throughout this section. Added

“SecureIP Model,” page 155.

• Chapter 7:

Removed content discussing Ethernet MAC wrappers and replaced it with“Using the

Embedded Ethernet MAC,” page 167.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com UG074 (v2.2) February 22, 2010

Page 7

Date Version Revision

www.BDTIC.com/XILINX

10/28/09 2.1 • Chapter 2:

Updated the description of TIEEMAC#CONFIGVEC[62] and

TIEEMAC#CONFIGVEC[61] Table 2-11, page 30 with the full-duplex mode

requirement.

• Chapter 3:

Updated“IFG Adjustment,” page 46 and “Flow Control Block,” page 61 with the fullduplex mode requirement.

02/22/10 2.2 • Chapter 4:

• Replaced EMAC#CLIENTTXGMIIMIICLKOUT with GTX_CLK in “Tri-Mode

Operation,” page 109.

• Updated BUFGMUX and GTX_CLK in upper portion of Figure 4-9, page 110.

• Updated description of Link Status and added table note to Table 4-11, page 141.

• Appendix A:

Changed T

page 171.

xMACWL

to Clock Low and T

xMACWH

to Clock High in Figure A-1,

UG074 (v2.2) February 22, 2010 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

Page 8

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com UG074 (v2.2) February 22, 2010

www.BDTIC.com/XILINX

Page 9

Table of Contents

www.BDTIC.com/XILINX

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Online Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Chapter 1: Introduction

Ethernet MAC Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Chapter 2: Ethernet MAC Architecture

Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Ethernet MAC Primitive. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Ethernet MAC Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Client Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Clock Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Host Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Reset and CLIENTEMAC#DCMLOCKED Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Tie-Off Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Management Data Input/Output (MDIO) Interface Signals . . . . . . . . . . . . . . . . . . . . 32

Mode-Dependent Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

RocketIO Multi-Gigabit Transceiver Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Chapter 3: Client, Host, and MDIO Interfaces

Client Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Transmit (TX) Client – 8-bit Wide Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Transmit (TX) Client – 16-bit Wide Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Receive (RX) Client – 8-bit Wide Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Receive (RX) Client – 16-bit Wide Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Address Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Flow Control Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Statistics Vector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Host Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Address Filter Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Using the DCR Bus as the Host Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Description of Ethernet MAC Register Access through the DCR Bus . . . . . . . . . . . . . 89

Address Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

MDIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 9

UG074 (v2.2) February 22, 2010

Page 10

Introduction to MDIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

www.BDTIC.com/XILINX

MDIO Implementation in the EMAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Accessing MDIO via the EMAC Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Chapter 4: Physical Interface

Media Independent Interface (MII). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

MII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

MII Clock Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

MII Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Gigabit Media Independent Interface (GMII) Signals. . . . . . . . . . . . . . . . . . . . . . . 105

GMII Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

GMII Clock Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Tri-Mode Operation with Byte PHY Enabled (Full-Duplex Only) . . . . . . . . . . . . . . . 110

GMII Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

10/100/1000 RGMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

1 Gb/s RGMII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

1 Gb/s RGMII Clock Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Tri-Mode RGMII v2.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Tri-Mode RGMII v1.3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

RGMII Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

10/100/1000 Serial Gigabit Media Independent Interface (SGMII) . . . . . . . . . . . 123

SGMII RX Elastic Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

10/100/1000 SGMII Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

10/100/1000 SGMII Clock Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

SGMII Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

1000BASE-X PCS/PMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

1000BASE-X PCS/PMA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Shim . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

1000BASE-X PCS/PMA Clock Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

PCS/PMA Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

R

Chapter 5: Miscellaneous Functions

Clock Frequency Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Transmit Clocking Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Receive Clocking Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Ethernet MAC Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Auto-Negotiation Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Overview of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Auto-Negotiation Link Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Using the Auto-Negotiation Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Chapter 6: Use Models

Simulation Models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

SecureIP Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Model Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Pinout Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Interfacing to the Processor DCR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

10 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 11

R

www.BDTIC.com/XILINX

Interfacing to an FPGA Fabric-Based Statistics Block . . . . . . . . . . . . . . . . . . . . . . . 161

When the Ethernet MAC Is Implemented with the Host Bus . . . . . . . . . . . . . . . . . . . 161

When the Ethernet MAC Is Implemented with the DCR Bus . . . . . . . . . . . . . . . . . . . 163

Chapter 7: Using the Embedded Ethernet MAC

Accessing the Ethernet MAC from the CORE Generator tool . . . . . . . . . . . . . . . . 167

Simulating the Ethernet MAC using the Ethernet MAC wrappers . . . . . . . . . . . 167

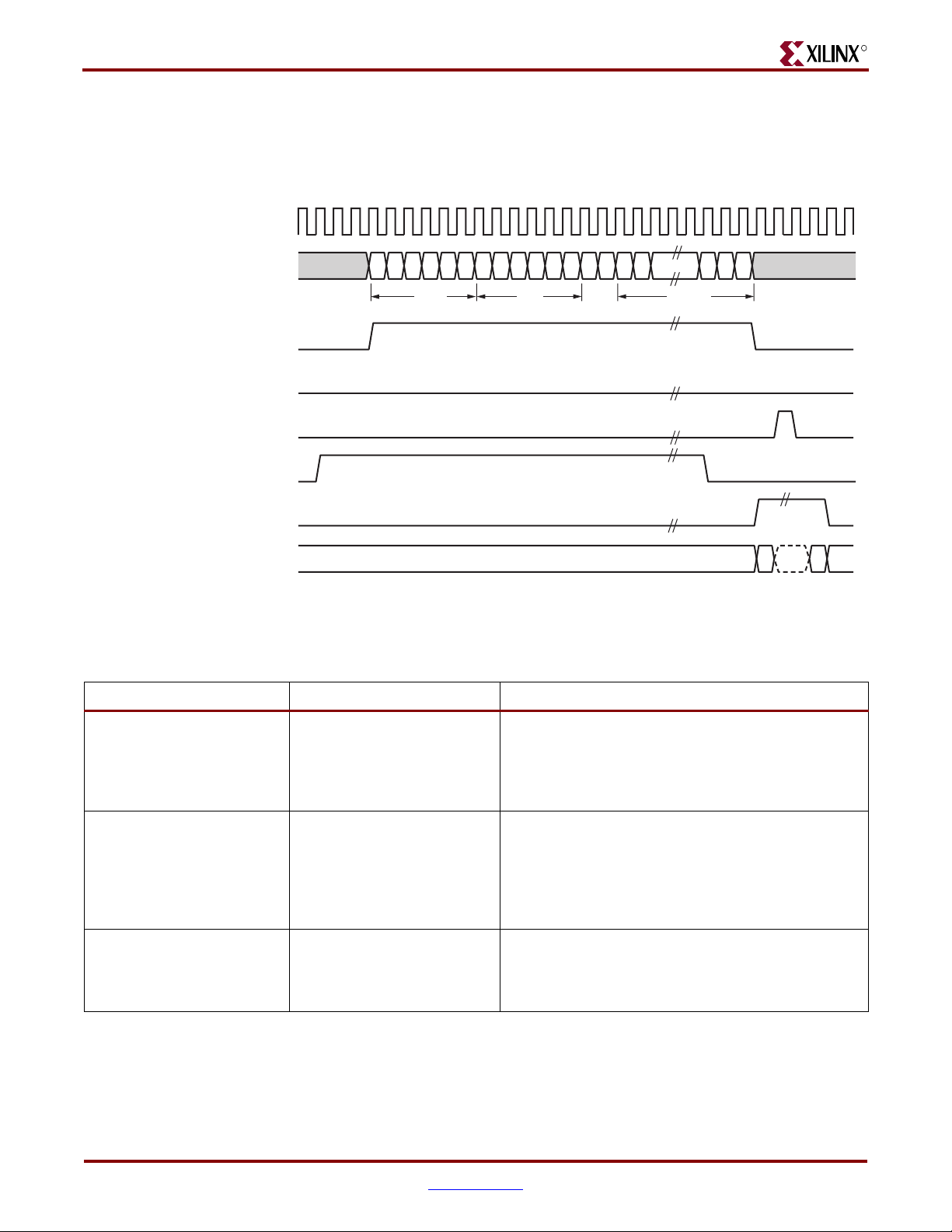

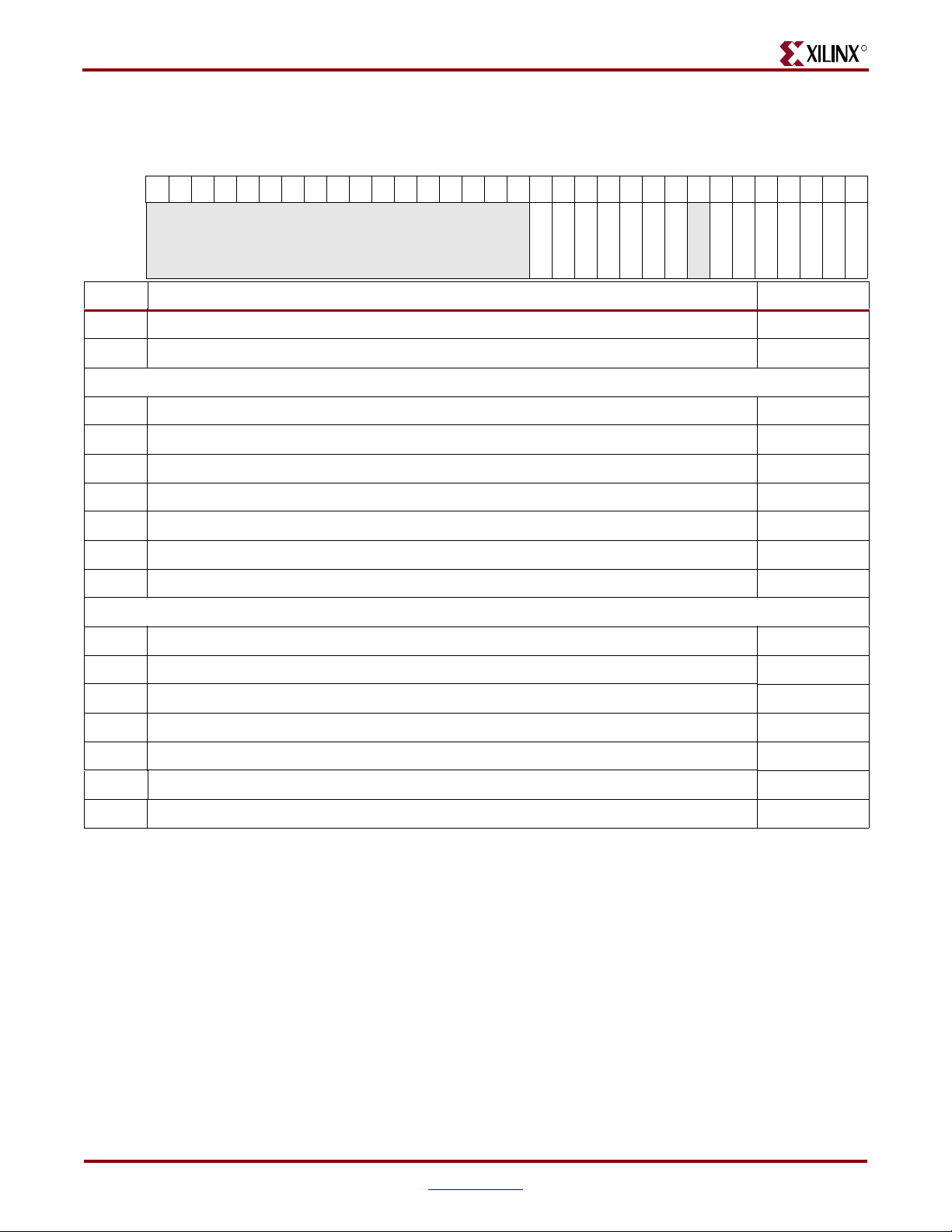

Appendix A: Ethernet MAC Timing Model

Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Input Setup/Hold Times Relative to Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Clock to Output Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Core Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Timing Diagram and Timing Parameter Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 11

UG074 (v2.2) February 22, 2010

Page 12

R

www.BDTIC.com/XILINX

12 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 13

R

www.BDTIC.com/XILINX

About This Guide

This document is the Virtex®-4 FPGA Embedded Tri-Mode Ethernet MAC User Guide.

Guide Contents

This user guide contains the following chapters:

• Chapter 1, “Introduction,” introduces the Virtex-4 FPGA Embedded Tri-Mode

Ethernet MAC and summarizes its features.

• Chapter 2, “Ethernet MAC Architecture,” describes the architecture of the Ethernet

MAC and defines its signals.

• Chapter 3, “Client, Host, and MDIO Interfaces,” provides design information for the

client, host, and MDIO interfaces.

• Chapter 4, “Physical Interface,” describes design considerations for the supported

interfaces when using the Ethernet MAC.

• Chapter 5, “Miscellaneous Functions,” provides useful information for designing

with the Ethernet MAC.

• Chapter 6, “Use Models,” describes some available models and how to interface the

Ethernet MAC to a processor DCR or an FPGA statistics block.

• Chapter 7, “Using the Embedded Ethernet MAC,” describes the Verilog and VHDL

CORE Generator™ wrappers.

• Appendix A, “Ethernet MAC Timing Model,” provides details on the timing

parameters of the Ethernet MAC timing model.

Preface

Additional Resources

For additional information, go to http://www.xilinx.com/support.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 13

UG074 (v2.2) February 22, 2010

Page 14

Preface: About This Guide

www.BDTIC.com/XILINX

Conventions

This document uses the following conventions. An example illustrates each convention.

Typographical

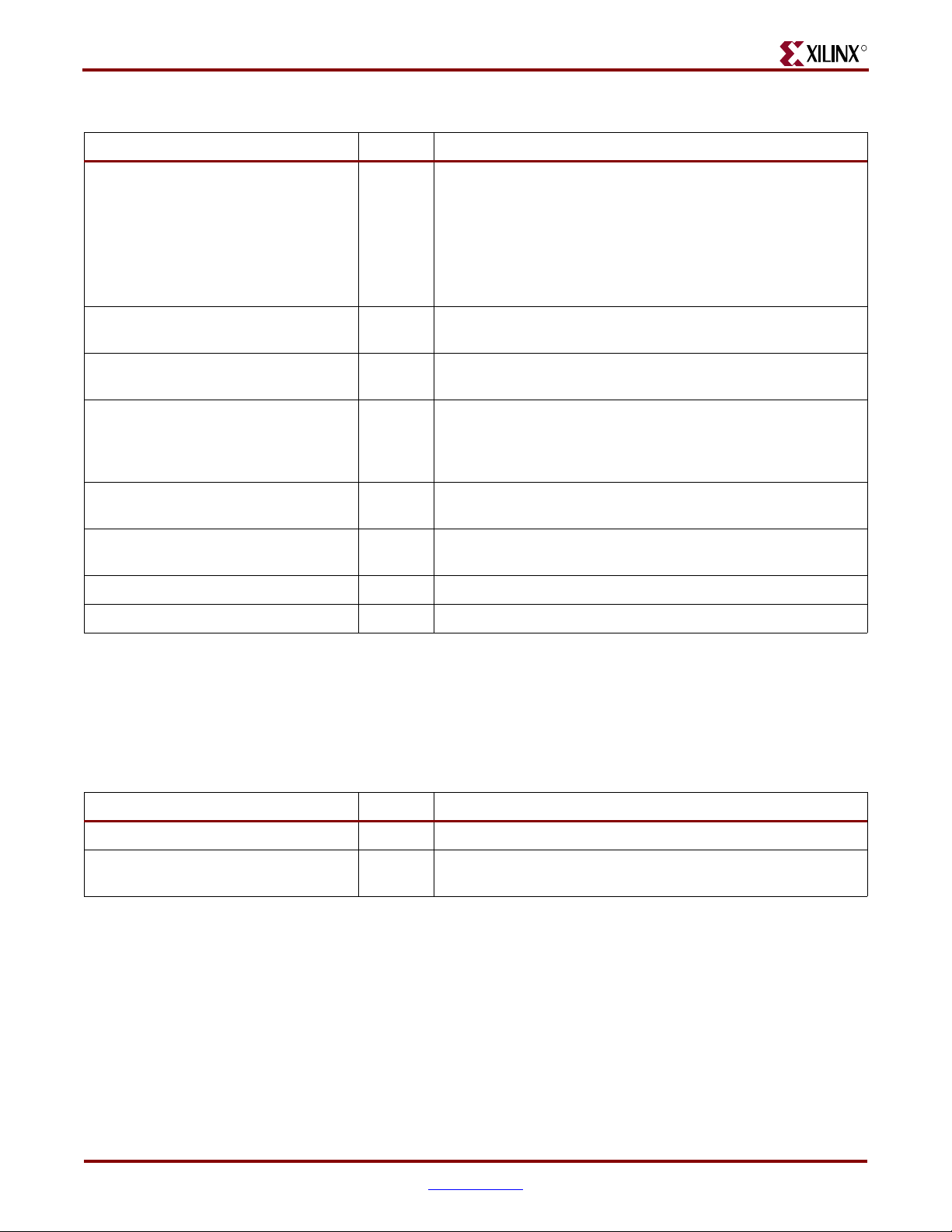

The typographical conventions in the following table are used in this document:

R

Convention Meaning or Use Example

Italic font

Byte/bit

Hex and binary

notation

Vertical ellipsis

.

.

.

Horizontal ellipsis . . .

References to other manuals

Emphasis in text

“B” means “byte,”and

“b” means “bit”

EXCEPTIONS:

Hex and binary numbers are in a

monospace typeface.

The 0x prefix is often used to

designate a hex string.

Repetitive material that has

been omitted

Repetitive material that has

been omitted

See the Virtex-4 Data Sheet for

more information.

If a wire is drawn so that it

overlaps the pin of a symbol, the

two nets are not connected.

8B word

64b word

8B/10B = 8 bit/10 bit

64B/66B = 64 bit/66 bit

0 or 1 [binary]

11010011 [binary]

0x0123456789ABCDEF

IOB #1: Name = QOUT’

IOB #2: Name = CLKIN’

.

.

.

allow block block_name

loc1 loc2 ... locn;

Online Document

The cross-reference and linking conventions shown in the following table are used in this

document:

Convention Meaning or Use Example

Blue text

Red text

Blue, underlined text

14 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

Cross-reference link to a location

in the current document

Cross-reference link to a location

in another document

Hyperlink to a website (URL)

See the section “Additional

Resources” for details.

Refer to “Title Formats” in

Chapter 1 for details.

See the Virtex-4 User Guide.

Go to http://www.xilinx.com

for the latest speed files.

UG074 (v2.2) February 22, 2010

Page 15

R

www.BDTIC.com/XILINX

Introduction

This chapter introduces the Virtex®-4 FPGA Embedded Tri-Mode Ethernet Media Access

Controller (MAC). It contains the following sections:

• “Ethernet MAC Overview”

• “Features”

Ethernet MAC Overview

Figure 1-1 shows the Virtex-4 FPGA Tri-Mode Ethernet MAC that is used to provide

Ethernet connectivity to the Virtex-4 FX family of devices.

Chapter 1

FPGA Auxiliary

Processor Port

IS-PLB Port

DS-PLB Port

DCR

Interface

Physical

Interface

Processor Block

APU

Control

Te st

Reset and

Control

DCR

Control

APU

ISPLB

DSPLB

DCR

ISOCM

Control

ISOCM

PPC405

Processor

DSOCM

DSOCM

Control

EMAC

Block

DCR

Bus

Physical

Interface

Figure 1-1: Virtex-4 FPGA Embedded Tri-Mode Ethernet MAC

Client Data

Interface

EMAC

Host

Interface

EMAC

Client Data

Client

Statistics

Interface

Generic

Host Bus

Client

Statistics

Interface

Interface

UG074_1_01_012408

The Virtex-4 FPGA Ethernet MAC has two Ethernet MACs sharing a single host interface.

Either or both of the Ethernet MACs can be selected to access the Ethernet MAC registers.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 15

UG074 (v2.2) February 22, 2010

Page 16

Chapter 1: Introduction

www.BDTIC.com/XILINX

Features

R

The key features of the Virtex-4 FPGA Ethernet MAC are:

• Fully integrated 10/100/1000 Mb/s Ethernet MAC

• Designed to the IEEE Std 802.3-2002 specification

• Configurable full-duplex operation in 10/100/1000 Mb/s

• Configurable half-duplex operation in 10/100 Mb/s

• Management Data Input/Output (MDIO) interface to manage objects in the physical

layer

• User-accessible raw statistic vector outputs

• Support for VLAN frames

• Configurable inter-frame gap (IFG) adjustment in full-duplex operation

• Configurable in-band Frame Check Sequence (FCS) field passing on both transmit

and receive paths

• Auto padding on transmits and stripping on receives

• Configured and monitored through a host interface

• Hardware-selectable Device Control Register (DCR) bus or generic host bus interface

• Configurable flow control through Ethernet MAC Control PAUSE frames;

symmetrically or asymmetrically enabled

• Configurable support for jumbo frames of any length

• Configurable receive address filter for unicast, multicast, and broadcast addresses

• Media Independent Interface (MII), Gigabit Media Independent Interface (GMII), and

Reduced Gigabit Media Independent Interface (RGMII)

• Includes a 1000BASE-X Physical Coding Sublayer (PCS) and a Physical Medium

Attachment (PMA) sublayer for use with the RocketIO™ Multi-Gigabit Transceiver

(MGT) to provide a complete on-chip 1000BASE-X implementation

• Serial Gigabit Media Independent Interface (SGMII) supported through MGT

interface to external copper PHY layer for full-duplex operation only

16 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 17

R

www.BDTIC.com/XILINX

Ethernet MAC Architecture

This chapter describes the architecture of the Virtex®-4 FPGA Embedded Tri-Mode

Ethernet Media Access Controller (MAC). It contains the following sections:

• “Architecture Overview”

• “Ethernet MAC Primitive”

• “Ethernet MAC Signal Descriptions”

Architecture Overview

The Virtex-4 FPGA Embedded Tri-Mode Ethernet MAC supports 10/100/1000 Mb/s data

rates and is designed to IEEE Std 802.3-2002 specifications. The Ethernet MAC can operate

as a single speed Ethernet MAC at 10, 100, or 1000 Mb/s or as a tri-mode Ethernet MAC.

The Ethernet MAC supports the IEEE standard GMII and the RGMII protocols to reduce

the width of the bus to the external physical interface. A 1000BASE-X PCS/PMA sublayer,

when used in conjunction with the Virtex-4 FPGA RocketIO™ Multi-Gigabit Transceiver

(MGT), provides a complete on-chip 1000BASE-X implementation.

Chapter 2

Figure 2-1 shows a block diagram of the Ethernet MAC block. The block contains two

Ethernet MACs sharing a single host interface. The host interface can use either the generic

host bus or the DCR bus through the DCR bridge. Each Ethernet MAC has an address filter

to accept or reject incoming frames on the receive datapath. The Ethernet MAC outputs

raw statistic vectors to enable statistics gathering. The statistics vectors are multiplexed to

reduce the number of pins at the block boundary. An external module (StatsIP0 and/or

StatsIP1) can be designed and implemented in the FPGA fabric to accumulate all the

statistics of the Ethernet MAC. The “Interfacing to an FPGA Fabric-Based Statistics Block”

section provides additional information on the statistics block.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 17

UG074 (v2.2) February 22, 2010

Page 18

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

R

StatsIP1

Rx Stats MUX1 Tx Stats MUX1

ClientTx1/Rx1

To PowerPC 405 block

Generic Host Bus

ClientTx0/Rx0

FPGA Fabric

DCR Bus

Ethernet MAC

Block

EMAC1

DCR

Bridge

Rx Stats MUX0 Tx Stats MUX0

Host Interface

EMAC0

StatsIP0

Tx1/Rx1

PHY

Tx0/Rx0

ug074_2_01_091704

Figure 2-1: Ethernet MAC Block

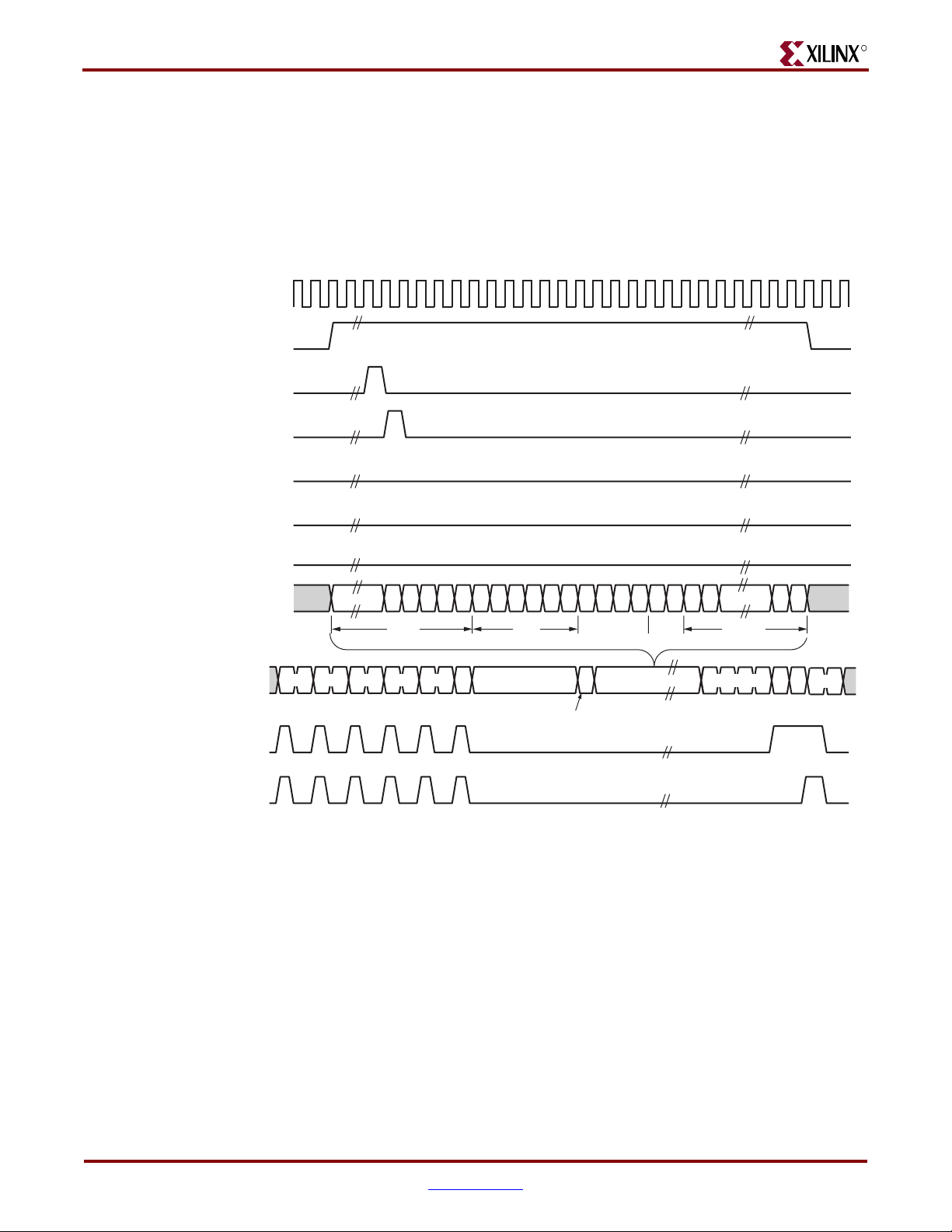

A detailed block diagram of the 10/100/1000 Ethernet MAC is shown in Figure 2-2. On the

physical side, it consists of the GMII and RGMII interfaces using standard I/Os to access

data and control signals to an external physical interface. In addition, the PCS/PMA

sublayer interfaces directly to the MGT.

The client side consists of the user transmit and receive interfaces. The flow control module

keeps traffic from being congested in the Ethernet MAC. The Management Data I/O

interface, (MDIO), allows access to the control and status registers in the external physical

interface or in the PCS sublayer when configured in 1000BASE-X and SGMII modes.

The clock management module automatically configures the output clocks to the correct

frequency based on the internal speed of the Ethernet MAC (10 Mb/s, 100 Mb/s, or

1000 Mb/s) and the Ethernet MAC mode settings (GMII, MII, RGMII, SGMII, and

1000BASE-X).

18 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 19

R

www.BDTIC.com/XILINX

Architecture Overview

Clock Management

MII / GMII / RGMII Interface

TX

Tr ansmit Engine

to External PHY

Flow Control

MGT

Generic

Host Bus

DCR Bus

RX

16-bit or 8-bit Client Interface

Receive Engine

MII / GMII / RGMII Interface

Address Filter Registers

Host

Interface

MDIO Interface

Configuration Registers

tx_stats_vec rx_stats_vec

Figure 2-2: Functional Block Diagram of 10/100/1000 Ethernet MAC

PCS / PMA Sublayer

MDIO Interface

to External PHY

Statistics

UG074_2_02_081308

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 19

UG074 (v2.2) February 22, 2010

Page 20

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

Ethernet MAC Primitive

The Virtex-4 FPGA Embedded Tri-Mode Ethernet MAC has an EMAC primitive. The

primitive contains access to both Ethernet MACs (EMAC0 and EMAC1).

By using the Ethernet MAC primitive, any of these supported interfaces can be created:

• Gigabit Media Independent Interface (GMII)

• Media Independent Interface (MII)

• Reduced Gigabit Media Independent Interface (RGMII)

• Serial Gigabit Media Independent Interface (SGMII)

• 1000BASE-X Physical Coding Sublayer (PCS) and Physical Medium Attachment

(PMA)

Detailed connections to support/create these interfaces using the Ethernet MAC primitive

are found in Chapter 4, “Physical Interface.”

The Ethernet MAC primitive is discussed in different sections:

• Receive / Transmit Client Interface

• See “Client Interface” in Chapter 3.

• Flow Control

See “Flow Control Block” in Chapter 3.

R

• Generic Host Bus

Interface to any host (i.e., PowerPC

and status of both Ethernet MACs. See “Host Interface” in Chapter 3.

• DCR Bus

Interface to the PowerPC processor through the DCR bus to access the control and

status of both Ethernet MACs. See “Using the DCR Bus as the Host Bus” in Chapter 3.

• Physical Interface

Physical interface depending on the mode of configuration. See Chapter 4, “Physical

Interface.”

• Multi-Gigabit Transceiver

Interface to the RocketIO transceivers when the Ethernet MAC is configured in either

SGMII or 1000BASE-X PCS/PMA mode. See “10/100/1000 Serial Gigabit Media

Independent Interface (SGMII)” or “1000BASE-X PCS/PMA” in Chapter 4.

• Management Data I/O (MDIO)

Interface to the Management Data I/O of either an external physical interface or the

PCS sublayer when configured in SGMII or 1000BASE-X PCS/PMA mode. See “MDIO

Interface” in Chapter 3.

The Ethernet MAC primitive can be simplified for specific customer needs using Ethernet

MAC wrappers. Chapter 7, “Using the Embedded Ethernet MAC,” describes how

Ethernet MAC wrappers use the CORE Generator™ software to simplify the Ethernet

MAC primitives.

®

or MicroBlaze™ processor) to access the control

Figure 2-3 illustrates the Ethernet MAC primitive. The # sign denotes both Ethernet MACs

(EMAC0 and EMAC1) in the EMAC primitive.

20 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 21

R

www.BDTIC.com/XILINX

CLIENTEMAC#DCMLOCKED

EMAC#CLIENTRXCLIENTCLKOUT

CLIENTEMAC#RXCLIENTCLKIN

EMAC#CLIENTRXD[15:0]

EMAC#CLIENTRXDVLD

EMAC#CLIENTRXDVLDMSW

EMAC#CLIENTRXGOODFRAME

EMAC#CLIENTRXBADFRAME

RX ClientTX Client

EMAC#CLIENTRXFRAMEDROP

EMAC#CLIENTRXDVREG6

EMAC#CLIENTRXSTATS[6:0]

EMAC#CLIENTRXSTATSBYTEVLD

EMAC#CLIENTRXSTATSVLD

EMAC#CLIENTTXCLIENTCLKOUT

CLIENTEMAC#TXCLIENTCLKIN

CLIENTEMAC#TXD[15:0]

CLIENTEMAC#TXDVLD

CLIENTEMAC#TXDVLDMSW

EMAC#CLIENTTXACK

CLIENTEMAC#TXUNDERRUN

EMAC#CLIENTTXCOLLISION

EMAC#CLIENTTXRETRANSMIT

CLIENTEMAC#TXIFGDELAY[7:0]

CLIENTEMAC#TXFIRSTBYTE

EMAC#CLIENTTXSTATS

EMAC#CLIENTTXSTATSBYTEVLD

EMAC#CLIENTTXSTATSVLD

CLIENTEMAC#PAUSEREQ

CLIENTEMAC#PAUSEVAL[15:0]

Flow

Control

Generic

Host Bus

Bus

DCR

HOSTADDR[9:0]

HOSTCLK

HOSTMIIMSEL

HOSTOPCODE[1:0]

HOSTREQ

HOSTMIIMRDY

HOSTRDDATA[31:0]

HOSTWRDATA[31:0]

HOSTEMAC1SEL

DCREMACENABLE

EMACDCRACK

EMACDCRDBUS[0:31]

DCREMACABUS[8:9]

DCREMACCLK

DCREMACDBUS[0:31]

DCREMACREAD

DCREMACWRITE

DCRHOSTDONEIR

EMAC#

Primitive

Ethernet MAC Primitive

RESET

PHYEMAC#GTXCLK

TIEEMAC#CONFIGVEC[79:0]

TIEEMAC#UNICASTADDR[47:0]

EMAC#CLIENTTXGMIIMIICLKOUT

CLIENTEMAC#TXGMIIMIICLKIN

PHYEMAC#RXCLK

PHYEMAC#RXD[7:0]

PHYEMAC#RXDV

PHYEMAC#RXER

PHYEMAC#MIITXCLK

EMAC#PHYTXCLK

EMAC#PHYTXD[7:0]

EMAC#PHYTXEN

EMAC#PHYTXER

PHYEMAC#COL

PHYEMAC#CRS

PHYEMAC#SIGNALDET

PHYEMAC#PHYAD[4:0]

EMAC#PHYENCOMMAALIGN

EMAC#PHYLOOPBACKMSB

EMAC#PHYMGTRXRESET

EMAC#PHYMGTTXRESET

EMAC#PHYPOWERDOWN

EMAC#PHYSYNCACQSTATUS

PHYEMAC#RXCLKCORCNT[2:0]

PHYEMAC#RXBUFSTATUS[1:0]

PHYEMAC#RXCHARISCOMMA

PHYEMAC#RXCHARISK

PHYEMAC#RXCHECKINGCRC

PHYEMAC#RXCOMMADET

PHYEMAC#RXDISPERR

PHYEMAC#RXLOSSOFSYNC[1:0]

PHYEMAC#RXNOTINTABLE

PHYEMAC#RXRUNDISP

PHYEMAC#RXBUFERR

EMAC#CLIENTANINTERRUPT

EMAC#PHYTXCHARDISPMODE

EMAC#PHYTXCHARDISPVAL

EMAC#PHYTXCHARISK

PHYEMAC#TXBUFERR

EMAC#PHYMCLKOUT

PHYEMAC#MCLKIN

PHYEMAC#MDIN

EMAC#PHYMDOUT

EMAC#PHYMDTRI

Physical Interface

Multi-Gigabit Transceiver

Management

Data I/O

Figure 2-3: Ethernet MAC Primitive

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 21

UG074 (v2.2) February 22, 2010

ug074_2_03_101804

Page 22

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

Ethernet MAC Signal Descriptions

This section defines all of the Ethernet MAC primitive signals. The signals are divided into

the following categories:

• “Client Signals,” page 22

• “Clock Signals,” page 25

• “Host Interface Signals,” page 26

• “Reset and CLIENTEMAC#DCMLOCKED Signals,” page 27

• “Tie-Off Pins,” page 28

• “Management Data Input/Output (MDIO) Interface Signals,” page 32

• “Mode-Dependent Signals,” page 32

• “RocketIO Multi-Gigabit Transceiver Signals,” page 34

All the signals available in the Ethernet MAC primitive are described in this section. The #

symbol denotes the EMAC0 or EMAC1 signals.

Client Signals

R

Client-Side Transmit (TX) Signals

Tab le 2 -1 describes the client-side transmit signals in the Ethernet MAC. These signals are

used to transmit data from the client to the Ethernet MAC.

Table 2-1: Transmit Client Interface Signals

Signal Direction Description

CLIENTEMAC#TXD[15:0] Input

CLIENTEMAC#TXDVLD Input

CLIENTEMAC#TXDVLDMSW Input

CLIENTEMAC#TXFIRSTBYTE Input

Frame data for transmit. The data path can be configured to be

either 8 or 16 bits wide. Bits [7:0] are used for 8-bit width. The

16-bit interface is available only in 1000BASE-X PCS/PMA

mode. See “Transmit (TX) Client – 16-bit Wide Interface” in

Chapter 3.

Asserted by the client to indicate a valid data input at

CLIENTEMAC#TXD[7:0].

When the width of CLIENTEMAC#TXD is set to 16 bits wide,

this signal denotes an odd number of bytes in the transmit data

path. In the frame with an odd number of bytes, the

CLIENTEMAC#TXD[7:0] is valid on the last byte.

When the width of CLIENTEMAC#TXD is set to 8 bits wide, this

signal is connected to ground.

Is asserted High for one clock cycle to indicate the start of data

flow on CLIENTEMAC#TXD. See Figure 3-3, “Normal Frame

Transmission Across Client Interface” in Chapter 3. Can be

grounded if not used.

CLIENTEMAC#TXIFGDELAY[7:0] Input

CLIENTEMAC#TXUNDERRUN Input

CLIENTEMAC#TXCLIENTCLKIN Input See “Transmit Clocking Scheme” in Chapter 5.

22 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

Configurable inter-frame gap (IFG) adjustment for full-duplex

mode.

Asserted by the client to force the Ethernet MAC to corrupt the

current frame.

UG074 (v2.2) February 22, 2010

Page 23

R

www.BDTIC.com/XILINX

Table 2-1: Transmit Client Interface Signals (Cont’d)

Signal Direction Description

Handshake signal – Asserted when the Ethernet MAC accepts

EMAC#CLIENTTXACK Output

EMAC#CLIENTTXCOLLISION Output

EMAC#CLIENTTXRETRANSMIT Output

EMAC#CLIENTTXSTATS Output

EMAC#CLIENTTXSTATSBYTEVLD Output

the first byte of data. On the next and subsequent rising clock

edges, the client must provide the remainder of the frame data.

See “Normal Frame Transmission” in Chapter 3.

Asserted by the Ethernet MAC to signal a collision on the

medium. Any transmission in progress should be aborted. This

signal is always deasserted in full-duplex mode.

Asserted by the Ethernet MAC at the same time as the

EMAC#CLIENTTXCOLLISION signal. The client should resupply the aborted frame to the Ethernet MAC for

retransmission. This signal is always deasserted in full-duplex

mode.

The statistics data on the last data frame sent. The 32-bit TX raw

statistics vector is output by one bit per cycle for statistics

gathering. See “Transmitter Statistics Vector” in Chapter 3.

Asserted if an Ethernet MAC frame byte is transmitted

(including destination address to FCS). This is valid on every TX

clock cycle.

Ethernet MAC Signal Descriptions

Asserted by the Ethernet MAC after a frame transmission to

EMAC#CLIENTTXSTATSVLD Output

EMAC#CLIENTTXCLIENTCLKOUT Output See “Transmit Clocking Scheme” in Chapter 5.

indicate a valid EMAC#CLIENTTXSTATS output. See

“Transmitter Statistics Vector” in Chapter 3.

Client-Side Receive (RX) Signals

Tab le 2 -2 describes the client-side receive signals. These signals are used by the Ethernet

MAC to transfer data to the client.

Table 2-2: Receive Client Interface Signals

Signal Direction Description

CLIENTEMAC#RXCLIENTCLKIN Input See “Receive Clocking Scheme” in Chapter 5.

Frame data received from the Ethernet MAC. The data path can

be co nfigure d t o either 8 bits or 16 bits wide. Bits [7:0] are used fo r

EMAC#CLIENTRXD[15:0] Output

EMAC#CLIENTRXDVLD Output

EMAC#CLIENTRXFRAMEDROP Output

8-bit width. The 16-bit interface is intended to be used in

1000BASE-X PCS/PMA mode. See “Receive (RX) Client – 16-bit

Wide Interface” in Chapter 3.

The Ethernet MAC indicates to the client the receipt of valid

frame data.

This signal is asserted to notify the client that an incoming receive

frames destination address does not match any addresses in the

address filter. The signal functions even when the address filter is

not enabled.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 23

UG074 (v2.2) February 22, 2010

Page 24

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

Table 2-2: Receive Client Interface Signals (Cont’d)

Signal Direction Description

This signal denotes an odd number of bytes in the receive data

path when the width of EMAC#CLIENTRXD is set to 16 bits

wide.

EMAC#CLIENTRXDVLDMSW Output

In a frame with an odd number of bytes, the

EMAC#CLIENTRXD[7:0] byte is valid on the last byte.

When the width of EMAC#CLIENTRXD is set to 8 bits wide, this

signal should be left unconnected.

R

EMAC#CLIENTRXGOODFRAME Output

EMAC#CLIENTRXBADFRAME Output

EMAC#CLIENTRXSTATS[6:0] Output

EMAC#CLIENTRXSTATSBYTEVLD Output

EMAC#CLIENTRXSTATSVLD Output

EMAC#CLIENTRXCLIENTCLKOUT Output See “Receive Clocking Scheme” in Chapter 5.

EMAC#CLIENTRXDVREG6 Output Reserved - not used.

This signal is asserted after the last receipt of data to indicate the

reception of a compliant frame.

This signal is asserted after the last receipt of data to indicate the

reception of a non-compliant frame.

The statistics data on the last received data frame. The 27-bit raw

RX statistics vector is multiplexed into a seven-bits per RX clock

cycle output for statistics gathering. See “Receiver Statistics

Vector” in Chapter 3.

Asserted if an Ethernet MAC frame byte (including destination

address to FCS) is received. Valid on every RX clock cycle.

Asserted by the Ethernet MAC after the end of receiving a frame

to indicate a valid EMAC#CLIENTRXSTATS[6:0] output.

Flow Control Client-Side Interface Signals

Tab le 2 -3 describes the signals used by the client to request a flow control action from the

transmit engine. The flow control block is designed per the specifications in Clause 31 of

the IEEE Std 802.3-2002 standard. Flow control frames received by the Ethernet MAC are

automatically handled.

Table 2-3: Flow Control Interface Signals

Signal Direction Description

CLIENTEMAC#PAUSEREQ Input Asserted by client to transmit a pause frame.

CLIENTEMAC#PAUSEVAL[15:0] Input

24 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

The amount of pause time for the transmitter as defined in the

IEEE Std 802.3-2002 specification.

UG074 (v2.2) February 22, 2010

Page 25

R

www.BDTIC.com/XILINX

Clock Signals

Tab le 2 -4 shows the clock signals necessary to drive the Ethernet MAC.

Table 2-4: Clock Signals

Signal Direction Description

PHYEMAC#GTXCLK Input

Ethernet MAC Signal Descriptions

Clock supplied by the user to derive the other transmit clocks.

Clock tolerance must be within the IEEE Std 802.3-2002

specification.

EMAC#CLIENTRXCLIENTCLKOUT Output

EMAC#CLIENTTXCLIENTCLKOUT Output

CLIENTEMAC#RXCLIENTCLKIN Input

CLIENTEMAC#TXCLIENTCLKIN Input

EMAC#CLIENTTXGMIIMIICLKOUT Output

CLIENTEMAC#TXGMIIMIICLKIN Input

Notes:

1. The Ethernet MAC uses this clock to generate an internal clock that eliminates clock skew between the Ethernet MAC and the client

logic in the FPGA.

Clock for receive client generated by the clock generator of the

Ethernet MAC.

Clock for transmit client generated by the clock generator of the

Ethernet MAC.

Clock from receive client for the running of the receiver engine of

the Ethernet MAC.

Clock from transmit client for the running of the transmitter

engine of the Ethernet MAC.

Clock for MII, GMII, and RGMII modules. Generated by the clock

generator of the Ethernet MAC.

Clock from MII, GMII, and RGMII modules for the running of the

MII/GMII/RGMII transmitter layer of the Ethernet MAC.

(1)

(1)

(1)

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 25

UG074 (v2.2) February 22, 2010

Page 26

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

Host Interface Signals

Host Bus Signals

Tab le 2 -5 outlines the host bus interface signals.

Table 2-5: Host Bus Signals

Signal Direction Description

R

HOSTCLK Input

HOSTOPCODE[1:0] Input

HOSTADDR[9:0] Input Address of register to be accessed.

HOSTWRDATA[31:0] Input Data bus to write to register.

HOSTRDDATA[31:0] Output Data bus to read from register.

HOSTMIIMSEL Input

HOSTREQ Input Used to signal a transaction on the MDIO interface.

HOSTEMAC1SEL Input

HOSTMIIMRDY Output

Notes:

1. All signals are synchronous to HOSTCLK and are active High.

2. When using the PowerPC 405 processor as a host processor and using the DCR bus for host access, the host bus signals are used to

read the optional FPGA fabric-based statistics registers. See “Interfacing to an FPGA Fabric-Based Statistics Block” in Chapter 6.

Clock supplied for running the host. User must supply this clock

at all times even if the host interface is not used.

Defines operation to be performed over MDIO interface. Bit [1] is

also used in configuration register access. See “Configuration

Registers” in Chapter 3.

When asserted, the MDIO interface is accessed. When

deasserted, the Ethernet MAC internal configuration registers

are accessed.

This signal is asserted when EMAC1 is being accessed through

the host interface and deasserted when EMAC0 is being accessed

through the host interface. It is ignored when the host interface is

not used.

When High, the MDIO interface has completed any pending

transaction and is ready for a new transaction.

26 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 27

R

www.BDTIC.com/XILINX

Ethernet MAC Signal Descriptions

DCR Bus Interface Signals

Tab le 2 -6 outlines the DCR bus interface signals.

Table 2-6: DCR Bus Signals

Signal Direction Description

DCREMACCLK Input Clock for the DCR interface from the PowerPC processor.

DCREMACABUS[8:9] Input

DCREMACREAD Input DCR read request.

DCREMACWRITE Input DCR write request.

DCREMACDBUS[0:31] Input DCR write data bus.

(1)

(1)

Input

Output

DCREMACENABLE

EMACDCRDBUS[0:31] Output DCR read data bus.

EMACDCRACK Output DCR acknowledge.

DCRHOSTDONEIR

Two LSBs of the DCR address bus. Bits[0] through [7] are decoded

in conjunction with the PowerPC block.

When using the DCR bus, this signal is connected directly to the

PPC405 output port DCREMACENABLER for DCR bus access.

When using the host bus interface, the signal is connected to the

logic ground.

Interrupt signal to the PowerPC processor when the Ethernet

MAC register access is done.

Notes:

1. All the DCR bus signals are internally connected to the PowerPC processor except for the DCREMACENABLE and

DCRHOSTDONEIR signals.

Reset and CLIENTEMAC#DCMLOCKED Signals

Tab le 2 -7 describes the Reset signal.

Table 2-7: Reset Signal

Signal Direction Description

Reset Input Asynchronous reset of both Ethernet MACs.

Tab le 2 -8 describes the CLIENTEMAC#DCMLOCKED signal.

Table 2-8: CLIENTEMAC#DCMLOCKED Signal

Signal Direction Description

If a DCM is used to derive any of the clock signals, the LOCKED

port of the DCM must be connected to the

CLIENTEMAC#DCMLOCKED port. The Ethernet MAC is held

CLIENTEMAC#DCMLOCKED Input

in reset until CLIENTEMAC#DCMLOCKED is asserted High.

If a DCM is not used, both CLIENTEMAC#DCMLOCKED ports

from EMAC0 and EMAC1 must be tied High.

If any Ethernet MAC is not used, CLIENTEMAC#DCMLOCKED

must be tied to High.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 27

UG074 (v2.2) February 22, 2010

Page 28

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

Tie-Off Pins

Configuration Vectors

This section describes the 80 tie-off pins (TIEEMAC#CONFIGVEC[79:0]) used to configure

the Virtex-4 FPGA Embedded Tri-Mode Ethernet MAC. The values of these tie-off pins are

loaded into the Ethernet MAC at power-up or when the Ethernet MAC is reset.

When TIEEMAC#CONFIGVEC[67] is High, the host interface is selected. Tie-off pins preconfigure the internal control registers of the Ethernet MAC. The host interface is then used

to dynamically change the register contents or to read the registers. When the host

interface is not selected, the tie-off pins directly control the behavior of the Ethernet MAC.

However, dynamically changing the register contents using the tie-off pins is not

recommended.

The configuration vectors are divided into three sections: physical interface configuration

vectors (Ta bl e 2 -9 ), mode configuration vectors (Tab le 2 -1 0), and MAC configuration

vectors (Ta bl e 2 -1 1). The MAC and physical interface configuration vectors can be

configured through the host interface and are intended to be used dynamically to change

register contents or read status registers. The mode configuration vectors preconfigure the

internal control registers (16-bit, PCS/PMA, Host, SGMII, RGMII, and MDIO interfaces)

but are not dynamically reconfigurable.

R

Table 2-9: Physical Interface Configuration Pins

Signal Direction Description

TIEEMAC#CONFIGVEC[79] Input Reserved, set to 1.

TIEEMAC#CONFIGVEC[78:74] — Only used in SGMII or 1000BASE-X modes. When MDIO and host are omitted from

the Ethernet MAC, this alternative can be used.

TIEEMAC#CONFIGVEC[78] Input

TIEEMAC#CONFIGVEC[77] Input

TIEEMAC#CONFIGVEC[76] Input

TIEEMAC#CONFIGVEC[75] Input

TIEEMAC#CONFIGVEC[74] Input

PHY_RESET: Asserting this pin resets the PCS/PMA module.

PHY_INIT_AN_ENABLE: Asserting this pin enables autonegotiation of the PCS/PMA module.

PHY_ISOLATE: Asserting this pin causes the PCS/PMA

sublayer logic to behave as if it is electrically isolated from the

attached Ethernet MAC, as defined in IEEE Std 802.3, Clause

22.2.4.1.6. Therefore, frames transmitted by the Ethernet MAC

are not forwarded through the PCS/PMA. Frames received by

the PCS/PMA are not relayed to the Ethernet MAC.

PHY_POWERDOWN: Asserting this pin causes the MGT to be

placed in a Low power state. A reset must be applied to clear the

Low power state.

PHY_LOOPBACK_MSB: Asserting this pin sets serial loopback

in the MGT.

28 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 29

R

www.BDTIC.com/XILINX

Table 2-10: Mode Configuration Pins

Signal Direction Description

Ethernet MAC Signal Descriptions

TIEEMAC#CONFIGVEC[73] Input

TIEEMAC#CONFIGVEC[72:71] — These pins determine the speed of the Ethernet MAC after reset or power-up. These

bits can be changed in the Ethernet MAC mode configuration register (Table 3-12, page 77) through the host interface

when the host interface is selected (by setting TIEEMAC#CONFIG[67] High). When TIEEMAC#CONFIG[67] is Low,

the speed of the Ethernet MAC is directly set by these two bits.

10 = 1000 Mb/s

01 = 100 Mb/s

00 =10Mb/s

11 = not applicable

TIEEMAC#CONFIGVEC[72] Input

TIEEMAC#CONFIGVEC[71] Input

TIEEMAC#CONFIGVEC[70:68] — Defines the physical interface of the Ethernet MAC. These pins are mutually

exclusive. 10/100 MII and GMII modes are enabled when TIEEMAC#CONFIGVEC[70:68] are deasserted; the RGMII,

SGMII, and 1000BASE-X modes are not set.

TIEEMAC#CONFIGVEC[70] Input

TIEEMAC#CONFIGVEC[69] Input

TIEEMAC#CONFIGVEC[68] Input

MDIO enable. Asserting this pin enables the use of MDIO in the

Ethernet MAC. See “MDIO Interface” in Chapter 3.

SPEED[1]

SPEED[0]

RGMII mode enable. Asserting this pin sets the Ethernet MAC in

RGMII mode.

SGMII mode enable. Asserting this pin sets the Ethernet MAC in

SGMII mode.

1000BASE-X PCS/PMA mode enable. Asserting this pin sets the

Ethernet MAC in 1000BASE-X mode.

TIEEMAC#CONFIGVEC[67] Input

TIEEMAC#CONFIGVEC[66] Input

TIEEMAC#CONFIGVEC[65] Input

Host Interface enable. Asserting this pin enables the use of the

Ethernet MAC host interface.

Transmit 16-bit client interface enable. When asserted, the TX

client data interface is 16 bits wide. When deasserted, the TX

client data interface is 8 bits wide.

Receive 16-bit client interface enable. When asserted, the RX

client data interface is 16 bits wide. When deasserted, the RX

client data interface is 8 bits wide.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 29

UG074 (v2.2) February 22, 2010

Page 30

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

Table 2-11: MAC Configuration Pins

Signal Direction Description

R

TIEEMAC#CONFIGVEC[64] Input

TIEEMAC#CONFIGVEC[63] Input

TIEEMAC#CONFIGVEC[62:61] — These pins configure the Ethernet MAC flow control module.

TIEEMAC#CONFIGVEC[62] Input

TIEEMAC#CONFIGVEC[61] Input

TIEEMAC#CONFIGVEC[60:54] — Configures the transmit engine of the Ethernet MAC.

TIEEMAC#CONFIGVEC[60] Input

TIEEMAC#CONFIGVEC[59] Input

Address Filter Enable: Asserting this pin enables the use of the

address filter module in the Ethernet MAC.

Length/Type Check Disable: When this pin is asserted, it

disables the comparison of the L/T field with the size of the data.

Receive Flow Control Enable. When this bit is

mode is enabled,

transmitter operation. When this bit is 0, the received flow

frames are passed up to the client.

Transmit Flow Control Enable. When this bit is

mode is enabled,

signal causes the Ethernet MAC to send a flow control frame out

from the transmitter. When 0, asserting the

CLIENTEMAC#PAUSE_REQ signal has no effect.

Transmitter Reset. When this bit is

transmitter is held in reset. This signal is an input to the reset

circuit for the transmitter block.

Transmitter Jumbo Frame Enable. When this bit is 1, the Ethernet

MAC transmitter allows frames larger than the maximum legal

frame length specified in IEEE Std 802.3-2002 to be sent. When

this bit is 0, the Ethernet MAC transmitter only allows frames up

to the legal maximum to be sent.

the received flow control frames inhibit

asserting the CLIENTEMAC#PAUSE_REQ

1, the Ethernet MAC

1 and full-duplex

1 and full duplex

TIEEMAC#CONFIGVEC[58] Input

TIEEMAC#CONFIGVEC[57] Input

TIEEMAC#CONFIGVEC[56] Input

TIEEMAC#CONFIGVEC[55] Input

TIEEMAC#CONFIGVEC[54] Input

Transmitter In-Band FCS Enable. When this bit is

MAC transmitter expects the FCS field to be passed in by the

client. When this bit is 0, the Ethernet MAC transmitter appends

padding as required, computes the FCS, and appends it to the

frame.

Transmitter Enable. When this bit is

operational. When this bit is 0, the transmitter is disabled.

Transmitter VLAN Enable. When this bit is

allows the transmission of VLAN tagged frames.

Transmitter Half Duplex. When this bit is

operates in half-duplex mode. When this bit is 0, the transmitter

operates in full-duplex mode.

Transmitter IFG Adjust enable. When this bit is

reads the value of the CLIENTEMAC#TXIFGDELAY[7:0] port

and sets the IFG accordingly. When this bit is 0, the transmitter

always inserts at least the legal minimum IFG.

1, the transmitter is

1, the transmitter

1, the Ethernet

1, the transmitter

1, the transmitter

30 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 31

R

www.BDTIC.com/XILINX

Ethernet MAC Signal Descriptions

Table 2-11: MAC Configuration Pins (Cont’d)

Signal Direction Description

TIEEMAC#CONFIGVEC[53:0] — Configures the receive engine of the Ethernet MAC.

TIEEMAC#CONFIGVEC[53] Input

TIEEMAC#CONFIGVEC[52] Input

TIEEMAC#CONFIGVEC[51] Input

TIEEMAC#CONFIGVEC[50] Input

TIEEMAC#CONFIGVEC[49] Input

TIEEMAC#CONFIGVEC[48] Input

TIEEMAC#CONFIGVEC[47:0] Input

Receiver Reset. When this bit is

This signal is an input to the reset circuit for the receiver block.

Receiver Jumbo Frame Enable. When this bit is 0, the receiver

does not pass frames longer than the maximum legal frame size

specified in IEEE Std 802.3-2002. When this bit is

does not have an upper limit on frame size.

Receiver In-band FCS Enable. When this bit is

MAC receiver passes the FCS field up to the client. When this bit

is 0, the Ethernet MAC receiver does not pass the FCS field. In

both cases, the FCS field are verified on the frame.

Receiver Enable. When this bit is

operational. When this bit is 0, the block ignores activity on the

physical interface RX port.

Receiver VLAN Enable. When this bit is

are accepted by the receiver.

Receiver Half Duplex. When this bit is

half-duplex mode. When this bit is 0, the receiver operates in full-

duplex mode.

Pause frame Ethernet MAC Source Address[47:0]. This address is

used by the Ethernet MAC to match against the destination

address of any incoming flow control frames, and as the source

address for any outbound flow control frames.

The address is ordered for the least significant byte in the register

to have the first byte transmitted or received; for example, an

Ethernet MAC address of AA-BB-CC-DD-EE-FF is stored in byte

[47:0] as 0xFFEEDDCCBBAA.

Tied to the same Ethernet MAC address as

TIEEMAC#UNICASTADDR[47:0].

1, the receiver is held in reset.

1, the receiver

1, the Ethernet

1, the receiver block is

1, VLAN tagged frames

1, the receiver operates in

Notes:

1. A reset is needed before changes on TIEEMAC#CONFIGVEC[73] and [70:64] take effect.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 31

UG074 (v2.2) February 22, 2010

Page 32

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

Unicast Address

Tab le 2 -1 2 describes the 48 tie-off pins (TIEEMAC#UNICASTADDR[47:0]) used to set the

Ethernet MAC address for the Virtex-4 FPGA Embedded Tri-Mode Ethernet MAC.

Table 2-12: Unicast Address Pins

Signal Direction Description

This 48-bit wide tie-off is used to set the Ethernet MAC unicast

address used by the address filter block to see if the incoming

frame is destined for the Ethernet MAC.

TIEEMAC#UNICASTADDR[47:0] Input

Notes:

1. All of the TIEEMAC#UNICASTADDR[47:0] bits are registered on input and can be treated as asynchronous inputs.

The address is ordered for the least significant byte in the register

to have the first byte transmitted or received; for example, an

Ethernet MAC address of 06-05-04-03-02-01 is stored in byte

[47:0] as 0x010203040506.

Management Data Input/Output (MDIO) Interface Signals

R

Tab le 2 -1 3 describes the Management Data Input/Output (MDIO) interface signals. The

MDIO format is defined in IEEE Std 802.3, Clause 22.

Table 2-13: MDIO Interface Signals

Signal Direction Description

EMAC#PHYMCLKOUT Output

PHYEMAC#MCLKIN Input

PHYEMAC#MDIN Input

EMAC#PHYMDOUT Output

EMAC#PHYMDTRI Output The 3-state control to accompany EMAC#PHYMDOUT.

Management clock derived from the host clock or

PHYEMAC#MCLKIN.

When the host is not used, access to the PCS must be provided by

an external MDIO controller. In this situation, the management

clock is an input to the core.

Signal from the physical interface for communicating the

configuration and status. If unused, must be tied High.

Signal to output the configuration and command to the physical

interface.

Mode-Dependent Signals

The Ethernet MAC has several signals that change definition depending on the selected

operating mode. This section describes the basic signals in the various operating modes.

Data and Control Signals

Tab le 2 -1 4 shows the data and control signals for the different modes. They are set from the

tie-off pins. These signals are multiplexed, and their functionality is defined when the

mode is set.

32 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 33

R

www.BDTIC.com/XILINX

Table 2-14: PHY Data and Control Signals

Signal Direction Mode Description

Ethernet MAC Signal Descriptions

10/100 MII

PHYEMAC#MIITXCLK Input

EMAC#PHYTXCLK Output GMII

EMAC#CLIENTTXGMIIMIICLKOUT Output

EMAC#PHYTXEN Output

EMAC#PHYTXER Output

16-bit client

interface

used in

1000BASE-X

PCS/PMA

GMII

RGMII

10/100 MII

GMII

RGMII The RGMII_TX_CTL_RISING signal to the PHY.

10/100 MII

GMII

RGMII

10/100 MII

The TX clock generated from the PHY when

operating in 10/100 MII mode.

When the transmit client interface is configured

to be 16 bits wide, this is the clock input port for

the CLIENTEMAC#TXCLIENTCLKIN/2. See

“Transmit (TX) Client – 16-bit Wide Interface” in

Chapter 3.

The TX clock out to the PHY in GMII 1000 Mb/s

mode only.

The TX clock out to the PHY for GMII tri-speed

mode operation and RGMII.

The data enable control signal to the PHY.

The error control signal to the PHY.

The RGMII_TX_CTL_FALLING signal to the

PHY.

EMAC#PHYTXD[3:0] is the transmit data signal

to the PHY. EMAC#PHYTXD[7:4] are driven

Low.

EMAC#PHYTXD[7:0] Output

PHYEMAC#RXCLK Input

GMII The transmit data signal to the PHY.

EMAC#PHYTXD[3:0] is the

RGMII

SGMII

1000BASE-X

10/100 MII

GMII

RGMII

16-bit client

interface

used in

1000BASE-X

PCS/PMA

RGMII_TXD_RISING and EMAC#PHYTXD[7:4]

is the RGMII_TXD_FALLING signal to the PHY.

The TX_DATA signal to the MGT.

The recovered clock from received data stream

by the PHY.

When the receive client interface is configured to

be 16 bits wide, this signal is the clock input port

for the CLIENTEMAC#RXCLIENTCLKIN/2.

See “Receive (RX) Client – 16-bit Wide Interface”

in Chapter 3.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 33

UG074 (v2.2) February 22, 2010

Page 34

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

Table 2-14: PHY Data and Control Signals (Cont’d)

Signal Direction Mode Description

R

PHYEMAC#RXDV Input

PHYEMAC#RXER Input

PHYEMAC#RXD[7:0] Input

10/100 MII

GMII

RGMII The RGMII_RX_CTL_RISING signal.

SGMII

1000BASE-X

10/100 MII

GMII

RGMII

10/100 MII

GMII The received data signal to the PHY.

RGMII

SGMII

1000BASE-X

The data valid control signal from the PHY.

The RXREALIGN signal from the MGT.

The error control signal from the PHY.

The RGMII_RX_CTL_FALLING signal from the

PHY.

PHYEMAC#RXD [3:0] is the received data signal

from the PHY. PHYEMAC#RXD [7:4] is left

unconnected.

PHYEMAC#RXD [3:0] is the

RGMII_RXD_RISING and PHYEMAC#RXD

[7:4] is the RGMII_RXD_FALLING signal from

the PHY.

The RX_DATA from the MGT.

10/100 MII

PHYEMAC#COL Input

PHYEMAC#CRS Input 10/100 MII

SGMII

1000BASE-X

The collision control signal from the PHY, used

in half-duplex mode.

The TXRUNDISP signal from the MGT.

The carrier sense control signal from the PHY,

used in half-duplex mode.

RocketIO Multi-Gigabit Transceiver Signals

Tab le 2 -1 5 shows the signals used to connect the Ethernet MAC to the RocketIO Multi-

Gigabit Transceiver (see UG076

Table 2-15: Multi-Gigabit Transceiver Connections

Signal Direction Description

EMAC#PHYENCOMMAALIGN Output Enable RocketIO PMA layer to realign to commas.

EMAC#PHYLOOPBACKMSB Output Loopback tests within the RocketIO Multi-Gigabit Transceivers.

EMAC#PHYMGTRXRESET Output Reset to RocketIO RXRESET.

EMAC#PHYMGTTXRESET Output Reset to RocketIO TXRESET.

EMAC#PHYPOWERDOWN Output Power-down the RocketIO Multi-Gigabit Transceivers.

, Virtex-4 RocketIO Multi-Gigabit Transceiver User Guide).

34 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 35

R

www.BDTIC.com/XILINX

Ethernet MAC Signal Descriptions

Table 2-15: Multi-Gigabit Transceiver Connections (Cont’d)

Signal Direction Description

The output from the receiver’s synchronization state machine of

IEEE Std 802.3, Clause 36.

EMAC#PHYSYNCACQSTATUS Output

EMAC#PHYTXCHARDISPMODE Output Set running disparity for current byte.

EMAC#PHYTXCHARDISPVAL Output Set running disparity value.

EMAC#PHYTXCHARISK Output K character transmitted in TXDATA.

When asserted High, the received bitstream is synchronized. The

state machine is in one of the SYNC_ACQUIRED states of IEEE

Std 802.3, figures 36-39.

When deasserted Low, no synchronization has been obtained.

PHYEMAC#RXBUFSTATUS[1:0] Input

PHYEMAC#RXCHARISCOMMA Input Comma detected in RXDATA.

PHYEMAC#RXCHARISK Input

PHYEMAC#RXCHECKINGCRC Input Reserved - tied to GND.

PHYEMAC#RXBUFERR Input Reserved - tied to GND.

PHYEMAC#RXCOMMADET Input Reserved - tied to GND.

PHYEMAC#RXDISPERR Input Disparity error in RXDATA.

PHYEMAC#RXLOSSOFSYNC[1:0] Input Reserved - tied to GND.

PHYEMAC#RXNOTINTABLE Input Indicates non-existent 8B/10 code.

PHYEMAC#RXRUNDISP Input

PHYEMAC#RXCLKCORCNT[2:0] Input Status showing the occurrence of a clock correction.

PHYEMAC#TXBUFERR Input TX buffer error (overflow or underflow).

Receiver Elastic Buffer Status: Bit[1] asserted indicates overflow

or underflow.

K character received or extra data bit in RXDATA. When

RXNOTINTABLE is asserted, this signal becomes the tenth bit in

RXDATA.

Running disparity in the received serial data. When

RXNOTINTABLE is asserted in RXDATA, this signal becomes

the ninth data bit.

Tab le 2 -1 6 shows the PCS/PMA signals.

Table 2-16: PCS/PMA Signals

Signal Direction Description

PHYEMAC#PHYAD[4:0] Input

PHYEMAC#SIGNALDET Input

EMAC#CLIENTANINTERRUPT Output Interrupt upon auto-negotiation.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 35

UG074 (v2.2) February 22, 2010

Physical interface address of MDIO register set for the PCS

sublayer.

Signal direct from PMD sublayer indicating the presence of light

detected at the optical receiver, as defined in IEEE Std 802.3,

Clause 36. If asserted High, the optical receiver has detected light.

If deasserted Low, indicates the absence of light.

If unused, this signal should be tied High for correct operation.

Page 36

Chapter 2: Ethernet MAC Architecture

www.BDTIC.com/XILINX

R

36 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 37

R

www.BDTIC.com/XILINX

Chapter 3

Client, Host, and MDIO Interfaces

This chapter provides useful design information for user interaction with the Virtex®-4

FPGA Tri-Mode Ethernet MAC. It contains the following sections:

• “Client Interface,” page 37

• “Host Interface,” page 72

• “MDIO Interface,” page 93

Client Interface

The client interface is designed for maximum flexibility for matching the client switching

fabric or network processor interface.

Both the transmit and receive data pathway can be configured to be either 8 bits wide or

16 bits wide, with each pathway synchronous to the CLIENTEMAC#TXCLIENTCLKIN

(transmit) or CLIENTEMAC#RXCLIENTCLKIN (receive) for completely independent

full-duplex operation.

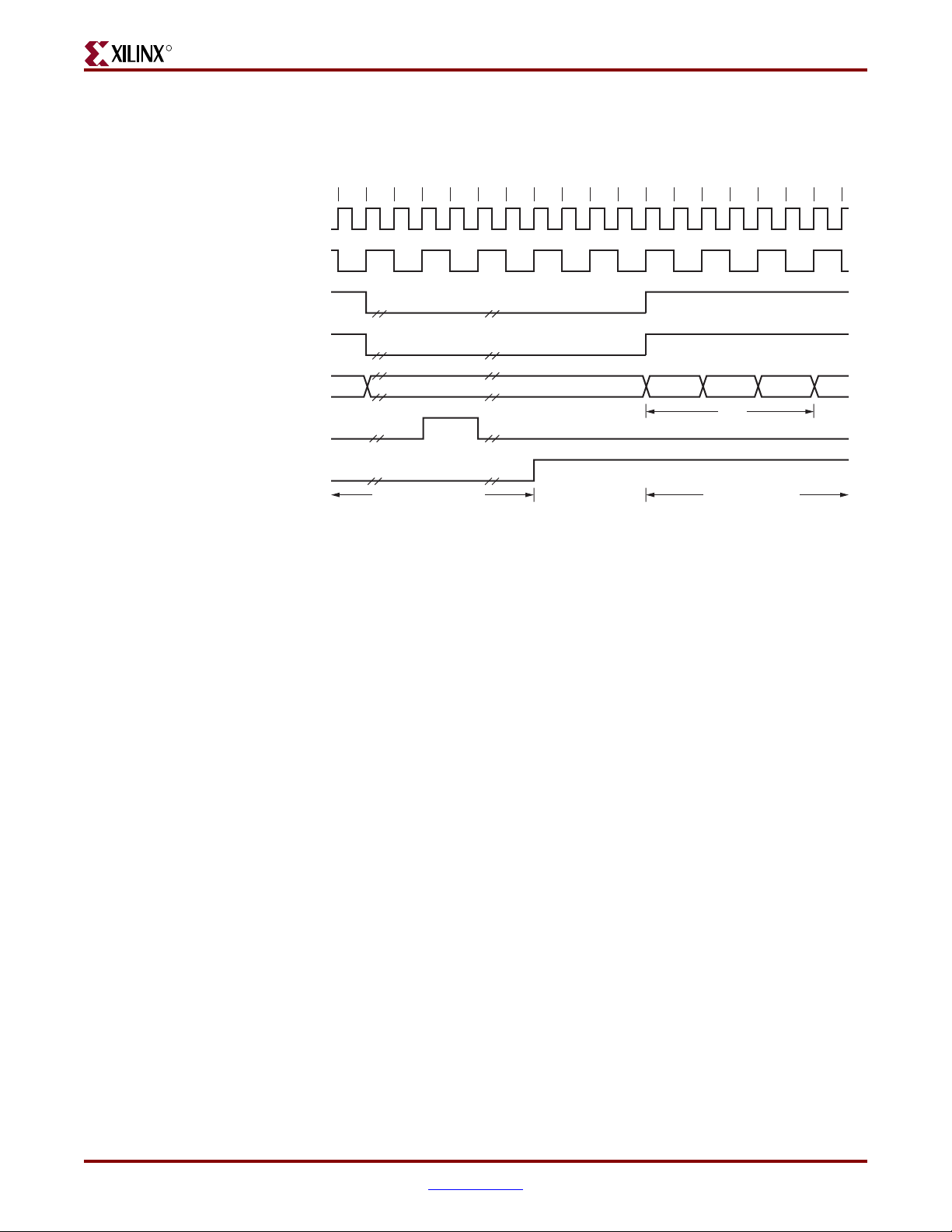

Figure 3-1 shows a block diagram of the transmit client interface. In 16-bit client mode,

PHYEMAC#MIITXCLK functions as CLIENTEMAC#TXCLIENTCLKIN/2.

TIEEMAC#CONFIGVEC[66] selects between an 8-bit or 16-bit client interface.

Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 37

UG074 (v2.2) February 22, 2010

Page 38

Chapter 3: Client, Host, and MDIO Interfaces

www.BDTIC.com/XILINX

R

PHYCLIENT

CLIENTEMAC#TXCLIENTCLKIN

PHYEMAC#MIITXCLK

CLIENTEMAC#TXD[15:0]

CLIENTEMAC#TXDVLDMSW

CLIENTEMAC#TXDVLD

EMAC#CLIENTTXACK

EMAC#CLIENTTXRETRANSMIT

EMAC#CLIENTTXCOLLISION

CLIENTEMAC#TXUNDERRUN

CLIENTEMAC#TXFIRSTBYTE

TIEEMAC#CONFIGVEC[66]

CLIENTEMAC#TXIFGDELAY[7:0]

FPGA Fabric

Tr ansmit

Client

Interface

(Internal Signal)

TX_DATA[7:0]

(Internal Signal)

TX_ACK_EARLY

(Internal Signal)

TX_ACK

(Internal signal)

TX_RETRANSMIT

(Internal Signal)

TX_COLLISION

(Internal Signal)

TX_UNDERRUN

(Internal Signal)

TXFIRSTBYTEREG

(Internal Signal)

TX_IFG_DELAY[7:0]

(Internal Signal)

Tr ansmit

Engine

TX_DATA_VALID

Ethernet MAC Block

Figure 3-1: Transmit Client Block Diagram

PHYEMAC#GTXCLK

EMAC#PHYTXCLK

EMAC#PHYTXD[7:0]

EMAC#PHYTXEN

EMAC#PHYTXER

ug074_3_03_070105

38 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Page 39

R

www.BDTIC.com/XILINX

Client Interface

Figure 3-2 shows a block diagram of the receive client interface. In 16-bit client mode,

PHYEMAC#RXCLK functions as CLIENTEMAC#RXCLIENTCLKIN/2.

TIEEMAC#CONFIGVEC[65] selects between an 8-bit or 16-bit client interface.

CLIENT PHY

CLIENTEMAC#RXCLIENTCLKIN

PHYEMAC#RXCLK

EMAC#CLIENTRXD[15:0]

EMAC#CLIENTRXDVLDMSW

EMAC#CLIENTRXDVLD

EMAC#CLIENTRXGOODFRAME

EMAC#CLIENTRXBADFRAME

CLIENTEMAC#RXCLIENTCLKIN

TIEEMAC#CONFIGVEC[65]

FPGA Fabric