Page 1

VCU118 Evaluation Board

User Guide

UG1224 (v1.0) December 15, 2016

Page 2

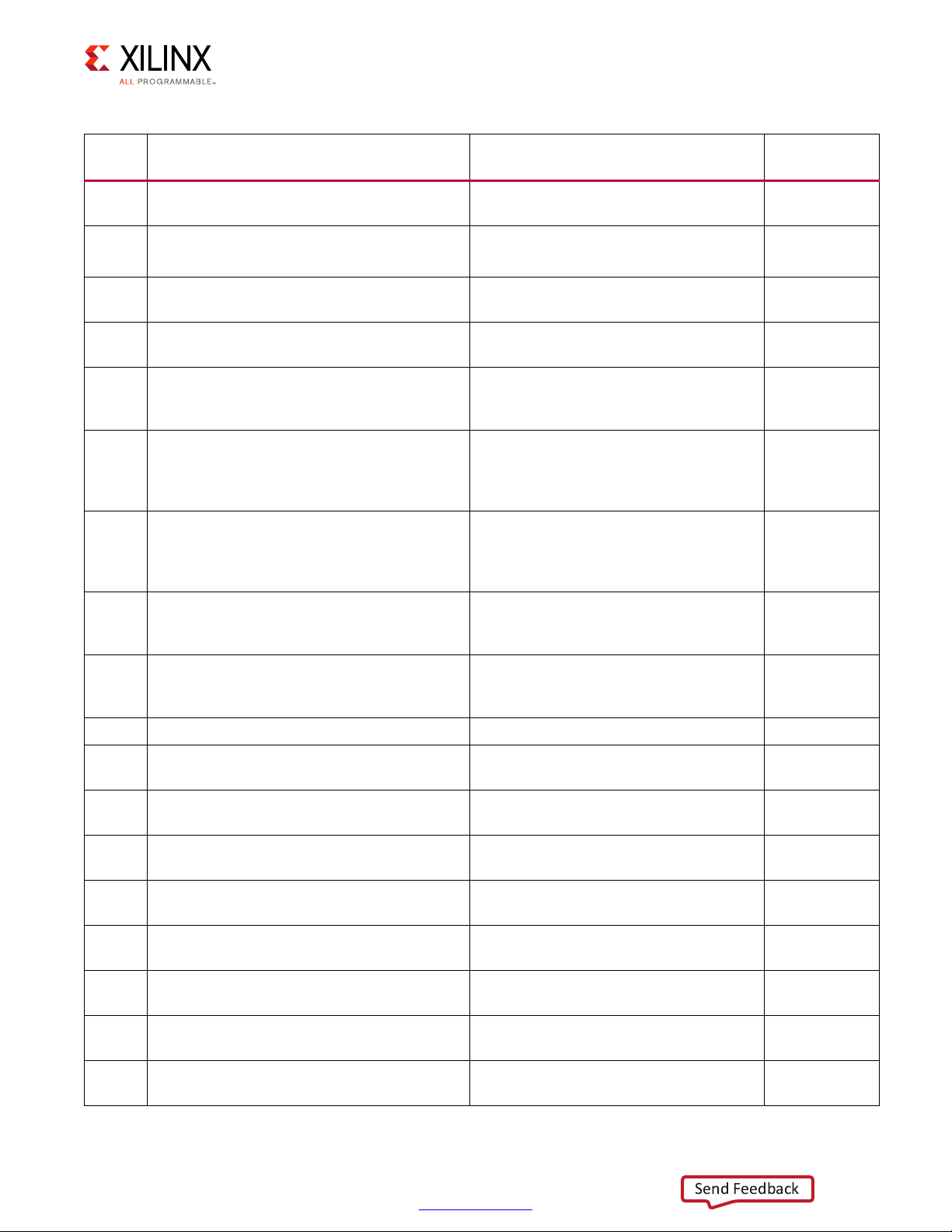

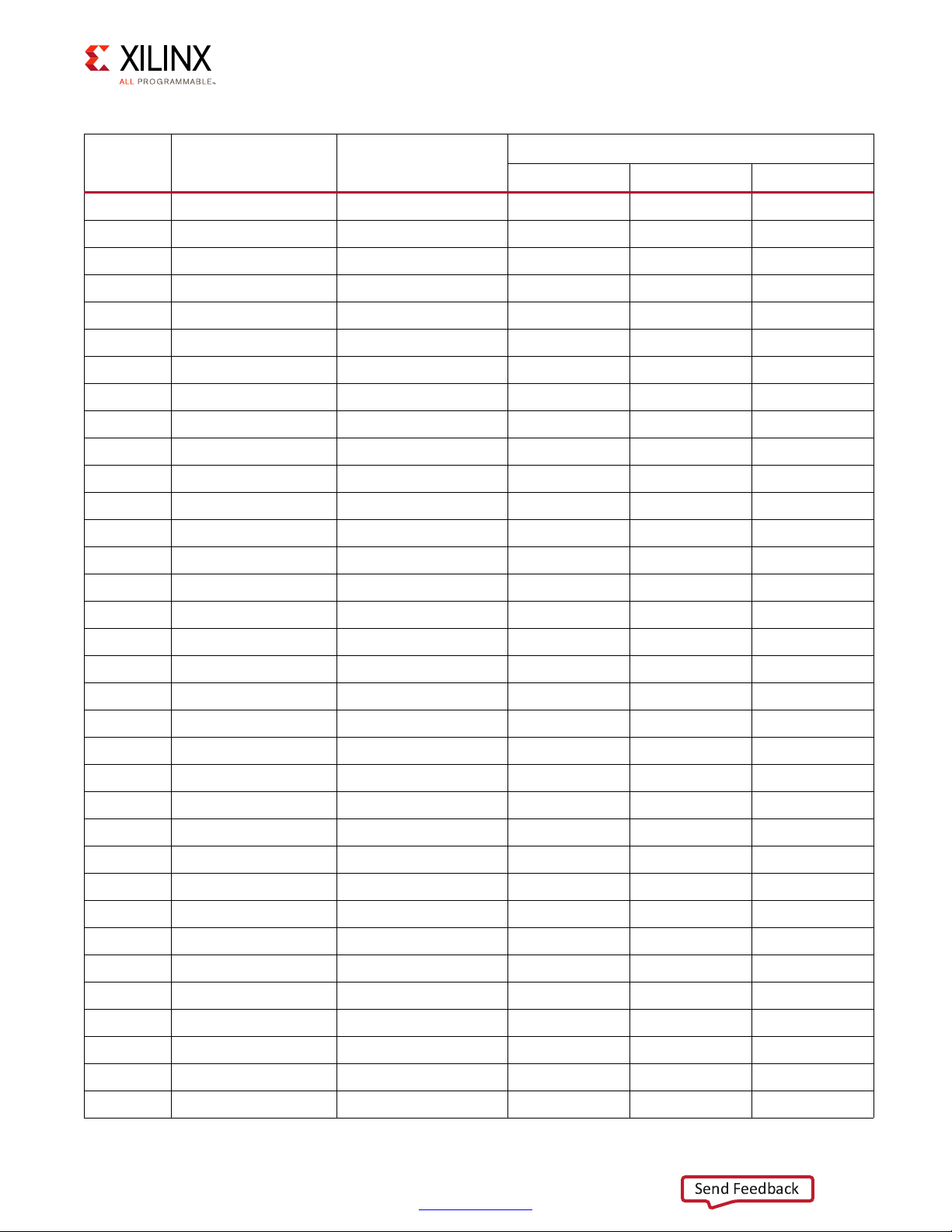

Revision History

Send Feedback

The following table shows the revision history for this document.

Date Version Revision

12/15/2016 1.0 Initial Xilinx release.

VCU118 Board User Guide 2

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 3

Table of Contents

Send Feedback

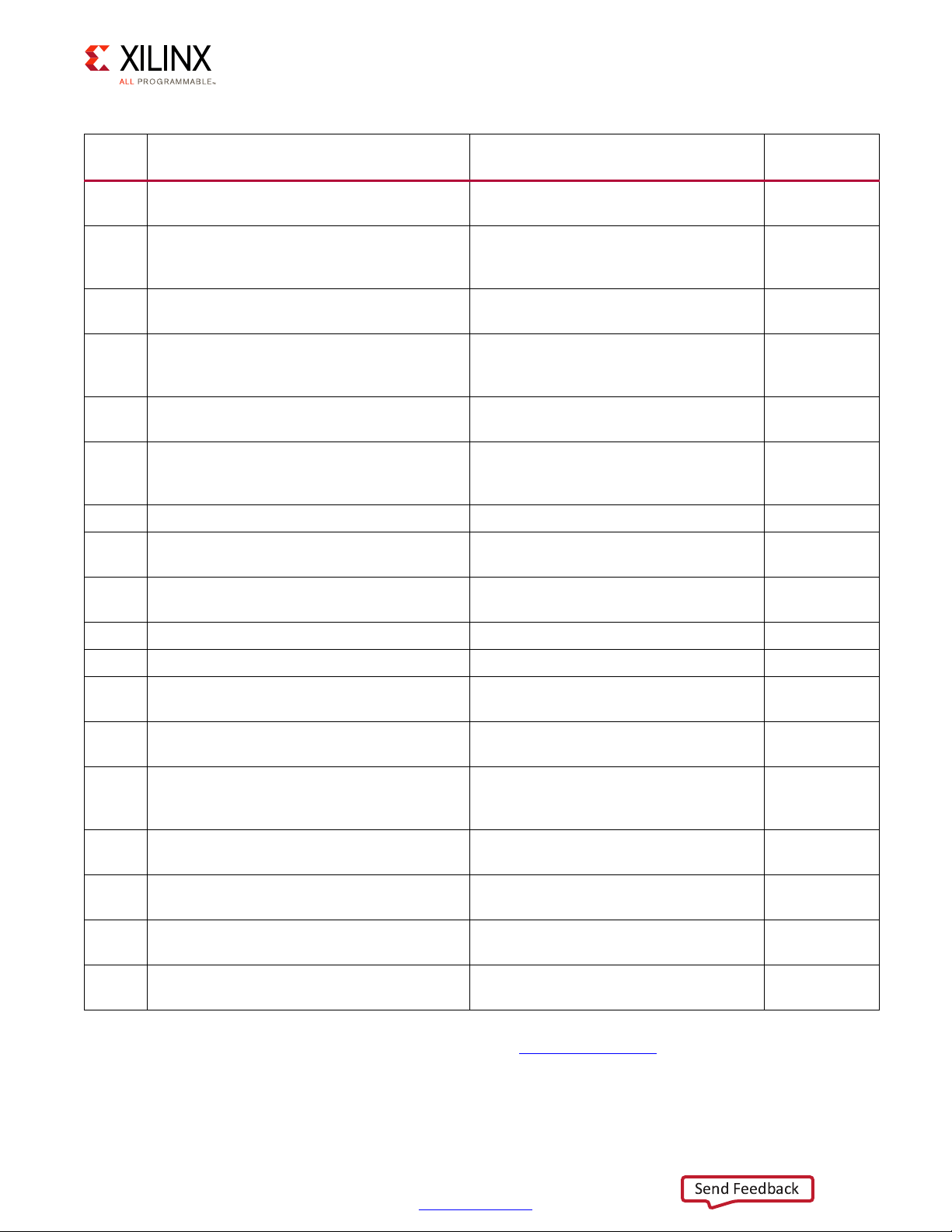

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Chapter 1: Introduction

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Board Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Board Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Environmental . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Operating Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Chapter 2: Board Setup and Configuration

Board Component Location. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Default Switch and Jumper Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Installing the VCU118 Board in a PC Chassis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

FPGA Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Chapter 3: Board Component Descriptions

VCU118 Board User Guide www.xilinx.com 3

UG1224 (v1.0) December 15, 2016

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Component Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Virtex UltraScale+ XCVU9P-L2FLGA2104 Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

DDR4 Component Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

RLD3 Component Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Linear BPI Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Micro-SD Card Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Digilent USB JTAG Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

FMC Connector JTAG Bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

System Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Programmable User Clock 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Programmable User Clock 2 (QSFP Clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

250 MHz Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

User SMA Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Jitter Attenuated Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

GTY Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

PCI Express Endpoint Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Page 4

28 Gb/s QSFP+ Module Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Send Feedback

FireFly Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

10/100/1000 Mb/s Tri-Speed Ethernet PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Ethernet PHY Status LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Dual USB-to-UART Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

I2C Bus, Topology, and Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

Status and User LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

User I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

User GPIO LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

User Pushbuttons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

CPU Reset Pushbutton . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

GPIO DIP Switch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

User Pmod GPIO Headers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

FPGA Mezzanine Card Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

VCU118 Board Power System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

FMC VADJ_1V8 Power Rail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Monitoring Voltage and Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Cooling Fan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

Configuration Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Appendix A: VITA 57.1 and 57.4 FMC Connector Pinouts

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Appendix B: Master Constraints File Listing

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

VCU118 Board Constraints File Listing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Appendix C: Regulatory and Compliance Information

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Declaration of Conformity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Electromagnetic Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

Safety . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

Markings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Appendix D: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Solution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

VCU118 Board User Guide www.xilinx.com 4

UG1224 (v1.0) December 15, 2016

Page 5

Introduction

Send Feedback

Overview

The VCU118 evaluation board for the Xilinx® Virtex® UltraScale+™ FPGA provides a

hardware environment for developing and evaluating designs targeting the UltraScale+

XCVU9P-L2FLGA2104 device. The VCU118 evaluation board provides features common to

many evaluation systems, including:

• DDR4 and RLD3 component memory

• Dual small form-factor pluggable (QSFP+) connector

• Sixteen-lane PCI Express

®

interface

Chapter 1

• Ethernet PHY

• General purpose I/O

•Two UART interfaces

™

• FireFly

Other features can be supported using modules compatible with the VITA-57.1 FPGA

mezzanine card (FMC) and VITA-57.4 FPGA mezzanine card plus high serial pin

(FMC+ HSPC) connectors on the VCU118 board.

Optical x4 28 G connector

Additional Resources

See Appendix D, Additional Resources and Legal Notices for references to documents, files,

and resources relevant to the VCU118 evaluation board.

VCU118 Board User Guide 5

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 6

X-Ref Target - Figure 1-1

X18010-100416

Send Feedback

Chapter 1: Introduction

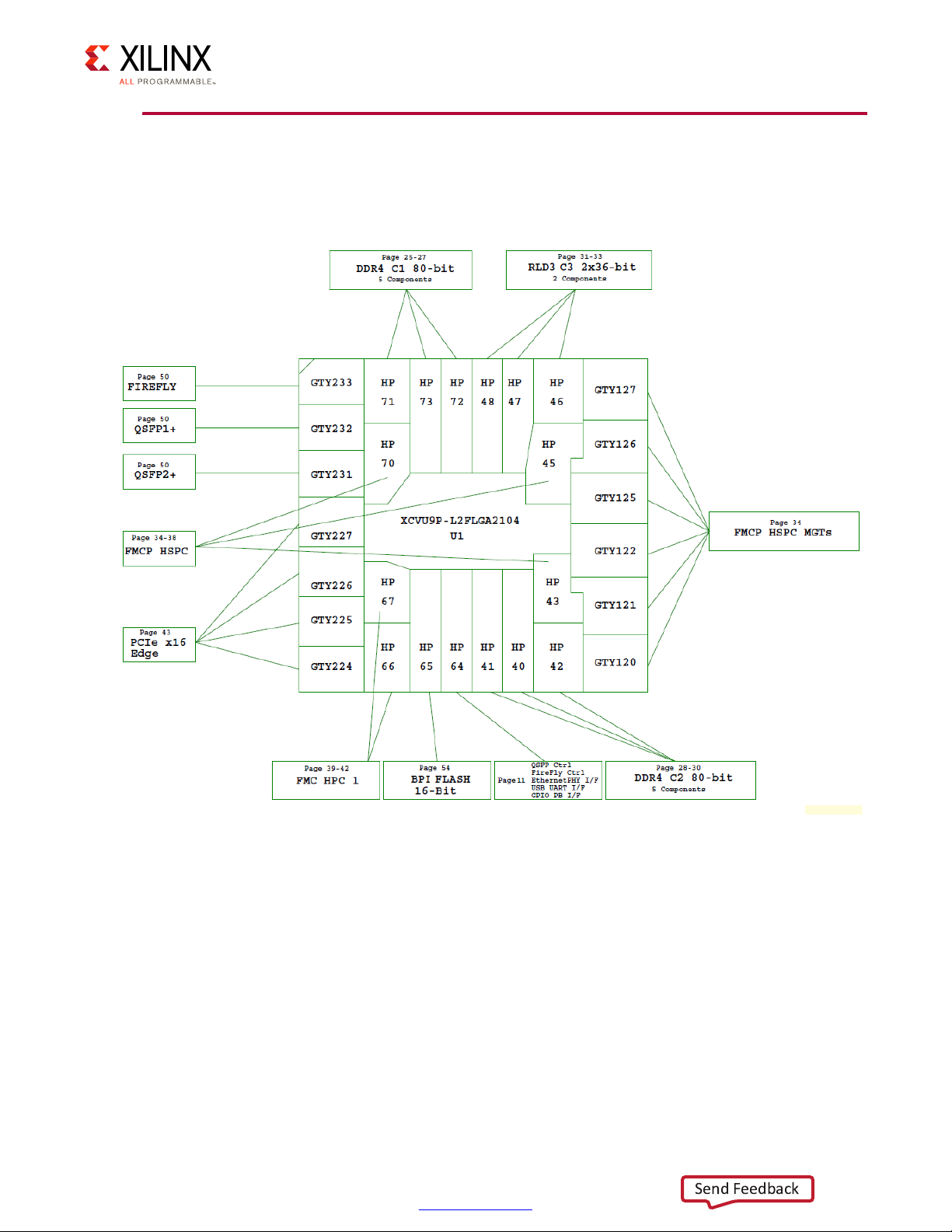

Block Diagram

A block diagram of the VCU118 evaluation board is shown in Figure 1-1.

VCU118 Board User Guide 6

UG1224 (v1.0) December 15, 2016

Figure 1-1: VCU118 Evaluation Board Block Diagram

www.xilinx.com

Page 7

Chapter 1: Introduction

Send Feedback

Board Features

The VCU118 evaluation board features are listed here. Detailed information for each feature

is provided in Component Descriptions in Chapter 3.

• Virtex UltraScale+ XCVU9P-L2FLGA2104 device

®

•Zynq

• Two 2.5 GB DDR4 80-bit component memory interfaces (five [256 Mb x 16] devices

each)

• 288 MB 72-bit RLD3 memory interface comprised of two 1.125 Gb 36-bit devices

• 1 Gb (128 MB) linear x16 BPI flash memory

• USB JTAG interface using a Digilent module with separate micro-B USB connector

• Clock sources:

°

-7000 AP SoC XC7Z010 based system controller

Si5335A quad clock generator

Three Si570 I2C programmable LVDS clock generators

°

One SG5032 fixed 250 MHz LVDS clock generator

°

Si5328B clock multiplier and jitter attenuator for QSFP

°

Subminiature version A (SMA) connectors (differential)

°

• 52 GTY transceivers (13 Quads)

FMC+ HSPC connector (twenty-four GTY transceivers)

°

2x28 Gb/s QSFP+ connectors (eight GTY transceivers)

°

Samtec Firefly connector (four GTY transceiver)

°

PCIe 16-lane edge connector (sixteen GTY transceivers)

°

• PCI Express endpoint connectivity

Gen1 16-lane (x16)

°

Gen2 16-lane (x16)

°

Gen3 8-lane (x8)

°

• Ethernet PHY SGMII interface with RJ-45 connector

VCU118 Board User Guide 7

UG1224 (v1.0) December 15, 2016

• Dual USB-to-UART bridge with micro-B USB connector

2

C bus

•I

•Status LEDs

• User I/O (4-pole DIP switch, 6 each push-button switches, 8 x LED)

www.xilinx.com

Page 8

Chapter 1: Introduction

Send Feedback

• Two Pmod 2x6 connectors (one male pin header, one right-angle receptacle)

• VITA 57.4 FMC+ HSPC connector J22

•VITA 57.1 FMC HPC1 connector J2

• Power management with PMBus voltage monitoring through Maxim power controllers

and GUI

• 10-bit 0.2 MSPS SYSMON analog-to-digital front end

• Configuration options:

BPI linear flash memory

°

Digilent USB configuration module

°

Platform cable USB II interface 2x7 2 mm connector

°

Board Specifications

Dimensions

Height: 6.927 inch (17.59 cm)

Thickness (±5%): 0.061 inch (0.1549 cm)

Length: 9.5 inch (24.13 cm)

Note:

IMPORTANT: The VCU118 board height exceeds the standard 4.376 inch (11.15 cm) height of a PCI

Express® card.

A 3D model of this board is not available.

Environmental

Temp erature

Operating: 0°C to +45°C

Storage: -25°C to +60°C

VCU118 Board User Guide 8

UG1224 (v1.0) December 15, 2016

Humidity

10% to 90% non-condensing

www.xilinx.com

Page 9

Operating Voltage

Send Feedback

Chapter 1: Introduction

+12 V

DC

VCU118 Board User Guide 9

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 10

Board Setup and Configuration

Send Feedback

Board Component Location

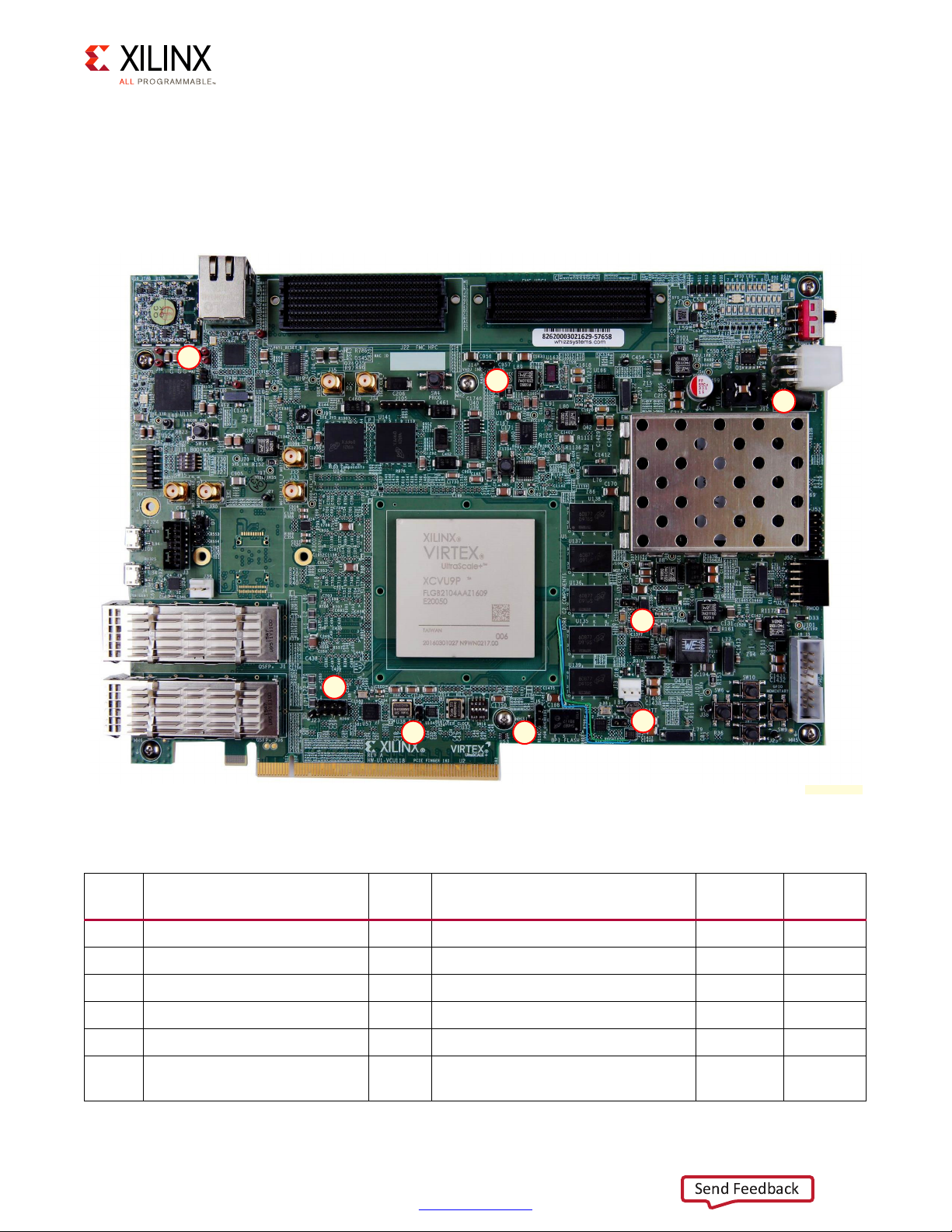

Figure 2-1 shows the VCU118 board component locations. Each numbered component

shown in the figure is keyed to Table 2-1. Table 2-1 identifies the components, references

the respective schematic page numbers, and links to a detailed functional description of the

components and board features in Chapter 3.

IMPORTANT: Figure 2-1 is for visual reference only and might not reflect the current revision of the

board.

CAUTION! The VCU118 board can be damaged by electrostatic discharge (ESD). Follow standard ESD

prevention measures when handling the board.

Chapter 2

VCU118 Board User Guide 10

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 11

X-Ref Target - Figure 2-1

Round callout references a component

on the front side of the board

Square callout references a component

on the backside side of the board

9

7

20

19

36

28

38

8

21

14

18

26

17

4

C1

40

5

33

34

22

15

27

23

24

30

39

29

37

25

11

31

31

4

C2

16

13 12 35

6 10

11

2

1

3

00

00

41

X18022-102616

Send Feedback

Chapter 2: Board Setup and Configuration

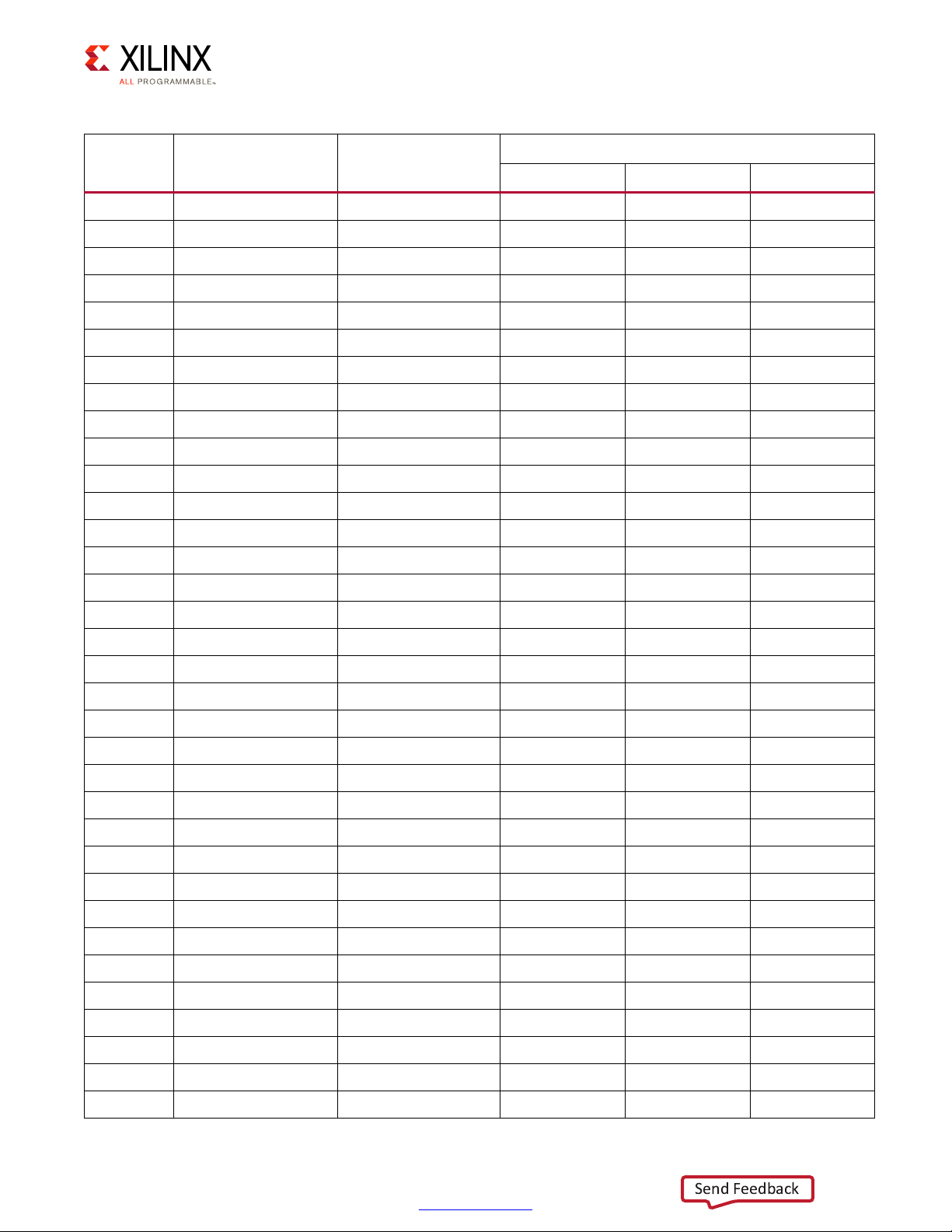

Table 2-1: VCU118 Board Component Descriptions

Callout Feature Notes

VCU118 Board User Guide 11

UG1224 (v1.0) December 15, 2016

Virtex UltraScale+ XCVU9P-L2FLGA2104

1

Device, (with fan-sink on soldered FPGA)

GTY transceivers, Right Side Quads (six

2

quads)

GTY transceivers, Left Side Quads (seven

3

quads)

DDR4 Component Memory, two 80-bit DDR4

4

component memory I/F, C1 (U60-U64)

Figure 2-1: VCU118 Evaluation Board Components

(bottom) and C2 (U135-U139) (top)

RLD3 Component Memory, RLD3 72-bit

5

component memory I/F C3 (U141-U142)

www.xilinx.com

XCVU9P-L2FLGA2104E

Cofan 30-5530-03

Embedded within FPGA U1 14-15

Embedded within FPGA U1 16-17

C1: 5 x Micron MT40A256M16GE-075E,

C2: 5 x Micron MT40A256M16GE-075E

Micron MT44K32M36RB-083F 31-32

Schematic

Page Number

25-27,

28-30

Page 12

Table 2-1: VCU118 Board Component Descriptions (Cont’d)

Send Feedback

Chapter 2: Board Setup and Configuration

Callout Feature Notes

Linear BPI Flash Memory, BPI 16-bit

6

7

8

9

10

11

12

configuration memory 1 Gb (U133)

Micro-SD Card Interface, (bottom)

Micro-SD card interface connector (J83)

Digilent USB JTAG Module, USB JTAG micro-B

connector (J106)

Digilent USB JTAG Module (U115), with

micro-B connector

Clock Generation, multi-output clock

generator, SYSCLK and other clocks, 1.8V

LVDS (U122)

System Clock, programmable user clock

Si570_0, I

LVDS (U18) (bottom) with 1-to-2 LVDS

MUX/buffer (U157) (top)

Programmable User Clock 1, programmable

user clock Si570_1, I

clock, 3.3V LVDS (U32) with 1-to-2 LVDS

MUX/buffer (U104)

2

C programmable user clock, 3.3V

2

C programmable user

Micron MT28GU01GAAA1EGC-0SIT 54

Molex 5025700893 49

Hirose ZX62D-AB-5P8 24

Digilent JTAG-SMT2-NC 24

SI5335A-B02436-GM, 4 outputs:

300 MHz, 125 MHz, 90 MHz, 33.33 MHz

Silicon Labs SI570BAB0000544DG

(default 156.250 MHz) with Si53340

MUX/buffer

Silicon Labs SI570BAB0000544DG

(default 156.250 MHz) with Si53340

MUX/buffer

Schematic

Page Number

44

44

45

Programmable User Clock 2 (QSFP Clock),

13

14

15 User SMA Clock pair J34(P)/J35(N) Rosenberger 32K10K-400L5 45

16

17

18

19

20

21

22

23

programmable user clock Si570_2, I

programmable user clock, 3.3V LVDS (U38)

250 MHz Clock, fixed SG5032 250 MHz user

clock, 3.3V LVDS (U14) (bottom) with 1-to-2

LVDS MUX/buffer (U21) (bottom)

Jitter Attenuated Clock, jitter attenuated

QSFP clock (U57)

PCI Express Endpoint Connectivity, PCI

Express connector (P1)

Two 28 Gb/s QSFP+ Module Connectors,

QSFP1 (U145), QSFP2 (U123)

10/100/1000 Mb/s Tri-Speed Ethernet PHY

with RJ45, SGMII mode only, (U7, J10)

Ethernet PHY Status LEDs, LEDs are

integrated into J10 bezel

Dual USB-to-UART Bridge, bridge device

(U34) with mini-B connector (J4)

I2C Bus, Topology, and Switches, I

2

C bus MUX (U28) (bottom)

I

I2C Bus, Topology, and Switches, I

2

C bus MUX (U80)

I

2

C

2

C bus,

2

C bus,

Silicon Labs SI570BAB0000544DG

(default 156.250 MHz)

Epson SG5032VAN_250.000000M-KEGA3

with ICS85411AMLF 1-to-2 buffer

Silicon Labs SI5328B 51

8-lane card edge connector 43

Amphenol FS1-Z38-20Z6-10 50

TI DP83867ISRGZ with Wurth

7499111221A RJ45 (with magnetics)

Wurth 7499111221A RJ45 integrated

status LEDs

Silicon Labs CP2105-F01-GM bridge,

Hirose ZX62D-AB-5P8 connector

TI TCA9548APWR 58

TI TCA9548APWR 58

45

45

52

52

53

VCU118 Board User Guide 12

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 13

Table 2-1: VCU118 Board Component Descriptions (Cont’d)

Send Feedback

Chapter 2: Board Setup and Configuration

Callout Feature Notes

24

25

26

27

28

29

30 Switches, power on/off slide switch SW1 C&K 1201M2S3AQE2 59

31

32

User GPIO LEDs (DS6-DS10, DS12, DS13,

DS18)

User Pushbuttons, (SW10, SW17, SW9, SW6,

SW7), CPU reset pushbutton (SW5) all

active-High

GPIO DIP Switch, GPIO DIP switch (SW12)

(bottom)

Program_B Pushbutton Switch, program_B

pushbutton switch, FPGA PROG pushbutton

(SW4)

VCU118 XC7Z010 system controller, mode

switch DIP, switch (SW15)

User Pmod GPIO Headers, (J52 right-angle

receptacle, J53 male pin header) (top) with

level shifters (U41,U42) (bottom)

VCU118 Board Power System, power

management system (top and bottom)

Monitoring Voltage and Current, power

management voltage and current sensing

GPIO LEDs, green 0603 Lumex

SML-LX0603GW-TR

E-Switch TL3301EF100QG (north, south,

east, west, center pattern)

4-pole CTS 218-4LPSTRF 55

E-Switch TL3301EF100QG 55

4-pole CTS 218-4LPSTRF 49

J52 Sullins PPPC062LJBN-RC,

J53 Sullins PBC36DAAN,

NXP NVT2008PW

Maxim MAX20751E and MAX15301

dig-ital P.O.L. controllers

TI Current and Power Monitor

INA226AIDGS

Page Number

Schematic

55

55

57

60-75

60-67

33 GTY Transceivers, FMCP HSPC connector J22 Samtec ASP_184329_01 34-38

34 FMC HPC1 Connector J2 Samtec ASP_134486_01 39-42

35

36

37

38

39

41 FireFly Connector, signal and power pair (J6)

40

Notes:

1. The VCU118 board schematics are available for download. See the VCU118 Evaluation Kit.

2. The VCU118 board jumper header locations are shown in Figure 2-2.

Configuration Options, FPGA U1

configuration mode DIP switch, (SW16)

System Controller, VCU118 Zynq-7000 AP

SoC XC7Z010CLG225 (U111)

Monitoring Voltage and Current, VCU118

board power system 2x8 shrouded PMBus

connector (J39)

Digilent USB JTAG Module, USB JTAG

module, shrouded JTAG cable connector (J3)

Power On/Off Slide Switch SW1, power input

connector (J15)

PCI Express Endpoint Connectivity, lane

width select header, (J7)

4-pole CTS 218-4LPSTRF 3

XC7Z010CLG225 46-49

ASSMAN AWHW16G-0202 59

2x7 2 mm Molex 87832-1420 24

2x6 Molex-39-30-1060 59

Samtec Signal: UEC5-019-2-H-D-RA-1,

Samtec Power: UCC8-10-1-H-S-1-A

2x4 0.1 inch male header Sullins

PBC36DAAN

50

43

VCU118 Board User Guide 13

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 14

Default Switch and Jumper Settings

Send Feedback

Switches

Default switch settings are listed in Table 2-2. Switch locations are shown in Figure 2-1.

Table 2-2 also references the respective schematic page numbers.

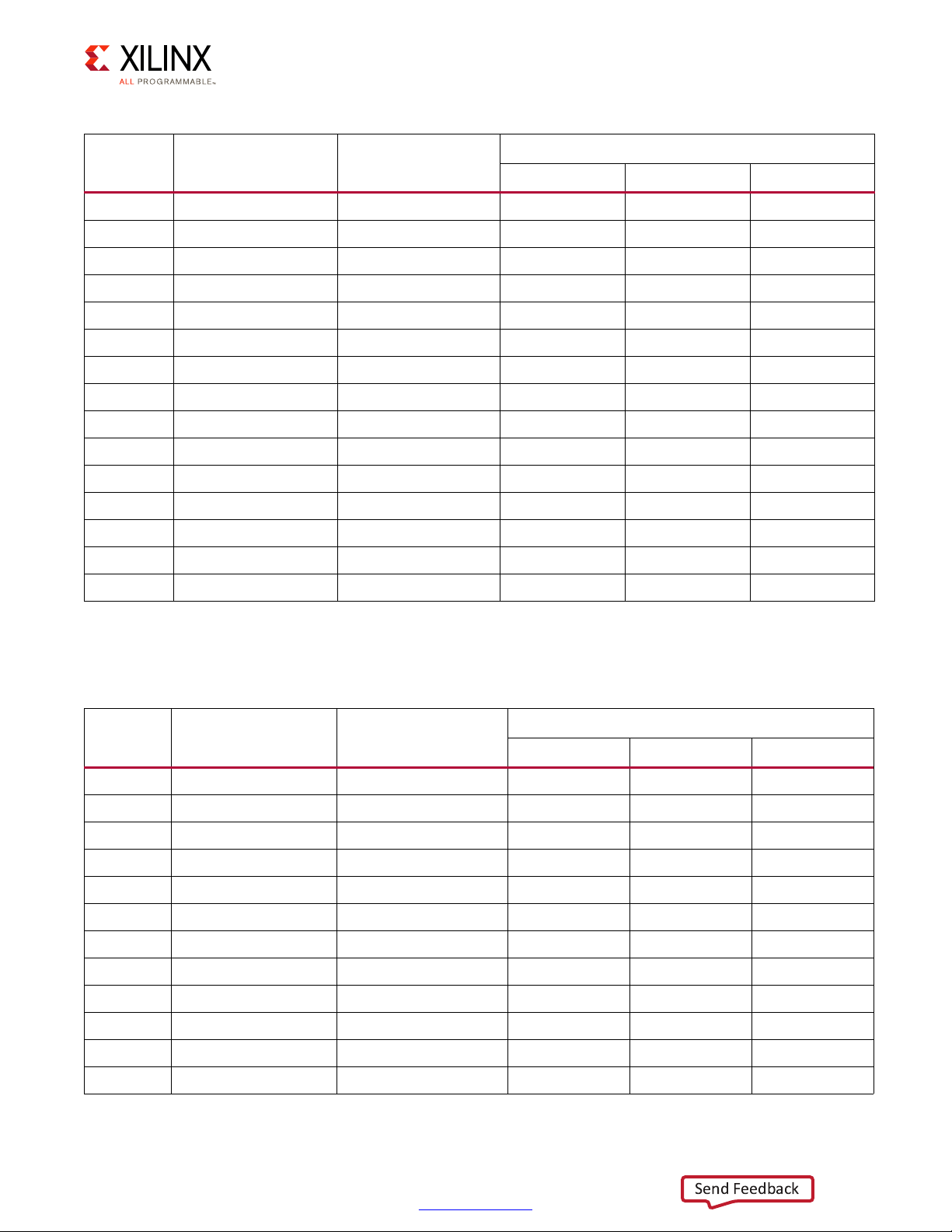

Table 2-2: Default Switch Settings

Chapter 2: Board Setup and Configuration

Switch Function Default Comments

SW1 SPST slide switch OFF Board shipped with power switch off 30 59

SW12 4-pole GPIO 0000 Positions 1-4, GPIO 26 55

SW15 4-pole configuration 0000

SW16 4-pole configuration 0101

Notes:

1. DIP switches are active-High (connected net is pulled High when DIP switch is closed).

Positions 1-4, Zynq-7000 AP SoC System

Controller U111

Position 1, System Controller Enable

Positions 2-4, FPGA U1 mode M[2:0]

Figure 2-1

Callout

28 49

35 3

Schematic

Page

VCU118 Board User Guide 14

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 15

X-Ref Target - Figure 2-2

8

6

5

7

3

14

2

X18026-100416

Send Feedback

Chapter 2: Board Setup and Configuration

Jumpers

Figure 2-2 shows the VCU118 board jumper header locations. Each numbered component

shown in the figure is keyed to Table 2-3, which identifies the default jumper settings and

references the respective schematic page numbers.

Table 2-3: Default Jumper Settings

Jumper Function Default Comments

J12 Maxim regulator inhibit Off Used when programming PWR. SYS. 5 59

J14 U30 VADJ_1V8 enable Off

VCU118 Board User Guide 15

UG1224 (v1.0) December 15, 2016

Figure 2-2: VCU118 Board Header Jumper Locations

J5 Power on reset (POR) override 2-3 U1 POR_OVERRIDE pin AG12 to GND 1 3

J7 PCIe lane size select 7-8 16-lane configuration 2 43

J8 SYSCLK source select Off SI5335A 300 MHz default 3 44

J9 USER/MGT_SI570 source select Off SI570 U32 156.250 MHz 4 45

Input to U25 AND, VADJ_1V8

enabled

Figure 2-2

Schematic

Callout

663

Page

www.xilinx.com

Page 16

Table 2-3: Default Jumper Settings (Cont’d)

X17987-100416

Send Feedback

Chapter 2: Board Setup and Configuration

Jumper Function Default Comments

J29 BPI Flash A25 source select 1-2 A25 connected to FPGA U1 pin BE17 7 54

J110

Zynq-7000 AP SoC System

Controller U111 QSPI_IO3

Off

QSPI_IO3 P/U w/20K (On = P/D to

GND)

Figure 2-2

Callout

847

Installing the VCU118 Board in a PC Chassis

Installation of the VCU118 board inside a computer chassis is required when developing or

testing PCI Express® functionality.

When the VCU118 board is used inside a computer chassis (that is, plugged in to the PCIe®

slot), power is provided from the ATX power supply 4-pin peripheral connector through the

ATX adapter cable (Figure 2-3) to J15 on the VCU118 board. The Xilinx part number for this

cable is 2600304. See [Ref 29] for ordering information.

X-Ref Target - Figure 2-3

Schematic

Page

VCU118 Board User Guide 16

UG1224 (v1.0) December 15, 2016

Figure 2-3: ATX Power Supply Adapter Cable

To install the VCU118 board in a PC chassis:

1. On the VCU118 board, remove the six screws retaining the six rubber feet with their

standoffs, and the PCIe bracket. Reinstall the PCIe bracket using two of the previously

removed screws.

2. Power down the host computer and remove the power cord from the PC.

3. Open the PC chassis following the instructions provided with the PC.

4. Select a vacant PCIe expansion slot and remove the expansion cover (at the back of the

chassis) by removing the screws on the top and bottom of the cover.

www.xilinx.com

Page 17

Chapter 2: Board Setup and Configuration

Send Feedback

5. The VCU118 board requires three adjacent PCIe slots. The VCU118 board has a large

cooling fan that exceeds the PCIe top side component height restriction and has several

spring loaded screws on the back side of the board. Ensure the slots closest to the front

and back of the board are free of obstructions.

6. Plug the VCU118 board into the center of the three open slots.

7. Install the top mounting bracket screw into the PC expansion cover retainer bracket to

secure the VCU118 board in its slot.

8. Connect the ATX power supply to the VCU118 board using the ATX power supply

adapter cable as shown in Figure 2-3.

a. Plug the 6-pin 2 x 3 Molex connector on the adapter cable into J15 on the VCU118

board.

b. Plug the 4-pin 1 x 4 peripheral power connector from the ATX power supply into the

4-pin adapter cable connector.

CAUTION! Do NOT plug a PC ATX power supply 6-pin connector into J15 on the VCU118 evaluation

board. The ATX 6-pin connector has a different pin out than J15. Connecting an ATX 6-pin connector

into J15 damages the VCU118 evaluation board and voids the board warranty.

9. Slide the VCU118 board power switch SW1 to the ON position. The PC can now be

powered on.

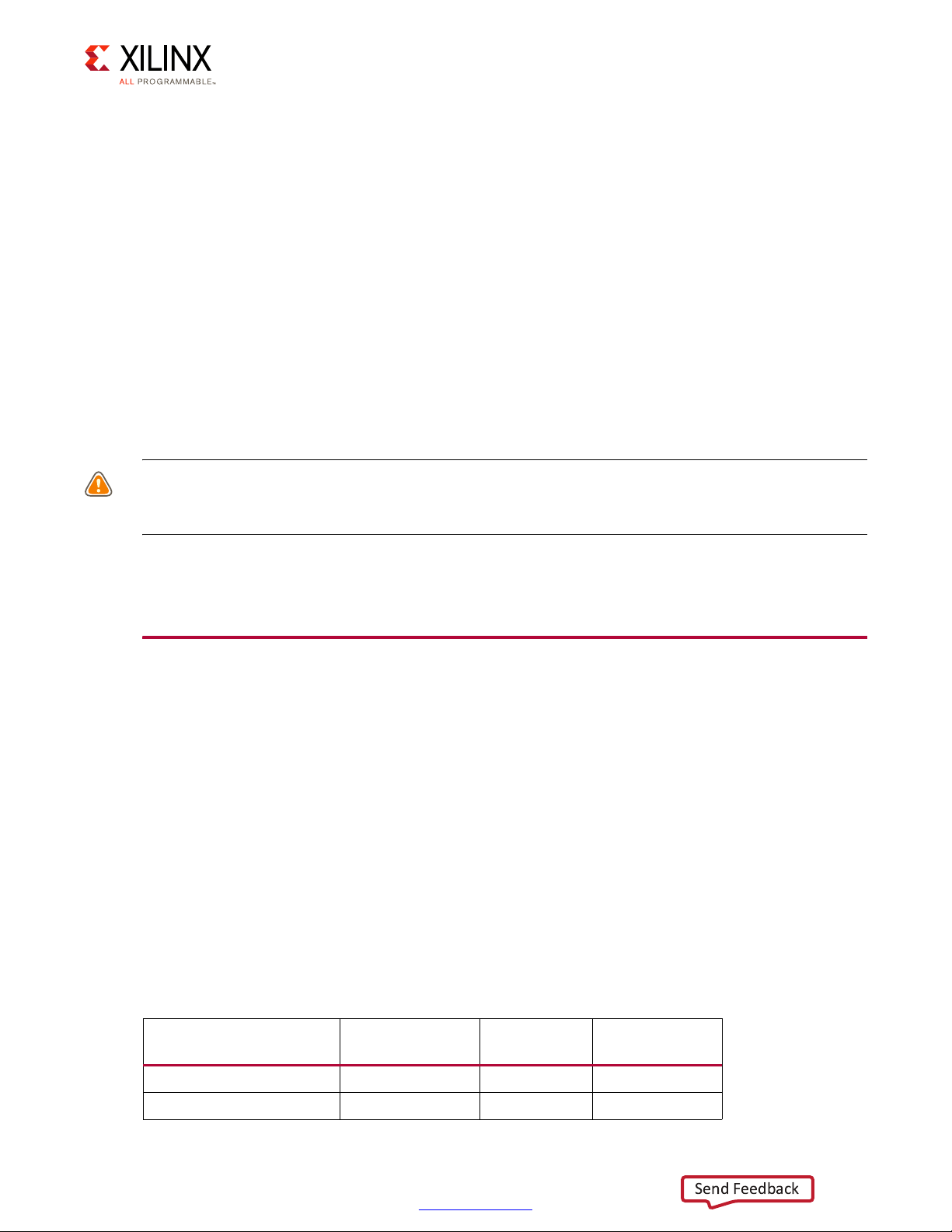

FPGA Configuration

The VCU118 board supports two of the seven UltraScale FPGA configuration modes:

• Master BPI using the onboard linear BPI flash memory

•JTAG using:

USB JTAG configuration port (Digilent module U115)

°

Platform cable USB 2.0, 2 mm, keyed flat cable header (J3)

°

Each configuration interface corresponds to one or more configuration modes and bus

widths, as listed in Table 2-4. The mode switches M2, M1, and M0 are on SW16 positions 2,

3, and 4, respectively. The FPGA default mode setting M[2:0] = 101 selects the JTAG

configuration mode.

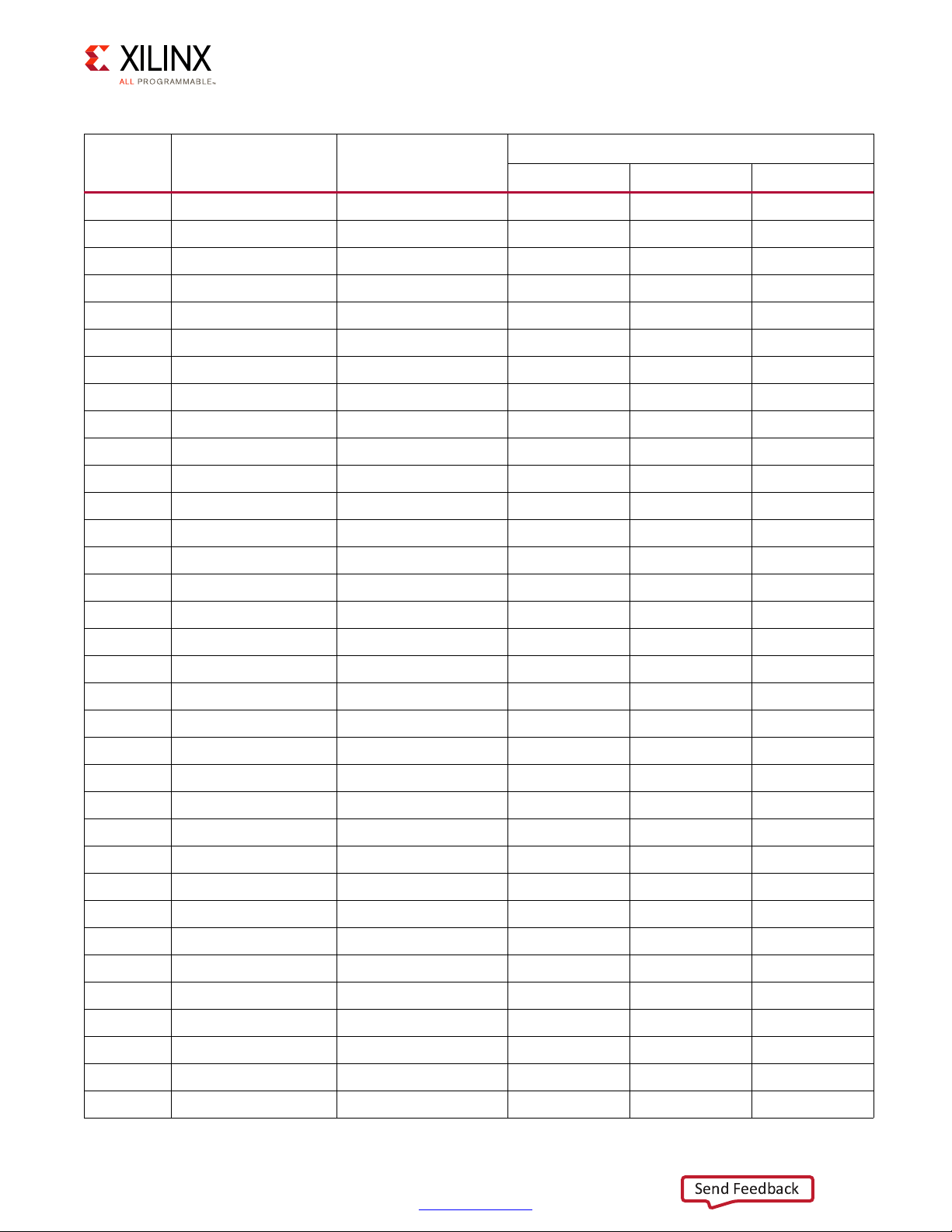

Table 2-4: Configuration Modes

VCU118 Board User Guide 17

UG1224 (v1.0) December 15, 2016

Configuration Mode

Master BPI 010 x8,x16 Output

JTAG 101 x1 Not Applicable

SW16 DIP Switch

Settings M[2:0]

Bus Width CCLK Direction

www.xilinx.com

Page 18

Chapter 2: Board Setup and Configuration

;

Send Feedback

For complete details on configuring the FPGA, see UltraScale Architecture Configuration

User Guide (UG570) [Ref 2].

Figure 2-4 shows the configuration mode DIP switch SW16 default switch positions.

X-Ref Target - Figure 2-4

Figure 2-4: SW16 Default Settings

VCU118 Board User Guide 18

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 19

Board Component Descriptions

Send Feedback

Overview

This chapter provides a detailed functional description of the board’s components and

features. Table 2-1, page 11 identifies the components, references the respective schematic

page numbers, and links to the corresponding detailed functional description in this

chapter. Component locations are shown in Figure 2-1, page 11.

Component Descriptions

Chapter 3

Virtex UltraScale+ XCVU9P-L2FLGA2104 Device

[Figure 2-1, callout 1]

The VCU118 board is populated with the Virtex UltraScale+ XCVU9P-L2FLGA2104 device.

For more information on Virtex UltraScale+ FPGAs, see Virtex UltraScale+ FPGAs Data

Sheet: DC and AC Switching Characteristics (DS923) [Ref 1].

VCU118 Board User Guide 19

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 20

Chapter 3: Board Component Descriptions

To VBATT pin

U1.AT11

X18008-100416

Send Feedback

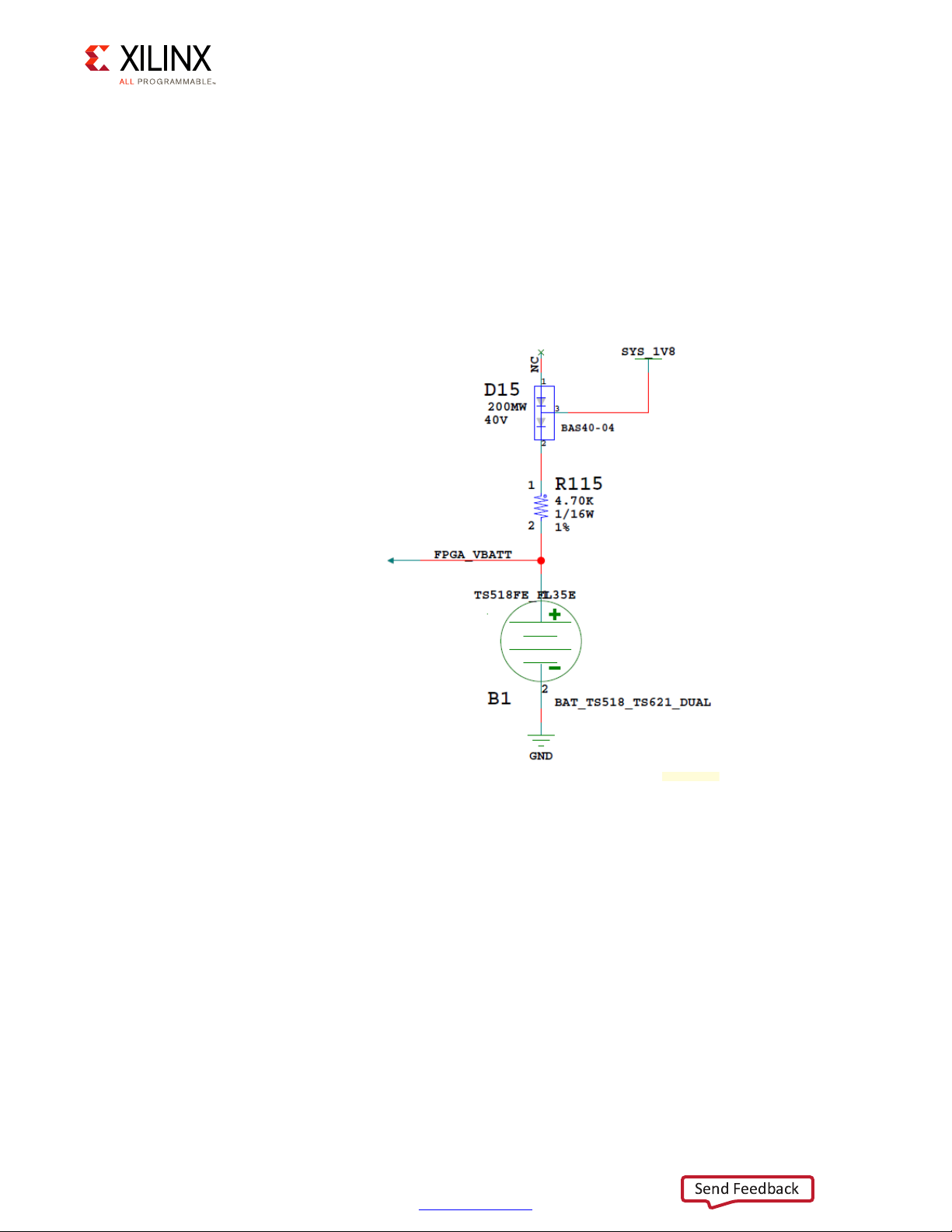

Encryption Key Battery Backup Circuit

The XCVU9P device U1 implements bitstream encryption key technology. The VCU118

board provides the encryption key backup battery circuit shown in Figure 3-1. The Seiko

TS518FE rechargeable 1.5V lithium button-type battery B1 is soldered to the board with the

positive output connected to the XCVU9P device U1 VBATT pin AT11. The battery supply

current I

from the SYS_1V8 1.8V rail through a series diode with a typical forward voltage drop of

0.38V and 4.7 KΩ current limit resistor. The nominal charging voltage is 1.42V.

X-Ref Target - Figure 3-1

specification is 150 nA maximum when the board power is off. B1 is charged

BATT

VCU118 Board User Guide 20

UG1224 (v1.0) December 15, 2016

Figure 3-1: Encryption Key Backup Circuit

www.xilinx.com

Page 21

Chapter 3: Board Component Descriptions

Send Feedback

I/O Voltage Rails

There are 16 I/O banks available on the XCVU9P device and the VCU118 board. The voltages

applied to the FPGA I/O banks used by the VCU118 board are listed in Table 3-1.

Table 3-1: I/O Bank Voltage Rails

FPGA (U1) Bank Power Supply Rail Net Name Voltage

Bank 0 VCC1V8_FPGA 1.8V

HP Bank 40 VCC1V2_FPGA 1.2V

HP Bank 41 VCC1V2_FPGA 1.2V

HP Bank 42 VCC1V2_FPGA 1.2V

HP Bank 43 VADJ_1V8_FPGA 1.8V

HP Bank 45 VADJ_1V8_FPGA 1.8V

HP Bank 46 VCC1V2_FPGA 1.2V

HP Bank 47 VCC1V2_FPGA 1.2V

HP Bank 48 VCC1V2_FPGA 1.2V

HP Bank 64 VCC1V8_FPGA 1.8V

HP Bank 65 VCC1V8_FPGA 1.8V

HP Bank 66 VADJ_1V8_FPGA 1.8V

HP Bank 67 VADJ_1V8_FPGA 1.8V

HP Bank 70 VADJ_1V8_FPGA 1.8V

HP Bank 71 VCC1V2_FPGA 1.2V

HP Bank 72 VCC1V2_FPGA 1.2V

HR Bank 73 VCC1V2_FPGA 1.2V

VCU118 Board User Guide 21

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 22

Chapter 3: Board Component Descriptions

Send Feedback

DDR4 Component Memory

[Figure 2-1, callout 4]

The 2.5 GB DDR4 component memory system is comprised of two sets of five 256 Mb x 16

(80-bit wide) DDR4 SDRAM devices (Micron MT40A256M16GE-075E) located at U60-U64

(C1) and U135-U139 (C2). This dual memory system is connected in 80-bit wide interfaces

to the U1 XCVU9P HP banks 71, 72, 73 (C1) and 40, 41, 42 (C2). The DDR4 0.6V VTT

termination voltages (nets DDR4_C1_VTT and DDR4_C2_VTT) are sourced from the TI

TPS51200DR linear regulators U24 and U134. The DDR4 memory interface bank VREF pins

are not connected, which, coupled with an XDC set_property INTERNAL_VREF constraint,

invoke the INTERNAL VREF mode. The connections between the C1 80-bit interface DDR4

component memories and XCVU9P banks 71, 72, and 73 are listed in Table 3-2.

Table 3-2: DDR4 Memory 80-bit I/F C1 to FPGA U1 Banks 71, 72, and 73

FPGA (U1)

Pin

F11 DDR4_C1_DQ0 POD12_DCI G2 DQL0 U60

E11 DDR4_C1_DQ1 POD12_DCI F7 DQL1 U60

F10 DDR4_C1_DQ2 POD12_DCI H3 DQL2 U60

F9 DDR4_C1_DQ3 POD12_DCI H7 DQL3 U60

H12 DDR4_C1_DQ4 POD12_DCI H2 DQL4 U60

G12 DDR4_C1_DQ5 POD12_DCI H8 DQL5 U60

E9 DDR4_C1_DQ6 POD12_DCI J3 DQL6 U60

D9 DDR4_C1_DQ7 POD12_DCI J7 DQL7 U60

R19 DDR4_C1_DQ8 POD12_DCI A3 DQU0 U60

P19 DDR4_C1_DQ9 POD12_DCI B8 DQU1 U60

M18 DDR4_C1_DQ10 POD12_DCI C3 DQU2 U60

M17 DDR4_C1_DQ11 POD12_DCI C7 DQU3 U60

N19 DDR4_C1_DQ12 POD12_DCI C2 DQU4 U60

N18 DDR4_C1_DQ13 POD12_DCI C8 DQU5 U60

N17 DDR4_C1_DQ14 POD12_DCI D3 DQU6 U60

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

VCU118 Board User Guide 22

UG1224 (v1.0) December 15, 2016

M16 DDR4_C1_DQ15 POD12_DCI D7 DQU7 U60

D11 DDR4_C1_DQS0_T DIFF_POD12_DCI G3 DQSL_T U60

D10 DDR4_C1_DQS0_C DIFF_POD12_DCI F3 DQSL_C U60

P17 DDR4_C1_DQS1_T DIFF_POD12_DCI B7 DQSU_T U60

P16 DDR4_C1_DQS1_C DIFF_POD12_DCI A7 DQSU_C U60

G11 DDR4_C1_DM0 POD12_DCI E7 DML_B/DBIL_B U60

R18 DDR4_C1_DM1 POD12_DCI E2 DMU_B/DBIU_B U60

L16 DDR4_C1_DQ16 POD12_DCI G2 DQL0 U61

www.xilinx.com

Page 23

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-2: DDR4 Memory 80-bit I/F C1 to FPGA U1 Banks 71, 72, and 73 (Cont’d)

FPGA (U1)

Pin

K16 DDR4_C1_DQ17 POD12_DCI F7 DQL1 U61

L18 DDR4_C1_DQ18 POD12_DCI H3 DQL2 U61

K18 DDR4_C1_DQ19 POD12_DCI H7 DQL3 U61

J17 DDR4_C1_DQ20 POD12_DCI H2 DQL4 U61

H17 DDR4_C1_DQ21 POD12_DCI H8 DQL5 U61

H19 DDR4_C1_DQ22 POD12_DCI J3 DQL6 U61

H18 DDR4_C1_DQ23 POD12_DCI J7 DQL7 U61

F19 DDR4_C1_DQ24 POD12_DCI A3 DQU0 U61

F18 DDR4_C1_DQ25 POD12_DCI B8 DQU1 U61

E19 DDR4_C1_DQ26 POD12_DCI C3 DQU2 U61

E18 DDR4_C1_DQ27 POD12_DCI C7 DQU3 U61

G20 DDR4_C1_DQ28 POD12_DCI C2 DQU4 U61

F20 DDR4_C1_DQ29 POD12_DCI C8 DQU5 U61

E17 DDR4_C1_DQ30 POD12_DCI D3 DQU6 U61

D16 DDR4_C1_DQ31 POD12_DCI D7 DQU7 U61

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

K19 DDR4_C1_DQS2_T DIFF_POD12_DCI G3 DQSL_T U61

J19 DDR4_C1_DQS2_C DIFF_POD12_DCI F3 DQSL_C U61

F16 DDR4_C1_DQS3_T DIFF_POD12_DCI B7 DQSU_T U61

E16 DDR4_C1_DQS3_C DIFF_POD12_DCI A7 DQSU_C U61

K17 DDR4_C1_DM2 POD12_DCI E7 DML_B/DBIL_B U61

G18 DDR4_C1_DM3 POD12_DCI E2 DMU_B/DBIU_B U61

D17 DDR4_C1_DQ32 POD12_DCI G2 DQL0 U62

C17 DDR4_C1_DQ33 POD12_DCI F7 DQL1 U62

C19 DDR4_C1_DQ34 POD12_DCI H3 DQL2 U62

C18 DDR4_C1_DQ35 POD12_DCI H7 DQL3 U62

D20 DDR4_C1_DQ36 POD12_DCI H2 DQL4 U62

D19 DDR4_C1_DQ37 POD12_DCI H8 DQL5 U62

C20 DDR4_C1_DQ38 POD12_DCI J3 DQL6 U62

B20 DDR4_C1_DQ39 POD12_DCI J7 DQL7 U62

N23 DDR4_C1_DQ40 POD12_DCI A3 DQU0 U62

M23 DDR4_C1_DQ41 POD12_DCI B8 DQU1 U62

R21 DDR4_C1_DQ42 POD12_DCI C3 DQU2 U62

VCU118 Board User Guide 23

UG1224 (v1.0) December 15, 2016

P21 DDR4_C1_DQ43 POD12_DCI C7 DQU3 U62

R22 DDR4_C1_DQ44 POD12_DCI C2 DQU4 U62

www.xilinx.com

Page 24

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-2: DDR4 Memory 80-bit I/F C1 to FPGA U1 Banks 71, 72, and 73 (Cont’d)

FPGA (U1)

Pin

P22 DDR4_C1_DQ45 POD12_DCI C8 DQU5 U62

T23 DDR4_C1_DQ46 POD12_DCI D3 DQU6 U62

R23 DDR4_C1_DQ47 POD12_DCI D7 DQU7 U62

A19 DDR4_C1_DQS4_T DIFF_POD12_DCI G3 DQSL_T U62

A18 DDR4_C1_DQS4_C DIFF_POD12_DCI F3 DQSL_C U62

N22 DDR4_C1_DQS5_T DIFF_POD12_DCI B7 DQSU_T U62

M22 DDR4_C1_DQS5_C DIFF_POD12_DCI A7 DQSU_C U62

B18 DDR4_C1_DM4 POD12_DCI E7 DML_B/DBIL_B U62

P20 DDR4_C1_DM5 POD12_DCI E2 DMU_B/DBIU_B U62

K24 DDR4_C1_DQ48 POD12_DCI G2 DQL0 U63

J24 DDR4_C1_DQ49 POD12_DCI F7 DQL1 U63

M21 DDR4_C1_DQ50 POD12_DCI H3 DQL2 U63

L21 DDR4_C1_DQ51 POD12_DCI H7 DQL3 U63

K21 DDR4_C1_DQ52 POD12_DCI H2 DQL4 U63

J21 DDR4_C1_DQ53 POD12_DCI H8 DQL5 U63

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

K22 DDR4_C1_DQ54 POD12_DCI J3 DQL6 U63

J22 DDR4_C1_DQ55 POD12_DCI J7 DQL7 U63

H23 DDR4_C1_DQ56 POD12_DCI A3 DQU0 U63

H22 DDR4_C1_DQ57 POD12_DCI B8 DQU1 U63

E23 DDR4_C1_DQ58 POD12_DCI C3 DQU2 U63

E22 DDR4_C1_DQ59 POD12_DCI C7 DQU3 U63

F21 DDR4_C1_DQ60 POD12_DCI C2 DQU4 U63

E21 DDR4_C1_DQ61 POD12_DCI C8 DQU5 U63

F24 DDR4_C1_DQ62 POD12_DCI D3 DQU6 U63

F23 DDR4_C1_DQ63 POD12_DCI D7 DQU7 U63

M20 DDR4_C1_DQS6_T DIFF_POD12_DCI G3 DQSL_T U63

L20 DDR4_C1_DQS6_C DIFF_POD12_DCI F3 DQSL_C U63

H24 DDR4_C1_DQS7_T DIFF_POD12_DCI B7 DQSU_T U63

G23 DDR4_C1_DQS7_C DIFF_POD12_DCI A7 DQSU_C U63

L23 DDR4_C1_DM6 POD12_DCI E7 DML_B/DBIL_B U63

G22 DDR4_C1_DM7 POD12_DCI E2 DMU_B/DBIU_B U63

A24 DDR4_C1_DQ64 POD12_DCI G2 DQL0 U64

VCU118 Board User Guide 24

UG1224 (v1.0) December 15, 2016

A23 DDR4_C1_DQ65 POD12_DCI F7 DQL1 U64

C24 DDR4_C1_DQ66 POD12_DCI H3 DQL2 U64

www.xilinx.com

Page 25

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-2: DDR4 Memory 80-bit I/F C1 to FPGA U1 Banks 71, 72, and 73 (Cont’d)

FPGA (U1)

Pin

C23 DDR4_C1_DQ67 POD12_DCI H7 DQL3 U64

B23 DDR4_C1_DQ68 POD12_DCI H2 DQL4 U64

B22 DDR4_C1_DQ69 POD12_DCI H8 DQL5 U64

B21 DDR4_C1_DQ70 POD12_DCI J3 DQL6 U64

A21 DDR4_C1_DQ71 POD12_DCI J7 DQL7 U64

D7 DDR4_C1_DQ72 POD12_DCI A3 DQU0 U64

C7 DDR4_C1_DQ73 POD12_DCI B8 DQU1 U64

B8 DDR4_C1_DQ74 POD12_DCI C3 DQU2 U64

B7 DDR4_C1_DQ75 POD12_DCI C7 DQU3 U64

C10 DDR4_C1_DQ76 POD12_DCI C2 DQU4 U64

B10 DDR4_C1_DQ77 POD12_DCI C8 DQU5 U64

B11 DDR4_C1_DQ78 POD12_DCI D3 DQU6 U64

A11 DDR4_C1_DQ79 POD12_DCI D7 DQU7 U64

D22 DDR4_C1_DQS8_T DIFF_POD12_DCI G3 DQSL_T U64

C22 DDR4_C1_DQS8_C DIFF_POD12_DCI F3 DQSL_C U64

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

A9 DDR4_C1_DQS9_T DIFF_POD12_DCI B7 DQSU_T U64

A8 DDR4_C1_DQS9_C DIFF_POD12_DCI A7 DQSU_C U64

E24 DDR4_C1_DM8 POD12_DCI E7 DML_B/DBIL_B U64

C9 DDR4_C1_DM9 POD12_DCI E2 DMU_B/DBIU_B U64

D14 DDR4_C1_A0 SSTL12_DCI P3 A0 U60-U64

B15 DDR4_C1_A1 SSTL12_DCI P7 A1 U60-U64

B16 DDR4_C1_A2 SSTL12_DCI R3 A2 U60-U64

C14 DDR4_C1_A3 SSTL12_DCI N7 A3 U60-U64

C15 DDR4_C1_A4 SSTL12_DCI N3 A4 U60-U64

A13 DDR4_C1_A5 SSTL12_DCI P8 A5 U60-U64

A14 DDR4_C1_A6 SSTL12_DCI P2 A6 U60-U64

A15 DDR4_C1_A7 SSTL12_DCI R8 A7 U60-U64

A16 DDR4_C1_A8 SSTL12_DCI R2 A8 U60-U64

B12 DDR4_C1_A9 SSTL12_DCI R7 A9 U60-U64

C12 DDR4_C1_A10 SSTL12_DCI M3 A10/AP U60-U64

B13 DDR4_C1_A11 SSTL12_DCI T2 A11 U60-U64

C13 DDR4_C1_A12 SSTL12_DCI M7 A12/BC_B U60-U64

VCU118 Board User Guide 25

UG1224 (v1.0) December 15, 2016

D15 DDR4_C1_A13 SSTL12_DCI T8 A13 U60-U64

G15 DDR4_C1_BA0 SSTL12_DCI N2 BA0 U60-U64

www.xilinx.com

Page 26

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-2: DDR4 Memory 80-bit I/F C1 to FPGA U1 Banks 71, 72, and 73 (Cont’d)

FPGA (U1)

Pin

G13 DDR4_C1_BA1 SSTL12_DCI N8 BA1 U60-U64

H13 DDR4_C1_BG0 SSTL12_DCI M2 BG0 U60-U64

H14 DDR4_C1_A14_WE_B SSTL12_DCI L2 WE_B/A14 U60-U64

H15 DDR4_C1_A15_CAS_B SSTL12_DCI M8 CAS_B_A15 U60-U64

F15 DDR4_C1_A16_RAS_B SSTL12_DCI L8 RAS_B/A16 U60-U64

F14 DDR4_C1_CK_T DIFF_SSTL12_DCI K7 CK_T U60-U64

E14 DDR4_C1_CK_C DIFF_SSTL12_DCI K8 CK_C U60-U64

A10 DDR4_C1_CKE SSTL12_DCI K2 CKE U60-U64

E13 DDR4_C1_ACT_B SSTL12_DCI L3 ACT_B U60-U64

G10 DDR4_C1_PAR SSTL12_DCI T3 PAR U60-U64

C8 DDR4_C1_ODT SSTL12_DCI K3 ODT U60-U64

F13 DDR4_C1_CS_B SSTL12_DCI L7 CS_B U60-U64

R17 DDR4_C1_ALERT_B SSTL12_DCI P9 ALERT_B U60-U64

N20 DDR4_C1_RESET_B LVCMOS12 P1 RESET_B U60-U64

A20 DDR4_C1_TEN SSTL12_DCI N9 TEN U60-U64

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

The connections between the C2 80-bit interface DDR4 component memories (U135-U139)

and XCVU9P banks 40, 41, and 42 are listed in Table 3-3.

Table 3-3: DDR4 Memory 80-bit I/F C2 to FPGA U1 Banks 40, 41, and 42

FPGA (U1)

Pin

BD30 DDR4_C2_DQ0 POD12_DCI G2 DQL0 U135

BE30 DDR4_C2_DQ1 POD12_DCI F7 DQL1 U135

BD32 DDR4_C2_DQ2 POD12_DCI H3 DQL2 U135

BE33 DDR4_C2_DQ3 POD12_DCI H7 DQL3 U135

BC33 DDR4_C2_DQ4 POD12_DCI H2 DQL4 U135

BD33 DDR4_C2_DQ5 POD12_DCI H8 DQL5 U135

BC31 DDR4_C2_DQ6 POD12_DCI J3 DQL6 U135

BD31 DDR4_C2_DQ7 POD12_DCI J7 DQL7 U135

BA32 DDR4_C2_DQ8 POD12_DCI A3 DQU0 U135

BB33 DDR4_C2_DQ9 POD12_DCI B8 DQU1 U135

BA30 DDR4_C2_DQ10 POD12_DCI C3 DQU2 U135

BA31 DDR4_C2_DQ11 POD12_DCI C7 DQU3 U135

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

VCU118 Board User Guide 26

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 27

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-3: DDR4 Memory 80-bit I/F C2 to FPGA U1 Banks 40, 41, and 42 (Cont’d)

FPGA (U1)

Pin

AW31 DDR4_C2_DQ12 POD12_DCI C2 DQU4 U135

AW32 DDR4_C2_DQ13 POD12_DCI C8 DQU5 U135

AY32 DDR4_C2_DQ14 POD12_DCI D3 DQU6 U135

AY33 DDR4_C2_DQ15 POD12_DCI D7 DQU7 U135

BF30 DDR4_C2_DQS0_T DIFF_POD12_DCI G3 DQSL_T U135

BF31 DDR4_C2_DQS0_C DIFF_POD12_DCI F3 DQSL_C U135

AY34 DDR4_C2_DQS1_T DIFF_POD12_DCI B7 DQSU_T U135

BA34 DDR4_C2_DQS1_C DIFF_POD12_DCI A7 DQSU_C U135

BE32 DDR4_C2_DM0 POD12_DCI E7 DML_B/DBIL_B U135

BB31 DDR4_C2_DM1 POD12_DCI E2 DMU_B/DBIU_B U135

AV30 DDR4_C2_DQ16 POD12_DCI G2 DQL0 U136

AW30 DDR4_C2_DQ17 POD12_DCI F7 DQL1 U136

AU33 DDR4_C2_DQ18 POD12_DCI H3 DQL2 U136

AU34 DDR4_C2_DQ19 POD12_DCI H7 DQL3 U136

AT31 DDR4_C2_DQ20 POD12_DCI H2 DQL4 U136

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

AU32 DDR4_C2_DQ21 POD12_DCI H8 DQL5 U136

AU31 DDR4_C2_DQ22 POD12_DCI J3 DQL6 U136

AV31 DDR4_C2_DQ23 POD12_DCI J7 DQL7 U136

AR33 DDR4_C2_DQ24 POD12_DCI A3 DQU0 U136

AT34 DDR4_C2_DQ25 POD12_DCI B8 DQU1 U136

AT29 DDR4_C2_DQ26 POD12_DCI C3 DQU2 U136

AT30 DDR4_C2_DQ27 POD12_DCI C7 DQU3 U136

AP30 DDR4_C2_DQ28 POD12_DCI C2 DQU4 U136

AR30 DDR4_C2_DQ29 POD12_DCI C8 DQU5 U136

AN30 DDR4_C2_DQ30 POD12_DCI D3 DQU6 U136

AN31 DDR4_C2_DQ31 POD12_DCI D7 DQU7 U136

AU29 DDR4_C2_DQS2_T DIFF_POD12_DCI G3 DQSL_C U136

AV29 DDR4_C2_DQS2_C DIFF_POD12_DCI F3 DQSL_T U136

AP31 DDR4_C2_DQS3_T DIFF_POD12_DCI B7 DQSU_C U136

AP32 DDR4_C2_DQS3_C DIFF_POD12_DCI A7 DQSU_T U136

AV33 DDR4_C2_DM2 POD12_DCI E7 DML_B/DBIL_B U136

AR32 DDR4_C2_DM3 POD12_DCI E2 DMU_B/DBIU_B U136

VCU118 Board User Guide 27

UG1224 (v1.0) December 15, 2016

BE34 DDR4_C2_DQ32 POD12_DCI G2 DQL0 U137

BF34 DDR4_C2_DQ33 POD12_DCI F7 DQL1 U137

www.xilinx.com

Page 28

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-3: DDR4 Memory 80-bit I/F C2 to FPGA U1 Banks 40, 41, and 42 (Cont’d)

FPGA (U1)

Pin

BC35 DDR4_C2_DQ34 POD12_DCI H3 DQL2 U137

BC36 DDR4_C2_DQ35 POD12_DCI H7 DQL3 U137

BD36 DDR4_C2_DQ36 POD12_DCI H2 DQL4 U137

BE37 DDR4_C2_DQ37 POD12_DCI H8 DQL5 U137

BF36 DDR4_C2_DQ38 POD12_DCI J3 DQL6 U137

BF37 DDR4_C2_DQ39 POD12_DCI J7 DQL7 U137

BD37 DDR4_C2_DQ40 POD12_DCI A3 DQU0 U137

BE38 DDR4_C2_DQ41 POD12_DCI B8 DQU1 U137

BC39 DDR4_C2_DQ42 POD12_DCI C3 DQU2 U137

BD40 DDR4_C2_DQ43 POD12_DCI C7 DQU3 U137

BB38 DDR4_C2_DQ44 POD12_DCI C2 DQU4 U137

BB39 DDR4_C2_DQ45 POD12_DCI C8 DQU5 U137

BC38 DDR4_C2_DQ46 POD12_DCI D3 DQU6 U137

BD38 DDR4_C2_DQ47 POD12_DCI D7 DQU7 U137

BE35 DDR4_C2_DQS4_T DIFF_POD12_DCI G3 DQSL_T U137

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

BF35 DDR4_C2_DQS4_C DIFF_POD12_DCI F3 DQSL_C U137

BE39 DDR4_C2_DQS5_T DIFF_POD12_DCI B7 DQSU_T U137

BF39 DDR4_C2_DQS5_C DIFF_POD12_DCI A7 DQSU_C U137

BC34 DDR4_C2_DM4 POD12_DCI E7 DML_B/DBIL_B U137

BE40 DDR4_C2_DM5 POD12_DCI E2 DMU_B/DBIU_B U137

BB36 DDR4_C2_DQ48 POD12_DCI G2 DQL0 U138

BB37 DDR4_C2_DQ49 POD12_DCI F7 DQL1 U138

BA39 DDR4_C2_DQ50 POD12_DCI H3 DQL2 U138

BA40 DDR4_C2_DQ51 POD12_DCI H7 DQL3 U138

AW40 DDR4_C2_DQ52 POD12_DCI H2 DQL4 U138

AY40 DDR4_C2_DQ53 POD12_DCI H8 DQL5 U138

AY38 DDR4_C2_DQ54 POD12_DCI J3 DQL6 U138

AY39 DDR4_C2_DQ55 POD12_DCI J7 DQL7 U138

AW35 DDR4_C2_DQ56 POD12_DCI A3 DQU0 U138

AW36 DDR4_C2_DQ57 POD12_DCI B8 DQU1 U138

AU40 DDR4_C2_DQ58 POD12_DCI C3 DQU2 U138

AV40 DDR4_C2_DQ59 POD12_DCI C7 DQU3 U138

VCU118 Board User Guide 28

UG1224 (v1.0) December 15, 2016

AU38 DDR4_C2_DQ60 POD12_DCI C2 DQU4 U138

AU39 DDR4_C2_DQ61 POD12_DCI C8 DQU5 U138

www.xilinx.com

Page 29

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-3: DDR4 Memory 80-bit I/F C2 to FPGA U1 Banks 40, 41, and 42 (Cont’d)

FPGA (U1)

Pin

AV38 DDR4_C2_DQ62 POD12_DCI D3 DQU6 U138

AV39 DDR4_C2_DQ63 POD12_DCI D7 DQU7 U138

BA35 DDR4_C2_DQS6_T DIFF_POD12_DCI G3 DQSL_C U138

BA36 DDR4_C2_DQS6_C DIFF_POD12_DCI F3 DQSL_T U138

AW37 DDR4_C2_DQS7_T DIFF_POD12_DCI B7 DQSU_C U138

AW38 DDR4_C2_DQS7_C DIFF_POD12_DCI A7 DQSU_T U138

AY37 DDR4_C2_DM6 POD12_DCI E7 DML_B/DBIL_B U138

AV35 DDR4_C2_DM7 POD12_DCI E2 DMU_B/DBIU_B U138

BF26 DDR4_C2_DQ64 POD12_DCI G2 DQL0 U139

BF27 DDR4_C2_DQ65 POD12_DCI F7 DQL1 U139

BD28 DDR4_C2_DQ66 POD12_DCI H3 DQL2 U139

BE28 DDR4_C2_DQ67 POD12_DCI H7 DQL3 U139

BD27 DDR4_C2_DQ68 POD12_DCI H2 DQL4 U139

BE27 DDR4_C2_DQ69 POD12_DCI H8 DQL5 U139

BD25 DDR4_C2_DQ70 POD12_DCI J3 DQL6 U139

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

BD26 DDR4_C2_DQ71 POD12_DCI J7 DQL7 U139

BC25 DDR4_C2_DQ72 POD12_DCI A3 DQU0 U139

BC26 DDR4_C2_DQ73 POD12_DCI B8 DQU1 U139

BB28 DDR4_C2_DQ74 POD12_DCI C3 DQU2 U139

BC28 DDR4_C2_DQ75 POD12_DCI C7 DQU3 U139

AY27 DDR4_C2_DQ76 POD12_DCI C2 DQU4 U139

AY28 DDR4_C2_DQ77 POD12_DCI C8 DQU5 U139

BA27 DDR4_C2_DQ78 POD12_DCI D3 DQU6 U139

BB27 DDR4_C2_DQ79 POD12_DCI D7 DQU7 U139

BE25 DDR4_C2_DQS8_T DIFF_POD12_DCI G3 DQSL_C U139

BF25 DDR4_C2_DQS8_C DIFF_POD12_DCI F3 DQSL_T U139

BA26 DDR4_C2_DQS9_T DIFF_POD12_DCI B7 DQSU_C U139

BB26 DDR4_C2_DQS9_C DIFF_POD12_DCI A7 DQSU_T U139

BE29 DDR4_C2_DM8 POD12_DCI E7 DML_B/DBIL_B U139

BA29 DDR4_C2_DM9 POD12_DCI E2 DMU_B/DBIU_B U139

AM27 DDR4_C2_A0 SSTL12_DCI P3 A0 U135-U139

AL27 DDR4_C2_A1 SSTL12_DCI P7 A1 U135-U139

VCU118 Board User Guide 29

UG1224 (v1.0) December 15, 2016

AP26 DDR4_C2_A2 SSTL12_DCI R3 A2 U135-U139

AP25 DDR4_C2_A3 SSTL12_DCI N7 A3 U135-U139

www.xilinx.com

Page 30

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-3: DDR4 Memory 80-bit I/F C2 to FPGA U1 Banks 40, 41, and 42 (Cont’d)

FPGA (U1)

Pin

AN28 DDR4_C2_A4 SSTL12_DCI N3 A4 U135-U139

AM28 DDR4_C2_A5 SSTL12_DCI P8 A5 U135-U139

AP28 DDR4_C2_A6 SSTL12_DCI P2 A6 U135-U139

AP27 DDR4_C2_A7 SSTL12_DCI R8 A7 U135-U139

AN26 DDR4_C2_A8 SSTL12_DCI R2 A8 U135-U139

AM26 DDR4_C2_A9 SSTL12_DCI R7 A9 U135-U139

AR28 DDR4_C2_A10 SSTL12_DCI M3 A10/AP U135-U139

AR27 DDR4_C2_A11 SSTL12_DCI T2 A11 U135-U139

AV25 DDR4_C2_A12 SSTL12_DCI M7 A12/BC_B U135-U139

AT25 DDR4_C2_A13 SSTL12_DCI T8 A13 U135-U139

AR25 DDR4_C2_BA0 SSTL12_DCI N2 BA0 U135-U139

AU28 DDR4_C2_BA1 SSTL12_DCI N8 BA1 U135-U139

AU27 DDR4_C2_BG0 SSTL12_DCI M2 BG0 U135-U139

AV28 DDR4_C2_A14_WE_B SSTL12_DCI L2 WE_B/A14 U135-U139

AU26 DDR4_C2_A15_CAS_B SSTL12_DCI M8 CAS_B_A15 U135-U139

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

AV26 DDR4_C2_A16_RAS_B SSTL12_DCI L8 RAS_B/A16 U135-U139

AT26 DDR4_C2_CK_T DIFF_SSTL12_DCI K7 CK_T U135-U139

AT27 DDR4_C2_CK_C DIFF_SSTL12_DCI K8 CK_C U135-U139

AW28 DDR4_C2_CKE SSTL12_DCI K2 CKE U135-U139

AN25 DDR4_C2_ACT_B SSTL12_DCI L3 ACT_B U135-U139

BF29 DDR4_C2_PAR SSTL12_DCI P9 ALERT_B U135-U139

BB29 DDR4_C2_ODT SSTL12_DCI T3 PAR U135-U139

AY29 DDR4_C2_CS_B SSTL12_DCI K3 ODT U135-U139

AR29 DDR4_C2_ALERT_B SSTL12_DCI L7 CS_B U135-U139

BD35 DDR4_C2_RESET_B LVCMOS12 P1 RESET_B U135-U139

AY35 DDR4_C2_TEN SSTL12_DCI N9 TEN U135-U139

The VCU118 dual DDR4 80-bit memory component interfaces adhere to the constraints

guidelines documented in the “DDR3/DDR4 Design Guidelines” section of the UltraScale

Architecture-Based FPGAs Memory IP LogiCORE IP Product Guide (PG150) [Ref 4]. The

VCU118 board DDR4 memory component interface is a 40Ω impedance implementation.

For more information on the internal VREF, see the “Supply Voltages for the SelectIO Pins

VREF” and the “Internal VREF” sections in the UltraScale Architecture SelectIO Resources User

Guide (UG571) [Ref 3]. For more details about the Micron DDR4 component memory, see

the Micron MT40A256M16GE data sheet at the Micron website [Ref 18].

VCU118 Board User Guide 30

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 31

Chapter 3: Board Component Descriptions

Send Feedback

RLD3 Component Memory

[Figure 2-1, callout 5]

The 288 MB RLD3 72-bit wide component memory system is comprised of two 36-bit 1.125

Gb RLDRAM3 devices (Micron MT44K32M36RB-083E) located at U141-U142. This memory

system is connected to the XCVU9P HP banks 46, 47, and 48. The RLD3 0.6V VTT termination

voltage (net RLD3_C3_VTT) is sourced from TI TPS51200DR linear regulator U143. The RLD3

memory interface bank VREF pins are not connected, which, coupled with an XDC

set_property INTERNAL_VREF constraint, invoke the INTERNAL VREF mode. The

connections between the RLD3 component memories and XCVU9P banks 46, 47, and 48 are

listed in Table 3-4.

Table 3-4: RLD3 Memory 72-bit I/F to FPGA U1 Banks 46, 47, and 48

FPGA

(U1) Pin

H39 RLD3_C3_72B_DQ0 SSTL12 D11 DQ0 U141

H40 RLD3_C3_72B_DQ1 SSTL12 E10 DQ1 U141

G40 RLD3_C3_72B_DQ2 SSTL12 C8 DQ2 U141

F40 RLD3_C3_72B_DQ3 SSTL12 C10 DQ3 U141

H38 RLD3_C3_72B_DQ4 SSTL12 C12 DQ4 U141

G38 RLD3_C3_72B_DQ5 SSTL12 B9 DQ5 U141

K37 RLD3_C3_72B_DQ6 SSTL12 B11 DQ6 U141

J37 RLD3_C3_72B_DQ7 SSTL12 A8 DQ7 U141

F38 RLD3_C3_72B_DQ8 SSTL12 A10 DQ8 U141

J35 RLD3_C3_72B_DQ9 SSTL12 J10 DQ9 U141

H35 RLD3_C3_72B_DQ10 SSTL12 K11 DQ10 U141

J36 RLD3_C3_72B_DQ11 SSTL12 K13 DQ11 U141

H37 RLD3_C3_72B_DQ12 SSTL12 L8 DQ12 U141

H34 RLD3_C3_72B_DQ13 SSTL12 L10 DQ13 U141

G35 RLD3_C3_72B_DQ14 SSTL12 L12 DQ14 U141

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

F35 RLD3_C3_72B_DQ15 SSTL12 M9 DQ15 U141

F36 RLD3_C3_72B_DQ16 SSTL12 M11 DQ16 U141

G36 RLD3_C3_72B_DQ17 SSTL12 N8 DQ17 U141

E37 RLD3_C3_72B_DQ18 SSTL12 D3 DQ18 U141

E38 RLD3_C3_72B_DQ19 SSTL12 E4 DQ19 U141

C39 RLD3_C3_72B_DQ20 SSTL12 C6 DQ20 U141

B40 RLD3_C3_72B_DQ21 SSTL12 C4 DQ21 U141

A39 RLD3_C3_72B_DQ22 SSTL12 C2 DQ22 U141

VCU118 Board User Guide 31

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 32

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-4: RLD3 Memory 72-bit I/F to FPGA U1 Banks 46, 47, and 48 (Cont’d)

FPGA

(U1) Pin

A40 RLD3_C3_72B_DQ23 SSTL12 B5 DQ23 U141

D40 RLD3_C3_72B_DQ24 SSTL12 B3 DQ24 U141

C40 RLD3_C3_72B_DQ25 SSTL12 A6 DQ25 U141

B38 RLD3_C3_72B_DQ26 SSTL12 A4 DQ26 U141

D35 RLD3_C3_72B_DQ27 SSTL12 J4 DQ27 U141

C35 RLD3_C3_72B_DQ28 SSTL12 K3 DQ28 U141

D34 RLD3_C3_72B_DQ29 SSTL12 K1 DQ29 U141

C34 RLD3_C3_72B_DQ30 SSTL12 L6 DQ30 U141

B36 RLD3_C3_72B_DQ31 SSTL12 L4 DQ31 U141

B37 RLD3_C3_72B_DQ32 SSTL12 L2 DQ32 U141

B35 RLD3_C3_72B_DQ33 SSTL12 M5 DQ33 U141

A36 RLD3_C3_72B_DQ34 SSTL12 M3 DQ34 U141

A34 RLD3_C3_72B_DQ35 SSTL12 N6 DQ35 U141

F39 RLD3_C3_72B_DM0 SSTL12 B7 DM0 U141

A35 RLD3_C3_72B_DM1 SSTL12 M7 DM1 U141

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

J39 RLD3_C3_72B_QK0_P DIFF_SSTL12 D9 QK0 U141

J40 RLD3_C3_72B_QK0_N DIFF_SSTL12 E8 QK0_B U141

F34 RLD3_C3_72B_QK1_P DIFF_SSTL12 K9 QK1 U141

E34 RLD3_C3_72B_QK1_N DIFF_SSTL12 J8 QK1_B U141

E39 RLD3_C3_72B_QK2_P DIFF_SSTL12 D5 QK2 U141

D39 RLD3_C3_72B_QK2_N DIFF_SSTL12 E6 QK2_B U141

D37 RLD3_C3_72B_QK3_P DIFF_SSTL12 K5 QK3 U141

C37 RLD3_C3_72B_QK3_N DIFF_SSTL12 J6 QK3_B U141

G37 RLD3_C3_72B_QVLD0 SSTL12 J12 QVLD0 U141

A38 RLD3_C3_72B_QVLD1 SSTL12 J2 QVLD1 U141

T24 RLD3_C3_72B_DQ36 SSTL12 D11 DQ0 U142

R24 RLD3_C3_72B_DQ37 SSTL12 E10 DQ1 U142

R27 RLD3_C3_72B_DQ38 SSTL12 C8 DQ2 U142

P27 RLD3_C3_72B_DQ39 SSTL12 C10 DQ3 U142

P25 RLD3_C3_72B_DQ40 SSTL12 C12 DQ4 U142

N25 RLD3_C3_72B_DQ41 SSTL12 B9 DQ5 U142

P26 RLD3_C3_72B_DQ42 SSTL12 B11 DQ6 U142

N27 RLD3_C3_72B_DQ43 SSTL12 A8 DQ7 U142

P24 RLD3_C3_72B_DQ44 SSTL12 A10 DQ8 U142

VCU118 Board User Guide 32

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 33

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-4: RLD3 Memory 72-bit I/F to FPGA U1 Banks 46, 47, and 48 (Cont’d)

FPGA

(U1) Pin

M25 RLD3_C3_72B_DQ45 SSTL12 J10 DQ9 U142

L26 RLD3_C3_72B_DQ46 SSTL12 K11 DQ10 U142

L28 RLD3_C3_72B_DQ47 SSTL12 K13 DQ11 U142

K28 RLD3_C3_72B_DQ48 SSTL12 L8 DQ12 U142

L24 RLD3_C3_72B_DQ49 SSTL12 L10 DQ13 U142

L25 RLD3_C3_72B_DQ50 SSTL12 L12 DQ14 U142

K26 RLD3_C3_72B_DQ51 SSTL12 M9 DQ15 U142

J26 RLD3_C3_72B_DQ52 SSTL12 M11 DQ16 U142

K27 RLD3_C3_72B_DQ53 SSTL12 N8 DQ17 U142

H27 RLD3_C3_72B_DQ54 SSTL12 D3 DQ18 U142

G27 RLD3_C3_72B_DQ55 SSTL12 E4 DQ19 U142

F28 RLD3_C3_72B_DQ56 SSTL12 C6 DQ20 U142

E28 RLD3_C3_72B_DQ57 SSTL12 C4 DQ21 U142

H28 RLD3_C3_72B_DQ58 SSTL12 C2 DQ22 U142

G28 RLD3_C3_72B_DQ59 SSTL12 B5 DQ23 U142

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

E26 RLD3_C3_72B_DQ60 SSTL12 B3 DQ24 U142

E27 RLD3_C3_72B_DQ61 SSTL12 A6 DQ25 U142

G25 RLD3_C3_72B_DQ62 SSTL12 A4 DQ26 U142

B28 RLD3_C3_72B_DQ63 SSTL12 J4 DQ27 U142

A28 RLD3_C3_72B_DQ64 SSTL12 K3 DQ28 U142

C27 RLD3_C3_72B_DQ65 SSTL12 K1 DQ29 U142

B27 RLD3_C3_72B_DQ66 SSTL12 L6 DQ30 U142

B26 RLD3_C3_72B_DQ67 SSTL12 L4 DQ31 U142

A26 RLD3_C3_72B_DQ68 SSTL12 L2 DQ32 U142

D25 RLD3_C3_72B_DQ69 SSTL12 M5 DQ33 U142

D26 RLD3_C3_72B_DQ70 SSTL12 M3 DQ34 U142

C25 RLD3_C3_72B_DQ71 SSTL12 N6 DQ35 U142

N24 RLD3_C3_72B_DM2 SSTL12 B7 DM0 U142

B25 RLD3_C3_72B_DM3 SSTL12 M7 DM1 U142

T26 RLD3_C3_72B_QK4_P DIFF_SSTL12 D9 QK0 U142

R26 RLD3_C3_72B_QK4_N DIFF_SSTL12 E8 QK0_B U142

M27 RLD3_C3_72B_QK5_P DIFF_SSTL12 K9 QK1 U142

M28 RLD3_C3_72B_QK5_N DIFF_SSTL12 J8 QK1_B U142

G26 RLD3_C3_72B_QK6_P DIFF_SSTL12 D5 QK2 U142

VCU118 Board User Guide 33

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 34

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-4: RLD3 Memory 72-bit I/F to FPGA U1 Banks 46, 47, and 48 (Cont’d)

FPGA

(U1) Pin

F26 RLD3_C3_72B_QK6_N DIFF_SSTL12 E6 QK2_B U142

D27 RLD3_C3_72B_QK7_P DIFF_SSTL12 K5 QK3 U142

C28 RLD3_C3_72B_QK7_N DIFF_SSTL12 J6 QK3_B U142

J27 RLD3_C3_72B_QVLD2 DIFF_SSTL12 J12 QVLD0 U142

F25 RLD3_C3_72B_QVLD3 DIFF_SSTL12 J2 QVLD1 U142

A29 RLD3_C3_72B_A0 SSTL12 E2 A0 U141-U142

C29 RLD3_C3_72B_A1 SSTL12 F5 A1 U141-U142

D29 RLD3_C3_72B_A2 SSTL12 F4 A2 U141-U142

B30 RLD3_C3_72B_A3 SSTL12 F9 A3 U141-U142

C30 RLD3_C3_72B_A4 SSTL12 F10 A4 U141-U142

A31 RLD3_C3_72B_A5 SSTL12 F12 A5 U141-U142

A30 RLD3_C3_72B_A6 SSTL12 G3 A6 U141-U142

A33 RLD3_C3_72B_A7 SSTL12 F1 A7 U141-U142

B33 RLD3_C3_72B_A8 SSTL12 G11 A8 U141-U142

B32 RLD3_C3_72B_A9 SSTL12 F13 A9 U141-U142

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

B31 RLD3_C3_72B_A10 SSTL12 H13 A10 U141-U142

C33 RLD3_C3_72B_A11 SSTL12 D1 A11 U141-U142

C32 RLD3_C3_72B_A12 SSTL12 H11 A12 U141-U142

D30 RLD3_C3_72B_A13 SSTL12 D13 A13 U141-U142

E29 RLD3_C3_72B_A14 SSTL12 H3 A14 U141-U142

F29 RLD3_C3_72B_A15 SSTL12 G2 A15 U141-U142

D32 RLD3_C3_72B_A16 SSTL12 H4 A16 U141-U142

E32 RLD3_C3_72B_A17 SSTL12 H10 A17 U141-U142

D31 RLD3_C3_72B_A18 SSTL12 G12 A18 U141-U142

E31 RLD3_C3_72B_A19 SSTL12 H1 A19 U141-U142

R28 RLD3_C3_72B_A20 SSTL12 F2 NF_A20 U141-U142

E33 RLD3_C3_72B_BA0 SSTL12 G9 BA0 U141-U142

F33 RLD3_C3_72B_BA1 SSTL12 G5 BA1 U141-U142

F30 RLD3_C3_72B_BA2 SSTL12 H8 BA2 U141-U142

G30 RLD3_C3_72B_BA3 SSTL12 H6 BA3 U141-U142

K29 RLD3_C3_72B_WE_B SSTL12 F6 WE_B U141-U142

L30 RLD3_C3_72B_REF_B SSTL12 F8 REF_B U141-U142

H29 RLD3_C3_72B_CK_P SSTL12 H7 CK U141-U142

H30 RLD3_C3_72B_CK_N SSTL12 G7 CK_B U141-U142

VCU118 Board User Guide 34

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 35

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-4: RLD3 Memory 72-bit I/F to FPGA U1 Banks 46, 47, and 48 (Cont’d)

FPGA

(U1) Pin

L29 RLD3_C3_72B_RESET_B SSTL12 A13 RESET_B U141-U142

N29 RLD3_C3_72B_CS_B SSTL12 E12 CS_B U141-U142

K31 RLD3_C3_72B_DK0_P DIFF_SSTL12 D7 DK0 U141

J31 RLD3_C3_72B_DK0_N DIFF_SSTL12 C7 DK0_B U141

K32 RLD3_C3_72B_DK1_P DIFF_SSTL12 K7 DK1 U141

J32 RLD3_C3_72B_DK1_N DIFF_SSTL12 L7 DK1_B U141

J29 RLD3_C3_72B_DK2_P DIFF_SSTL12 D7 DK0 U142

J30 RLD3_C3_72B_DK2_N DIFF_SSTL12 C7 DK0_B U142

H33 RLD3_C3_72B_DK3_P DIFF_SSTL12 K7 DK1 U142

G33 RLD3_C3_72B_DK3_N DIFF_SSTL12 L7 DK1_B U142

Schematic Net Name I/O Standard

Pin # Pin Name Ref. Des.

Component Memory

The VCU118 RLD3 72-bit memory component interface adheres to the constraints

guidelines documented in the RLD3 Design Guidelines section of UltraScale

Architecture-Based FPGAs Memory IP LogiCORE IP Product Guide (PG150) [Ref 4]. The

VCU118 RLD3 memory component interface is a 40Ω impedance implementation. For more

information on the internal VREF, see the "Supply Voltages for the SelectIO Pins", “V

and “Internal V

” sections in UltraScale Architecture SelectIO Resources (UG571) [Ref 3].

REF

For more details about the Micron RLD3 component memory, see the Micron

MT44K32M36RB-083E Data Sheet [Ref 18].

REF

”,

VCU118 Board User Guide 35

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 36

Chapter 3: Board Component Descriptions

Send Feedback

Linear BPI Flash Memory

[Figure 2-1, callout 6]

The linear BPI flash memory located at U133 provides 128 MB (1 Gbit) of nonvolatile

storage that can be used for configuration or software storage. The data, address, and

control signals are connected to the U1 XCVU9P bank 65. The BPI flash memory device is

packaged in a 64-pin BGA.

• Part number: MT28GU01GAAA1EGC-0SIT (Micron)

• Supply voltage: 1.8V

• Datapath width: 16 bits (with 26 address lines and 7 control signals)

• Data rate: up to 90 MHz

The linear BPI flash memory can synchronously configure the FPGA in master BPI mode at

the 90 MHz data rate supported by the MT28GU01GAAA1EGC flash memory by using a

configuration bitstream generated with BitGen options for synchronous configuration and

for a configuration clock division of one. The fastest configuration method uses the

external 90 MHz oscillator connected to the FPGA bank 65 EMCCLK pin AL20. By default,

UltraScale FPGAs use the parallel NOR flash asynchronous read in the master BPI

configuration mode.

A full XCVU9P 641,272,864-bit uncompressed bitstream requires 60% of the 1 Gbit linear

BPI NOR flash size, so one XCVU9P bitstream is supported.

The BPI flash upper address A25 pin is wired to pull-up header J29 to allow one of two

compressed bitstreams to be manually selected.

See the UltraScale Architecture Configuration User Guide (UG570) [Ref 2] for more

information.

Add these constraints for compression to designs targeted for the VCU118 board.

• When loading from BPI flash:

set_property BITSTREAM.CONFIG.EXTMASTERCCLK_EN div-1 [current_design]

set_property BITSTREAM.CONFIG.BPI_SYNC_MODE Type1 [current_design]

set_property CONFIG_MODE BPI16 [current_design]

*set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

Note: Compression is an optional setting that can improve indirect flash programming time.

• To match the VCU118 configuration of FPGA U1 bank 0:

set_property CFGBVS GND [current_design]

set_property CONFIG_VOLTAGE 1.8 [current_design]

VCU118 Board User Guide 36

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 37

X-Ref Target - Figure 3-2

X18006-100416

Send Feedback

Chapter 3: Board Component Descriptions

Figure 3-2: Linear BPI 128 MB (1 Gbit) Flash Memory

VCU118 Board User Guide 37

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 38

Chapter 3: Board Component Descriptions

Send Feedback

The connections between the BPI flash memory and the FPGA are listed in Table 3-4.

Table 3-5: BPI Flash Memory Connections to FPGA U1

FPGA (U1) Pin Net Name I/O Standard

U58 BPI Flash Memory

Pin # Pin Name

AP11 BPI_FLASH_D0 (NA BANK0) F2 DQ0

AN11 BPI_FLASH_D1 (NA BANK0) E2 DQ1

AM11 BPI_FLASH_D2 (NA BANK0) G3 DQ2

AL11 BPI_FLASH_D3 (NA BANK0) E4 DQ3

AM19 BPI_FLASH_D4 LVCMOS18 E5 DQ4

AM18 BPI_FLASH_D5 LVCMOS18 G5 DQ5

AN20 BPI_FLASH_D6 LVCMOS18 G6 DQ6

AP20 BPI_FLASH_D7 LVCMOS18 H7 DQ7

AN19 BPI_FLASH_D8 LVCMOS18 E1 DQ8

AN18 BPI_FLASH_D9 LVCMOS18 E3 DQ9

AR18 BPI_FLASH_D10 LVCMOS18 F3 DQ10

AR17 BPI_FLASH_D11 LVCMOS18 F4 DQ11

AT20 BPI_FLASH_D12 LVCMOS18 F5 DQ12

AT19 BPI_FLASH_D13 LVCMOS18 H5 DQ13

AT17 BPI_FLASH_D14 LVCMOS18 G7 DQ14

AU17 BPI_FLASH_D15 LVCMOS18 E7 DQ15

AR20 BPI_FLASH_A0 LVCMOS18 A1 A0

AR19 BPI_FLASH_A1 LVCMOS18 B1 A1

AV20 BPI_FLASH_A2 LVCMOS18 C1 A2

AW20 BPI_FLASH_A3 LVCMOS18 D1 A3

AU19 BPI_FLASH_A4 LVCMOS18 D2 A4

AU18 BPI_FLASH_A5 LVCMOS18 A2 A5

AV19 BPI_FLASH_A6 LVCMOS18 C2 A6

AV18 BPI_FLASH_A7 LVCMOS18 A3 A7

AW18 BPI_FLASH_A8 LVCMOS18 B3 A8

AY18 BPI_FLASH_A9 LVCMOS18 C3 A9

AY19 BPI_FLASH_A10 LVCMOS18 D3 A10

BA19 BPI_FLASH_A11 LVCMOS18 C4 A11

BA17 BPI_FLASH_A12 LVCMOS18 A5 A12

BB17 BPI_FLASH_A13 LVCMOS18 B5 A13

BB19 BPI_FLASH_A14 LVCMOS18 C5 A14

BC19 BPI_FLASH_A15 LVCMOS18 D7 A15

VCU118 Board User Guide 38

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 39

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-5: BPI Flash Memory Connections to FPGA U1 (Cont’d)

FPGA (U1) Pin Net Name I/O Standard

U58 BPI Flash Memory

Pin # Pin Name

BB18 BPI_FLASH_A16 LVCMOS18 D8 A16

BC18 BPI_FLASH_A17 LVCMOS18 A7 A17

AY20 BPI_FLASH_A18 LVCMOS18 B7 A18

BA20 BPI_FLASH_A19 LVCMOS18 C7 A19

BD18 BPI_FLASH_A20 LVCMOS18 C8 A20

BD17 BPI_FLASH_A21 LVCMOS18 A8 A21

BC20 BPI_FLASH_A22 LVCMOS18 G1 A22

BD20 BPI_FLASH_A23 LVCMOS18 H8 A23

BE18 BPI_FLASH_A24 LVCMOS18 B6 A24

BE17 BPI_FLASH_A25 LVCMOS18 B8 A25

NC NC NA H1 A26

BF16 BPI_FLASH_FWE_B LVCMOS18 G8 WE_B

p/u R1018 BPI_FLASH_WP_B (NA BANK0) C6 WP_B

AW17 BPI_FLASH_ADV LVCMOS18 F6 ADV_B

AC12 FPGA_INIT_B (NA BANK0) D4 RST_B

BF17 BPI_FLASH_OE_B LVCMOS18 F8 OE_B

AJ11 BPI_FLASH_CE_B (NA BANK0) B4 CE_B

AL19 BPI_WAIT LVCMOS18 F7 WAIT

AL20 FPGA_CCLK LVCMOS18 E6 CLK

Additional FPGA bitstreams can be stored and used for configuration by setting the warm

boot start address (WBSTAR) register contained in UltraScale FPGAs. More information is

available in the reconfiguration and multi-boot section in the UltraScale Architecture

Configuration User Guide (UG570) [Ref 2]. The configuration section in this document

provides details on the master BPI configuration mode. For more information about the

Micron MT28GU01GAAA1EGC-0SIT, see the Micron Technology website [Ref 18].

Micro-SD Card Interface

[Figure 2-1, callout 7]

The VCU118 board includes a secure digital input/output (SDIO) interface allowing the

U111 XC7Z010 Zynq-7000 AP SoC system controller access to general purpose nonvolatile

micro-SD memory cards and peripherals. The micro-SD card slot is designed to support

50 MHz high speed micro-SD cards.

VCU118 Board User Guide 39

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 40

X-Ref Target - Figure 3-3

Digilent

USB

Module

(U115)

TCK

TMS

TDI

TDO

JTAG

Con

(J3)

TDO

TDI

TMS

TCK

1.8V 3.3V

U19

FPGA

TCK

TMS

TDI TDO

1.8V 3.3V

U19

Level-shifted to 3.3V

FMC

HPC1

Connector

TDITDO

FMC+

HSPC

Connector

TDITDO

1.8V 3.3V

U13

Level-shifted to 1.8V

J2 J22

SPST Bus Switch

U132

SPST Bus Switch

U26

N.C. N.C.

Level-shifted to 3.3V

To FMC HSPC J22

and FMC HPC1 J2

U1

System

Ctlr.

(U 111)

TDO

TCK

TMS

TDI

X18023-100416

Send Feedback

Chapter 3: Board Component Descriptions

Digilent USB JTAG Module

[Figure 2-1, callout 8, 9]

JTAG configuration is provided through a Digilent onboard USB-to-JTAG configuration

logic module (U115) where a host computer accesses the VCU118 board JTAG chain

through a type-A (host side) to micro-B (VCU118 board side J106) USB cable.

A 2 mm JTAG header (J3) is also provided in parallel for access by Xilinx download cables,

such as the Platform Cable USB II. JTAG initiated configuration takes priority over the

configuration method selected through the FPGA mode pins M[2:0], wired to SW16

positions [2:4]. The JTAG chain of the VCU118 board is illustrated in Figure 3-3.

For more details about the Digilent USB JTAG Module, see the Digilent website [Ref 21].

Figure 3-3: JTAG Chain Block Diagram

VCU118 Board User Guide 40

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 41

Chapter 3: Board Component Descriptions

Send Feedback

FMC Connector JTAG Bypass

When an FMC is attached to the VCU118 board, it is automatically added to the JTAG chain

through electronically controlled single-pole single-throw (SPST) switches U26 (HSPC) and

U132 (HPC1). The SPST switches are in a normally closed state and transition to an open

state when the FMC is attached. Switch U26 adds an attached FMC to the FPGAs JTAG chain

as determined by the FMC_HSPC_H_PRSNT_M2C_B signal. Switch U132 adds an attached

FMC to the FPGAs JTAG chain as determined by the FMC_HPC1_PRSNT_M2C_B signal.

IMPORTANT: The attached FMC must implement a TDI-to-TDO connection through a device or bypass

jumper to ensure that the JTAG chain connects to the FPGA U1.

The JTAG connectivity on the VCU118 board allows a host computer to download bitstreams

to the FPGA using the Xilinx tools. In addition, the JTAG connector allows debug tools such

as the Vivado serial I/O analyzer or a software debugger to access the FPGA. The Xilinx tools

can also program the BPI parallel flash memory.

Clock Generation

[Figure 2-1, callout 10]

The VCU118 evaluation board provides multiple clock sources to the FPGA as listed in

Table 3-6.

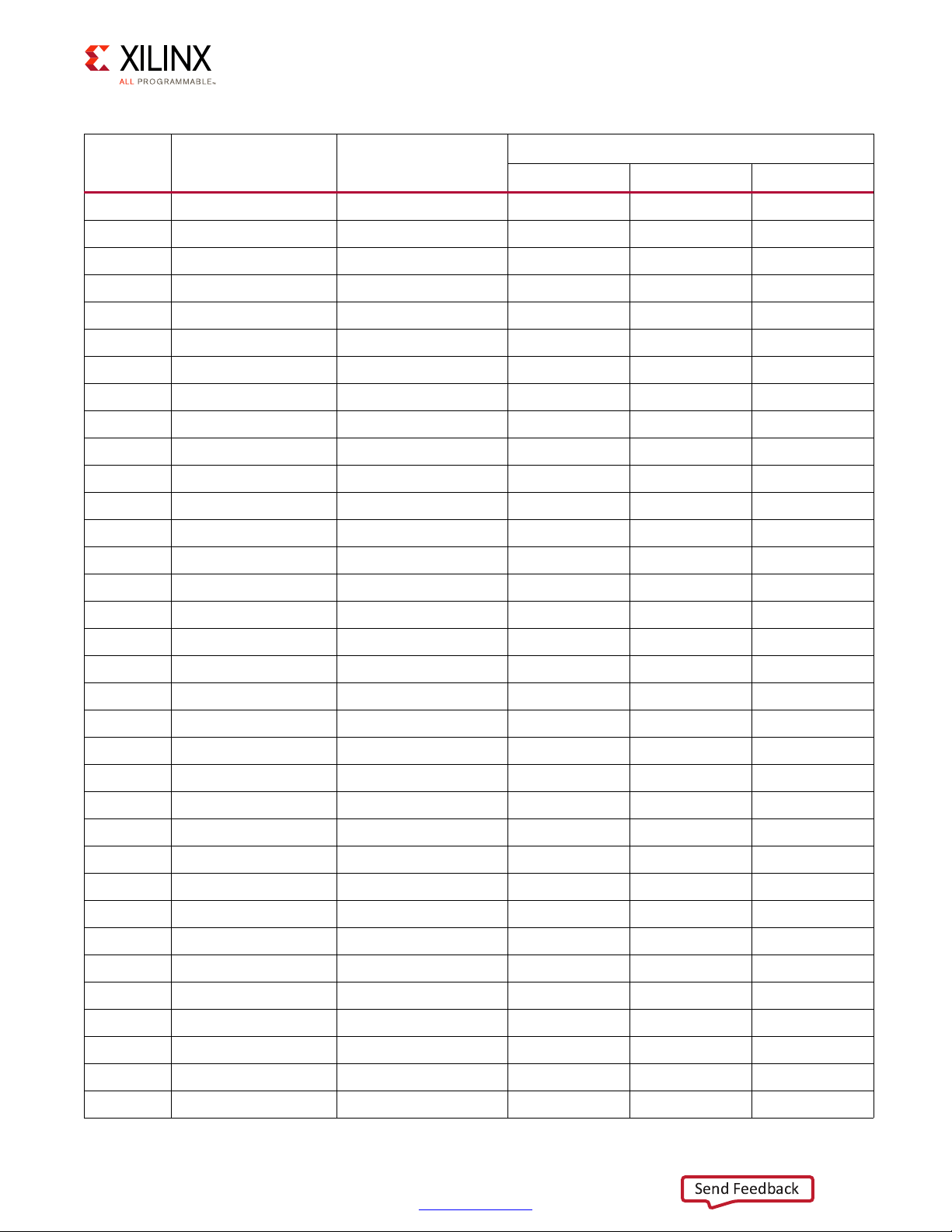

Table 3-6: VCU118 Board Clock Sources

Clock Name Clock Ref. Des. Description

System clock 300 MHz U122/U157

System clock 125 MHz U122

EMC clock 90 MHz U122

System control clock 33.333 MHz U122

User clock 10 MHz-810 MHz U32/U104

Silicon Labs Si5335A 1.8V LVDS any frequency quad

clock generator CLK0 drives U157 clock buffer.

(SYSCLK1_300_P/N)

Silicon Labs Si5335A 1.8V LVDS any frequency quad

clock generator CLK1. (CLK_125 MHz)

Silicon Labs Si5335A 1.8V LVCMOS single-ended any

frequency quad clock generator CLK2.

(FPGA_EMCCLK)

Silicon Labs Si5335A 1.8V LVCMOS single-ended any

frequency quad clock generator CLK3. (SYSCTLR_CLK)

2

Silicon Labs Si570 3.3V LVDS I

oscillator, 156.250 MHz default. U32 output Q0 drives

U104 quad clock buffer. (US-ER_SI570_CLOCK_P/N

and MGT_SI570_CLOCK1_P/N through

MGT_SI570_CLOCK3_P/N)

C programmable

VCU118 Board User Guide 41

UG1224 (v1.0) December 15, 2016

QSFP1 Jitter attenuated clock U57

Silicon Labs Si5328B LVDS precision clock

multiplier/jitter attenuator. See Jitter Attenuated

Clock (SI5328_OUT1_P/N)

www.xilinx.com

Page 42

Table 3-6: VCU118 Board Clock Sources (Cont’d)

Send Feedback

Clock Name Clock Ref. Des. Description

QSFP2 Jitter attenuated clock U57

Chapter 3: Board Component Descriptions

Silicon Labs Si5328B LVDS precision clock

multiplier/jitter attenuator. See Jitter Attenuated

Clock (SI5328_OUT2_P/N)

User SMA clock J34(P), J35(N)

User clock input SMAs. See User SMA Clock

(USER_SMA_CLOCK_P and USER_SMA_CLOCK_N).

Silicon Labs Si570 3.3V LVDS I

QSFP clock 10 MHz-810 MHz U38

oscillator, 156.250 MHz default.

(QSFP_SI570_CLOCK_P/N)

Epson SG5032 3.3V LVDS I

Fixed 250 MHz U14/U21

MHz. U14 output drives U21 dual clock buffer.

(250MHZ_CLK1_P/N and 250MHZ_CLK2_P/N)

Table 3-7 lists the VCU118 clock sources to FPGA U1 connections.

Table 3-7: VCU118 Clock Sources to XCVU9P FPGA U1 Connections

Clock Source

Device/U#.Pin#

SI53340/U157.9 SYSCLK1_300_P LVDS G31

SI53340/U157.10 SYSCLK1_300_N LVDS F31

SI5335A/U122.18 CLK_125MHZ_P LVDS AY24

SI5335A/U122.17 CLK_125MHZ_N LVDS AY23

SI5335A/U122.14 FPGA_EMCCLK

SI5335A/U122.10 SYSCTLR_CLK

Schematic Net Name I/O Standard FPGA (U1) Pin

(2)

(2)

LVCMOS18 AL20

LVCMOS18 U111.C7

2

C programmable

2

C oscillator, fixed 250

SI53340/U104.9 USER_SI570_CLOCK_P LVDS H32

SI53340/U104.10 USER_SI570_CLOCK_N LVDS G32

SI53340/U157.13 USER_SI570_CLOCK1_P LVDS AW23

SI53340/U157.14 USER_SI570_CLOCK1_N LVDS AW22

SI53340/U104.11 MGT_SI570_CLOCK1_P NA

SI53340/U104.12 MGT_SI570_CLOCK1_N NA

SI53340/U104.13 MGT_SI570_CLOCK2_P NA

SI53340/U104.14 MGT_SI570_CLOCK2_N NA

SI53340/U104.15 MGT_SI570_CLOCK3_P NA

SI53340/U104.16 MGT_SI570_CLOCK3_N NA

SI5328B/U57.28 SI5328_OUT1_P NA

SI5328B/U57.29 SI5328_OUT1_N NA

SI5328B/U57.28 SI5328_OUT2_P NA

SI5328B/U57.29 SI5328_OUT2_N NA

(2)

(2)

(2)

(2)

(2)

(2)

(1)

(1)

(1)

(1)

AJ9

AJ8

R9

R8

L9

L8

U9

U8

N9

N8

SMA/J34.1 USER_SMA_CLOCK_P LVDS R32

VCU118 Board User Guide 42

UG1224 (v1.0) December 15, 2016

www.xilinx.com

Page 43

Chapter 3: Board Component Descriptions

Send Feedback

Table 3-7: VCU118 Clock Sources to XCVU9P FPGA U1 Connections (Cont’d)

Clock Source

Device/U#.Pin#

SMA/J35.1 USER_SMA_CLOCK_N LVDS P32

SMA/U38.4 QSFP_SI570_CLOCK_P NA

SMA/U38.5 QSFP_SI570_CLOCK_N NA

ICS85411A/U21.1 250MHZ_CLK1_P LVDS E12

ICS85411A/U21.2 250MHZ_CLK1_N LVDS D12

ICS85411A/U21.3 250MHZ_CLK2_P LVDS AW26

ICS85411A/U21.4 250MHZ_CLK2_N LVDS AW27

Notes:

1. Series capacitor coupled, MGT connections I/O standard is not applicable.

2. SI570 U32 SI570_OUTPUT_P/N nets are wired to quad clock buffer U104, (1) also applies.

Schematic Net Name I/O Standard FPGA (U1) Pin

(2)

(2)

W9

W8

System Clock

[Figure 2-1, callout 11]

The system clock source is a Silicon Labs SI5335A quad clock generator U122. The system

clock (SYSCLK) is a LVDS 300 MHz clock sourced from the CLK0A output pair of U122.

SYSCLK is wired to SI53340 U157 clock MUX/quad-buffer input CLK0 P/N inputs (pins 6 (P)

and 7 (N)).

The 3.3V SI53340 U157 has four LVDS output clock pairs:

• U157 output Q0 drives clock pair SYSCLK1_300_P/N, connected to XCVU9P FPGA U1

bank 47 global clock (GC) pins G31 and F31 (series capacitor coupled), respectively.

• U157 output Q1 drives clock pair SYSCLK2_300_P/N which is not connected to XCVU9P

FPGA U1, it is wired to the SI53340 U104 CLK1 input.

• U157 output Q2 drives clock pair USER_SI570_CLOCK1_P/N, connected to XCVU9P

FPGA U1 bank 64 global clock (GC) pins AW23 and AW22, respectively.

• U157 output Q3 is not connected.

Clock generator: U122 Silicon Labs SI5335A-B03426-GM (CLK0A 300 MHz)

• Low phase jitter of 0.7 pS RMS

• LVDS differential output

• Quad clock buffer: Silicon Labs SI53340-B-GM (SYSCLK1, SYSCLK2 300 MHz)

• Additive phase jitter of 43 fs RMS

VCU118 Board User Guide 43

UG1224 (v1.0) December 15, 2016

• LVDS differential output

www.xilinx.com

Page 44

X-Ref Target - Figure 3-4

X18004-102616

Send Feedback

Chapter 3: Board Component Descriptions

The 300 MHz system clock circuit (U122 upper right CLK0 branch) is shown in Figure 3-4.

Figure 3-4: VCU118 System Clock

The VCU118 SYSCLKn_300 clocks have an optional clock oscillator source U18 as shown in

Figure 3-4. SI570 I