Page 1

TM

LogiCORE

IP

Ethernet AVB

Endpoint v2.4

User Guide

UG492 July 23, 2010

Page 2

Xilinx is providing this product documentation, hereinafter “Information,” to you “AS IS” with no warranty of any kind, express or implied.

Xilinx makes no representation that the Information, or any particular implementation thereof, is free from any claims of infringement. You

are responsible for obtaining any rights you may require for any implementation based on the Information. All specifications are subject to

change without notice.

XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE INFORMATION OR

ANY IMPLEMENTATION BASED THEREON, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR REPRESENTATIONS THAT

THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR

FITNESS FOR A PARTICULAR PURPOSE.

Except as stated herein, none of the Information may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or

transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without

the prior written consent of Xilinx.

© 2008-2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx

in the United States and other countries. The PowerPC name and logo are registered trademarks of IBM Corp. and used under license.All

other trademarks are the property of their respective owners.

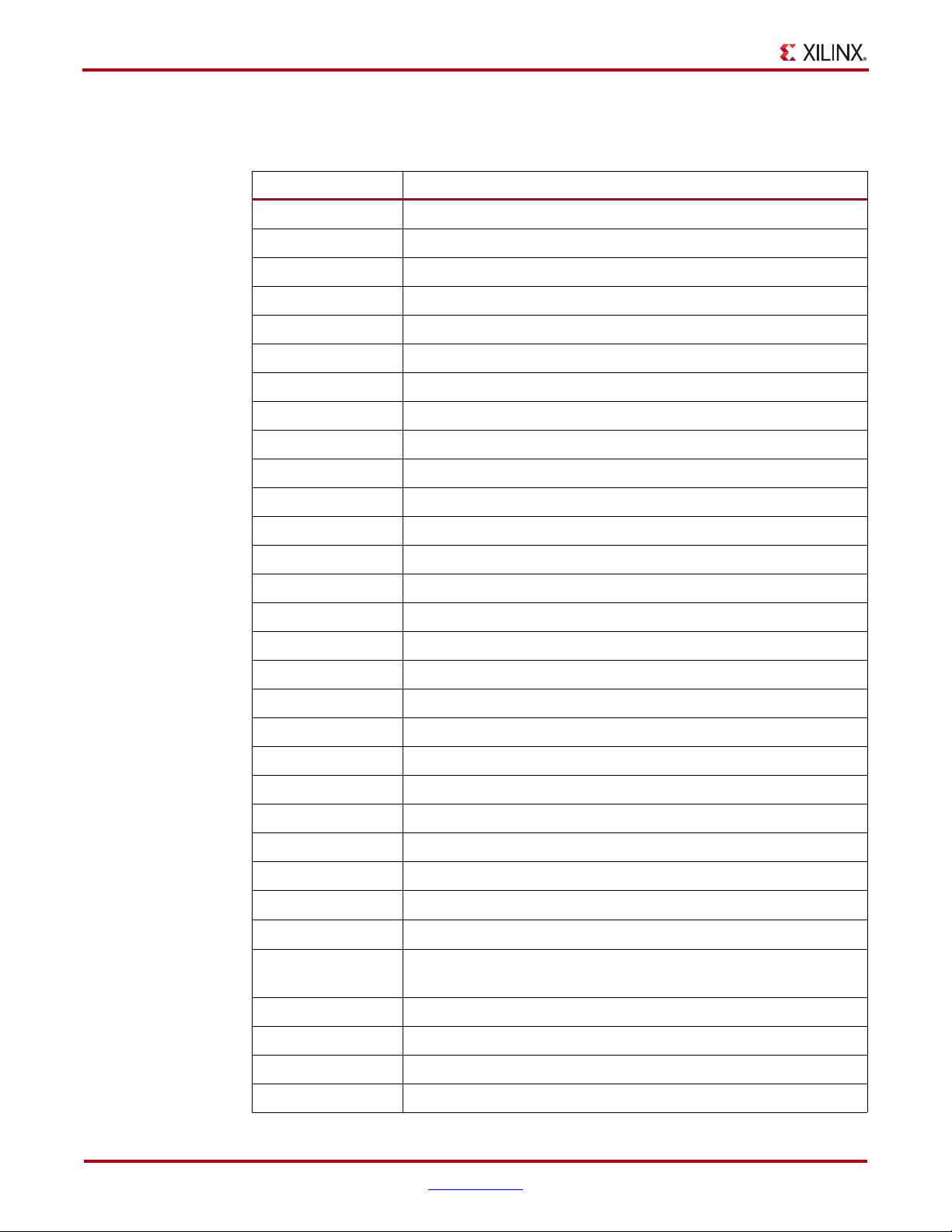

Revision History

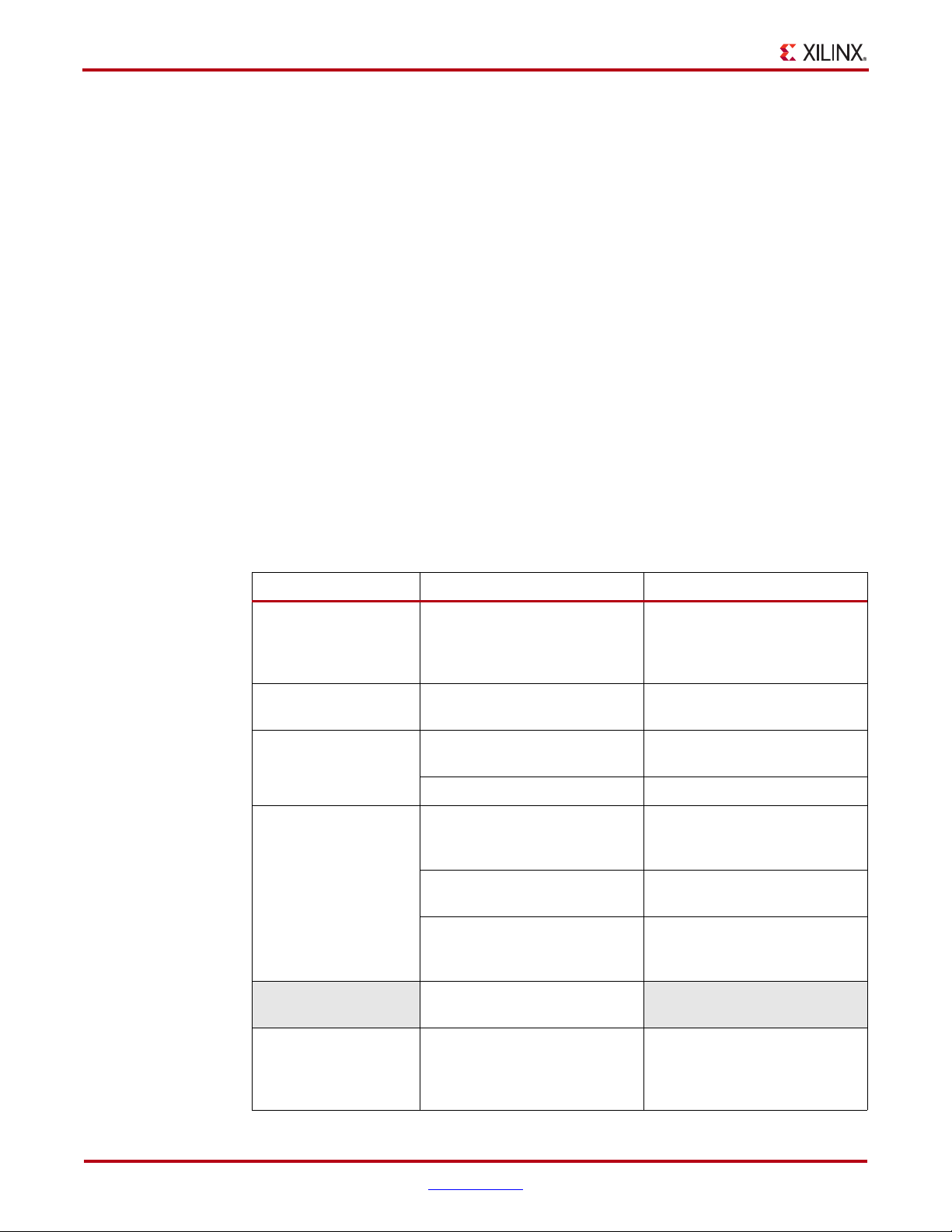

The following table shows the revision history for this document.

Date Version Revision

9/18/08 v1.1 Initial Xilinx release; ISE® 10.1, Update 3.

4/24/09 v1.2 Updated to version 1.2 of the core; Xilinx tools 11.1.

6/24/09 v2.1 Updated to version 2.1 of the core; Xilinx tools 11.2.

9/16/09 v2.2 Updated to version 2.2 of the core; Xilinx tools 11.3.

4/19/10 v2.3 Updated to version 2.3 of the core; Xilinx tools 12.1.

7/23/10 v2.4 Updated to version 2.4 of the core; Xilinx tools 12.2.

Added four chapters from the Getting Started Guide to this User Guide:

• Licensing the Core

• Quick Start Example Design

• Detailed Example Design (Standard Format)

• Detailed Example Design (EDK format)

The Getting Started Guide is being discontinued in this release.

Ethernet AVB Endpoint User Guide www.xilinx.com UG492 July 23, 2010

Page 3

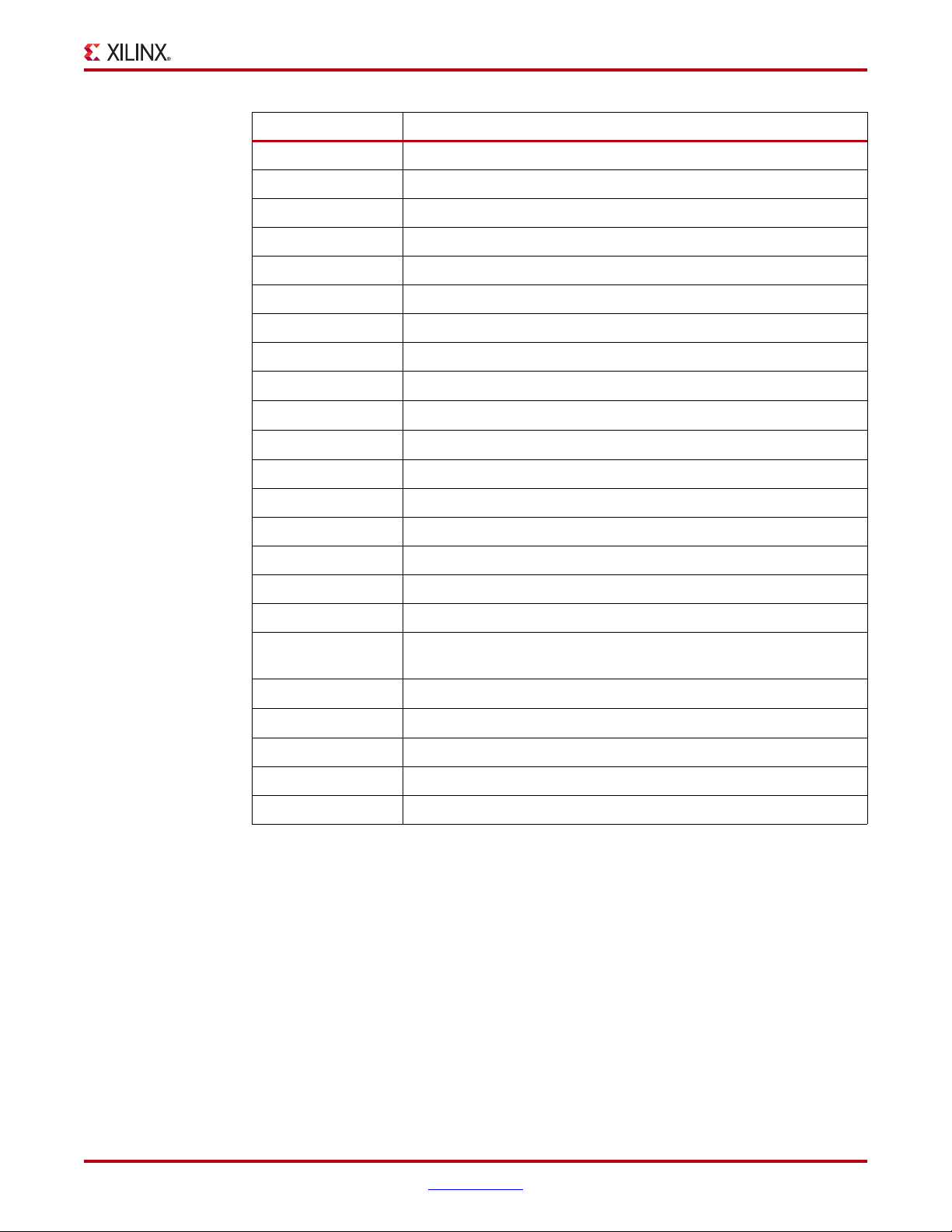

Table of Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Schedule of Figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Schedule of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Online Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

List of Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Chapter 1: Introduction

System Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

About the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Recommended Design Experience. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Additional Core Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Technical Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Feedback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Ethernet AVB Endpoint Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Chapter 2: Licensing the Core

Before you Begin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

License Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Simulation Only . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Full System Hardware Evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Full . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Obtaining Your License Key. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Simulation License . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Full System Hardware Evaluation License . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Obtaining a Full License Key . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Installing the License File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Chapter 3: Overview of Ethernet Audio Video Bridging

AVB Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

P802.1AS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

P802.1Qav . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

P802.1Qat. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Typical Implementation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Ethernet AVB Endpoint User Guide www.xilinx.com 3

UG492 July 23, 2010

Page 4

Chapter 4: Generating the Core

Ethernet AVB GUI Page 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Component Name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Core Delivery Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Ethernet AVB GUI Page 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Number of PLB Masters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

PLB Base Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Parameter Values in the XCO File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Output Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Chapter 5: Core Architecture

Standard CORE Generator Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

EDK pcore Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Functional Block Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

PLB Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

AV Traffic Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Legacy Traffic Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Tx Arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Rx Splitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

MAC Header Filters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Precise Timing Protocol Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Software Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Tri-Mode Ethernet MACs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Core Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Clocks and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Legacy Traffic Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

AV Traffic Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Tri-Mode Ethernet MAC Client Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Processor Local Bus (PLB) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Interrupt Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

PTP Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Chapter 6: Ethernet AVB Endpoint Transmission

Tx Legacy Traffic I/F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Error Free Legacy Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Errored Legacy Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Tx AV Traffic I/F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Tx Arbiter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Chapter 7: Ethernet AVB Endpoint Reception

Rx Splitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Rx Legacy Traffic I/F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Error Free Legacy Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Errored Legacy Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Legacy MAC Header Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Rx AV Traffic I/F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Error Free AV Traffic Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Errored AV Traffic Reception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 5

Chapter 8: Real Time Clock and Time Stamping

Real Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

RTC Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Clock Outputs Based on the Synchronized RTC Nanoseconds Field . . . . . . . . . . . . . 79

Time Stamping Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Time Stamp Sampling Position of MAC Frames. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

IEEE1722 Real Time Clock Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Chapter 9: Precise Timing Protocol Packet Buffers

Tx PTP Packet Buffer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Rx PTP Packet Buffer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Chapter 10: Configuration and Status

Processor Local Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Single Read Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Single Write Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

PLB Address Map and Register Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Ethernet AVB Endpoint Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Tri-Mode Ethernet MAC Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Chapter 11: Constraining the Core

Required Constraints. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Device, Package, and Speedgrade Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

I/O Location Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Placement Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Timing Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Chapter 12: System Integration

Using the Xilinx LogiCORE IP Tri-Mode Ethernet MACs . . . . . . . . . . . . . . . . . . . 111

LogiCORE IP Tri-Mode Ethernet MAC (Soft Core) . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

LogiCORE IP Embedded Tri-Mode Ethernet MACs . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Connection of the PLB to the EDK for LogiCORE IP Ethernet MACs. . . . . . . . . . . . 119

Using the Xilinx XPS LocalLink Tri-Mode Ethernet MAC . . . . . . . . . . . . . . . . . . . 124

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

xps_ll_temac configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

System Overview: AVB capable xps_ll_temac . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Ethernet AVB Endpoint Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

MHS File Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Chapter 13: Software Drivers

Clock Master. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Clock Slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Software System Integration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Driver Instantiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Interrupt Service Routine Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Core Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Ethernet AVB Endpoint Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Starting and Stopping the AVB Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Ethernet AVB Endpoint User Guide www.xilinx.com 5

UG492 July 23, 2010

Page 6

Chapter 14: Quick Start Example Design

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Generating the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Implementing the Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Simulating the Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Setting up for Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Functional Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Timing Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

What’s Next? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Chapter 15: Detailed Example Design (Standard Format)

Directory and File Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

<project directory> . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

<project directory>/<component name> . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

<component name>/doc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

<component name>/example design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

<component name>/implement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

implement/results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

<component name>/simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

simulation/functional . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

simulation/timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

<component_name>/drivers/v2_04_a . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

drivers/avb_v2_04_a/data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

drivers/avb_v2_04_a/examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

drivers/avb_v2_04_a/src . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Implementation Scripts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Simulation Scripts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Functional Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Timing Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Example Design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Top-Level Example Design HDL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Ethernet Frame Stimulus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Ethernet Frame Checker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Loopback Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

PLB Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Customizing the Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

6 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 7

Chapter 16: Detailed Example Design (EDK format)

Directory and File Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

<project directory> . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

<project directory>/<component name> . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

<component name>/doc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

<component name>/MyProcessorIPLib . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

MyProcessorIPLib/pcores/eth_avb_endpoint_v2_04_a . . . . . . . . . . . . . . . . . . . . . . . 161

pcores/eth_avb_endpoint_v2_04_a/data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

pcores/eth_avb_endpoint_v2_04_a/hdl/vhdl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

pcores/eth_avb_endpoint_v2_04_a/netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

MyProcessorIPLib/drivers/avb_v2_04_a . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

drivers/avb_v2_04_a/data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

drivers/avb_v2_04_a/examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

drivers/avb_v2_04_a/src . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Importing the Ethernet AVB Endpoint Core into the Embedded

Development Kit (EDK)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Appendix A: RTC Time Stamp Accuracy

Time Stamp Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

RTC Real Time Instantaneous Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

RTC Sampling Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Accuracy Resulting from the Combined Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Ethernet AVB Endpoint User Guide www.xilinx.com 7

UG492 July 23, 2010

Page 8

8 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 9

Schedule of Figures

Chapter 1: Introduction

Chapter 2: Licensing the Core

Chapter 3: Overview of Ethernet Audio Video Bridging

Figure 3-1: Example AVB Home Network. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 3-2: Example Ethernet AVB Endpoint System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Chapter 4: Generating the Core

Figure 4-1: GUI Page 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 4-2: GUI Page 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Chapter 5: Core Architecture

Figure 5-1: Ethernet AVB Endpoint Core Block Diagram for Connection to

LogiCORE IP Tri-Mode Ethernet MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 5-2: Ethernet AVB Endpoint Core Block Diagram for Connection to the

XPS Tri-Mode Ethernet MAC (xps_ll_temac) in the EDK. . . . . . . . . . . . . . . . . . . . . . . . 41

Chapter 6: Ethernet AVB Endpoint Transmission

Figure 6-1: Normal Frame Transmission across the Legacy Traffic Interface . . . . . . . . . 58

Figure 6-2: Legacy Frame Transmission with Underrun . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 6-3: Normal Frame Transmission across the AV Traffic Interface. . . . . . . . . . . . . 60

Figure 6-4: Credit-based Shaper Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Chapter 7: Ethernet AVB Endpoint Reception

Figure 7-1: Normal Frame Reception across the Legacy Traffic Interface. . . . . . . . . . . . . 66

Figure 7-2: Errored Frame Reception across the Legacy Traffic Interface. . . . . . . . . . . . . 67

Figure 7-3: Normal Frame Reception: Address Filter Match . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 7-4: Filtering of Frames with a Full DA Match . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 7-5: Filtering of Frames with a Partial DA Match . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 7-6: Filtering of VLAN Frames with a Specific Priority Value. . . . . . . . . . . . . . . . 72

Figure 7-7: Normal Frame Reception across the AV Traffic Interface . . . . . . . . . . . . . . . . 73

Figure 7-8: Errored Frame Reception across the AV Traffic Interface . . . . . . . . . . . . . . . . 74

Chapter 8: Real Time Clock and Time Stamping

Figure 8-1: Real Time Counter (RTC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 8-2: Increment of Sub-nanoseconds and Nanoseconds Field . . . . . . . . . . . . . . . . . 77

Figure 8-3: Time Stamping Position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Ethernet AVB Endpoint User Guide www.xilinx.com 9

UG492 July 23, 2010

Page 10

Chapter 9: Precise Timing Protocol Packet Buffers

Figure 9-1: Tx PTP Packet Buffer Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 9-2: Rx PTP Packet Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Chapter 10: Configuration and Status

Figure 10-1: Single Read Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Figure 10-2: Single Write Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 10-3: PLB Address Space of the Ethernet AVB Endpoint Core and Connected

Tri-Mode Ethernet MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Chapter 11: Constraining the Core

Chapter 12: System Integration

Figure 12-1: Connection to the Tri-Mode Ethernet MAC Core

(without Ethernet Statistics) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 12-2: Connection to the Tri-Mode Ethernet MAC and Ethernet Statistic Cores 115

Figure 12-3: Connection to the Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC

(without Ethernet Statistics) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Figure 12-4: Connection to the Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC

and Ethernet Statistic Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Figure 12-5: Connection of the Ethernet AVB Endpoint Core into an Embedded

Processor Sub-system . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Figure 12-6: Connection into an Embedded Processor Sub-system with an

EDK Top-level Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Figure 12-7: Connection into an Embedded Processor Sub-system with an

ISE Software Top-Level Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Figure 12-8: Connection of the Ethernet AVB Endpoint Core into an Embedded

Processor Sub-system . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 12-9: Connection to the XPS LocalLink Tri-Mode Ethernet MAC. . . . . . . . . . . . 127

Chapter 13: Software Drivers

Chapter 14: Quick Start Example Design

Figure 14-1: Ethernet AVB Endpoint Example Design and Test Bench . . . . . . . . . . . . . 138

Figure 14-2: Ethernet AVB Endpoint Core Customization Screen . . . . . . . . . . . . . . . . . . 140

Chapter 15: Detailed Example Design (Standard Format)

Figure 15-1: Example Design HDL for the Ethernet AVB Endpoint . . . . . . . . . . . . . . . . 152

Figure 15-2: Ethernet AVB Endpoint Demonstration Test Bench . . . . . . . . . . . . . . . . . . 156

Figure 15-3: Simulator Wave Window Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

10 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 11

Chapter 16: Detailed Example Design (EDK format)

Appendix A: RTC Time Stamp Accuracy

Figure A-1: RTC Periodic Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Figure A-2: RTC Sampling Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Figure A-3: Sampling Position Uncertainty . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Figure A-4: Overall Time Stamp Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Ethernet AVB Endpoint User Guide www.xilinx.com 11

UG492 July 23, 2010

Page 12

12 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 13

Schedule of Tables

Chapter 1: Introduction

Chapter 2: Licensing the Core

Chapter 3: Overview of Ethernet Audio Video Bridging

Chapter 4: Generating the Core

Table 4-1: XCO File Values and Default Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Chapter 5: Core Architecture

Table 5-1: Clocks and Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 5-2: Legacy Traffic Signals: Transmitter Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 5-3: Legacy Traffic Signals: Receiver Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 5-4: AV Traffic Signals: Transmitter Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 5-5: AV Traffic Signals: Receiver Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 5-6: Tri-Mode Ethernet MAC Transmitter Interface. . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 5-7: Tri-Mode Ethernet MAC Receiver Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 5-8: Tri-Mode Ethernet MAC Host Interface (Configuration/Status) . . . . . . . . . . . 51

Table 5-9: PLB Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 5-10: Interrupt Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 5-11: PTP Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Chapter 6: Ethernet AVB Endpoint Transmission

Chapter 7: Ethernet AVB Endpoint Reception

Chapter 8: Real Time Clock and Time Stamping

Chapter 9: Precise Timing Protocol Packet Buffers

Chapter 10: Configuration and Status

Table 10-1: Tx PTP Packet Buffer Control Register (PLB_base_address + 0x2000) . . . . . 92

Table 10-2: Rx PTP Packet Buffer Control Register (PLB_base_address + 0x2004) . . . . . 93

Table 10-3: Rx Filtering Control Register (PLB_base_address + 0x2008) . . . . . . . . . . . . . . 93

Table 10-4: Tx Arbiter Send Slope Control Register (PLB_base_address + 0x200C) . . . . 94

Table 10-5: Tx Arbiter Idle Slope Control Register (PLB_base_address + 0x2010) . . . . . 94

Table 10-6: RTC Nanoseconds Field Offset (PLB_base_address + 0x2800) . . . . . . . . . . . . 94

Ethernet AVB Endpoint User Guide www.xilinx.com 13

UG492 July 23, 2010

Page 14

Table 10-7: Seconds Field Offset bits [31:0] (PLB_base_address + 0x2808) . . . . . . . . . . . . 95

Table 10-8: Seconds Field Offset bits [47:32] (PLB_base_address + 0x280C) . . . . . . . . . . 95

Table 10-9: RTC Increment Value Control Register (PLB_base_address + 0x2810). . . . . 95

Table 10-10: Current RTC Nanoseconds Value (PLB_base_address + 0x2814). . . . . . . . . 96

Table 10-11: Current RTC Seconds Field Value bits [31:0] (PLB_base_address + 0x2818) 96

Table 10-12: Current RTC Seconds Field Value bits [47:32]

(PLB_base_address + 0x281C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 10-13: RTC Interrupt Clear Register (PLB_base_address + 0x2820). . . . . . . . . . . . . 96

Table 10-14: RTC Phase Adjustment Register (PLB_base_address + 0x2824). . . . . . . . . . 97

Table 10-15: Software Reset Register (Address at PLB_base_address + 0x2828) . . . . . . . 97

Table 10-16: MAC Header Filter Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 10-17: Tri-Mode Ethernet MAC and Ethernet Statistics

Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Chapter 11: Constraining the Core

Chapter 12: System Integration

Chapter 13: Software Drivers

Chapter 14: Quick Start Example Design

Chapter 15: Detailed Example Design (Standard Format)

Table 15-1: Project Directory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 15-2: Component Name Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 15-3: Doc Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 15-4: Example Design Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 15-5: Implement Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 15-6: Results Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 15-7: Simulation Directory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 15-8: Functional Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 15-9: Timing Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 15-10: Driver Data Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 15-11: Driver Example Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 15-12: Driver Source Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

14 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 15

Chapter 16: Detailed Example Design (EDK format)

Table 16-1: Project Directory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Table 16-2: Component Name Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Table 16-3: Doc Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 16-4: Driver Data Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 16-5: Driver Data Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 16-6: pcore netlist Directory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 16-7: Driver Data Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Table 16-8: Driver Example Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Table 16-9: Driver Source Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Appendix A: RTC Time Stamp Accuracy

Ethernet AVB Endpoint User Guide www.xilinx.com 15

UG492 July 23, 2010

Page 16

16 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 17

About This Guide

The LogiCORE™ IP Ethernet AVB User Guide provides information about the Ethernet

Audio Video Bridging (AVB) Endpoint core, including how to customize, generate, and

implement the core in supported Xilinx FPGA families.

Guide Contents

This guide contains the following chapters:

• Preface, “About this Guide” introduces the organization and purpose of this guide

and the conventions used in this document.

• Chapter 1, “Introduction” introduces the core and provides related information

including additional core resources, technical support, and how to submit feedback to

Xilinx.

• Chapter 2, “Licensing the Core” describes the available license options for the core

and how to obtain them.

• Chapter 3, “Overview of Ethernet Audio Video Bridging” provides an overview of

Ethernet Audio Video Bridging, including relevant specifications and a typical

implementation.

• Chapter 4, “Generating the Core” provides information about generating and

customizing the core using the CORE Generator™ software.

• Chapter 5, “Core Architecture” describes the major functional blocks of the Ethernet

AVB Endpoint core.

• Chapter 6, “Ethernet AVB Endpoint Transmission” describes data transmission over

an AVB network.

• Chapter 7, “Ethernet AVB Endpoint Reception” describes data reception over an AVB

network.

• Chapter 8, “Real Time Clock and Time Stamping” describes two components that are

partially responsible for the AVB timing synchronization protocol.

• Chapter 9, “Precise Timing Protocol Packet Buffers” describes two components that

are partially responsible for the transmission and reception of Ethernet Precise Timing

Protocol frames; these frames contain the AVB timing synchronization data.

• Chapter 10, “Configuration and Status” defines general guidelines for configuring

and monitoring the Ethernet AVB Endpoint core, including an introduction to the PLB

configuration bus and a description of the core management registers.

• Chapter 11, “Constraining the Core” defines the Ethernet AVB core constraints.

• Chapter 12, “System Integration” describes the integration of the Ethernet AVB

Endpoint core into a system, including connection of the core to the Xilinx Tri-Mode

Ethernet MAC and Ethernet Statistic cores.

Preface

Ethernet AVB Endpoint User Guide www.xilinx.com 17

UG492 July 23, 2010

Page 18

Preface: About This Guide

• Chapter 13, “Software Drivers” describes the function of the software drivers

• Chapter 14, “Quick Start Example Design”Chapter 3, “Quick Start Example Design”

• Chapter 15, “Detailed Example Design (Standard Format)” provides detailed

• Chapter 16, “Detailed Example Design (EDK format)” provides detailed information

• Appendix A, “RTC Time Stamp Accuracy” describe the necessity of accurate time

Conventions

This document uses the following conventions. An example illustrates each convention.

delivered with the core.

provides instructions to quickly generate the core and run the example design

through implementation and simulation using the default settings.

information about the core when generated in the standard CORE Generator format,

including a description of files and the directory structure generated

about the core when generated in the Standard Embedded Development Kit (EDK)

format, including a description of files and the directory structure generated.

stamps, essential to the Precise Timing Protocol across the network link, and provides

some of the ways inaccuracies are introduced.

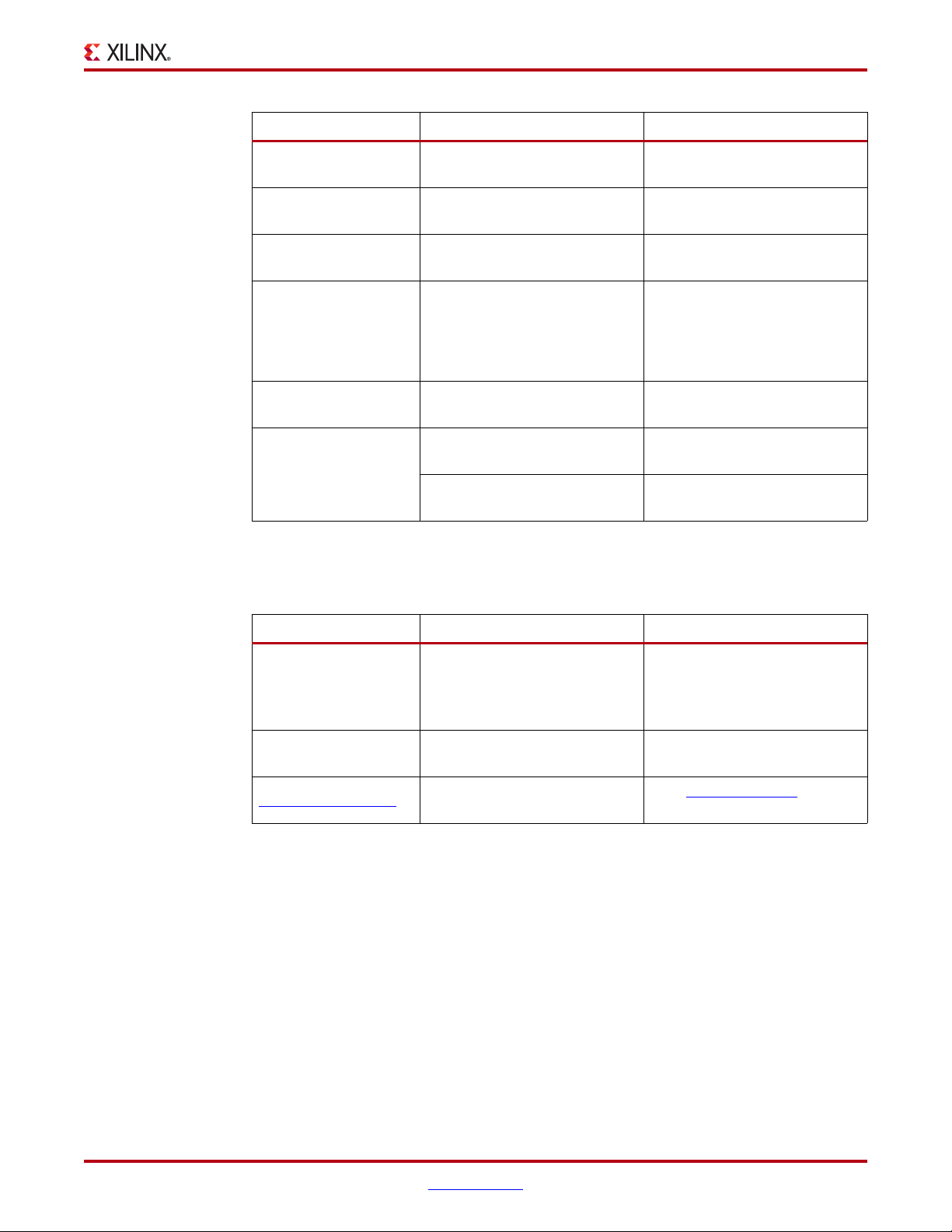

Typographical

The following typographical conventions are used in this document:

Courier font

Courier bold

Helvetica bold

Italic font

Convention Meaning or Use Example

Messages, prompts, and

program files that the system

displays. Signal names in text

also.

Literal commands that you enter

in a syntactical statement

Commands that you select from

a menu

Keyboard shortcuts Ctrl+C

Variables in a syntax statement

for which you must supply

values

References to other manuals

Emphasis in text

speed grade: - 100

ngdbuild design_name

File → Open

ngdbuild design_name

See the User Guide for more

information.

If a wire is drawn so that it

overlaps the pin of a symbol, the

two nets are not connected.

Dark Shading

Square brackets [ ]

18 www.xilinx.com Ethernet AVB Endpoint User Guide

Items that are not supported or

reserved

An optional entry or parameter.

However, in bus specifications,

such as bus[7:0], they are

required.

This feature is not supported

ngdbuild [option_name]

design_name

UG492 July 23, 2010

Page 19

Convention Meaning or Use Example

Conventions

Braces { }

Vertical bar |

Angle brackets < >

Vertical ellipsis

.

.

.

Horizontal ellipsis . . .

Notations

Online Document

The following conventions are used in this document:

A list of items from which you

must choose one or more

Separates items in a list of

choices

User-defined variable or in code

samples

Repetitive material that has

been omitted

Repetitive material that has

been omitted

The prefix ‘0x’ or the suffix ‘h’

indicate hexadecimal notation

An ‘_n’ means the signal is

active low

lowpwr ={on|off}

lowpwr ={on|off}

<directory name>

IOB #1: Name = QOUT’

IOB #2: Name = CLKIN’

.

.

.

allow block block_name loc1

loc2 ... locn;

A read of address 0x00112975

returned 45524943h.

usr_teof_n is active low.

Convention Meaning or Use Example

See the section “Guide

Contents” for details.

See “Title Formats” in Chapter 1

for details.

See Figure 2-5 in the Vir tex-5

FPGA User Guide.

Go to www.xilinx.com

latest speed files.

Blue text

Red text

Blue, underlined text

Cross-reference link to a

location in the current

document

Cross-reference link to a

location in another document

Hyperlink to a website (URL)

for the

Ethernet AVB Endpoint User Guide www.xilinx.com 19

UG492 July 23, 2010

Page 20

Preface: About This Guide

List of Abbreviations

The following table describes acronyms used in this manual.

Acronym Spelled Out

AV Audio Video

AVB Audio Video Bridging

BMCA Best Master Clock Algorithm

CRC Cyclic Redundancy Check

DA Destination Address

DMA Direct Memory Access

DSP Digital Signal Processor

EDK Embedded Development Kit

EMAC Ethernet MAC

FCS Frame Check Sequence

FIFO First In First Out

FPGA Field Programmable Gate Array.

Gbps Gigabits per second

GMII Gigabit Media Independent Interface

GUI Graphical User Interface

HDL Hardware Description Language

IES Incisive Unified Simulator

I/F Interface

IO Input/Output

IP Intellectual Property

ISE® Integrated Software Environment

KHz Kilo Hertz

LLDP Link Layer Discovery Protocol

MAC Media Access Controller

Mbps Megabits per second

MDIO Management Data Input/Output

MHS

Microprocessor Hardware Description: a proprietary file format,

using the .mhs file extension, for a XPS project

MHz Mega Hertz

ms milliseconds

MPMC Multi-Port Memory Controller

ns nanoseconds

20 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 21

Acronym Spelled Out

PHY physical-side interface

PHYAD Physical Address

PLB Processor Local Bus

PTP Precise Timing Protocol

REGAD Register Address

RTC Real Time Clock

RO Read Only

R/W Read/Write

Rx Receive

SFD Start of Frame Delimiter

SRP Stream Reservation Protocol

TEMAC Tri-Mode Ethernet MAC

TCP/IP Transmission Control Protocol / Internet Protocol.

Conventions

TOE TCP/IP Offload Engine

Tx Transmitter

UCF User Constraints File

us microseconds

VHDL VHSIC Hardware Description Language

(VHSIC an acronym for Very High-Speed Integrated Circuits)

VLAN Virtual LAN (Local Area Network)

WO Write Only

XCO Xilinx CORE Generator core source file

XPS Xilinx Platform Studio (part of the EDK software)

XPS_LL_TEMAC XPS LocalLink Tri-Mode Ethernet MAC

Ethernet AVB Endpoint User Guide www.xilinx.com 21

UG492 July 23, 2010

Page 22

Preface: About This Guide

22 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 23

Introduction

This chapter introduces the core and provides related information including

recommended design experience, additional resources, technical support, and how to

submit feedback to Xilinx.

The Ethernet AVB Endpoint core is a fully verified solution that supports Verilog-HDL and

VHDL. In addition, the example design in this guide is provided in both Verilog and

VHDL formats.

System Requirements

Windows

• Windows XP Professional 32-bit/64-bit

• Windows Vista Business 32-bit/64-bit Linux

• Red Hat Enterprise Linux WS v4.0 32-bit/64-bit

• Red Hat Enterprise Desktop v5.0 32-bit/64-bit (with Workstation Option)

• SUSE Linux Enterprise (SLE) desktop and server v10.1 32-bit/64-bit

Chapter 1

About the Core

Software

• ISE® software v12.2

The Ethernet AVB Endpoint core is available through the Xilinx CORE Generator™

software included in the latest IP Update on the Xilinx IP Center. For detailed information

about the core, see the Ethernet AVB Endpoint product page

licensing options, see Chapter 2, “Licensing the Core.”

. For information about

Ethernet AVB Endpoint User Guide www.xilinx.com 23

UG492 July 23, 2010

Page 24

Chapter 1: Introduction

Recommended Design Experience

Although the Ethernet AVB Endpoint core is a fully verified solution, the challenge

associated with implementing a complete design varies depending on the configuration

and functionality of the application. For best results, previous experience building highperformance, pipelined FPGA designs using Xilinx implementation software and user

constraint files (UCFs) is recommended. In addition, previous experience using the

Embedded Development Kit (EDK) and developing embedded software applications is

recommended. Contact your local Xilinx representative for a closer review and estimation

for your specific requirements.

Additional Core Resources

For detailed information and updates about the Ethernet AVB Endpoint core, see the

following documents, available from the product page

• Ethernet AVB Endpoint Data Sheet

• Ethernet AVB Endpoint User Guide

From the document directory after generating the core:

• Ethernet AVB Endpoint Release Notes

.

Technical Support

For technical support, see www.support.xilinx.com/. Questions are routed to a team of

engineers with expertise using the Ethernet AVB Endpoint core.

Xilinx provides technical support for use of this product as described in this guide. Xilinx

cannot guarantee timing, functionality, or support of this product for designs that do not

follow these guidelines.

Feedback

Xilinx welcomes comments and suggestions about the Ethernet AVB Endpoint core and

the documentation supplied with the core.

Ethernet AVB Endpoint Core

For comments or suggestions about the Ethernet AVB Endpoint core, submit a WebCase

from www.xilinx.com/support/clearexpress/websupport.htm/

Be sure to include the following information:

• Product name

• Core version number

• Explanation of your comments

24 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 25

Document

Feedback

For comments or suggestions about this document, submit a WebCase from

www.xilinx.com/support/clearexpress/websupport.htm/

Be sure to include the following information:

• Document title

• Document number

• Page number(s) to which your comments refer

• Explanation of your comments

Ethernet AVB Endpoint User Guide www.xilinx.com 25

UG492 July 23, 2010

Page 26

Chapter 1: Introduction

26 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 27

Licensing the Core

This chapter provides instructions for obtaining a license key for the Ethernet AVB

Endpoint core, which you must do before using the core in your designs. The Ethernet AVB

Endpoint core is provided under the terms of the Xilinx

Before you Begin

This chapter assumes that you have installed the required Xilinx® ISE® Design Suite

version following the instructions provided by the Xilinx ISE Installation, Licensing and

Release Notes Guide, www.xilinx.com/support/documentation/dt_ise.htm

software requirements can be found on the product web page for this core,

www.xilinx.com/products/ipcenter/DO-DI-EAVB-EPT.htm

License Options

Chapter 2

Core Site License Agreement.

. Detailed

.

The Ethernet AVB Endpoint core provides three licensing options. After installing the

required ISE Design Suite version, choose a license option.

Simulation Only

The Simulation Only Evaluation license key is provided with the ISE CORE Generator tool.

This key lets you assess core functionality with either the example design provided with

the Ethernet AVB Endpoint core, or alongside your own design and allows you to

demonstrate the various interfaces to the core in simulation. (Functional simulation is

supported by a dynamically generated HDL structural model.)

Full System Hardware Evaluation

The Full System Hardware Evaluation license key is available at no cost and lets you fully

integrate the core into an FPGA design, place and route the design, evaluate timing, and

perform back-annotated gate-level simulation of the core using the demonstration test

bench provided with the core.

In addition, the license key lets you generate a bitstream from the placed and routed

design, which can then be downloaded to a supported device and tested in hardware. The

core can be tested in the target device for a limited time before timing out (ceasing to

function), at which time it can be reactivated by reconfiguring the device.

Ethernet AVB Endpoint User Guide www.xilinx.com 27

UG492 July 23, 2010

Page 28

Chapter 2: Licensing the Core

Full

The Full license key is available when you purchase a license for the core and provides full

access to all core functionality both in simulation and in hardware, including:

• Functional simulation support

• Back annotated gate-level simulation support

• Full implementation support including place and route and bitstream generation

• Full functionality in the programmed device with no time outs

Obtaining Your License Key

This section contains information about obtaining a simulation, full system hardware, and

full license keys.

Simulation License

No action is required to obtain the Simulation Only Evaluation license key; it is provided

by default with the Xilinx CORE Generator software.

Full System Hardware Evaluation License

To obtain a Full System Hardware Evaluation license, do the following:

1. Navigate to the product page

2. Click Evaluate.

3. Follow the instructions to install the required Xilinx ISE software and IP Service Packs.

Obtaining a Full License Key

To obtain a Full license key, please follow these instructions:

1. Purchase the license through your local sales office. Once the order has been entered,

an email will be sent to your Account Administrator with instructions on how to

access the account.

2. Navigate to the product page for this core:

www.xilinx.com/products/ipcenter/DO-DI-EAVB-EPT.htm

3. Click Order.

4. Follow the instructions to generate the required license key on the Xilinx Product

Licensing Site, www.xilinx.com/getproduct

Further details can be found at w

Installing the License File

for this core.

.

ww.xilinx.com/products/ipcenter/ipaccess_fee.htm.

The Simulation Only Evaluation license key is provided with the ISE software CORE

Generator system and does not require installation of an additional license file. For the Full

System Hardware Evaluation license and the Full license, an email will be sent to you

containing instructions for installing your license file. Additional details about IP license

key installation can be found in the ISE Design Suite Installation, Licensing and Release

Notes document.

28 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 29

Chapter 3

Overview of Ethernet Audio Video Bridging

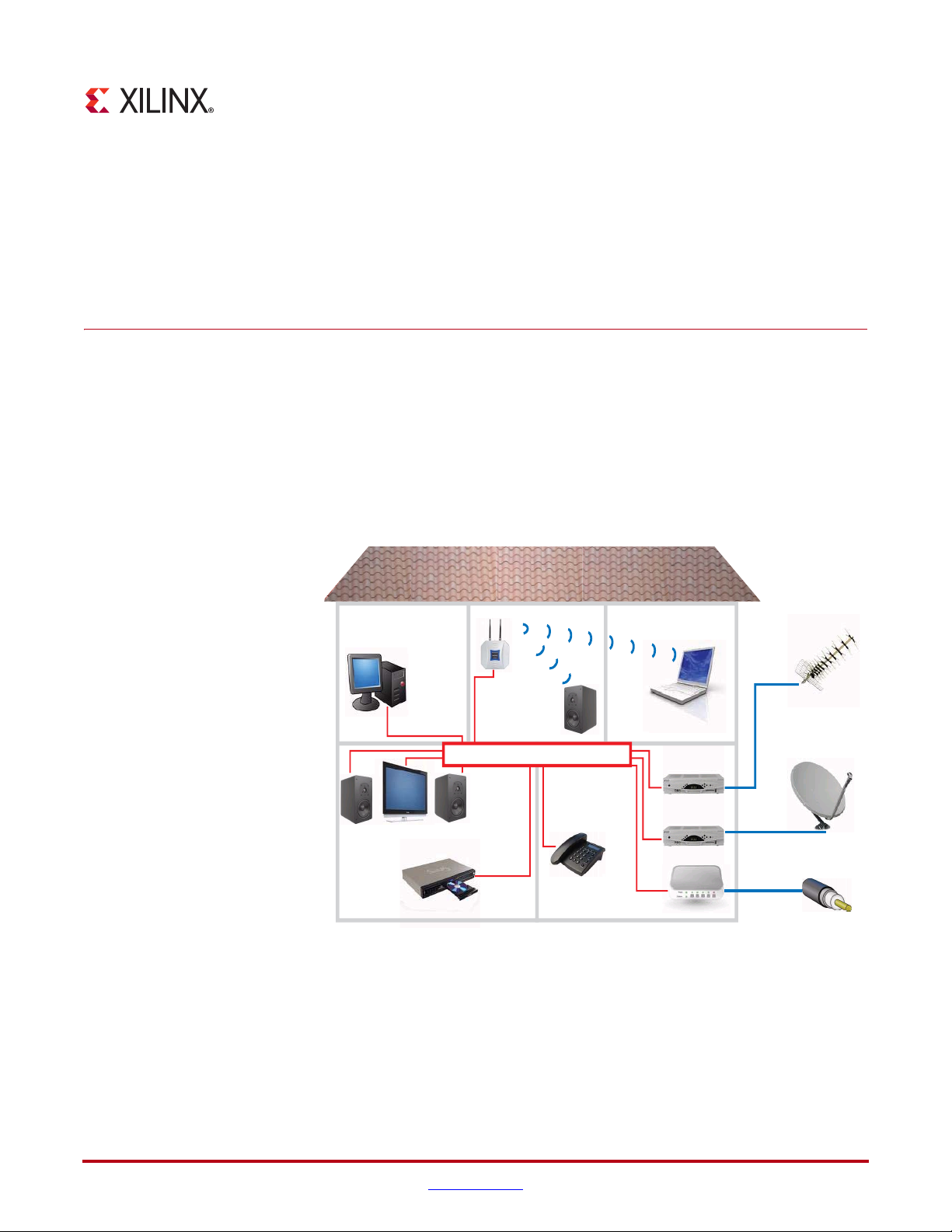

Figure 3-1 illustrates a potential home network, consisting of wired (ethernet) and wireless

components, which utilize the technology being defined by the IEEE802.1 Audio Video

Bridging Task Group. This illustrates potential audio/video talkers (for example, a Cable or

Satellite Content Provider, or home MP3 player) and a number of potential listeners (for

example TV sets which may exist in several rooms). In addition, users of the various

household PCs may be surfing the internet. It is important to note that all of this data is

being transferred across the single home network backbone.

X-Ref Target - Figure 3-1

Home Network

(wireless)

Home Network

Home Network (wired)

DVD player

Figure 3-1: Example AVB Home Network

Te rr e strial

Broadcast

Satellite

Broadband

Ethernet AVB Endpoint User Guide www.xilinx.com 29

UG492 July 23, 2010

Page 30

Chapter 3: Overview of Ethernet Audio Video Bridging

To understand the requirements of this network, we must differentiate between certain

types of data:

• Audio and Video streaming data, referred to in this document as AV traffic. Requires

a good quality of service to avoid, for example, TV picture breakup, and must be

transferred reliably and with guaranteed low latency.

• Other data, referred to in this document as legacy traffic. Does not have the strict

requirement of AV traffic: data can be started, stopped and delayed without serious

consequence for example, a PC surfing the internet.

For these reasons, an important aspect of the AVB technology is therefore to prioritize the

audio/video streaming data (AV traffic) over that of standard data transfer (legacy traffic).

AVB Specifications

The IEEE802.1 Audio Video Task Group is currently working on new specifications which

combine to define this technology:

P802.1AS

This specification defines how to synchronize a common time base across an entire AVB

network, utilizing functionality from IEEE1588 (version 2), and known as Precise Timing

Protocol (PTP). This common time base is in the form of a Real Time Clock (RTC),

effectively a large counter which consists of a 32-bit nanoseconds field and a 48-bit seconds

field. A single device on the network is designated as the clock master (by automatic

resolution) using a Best Master Clock Algorithm (BMCA). All other devices resolve to be

slaves. Using the P802.1AS PTP, all slave devices will regularly update their own RTC to

match that of the network clock master.

This common time base has various applications:

• It can be used to synchronize media clocks (audio clocks or video pixel clocks) across

the entire network to match audio and video data rates between talkers and listeners.

• It can be used by an Ethernet AVB Endpoint System, that is, configured as a "talker",

to time a class measurement interval for an SR stream. (The class measurement

interval for a stream depends upon the SR class associated with the stream: SR class A

corresponds to a class measurement interval of 125 microseconds; SR class B

corresponds to a class measurement interval of 250 microseconds). The class

measurement interval for a stream is used to limit the number of data frames that are

placed into the stream's queue per class measurement interval.

• It can be used by higher layer applications (for example IEEE1722) to provide

presentation time stamps for audio and video data. This is used, for example, to

synchronize the lip sync on a TV set so a viewer hears the words at the same time as

they see the lips move.

The P802.1AS specification is implemented in the Ethernet AVB Endpoint using a

combination of hardware and software. The hardware components are incorporated into

the core, and the software component is provided with the core in the form of drivers.

These drivers should be run on an embedded processor (MicroBlaze™ or PowerPC®).

30 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 31

P802.1Qav

This specification defines the mechanism for queuing and forwarding AV traffic from a

talker to a listener across the network. This can involve several network hops (network

bridge devices that the data must pass through).

P802.1Qav is also responsible for enforcing the 75% maximum bandwidth restriction

across each link of the network that can be reserved for the AV traffic.

Only a subset of the P802.1Qav requirements for an Endpoint is implemented in the

Ethernet AVB Endpoint core, with the following assumptions for talkers and listeners:

Ta lk er Assumptions

• AV traffic Ethernet frames that are input to the Ethernet AVB Endpoint use the VLAN

• Legacy traffic Ethernet frames that are input to the Ethernet AVB Endpoint do not use

• The credit shaping algorithm operates on the AV traffic port; so in order to comply

• The Ethernet AVB Endpoint assumes that any per-stream traffic management has

• If multiple AV streams are input to the Ethernet AVB Endpoint via the AV traffic port,

AVB Specifications

priority values that the Bridges in the network recognize as being associated with SR

classes exclusively for transmitting stream data.

the VLAN priority values that the Bridges in the network recognize as being

associated with SR classes exclusively for transmitting stream data.

with the transmission selection rules for P802.1Qav, all Ethernet frames input on the

AV traffic port are assumed to be of the same SR Class. However, the Ethernet AVB

Endpoint does not enforce this rule and it is acceptable to send a mix of SR Class A

and SR Class B Ethernet frames on the AV traffic port. In this case the Ethernet AVB

Endpoint will not prioritize SR Class A Ethernet frames over SR Class B Ethernet

frames; instead it will apply the credit-based shaper algorithm to all of the Ethernet

frames that are input on the AV t r a ffic port.

been done prior to AV traffic being input on the AV traffic port. To comply with the

transmission selection rules for P802.1Qav it is assumed that if multiple streams are

input to the Ethernet AVB Endpoint via the AV traffic port, that the credit-based shaper

algorithm has been used per stream as the transmission selection mechanism, prior to

the AV traffic being input on the AV traffic port.

it is assumed that the IdleSlope/SendSlope control registers (See “Tx Arbiter Send

Slope Control Register” and “Tx Arbiter Idle Slope Control Register”) are

programmed correctly to be the sum of the IdleSlope /SendSlope values for all the

streams that are input on the AV traffic port. The credit-based shaper algorithm used

on the AV traffic port will enforce a hiLimit/loLimit on the credits to ensure that this

interface is not misused.

Listener Assumptions

• The Ethernet AVB Endpoint provides a mechanism for identifying received AV traffic

for either one or two SR classes (see “Rx Filtering Control Register”); however, it does

not provide any buffering for AV traffic Ethernet frames. Buffering is expected to be

done outside the Ethernet AVB Endpoint, after it has separated out the AV traffic

Ethernet frames, as the buffering requirements are expected to be application-specific.

Ethernet AVB Endpoint User Guide www.xilinx.com 31

UG492 July 23, 2010

Page 32

Chapter 3: Overview of Ethernet Audio Video Bridging

P802.1Qat

This specification defines a Stream Reservation Protocol (SRP) which must be used over

the AVB network. Every listener that intends to receive audio/video AV traffic from a

talker must make a request to reserve that bandwidth. Both the talker and every bridge

device that exists between the talker and the listener has the right to decline this request.

Only if each device is capable of routing the new AV traffic stream without violating the

75% total bandwidth restriction (when taking into account previously granted bandwidth

commitments), will the bandwidth request be successful. However, after granted, this

audio / video stream is reliably routed across the network until the reservation is

removed.

Note:

No hardware components are required for the P802.1Qat specification because this is a pure

software task. This software is not provided by the Ethernet AVB Endpoint core.

Typical Implementation

X-Ref Target - Figure 3-2

Xilinx Device

Audio /

Video

Sources /

Sinks

IEEE 1722

Packet

Manager

Embedded

Processor

System

with TCP/IP

stack

PLB management

AV

traffic

legacy

traffic

Ethernet

AVB

Endpoint

LogiCORE

Tri-Mode

Ethernet

MAC

LogiCORE

Ethernet

PHY

AVB

network

Figure 3-2: Example Ethernet AVB Endpoint System

Figure 3-2 illustrates a typical implementation for the Ethernet AVB Endpoint core.

Endpoint refers to a talker or listener device from the example network shown in

Figure 3-1, as opposed to an intermediate bridge function, which is not supported.

In the implementation, the Ethernet AVB Endpoint core is shown connected to a Xilinx TriMode Ethernet MAC core, which in turn is connected to an AVB capable network. All

devices attached to this network should be AVB capable to obtain the full Quality of

Service advantages for the AV traffic. This AVB network can be a professional or consumer

network (as illustrated in Figure 3-1).

32 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 33

Typical Implementation

Figure 3-2 illustrates that the Ethernet AVB Endpoint core supports the two main types of

data interfaces at the client side:

1. The AV traffic interface is intended for the Quality of Service audio/video data.

Illustrated are a number of audio/video sources (for example, a DVD player), and a

number of audio/video sinks (for example, a TV set). The Ethernet AVB Endpoint

gives priority to the AV traffic interface over the legacy traffic interface, as dictated by

IEEE P802.1Qav 75% bandwidth restrictions.

2. The legacy traffic interface is maintained for best effort ethernet data: Ethernet as we

know it today (for example, the PC surfing the internet in Figure 3-1). Wherever

possible, priority is given to the AV traffic interface (as dictated by IEEE P802.1Qav

bandwidth restrictions) but a minimum of 25% of the total Ethernet bandwidth is

always available for legacy ethernet applications.

The AV traffic interface in Figure 3-2 is shown as interfacing to a 1722 Packet Manager

block. The IEEE1722 is also an evolving standard which will specify the embedding of

audio/video data streams into Ethernet Packets. The 1722 headers within these packets

can optionally include presentation time stamp information. Contact Xilinx for further

system-level information.

Ethernet AVB Endpoint User Guide www.xilinx.com 33

UG492 July 23, 2010

Page 34

Chapter 3: Overview of Ethernet Audio Video Bridging

34 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 35

Generating the Core

The Ethernet AVB Endpoint core is fully configurable using the CORE Generator™

software, which provides a Graphical User Interface (GUI) for defining parameters and

options. For help starting and using the CORE Generator software, see the documentation

supplied with the ISE® software, including the CORE Generator User Guide, available from

www.xilinx.com/support/software_manuals.htm

Ethernet AVB GUI Page 1

Figure 4-1 shows page 1 of the Ethernet AVB Endpoint GUI customization screen.

X-Ref Target - Figure 4-1

Chapter 4

.

Figure 4-1: GUI Page 1

Ethernet AVB Endpoint User Guide www.xilinx.com 35

UG492 July 23, 2010

Page 36

Chapter 4: Generating the Core

Component Name

The component name is used as the base name of the output files generated for the core.

Names must begin with a letter and must be composed from the following characters: a

through z, 0 through 9 and “_”.

Core Delivery Format

The Ethernet AVB Endpoint core can be delivered in two different formats, selectable from

this section of the CORE Generator software Customization GUI:

• Standard CORE Generator software format (provided for the standard ISE software

environment)

This option will deliver the core in the standard CORE Generator software output

format, as used by many other cores including previous versions of this core and all

other Ethernet LogiCORE™ IP solutions.

When generated in this format, the core is designed to interface to the LogiCORE IP

Tri-Mode Ethernet MAC or the LogiCORE IP Embedded Tri-Mode Ethernet MAC

wrappers (available in selected Virtex® families). See Chapter 12, “System

Integration”.

When generated in this format, “Ethernet AVB GUI Page 2” is available for

customization of the “PLB Interface”.

• Generate as an EDK pcore (provided for the Embedded Development Kit)

This option will deliver the core in the standard pcore format, suitable for directly

importing into the Xilinx Embedded Development Kit (EDK) environment.

When generated in this format, the core is designed to interface to the XPS LocalLink

Tri-Mode Ethernet MAC (xps_ll_temac). See Chapter 12, “System Integration”.

When generated in this format, page 2 of the GUI is not available; the “PLB Interface”

will be configured dynamically by the EDK Xilinx Platform Studio (XPS) software.

For directory and file definitions for the two available formats, see Chapter 15, “Detailed

Example Design (Standard Format)” and Chapter 16, “Detailed Example Design (EDK

format).”

36 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 37

Ethernet AVB GUI Page 2

Figure 4-2 shows page 2 of the Ethernet AVB Endpoint GUI customization screen. This

page provides options for configuring the “PLB Interface” of the core. This option is only

required when generating in the Standard CORE Generator software format.

X-Ref Target - Figure 4-2

Ethernet AVB GUI Page 2

Number of PLB Masters

The Ethernet AVB Endpoint core is a PLB slave. On the connected PLB, there may be

several PLB Masters. Each slave must uniquely acknowledge individual masters using

unique PLB signals during transactions. For this reason, set this integer value to match the

number of PLB masters that will be present on the PLB.

PLB Base Address

The Ethernet AVB Endpoint core is a PLB slave. The base address of the core must be

selected. Valid range is 0x00000000 to 0xFFFF8000. The least significant 15 bits of the base

address must be set to 0 (bits 17 to 31 of the PLB Base Address).

Figure 4-2: GUI Page 2

Ethernet AVB Endpoint User Guide www.xilinx.com 37

UG492 July 23, 2010

Page 38

Chapter 4: Generating the Core

Parameter Values in the XCO File

XCO file parameter names and their values are identical to the names and values shown in

the GUI.

Tab le 4- 1 shows the XCO file parameters and values and summarizes the GUI defaults.

The following is an example of the CSET parameters in an XCO file:

CSET component_name=eth_avb_endpoint_v2_4

CSET number_of_plb_masters=2

CSET plb_base_address=00000000

Table 4-1: XCO File Values and Default Values

Parameter XCO File Values Default GUI Setting

component_name ASCII text starting with a letter and

generate_as_edk_pcore Select between true and false false

number_of_plb_masters Select from the range: 1 to 16 2

plb_base_address Select from the range: 0x00000000

Output Generation

The output files generated by the CORE Generator software are placed in the project

directory. The list of output files includes the following items.

• The netlist file for the core

• Supporting CORE Generator software files

• Release notes and documentation

• Subdirectories containing an HDL example design

• Scripts to run the core through the back-end tools and to simulate the core using

Mentor Graphics ModelSim v6.5c, Cadence Incisive Enterprise Simulator (IES) v9.2,

and Synopsys VCS and VCS MX 2009.12

See the following chapters for a complete description of the CORE Generator software

output files and for detailed information about the HDL example design.

eth_avb_endpoint_v2_4

based on the following character

set: a..z, 0..9 and _

0x00000000

to 0xFFFF8000

• Chapter 14, “Quick Start Example Design”

• Chapter 15, “Detailed Example Design (Standard Format)”

• Chapter 16, “Detailed Example Design (EDK format)”

38 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 39

Core Architecture

As described in Chapter 4, “Generating the Core”, the core can be generated in one of two

formats, the functionality of which is described in this chapter:

• “Standard CORE Generator Format” (provided for the standard ISE® software

environment)

This option will deliver the core in the standard CORE Generator™ output format, as

used by many other cores including previous versions of this core and all other

Ethernet LogiCORE™ IP solutions.

When generated in this format, the core is designed to interface to the LogiCORE IP

Tri-Mode Ethernet MAC or the LogiCORE IP Embedded Tri-Mode Ethernet MAC

wrappers (available in selected Virtex® families). See Figure 5-1.

• “EDK pcore Format”(provided for the Embedded Development Kit)

This option will deliver the core in the standard pcore format, suitable for directly

importing into the Xilinx Embedded Development Kit (EDK) environment.

Chapter 5

When generated in this format, the core is designed to interface to the XPS LocalLink

Tri-Mode Ethernet MAC (xps_ll_temac). See Figure 5-2.

Ethernet AVB Endpoint User Guide www.xilinx.com 39

UG492 July 23, 2010

Page 40

Chapter 5: Core Architecture

PLB I/F

Standard CORE Generator Format

Figure 5-1 illustrates the functional blocks of the Ethernet AVB Endpoint core when it is

generated in standard CORE Generator format. As illustrated, this is intended to be

connected to the LogiCORE IP Tri-Mode Ethernet MAC (or to the LogiCORE IP Embedded

Ethernet Wrappers available in certain Virtex devices).

Each of the functional blocks illustrated will be introduced in the following sections of this

chapter. However, observe from the figure that:

• The Host I/F (management interface) of the Tri-Mode Ethernet MAC is connected

directly to the Ethernet AVB Endpoint LogiCORE IP. This enables the MAC to be fully

configured via the “PLB Interface” of the Ethernet AVB Endpoint core.

• The core provides two independent full-duplex interfaces for customer logic: the “AV

Traffic Interface” and the “Legacy Traffic Interface”.

• The “Legacy Traffic Interface” contains “MAC Header Filters”; these are provided to

replace the Address Filter functionality of the LogiCORE IP Tri-Mode Ethernet MACs

(which must be disabled).

X-Ref Target - Figure 5-1

Ethernet AVB Endpoint

.c, .h

software

drivers

Embedded

Processor

Micro

Traffic

Legacy

Traffic

AV

Rx

Tx

Tx

Rx

PLB

AV Traffic I/F

PLB I/F

Legacy Traffic I/F

MAC Header Filters

Precise Timing Protocol (PTP)

Tx PTP Packet Buffer

Rx PTP Packet Buffer

Tx Arbiter

Tx Time Stamp

Real Time Counter

Rx Time Stamp

Rx Splitter

Tri-Mode

Ethernet

MAC

Tx Client Tx PHY

Rx PHYRx Client

Host I/F

Figure 5-1: Ethernet AVB Endpoint Core Block Diagram for Connection to LogiCORE IP Tri-Mode Ethernet

MAC

40 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Page 41

EDK pcore Format

PLB I/F

Figure 5-2 illustrates the functional blocks of the Ethernet AVB Endpoint core when it is

generated in EDK pcore format. As illustrated, this is intended to be connected to the XPS

LocalLink Tri-Mode Ethernet MAC.

Each of the functional blocks illustrated will be introduced in the following sections of this

chapter. However, observe from the figure that:

• The xps_ll_temac contains its own PLB interface. Consequently, the logic connecting

the “PLB Interface” of the Ethernet AVB Endpoint core to the Host I/F (as seen in

Figure 5-1) is not present in this case.

• The “Legacy Traffic Interface” of the Ethernet AVB Endpoint core is connected