Page 1

Product Not Recommended for New Designs

ML365 Virtex-II Pro

QDR II SRAM (200 MHz)

Memory Board User Guide

UG066 (v1.0) June 29, 2004

R

Page 2

Product Not Recommended for New Designs

R

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved.

CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are

registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator,

CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and

Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroBlaze, MicroVia,

MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, RocketIO, SelectIO, SelectRAM, SelectRAM+,

Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze,

VersaBlock, VersaRing, Virtex-II Pro, Virtex-II EasyPath, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACTFloorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker,

XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey

any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any

time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for

the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or

information shown or described herein “as is.” By providing the design, code, or information as one possible implementation of a feature,

application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are

responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with

respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation

is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devices

and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown

or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to

correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability

for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without

the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owned and copyrighted by Xilinx. Copyright 1994-2004 Xilinx, Inc. All Rights Reserved. Except as stated

herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form

or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent

of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and

publicity, and communications regulations and statutes.

ML365 Virtex-II Pro QDR II SRAM Memory Board User Guide

UG066 (v1.0) June 29, 2004)

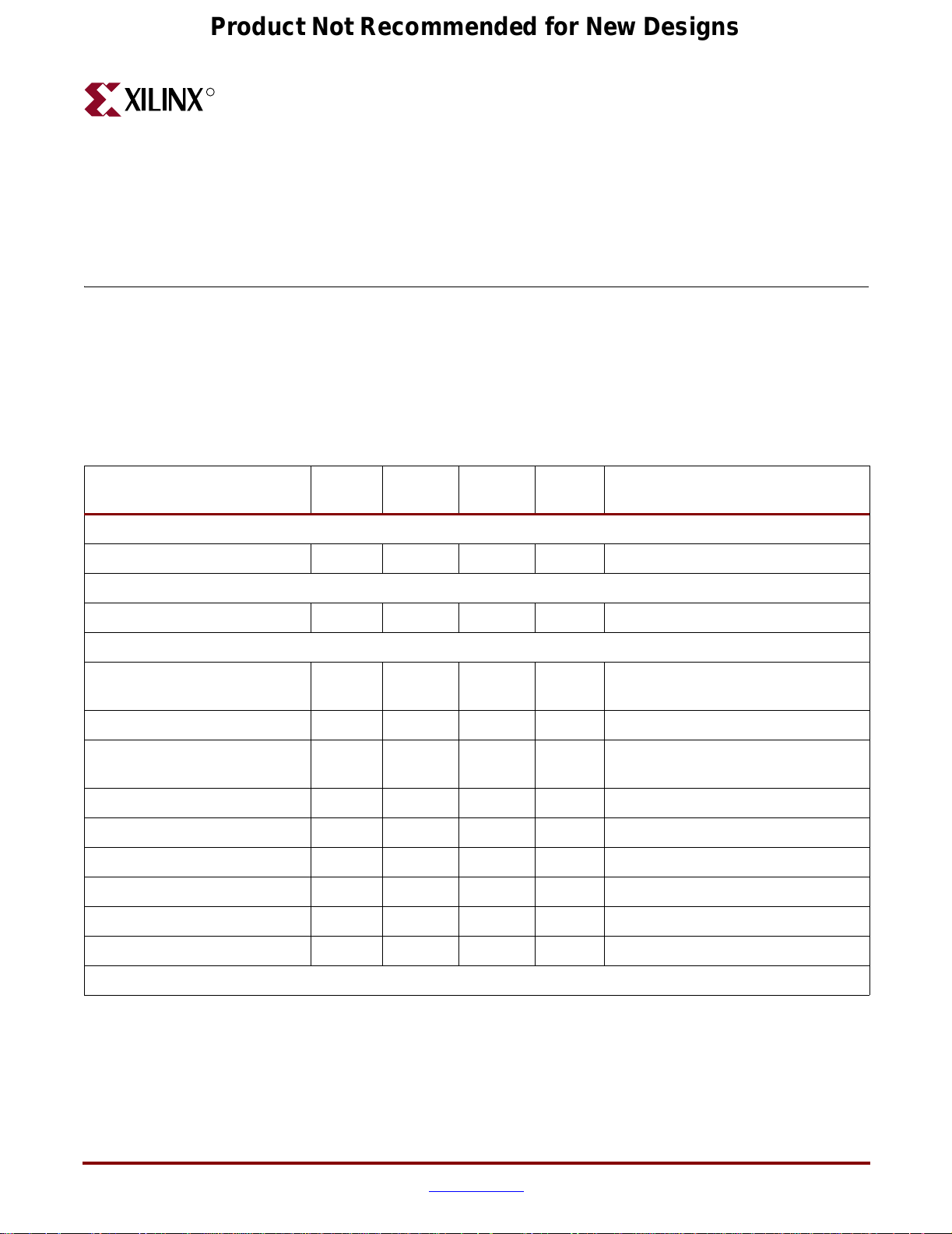

The following table shows the revision history for this document.

Version Revision

06/29/04 1.0 Initial Xilinx Release

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com UG066 (v1.0) June 29, 2004

1-800-255-7778

Page 3

Product Not Recommended for New Designs

R

About This Guide

This document describes the design of the ML365 V irtex-II Pro™ QDR II SRAM (200 MHz)

Memory Board, which connects a V irtex-II Pro FPGA to Quad Data Ra te (Q DR) memories .

Guide Contents

This manual contains the following chapters:

• Chapter 1, “Introduction,” describes the purpose of the ML365 board and provides its

key features.

• Chapter 2, “Architecture,” provides a block diagram of the memory board and

describes the key components.

• Chapter 3, “Electrical Requirements,” lists the electrical specif ications for the memory

board.

• Chapter 4, “Signal Integrity Recommendations and Simulations,” provides

information on termination, transmission lines, and duty cycles. It also gives the

results of several IBIS simulations.

• Chapter 5, “Board Layout Guidelines,” provides information on decoupling

capacitors, ground signals, and PCB layout.

• Appendix 1, “Related Documentation,” lists data sheet and external website

references specific to the ML365 components.

• Appendix 2, “FPGA Pinout,” provides the pinout of the Virtex-II Pro FPGA.

• Appendix 3, “Memory Board Schematics and Characterization Results” shows the

schematics for the board.

Preface

Additional Resources

For additional information, go to http://support.xilinx.com. The following table lists

some of the resources you can access from this website. You can also directly access these

resources using the provided URLs.

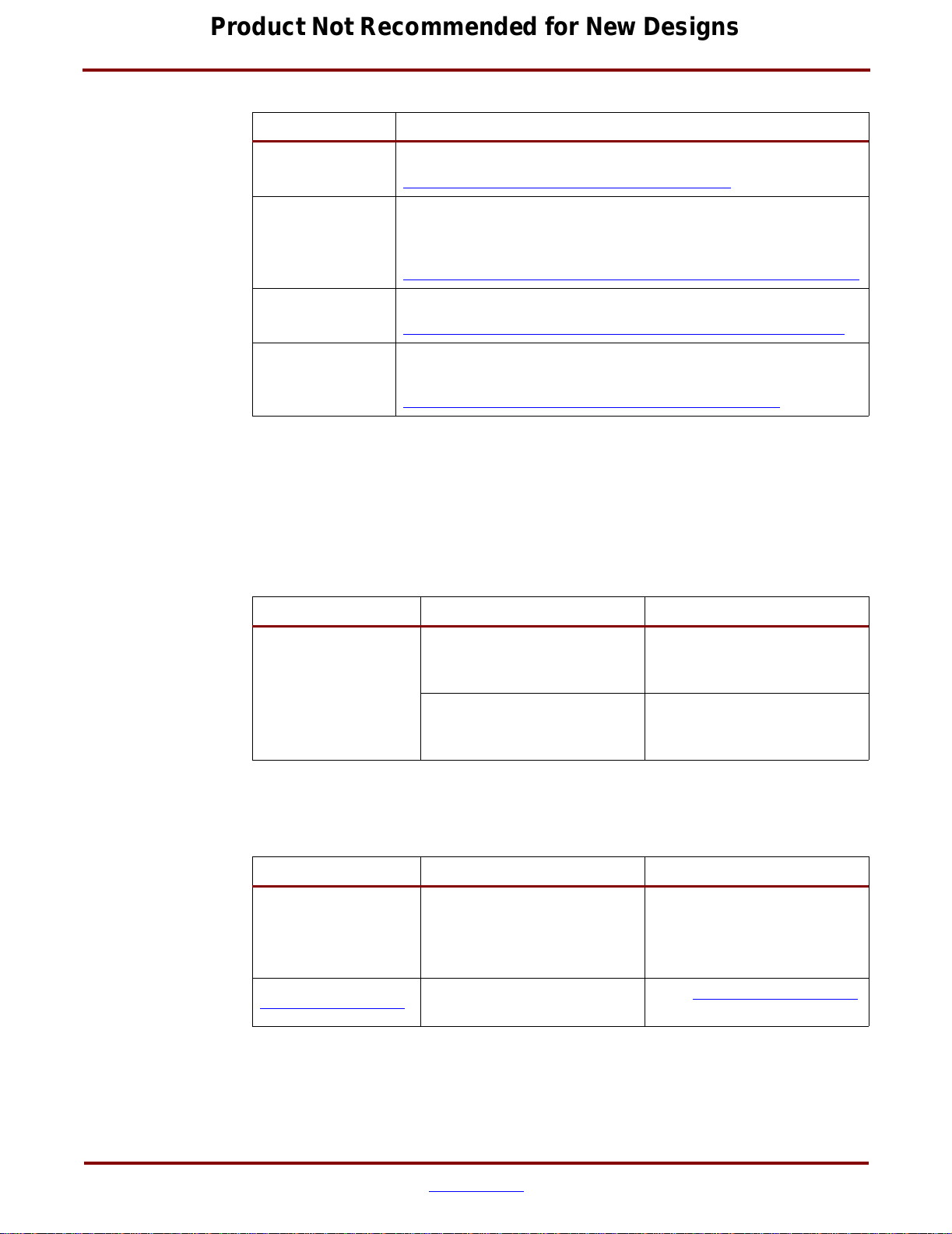

Resource Description/URL

Tutorials Tutorials covering Xilinx design flows, from design entry to

verification and debugging:

http://support.xilinx.com/support/techsup/tutorials/index.htm

Answer Browser Database of Xilinx so luti on records:

http://support.xilinx.com/xlnx/xil_ans_browser.jsp

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 3

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 4

Product Not Recommended for New Designs

Conventions

Resource Description/URL

Application Notes Descriptions of device-specific design techniques and approaches:

http://support.xilinx.com/apps/appsweb.htm

Data Sheets Device-specific information on Xilinx device characteristics,

including readback, boundary scan, configuration, length count,

and debugging:

http://support.xilinx.com/xlnx/xweb/xil_publications_index.jsp

Problem Solvers Interactive tools that allow you to troubleshoot your design issues:

http://support.xilinx.com/support/troubleshoot/psolvers.htm

Tech Tips Latest news, design tips, and patch information for the Xilinx

design environment:

http://www.support.xilinx.com/xlnx/xil_tt_home.jsp

This document uses the following conventions. An example illustrates each convention.

Typographical

The following typographical conventions are used in this document:

Convention Meaning or Use Example

Italic font

Online Document

The following conventions are used in this document:

Convention Meaning or Use Example

Blue text

References to other manuals

Emphasis in text

Cross -reference link to a

location in the current

document

See the Development System

Reference Guide for more

information.

If a wire is drawn so that it

overlaps the pin of a symbol,

the two nets are not connected.

See the section “Additional

Resources” for details.

Refer to “Title Formats” in

Chapter 1 for details.

Blue, underlined text

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 4

UG066 (v1.0) June 29, 2004 1-800-255-7778

Hyperlink to a website (URL)

Go to http://www.xilinx.com

for the latest speed files.

Page 5

Product Not Recommended for New Designs

Table of Contents

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Online Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Schedule of Figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Schedule of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 1: Introduction

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Chapter 2: Architecture

ML365 Board Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Block Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Memories. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

QDR II SRAM (U5, Banks 6 and 7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

QDR II SRAM (U11, Banks 2 and 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

QDR II SRAM (U12, Banks 0 and 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

RS232 (J5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

200 MHz LVPECL Clock (Y1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

250 MHz LVPECL Clock (Y2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

SMA Clock Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

User I/Os. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

GPIO (P19) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

DIP Switch (SW3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Push Buttons. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Rotary Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Power On or Off Slide Switch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Jumper Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Grounded I/Os. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Liquid Crystal Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Write Cycle for the LCD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Display Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Power. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Power Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3 V Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 5

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 6

Product Not Recommended for New Designs

R

2.5 V Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.8 V Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.5 V Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

FPGA Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Selecting the Configuration Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Serial Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Master Serial Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Slave Serial Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

SystemAce Configuration (Default Mode). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

SelectMap Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

JTAG Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Chapter 3: Electrical Requirements

Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

FPGA Internal Power Budget. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Chapter 4: Signal Integrity Recommendations and Simulations

Termination and Transmission Line Summaries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Terminations and Transmission Lines for QDR Components . . . . . . . . . . . . . . . . 34

Data and Clock Signals (D, Q, CQ, CQ

Address and Control Signals (A, R

IBIS Simulations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Notes on the Simulation Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Data Signal Simulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Data Signals from the FPGA to the Memory (HSTL_18_C2 at FPGA) . . . . . . . . . . . . 37

Data Signals from the QDR II SRAM, Component U11 to the FPGA Measured at the FPGA39

Eye Diagram for the Component U11, Bit 4 Signal Measured at the FPGA . . . . . . . . 40

Clock Signal Simulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Typical, Slow, and Fast Cases for Clock Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Address and Control Signal Simulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Typical Case Simulation at All Memory Components. . . . . . . . . . . . . . . . . . . . . . . . . . 44

, and CLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

, W, BW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Chapter 5: Board Layout Guidelines

Decoupling Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Providing Additional Ground Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Board Stackup Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Appendix 1: Related Documentation

Appendix 2: FPGA Pinout

Appendix 3: Memory Board Schematics and Characterization Results

Schematics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Characterization Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Long-Term Runs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Corners Results Matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

6 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 7

Product Not Recommended for New Designs

Schedule of Figures

Chapter 1: Introduction

Figure 1-1: Simplified Block Diagram of Memory Board Interface. . . . . . . . . . . . . . . . . . 11

Chapter 2: Architecture

Figure 2-1: ML365 Board Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 2-2: LCD Write Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 2-3: Display Initialization Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 2-4: LCD Panel Character Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 2-5: SelectMap Connectors P99 and P111 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 2-6: SystemAce and JTAG Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 2-7: JTAG I/O Connector P103. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Chapter 3: Electrical Requirements

Chapter 4: Signal Integrity Recommendations and Simulations

Figure 4-1: Signal Terminations for Transmitted and Received Data. . . . . . . . . . . . . . . . 36

Figure 4-2: Data Signal Bit 4 from the FPGA to the Memory (Typical Case). . . . . . . . . . 37

Figure 4-3: Eye Diagram for Data Bit 4 from the FPGA to the QDR II SRAM, U11. . . . 38

Figure 4-4: Data Signals from the QDR II SRAM U11 at the FPGA (Typical,

Slow/Weak and Fast/Strong Cases) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 4-5: Eye Diagram for Data Bit 4 at the FPGA from Component U11. . . . . . . . . . . 40

Figure 4-6: Clock Signal Terminations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 4-7: Clock K Signal from the FPGA to the QDR II SRAM, Component U11 . . . 42

Figure 4-8: Clock CQ Signal from the FPGA to the QDR II SRAM Component U11 . . 43

Figure 4-9: Address and Control Signal Terminations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 4-10: Address/Control Signals for the QDR II SRAM, Component U11, Bit 4 . . 45

Chapter 5: Board Layout Guidelines

Figure 5-1: Picture of the Top Layer of the ML365 Revision 1.0b Board. . . . . . . . . . . . . . 50

Figure 5-2: Picture of the Bottom Layer of the ML365 Revision 1.0b Board . . . . . . . . . . . 51

Appendix 1: Related Documentation

Appendix 2: FPGA Pinout

Appendix 3: Memory Board Schematics and Characterization Results

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 7

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 8

Product Not Recommended for New Designs

R

8 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 9

Product Not Recommended for New Designs

Schedule of Tables

Chapter 1: Introduction

Chapter 2: Architecture

Table 2-1: GPIO Header Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 2-2: DIP Switch Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2-3: Power-On Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2-4: FPGA Configuration Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2-5: SystemAce Configuration Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2-6: Jumper Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 2-7: LCD Pin Descriptions and PFGA Connections . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 2-8: LCD Write Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 2-9: Instruction Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 2-10: Configuration Modes Supported on the QDR II SRAM Demonstration Board 24

Table 2-11: Jumper Positions for SystemAce Configuration . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 2-12: JTAG Connector Pins (P1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Chapter 3: Electrical Requirements

Table 3-1: ML365 Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 3-2: XC2VP20FF1152 Estimated Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 3-3: XC2VP20FF1152 Temperature Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 3-4: Device Quiescent Power. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 3-5: CLB Logic Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 3-6: Digital Clock Manager Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 3-7: Input/Output Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Chapter 4: Signal Integrity Recommendations and Simulations

Table 4-1: QDR SRAM Terminations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Chapter 5: Board Layout Guidelines

Table 5-1: Decoupling Capacitor Recommendations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 5-2: Suggested Stackup for a 12-layer board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Appendix 1: Related Documentation

Appendix 2: FPGA Pinout

Table 2-1: FPGA Pin Out. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Appendix 3: Memory Board Schematics and Characterization Results

Table 3-1: Corners Results Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 9

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 10

Product Not Recommended for New Designs

R

10 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 11

Product Not Recommended for New Designs

R

Introduction

Overview

The ML365 Virtex-II Pro QDR II SRAM Memory Board provides a communications

platform between a Virtex-II Pro FPGA and high-speed, quad data-rate (QDR) memories

with operating speeds up to 200 MHz. The ML365 has three major functions:

• Test and verify the interoperability of Virtex-II Pro devices with high-speed QDR II

SRAM memories

• Serve as a development platform for Xilinx and its customers to use for building

memory interfaces

• Provide a means by which Xilinx can demonstrate high-speed QDR II SRAM memory

interoperability

Chapter 1

This document describes the functional blocks within the ML365. It also provides various

recommend ations an d requirements for usage of the board, including electrical

requirements, logic analyzer requirements, and signal integrity issues. Simulation results

using IBIS also are included.

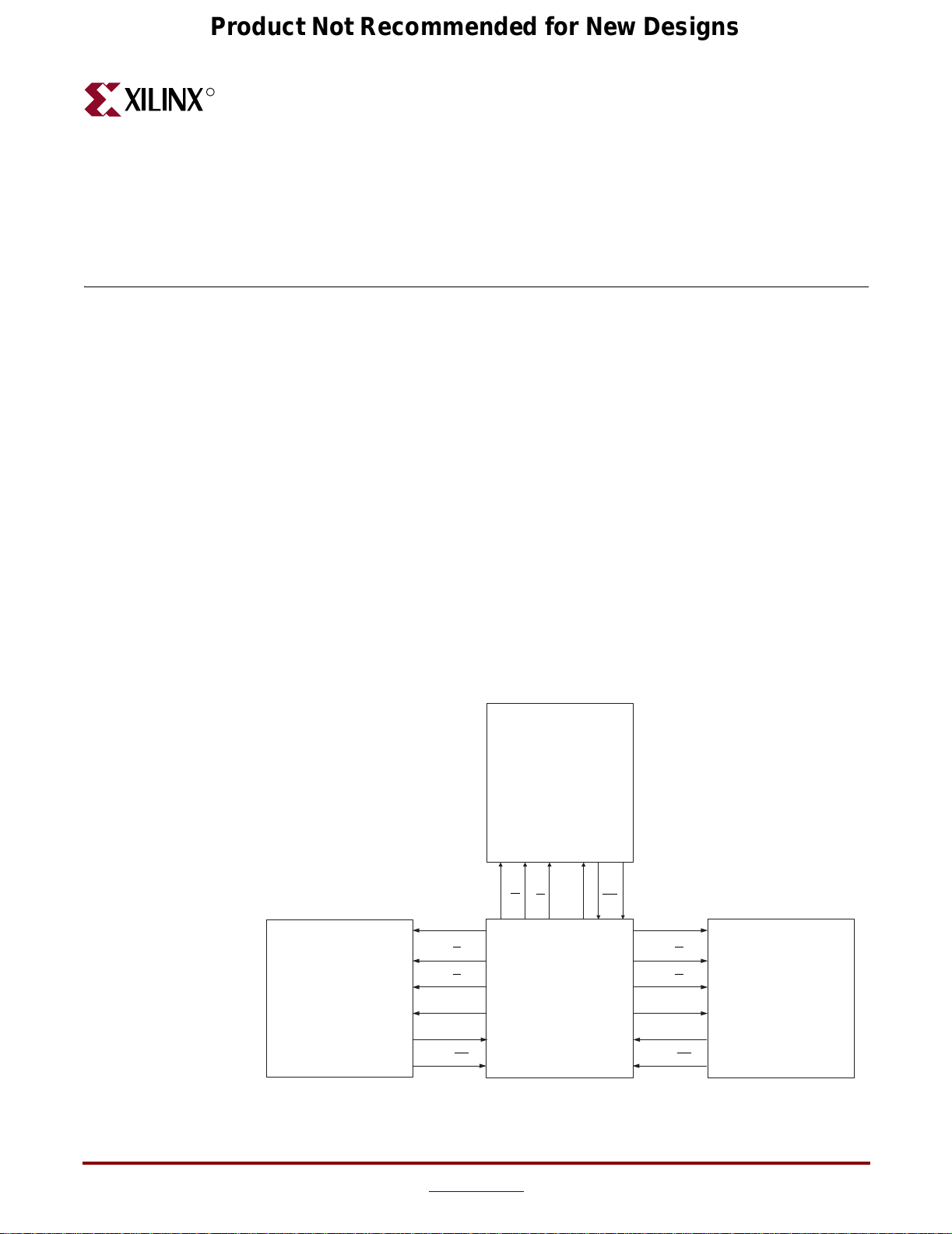

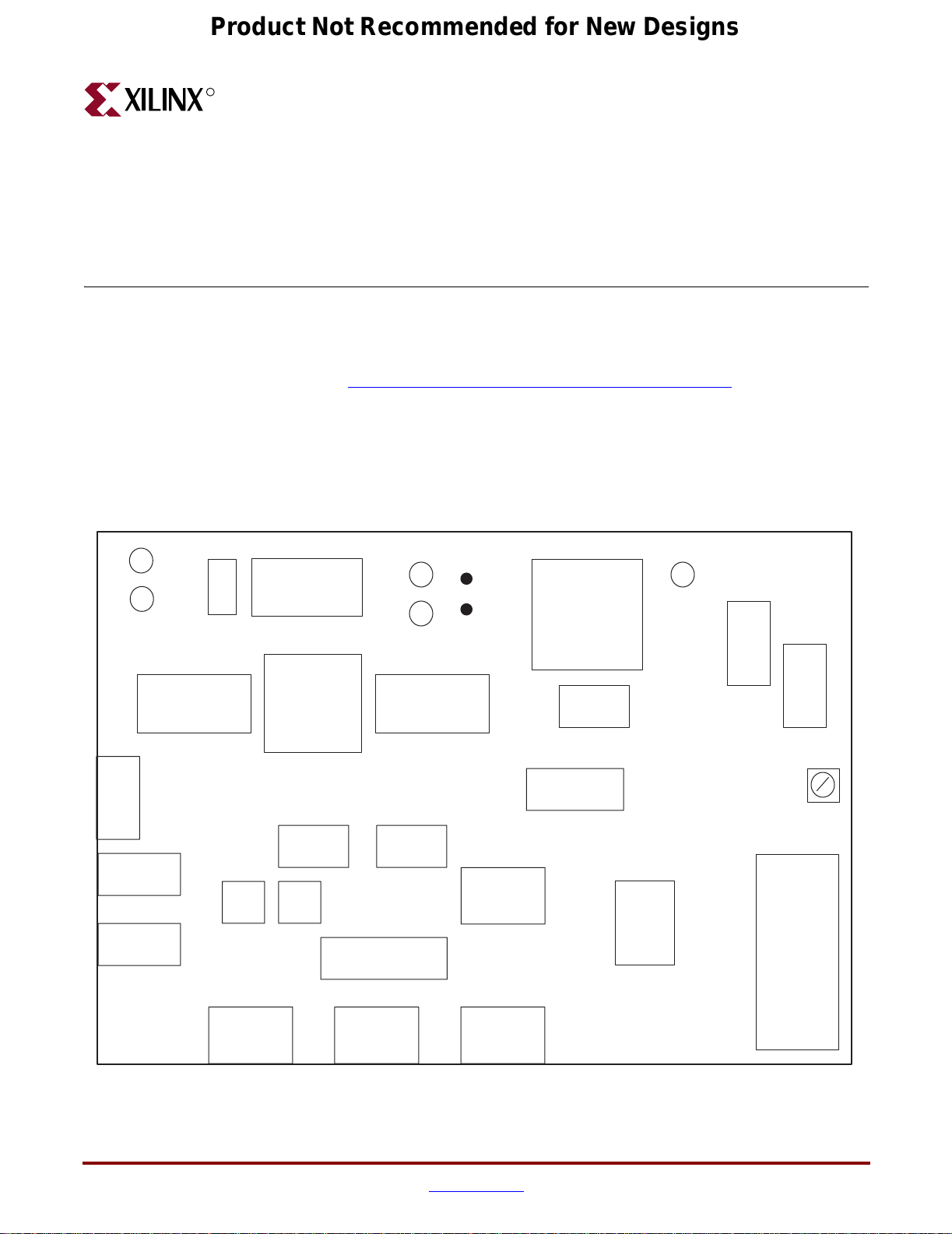

Figure 1-1 shows a simplified block diagram of the ML365 memory interfaces.

QDR II SRAM

1M x 36

FBGA 165

4-Word Burst

C,

QDR II SRAM

1M x 36

FBGA 165

4-Word Burst

(36-bits)

D (36-bits)

C, C

K, K

Addr, Ctrl

Q (36-bits)

CQ, CQ

D

Addr,

K,

C

Ctrl

K

Virtex-II Pro FPGA

XC2VP20FF1152-6

CQ,

CQ

Q

(36-bits)

D (36-bits)

Addr, Ctrl

Q (36-bits)

C, C

K, K

CQ, CQ

QDR II SRAM

1M x 36

FBGA 165

4-Word Burst

ug124_01_062204

Figure 1-1: Simplified Block Diagram of Memory Board Interface

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 11

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 12

Features

Product Not Recommended for New Designs

The ML365 demonstrates a 36-bit interface to a 36 MByte, 200 MHz QDR II SRAM

component. There are thr ee independent 36-bit interfaces on the board; one on the le ft side

of the FPGA, the second on the right side of the FPGA, and the third on top of the FPGA.

The key features of the ML365 are summarized as follows:

• One Virtex-II Pro FPGA (XC2VP20FF1152)

• Three QDR II SRAM Components (Samsung K7R323684M or NEC UPD44165364F5)

♦ 18 MBytes

♦ 36-bit Data interface

• Three separate controllers for each 36-bit memory interface

• Characterized 200 MHz clock operation for interfaces A (interface to the FPGA on the

right side, U5) and B (interface to the FPGA on the left side, U11)

• One additional memory interface on the top banks of the FPGA (interface C, U12)

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 12

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 13

Product Not Recommended for New Designs

R

Architecture

This chapter provides functional descriptio ns of the major blocks wi thin the ML365 board

design. For additional detailed information on the design, refer to the schematics, which

are located at http://www.xilinx.com/bvdocs/userguides/ug06

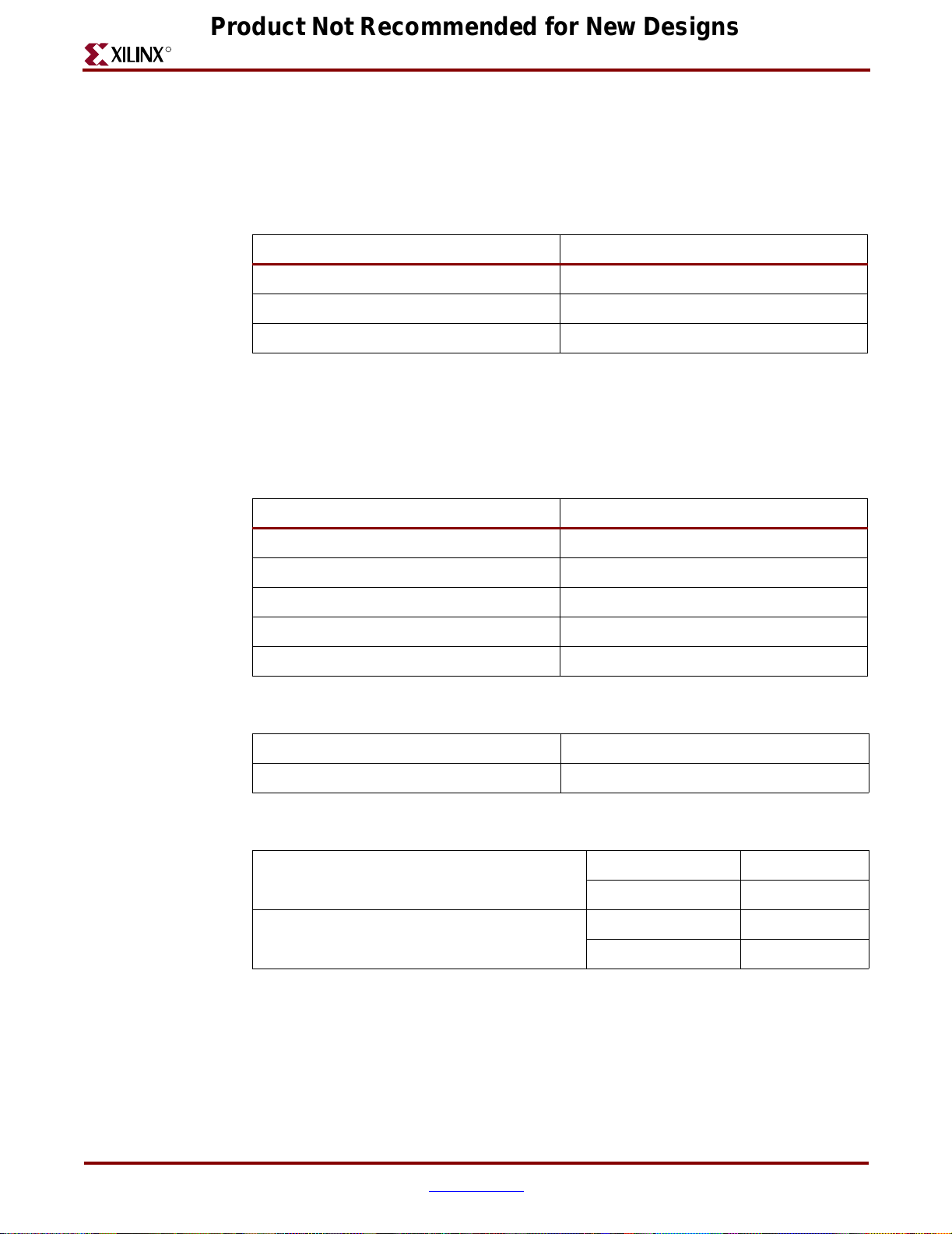

ML365 Board Block Diagram

Figure 2-1 shows a block diagram of the ML365 board. Refer to “Block Descriptions” for

additional information on the major blocks.

Chapter 2

6.zip.

RS-232

Serial

Por t

On / Off

Switch

DC 5V

Input Jack

FPGA

Reset

PROG

QDR II SRAM

Mode

DIP

SW

1M x 36

SMA

QDR II SRAM

1M x 36

XC2VP20

FF1152C

Clock

250 MHz

SMA

USER1

Switch

USER2

Switch

QDR II SRAM

Clock

200 MHz

GPIO Header

1M x 36

USER1

LED

USER2

LED

TPS54810

1.8V, 8A

Regulator

SYSTEM ACE

Controller

TQFP144

JTAG

Jumpers

SelectMap

Header

XCONFIG

Header

SystemAce

Reset

JTAG

Header

JTAG

Parallel

PC-IV

Por t

SystemAce

File Select

Rotary Switch

SEIKO 1X16

LCD Display

L167100J000

PT5502N

2.5V, 3A

Regulator

PT5505N

1.5V, 3A

Regulator

PT5501N

3.3V, 3A

Regulator

ug066_c2_01_060804

Figure 2-1: ML365 Board Block Diagram

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 13

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 14

Product Not Recommended for New Designs

R

Block Descriptions

This section describes the major blocks of the ML365 board.

FPGA

The ML365 uses a Xilinx XC2VP20FF1152C-6 Virtex-II Pro device. This device is packaged

in a 1152-pin BGA package with a -6 speed grade. Refer to Appendix 2, “FPGA Pinout,”for

a complete pinout of the Virtex-II Pro device.

Memories

The ML365 board supports three types of memories in two speed grades.

QDR II SRAM (U5, Banks 6 and 7)

The QDR II SRAM component connected to FPGA I/O banks 6 and 7 is a 165-pin, 200 MHz

Samsung K7R323684M or NEC UPD44165364F5 SRAM in a Ball Grid Array package. This

component has a 36-bit wide data interface.

Chapter 2: Architecture

QDR II SRAM (U11, Banks 2 and 3)

The QDR II SRAM component connected to FPGA I/O banks 2 and 3 is a 165-pin, 200 MHz

Samsung K7R323684M or NEC UPD44165364F5 SRAM. This component has a 36-bit wide

data interface.

QDR II SRAM (U12, Banks 0 and 1)

The QDR II SRAM component connected to FPGA I/O banks 0 and 1 is a 165-pin, 250 MHz

Samsung K7R323684M or NEC UPD44165364F5 SRAM. This component has a 36-bit wide

data interface.

RS232 (J5)

The ML365 board provides an RS232 serial interface using a Maxim MAX3316ECUP

device. The maximum speed of this device is 460 Kb/s. The RS232 interface is accessible

through a male DB9 serial connector.

Clocks

The ML365 board has 200 MHz and 250 MHz LVPECL (2.5 V) clock oscillators on board. It

also has two SMA connectors for external differential clock inputs.

200 MHz LVPECL Clock (Y1)

The LVPECL clock is an Epson EG-2121CA-200 MHz oscillator with a differential output.

The oscillator runs at 200 MHz ± 100 PPM with an operating voltage of 2.5 V ± 5%. It is

terminated at the FPGA with a 50 ohm resistor. FPGA pins AH17 and AJ17 in Bank 4 serve

as the OSC_200M_N and OSC_200M_P inputs, respectively.

250 MHz LVPECL Clock (Y2)

The LVPECL clock is an Epson EG-2121CA-250 MHz clock oscillator with a differential

output. This oscillator runs at 250 MHz ± 100 PPM with an operating voltage of 2.5 V ± 5%.

14 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 15

Product Not Recommended for New Designs

Block Descriptions

SMA Clock Connectors

User I/Os

GPIO (P19)

R

FPGA pins AK17 and AL17 in Bank 4 serve as the OSC_250M_N and OSC_250M_P inputs,

respectively.

Two SMA connectors are provided for the input of an off-board differential clock. The

traces from the SMAs are run as a pair to the FPGA where they are terminated with a

50 ohm resistor. AK18 serves as the EXT CLK1 _P input, and AL18 serves as the

EXTCLK1_N input for the SMA connector pair.

This subsection describes the devices that connect to the User I/Os of the ML365 board.

The ML365 board contains 16 General-Purpose I/Os (GPIOs) that are accessible thr ough a

2 x 16 .100" pin header (P19). The odd-numbered pins on each header are connected to an

FPGA pin, and the even-numbered pins on each header are connected to GND (refer to

Table 2-1). The GPIO header pins are accessed through I/Os in Bank 0. The header pins

each have a pull-down resistor of 51 ohms.

Table 2-1: GPIO Header Pins

GPIO Header Pin # FPGA I/O Pin

G1 AL13 G2

G3 AL12 G4

G5 AD16 G6

G7 AE16 G8

G9 AM14 G10

G11 AM13 G12

G13 AF16 G14

G15 AG16 G16

G17 AH15 G18

G19AJ15G20

G21AD17G22

G23 AE17 G24

G25 AH16 G26

GPIO Header Pin #

Ground Connections

G27AJ16G28

G29AK16G30

G31 AF17 G32

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 15

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 16

Product Not Recommended for New Designs

R

DIP Switch (SW3)

One 3-position DIP switch (SW3) is connected to the FPGA I/O as shown in Table 2-2.

These switches are used to set the FPGA configuration mode pins M0, M1, and M2.

Table 2-2: DIP Switch Connections

DIP Switch Input FPGA I/O Pin #

DIP1 AF26 (M0)

DIP2 AE26 (M1)

DIP3 AE25 (M2)

LEDs

Eleven surface-mounted blue LEDs are installed as status indicators. Refer to Table 2-3,

Table 2-4, and Table 2-5.

Chapter 2: Architecture

Table 2-3: Power-On Status

Status Indication FPGA I/O Pin #

5.0V on D9

2.5V on D7

3.3V on D5

1.8V on D8

1.5V on D6

Table 2-4: FPGA Configuration Status

Configuration INIT D3

Configuration DONE D4

Table 2-5: SystemAce Configuration Status

System Ace LEDs

User LEDs

Error D2

Status D1

USER1 AF15

USER2 AE15

16 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 17

Product Not Recommended for New Designs

Block Descriptions

Push Buttons

Rotary Switch

Power On or Off Slide Switch

R

The ML365 board contains five momentary push buttons. Their functions are as follows:

• Program the FPGA

• Reset FPGA

• Reset SystemAce

• USER1

• USER2

The ML365 board contains one eight-position rotary switch used to select the SystemAce

file address. One of eight configuration fi le images is loaded f r om the Compact Flash card

present in the socket.

The power on or off slide switch is a DPST s lide switch used to apply 5V input power to the

board.

Jumper Settings

Table 2-6 list s the jumper settings for the complete PCB.

Table 2-6: Jumper Settings

Pin # Purpose

P6 QDR II U5 DLL enable DLL enable DLL bypass

P7 QDR II U5 ZQ select Minimum Z mode 0.2RQ = 50 ohm

P20 QDR II U11 DLL enable DLL enable DLL bypass

P21 QDR II U11 ZQ select Minimum Z mode 0.2RQ = 50 ohm

P22 QDR II U12 DLL enable DLL enable DLL bypass

P23 QDR II U 12 ZQ select Minimum Z mode 0.2RQ = 50 ohm

P2 System Ace On = Disable after reset

Grounded I/Os

Unused I/Os are connected to GND in all FPGA banks. This was done to improve power

dissipation and SSO ground bounce. Users must not drive any unused I/Os that are

connected to GND.

Jumper Position

1 - 2 2 - 3

Off = Enable after reset

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 17

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 18

Product Not Recommended for New Designs

R

Liquid Crystal Display

The Seiko L167100J000 Liquid Crystal Display (LCD) is a 5V, 1-line X16 character display

without a backlight. The LCD is connected to the PCB using two rows of 1 x 16 pin SIP

headers placed 31 mm. apart. The LCD interfaces uses bank 5 of the FPGA. The LCD pin

descriptions and FPGA pinouts are listed in Table 2-7.

Table 2-7: LCD Pin Descriptions and PFGA Connections

Symbol Function FPGA Pin #

Chapter 2: Architecture

V

SS

V

DD

V

O

Power supply (GND) N/A

Power supply (+5V) N/A

Contrast adjustment N/A

RS Register selection AF22

R/W Read / Write selection AG22

E Read / Write enable AE22

DB (0-7) Data bus AF25 (DB0), AL28, AM28, AE24,

AF24, AG25, AH25, AK27 (DB7)

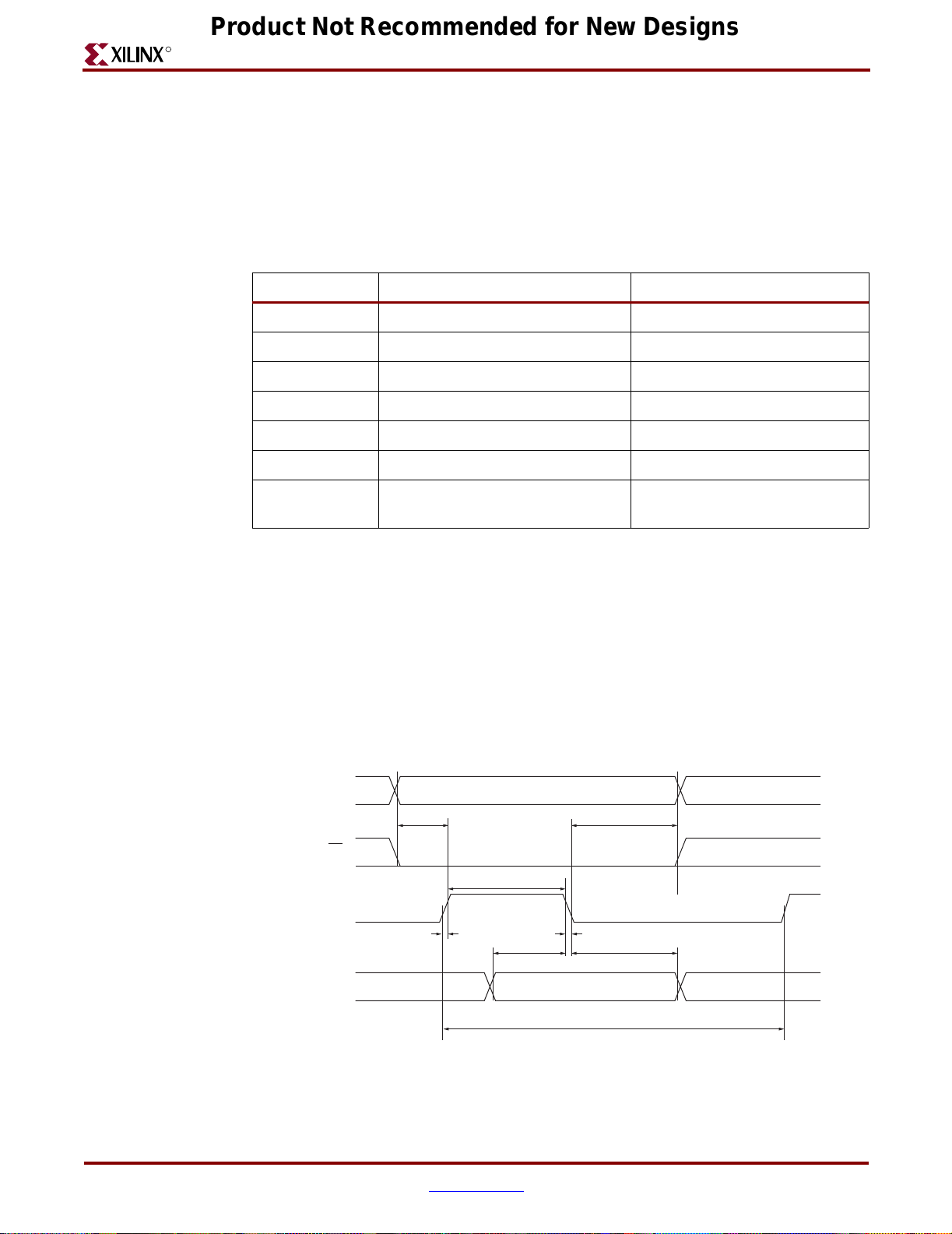

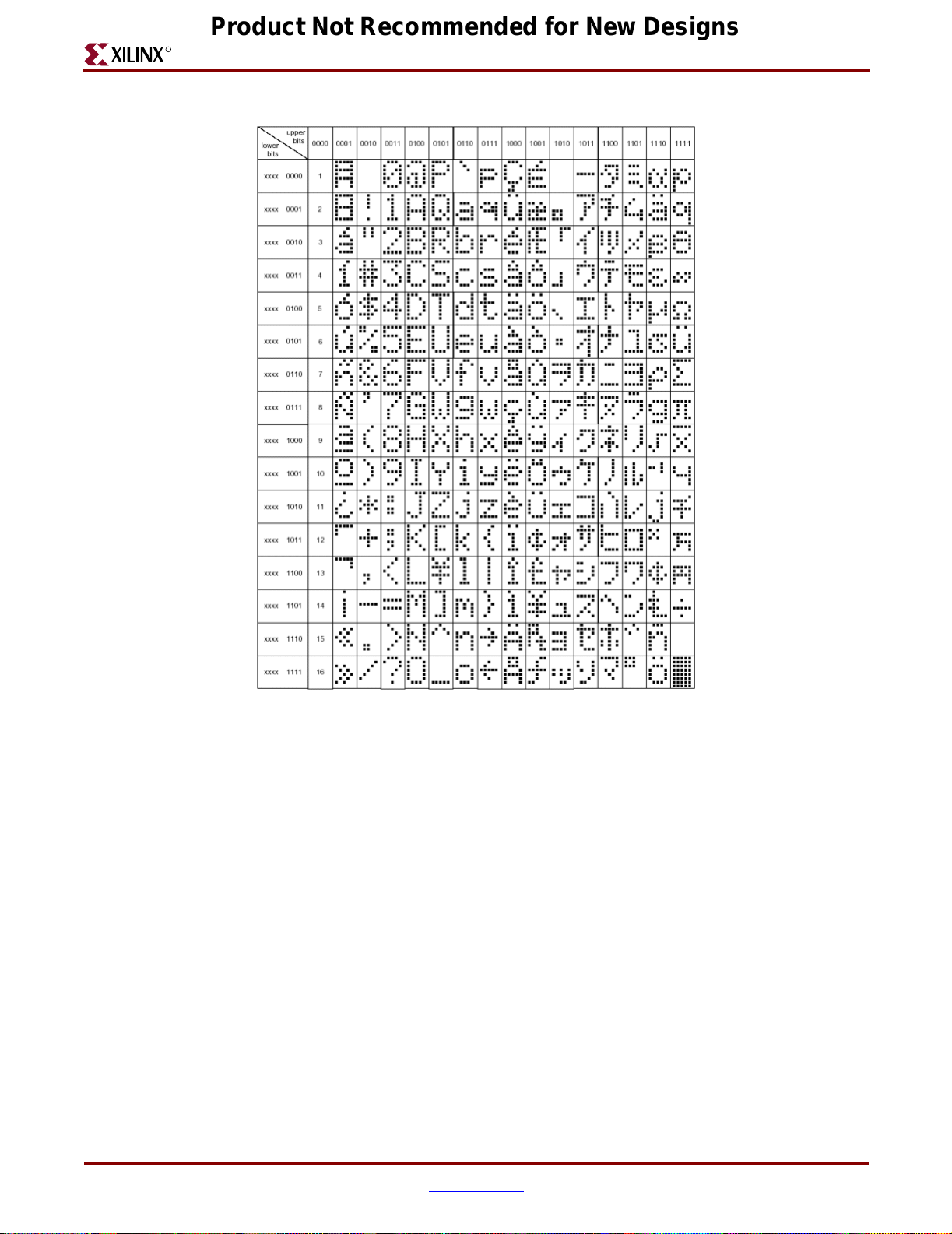

The information needed to control the LCD panel is provided in the following figures and

tables. Figure 2-2 shows the LCD write timing diagram, and Table 2-8 lists the LCD write

timing parameters.

Table 2-9 shows the instruction codes for the LCD. Figure 2-3 shows the Display

Initialization Sequence, and Figure 2-7, the LCD panel character set. For complete

information, refer to the manufacturer’s data sheet.

Write Cycle for the LCD

Reading from the LCD panel memory is not implemented on this demonstration board.

RS

R / W

DB[7:0]

t

AS

PW

EH

E

t

ER

t

DSW

t

t

CYC

EF

t

AH

t

H

E

ug066_c2_02_060704

Figure 2-2: LCD Write Timing Diagram

18 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 19

Product Not Recommended for New Designs

Block Descriptions

R

Table 2-8: LCD Write Timing Parameters

Enable pause width / High Level PW

Address setup time / RS, R/W - E t

Display Commands

Table 2-9 provides display commands or instruction code for the LCD. Refer to the Table

Notes for additional information.

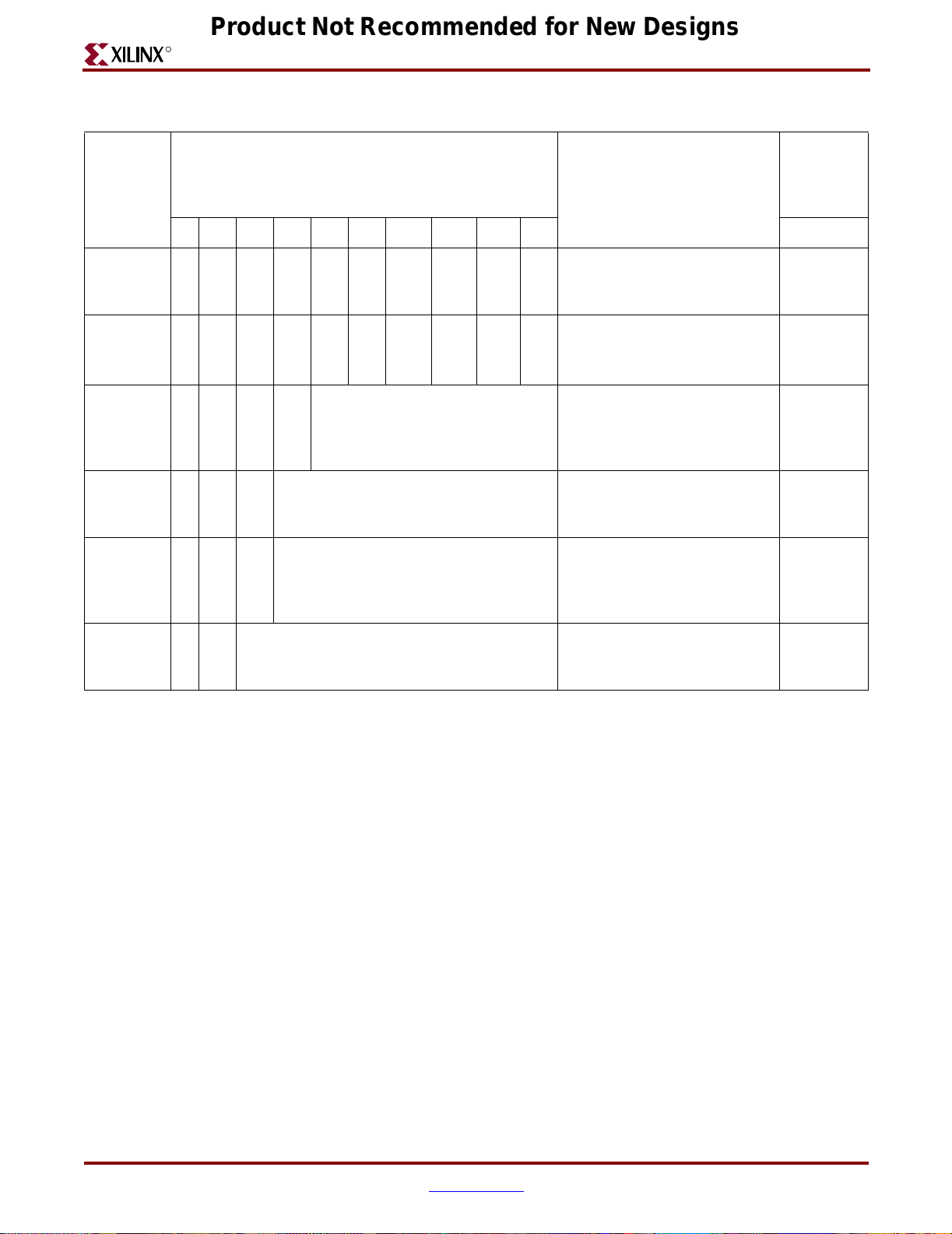

Table 2-9: Instruction Code

Instruction

Item Symbol

Enable cycle time t

Enable rise and fall time t

Address hold time t

Data setup time t

Data hold time t

Code

Standard

Unit

Minimum Maximum

E500 ns

CYC

230 ns

20 ns

40 ns

10 ns

80 ns

10 ns

ER

DSW

, t

AS

AH

H

EH

EF

Maximum

Execution

Description

(Notes 2 and 3)

Time

(Note 1)

Clear

Display

Return

Home

Entry

Mode

Set

Display

On/Off

Control

RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

000000 0 0 0 1Clears entire display and sets

Data Display RAM (DDR)

address 0 in the address

counter.

000000 0 0 1 *Sets DDR address0 in the

address counter. Also returns

display being shifted to

original position. DDR

contents remain unchanged.

000000 0 1I/DSSets cursor move direction

and specifies shift of display.

These operations are

performed during data write

and read.

000000 1 D CBSets ON/OFF of entire

display (D), cursor ON/OFF

(C), and blink of cursor

position character (B).

µs -

82

1.64 ms

µs -

40

1.6 ms

µs –

40

1.64 ms

µs

40

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 19

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 20

Product Not Recommended for New Designs

R

Table 2-9: Instruction Code

Instruction

RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Code

Chapter 2: Architecture

Description

(Notes 2 and 3)

Maximum

Execution

Time

(Note 1)

Cursor or

Display

Shift

Function

Set

Set

CG RAM

Address

Set

DD RAM

Address

Read

Busy Flag

and

Address

Write Data

to CG

or DDR

000001S/CR/L* *Moves cursor and shifts

40 µs

display without changing

DDR contents.

00001DLN F * *Sets interface data length (DL),

40

number of display lines (L),

and character fonts (F).

0001 A

CC

Sets Character Generator

40 µs

RAM (CGR) address. CGR

data is sent and received after

this setting.

00 1 A

DD

Sets DDR address. CGR data

40 µs

is sent and received after this

setting.

01BF A

C

Reads Busy flag (BF)

1 µs

indicating internal operation

is being performed and reads

address counter contents.

1 0 Write Data Writes data into DDR or CGR. 40

µs

µs

*Not applicable

Notes:

1.Maximum execution time is when f

changes.

2.DD RAM: Display data RAM

CG RAM: Character generator RAM

A

: CG RAM address

CG

A

: DDR address - corresponds to cursor address

DD

A

: Address counter used for both DDR and CG RAM address

C

I/D = 1: Increment or I/D = 0: Decrement

S = 1: Display shi ft or S = 0: No Display shift

D=1: Display ON or D=0: Display OFF

C = 1: Cursor ON or C = 0: Cursor OFF

B = 1: Blink ON or B = 0: Blink OFF

S/C = 1: Display shift or S/C = 0: Cursor move

R/L = 1: Shift to the right or R/L = 0: Shift to the left

DL = 1: 8 bits or DL = 0: 4 bits

N=1: 2lines

F=0: 5x 7 dots

BF = 1: In ternally operatin g or BF = 0: Can accept instruction

cp

or f

is 250 kHz. Execution time changes when frequency

osc

20 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 21

Product Not Recommended for New Designs

Block Descriptions

R

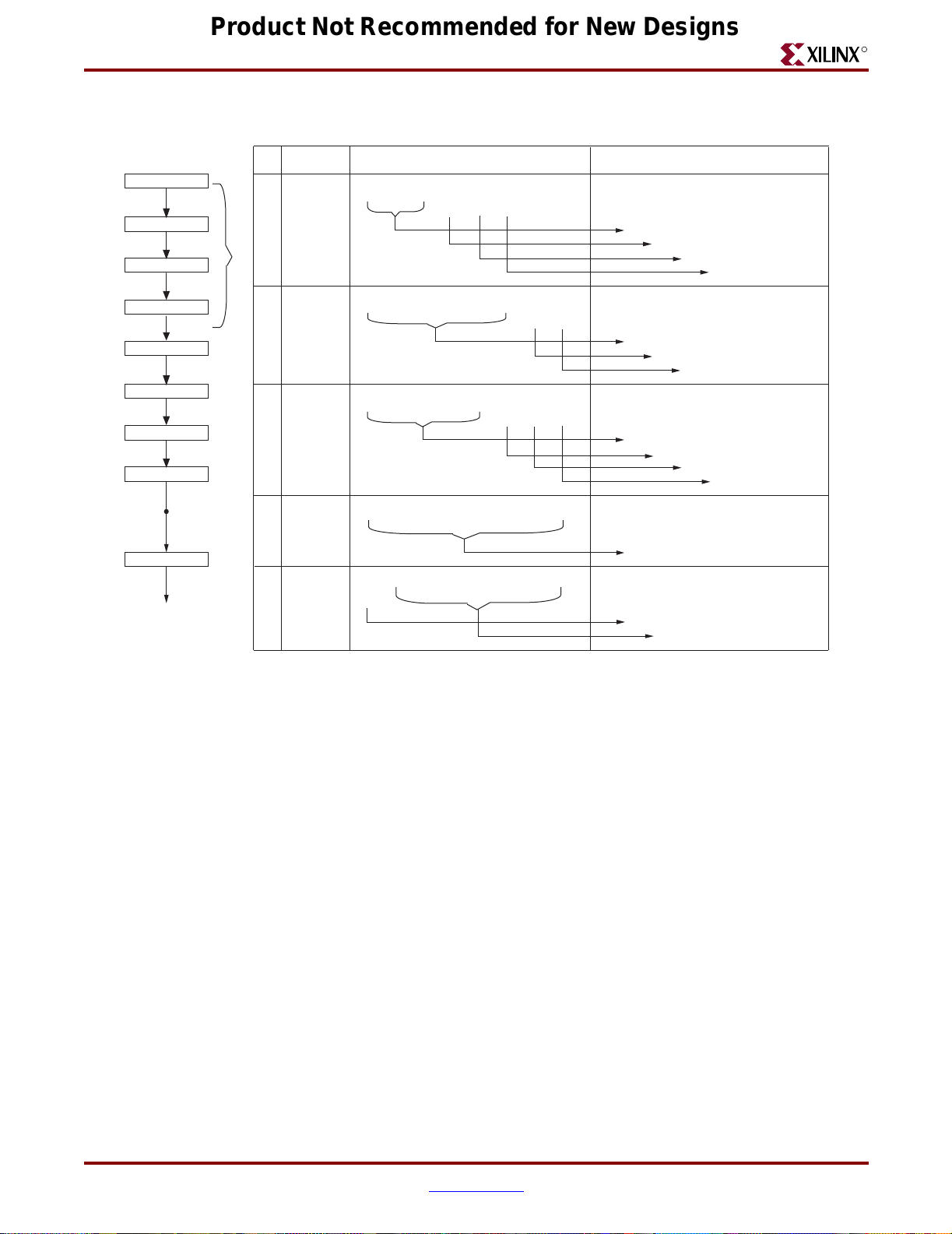

Initialization

Flow Chart

Power On

≥ 15 mS

38 (Hex)

≥ 4.1 mS

38 (Hex)

≥ 100 uS

38 (Hex)

≥ 40 uS

38 (Hex)

≥ 40 uS

06 (Hex)

≥ 40 uS

0E (Hex)

≥ 40 uS

01 (Hex)

≥ 1.64 uS

End of

Initialization

80 (Hex)

≥ 40 uS

Hex Code D

R

E

S

E

T

S

E

Q

U

E

N

C

E

(1)

(2)

38 (Hex)

06 (Hex)

(1)

(2)

(3)

0E (Hex)

(3)

(4)

(4)

01 (Hex)

(5)

80 (Hex)

(5)

7D6D5D4D3D2D1D0

0

01

0000

0

00

1

00000

0

00

1

1000

00

1

0

0000

11

1

1

Function Set

8-bit Data Length

2 Line

5 x 7 Dot Format

Entry Mode Set

Increment One

No Shift

000

Display On/Off Control

Display On

Cursor On

Blink Off

1

Display Clear

Figure 2-3: Display Initialization Sequence

DD RAM Address Set

1st Digit

ug066_c2_03_060804

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 21

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 22

Product Not Recommended for New Designs

R

Chapter 2: Architecture

Figure 2-4: LCD Panel Character Set

ug066_c2_04_060704

22 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 23

Power

Power

Product Not Recommended for New Designs

Power Distribution

The ML365 board uses a 5V +/- 10% input voltage source to generate all the on-board

voltages (1.5V, 1.8V, 2.5V, and 3.3V).

Input Voltage

The input voltage is specified at 5 V @ 6.5 A. The recommended power supply is a CUI Inc.

DTS050650UTC-PSP-SZ. The jack used is a 2 mm. barrel jack. The slide switch turns the

power on or off. Four regulators on the board provide different voltages required by

various components on the board.

3.3 V Generation

The Texas Instruments PT5501N voltage regulator generat es the 3.3 V @ 3 A power. This

power regulator is packaged in a 5-pin, thermally-efficient copper case that is solderable,

and provides the auxiliary supply for some of the FPGA I/Os (V

CCO

).

R

2.5 V Generation

The Texas Instruments PT5502N voltage regulator generat es the 2.5 V @ 3 A power. This

power regulator is packaged in a 5-pin, thermally-ef ficient copper case that is solderable. It

supplies the clock oscillators, System Ace device, LCD Display unit, and for some of the

FPGA I/Os (V

CCAUX

).

1.8 V Generation

The Texas Instruments TSP54810 voltage regulator generates the 1.8 V @ 8 A power. This

power regulator has a thermally-enhanced 28-pin TSSOP package, and supplies the

memory devices.

1.5 V Generation

The Texas Instruments PT5505N voltage regulator generat es the 1.5 V @ 3 A power. This

power regulator is packaged in a 5-pin, thermally-efficient copper case that is solderable,

and provides the core voltage to the FPGA (V

CCINT

).

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 23

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 24

Product Not Recommended for New Designs

R

FPGA Configuration

The demonstration board FPGA programming options are very flexible (refer to the

following five configuration modes). For a detailed explanation of the basic Virtex-II

configurations, refer to the Virtex-II Platform FPGA User Guide. The five Virtex-II

configuration modes are:

• Master Serial mode (not used on QDR II Demo Board)

• Slave Serial / SystemAce mode (QDR II Demo Board default)

• Master SelectMap mode

• Slave SelectMap mode

• JT AG mode

Selecting the Configuration Mode

The FPGA programming modes are set with the mode lines (M0, M1, M2) by means of the

3-pole DIP switch (SW5). Table 2-10 shows the programming modes.

Chapter 2: Architecture

Table 2-10: Configuration Modes Supported on the QDR II SRAM Demonstration Board

Mode M2 M1 M0 CCLK Data Width Data DOUT

Master Serial

Slave Serial 1 1 1 In 1 Yes

SystemAce

Master SelectMap 011 Out 8 No

Slave SelectMap 110 In 8 No

JTAG 101 N/A 1 No

(1)

(2)

1. Not used on QDR II Demonstration Board.

2. SystemAce is a Slave Serial configuration mode, and is the default for the QDR II Demonstration Board.

An LED on the Done pin adds a visual aid to detect a good FPGA configuration. If the LED

is “on”, the FPGA configuration is complete.

000 Out 1 Yes

111 N/A N/A N/A

Serial Configuration

The Virtex-II is programmable in serial mode in one of two ways:

Master Serial Mode

This mode is not used in the QDR II Demonstration Board.

Slave Serial Mode

In Slave Serial Mode, the FPGA CCLK pin is driven by an external source. The FPGA is

configured by loading one bit per CCLK cycle in the DIN pin.

24 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 25

Product Not Recommended for New Designs

FPGA Configuration

SystemAce Configuration (Default Mode)

R

SystemAce is a Slave Serial configuration mode, and is the default mode for the QDR II

Demonstration Board.

If the SystemAce Controller (U2) detects a Compact Flash card present in sock et P2, it

attempts to load a configuration file from the Compact Flash card into the FPGA.

Table 2-11 shows the allowable correct jumper positions.

Table 2-11: Jumper Positions for SystemAce Configuration

Pins Jumpered Function

P1.4 to P113 TCK from SystemAce connected to TCK input of the FPGA

P1.7 to P114 TMS from SystemAce connected to TMS input of the FPGA

P1.5 to P1.6 SystemAce TDO connected to the TDI input of the FPGA

1. Recommended SW5 switch setting for the SystemAce mode is 111; refer to Table 2-10.

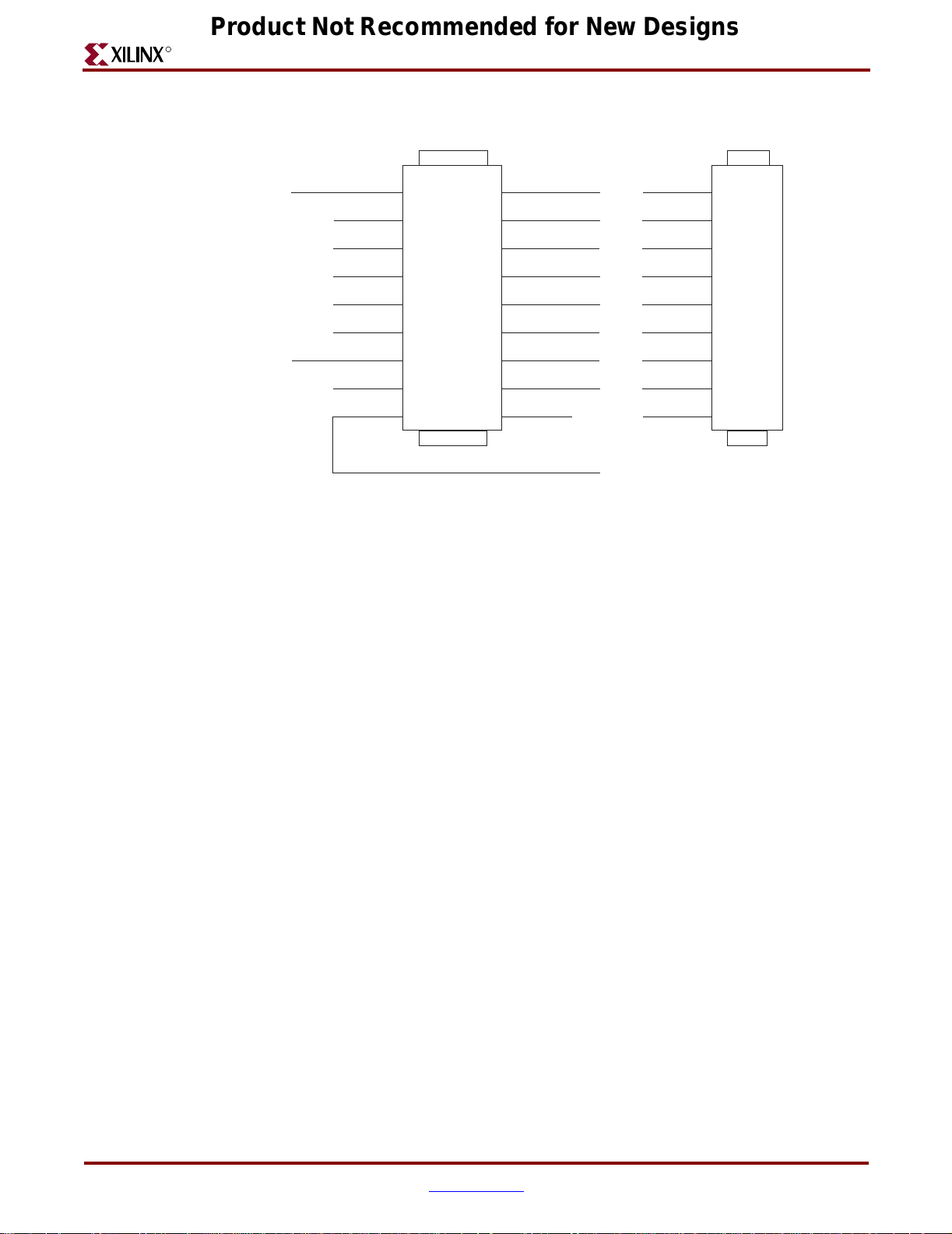

SelectMap Configuration

The Virtex-II FPGA is programmable us ing SelectMap, a parallel configuration mode. In

this mode, two possibilities of programming exist:

• Master Mode: FPGA delivers the CCLK download clock

• Slave Mode: FPGA must receive the CCLK clock from the external device

The demonstration board can be programmed in both modes using the SelectMap

connectors; P99 and P111. The FPGA on the demonstration board can be programmed in

slave mode using a MultiLINX cable, or in Master mode when an external device is

plugged into these connectors.

The SelectMap connector P99 carries FPGA bits [7:0]. When SelectMap is not used, the

SelectMap connector pins can also be used as normal I/O.

Figure 2-5 shows the layout of the SelectMap connectors P99 and P111.

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 25

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 26

Product Not Recommended for New Designs

R

Chapter 2: Architecture

FPGA CS#

FPGA RFWR#

P99

1

3

5

7

9

11 12

13 14

15

17

SelectMAP Header

2

4

6

8

10

16

18

FPGA BUSY

FPGA D0

FPGA D1

FPGA D2

FPGA D3

FPGA D4

FPGA D5

FPGA D6

FPGA D7

1

2

3

4

5

6

7

8

9

Header 9

Figure 2-5: SelectMap Connectors P99 and P111

P111

5V

GND

CCLK

DONE

DIN

PROG

INIT

ug066_c2_05_060804

26 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 27

Product Not Recommended for New Designs

FPGA Configuration

JTAG Configuration

The Virtex-II FPGA is programmable in JTAG mode. The JTAG chain contains two onboard devices (FPGA and SystemAce).

The JT AG input connector is P103, wir ed to the TSTCFG pins of the Sys temAce Contr oller

U2. The JT AG input connector is the start of the JT AG chain. The configuration output port

of the SystemAce Controller is wired to the FPGA via P1, P113, and P114 pins as shown in

Table 2-11. The FPGA can be isolated from the JTAG chain by removing the jumper blocks

from the P1 pins as specified in Table 2-11. Figure 2-6 shows how to build the JTAG chain,

and Table 2-12 shows the connections for the JTAG connector P1.

+5 V +2.5 V

P111

1

2

P26

PROG_B

CCLK

DIN

PROG

INIT

3

4

5

6

7

8

9

SYSACE_TDO

TCK

TMS

FPGA_TDO

+3.3 V

R

+3.3 V

Pushbutton

SW6

1

DIP Switch

SW5

SYSACE_CFGPROG#

SYSACE_CFGINIT#

10K

Resistors (4)

AH8

CCLK

D30

PROG_B

AL5

IO_L01P_4/INIT_B

AJ7

DONE

AH27

M0

AJ28

M1

AK29

M2

F29

HSWAP_EN

F7

TCK

U1I

XC2V3000

Figure 2-6: SystemAce and JTAG Connectors

Table 2-12: JTAG Connector Pins (P1)

Pin

Number

Function

1 3.3 Volts

2GND

3N/C

TDI

TDO

TMS

PWRDWN_B

DXN

DXP

VBATT

RSVD

D5

F6

AK6

F28

G27

C4

G8

FPGA_TDIC31

FPGA_TDO

TMS

TDO

TCK

ug066_c2_06_062804

P1

7

6

5

4

3

2

1

4TCK

5TDO

6FPGA_TDI

7TMS

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 27

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 28

Product Not Recommended for New Designs

R

Figure 2-7 shows the JTAG connector P103.

Chapter 2: Architecture

NC

NC

NC

1

2

3

4

5

P103

6

7

8

9

3.3V

GND

TCK

TDO

TDI

TMS

ug124_07_0603_04

Figure 2-7: JTAG I/O Connector P103

28 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 29

Product Not Recommended for New Designs

R

Electrical Requirements

Power Consumption

Table 3-1 lists the operating voltages, maximum currents, and power consumption used by

the ML365 board devices. Refer to Appendix 1, “Related Documentation,” for more

information on the source material.

Table 3-1: ML365 Power Consumption

Chapter 3

1

Voltag e

(V)

1.8 7236 1 3 Virtex-II Pro User Guide

Device Quantity

Total Available Power

Power Supply 1 5 6500 32.5

FPGA Power (Based on Design)

FPGA (XC2VP20-6 FF1152) 1 6.87 Power Estimator Tool

Board Power

Static Power-on Termination

Resistors (Split 100 ohms)

QDR SRAM (108-bit interface) 3 1.8 800 4.32 Samsung QDR SRAM Data Sheet

200 MHz LVPECL Clock

Oscillator

16-pin GPIO Header 2 2.6 160 .42 Average 10 mA * 16 pins

LEDs 11 — — 0.5 LED Circuits

DIP Switch 1 — — .06 Eight 3.3 kohm pullups

RS232 Serial Port 1 3.3 40 0.13 Maxim MAX3316ECUP Data Sheet

LCD — 2.5/3.3 100 0.33 LCD Datasheet

402

2 4 80 0.64 EPSON EG2121CA Data Sheet

Current

(mA)

Power

(W)

Source

System Ace Compact Flash — 2.5/3.3 150 .049 SystemACE Datasheet

Worst Case Power Consumption: 23.0

1. The resistor count is distributed as follows per devices, and multiplied by the number of devices (3):

- data bus D: 36 (x2 (split termination))

- clocks: CQ, C, K: 6 (x2 (split termination) )

- address bus A: 18 (x2 (split termination))

- R_n_int: 1 (x2 (split termination))

- Control signals: 6 (x2 (split termination))

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 29

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 30

Product Not Recommended for New Designs

FPGA Internal Power Budget

The following tables show the power consumption values inside the FPGA based on the

complete QDR design. These results are derived using the Xilinx Power Estimator tool.

Block Select RAM, Block Multiplier, Processor, and MGT Power tables are not included in

this section as they are not used in this application.

• Table 3-2, “XC2VP20FF1152 Estimated Power Consumption,” page 30

• Table 3-3, “XC2VP20FF1152 Temperature Specifications,” page 30

• Table 3-4, “Device Quiescent Power,” page 30

• Table 3-5, “CLB Logic Power,” page 31

• Table 3-6, “D ig ital Clock Manager Power,” page 31

• Table 3-7, “Input/Output Power,” page 31

Table 3-2: XC2VP20FF1152 Estimated Power Consumption

Parameter Value Units

Total Estimated Design Power 6500 mW

Estimated Design VCC

Estimated Design VCC

Estimated Design VCCO 3.3 V Power 100 mW

Estimated Design VCCO 2.5 V Power 173 mW

Estimated Design VCCO 1.8V Power 7859 mW

Estimated Design VCCO 1.5 V Power 0 mW

Estimated Design VCCO 1.2 V Power 0 mW

Table 3-3: XC2VP20FF1152 Temperature Specifications

Parameter Value Units

Ambient Temperature 25 °C

Air Flow 0 LFM

Junction Temperature 107 °C

Table 3-4: Device Quiescent Power

VCC

Subtotal (mW) VCC

INT

1.5 V Power 3500 mW

INT

2.5 V Power 417 mW

AUX

Subtotal (mW)

AUX

450 417

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 30

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 31

Product Not Recommended for New Designs

Table 3-5: CLB Logic Power

Name

Frequency

(MHz)

Tot al

Number

of CLB

Slices

Tot al

Number of

Flip/Flop or

Latches

Total Number

of Shift

Register

LUTs

Total

Number of

Select RAM

LUTs

Average

Toggle

Rate

%

Amount of

Routing

Used

VCC

Subtotal

(mW)

User Module 1 200 1299 1302 0 544 40% High 1220

User Module 2 0 0 0 0 0 0% Low 0

Total 1220

Table 3-6: Digital Clock Manager Power

Name

Clock Input Frequency

(MHz)

DCM Frequency Mode VCC

Subtotal (mW)

INT

User DCM 1 200 Low 6

User DCM 2 200 Low 6

Total 12

Table 3-7: Input/Output Power

Tot al

Name

CLK200 200 LVDS_25 1 0 100% 100% 15 DDR 2 8

CLK200_N 200 LVDS_25 1 0 100% 100% 35 DDR 2 8

Frequency

(MHz)

I/O Standard

Type

Number

of

Inputs

Number

Outputs

Tot al

of

Average

Tog gle

IOB

Rate

%

Average

Output

Enable

Rate

%

Average

Output

Load

(pF)

IOB

Registers

VCC

INT

Subtotal

(mW)

VCCO

Subtotal

INT

(mW)

GPIO 200 LVDCI_ 25 (50) 0 16 10% 100% 35 DDR 14 157

D/mem_R_n_ext 200 HSTL_II (1.8v) 0 111 25% 100% 35 DDR 11 752

Q/mem_R_n_int 200 HSTL_II_DCI (1.8v) 111 0 25% 0% 35 DDR 258 3662

Mem Addr/Control 200 HSTL_II_DCI (1.8v) 0 66 10% 100% 35 SDR 18 2431

Mem K/C 200 HSTL_II_DCI (1.8v) 0 12 25% 100% 35 DDR 13 536

Mem CQ 200 HSTL_II_DCI (1.8v) 6 0 25% 0% 35 DDR 25 260

A_R/W, C_R/W 200 HSTL_II (1.8v) 0 12 10% 100% 35 SDR 1 41

Total 344 7859

31 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 32

Product Not Recommended for New Designs

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 32

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 33

Product Not Recommended for New Designs

Termination and Transmission Line Summaries

Chapter 4

Signal Integrity Recommendations and Simulations

This chapter provides the following information:

• Summary of the termination schemes for various signals

(refer to “Termination and Transmission Line Summaries,” page 33).

• IBIS simulations and duty cycle measurements (refer to “IBIS Simulations,” page 35).

R

Termination and Transmission Line Summaries

Table 4-1 summarizes the terminations for the three QDR II SRAM components for both

the FPGA and memory.

Table 4-1: QDR SRAM Terminations

Number Signal Drivers at the FPGA Termination at FPGA Termination at Memory

1 Data (D) HSTL_18_C2_DCI No termination 50 ohm pull-up to 0.9 V

2 Data (Q) HSTL_18_C1 No termination No termination

3 Data Strobe (CQ, CQ

4 Clock (K, K

Address (A) HSTL_18_C2 No termination 100 ohm parallel split

5

Control (R

6

) HSTL_18_C2 50 ohm pull-up to 1.3V No termination

, W, BW) HSTL_18_C2 No termination 100 ohm parallel split

) HSTL_18_C2 50 ohm pull-up to 1.3V 50 ohm pull-up to 0.9 V

termination pull-up to

1.8 V

termination pull-up to

1.8 V

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 33

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 34

Product Not Recommended for New Designs

R

Chapter 4: Signal Integrity Recommendations and Simulations

Terminations and Transmission Lines for QDR Components

Data and Clock Signals (D, Q, CQ, CQ, and CLK)

For the QDR signals included in the data bus D, the terminations consist of a 50 ohm

parallel termination pulled-up to 0.9 Volts. As DCI is used in the FPGA, no termination is

required.

Use 50 ohm transmission lines with less than ±1% tolerance on

impedance. The recommendations for the transmission line lengths are:

• All the data and clock signals are point-to-point from the FPGA to each QDR

component. The flight time of the signals going to one individual QDR II SRAM

component need to be matched with respect to the other signals with a ±2% tolerance.

• All signals going to the memory component have been matched within a 200 ps.

window. This timing requirement includes the FPGA internal package skew

(available in Appendix 2, “FPGA Pinout”) and the skew between the ball of the FPGA

to the resistor pack as well as the length of the actual trace.

• The IBIS simulation provided in “IBIS Simulations,” page 35 have been processed

using the actual PCB characteristics, from the PCB layout tool and the memory and

FPGA driver IBIS models.

Address and Control Signals (A, R, W, BW)

For the address and control signals, no termination is r equir e d at the FPGA. At memory, a

50 ohm resistor pulled up to 0.9 V is used to terminate the transmission line.

Use 50 ohm transmission lines with ± 5% tolera

components. The recommendations for the transmission line lengths are as follows:

• All the data and clock signals are point-to-point from the FPGA to each QDR

component. The flight time of the signals going to one individual QDR II SRAM

component need to be matched with respect to to the other signals with a ± 2%

tolerance.

• All signals going to the memory component have been matched within a 200 ps.

window. This timing requirement includes the FPGA internal package skew

(available in Appendix 2, “FPGA Pinout”) and the skew between the ball of the FPGA

to the resistor pack as well as the length of the actual trace.

• The IBIS simulation provided in “IBIS Simulations,” page 35 have been processed

using the actual PCB characteristics, from the PCB layout tool and the memory and

FPGA driver IBIS models.

the transmission line

nce from the FPGA to all the memory

34 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 35

Product Not Recommended for New Designs

IBIS Simulations

IBIS Simulations

This section summarizes the various simulations run on the ML365 Board using IBIS. The

simulations have been completed using the Cadence SPECCTRAQuest tool. These

simulations account for specific PCB characteristics, ensuring high fidelity waveforms. For

each waveform presented in this section, the results of the test conditions are provided.

The simulations have been divided into the following categories:

Data Signal Simulations

R

♦ Data signals from the FPGA to the QDR II SRAM, U11, Component B, Data D,

Bit 4

- Typical Case

- Slow Weak Case

- Fast Strong Case

- Eye Diagram

♦ Data signals from the QDR II SRAM to the FPGA, U11, Component B, Data Q,

Bit 4

- Typical Case

- Slow Weak Case

- Fast Strong Case

- Eye Diagram

Clock Signal Simulations

♦ Clock signals from the FPGA to the QDR II SRAM, U11, Component B

- Typical Case

- Slow Weak Case

- Fast Strong Case

Address and Control Signal Simulations

♦ Address and control signals from the FPGA to the QDR II SRAM Memory

Component

- QDR II SRAM, U11, Component B, Address Bit 4 (Typical, Slow/Weak, and

Fast/Strong Cases)

Notes on the Simulation Results

The provided waveforms show the results of each simulation. The signals in these

waveforms are color-coded:

• Purple signal: T y pical driver

• Green signal: Fast/strong driv er

• Blue signal: Slow/weak driver

For the eye diagram, the typical drivers are used.

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 35

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 36

Product Not Recommended for New Designs

R

Data Signal Simulations

All of the data signal simulation use the following test conditions for typical, slow/weak,

and fast/strong cases:

• Topology for data signals: 50-ohm transmission lines

• Transmit:

♦ At the memory: 100-ohm parallel split termination pulled-up to V

(equivalent to a 50-ohm termination pulled up to V

♦ At the FPGA: HSTL_18_C2 drivers

• Receive:

♦ At the FPGA: HSTL_18_C1_DCI receivers (internal termination, VRP, and VRN

pins connected to reference resistors)

Figure 4-1 shows signal terminations for transmitted and received data.

Chapter 4: Signal Integrity Recommendations and Simulations

= 1.8 V

= 0.9V)

ref

V

dd

dd

FPGA

FPGA

QDR II SRAM

QDR II SRAM

ml365_01_061504

Figure 4-1: Signal Terminations for Transmitted and Received Data

36 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 37

IBIS Simulations

Data Signals from the FPGA to the Memory (HSTL_18_C2 at FPGA)

Product Not Recommended for New Designs

R

The simulations in this subsection test the data signals from the FPGA to the memory.

Simulations were performed for the following cases: typical, slow/weak, and fast/strong

(refer to Figure 4-2).

Figure 4-2: Data Signal Bit 4 from the FPGA to the Memory (Typical Case)

An eye diagram is provided as well (refer to Fi

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 37

UG066 (v1.0) June 29, 2004 1-800-255-7778

gure 4-3).

Page 38

Product Not Recommended for New Designs

R

Chapter 4: Signal Integrity Recommendations and Simulations

Figure 4-3: Eye Diagram for Data Bit 4 from the FPGA to the QDR II SRAM, U11

38 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 39

IBIS Simulations

Data Signals from the QDR II SRAM, Component U11 to the FPGA Measured at the FPGA

Product Not Recommended for New Designs

R

The simulations in this subsection test the data signals from the last memory component to

the FPGA. Simulations were performed for the following cases: typical, slow/weak, and

fast/strong. An eye diagram is provided as well (refer to Figure 4-5).

Figure 4-4 sho

ws the simulation waveforms for this case.

Figure 4-4: Data Signals from the QDR II SRAM U11 at the FPGA (Typical,

Slow/Weak and Fast/Strong Cases)

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 39

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 40

Product Not Recommended for New Designs

R

Eye Diagram for the Component U11, Bit 4 Signal Measured at the FPGA

Figure 4-5 shows the eye diagram for the data signals from the FPGA to the last memory

component.

Chapter 4: Signal Integrity Recommendations and Simulations

Figure 4-5: Eye Diagram for Data Bit 4 at the FPGA from Component U11

40 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 41

Product Not Recommended for New Designs

Clock Signal Simulations

Clock Signal Simulations

The simulations in this subsection test the uni-directional Clock K signal from the FPGA to

the QDR II SRAM, Component B. Simulations were performed for the following cases:

typical, slow/weak, and fast/strong. All of the clock signal simulations use the following

test conditions for typical, slow/weak, and fast/strong cases (refer to Figure 4-6).

• Topology for clock signals: 50-ohm transmission lines

• Clock K

♦ At the memory: 100-ohm parallel split termination pulled-up to V

(equivalent to a 50-ohm termination pulled up to V

♦ At the FPGA: HSTL_18_C2 drivers

• CQ Clock

♦ At the FPGA: HSTL_18_C1 receivers, 100-ohm parallel split termination pulled-

up to V

dd

= 0.9V)

ref

dd

= 1.8 V (equivalent to a 50-ohm termination pulled up to V

V

K Clock

dd

= 1.8 V

= 0.9V)

ref

R

FPGA

FPGA

QDR II SRAM

V

dd

QDR II SRAM

CQ Clock

ml365_02_062804

Figure 4-6: Clock Signal Terminations

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 41

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 42

Product Not Recommended for New Designs

R

Typical, Slow, and Fast Cases for Clock Signals

Figure 4-7 shows the simulation waveforms for this case.

Chapter 4: Signal Integrity Recommendations and Simulations

Figure 4-7: Clock K Signal from the FPGA to the QDR II SRAM, Component U11

Figure 4-8 shows the

QDR II SRAM, Component U11.

simulation waveforms for the Clock K Signal from the FPGA to the

42 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 43

Product Not Recommended for New Designs

Clock Signal Simulations

R

Figure 4-8: Clock CQ Signal from the FPGA to the QDR II SRAM Component U11

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 43

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 44

Product Not Recommended for New Designs

R

Chapter 4: Signal Integrity Recommendations and Simulations

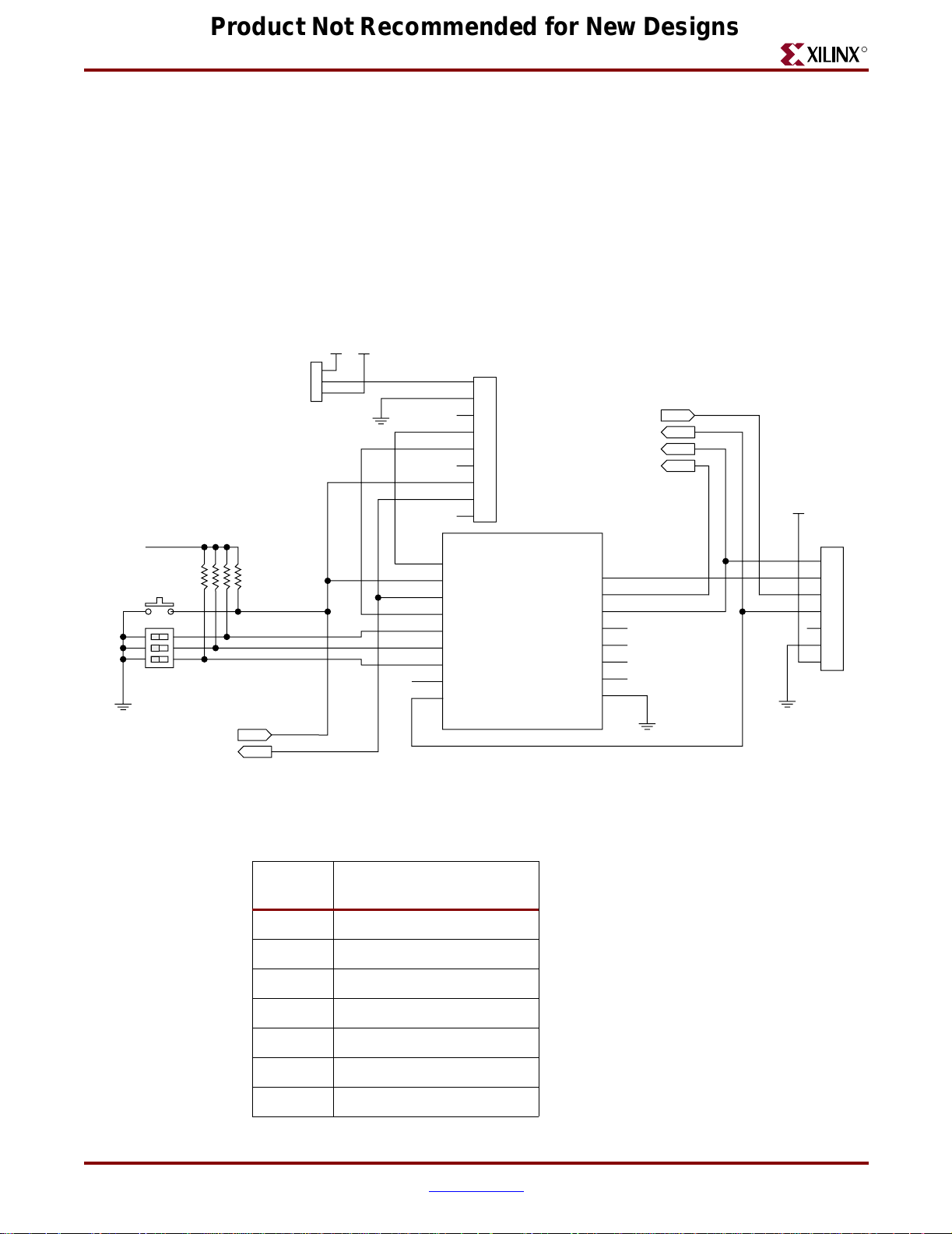

Address and Control Signal Simulations

The simulations in this subsection test the uni-directional address and control signals fr om

the FPGA to the QDR II SRAM, Component B, U11, Bi t 4. S imulations wer e performed for

typical, slow/weak, and fast/strong driver cases.

All of the clock signal simulations use the following test conditions for typical, slow weak,

ast strong cases

and f

• Topology for data signals: 50-ohm Transmission lines

• At the memory: 100-ohm parallel split termination pulled up to Vdd = 1.8 V

(equivalent to 50-ohm termination pulled up to Vref = 0.9V)

• At the FPGA: HSTL_18_C2 drivers

Figure 4-9 shows address and control signal terminations.

V

dd

Figure 4-9: Address and Control Signal Terminations

Typical Case Simulation at All Memory Components

Figure 4-10 shows the typical case simulation waveforms for the QDR II SRAM,

Component B, Bit 4.

QDR II SRAMFPGA

ml365_03_061504

44 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 45

Product Not Recommended for New Designs

Address and Control Signal Simulations

R

Figure 4-10: Address/Control Signals for the QDR II SRAM, Component U11, Bit 4

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 45

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 46

Product Not Recommended for New Designs

R

Chapter 4: Signal Integrity Recommendations and Simulations

46 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 47

Product Not Recommended for New Designs

R

Board Layout Guidelines

This chapter provides information on decoupling capacitors, ground signals, and PCB

layout.

Decoupling Guidelines

This section lists the decoupling capacitors used with the major components of the ML365

board. Refer to the board schematics for the exact placement.

Chapter 5

Table 5-1 lists the decoupling capacitors for the Virtex-II Pr o FPGA and the QDR II SRAM.

VAUX and VDD are common to these two devices. Refer to the Xilinx application note

XAPP623 for the implementation methodology. A balanced decoupling network is

implemented for each bank, VCCINT, VAUX, and VREF.

Table 5-1: Decoupling Capacitor Recommendations

Decoupling

Capacitors

Pin(s)

VCC 5V

LCD, RS232

3.3V

System ACE

0.01µF ceramic capacitor, X7R, C0402 8

0.047µF ceramic capacitor, X7R , C0603 4

2.2µF ceramic capacitor, X7R, C1206 4

33µF ceramic capacitor, 10V, C7343 0

330µF solid tantalum capacitor, 10V, C7343 3

0.01µF ceramic capacitor, X7R, C0402 14

0.047µF ceramic capacitor, X7R , C0603 7

2.2µF ceramic capacitor, X7R, C1206 7

33µF ceramic capacitor, 10V, C7343 1

Capacitor Value Distribution

330µF solid tantalum capacitor, 10V, C7343 4

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 47

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 48

Product Not Recommended for New Designs

R

Table 5-1: Decoupling Capacitor Recommendations

Decoupling

Capacitors

Pin(s)

Capacitor Value Distribution

Chapter 5: Board Layout Guidelines

VAUX 2.5V

1 capacitor per

pin, in a

balanced

decoupling

network.

VCCO 1.8V

HSTL 1.8V

electrical

standard

VCCINT 1.5V

1 capacitor per

pin, in a

balanced

decoupling

network.

VTT 0.9V

HSTL 1.8V/2

for FPGA Vref

inputs

0.01µF ceramic capacitor, X7R, C0402 31

0.047µF ceramic capacitor, X7R , C0603 14

2.2µF ceramic capacitor, X7R, C1206 7

33µF ceramic capacitor, 10V, C7343 4

330µF solid tantalum capacitor, 10V, C7343 2

0.01µF ceramic capacitor, X7R, C0402 76

0.047µF ceramic capacitor, X7R , C0603 38

2.2µF ceramic capacitor, X7R, C1206 23

33µF ceramic capacitor, 10V, C7343 9

330µF solid tantalum capacitor, 10V, C7343 7

0.01µF ceramic capacitor, X7R, C0402 30

0.047µF ceramic capacitor, X7R , C0603 11

2.2µF ceramic capacitor, X7R, C1206 11

33µF ceramic capacitor, 10V, C7343 8

330µF solid tantalum capacitor, 10V, C7343 6

0.01µF ceramic capacitor, X7R, C0402 5

0.047µF ceramic capacitor, X7R , C0603 1

2.2µF ceramic capacitor, X7R, C1206 4

33µF ceramic capacitor, 10V, C7343 0

330µF solid tantalum capacitor, 10V, C7343 0

VTT 0.9V

HSTL 1.8V/2

for memory

Vref inputs

0.01µF ceramic capacitor, X7R, C0402 13

0.047µF ceramic capacitor, X7R , C0603 9

2.2µF ceramic capacitor, X7R, C1206 0

33µF ceramic capacitor, 10V, C7343 0

330µF solid tantalum capacitor, 10V, C7343 0

Providing Additional Ground Pins

Unused and No Connect pinscan be connected to ground to improve the thermal

dissipation through the metal planes in the Printed Circuit Boar d. Since DCI can be used in

the FPGA, the heat resulting from its use can be significant.

48 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 49

Product Not Recommended for New Designs

Board Stackup Guidelines

Board Stackup Guidelines

Table 5-2 shows a suggested stackup for a 12-layer board (4 signal layers, 6 dedicated

planes, 2 layers with both signals and ground planes). Figure 5-1 shows the top layer of the

ML365 (Revision 1.0b) board, and Figure 5-2 shows the bottom layer of the board.

Table 5-2: Suggested Stackup for a 12-layer board

12-Layer

Board

Stackup#

1 Plane GND Gnd 1 / Sig 1 Ground plane, some memory traces

2 Plane +2.5V/ +5V Pwr 1 Carve out two power planes on this layer

3 Signal +1.8V/ +2.5V Sig 2 Some HSTL traces to the memory on this layer

4 Signal +1.8V/ +2.5V Sig 3 Some HSTL traces to the memory on this layer

5 Plane GND Gnd 2 Ground plane

Type Layer Trace / Spacing Comments

R

6 Plane +1.5V Pwr 2 1.5V power plane

7 Plane +0.9V Pwr 3 0.9V reference plane

8 Plane GND Gnd 3 Ground plane

9 Signal +1.8V/ +2.5V Sig 4 Some HSTL traces to the memory on this layer

10 Signal GND Sig 5 Ground plane

11 Plane +1.8V & +3.3V Pwr 4 Carve out two power planes on this layer

12 Plane GND Gnd 4 / Sig 6 Ground plane, some memory traces

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 49

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 50

Product Not Recommended for New Designs

R

Chapter 5: Board Layout Guidelines

Figure 5-1: Picture of the Top Layer of the ML365 Revision 1.0b Board

50 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 51

Product Not Recommended for New Designs

Board Stackup Guidelines

R

Figure 5-2: Picture of the Bottom Layer of the ML365 Revision 1.0b Board

ML365 Virtex-II Pro QDR II SRAM Mem. Board www.xilinx.com 51

UG066 (v1.0) June 29, 2004 1-800-255-7778

Page 52

Product Not Recommended for New Designs

R

Chapter 5: Board Layout Guidelines

52 www.xilinx.com ML365 Virtex-II Pro QDR II SRAM Mem. Board

1-800-255-7778 UG066 (v1.0) June 29, 2004

Page 53

Product Not Recommended for New Designs

R

Related Documentation

This appendix provides references to documents and web pages for components on the

ML365 board.

• Xilinx, Inc.

♦ Virtex-II Pro X™ Platform FPGAs