Page 1

0

PLB PCI Full Bridge (v1.00a)

DS508 March 21, 2006

0 0

Introduction

The PLB PCI Full Bridge design provides full bridge

functionality between the Xilinx 64-bit PLB and a 32-bit

Revision 2.2 compliant Peripheral Component

Interconnect (PCI) bus. The bridge is referred to as the

PLB PCI Bridge in this document.

The Xilinx PLB is a 64-bit bus subset of the IBM PLB

described in the 64-Bit Processor Local Bus Architecture

Specification v3.5. Details on the Xilinx PLB and the PLB

IPIF are found in the Processor IP Reference Guide. This

guide is accessed via EDK help or the Xilinx website at:

http://www.xilinx.com/ise/embedded/proc_ip_ref_

guide.pdf.

The LogiCORE PCI v3.0 core provides an interface with

the PCI bus. Details of the LogiCORE PCI 32 v3.0 core

operation is found in the

v3.0 Product Specification and the Xilinx The Real-PCI

Design Guide v3.0.

Xilinx LogiCORE PCI Interface

Product Specification

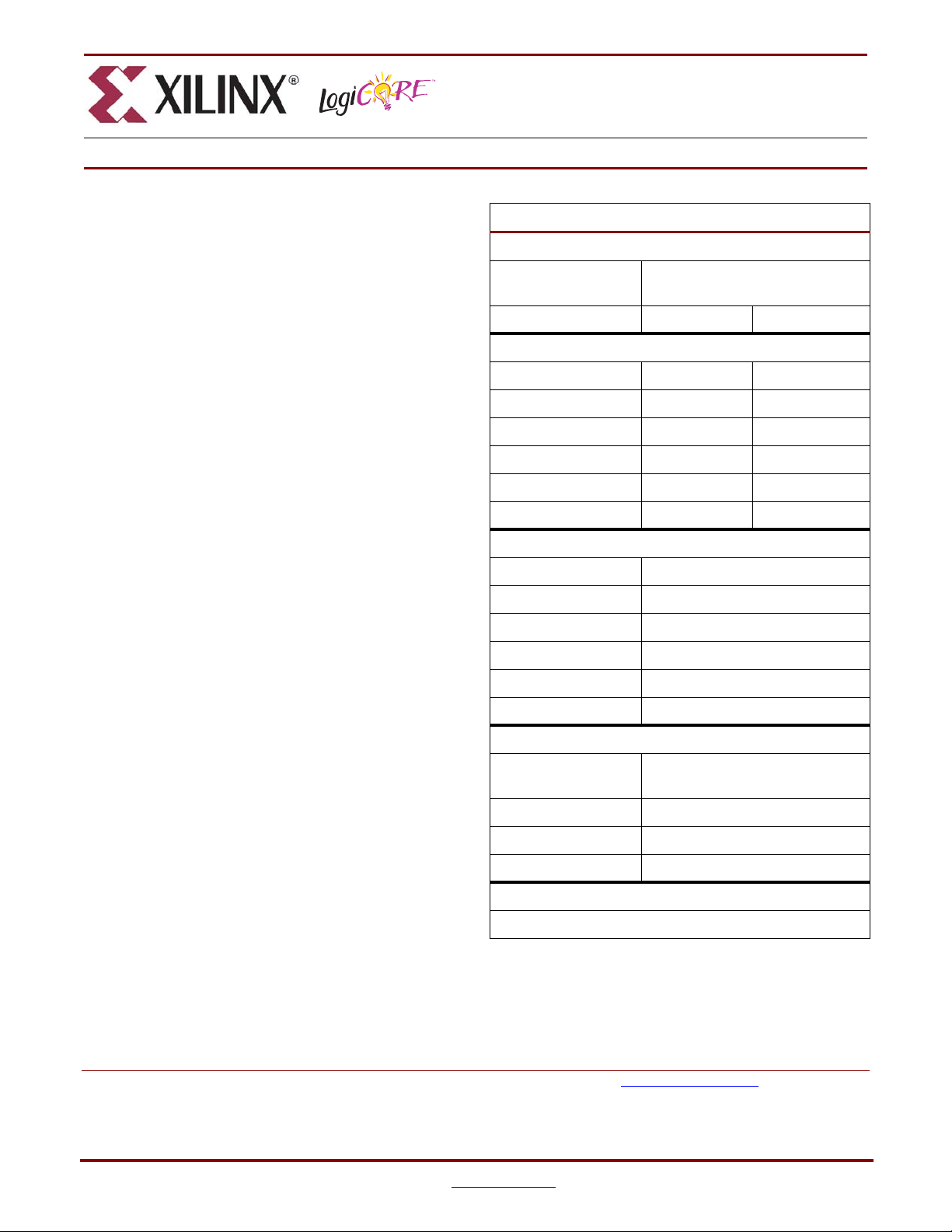

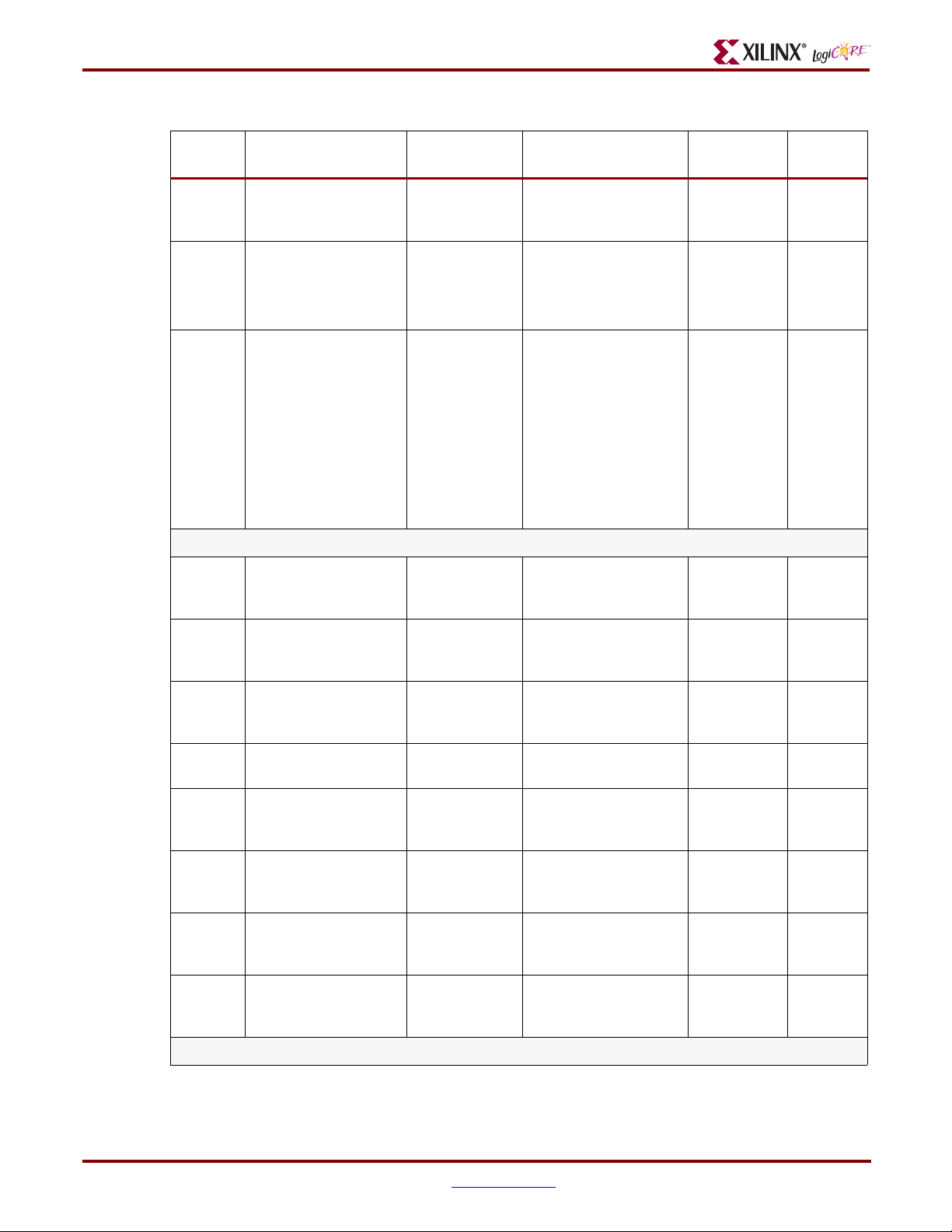

LogiCORE™ Facts

Core Specifics

Supported Device

Family

Version of Core plb_pci v1.00a

Resources Used

Virtex-IIP Min Max

I/O (PCI) 49 50

I/O (PLB-related) 397 433

LUTs 3350 3870

FFs 2570 2970

Block RAMs 8 8

Documentation Product Specification

Design File Formats VHDL

C

Provided with Core

Virtex™-II Pro, Virtex-4

ESS

Host bridge functionality (often called North bridge

functionality) is an optional functionality.

Configuration Read and Write PCI commands can be

performed from the PLB-side of the bridge. The PLB

PCI Bridge supports a 32-bit/33 MHz PCI bus only.

Exceptions to the support of PCI commands supported

by the v3.0 core are outlined in the

The PLB PCI Bridge design has parameters that allow

customers to configure the bridge to suit their

application. The parameterizable features of the design

are discussed in the

Bus Interface Parameters section.

A

Features section.

RLY AC

E

Constraints File example UCF-file

Verification N/A

Instantiation Template N/A

Reference Designs None

Design Tool Requirements

Xilinx Implementation

Tools

Verification N/A

Simulation ModelSim SE/EE 5.8d or later

Synthesis XST

Support

Support provided by Xilinx, Inc.

8.1.1i or later

© 2005 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at http://www.xilinx.com/legal.htm. All other trademarks and

registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application,

or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

DS508 March 21, 2006 www.xilinx.com 1

Product Specification

Page 2

PLB PCI Full Bridge (v1.00a)

Features

• Independent PLB and PCI clocks

• 33 MHz, 32-bit PCI bus support

• Utilizes two pairs of FIFOs to exploit the separate master and slave PLB IPIF modules.

• Includes a master IP module for remote PCI initiator transactions, which follows the protocol for

interfacing with the master IPIF module utilizing Xilinx LocalLink protocol. The PLB PCI Bridge

translates the PCI initiator request to PLB IPIF master transactions.

• Includes a slave IP module for remote PLB master transactions, which follows the protocol for

interfacing with the slave IPIF module utilizing Xilinx IPIC protocol. The PLB PCI Bridge translates

the PLB master request to PCI initiator transactions. The SRAM-like interface is utilized at the IPIC

interface for data transfers.

• The PLB IPIF slave attachment has a timer that limits the time for both read and write dataphase

operations to complete. When the timer expires, Sl_MErr signal is asserted. See PLB IPIF Product

Specification for details.

• Full bridge functionality

- PLB Master read and write of a remote PCI target (both single and burst)

- PCI Initiator read and write to a remote PLB slave (both single and multiple).

- I/O read and I/O write commands are supported only for PLB master read and writes of PCI

I/O space as designated by its associated memory designator parameter. All memory space on

the PLB-side is designated as memory space in the PCI sense, therefore, I/O commands cannot

be used to access memory on the PLB-side.

- Configuration read and writes are supported (including self-configuration transactions) only

when upper word address lines are utilized for IDSEL lines. The Configuration Read and Write

commands are automatically executed by writing to the Configuration Data Port Register. Data

in the Configuration Address Port Register and the Configuration Bus Number/Subordinate Bus

Number Register are used in execution of the configuration transaction per PCI 2.2 specification.

• PCI Memory Read Line (MRL) command is supported in which the v3.0 core is a target. MRL is

aliased to a Memory Read command which has a single data phase on the PCI.

• PCI Memory Write Invalidate (MWI) command is supported in which the v3.0 core is a target. The

v3.0 core does not support this command when it is an initiator. MWI is aliased to a Memory Write

command which has a single data phase on the PCI.

• Supports up to 6 PLB devices, in the sense defined by independent parameters and unique PLB

memory space for each device

- Each device has the following parameters: PLB BAR, high (upper) address, memory designator,

and translation for mapping PLB address space to PCI address space. Byte addressing integrity is

maintained by default in all transfers. Address translation is performed by high-order bit

substitution. High-order bit definition can be done with parameters or dynamically via registers.

EARLY ACCESS

• Supports up to 3 PCI devices (or BARs in PCI context) with unique memory PCI memory space.

The v3.0 core supports up to 3 PCI BAR.

- Each device has the following parameters: PCI BAR, length, memory designator, and translation

for mapping PCI address space to PLB address space. Byte addressing integrity is maintained by

2 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 3

PLB PCI Full Bridge (v1.00a)

default in all transfers. Address translation is performed by high-order bit substitution.

High-order bit definition is defined only by parameters

•Registers include

- Interrupt and interrupt enable registers at different hierarchal levels

-Reset

- Configuration Address Port, Configuration Data Port and Bus Number/Subordinate Bus

Number

- High-order bits for PLB to PCI address translation

- Bridge Device number on PCI bus

• PLB-side Interrupts include

- PLB Master Read SERR and PERR

- PLB Master Read Target Abort

- PLB Master Write SERR and PERR

- PLB Master Write Target Abort

- PLB Master Write Master Abort

- PLB Master Burst Write Retry and Retry Disconnect

-PLB Master Burst Write Retry Timeout

- PCI Initiator Read and Write SERR

• Asynchronous FIFOs with backup capability

• Synchronization circuits for signals that cross time-domain boundaries

• Responds to the PCI latency timer

• Completes posted write operations prior to initiating new operations

• Signal set required for integrating a PCI bus arbiter in the FPGA with the PLB PCI bridge is

available at the top-level of the PLB PCI bridge module. The signal set includes PCLK, RST_N,

FRAME_I, REQ_N_toArb and IRDY_I

• Supports PCI clock generated in FPGA

• Parameterized control of IO-buffer insertion of INTR_A and REQ_N IO-buffers

• All address translations performed by high-order bit substitution. The number of bits substituted

depends on the address range

- Parameterized selection of IPIF BAR high-order bits defined by programmable registers for

dynamic translation operation or by parameters for reduced resource utilization

Y

L

ACCESS

AR

• Parameterized selection of device ID number (when configuration functionality is included)

defined by a programmable register for dynamic device number definition or by parameter to

reduce resource utilization

E

• The PLB PCI bridge does not have an integral DMA

• Input signal to provide the means to asynchronous asset INTR_A from a user supplied register (i.e.,

a PLB GPIO). The signal is Bus2PCI_INTR is an active high signal

• PCI Monitor output port to monitor PCI bus activity

DS508 March 21, 2006 www.xilinx.com 3

Product Specification

Page 4

PLB PCI Full Bridge (v1.00a)

System Reset

When the bridge is reset, both RST_N and PLB_reset must be simultaneously held at reset for at least

twenty clock periods of the slowest clock.

Evaluation Version

The PLB PCI Bridge is delivered with a hardware evaluation license. When programmed into a Xilinx

device, the core will function in hardware for about 8 hours at the typical frequency of operation. To use

the PLB PCI Bridge without this timeout limitation, a full license must be purchased.

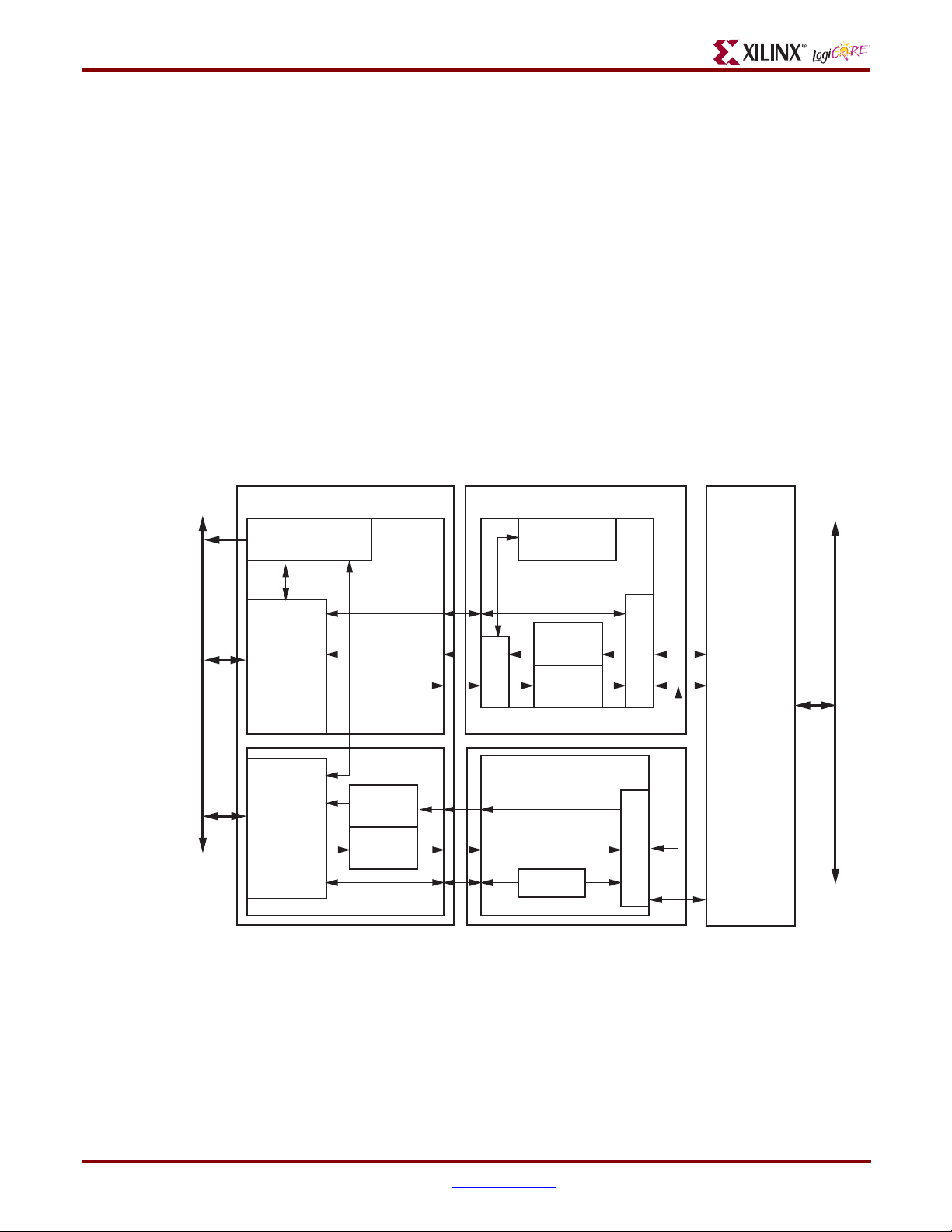

Functional Description

The PLB PCI Bridge design is shown in Figure 1 and described in the following sections. As shown,

PLB IPIF PCI Bridge is comprised of three main modules:

• The PLB IPIF (Processor Local Bus Intellectual Property InterFace). It interfaces to the PLB bus.

• The IPIF v3.0 Bridge. It interfaces between the PLB IPIF and the v3.0 core.

• The LogiCORE PCI32 Interface v3.0 core. It interfaces to the PCI bus.

Figure Top x-ref 1

Interrupt

Module

PLB IPIF

IPIF/V3 Bridge Xilinx

v3.0 PCI Core

Bridge

Registers

PLB Bus

Slave

Attachment

Master

Attachment

PCI2IPIF

FIFO

IPIF2PCI

FIFO

Slave SM

Master SM

PCI2IPIF

FIFO

IPIF2PCI

FIFO

Initiator

Target

PCI Bus

EARLY ACCESS

ds508_01_112205

Figure 1: PLB PCI Full Bridge Block Diagram

LogiCore Version 3.0 32-bit PCI Core Requirements

The PLB PCI bridge uses the 32-bit Xilinx LogiCore Version 3 IP core. Before the bridge can perform

transactions on the PCI bus, the v3.0 core must be configured via configuration transactions from either

the PCI-side or if configuration functionality is included in the bridge configuration, from the PLB-side.

Both a design guide and an implementation guide are available for the Xilinx LogiCore v3.0 PCI IP

4 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 5

PLB PCI Full Bridge (v1.00a)

core. These documents detail the v3.0 core operation, including configuration cycles, and are available

from Xilinx.

As required by the LogiCORE v3.0 core, GNT_N must be asserted for two clock cycles to initiate a PCI

transaction by the PLB PCI Bridge.

Bus Interface Parameters

Because many features in the IPIF v3.0 Bridge design can be parameterized, the user can realize a PLB

PCI Full Bridge uniquely tailored while using only the resources required for the desired functionality.

This approach also achieves the best possible performance with the lowest resource usage.

shown the features that can be parameterized in the PLB PCI Bridge design.

Address Translation

Address space on the PCI side that is accessible from the PLB side must be translated to a 2N contiguous

block on the PLB side. Up to six contiguous blocks are possible. Each block has parameters for base

address (C_IPIFBAR_N), high address, address translation vector, and memory designator (memory or

I/O).

All address space on the PLB side that is accessible from the PCI side must be translated to a maximum

of three 2

v3.0 core supports up to 3 BARs. Each block has parameters for length, which must be a 2

address translation vector. Only PCI memory space is supported.

N

contiguous blocks on the PCI side. Up to three blocks are possible because the LogiCore PCI

Tab le 1

N

range, and

Address translations in both directions are performed as follows:

• High-order address bits are substituted for the address vector before crossing to the other bus

domain. The number of high-order bits substituted in the PLB address presented to the bridge is

given by the number of bits that are the same between the C_IPIFBAR_N and C_

IPIF_HIGHADDR_N parameters. The number of high-order bits substituted in the PCI address

presented to the bridge for a translation from PCI to PLB domains is given by the bus width minus

the parameter C_PCIBAR_LEN_N.

• The low-order bits are transferred directly between bus domains. The bits substituted in a

translation from PLB to PCI domains can be selected via a parameter

(C_INCLUDE_BAROFFSET_REG) as either a parameter (C_IPIFBAR2PCIBAR_N) or a

programmable register for each BAR. The bits that are substituted for in a translation from PCI to

PLB domains is defined by a parameter (C_PCIBAR2IPIFBAR_M) for each BAR.

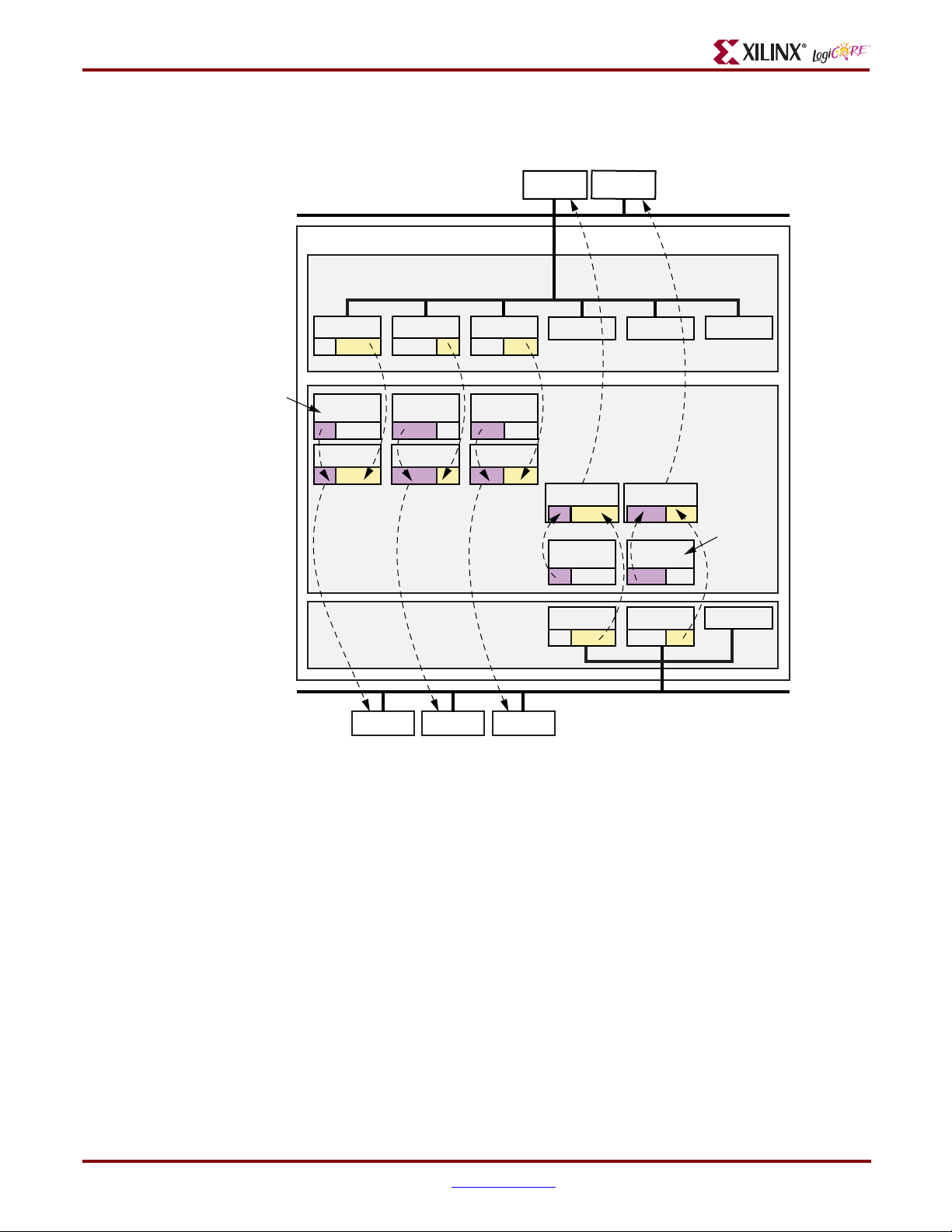

Figure 2 shows two sets of base address register (BAR) parameters and how they are used. The two sets

are independent sets: one set for the up to six PLB-side device (IPIFBAR) address ranges and another

set for the up to three PCI-side device (PCIBAR) address ranges.

This document includes three examples of how to use the two sets of base address register (BAR)

parameters:

Example 1, shown in Figure 2, outlines the use of the two sets of BAR parameters.

Example 2 outlines the use of the IPIFBAR parameters sets for the specific address translations of PLB

addresses within the range of a given IPIFBAR to a remote PCI address space.

E

AR

Y

L

ACCESS

DS508 March 21, 2006 www.xilinx.com 5

Product Specification

Page 6

PLB PCI Full Bridge (v1.00a)

Example 3 outlines the use of the PCIBAR parameter sets for the address translation of PCI addresses

within the range of a given PCIBAR to a remote PLB address space.

Figure Top x-ref 2

PLB Bus

PLB PCI Full Bridge

IPIF

C_IPIFBAR_NUM = 3

BAR_10

BAR_11

IPIFBAR_0

Note 1

PCI Bus

Figure 2: Translation of Addresses Bus-to-Bus with High-Order Bit Substitution

(high-order

bit sub)

Addr to PCI

IPIFBAR_1

(high-order

bit sub)

Addr to PCI

v3.0 LogiCORE

C_PCIBAR_NUM = 2

PBAR_21 PBAR_22PBAR_20

IPIFBAR_2

(high-order

bit sub)

Addr to PCI

IPIFBAR_3 IPIFBAR_4

IPIF to v3.0 LogiCORE Bridge

Addr to PLB

(high-order

bit sub)

PCIBAR_0

Addr to PLB

(high-order

bit sub)

PCIBAR_1

IPIFBAR_5

Note 2

PCIBAR_2

ds508_02_112205

Example 1

Because address translations are performed only when the PLB PCI Bridge is configured with FIFOs,

the example shown in

Figure 2 is for an PLB PCI Bridge configuration with FIFOs only. In this example, it

is assumed that C_INCLUDE_BAROFFSET_REG=0, therefore, the parameters C_IPIFBAR2PCIBAR_N

define the high-order bits for substitution in translating the address on the PLB bus to the PCI bus.

The PLB parameters are C_IPIFBAR_N, C_IPIF_HIGHADDR_N, and C_IPIFBAR2PCIBAR_N for N=0

EARLY ACCESS

to 5.

The PCI parameters are C_PCIBAR_LEN_M and C_PCIBAR2IPIFBAR_M for M=0 to 2.

Example 2

Example 2 shows of the settings of the two independent sets of base address register (BAR) parameters

for specifics of address translation of PLB addresses within the range of a given IPIFBAR to a remote

PCI address space. Note that this setting does not depend on the PCIBARs of the PLB PCI Bridge.

6 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 7

PLB PCI Full Bridge (v1.00a)

As in example 1, it is assumed that the parameter C_INCLUDE_BAROFFSET_REG=0, therefore the

C_IPIFBAR2PCIBAR_N parameters define the address translation.

In this example, where C_IPIFBAR_NUM=4, the following assignments for each range are made:

C_IPIFBAR_0=0x12340000

C_IPIF_HIGHADDR_0=0x1234FFFF

C_IPIFBAR2PCIBAR_0=0x5671XXXX (Bits 16-31 are don’t cares)

C_IPIFBAR_1=0xABCDE000

C_IPIF_HIGHADDR_1=0xABCDFFFF

C_IPIFBAR2PCIBAR_1=0xFEDC0xXX (Bits 19-31 are don’t cares)

C_IPIFBAR_2=0xFE000000

C_IPIF_HIGHADDR_2=0xFFFFFFFF

C_IPIFBAR2PCIBAR_2=0x40xXXXXX (Bits 7-31 are don’t cares)

C_IPIFBAR_3=0x00000000

C_IPIF_HIGHADDR_3=0x0000007F

C_IPIFBAR2PCIBAR_3=8765438X (Bits 25-31 are don’t cares)

Accessing the PLB PCI Bridge IPIFBAR_0 with address 0x12340ABC on the PLB bus yields

0x56710ABC on the PCI bus.

Accessing the PLB PCI Bridge IPIFBAR_1 with address 0xABCDF123 on the PLB bus yields

0xFEDC1123 on the PCI bus.

Accessing the PLB PCI Bridge IPIFBAR_2 with address 0xFFFEDCBA on the PLB bus yields

0x41FEDCBA on the PCI bus.

Accessing the PLB PCI Bridge IPIFBAR_3 with address 0x00000071 on the PLB bus yields

Ox876543F1 on the PCI bus.

Example 3

Example 3 outlines address translation of PCI addresses within the range of a given PCIBAR to PLB

address space. Note that this translation is independent of the PLB PCI Bridge IPIF BARs.

The parameters C_PCIBAR2IPIFBAR_M parameters define the address translation for all

C_PCIBAR_NUM.

In this example, where C_PCIBAR_NUM=2, the following range assignments are made:

BAR 0 is set to 0xABCDE800 by host

C_PCIBAR_LEN_0=11

C_PCIBAR2IPIFBAR_0=0x123450XX (Bits 21-31 are don’t cares)

BAR 1 is set to 0x12000000 by host

C_PCIBAR_LEN_1=25

C_PCIBAR2IPIFBAR_1=0xFEXXXXXX (Bits 7-31 are don’t cares)

Accessing the PLB PCI Bridge PCIBAR_0 with address 0xABCDEFF4 on the PCI bus yields

0x123457F4 on the PLB bus.

E

AR

Y

L

ACCESS

DS508 March 21, 2006 www.xilinx.com 7

Product Specification

Page 8

PLB PCI Full Bridge (v1.00a)

Accessing the PLB PCI Bridge PCIBAR_1 with address 0x1235FEDC on the PCI bus yields

0xFE35FEDC on the PLB bus.

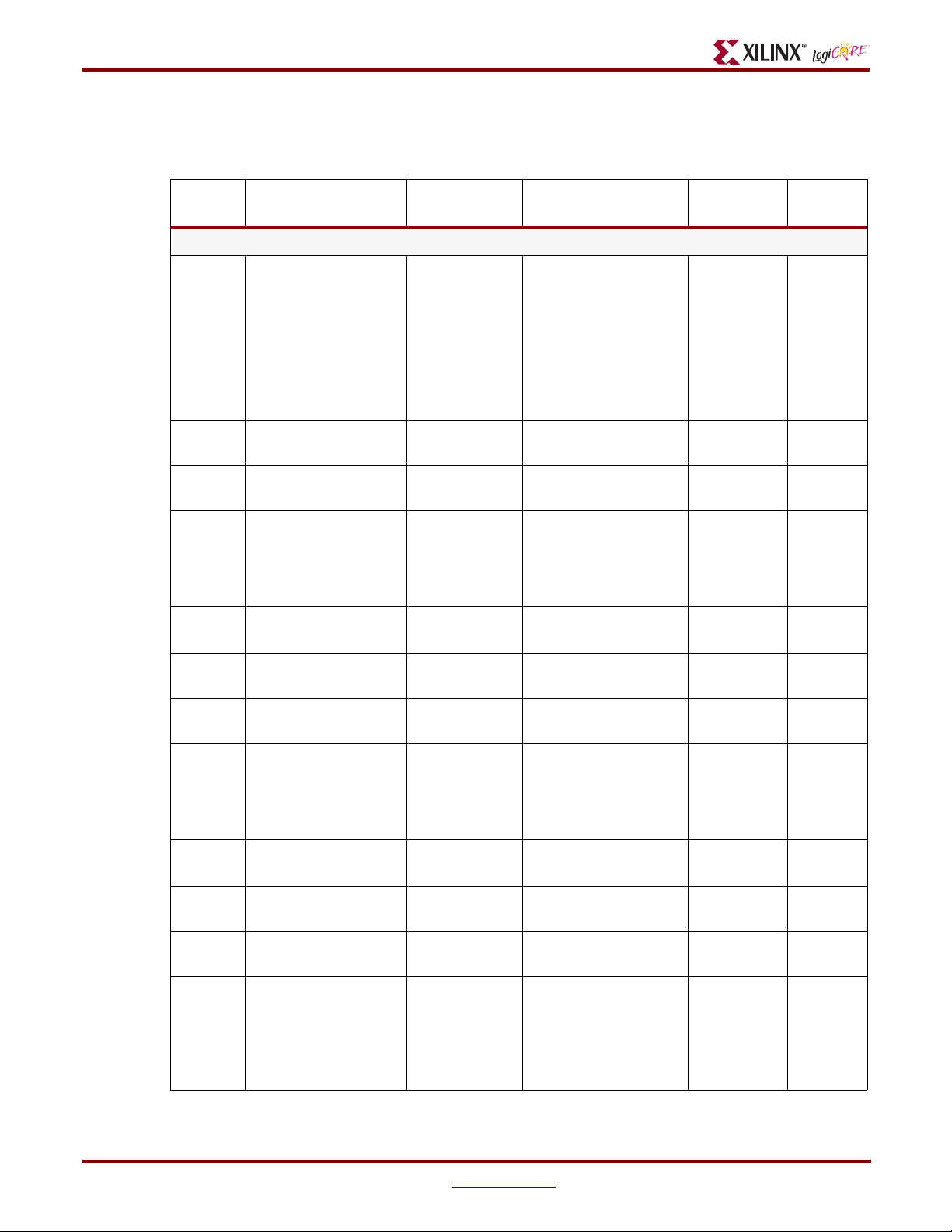

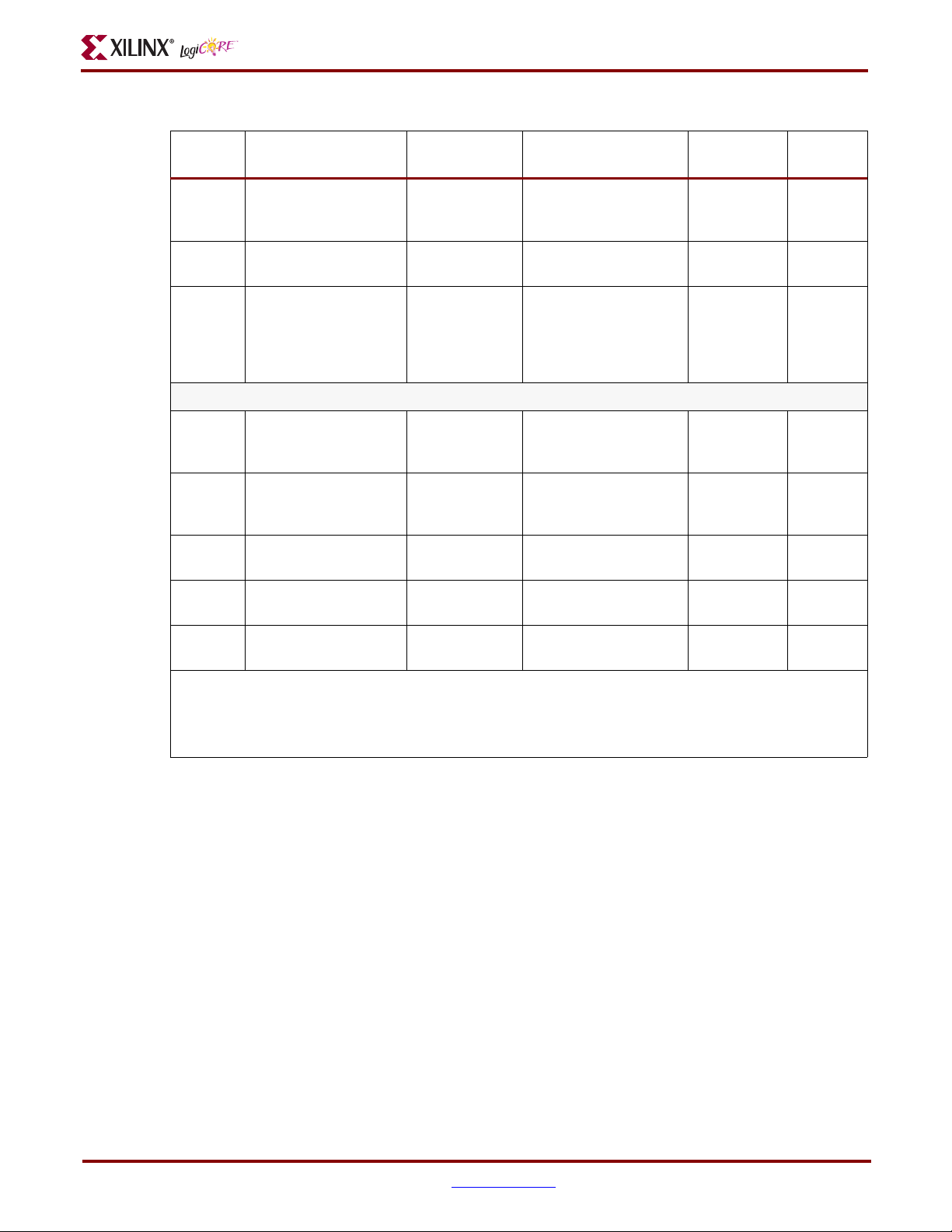

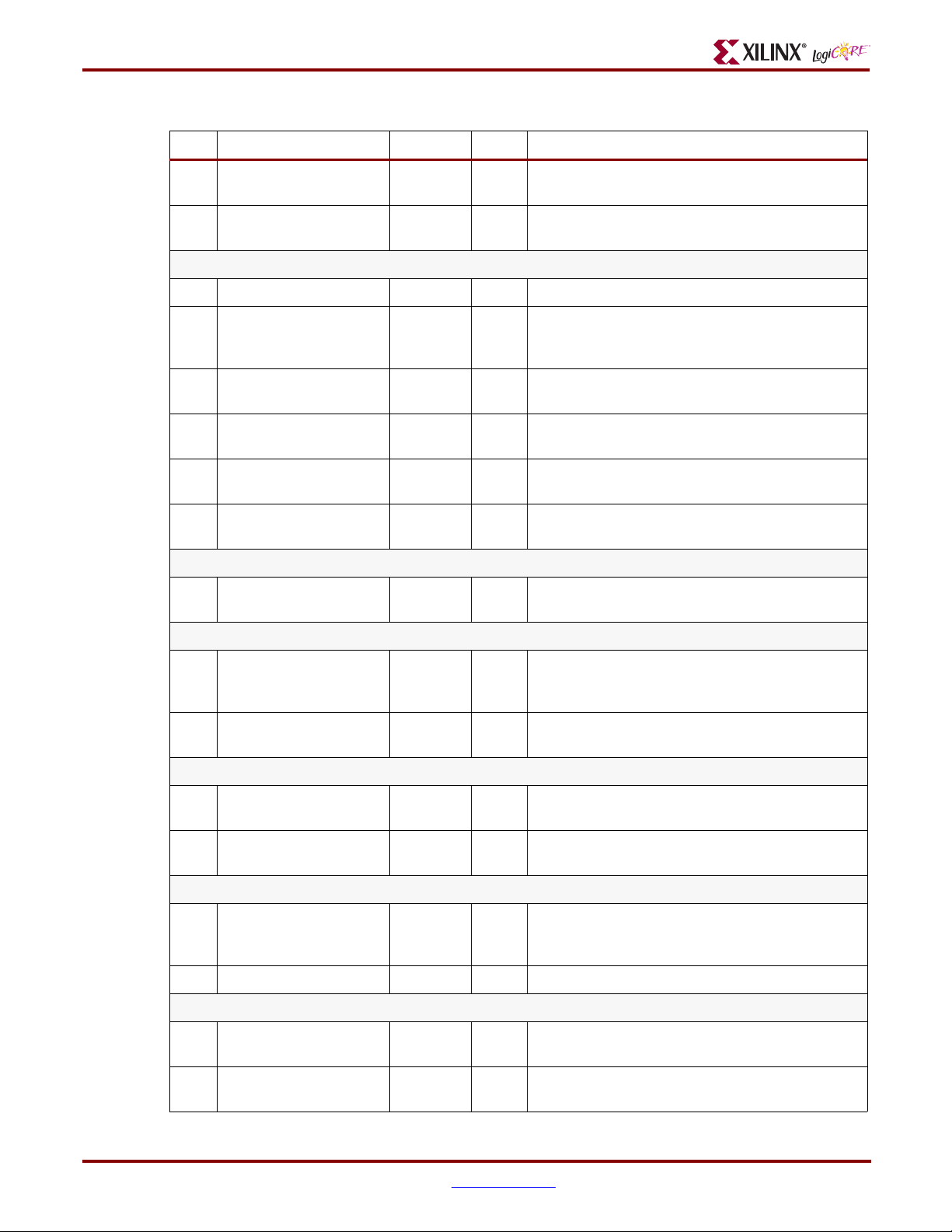

Table 1: PLB PCI Bridge Interface Design Parameters

Generic

G1 Number of IPIF devices

G2 IPIF device 0 BAR C_IPIFBAR_0 Valid PLB address

G3

G4

G5

Feature /

Description

IPIF BAR high address 0C_IPIFBAR_

PCI BAR to which IPIF

BAR 0 is mapped

unless

C_INCLUDE_BAROFF

SET_REG = 1

IPIF BAR 0 memory

designator

Parameter

Name

Bridge Features Parameter Group

C_IPIFBAR

_NUM

HIGHADDR_0

C_IPIFBAR2

PCIBAR_0

C_IPIF_SPACE

TYPE_0

1

Allowable Values

1-6; Parameters listed

below corresponding to

unused BARs are

ignored, but must be

valid values. BAR label

0 is the required bar for

all values 1-6 and the

index increments from 0

as BARs are added

Valid PLB address

Vector of length

C_PLB_AWIDTH

0 = I/O space

1 = Memory space

(1)

(1)

Default

Val ue

6 integer

0xFFFFFFFF

0x00000000

0xFFFFFFFF

1 integer

VHDL

Type

std_logic_

vector

std_logic_

vector

std_logic_

vector

G6 IPIF device 1 BAR C_IPIFBAR_1 Valid PLB address

G7

G8

G9

G10 IPIF device 2 BAR C_IPIFBAR_2 Valid PLB address

G11

G12

IPIF BAR high address 1C_IPIFBAR_

HIGHADDR_1

PCI BAR to which IPIF

BAR 1 is mapped

unless

C_INCLUDE_BAROFF

SET_REG = 1

IPIF BAR 1 memory

designator

C_IPIFBAR2

PCIBAR_1

C_IPIF_SPACE

TYPE_1

Valid PLB address

Vector of length

C_PLB_AWIDTH

0 = I/O space

1 = Memory space

EARLY ACCESS

IPIF BAR high address 2C_IPIFBAR_

HIGHADDR_2

PCI BAR to which IPIF

BAR 2 is mapped

unless

C_INCLUDE_BAROFF

SET_

REG = 1

C_IPIFBAR2

PCIBAR_2

Valid PLB address

Vector of length

C_PLB_AWIDTH

(1)

(1)

(1)

(1)

0xFFFFFFFF

0x00000000

0xFFFFFFFF

1 integer

0xFFFFFFFF

0x00000000

0xFFFFFFFF

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

8 www.xilinx.com DS508 March 21, 2006

Product Specification

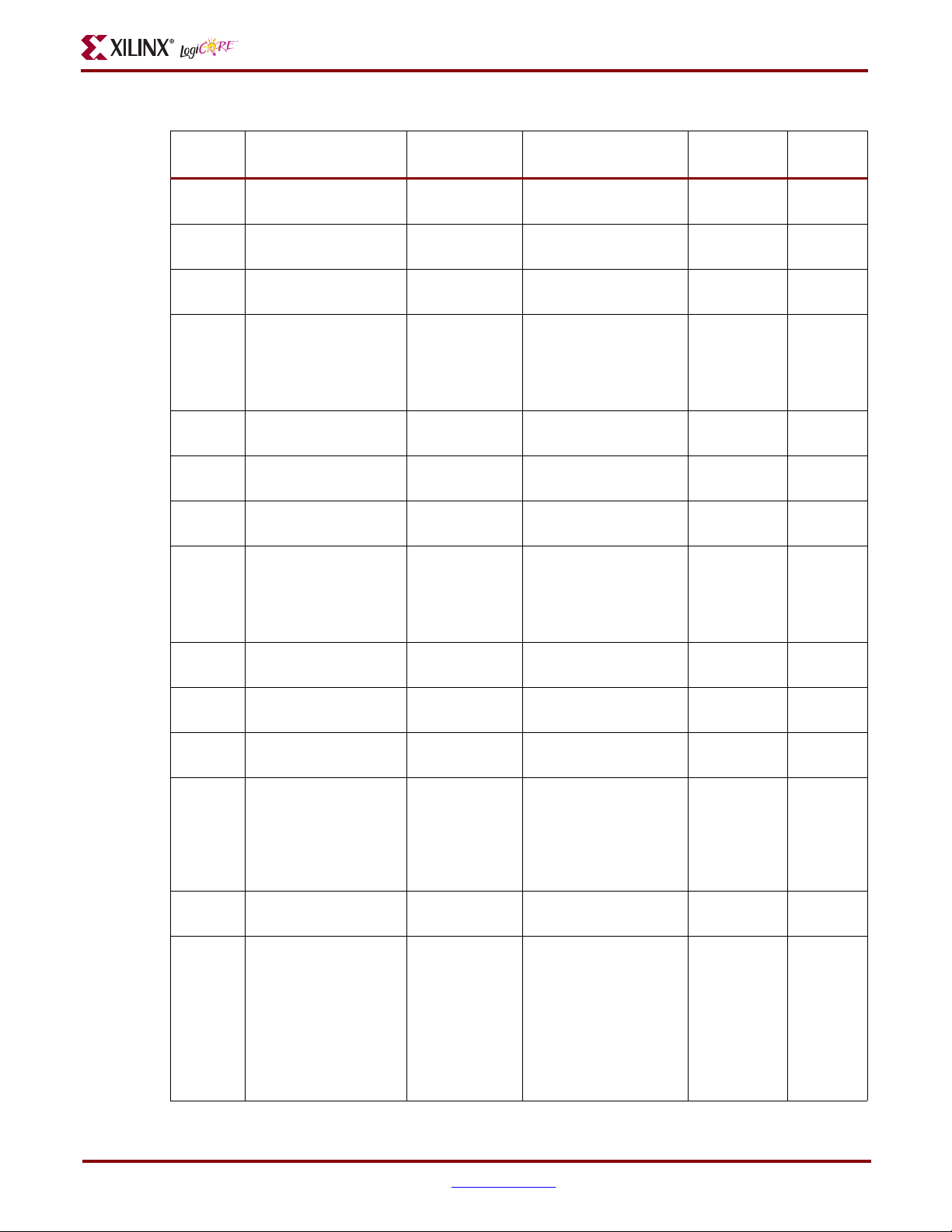

Page 9

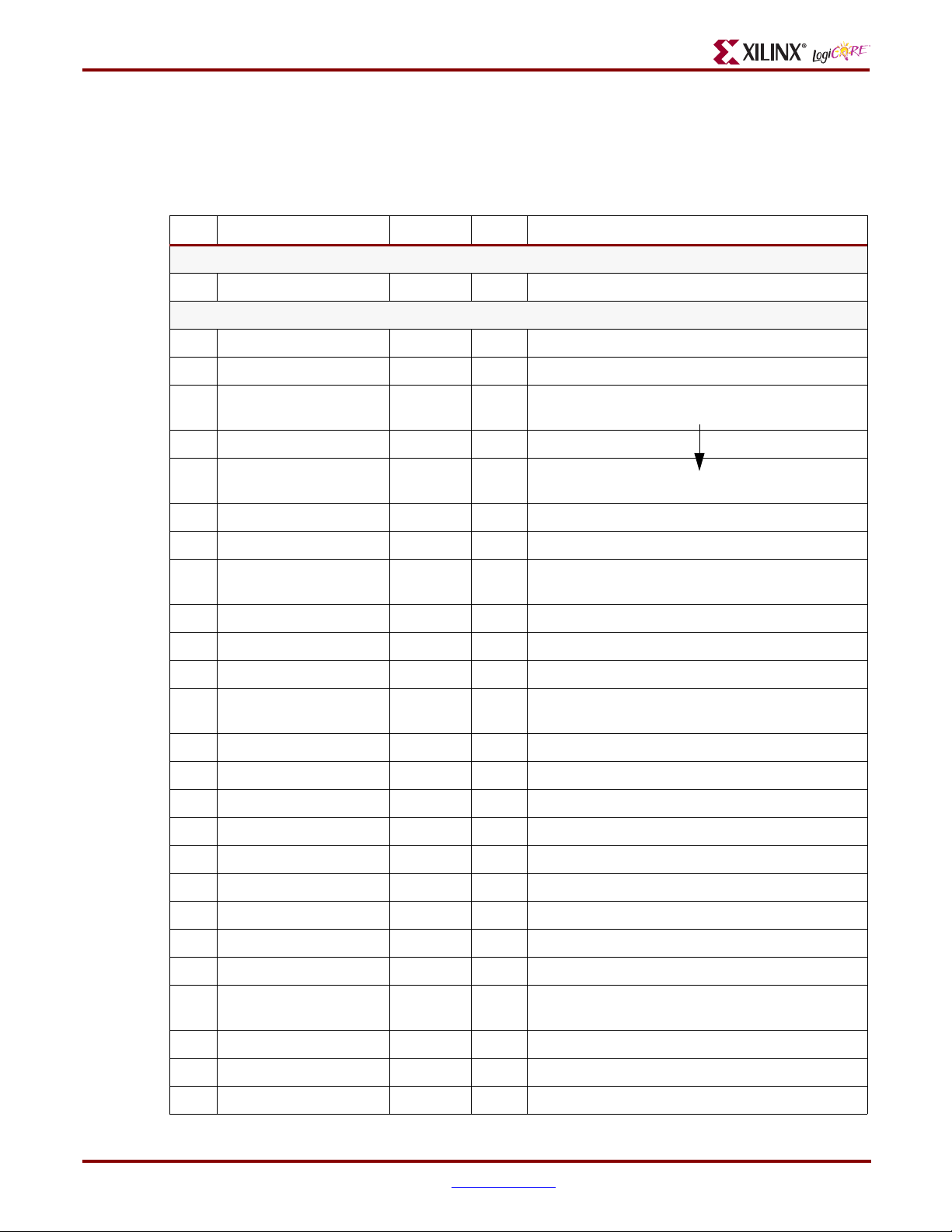

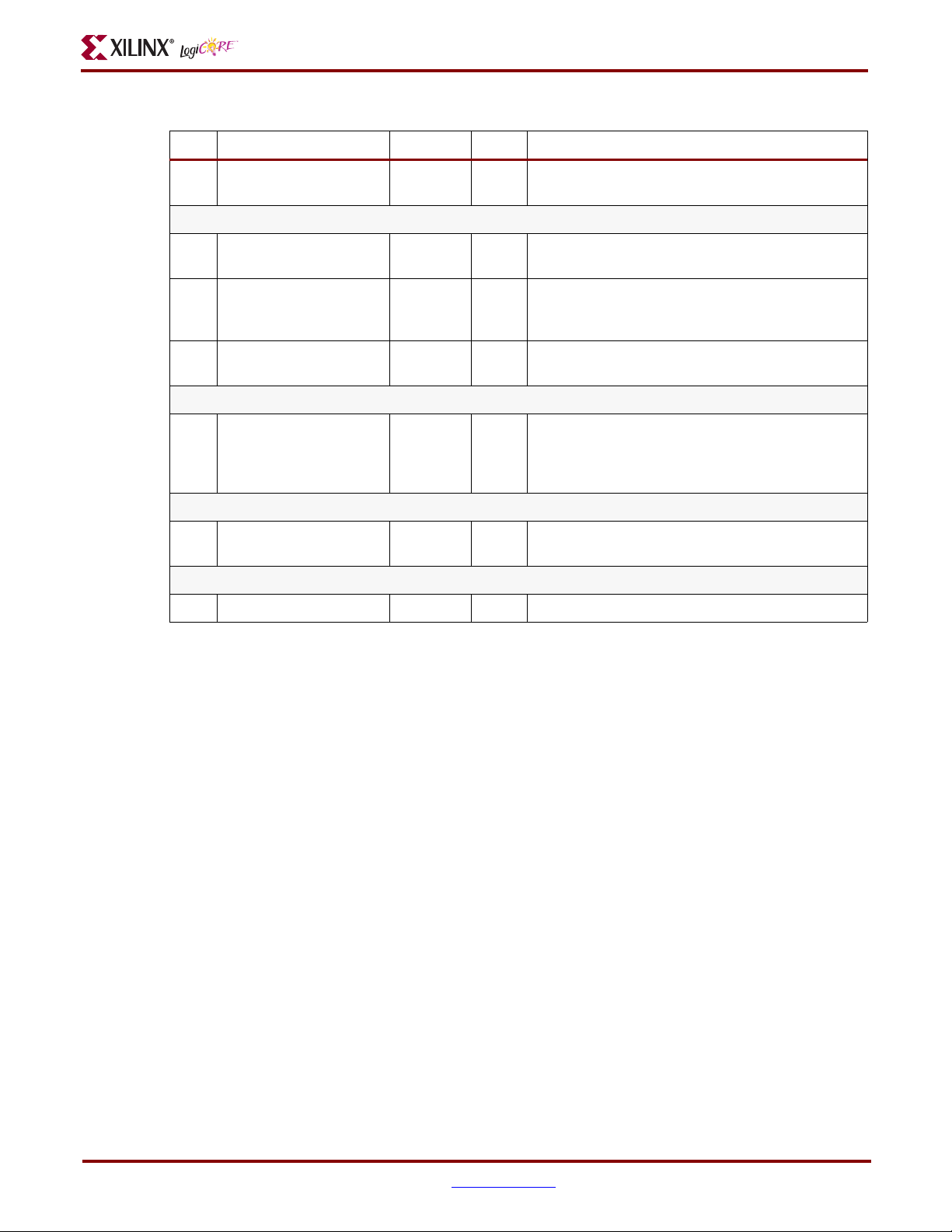

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

PLB PCI Full Bridge (v1.00a)

Generic

G13

G14 IPIF device 3 BAR C_IPIFBAR_3 Valid PLB address

G15

G16

G17

G18 IPIF device 4 BAR C_IPIFBAR_4 Valid PLB address

G19

G20

Feature /

Description

IPIF BAR 2 memory

designator

IPIF BAR high

address 3

PCI BAR to which IPIF

BAR 3 is mapped

unless

C_INCLUDE_BAROFF

SET_REG = 1.

IPIF BAR 3 memory

designator

IPIF BAR high

address 4

PCI BAR to which IPIF

BAR 4 is mapped

unless

C_INCLUDE_BAROFF

SET_REG = 1

Parameter

Name

C_IPIF_SPACE

TYPE_2

C_IPIFBAR_

HIGHADDR_3

C_IPIFBAR2

PCIBAR_3

C_IPIF_SPACE

TYPE_3

C_IPIFBAR_

HIGHADDR_4

C_IPIFBAR2

PCIBAR_4

Allowable Values

0 = I/O space

1 = Memory space

Valid PLB address

Vector of length

C_PLB_AWIDTH

0 = I/O space

1 = Memory space

Valid PLB address

Vector of length

C_PLB_AWIDTH

(1), (2)

(1), (2)

(1), (2)

(1), (2)

Default

Val ue

1 integer

0xFFFFFFFF

0x00000000

0xFFFFFFFF

1 integer

0xFFFFFFFF

0x00000000

0xFFFFFFFF

VHDL

Type

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

G21

G22 IPIF device 5 BAR C_IPIFBAR_5 Valid PLB address

G23

G24

G25

IPIF BAR 4 memory

designator

IPIF BAR high

address 5

PCI BAR to which IPIF

BAR 5 is mapped

unless

C_INCLUDE_BAROFF

SET_

REG = 1

IPIF BAR 5 memory

designator

C_IPIF_SPACE

TYPE_4

C_IPIFBAR_

HIGHADDR_5

Y

L

C_IPIFBAR2

PCIBAR_5

C_IPIF_SPACE

TYPE_5

0 = I/O space

1 = Memory space

ACCESS

Valid PLB address

Vector of length

C_PLB_AWIDTH

0 = I/O space

1 = Memory space

AR

1-3; Parameters listed

below corresponding to

E

G26 Number of PCI devices

C_PCIBAR_

NUM

unused BARs are

ignored, but must be

valid values. BAR label

0 is the required bar for

all values 1-3 and the

index increments from 0

as BARs are added

(1), (2)

(1), (2)

1 integer

0xFFFFFFFF

0x00000000

0xFFFFFFFF

1 integer

3 integer

std_logic_

vector

std_logic_

vector

std_logic_

vector

DS508 March 21, 2006 www.xilinx.com 9

Product Specification

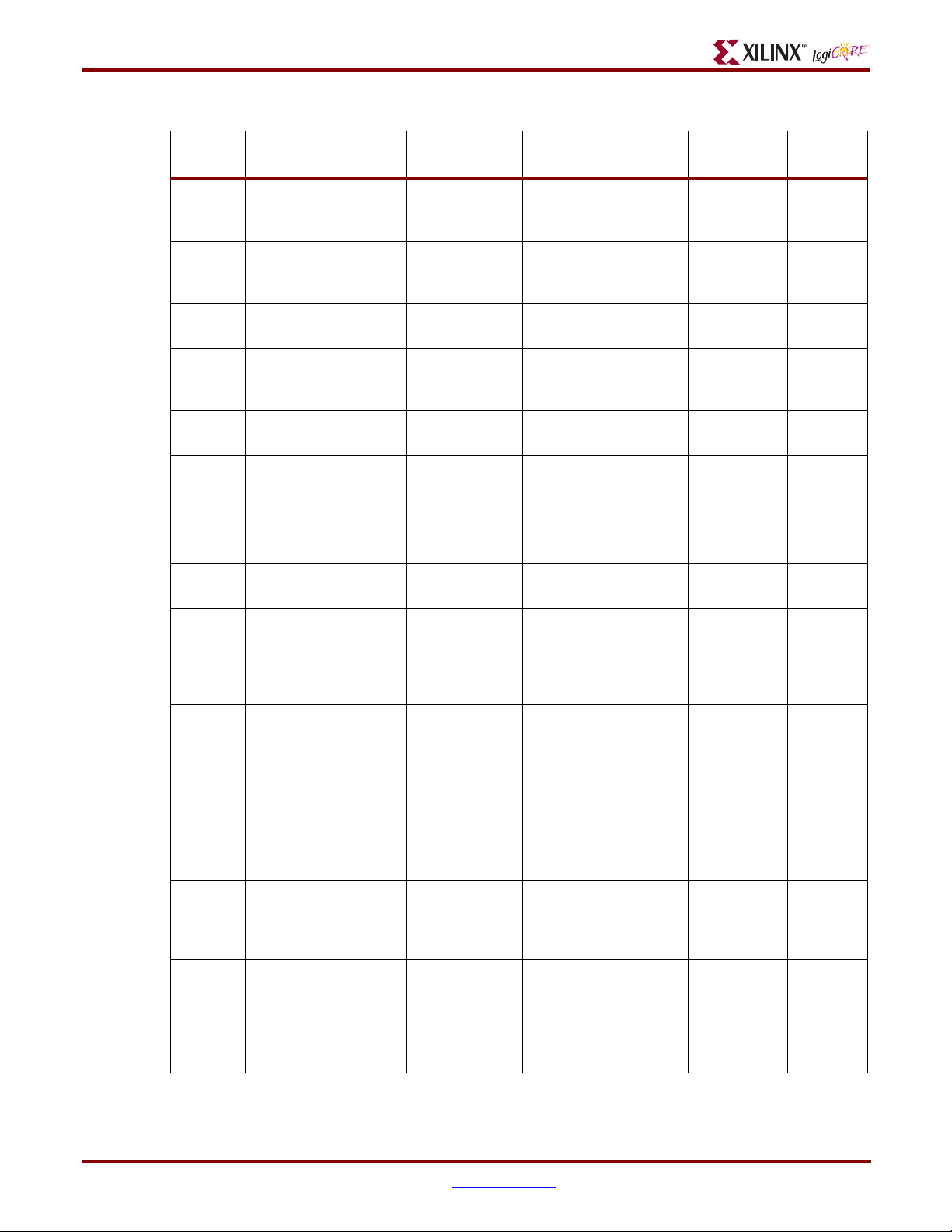

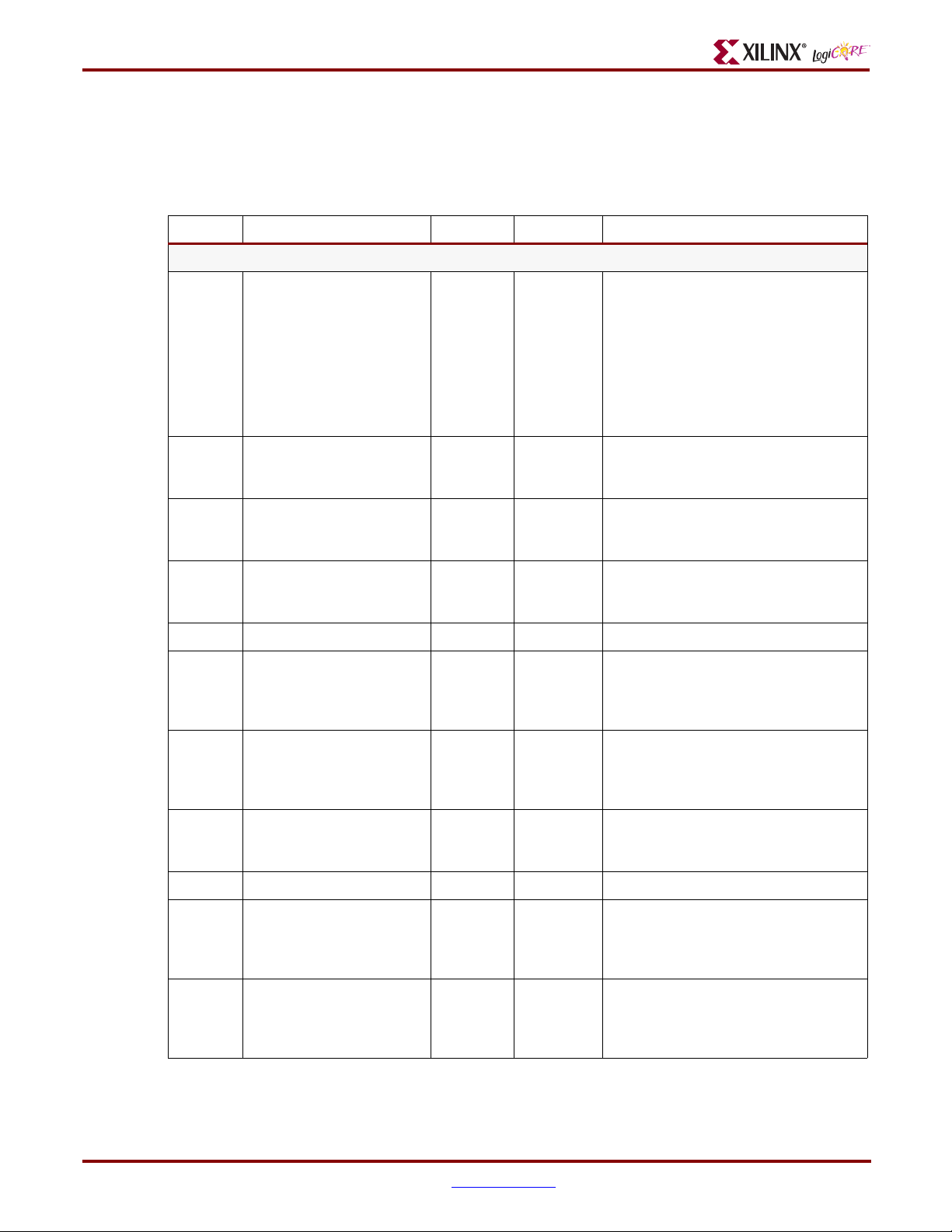

Page 10

PLB PCI Full Bridge (v1.00a)

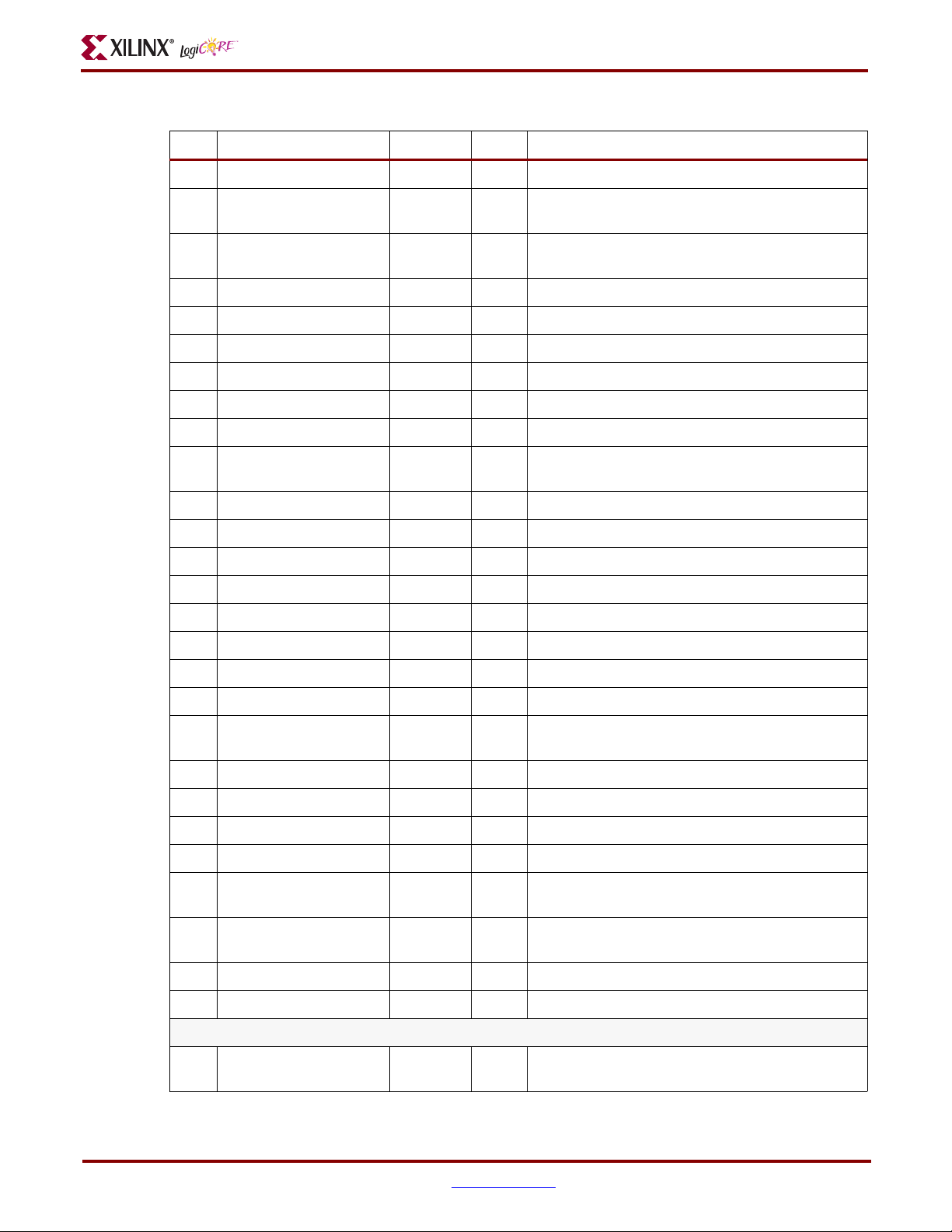

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

Generic

G27

G28

G29

G30

G31

G32

G33 PCI address bus width

G34 PCI data bus width

Feature /

Description

IPIF BAR to which PCI

BAR 0

is mapped

Power of 2 in the size in

bytes of PCI BAR 0

space

IPIF BAR to which PCI

BAR 1 is mapped

Power of 2 in the size in

bytes of PCI BAR 1

space

IPIF BAR to which PCI

BAR 2 is mapped

Power of 2 in the size in

bytes of PCI BAR 2

space

Parameter

Name

C_PCIBAR2

IPIFBAR_0

C_PCIBAR_

LEN_0

C_PCIBAR2IPI

FBAR_1

C_PCIBAR_

LEN_1

C_PCIBAR2

IPIFBAR_2

C_PCIBAR_

LEN_2

C_PCI_ABUS_

WIDTH

C_PCI_DBUS_

WIDTH

Allowable Values

Vector of length

C_PLB_AWIDTH

5 to 29 16 integer

Vector of length

C_PLB_AWIDTH

5 to 29 16 integer

Vector of length

C_PLB_AWIDTH

5 to 29 16 integer

32 32 integer

32 32 integer

Default

Val ue

0x00000000

0x00000000

0x00000000

VHDL

Type

std_logic_

vector

std_logic_

vector

std_logic_

vector

G35

G36

G37

G38

G39

Both PCI2IPIF FIFO

address bus widths.

Usable depth is

2^C_PCI2IPIF_FIFO_A

BUS_WIDTH - 3

Both IPIF2PCI FIFO

address bus widths.

Usable depth is

2^C_IPIF2PCI_FIFO_A

BUS_WIDTH - 3

Include explicit

instantiation of INTR_A

io-buffer (must be 1 to

include io-buffer)

Include explicit

instantiation of REQ_N

EARLY ACCESS

io-buffer (must be 1 to

include io-buffer)

Minimum PCI2IPIF

FIFO occupancy level

that triggers the bridge

to initiate a prefetch PCI

read of a remote PCI

agent

C_PCI2IPIF_

FIFO_ABUS_

WIDTH

C_IPIF2PCI_

FIFO_ABUS_

WIDTH

C_INCLUDE_

INTR_A_BUF

C_INCLUDE_

REQ_N_BUF

C_TRIG_PCI_

READ_OCC_

LEVEL

4-14 9 integer

4-14 9 integer

0 = not included

1 = included

0 = not included

1 = included

5 to the lesser of 24 or

the PCI2IPIF FIFO

DEPTH-3. PCI2IPIF

FIFO DEPTH given by

2^C_PCI2IPIF_FIFO_

ABUS_WIDTH

1 integer

1 integer

32 integer

10 www.xilinx.com DS508 March 21, 2006

Product Specification

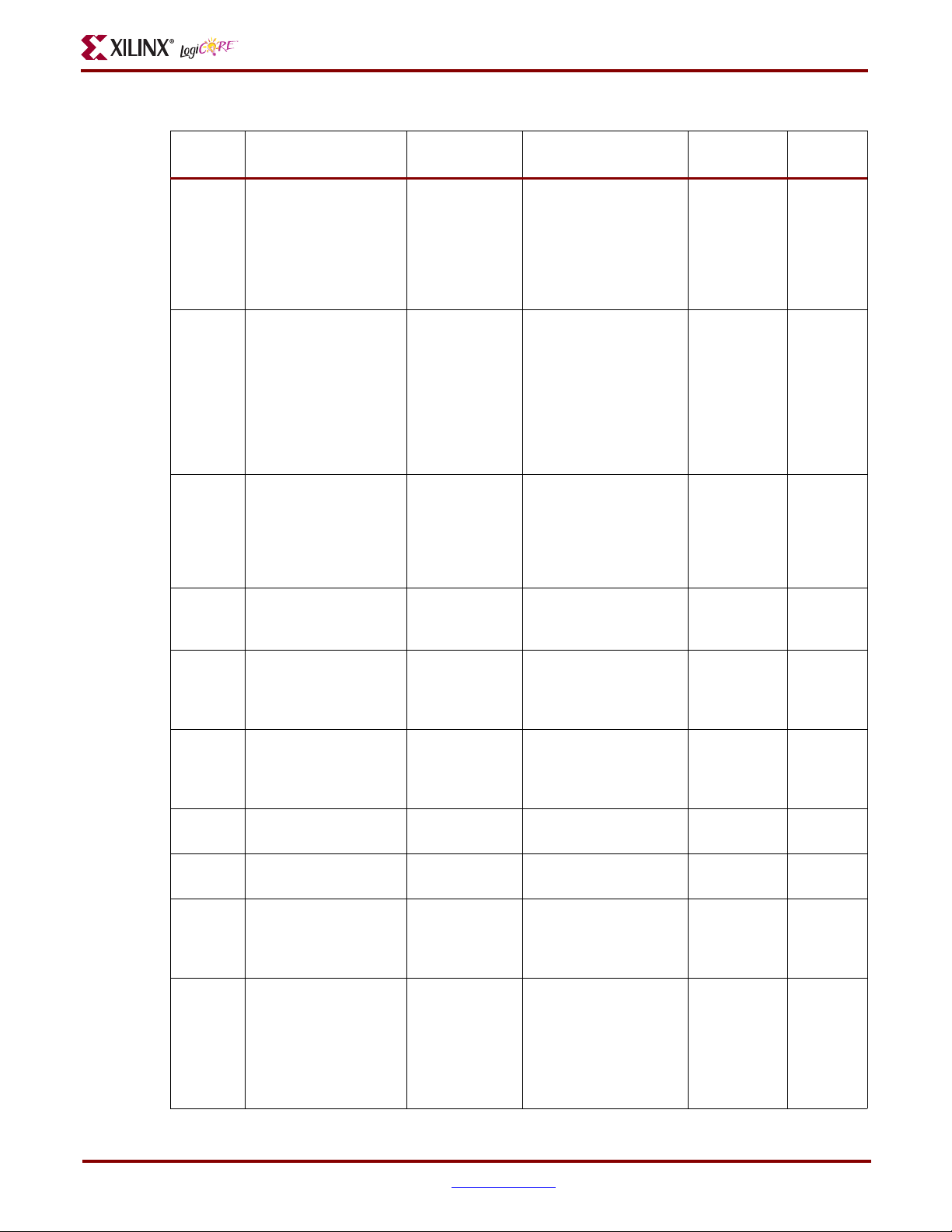

Page 11

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

PLB PCI Full Bridge (v1.00a)

Generic

G40

G41

G42

Feature /

Description

PCI2IPIF FIFO

occupancy level in

double words that

triggers the bridge to

initiate an IPIF burst

write to remote PLB

device

IPIF2PCI FIFO

occupancy level that

starts data transfer

(Both as initiator and

target on PCI) to PCI

agent with multiple data

phases per transfer

(must meet 16 PCI

period maximum).

Minimum IPIF2PCI

FIFO occupancy level

that triggers bridge to

initiate a prefetch IPIF

read of a remote PLB

slave

Parameter

Name

C_TRIG_IPIF_

WRBURST_

OCC_LEVEL

C_TRIG_PCI_

DATA_XFER_

OCC_LEVEL

C_TRIG_IPIF_

READ_OCC_

LEVEL

Allowable Values

2 to the lesser of 24 or

the PCI2IPIF FIFO

DEPTH-3. PCI2IPIF

FIFO DEPTH given by

2^C_PCI2IPIF_FIFO_A

BUS_WIDTH

2 to the lesser of 24 or

the IPIF2PCI FIFO

DEPTH-3. IPIF2PCI

FIFO DEPH given by

2^C_IPIF2PCI_FIFO_

ABUS_WIDTH

2 to the lesser of 24 or

the IPIF2PCI FIFO

DEPTH-3. IPIF2PCI

FIFO DEPH given by

2^C_IPIF2PCI_FIFO_

ABUS_WIDTH

Default

Val ue

8 integer

8 integer

16 integer

VHDL

Type

Number of PCI retry

G43

G44

G45

G46 Device base address

G47

G48

G49

attempts in IPIF

posted-write operations

Number of PCI clock

periods between retries

in posted- write

operations

Number of IPIF retry

attempts in

posted-write PCI

initiator operations

Device absolute high

address

Include the registers for

high-order bits to be

AR

substituted in

translation

E

Include the register for

local bridge device

number when

configuration

functionality

(C_INCLUDE_PCI_CO

NFIG =1) is included

C_NUM_PCI_R

ETRIES_IN_

WRITES

C_NUM_PCI_P

RDS_BETWN_

RETRIES_IN_

WRITES

C_NUM_IPIF_

RETRIES_IN_

Y

WRITES

L

C_BASE

ADDR

C_HIGHADDR Valid PLB address

C_INCLUDE_

BAROFFSET_

REG

C_INCLUDE_D

EVNUM_REG

Any integer 3 integer

Any integer 6 integer

ACCESS

Any integer 6 integer

Valid PLB address

1 = include

0 = exclude

1 = include

0 = exclude

(1), (2)

(1), (2)

0xFFFFFFFF

0x00000000

0 integer

0 integer

std_logic_

vector

std_logic_

vector

DS508 March 21, 2006 www.xilinx.com 11

Product Specification

Page 12

PLB PCI Full Bridge (v1.00a)

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

Generic

G50

G51

G52

G53

Feature /

Description

Number of IDELAY

controllers instantiated.

Ignored it not Virtex-4

Includes IDELAY

primitive on GNT_N.

Set by tcl-scripts and

ignored if not Virtex-4.

Provides a means for

BSB to pass LOC

coordinates for

IDELAYCTRLs for a

given board to

EDK and is optional for

user to set LOC

constraints. This

parameter has no

impact on bridge

functionality.

PCI Configuration

Space Header Device IDC_DEVICE_ID 16-bit vector 0x0000

Parameter

Name

C_NUM_

IDELAYCTRL

C_INCLUDE_

GNT_DELAY

C_IDELAY

CTRL_LOC

v3.0 Core Parameters Group

Allowable Values

2-6

(Virtex-4 only)

1=Include IDELAY

primitive

(Virtex-4 only)

0=No IDELAY primitive

See Device

Implementation section,

subsection Virtex-4

Support for allowed

values

Default

Val ue

2 integer

0 integer

NOT_SET string

VHDL

Type

std_logic_

vector

G54

G55

G56

G57

G58

G59

G60

PCI Configuration

Space Header Vendor

ID

PCI Configuration

Space Header Class

Code

PCI Configuration

Space Header Rev ID

PCI Configuration

Space Header

Subsystem ID

PCI Configuration

Space Header

Subsystem Vendor ID

EARLY ACCESS

PCI Configuration

Space Header

Maximum Latency

PCI Configuration

Space Header

Minimum Grant

C_VENDOR_

ID

C_CLASS_

CODE

C_REV_ID 8-bit vector 0x00

C_SUB

SYSTEM_ID

C_SUBSYSTE

M_VENDOR_

C_MAX_LAT 8-bit vector 0x0F

C_MIN_GNT 8-bit vector 0x04

Configuration

16-bit vector 0x0000

24-bit vector 0x000000

16-bit vector 0x0000

ID16-bit vector 0x0000

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

std_logic_

vector

12 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 13

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

PLB PCI Full Bridge (v1.00a)

Generic

G61

G62

G63

G64

G65

G66 PLB Address width

G67 PLB Data width

Feature /

Description

Include configuration

functionality via IPIF

transactions

Number of IDSEL

signals supported

PCI address bit that PCI

v3.0 core IDSEL is

connected to

PLB master ID bus

width (set automatically

by XPS)

Number of masters on

PLB bus (set

automatically by XPS)

Parameter

Name

C_INCLUDE_

PCI_CONFIG

C_NUM_

IDSEL

C_BRIDGE_

IDSEL_ADDR_

BIT

IPIF Parameters Group

C_PLB_MID_

WIDTH

C_PLB_NUM_

MASTERS

C_PLB_

AWIDTH

C_PLB_

DWIDTH

Allowable Values

0 = Not included

1 = Included

1 to 16 8 integer

31 down to 16

Must be <= 15 +

C_NUM_IDSEL.

AD(31 down to 0) index

labeling

log2(C_PLB_NUM_MA

STERS)

1-16 8 integer

32 (only allowed value 32 integer

64 (only allowed value 64 integer

Default

Val ue

1 integer

16 integer

3 integer

VHDL

Type

G68

Notes:

1. The range specified must comprise a complete, contiguous power of two range, such that the range = 2n and

the n least significant bits of the Base Address are zero.

2. The minimum address range specified by C_BASEADDR and C_HIGHADDR must be at least 0x1FF.

C_BASEADDR must be a multiple of the range, where the range is C_HIGHADDR - C_BASEADDR + 1.

Specifies the target

technology

C_FAMILY

See PLB IPIF data

sheet

virtex2 string

ACCESS

Y

L

AR

E

DS508 March 21, 2006 www.xilinx.com 13

Product Specification

Page 14

PLB PCI Full Bridge (v1.00a)

PLB PCI Bus Interface I/O Signals

The I/O signals for the PLB PCI Bridge are listed in Tab le 2. The interfaces referenced in this table are

shown in Figure 1 in the PLB PCI Bridge block diagram.

Table 2: PLB PCI Bridge I/O Signals

Port Signal Name Interface I/O Description

P1 IP2INTC_Irpt Internal O Interrupt from IP to the Interrupt Controller

P2 PLB_Clk PLB Bus I PLB main bus clock. See table note 1.

P3 PLB_Rst PLB Bus I PLB main bus reset. See table note 1.

PLB_ABus(0:C_PLB_

P4

AWIDTH-1)

P5 PLB_PAValid PLB Bus I

PLB_masterID(0:C_PLB

P6

_MID_WIDTH-1)

System Signals

PLB Signals

PLB Bus I Note 1 applies from P4 to P53.

PLB Bus I

P7 PLB_abort PLB Bus I

P8 PLB_RNW PLB Bus I

PLB_BE(0:[C_PLB_DWI

P9

DTH/8]-1)

P10 PLB_MSize(0:1) PLB Bus I

P11 PLB_size(0:3) PLB Bus I

P12 PLB_type(0:2) PLB Bus I

PLB_wrDBus(0:C_PLB_

P13

DWIDTH-1)

P14 PLB_wrBurst PLB Bus I

P15 PLB_rdBurst PLB Bus I

P16 Sl_addAck PLB Bus O

P17 Sl_SSize(0:1) PLB Bus O

P18 Sl_wait PLB Bus O

P19 Sl_rearbitrate PLB Bus O

P20 Sl_wrDAck PLB Bus O

P21 Sl_wrComp PLB Bus O

EARLY ACCESS

PLB Bus I

PLB Bus I

P22 Sl_wrBTerm PLB Bus O

Sl_rdDBus(0:C_PLB_D

P23

WIDTH-1)

P24 Sl_rdWdAddr(0:3) PLB Bus O

P25 Sl_rdDAck PLB Bus O

P26 Sl_rdComp PLB Bus O

14 www.xilinx.com DS508 March 21, 2006

PLB Bus O

Product Specification

Page 15

PLB PCI Full Bridge (v1.00a)

Table 2: PLB PCI Bridge I/O Signals (Contd)

Port Signal Name Interface I/O Description

P27 Sl_rdBTerm PLB Bus O

Sl_MBusy(0:C_PLB_NU

P28

M_MASTERS-1)

Sl_MErr(0:C_PLB_NUM

P29

_MASTERS-1)

P30 PLB_MAddrAck PLB Bus I

P31 PLB_MSSize(0:1) PLB Bus I

P32 PLB_MRearbitrate PLB Bus I

P33 PLB_MBusy PLB Bus I

P34 PLB_MErr PLB Bus I

P35 PLB_MWrDAck PLB Bus I

PLB_MRdDBus(0:C_PL

P36

B_DWIDTH-1)

PLB Bus O

PLB Bus O

PLB Bus I

P37 PLB_MRdWdAddr(0:3) PLB Bus I

P38 PLB_MRdDAck PLB Bus I

P39 PLB_MRdBTerm PLB Bus I

P40 PLB_MWrBTerm PLB Bus I

P41 M_request PLB Bus O

P42 M_priority PLB Bus O

P43 M_buslock PLB Bus O

P44 M_RNW PLB Bus O

M_BE(0:[C_PLB_DWIDT

P45

H/8]-1)

P46 M_MSize(0:1) PLB Bus O

P47 M_size(0:3) PLB Bus O

P48 M_type(0:2) PLB Bus O

P49 M_abort PLB Bus O

M_ABus(0:C_PLB_AWI

P50

DTH-1)

P51

M_wrDBus(0:C_PLB_D

WIDTH-1)

AR

PLB Bus O

Y

L

PLB Bus O

PLB Bus O

ACCESS

P52 M_wrBurst PLB Bus O

P53 M_rdBurst PLB Bus O Table note 1 applies from P53 to P4.

P54

DS508 March 21, 2006 www.xilinx.com 15

Product Specification

E

AD[C_PCI_DBUS_WIDT

H-1:0]

PCI Address and Data Path Signals

PCI Bus I/O Time-multiplexed address and data bus

Page 16

PLB PCI Full Bridge (v1.00a)

Table 2: PLB PCI Bridge I/O Signals (Contd)

Port Signal Name Interface I/O Description

CBE[(C_PCI_DBUS_WI

P55

DTH/8)-1:0]

PCI Bus I/O Time-multiplexed bus command and byte enable bus

P56 PA R PCI Bus I/O

PCI Transaction Control Signals

P57 FRAME_N PCI Bus I/O Driven by an initiator to indicate a bus transaction

P58 DEVSEL_N PCI Bus I/O

P59 TRDY_N PCI Bus I/O

P60 IRDY_N PCI Bus I/O

P61 STOP_N PCI Bus I/O

P62 IDSEL PCI Bus I

PCI Interrupt Signals

P63 INTR_A PCI Bus O

PCI Error Signals

P64 PERR_N PCI Bus I/O

Generates and checks even parity across AD and

CBE

Indicates that a target has decoded the address

presented during the address phase and is claiming

the transaction

Indicates that the target is ready to complete the

current data phase

Indicates that the initiator is ready to complete the

current data phase

Indicates that the target has requested to stop the

current transaction

Indicates that the interface is the target of a

configuration cycle

Indicates that LogiCORE PCI interface requests an

interrupt

Indicates that a parity error was detected while the

LogiCORE PCI interface was the target of a write

transfer or the initiator of a read transfer

P65 SERR_N PCI Bus I/O

PCI Arbitration Signals

P66 REQ_N PCI Bus O

P67 GNT_N PCI Bus I

PCI System Signals

EARLY ACCESS

P68 RST_N PCI Bus I

P69 PCLK PCI Bus I PCI bus clock signal

PCI Bus Internal Arbiter Signals

P70 REQ_N_toArb Internal O

P71 FRAME_I Internal O

Indicates that a parity error was detected during an

address cycle, except during special cycles

Indicates to the arbiter that the LogiCORE PCI

initiator requests access to the bus

Indicates that the arbiter has granted the bus to the

LogiCORE PCI initiator

PCI bus reset signal is used to bring PCI-specific

registers, sequences, and signals to a consistent

state

Input from PCI Bus REQ_N available at top-level as

output from bridge

Input from PCI Bus FRAME_N availalble at top-level

as output from bridge

16 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 17

PLB PCI Full Bridge (v1.00a)

Table 2: PLB PCI Bridge I/O Signals (Contd)

Port Signal Name Interface I/O Description

P72 IRDY_I Internal O

PCI 64-bit Extensions (reserved for future support of 64-bit PCI)

P73 PA R6 4 PCI Bus I/O

P74 ACK64_N PCI Bus I/O

P75 REQ64_N PCI Bus I/O

User Asserted PCI Interrupt Signal

P76 Bus2PCI_INTR Internal I

Virtex-4 Only, IDELAY Clock

P77 RCLK Internal I

PCI Bus Monitoring Debug Vector Signal

P78 PCI_monitor(0:47) Internal O Output vector to monitor PCI Bus.

Input from PCI Bus IRDY_N availalble at top-level as

output from bridge

Generates and checks even parity across AD[63:32]

and CBE[7:4]

Indicates that a target has decoded the address

presented during the address phase and is claiming

the transaction as a 64-bit target

Driven by the initiator to indicate a 64-bit bus

transaction

Active high signal to asynchronously assert INTR_A.

Inverted signal drives INTR_N user application input

of v3.0 core. See v3.0 core documents for details on

INTR_N functionality.

200 MHz clock input to IDELAY elements of Virtex-4

buffers. Ignored if not Virtex-4 architecture.

Notes:

1. This signal’s function and timing are defined in the IBM 64-Bit Processor Local Bus Architecture Specification

Version 3.5.

The REQ_N_toArb facilitates an interface to an internal (i.e., in the FPGA) pci arbiter. The v3.0 input

buffer for GNT_N is removed. This allows an internal connection to GNT_N when using an internal

arbiter. When an external arbiter is used, GNT_N_fromArb is not needed.

REQ_N is a 3-stated I/O. The REQ_N_toArb port is available to maintain a v3.0 core-like interface. The

REQ_N_toArb port allows the use of the same port list for PCI bus interface and the ucf-file for the v3.0

core is the standard file.

The v3.0 core requires that GNT_N be asserted for two clock cycles to initiate a transaction upon

receiving grants.

Bus2PCI_INTR is an active High signal. It allows asynchronous assertion of INTR_A on the PCI bus.

The signal is driven by user supplied circuitry (i.e., a PLB GPIO IP core). If it is not connected in the

mhs-file, then EDK 8.1 tools will tie the signal Low. The signal is inverted in the PLB PCI Bridge and

AND’d with the bridge interrupt signal (active Low) to drive the INTR_N input of the v3.0 core. This

signal then asynchronously drives INTR_A on the PCI bus. See the v3.0 core specifications on INTR_A

behavior relative to v3.0 input INTR_N. The v3.0 core command register interrupt disable bit controls the

INTR_A operation and v3.0 core status register Interrupt status bit flags if v3.0 core INTR_A is asserted.

E

AR

Y

L

ACCESS

DS508 March 21, 2006 www.xilinx.com 17

Product Specification

Page 18

PLB PCI Full Bridge (v1.00a)

Port and Parameter Dependencies

The dependencies between the IPI v3.0 Bridge design port (i.e., I/O signals) and parameters are shown

in

Tab le 1.

Table 3: PLB PCI Bridge Parameters-Port Dependencies

Generic Parameter Affects Depends Description

G1 C_IPIFBAR_NUM G5-G25

G2 C_IPIFBAR_0 G3 G3

Bridge Features Parameter Group

The set of PLB/IPIF BAR-parameters of

N = 0 to C_IPIFBAR_NUM-1 are

meaningful. When C_IPIFBAR_NUM <

6, the parameters of N =

C_IPIFBAR_NUM up to and including 5

have no effect. If C_IPIFBAR_NUM = 6,

the set of PLB/IPIF BAR-parameters of N

= 0 to 5 are all meaningful (i.e., G2-G25

are meaningful).

G2 to G3 define range in PLB-memory

space that is responded to by this device

(IPIF BAR)

G2 to G3 define range in PLB-memory

G3 C_IPIFBAR_HIGHADDR_0 G2 G2

G4 C_IPIFBAR2PCIBAR_0

G5 C_IPIF_SPACETYPE_0

G6 C_IPIFBAR_1 G7 G1 and G7

G7 C_IPIFBAR_HIGHADDR_1 G6 G1 and G6

G8 C_IPIFBAR2PCIBAR_1

G9 C_IPIF_SPACETYPE_1 G1 Meaningful only if G1>1

G2, G3 and

G48

G1, G6, G7

and G48

EARLY ACCESS

G10 C_IPIFBAR_2 G11

G1 and

G11

space that is responded to by this device

(IPIF BAR)

Meaningful only if G48 = 0 and in this

case only high-order bits that are the

same in G2 and G3 are meaningful.

Meaningful only if G1>1, then G6 to G7

define the range in PLB-memory space

that is responded to by this device (IPIF

BAR)

Meaningful only if G1>1, then G6 to G7

define the range in PLB-memory space

that is responded to by this device (IPIF

BAR)

Meaningful only if G48 = 0 and G1>1. In

this case only high-order bits that are the

same in G6 and G7 are meaningful.

Meaningful only if G1>2, then G10 to

G11 define the range in PLB-memory

space that is responded to by this device

(IPIF BAR)

Meaningful only if G1>2, then G10 to

G11 C_IPIFBAR_HIGHADDR_2 G10

18 www.xilinx.com DS508 March 21, 2006

G1 and

G10

G11 define the range in PLB-memory

space that is responded to by this device

(IPIF BAR)

Product Specification

Page 19

PLB PCI Full Bridge (v1.00a)

Table 3: PLB PCI Bridge Parameters-Port Dependencies (Contd)

Generic Parameter Affects Depends Description

G1, G10,

G12 C_IPIFBAR2PCIBAR_2

G13 C_IPIF_SPACETYPE_2 G1 Meaningful only if G1>2

G14 C_IPIFBAR_3 G15

G15 C_IPIFBAR_HIGHADDR_3 G14

G16 C_IPIFBAR2PCIBAR_3

G17 C_IPIF_SPACETYPE_3 G1 Meaningful only if G1>3

G18 C_IPIFBAR_4 G19

G19 C_IPIFBAR_HIGHADDR_4 G18

G11 and

G48

G1 and

G15

G1 and

G14

G1, G14,

G15 and

G48

G1 and

G19

G1 and

G18

Meaningful only if G48 = 0 and G1>2. In

this case only high-order bits that are the

same in G10 and G11 are meaningful.

Meaningful only if G1>3, then G14 to

G15 define the range in PLB-memory

space that is responded to by this device

(IPIF BAR)

Meaningful only if G1>3, then G14 to

G15 define the range in PLB-memory

space that is responded to by this device

(IPIF BAR)

Meaningful only if G48 = 0 and G1>3. In

this case only high-order bits that are the

same in G14 and G15 are meaningful.

Meaningful only if G1>4, then G18 to

G19 define the range in PLB-memory

space that is responded to by this device

(IPIF BAR)

Meaningful only if G1>4, then G18 to

G19 define the range in PLB-memory

space that is responded to by this device

(IPIF BAR)

G1, G18,

G20 C_IPIFBAR2PCIBAR_4

G21 C_IPIF_SPACETYPE_4 G1 Meaningful only if G1>4

G22 C_IPIFBAR_5 G23

Y

G19 and

G48

ACCESS

G1 and

G23

L

G23 C_IPIFBAR_HIGHADDR_5 G22

G24 C_IPIFBAR2PCIBAR_5

G25 C_IPIF_SPACETYPE_5 G1 Meaningful only if G1=6

E

AR

G1 and

G22

G1, G22,

G23 and

G48

Meaningful only if G48 = 0 and G1>4. In

this case only high-order bits that are the

same in G6 and G7 are meaningful.

Meaningful only if G1=6, then G6 to G7

define the range in PLB-memory space

that is responded to by this device (IPIF

BAR)

Meaningful only if G1=6, then G6 to G7

define the range in PLB-memory space

that is responded to by this device (IPIF

BAR)

Meaningful only if G48 = 0 and G1=6. In

this case only high-order bits that are the

same in G22 and G23 are meaningful.

DS508 March 21, 2006 www.xilinx.com 19

Product Specification

Page 20

PLB PCI Full Bridge (v1.00a)

Table 3: PLB PCI Bridge Parameters-Port Dependencies (Contd)

Generic Parameter Affects Depends Description

G26 C_PCIBAR_NUM G27-G32

The set of PCI/v3.0 BAR-parameters of

N = 0 to C_PCIBAR_NUM-1 are

meaningful and the parameters of N =

C_PCIBAR_NUM up to and including 2

have no effect. If C_PCIBAR_NUM = 3,

the set of PCI/v3.0 BAR-parameters of N

= 0 to 2 are all meaningful (i.e., G27-G32

are meaningful)

G27 C_PCIBAR2IPIFBAR_0 G28

G28 C_PCIBAR_LEN_0

G29 C_PCIBAR2IPIFBAR_1 G30

G30 C_PCIBAR_LEN_1 Not meaningful if G26=1

G31 C_PCIBAR2IPIFBAR_2 G32

G32 C_PCIBAR_LEN_2 Not meaningful if G26=1-2

G33 C_PCI_ABUS_WIDTH Only 1 setting

G34 C_PCI_DBUS_WIDTH Only 1 setting

G35

G36

G37

G38 C_INCLUDE_REQ_N_BUF P66

C_PCI2IPIF_FIFO_ABUS_

WIDTH

C_IPIF2PCI_FIFO_ABUS_

WIDTH

C_INCLUDE_INTR_A_

BUF

P63

Only the high-order bits above the length

defined by G28 are meaningful

Only the high-order bits above the length

defined by G30 are meaningful. Not

meaningful if G26=1

Only the high-order bits above the length

defined by G30 are meaningful. Not

meaningful if G26=1-2

If G37 = 0, an io-buffer for P63 is not

explicitly instantiated

If G38 = 0, an io-buffer for P66 is not

explicitly instantiated

Must be set to 5 to the lesser of 24 or the

G39

G40

G41

G42

20 www.xilinx.com DS508 March 21, 2006

C_TRIG_PCI_READ_OCC

_LEVEL

C_TRIG_IPIF_

EARLY ACCESS

WRBURST_OCC_LEVEL

C_TRIG_PCI_DATA_XFER

_OCC_LEVEL

C_TRIG_IPIF_READ_OCC

_LEVEL

G35

G35

G36

G36

PCI2IPIF FIFO DEPTH-1 where the

PCI2IPIF FIFO-1 depth is given by

2^G35

Must be set to 2 to the lesser of 24 or the

PCI2IPIF FIFO DEPTH-1 where the

PCI2IPIF FIFO-1 depth is given by

2^G35

Must be set to 2 to the lesser of 24 or the

IPIF2PCI FIFO DEPTH-3 where

IPIF2PCI FIFO DEPTH given by 2^G36

Must be set to 1 to the lesser of 24 or the

IPIF2PCI FIFO DEPTH-1 where

IPIF2PCI FIFO DEPTH given by 2^G36

Product Specification

Page 21

PLB PCI Full Bridge (v1.00a)

Table 3: PLB PCI Bridge Parameters-Port Dependencies (Contd)

Generic Parameter Affects Depends Description

G43

G44

G45

G46 C_BASEADDR G47 G47

G47 C_HIGHADDR G46 G46

G48

G49

G50 C_NUM_IDELAYCTRL G68 If G68 ≠ Virtex-4, G50 has no meaning

C_NUM_PCI_RETRIES_IN

_WRITES

C_NUM_PCI_PRDS_BET

WN_RETRIES_IN_

WRITES

C_NUM_IPIF_RETRIES_

IN_WRITES

C_INCLUDE_BAROFFSET

_REG

C_INCLUDE_DEVNUM_

REG

G4, G8,

G12, G16,

G20 and

G24

G63 G61, G62

G1

G46 to G47 define range in PLB-memory

space that is responded to by PLB PCI

bridge register address space

G46 to G47 define range in PLB-memory

space that is responded to by PLB PCI

bridge register address space

If G48=1, G4, G8, G12, G16, G20 and

G24 have no meaning. The number of

registers included is set by G1

If G61=0, G49 has no meaning. If G49

and G61=1, G63 has no meaning.

Meaningful bits in the Device Number

register are defined by G62

G51 C_INCLUDE_GNT_DELAY G68 If G68 ≠ Virtex-4, G51 has no meaning

If G68 ≠ Virtex-4, G52 has no meaning. If

G52 C_IDELAYCTRL_LOC

G53 C_DEVICE_ID

G54 C_VENDOR_ID

G55 C_CLASS_CODE

G56 C_REV_ID

G57 C_SUBSYSTEM_ID

G58

G59 C_MAX_LAT

G60 C_MIN_GNT

G61

C_SUBSYSTEM_VENDOR

_ID

AR

E

C_INCLUDE_PCI_

CONFIG

G50 and

G68

ACCESS

v3.0 Core Parameters Group

Y

L

Configuration

G62, G63,

P62

G68=Virtex-4, G52 must include the

number of LOC coordinates specified by

G50

If G61=1, signal P62 has an internal

connection and the top-level port P62

has no internal connection

DS508 March 21, 2006 www.xilinx.com 21

Product Specification

Page 22

PLB PCI Full Bridge (v1.00a)

Table 3: PLB PCI Bridge Parameters-Port Dependencies (Contd)

Generic Parameter Affects Depends Description

G62 C_NUM_IDSEL

G63

G64 C_PLB_MID_WIDTH

G65 C_PLB_NUM_MASTERS

G66 C_PLB_AWIDTH

C_BRIDGE_IDSEL_ADDR

_BIT

G49 and

G63

G62

IPIF Parameters Group

G61 and

G63

G49, G61

and G62

If G61=0, G62 has no meaning. If

G61=1, G62 sets the number of devices

supported in configuration operations.

Must be sufficiently large to include the

address bit defined by G63. If G49=1,

G62 restricts the allowed values that are

meaningful in the Device Number

Register

If G61=0 or G49=1, G63 has no

meaning. If G61=1 and G49=0, G63

must be consistent with the setting of

G62

G67 C_PLB_DWIDTH

G68 C_FAMILY G50-52

If G68 ≠ Virtex-4, G50-52 have no

meanings.

Supported PCI Bus Commands

The list of commands supported by the LogiCORE PCI interface is provided in Tab le 4.

Table 4: Supported PCI Bus Commands

Command PLB PCI Bridge

Code Name Ta rget Initiator

0000 Interrupt Acknowledge No No

0001 Special Cycle No No

0010 I/O Read No Ye s

0011 I/O Write No Ye s

0100 Reserved Ignore Ignore

0101 Reserved Ignore Ignore

0110 Memory Read Ye s Ye s

0111 Memory Write Ye s Ye s

1000 Reserved Ignore Ignore

EARLY ACCESS

1001 Reserved Ignore Ignore

1010 Configuration Read Ye s Optional

1011 Configuration Write Ye s Optional

1100 Memory Read Multiple Ye s Ye s

22 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 23

PLB PCI Full Bridge (v1.00a)

Table 4: Supported PCI Bus Commands

1101 Dual Address Cycle Ignore No

1110 Memory Read Line Ye s No

1111 Memory Write Invalidate Ye s No

PLB PCI Bridge Register Descriptions

The PLB PCI Bridge contains addressable registers for read/write operations as shown in Tab le 5. The

base address for these registers is set by the base address parameter (C_BASEADDR). The address of

each register is then calculated by an offset to the base address as shown in

in the user area of the PCI configuration header are mirrored in the IPIF register space as read-only

registers; this is included for debug utility. The registers that exist in a given PLB PCI bridge depend on

the configuration of the bridge.

Table 5: PLB PCI Bus Interface Registers

Register Name PLB Address Access

Device Interrupt Status Register (ISR) C_BASEADDR + 0x00 Read/TOW

Tab le 5. Registers that reside

Device Interrupt Pending Register (IPR) C_BASEADDR + 0x04 Read/Write

Device Interrupt Enable Register (IER) C_BASEADDR + 0x08 Read/Write

Device Interrupt ID (IID) C_BASEADDR + 0x18 Read

Global Interrupt Enable Register (GIE) C_BASEADDR + 0x1C Read/Write

Bridge Interrupt Register C_BASEADDR + 0x20 Read/TOW

Bridge Interrupt Enable Register C_BASEADDR + 0x28 Read/Write

Reset Module C_BASEADDR + 0x80 Read/Write

Configuration Address Port C_BASEADDR + 0x10C Read/Write

Configuration Data Port C_BASEADDR + 0x110 Read/Write

Bus Number/Subordinate Bus Number C_BASEADDR + 0x114 Read/Write

IPIFBAR2PCIBAR_0 high-order bits C_BASEADDR + 0x180 Read/Write

IPIFBAR2PCIBAR_1 high-order bits C_BASEADDR + 0x184 Read/Write

IPIFBAR2PCIBAR_2 high-order bits C_BASEADDR + 0x188 Read/Write

IPIFBAR2PCIBAR_3 high-order bits C_BASEADDR + 0x18C Read/Write

IPIFBAR2PCIBAR_4 high-order bits C_BASEADDR + 0x190 Read/Write

IPIFBAR2PCIBAR_5 high-order bits C_BASEADDR + 0x194 Read/Write

Host Bridge device number C_BASEADDR + 0x198 Read/Write

AR

Y

L

ACCESS

E

DS508 March 21, 2006 www.xilinx.com 23

Product Specification

Page 24

PLB PCI Full Bridge (v1.00a)

Register and Parameter Dependencies

The addressable registers in the PLB PCI Bridge depend on the parameter settings shown in Tab le 6.

Table 6: Register and Parameter Dependencies

Device Interrupt Status Register (ISR) Always present

Device Interrupt Pending Register (IPR) Always present

Device Interrupt Enable Register (IER) Always present

Device Interrupt ID (IID) Always present

Global Interrupt Enable Register (GIE) Always present

Bridge Interrupt Register Always present

Bridge Interrupt Enable Register Always present

Reset Module Always present

Configuration Address Port Present only if G61=1

Configuration Data Port Present only if G61=1

Register Name Parameter Dependence

Bus Number/Subordinate Bus Number Present only if G61=1

IPIFBAR2PCIBAR_0 High-Order Bits Present only if G48=1

IPIFBAR2PCIBAR_1 High-Order Bits Present only if G1>1 and G48=1

IPIFBAR2PCIBAR_2 High-Order Bits Present only if G1>2 and G48=1

IPIFBAR2PCIBAR_3 High-Order Bits Present only if G1>3 and G48=1

IPIFBAR2PCIBAR_4 High-Order Bits Present only if G1>4 and G48=1

IPIFBAR2PCIBAR_5 High-Order Bits Present only if G1=6 and G48=1

Host Bridge Device Number Present only if G49=1

PLB PCI Bridge Interrupt Registers Descriptions

The interrupt module registers are always included in the bridge.

Interrupt Module Specifications

The interrupt registers are in the interrupt module that is instantiated in the IPIF module of the PLB PCI

Bridge. Details on the IPIF interrupt module including discussion of ISR, IPR, IER and IID are in the

PLB IPIF Interrupt Product Specification in the Processor IP Reference Guide.

EARLY ACCESS

24 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 25

PLB PCI Full Bridge (v1.00a)

Global Interrupt Enable Register Description

A global enable is provided to globally enable or disable interrupts from the PCI device. This bit is

AND’d with the output to the interrupt controller. Bit assignment is shown in

other registers, this bit is the MSB on the PLB. This bit is read/write and cleared upon reset.

Table 7: Global Interrupt Enable Register Bit Definitions (Bit assignment assumes 32-bit bus)

Ta bl e 7. Unlike most

Bit(s) Name Access

Interrupt Global

0

1-31 Read 0x0 Unassigned-

Bridge Interrupt Register Description

The PLB PCI Bridge has twelve interrupt conditions. The Bridge Interrupt Enable Register enables each

interrupt independently. Bit assignment in the Interrupt register for a 32-bit data bus is shown in

Tab le 8. The interrupt register is read-only and bits are toggled by writing a 1 to the bit(s) being cleared.

All bits are cleared upon reset. For more information, see the PLB IPIF Interrupt Product Specification;

the module is labeled PLB Interrupt module, but is used in the PLB IPIF.

Table 8: Bridge Interrupt Register Bit Definitions (Bit Assignment Assumes 32-bit Bus)

Bit(s) Name Access

0-18 Read 0x0 Unassigned

19

20

21 Reserved 0x0 Reserved

22

23

Enable

PCI Initiator

Write SERR

PCI Initiator

Read SERR

PLB Master

Write Retry

Timeout

PLB Master

Write Retry

Disconnect

Read/Write 0x0

Read/Write

1 to clear

Read/Write

1 to clear

Read/Write

1 to clear

AR

Read/Write

1 to clear

E

24

PLB Master

Write Retry

Read/Write

1 to clear

Reset

Val ue

Reset

Val ue

0x0

0x0

Y

L

0x0

0x0

0x0

Description

Interrupt Global Enable- PLB bit (0) is the Interrupt

Global Enable bit. Enables all individually enabled

interrupts to be passed to the interrupt controller.

• 0 - Not enabled

• 1 - Enabled

Description

PCI Initiator Write SERR- Interrupt(19) indicates a SERR

ACCESS

error was detected during a PCI initiator write of data to a

PLB slave.

PCI Initiator Read SERR- Interrupt(20) indicates a SERR

error was detected during a PCI initiator read of data from a

PLB slave.

PLB Master Burst Write Retry Timeout- Interrupt(22)

indicates the automatic PCI write retries were not

successful due to a latency timeout on the last retry during

a PLB Master burst write to a PCI target.

PLB Master Burst Write Retry Disconnect- Interrupt(23)

indicates the automatic PCI write retries were not

successful due to a target disconnect on the last retry during

a PLB Master burst write to a PCI target.

PLB Master Write Retry- Interrupt(24) indicates the

automatic PCI write retries were not successful due to a PCI

retry on the last retry during a PLB Master burst write to a

PCI target.

DS508 March 21, 2006 www.xilinx.com 25

Product Specification

Page 26

PLB PCI Full Bridge (v1.00a)

Table 8: Bridge Interrupt Register Bit Definitions (Bit Assignment Assumes 32-bit Bus) (Contd)

Bit(s) Name Access

25

26

27

28

29

30

31

PLB Master

Write Master

Abort

PLB Master

Write Target

Abort

PLB Master

Write PERR

PLB Master

Write SERR

PLB Master

Read Target

Abort

PLB Master

Read PERR

PLB Master

Read SERR

Read/Write

1 to clear

Read/Write

1 to clear

Read/Write

1 to clear

Read/Write

1 to clear

Read/Write

1 to clear

Read/Write

1 to clear

Read/Write

1 to clear

Reset

Val ue

0x0

0x0

0x0

0x0

0x0

0x0

0x0

Description

PLB Master Write Master Abort- Interrupt(25) indicates

that the PLB PCI Bridge asserted a PCI master abort due to

no response from a target.

PLB Master Write Target Abort- Interrupt(26) indicates a

PCI target abort occurred during a PLB Master Write to a

PCI target.

PLB Master Write PERR- Interrupt(27) indicates a PERR

error is detected on a PLB Master write to a PCI target.

PLB Master Write SERR- Interrupt(28) indicates that a

SERR error was detected by the v3.0 core when performing

as a PCI initiator writing data to a PCI target.

PLB Master Read Target Abort- Interrupt(29) indicates

that a target abort was detected by the v3.0 core when

performing as a PCI initiator reading data from a PCI target.

PLB Master Read PERR- Interrupt(30) indicates that a

PERR was detected by the v3.0 core when performing as a

PCI initiator reading data from a PCI target.

PLB Master Read SERR- Interrupt(31) indicates that a

SERR error was detected by the v3.0 core when performing

as a PCI initiator reading data from a PCI target.

Bridge Interrupt Enable Register Description

The PLB PCI Bridge has interrupt enable features as described in IPSPEC048 PLB Device Interrupt

Architecture. Bit assignment in the Bridge Interrupt Enable Register is shown in

Tab le 9. The interrupt

enable register is read/write. All bits are cleared upon reset.

Table 9: Bridge Interrupt Enable Register Bit Definitions (Bit assignment assumes 32-bit bus)

Bit(s) Name Access

0-18 Read 0x0 Unassigned-

PCI Initiator

19

Write SERR

Read/Write 0x0

EARLY ACCESS

PCI Initiator

20

Read SERR

21 Reserved 0x0 • Reserved

PLB Master

Write Retry

22

Timeout

Read/Write 0x0

Read/Write 0x0

Reset

Val ue

Description

PCI Initiator Write SERR Enable- Enables this interrupt to

be passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PCI Initiator Read SERR Enable- Enables this interrupt to

be passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Burst Write Retry Timeout Enable- Enables

this interrupt to be passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

26 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 27

PLB PCI Full Bridge (v1.00a)

Table 9: Bridge Interrupt Enable Register Bit Definitions (Bit assignment assumes 32-bit bus) (Contd)

Bit(s) Name Access

PLB Master

23

24

25

26

27

28

29

30

31

Write Retry

Disconnect

PLB Master

Write Retry

PLB Master

Write Master

Abort

PLB Master

Write Target

Abort

PLB Master

Write PERR

PLB Master

Write SERR

PLB Master

Read Target

Abort

PLB Master

Read PERR

PLB Master

Read SERR

Read/Write 0x0

Read/Write 0x0

Read/Write 0x0

Read/Write 0x0

Read/Write 0x0

Read/Write 0x0

Read/Write 0x0

Read/Write 0x0

Read/Write 0x0

Reset

Val ue

Y

L

PLB Master Burst Write Retry Disconnect Enable-

Enables this interrupt to be passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Write Retry Enable- Enables this interrupt to be

passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Write Master Abort Enable- Enables this

interrupt to be passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Write Target Abort Enable- Enables this

interrupt to be passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Write PERR Enable- Enables this interrupt to be

passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Write SERR Enable- Enables this interrupt to be

passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Read Target Abort Enable- Enables this

ACCESS

interrupt to be passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Read PERR Enable- Enables this interrupt to be

passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

PLB Master Read SERR Enable- Enables this interrupt to be

passed to the interrupt controller.

• 0 - Not enabled.

• 1 - Enabled.

AR

PLB PCI Bridge Reset Register Description

Description

The IP Reset module is always instantiated in the PLB PCI Bridge. Details on the IPIF Reset module can

be found in the

PCI Bridge, independently of other modules in the system. The MIR is not included.

DS508 March 21, 2006 www.xilinx.com 27

Product Specification

E

Processor IP Reference Guide. The IP Reset module permits the software reset of the PLB

Page 28

PLB PCI Full Bridge (v1.00a)

Configuration Address Port Register Description

The Configuration Address Port Register exists only if the bridge is configured with PCI host bridge

configuration functionality (i.e.,

hardwired as in

are 32-bit accesses. Data is latched on a write in all 32-bits except where bits are hard-wired. A read

yields all 32-bits. Reset clears all bits. Eight and sixteen bit accesses are not supported, therefore, such

accesses are not passed on as IO accesses. Byte address integrity is maintained from PCI little endian

word format when writing/reading data to/from the Configuration Address Port Register which is

defined in big endian word format.

Table 10: Configuration Address Port Register Bit Definitions (Bit assignment assumes 32-bit bus)

C_INCLUDE_PCI_CONFIG=1). This register is read/write with s ome b its

Ta bl e 10. Definition of this register is a subset of the PCI 2.2. All accesses to the register

Bit(s) Name Access

0-5 D0-D5 Read/Write 0x0

6-7 D6-D7 Read 0x0 Hard-wired to 0, read-only

8-12 D8-D12 Read/Write 0x0 Identifies the target PCI Device (0-31)

13-15 D13-D15 Read/Write 0x0 Identifies the target function (1-8)

16-23 D16-D23 Read/Write 0x0 Identifies the target PCI Bus (1-256)

24 D24 Read/Write 0x0 Active high enable bit

25-31 D25-D31 Read 0x0 Reserved and hardwired to 0.

Reset

Val ue

Description

Identifies the target word address (32bits) within the

function’s configuration space (1-64)

Configuration Data Port Register Description

The Configuration Data Port Register exists only if the bridge is configured with PCI host bridge

configuration functionality (i.e.,

of this register follows PCI 2.2. All accesses to the register are 32-bit accesses. A read initiates a

configuration read command and a write initiates a configuration write command. Determination of

whether the command is a type 0 or type 1 depends on the comparison results of the bus number

compare. The fields are defined in

from PCI little endian word format when writing/reading data to/from the Configuration Data Port

register which is defined in big endian word format.

Table 11: Configuration Data Port Address Register Bit Definitions (Bit Assignment Assumes 32-bit Bus)

C_INCLUDE_PCI_CONFIG=1). This register is read/write and definition

Tab le 11. Reset clears all bits. Byte address integrity is maintained

Bit(s) Name Access

0-31 D0 - D31 Read/Write 0x0

EARLY ACCESS

Reset

Val ue

Description

Read or write causes automatic execution of Configuration

Read Command or Configuration Write Command using

address/bus information in the Configuration Address Port

register.

Bus Number/Subordinate Bus Number Register Description

The Bus Number/Subordinate Bus Number Register exists only if the bridge is configured with PCI

host bridge configuration functionality (i.e.,

All accesses to the register are 32-bit accesses. The bus number is an 8-bit value defining the primary

28 www.xilinx.com DS508 March 21, 2006

C_INCLUDE_PCI_CONFIG=1). This register is read/write.

Product Specification

Page 29

PLB PCI Full Bridge (v1.00a)

bus number. The highest subordinate bus number is also an 8-bit value. The fields are defined in

Tab le 12. Reset clears all bits.

Table 12: Bus Number/Subordinate Bus Number Register Bit Definitions (Bit Assignment Assumes 32-bit

Bus)

Bit(s) Name Access

0-7 D0- D7 Read 0x0 Reserved

8-15 D8 - D15 Read/Write 0x0 Bus number

16-23 D16 - D23 Read 0x0 Reserved

24-31 D24 - D31 Read/Write 0x0 Maximum subordinate bus number

IPIFBAR2PCIBAR_N High-Order Bits Register Description

When configured to include these registers (i.e., C_INCLUDE_BAROFFSET_REG=1), the values in the

registers are used to translate addresses on the PLB bus to the PCI. The register values are used instead

of the corresponding parameter C_IPIFBAR2PCIBAR_N for translation by high-order bit substitution.

The parameters C_IPIFBAR2PCIBAR_N have no effect on the bridge operation if the registers for

address translation are included.

The number of registers present is given by the number of IPIF BAR configured in the IPIF (i.e.,

C_IPIFBAR_NUM). The actual width of the Nth register is given by the number of high-order bits that

define the complete address range corresponding to the Nth IPIF BAR. When the register is read,

32-bits are returned with the low-order bits hard-wired to zero.

The IPIFBAR2PCIBAR_N registers are included in the bridge via the parameter

C_INCLUDE_BAROFFSET_REG.

These read/write registers allow dynamic, run-time changes of the high-order bits for the substitution

in the translation of an address from the PLB bus to the PCI bus. Low-order bits pass directly from the

PLB bus to the PCI bus. When the register is read, 32-bits are read with the low-order bits set to zero.

Tab le 13 shows the data format. The programmability of these registers allows PLB address

transactions to access any target on the PCI bus which has been arbitrarily assigned a PCI BAR by a

remote or local Host Bridge. Dynamic, run-time changes in the high-order bits for address translation

of PLB PCI bridge PCI BAR range translation to PLB slaves is not needed because the PLB slave

addresses are defined at build time.

Including these registers makes the parameters, C_IPIFBAR2PCIBAR_N, irrelevant because the value

in the Nth programmable register replaces the values of the corresponding parameter,

C_IPIFBAR2PCIBAR_N, in translating the PLB address to the PCI bus. When the registers are included,

the parameters, C_IPIFBAR2PCIBAR_N, for N=0 to C_IPIFBAR_NUM-1, have no effect.

Table 13: IPIFBAR2PCIBAR_N High-Order Bits (Bit assignment assumes 32-bit bus)

Bit(s) Name Access

AR

E

0-M D0 - DM Read/Write 0x0

M+1-31 DM+1 - D31 Read Only 0x0 Low-order bits set to zero

Reset

Value

Y

L

Reset

Val ue

Description

ACCESS

Description

M+1 high-order bits that are substituted in address

translation from Nth IPIFBAR access to PCI address

space

DS508 March 21, 2006 www.xilinx.com 29

Product Specification

Page 30

PLB PCI Full Bridge (v1.00a)

The example below shows how the IPIFBAR2PCIBAR_N registers assignments define translation of

PLB addresses within the range of a given IPIFBAR to PCI address space.

Setting C_INCLUDE_BAROFFSET_REG=1 includes high-order bit registers for all IPIFBARs defined

by C_IPIFBAR_NUM.

In this example where C_IPIFBAR_NUM=4, the following assignments for each range are made.

C_IPIFBAR_0=0x12340000

C_IPIF_HIGHADDR_0=0x1234FFFF

C_IPIFBAR2PCIBAR_0=Don’t care

C_IPIF_SPACETYPE_0=1

C_IPIFBAR_1=0xABCDE000

C_IPIF_HIGHADDR_1=0xABCDFFFF

C_IPIFBAR2PCIBAR_1=Don’t care

C_IPIF_SPACETYPE_1=0

C_IPIFBAR_2=0xFE000000

C_IPIF_HIGHADDR_2=0xFFFFFFFF

C_IPIFBAR2PCIBAR_2=Don’t care

C_IPIF_SPACETYPE_2=1

C_IPIFBAR_3=0x00000000

C_IPIF_HIGHADDR_3=0x0000007F

C_IPIFBAR2PCIBAR_3=Don’t care

C_IPIF_SPACETYPE_3=1

Associated with each IPIF BAR for C_IPIFBAR_N for N=0 to 3 are four registers for the high-order bits

to be substituted when making the translation to PCI memory and /IO space. For the previous

example, the following registers are set.

Register for C_IPIFBAR_0 (IPIFBAR2PCIBAR_0 High-Order Bit Register):

Programmable register for 16 high-order bits. The data in the register is substituted for the 16 msb of

the address that is translated to PCI bus.

Register for C_IPIFBAR_1 (IPIFBAR2PCIBAR_1 High-Order Bit Register):

Programmable register for 19 high-order bits. The data in the register is substituted for the 19 msb of

the address that is translated to PCI bus.

Register for C_IPIFBAR_2 (IPIFBAR2PCIBAR_2 High-Order Bit Register):

Programmable register for 7 high-order bits. The data in the register is substituted for the 7 msb of the

address that is translated to PCI bus.

Register for C_IPIFBAR_3 (IPIFBAR2PCIBAR_3 High-Order Bit Register):

Programmable register for 25 high-order bits. The data in the register is substituted for the 25 msb of

the address that is translated to PCI bus.

The remaining low-order bits are set to zero when a read of these registers is performed.

EARLY ACCESS

Writing 0x56710000 to IPIFBAR2PCIBAR_0 High-Order Bit Register and then accessing the PLB PCI

bridge IPIFBAR_0 with address 0x12340ABC on the PLB bus would yield 0x56710ABC on the PCI bus.

30 www.xilinx.com DS508 March 21, 2006

Product Specification

Page 31

PLB PCI Full Bridge (v1.00a)

Writing 0xFEDC0000 to IPIFBAR2PCIBAR_1 High-Order Bit Register and then accessing the PLB PCI

bridge IPIFBAR_1 with address 0xABCDF123 on the PLB bus would yield 0xFEDC1123 on the PCI bus.

Writing 0x40000000 to IPIFBAR2PCIBAR_2 High-Order Bit Register and then accessing the PLB PCI

bridge IPIFBAR_2 with address 0xFFFEDCBA on the PLB bus would yield 0x41FEDCBA on the PCI

bus.

Writing 0x12345680 to IPIFBAR2PCIBAR_3 High-Order Bit Register and then accessing the PLB PCI

bridge IPIFBAR_3 with address 0x0000004A on the PLB bus would yield 0x123456CA on the PCI bus.

Host Bridge Device Number Register Description

The Host Bridge Device Number register is included by setting C_INCLUDE_DEVNUM_REG=1. The

register can be included only if configuration functionality is included (i.e.,

C_INCLUDE_PCI_CONFIG=1).

This register is read/write and is four bits wide. Tab le 14 shows specifics of the data format. The

programmability of this register allows programmable definition of the bridge device number and

corresponding address bit that is internally connected to its IDSEL signal. The maximum value that can

be loaded in this register is given by the value set by parameter C_NUM_IDSEL minus 1 because the

device number must be consistent with the number of devices that are supported in configuation

transactions.

Table 14: Host Bridge Device Number (Bit assignment assumes 32-bit bus)

Bit(s) Name Access

0-27 D0-D27 Read Only 0x0 Set to zero.

28-31 D28 - D31 Read/Write 0x0

Reset

Val ue

Defines the device number of the PLB PCI bridge when