XILINX Command Line Tools User Guide

CommandLineToolsUser Guide

(FormerlytheDevelopmentSystemReferenceGuide)

UG628(v13.1)March2,2011

Xilinxisdisclosingthisuserguide,manual,releasenote,and/orspecication(the“Documentation”)toyou

solelyforuseinthedevelopmentofdesignstooperatewithXilinxhardwaredevices.Youmaynotreproduce,

distribute,republish,download,display,post,ortransmittheDocumentationinanyformorbyanymeans

including,butnotlimitedto,electronic,mechanical,photocopying,recording,orotherwise,withouttheprior

writtenconsentofXilinx.XilinxexpresslydisclaimsanyliabilityarisingoutofyouruseoftheDocumentation.

Xilinxreservestheright,atitssolediscretion,tochangetheDocumentationwithoutnoticeatanytime.Xilinx

assumesnoobligationtocorrectanyerrorscontainedintheDocumentation,ortoadviseyouofanycorrections

orupdates.Xilinxexpresslydisclaimsanyliabilityinconnectionwithtechnicalsupportorassistancethatmaybe

providedtoyouinconnectionwiththeInformation.

THEDOCUMENTATIONISDISCLOSEDTOYOU“ AS-IS”WITHNOWARRANTYOFANYKIND.XILINX

MAKESNOOTHERWARRANTIES,WHETHEREXPRESS,IMPLIED,ORSTATUTORY,REGARDING

THEDOCUMENTA TION,INCLUDINGANYW ARRANTIESOFMERCHANTABILITY,FITNESSFORA

PARTICULARPURPOSE,ORNONINFRINGEMENTOFTHIRD-PARTYRIGHTS.INNOEVENTWILL

XILINXBELIABLEFORANYCONSEQUENTIAL,INDIRECT,EXEMPLARY ,SPECIAL,ORINCIDENTAL

DAMAGES,INCLUDINGANYLOSSOFDATAORLOSTPROFITS,ARISINGFROMYOURUSEOFTHE

DOCUMENTA TION.

©Copyright2002-2011XilinxInc.AllRightsReserved.XILINX,theXilinxlogo,theBrandWindowandother

designatedbrandsincludedhereinaretrademarksofXilinx,Inc.Allothertrademarksarethepropertyoftheir

respectiveowners.ThePowerPCnameandlogoareregisteredtrademarksofIBMCorp.,andusedunderlicense.

Allothertrademarksarethepropertyoftheirrespectiveowners.

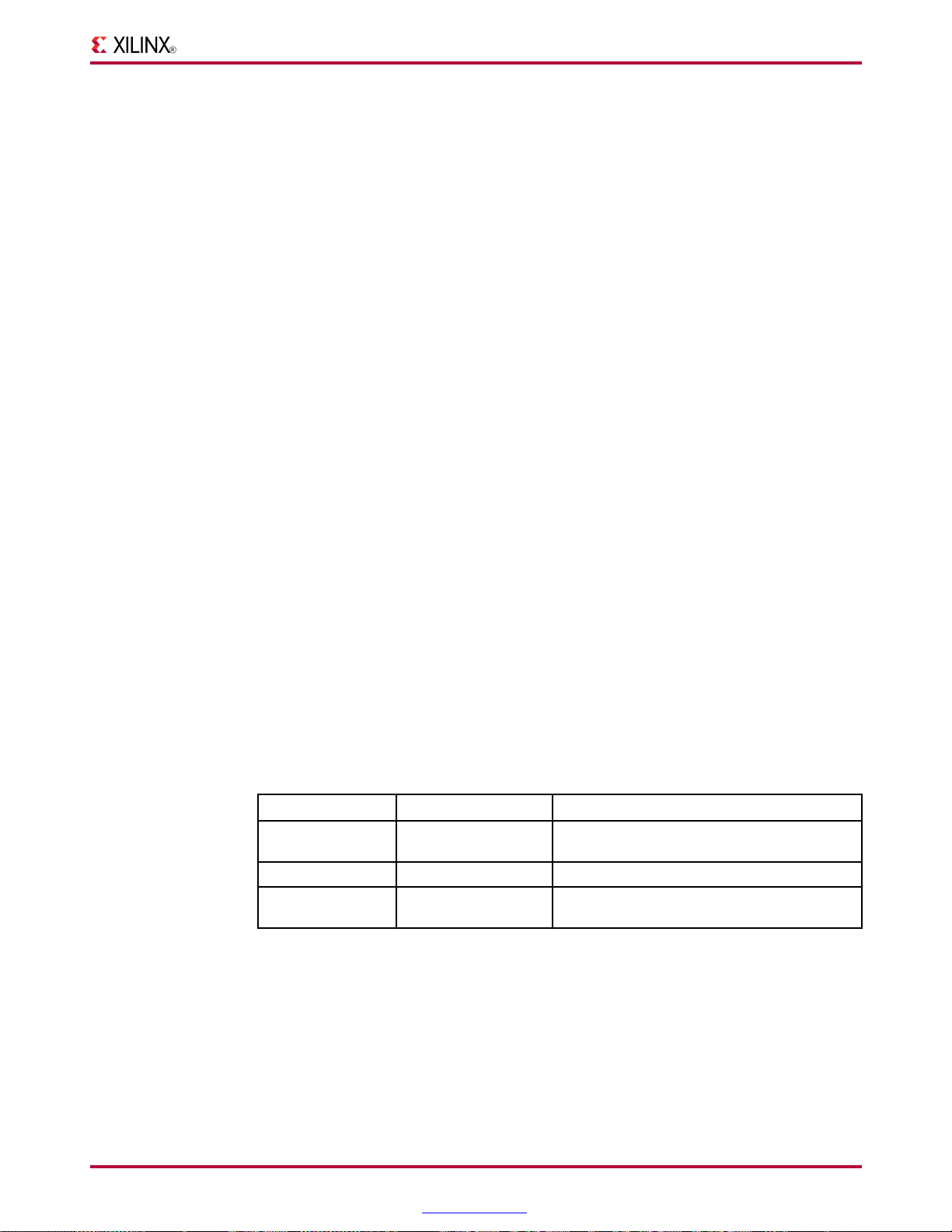

RevisionHistory

Thefollowingtableshowstherevisionhistoryforthisdocument.

Date

03/01/2011

03/02/2011

Version

13.1downloadAddinginformationforXilinx®7seriesFPGAdevices.

13.1WebreleaseAdditionalupdatesforXilinx7seriesFPGAdevices.

2w

w w . x i l i n x . c o m UG628(v13.1)March2,2011

CommandLineToolsUserGuide

TableofContents

RevisionHistory....................................................................................................2

Chapter1Introduction.................................................................................................9

CommandLineProgramOverview......................................................................9

CommandLineSyntax.........................................................................................10

CommandLineOptions......................................................................................10

InvokingCommandLinePrograms....................................................................14

Chapter2DesignFlow...............................................................................................15

DesignFlowOverview........................................................................................15

DesignEntryandSynthesis................................................................................18

DesignImplementation.......................................................................................22

DesignVerication...............................................................................................25

FPGADesignTips...............................................................................................31

Chapter3PARTGen...................................................................................................33

PARTGenOverview.............................................................................................33

PARTGenSyntax..................................................................................................39

PARTGenCommandLineOptions.....................................................................39

Chapter4NetGen.......................................................................................................43

NetGenOverview................................................................................................43

NetGenSimulationFlow.....................................................................................45

NetGenEquivalenceCheckingFlow..................................................................55

NetGenStaticTimingAnalysisFlow.................................................................59

PreservingandWritingHierarchyFiles.............................................................63

DedicatedGlobalSignalsinBack-AnnotationSimulation..............................65

Chapter5LogicalDesignRuleCheck(DRC)...........................................................67

LogicalDRCOverview........................................................................................67

LogicalDRCChecks............................................................................................67

Chapter6NGDBuild...................................................................................................71

NGDBuildOverview...........................................................................................71

NGDBuildSyntax................................................................................................74

NGDBuildOptions..............................................................................................75

Chapter7MAP............................................................................................................81

MAPOverview.....................................................................................................81

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 3

MAPProcess.........................................................................................................83

MAPSyntax..........................................................................................................84

MAPOptions........................................................................................................86

ResynthesisandPhysicalSynthesisOptimizations..........................................97

GuidedMapping..................................................................................................98

SimulatingMapResults......................................................................................99

MAPReport(MRP)File.....................................................................................100

PhysicalSynthesisReport(PSR)File................................................................105

HaltingMAP......................................................................................................107

Chapter8PhysicalDesignRuleCheck..................................................................109

DRCOverview...................................................................................................109

DRCSyntax........................................................................................................110

DRCOptions......................................................................................................110

DRCChecks.......................................................................................................111

DRCErrorsandWarnings.................................................................................111

Chapter9PlaceandRoute(PAR)...........................................................................113

PAROverview....................................................................................................113

PARProcess........................................................................................................115

PARSyntax.........................................................................................................116

DetailedListingofOptions...............................................................................117

PARReports.......................................................................................................123

ReportGen..........................................................................................................132

HaltingPAR........................................................................................................134

Chapter10SmartXplorer.........................................................................................135

What’sNew.........................................................................................................135

SmartXplorerOverview.....................................................................................136

UsingSmartXplorer...........................................................................................137

SelectingtheBestStrategy................................................................................143

RunningMultipleStrategiesinParallel...........................................................144

CustomStrategies..............................................................................................146

SmartXplorerCommandLineReference..........................................................148

SmartXplorerReports........................................................................................158

SettingUpSmartXplorertoRunonSSH.........................................................161

Chapter11XPWR(XPWR).......................................................................................163

XPWROverview................................................................................................163

XPWRSyntax......................................................................................................164

4w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

XPWRCommandLineOptions........................................................................165

XPWRCommandLineExamples......................................................................167

UsingXPWR.......................................................................................................167

PowerReports....................................................................................................169

Chapter12PIN2UCF................................................................................................171

PIN2UCFOverview...........................................................................................171

PIN2UCFSyntax................................................................................................174

PIN2UCFCommandLineOptions...................................................................175

Chapter13TRACE....................................................................................................177

TRACEOverview...............................................................................................177

TRACESyntax....................................................................................................178

TRACEOptions.................................................................................................179

TRACECommandLineExamples....................................................................183

TRACEReports..................................................................................................184

OFFSETConstraints...........................................................................................200

PERIODConstraints..........................................................................................207

HaltingTRACE..................................................................................................211

Chapter14Speedprint.............................................................................................213

SpeedprintOverview.........................................................................................213

SpeedprintCommandLineSyntax...................................................................217

SpeedprintCommandLineOptions.................................................................217

Chapter15BitGen....................................................................................................219

BitGenOverview...............................................................................................219

BitGenCommandLineSyntax..........................................................................221

BitGenCommandLineOptions.......................................................................222

Chapter16BSDLAnno.............................................................................................245

BSDLAnnoOverview........................................................................................245

BSDLAnnoCommandLineSyntax..................................................................246

BSDLAnnoCommandLineOptions................................................................246

BSDLAnnoFileComposition...........................................................................247

BoundaryScanBehaviorinXilinxDevices......................................................253

Chapter17PROMGen..............................................................................................255

PROMGenOverview.........................................................................................255

PROMGenSyntax..............................................................................................256

PROMGenOptions............................................................................................257

BitSwappinginPROMFiles............................................................................263

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 5

PROMGenExamples.........................................................................................264

Chapter18IBISWriter..............................................................................................265

IBISWriterOverview.........................................................................................265

IBISWriterSyntax..............................................................................................266

IBISWriterOptions............................................................................................267

Chapter19CPLDFit..................................................................................................269

CPLDFitOverview.............................................................................................269

CPLDFitSyntax..................................................................................................270

CPLDFitOptions................................................................................................271

Chapter20TSIM.......................................................................................................279

TSIMOverview..................................................................................................279

TSIMSyntax.......................................................................................................279

Chapter21TAEngine...............................................................................................281

TAEngineOverview...........................................................................................281

TAEngineSyntax................................................................................................282

TAEngineOptions..............................................................................................282

Chapter22Hprep6...................................................................................................283

Hprep6Overview...............................................................................................283

Hprep6Options..................................................................................................284

Chapter23XFLOW...................................................................................................287

XFLOWOverview..............................................................................................287

XFLOWSyntax...................................................................................................292

XFLOWFlowTypes...........................................................................................292

FlowFiles............................................................................................................297

XFLOWOptionFiles..........................................................................................300

XFLOWOptions.................................................................................................301

RunningXFLOW................................................................................................305

Chapter24NGCBuild...............................................................................................307

NGCBuildOverview.........................................................................................307

NGCBuildSyntax..............................................................................................308

NGCBuildOptions............................................................................................309

Chapter25Compxlib...............................................................................................315

CompxlibOverview...........................................................................................315

CompxlibSyntax................................................................................................316

CompxlibOptions..............................................................................................317

6w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

CompxlibCommandLineExamples................................................................322

SpecifyingRuntimeOptions.............................................................................323

SampleCongurationFile(WindowsV ersion)...............................................326

Chapter26XWebTalk...............................................................................................331

WebTalkOverview.............................................................................................331

XWebTalkSyntax...............................................................................................332

XWebTalkOptions.............................................................................................332

Chapter27TclReference........................................................................................335

TclOverview.......................................................................................................335

TclFundamentals...............................................................................................336

ProjectandProcessProperties...........................................................................338

XilinxTclCommandsforGeneralUse.............................................................356

XilinxTclCommandsforAdvancedScripting.................................................373

ExampleTclScripts............................................................................................388

AppendixAISEDesignSuiteFiles.........................................................................393

AppendixBEDIF2NGDandNGDBuild...................................................................397

EDIF2NGDOverview........................................................................................397

EDIF2NGDOptions...........................................................................................399

NGDBuild..........................................................................................................401

AppendixCAdditionalResources..........................................................................411

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 7

8w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Introduction

ThischapterdescribesthecommandlineprogramsfortheISE®DesignSuite.This

guidewasformerlyknownastheDevelopmentSystemReferenceGuide,buthasbeen

renamedtoCommandLineToolsUserGuide.

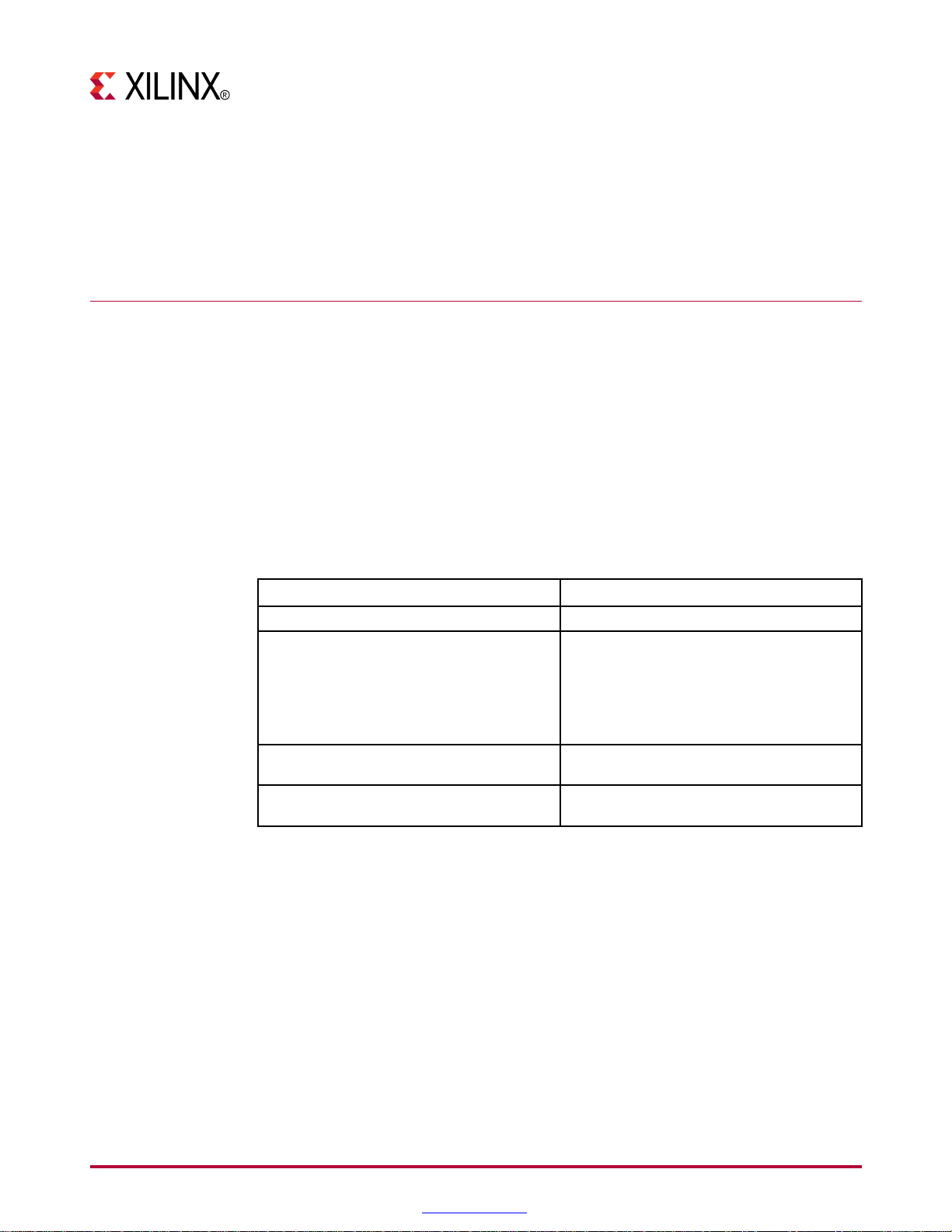

CommandLineProgramOverview

Xilinx®softwarecommandlineprogramsallowyoutoimplementandverifyyour

design.Thefollowingtableliststheprogramsyoucanuseforeachstepinthedesign

ow.Fordetailedinformation,seetheDesignFlowchapter.

CommandLineProgramsintheDesignFlow

Chapter1

DesignFlowStepCommandLineProgram

DesignImplementationNGDBuild,MAP ,PAR,SmartXplorer,BitGen

Timing-drivenPlacementandRouting,

Re-synthesis,&PhysicalSynthesis

Optimizations

TimingSimulationandBackAnnotation

(DesignVerication)

StaticTimingAnalysis

(DesignVerication)

Youcanruntheseprogramsinthestandarddesignoworusespecialoptionstorunthe

programsfordesignpreservation.Eachcommandlineprogramhasmultipleoptions,

whichallowyoutocontrolhowaprogramexecutes.Forexample,youcansetoptionsto

changeoutputlenames,tosetapartnumberforyourdesign,ortospecifylestoread

inwhenexecutingtheprogram.Youcanalsouseoptionstocreateguidelesandrun

guidemodetomaintaintheperformanceofapreviouslyimplementeddesign.

Someofthecommandlineprogramsdescribedinthisguideunderliemanyofthe

XilinxGraphicalUserInterfaces(GUIs).TheGUIscanbeusedwiththecommand

lineprogramsoralone.ForinformationontheGUIs,seetheonlineHelpprovided

witheachXilinxtool.

MAP

NoteMAPusesspeciedoptionstoenable

timing-drivenplacementandrouting

(-timing),andre-synthesisandphysical

synthesisoptimizationsthatcantransforma

designtomeettimingrequirements.

NetGen

TRACE

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 9

Chapter1:Introduction

CommandLineSyntax

Commandlinesyntaxalwaysbeginswiththecommandlineprogramname.The

programnameisfollowedbyanyoptionsandthenbylenames.Usethefollowing

ruleswhenspecifyingcommandlineoptions:

•Enteroptionsinanyorder,precededthemwithadash(minussignonthekeyboard)

andseparatethemwithspaces.

•Beconsistentwithuppercaseandlowercase.

•Whenanoptionrequiresaparameter,separatetheparameterfromtheoptionby

spacesortabs.Forexample,thefollowingshowsthecommandlinesyntaxfor

runningPARwiththeeffortlevelsettohigh:

–Correct:par-olhigh

–Incorrect:par-olhigh

•Whenusingoptionsthatcanbespeciedmultipletimes,precedeeachparameter

withtheoptionletter.Inthisexample,the-loptionshowsthelistoflibrariesto

search:

–Correct:-lxilinxun-lsynopsys

–Incorrect:-lxilinxunsynopsys

•Enterparametersthatareboundtoanoptionaftertheoption.

–Correct:-fcommand_file

–Incorrect:command_file-f

CommandLineOptions

-f(ExecuteCommandsFile)

Usethefollowingruleswhenspecifyinglenames:

•Enterlenamesintheorderspeciedinthechapterthatdescribesthecommand

lineprogram.Inthisexamplethecorrectorderisprogram,inputle,outputle,

andthenphysicalconstraintsle.

–Correct:parinput.ncdoutput.ncdfreq.pcf

–Incorrect:parinput.ncdfreq.pcfoutput.ncd

•Uselowercaseforallleextensions(forexample,.ncd).

Thefollowingoptionsarecommontomanyofthecommandlineprogramsprovided

withtheISE®DesignSuite.

•-f(ExecuteCommandsFile)

•-h(Help)

•-intstyle(IntegrationStyle)

•-p(PartNumber)

WithanyXilinx®commandlineprogramforusewithFPGAdesigns,youcanstore

commandlineprogramoptionsandlenamesinacommandle.Youcanthenexecute

theargumentsbyenteringtheprogramnamewiththe-foptionfollowedbythename

ofthecommandle.Thisisusefulifyoufrequentlyexecutethesameargumentseach

timeyouexecuteaprogramorifthecommandlinecommandbecomestoolong.

Syntax

-fcommand_file

10w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Chapter1:Introduction

Youcanusetheleinthefollowingways:

•Tosupplyallofthecommandoptionsandlenamesfortheprogram,asinthe

followingexample:

par-fcommand_le

command_leisthenameofthelethatcontainsthecommandoptionsandle

names.

•Toinsertcertaincommandoptionsandlenameswithinthecommandline,asin

thefollowingexample:

par-fplaceoptions-frouteoptionsdesign_i.ncddesign_o.ncd

–placeoptionsisthenameofalecontainingplacementcommandparameters.

–routeoptionsisthenameofalecontainingroutingcommandparameters.

YoucreatethecommandleinASCIIformat.Usethefollowingruleswhencreating

thecommandle:

•Separateprogramoptionsandlenameswithspaces.

•Precedecommentswiththepoundsign(#).

•PutnewlinesortabsanywherewhitespaceisallowedontheLinuxorDOS

commandline.

•Putallargumentsonthesameline,oneargumentperline,oracombinationofthese.

•Allcarriagereturnsandothernon-printablecharactersaretreatedasspacesand

ignored.

•Nolinelengthlimitationexistswithinthele.

Example

Followingisanexampleofacommandle:

#commandlineoptionsforparfordesignmine.ncd

-w

0l5

/home/yourname/designs/xilinx/mine.ncd

#directoryforoutputdesigns

/home/yourname/designs/xilinx/output.dir

#usetimingconstraintsfile

/home/yourname/designs/xilinx/mine.pcf

-h(Help)

Whenyouentertheprogramnamefollowedbythisoption,youwillgetamessage

listingalloptionsfortheprogramandtheirparameters,aswellastheletypesusedby

theprogram.Themessagealsoexplainseachoftheoptions.

Syntax

-h

-help

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 11

Chapter1:Introduction

SymbolDescription

[]

{}

italicsIndicatesavariablenameornumberforwhich

,

-

:

|

()

Enclosesitemsthatareoptional.

Enclosesitemsthatmayberepeated.

youmustsubstituteinformation.

Showsarangeforanintegervariable.

Showsthestartofanoptionname.

Bindsavariablenametoarange.

LogicalORtoshowachoiceofoneoutof

manyitems.TheORoperatormayonly

separatelogicalgroupsorliteralkeywords.

Enclosesalogicalgroupingforachoice

betweensub-formats.

Example

Followingareexamplesofsyntaxusedforlenames:

•inle[.ncd]showsthattypingthe.ncdextensionisoptionalbutthattheextension

mustbe.ncd.

•inle.ednshowsthatthe.ednextensionisoptionalandisappendedonlyifthere

isnootherextensioninthelename.

Forarchitecture-specicprograms,suchasBitGen,youcanenterthefollowingtogeta

verbosehelpmessageforthespeciedarchitecture:

program_name-harchitecture_name

Youcanredirectthehelpmessagetoaletoreadlaterortoprintoutbyenteringthe

following:

program_name-h>lename

OntheLinuxcommandline,enterthefollowingtoredirectthehelpmessagetoale

andreturntothecommandprompt.

program_name-h>&lename

-intstyle(IntegrationStyle)

Thisoptionlimitsscreenoutput,basedontheintegrationstylethatyouarerunning,to

warninganderrormessagesonly.

Syntax

-intstyleise|xflow|silent

Whenusing-intstyle,oneofthreemodesmustbespecied:

•-intstyleiseindicatestheprogramisbeingrunaspartofanintegrateddesign

environment.

•-intstylexflowindicatestheprogramisbeingrunaspartofanintegrated

batchow.

•-intstylesilentlimitsscreenoutputtowarninganderrormessagesonly.

Note-intstyleisautomaticallyinvokedwhenrunninginanintegratedenvironment

suchasProjectNavigatororXFLOW.

12w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Chapter1:Introduction

-p(PartNumber)

Thisoptionspeciesthepartintowhichyourdesignisimplemented.

Syntax

-ppart_number

Thisoptioncanspecifyanarchitectureonly,acompletepartspecication(device,

package,andspeed),orapartialspecication(forexample,deviceandpackageonly).

Thepartnumberordevicenamemustbefromadevicelibraryyouhaveinstalledon

yoursystem.

AcompleteXilinx®partnumberconsistsofthefollowingelements:

•Architecture(forexample,spartan3e)

•Device(forexample,xc3s100e)

•Package(forexample,vq100)

•Speed(forexample,-4)

NoteTheSpeedprintprogramlistsblockdelaysfordevicespeedgrades.The-soption

letsyouspecifyaspeedgrade.Ifyoudonotspecifyaspeedgrade,Speedprintreports

thedefaultspeedgradeforthedeviceyouaretargeting.

SpecifyingPartNumbers

Youcanspecifyapartnumberatvariouspointsinthedesignow,notallofwhich

requirethe-poption.

•Intheinputnetlist(doesnotrequirethe-poption)

•InaNetlistConstraintsFile(NCF)(doesnotrequirethe-poption)

•Withthe-poptionwhenyourunanetlistreader(EDIF2NGD)

•IntheUserConstraintsFile(UCF)(doesnotrequirethe-poption)

•Withthe-poptionwhenyourunNGDBuild

BythetimeyourunNGDBuild,youmusthavealreadyspeciedadevice

architecture.

•Withthe-poptionwhenyourunMAP

WhenyourunMAPyoumustspecifyanarchitecture,device,andpackage,either

ontheMAPcommandlineorearlierinthedesignow.Ifyoudonotspecifya

speed,MAPselectsadefaultspeed.YoucanonlyrunMAPusingapartnumber

fromthearchitectureyouspeciedwhenyouranNGCBuild.

•Withthe-poptionwhenyourunSmartXplorer(FPGAdesignsonly)

•Withthe-poptionwhenyourunCPLDFit(CPLDdesignsonly)

NotePartnumbersspeciedinalaterstepofthedesignowoverrideapartnumber

speciedinanearlierstep.Forexample,apartspeciedwhenyourunMAPoverridesa

partspeciedintheinputnetlist.

Examples

Thefollowingexamplesshowhowtospecifypartsonthecommandline.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 13

Chapter1:Introduction

SpecificationExamples

Architectureonly

Deviceonlyxc4vfx12

DevicePackagexc4fx12sf363

Device-Packagexc4vfx12-sf363

DeviceSpeed-Packagexc4vfx1210-sf363

DevicePackage-Speedxc4fx12sf363-10

Device-Speed-Packagexc4vfx12-10-sf363

Device-SpeedPackagexc4vfx12-10sf363

virtex4

virtex5

spartan3

spartan3a

xc9500

xpla3(CoolRunner™XPLA3devices)

xc3s100e

xc3s100evq100

xc3s100e-vq100

xc3s100e4-vq100

xc3s100evq100-4

xc3s100e-4-vq100

xc3s100e-4vq100

InvokingCommandLinePrograms

YoustartXilinx®commandlineprogramsbyenteringacommandattheLinuxorDOS

commandline.Seetheprogram-specicchaptersinthisbookfortheappropriatesyntax

XilinxalsoofferstheXFLOWprogram,whichletsyouautomatetherunningofseveral

programsatonetime.SeetheXFLOWchapterformoreinformation.

14w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

DesignFlow

Thischapterdescribestheprocessforcreating,implementing,verifying,and

downloadingdesignsforXilinx®FPGAandCPLDdevices.Foracomplete

descriptionofXilinxFPGAandCPLDsdevices,refertotheXilinxDataSheetsat:

t t p : / / w w w . x i l i n x . c o m / s u p p o r t / d o c u m e n t a t i o n / i n d e x . h t m

h

DesignFlowOverview

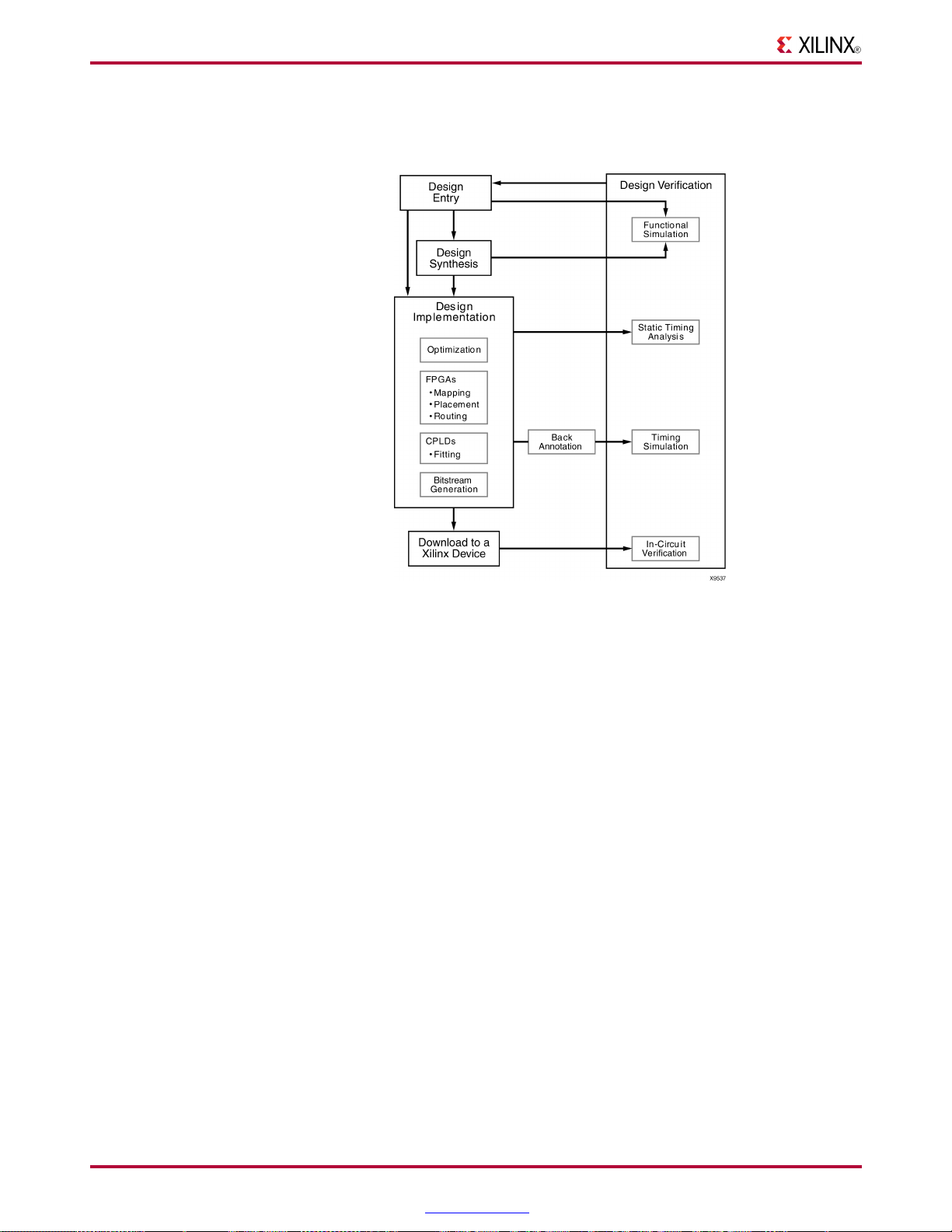

Thestandarddesignowcomprisesthefollowingsteps:

1.DesignEntryandSynthesis-CreateyourdesignusingaXilinx®-supported

schematiceditor,aHardwareDescriptionLanguage(HDL)fortext-basedentry ,or

both.IfyouuseanHDLfortext-basedentry ,youmustsynthesizetheHDLleinto

anEDIFleor,ifyouareusingtheXilinxSynthesisTechnology(XST)GUI,you

mustsynthesizetheHDLleintoanNGCle.

2.DesignImplementation-Convertthelogicaldesignleformat,suchasEDIF ,that

youcreatedinthedesignentryandsynthesisstageintoaphysicalleformatby

implementingtoaspecicXilinxarchitecture.Thephysicalinformationiscontained

intheNativeCircuitDescription(NCD)leforFPGAsandtheVM6leforCPLDs.

ThencreateabitstreamlefromtheselesandoptionallyprogramaPROMor

EPROMforsubsequentprogrammingofyourXilinxdevice.

3.DesignV erication-Usingagate-levelsimulatororcable,ensurethatyourdesign

meetstimingrequirementsandfunctionsproperly .SeetheiMPACTonlinehelpfor

informationaboutXilinxdownloadcablesanddemonstrationboards.

Chapter2

Thefulldesignowisaniterativeprocessofentering,implementing,andverifying

yourdesignuntilitiscorrectandcomplete.Thecommandlinetoolsprovidedwiththe

ISE®DesignSuiteallowquickdesigniterationsthroughthedesignowcycle.Xilinx

devicespermitunlimitedreprogramming.Youdonotneedtodiscarddeviceswhen

debuggingyourdesignincircuit.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 15

Chapter2:DesignFlow

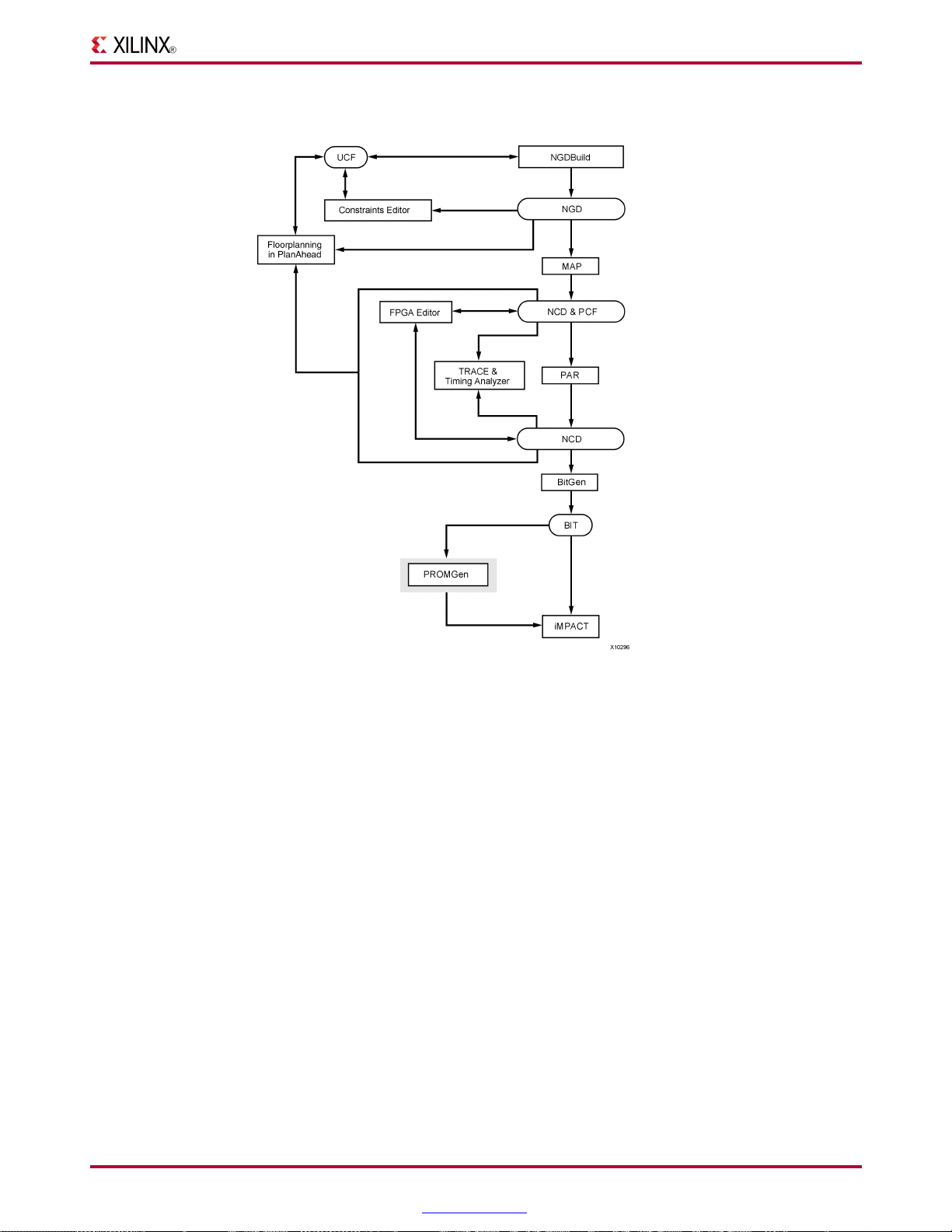

XilinxDesignFlow

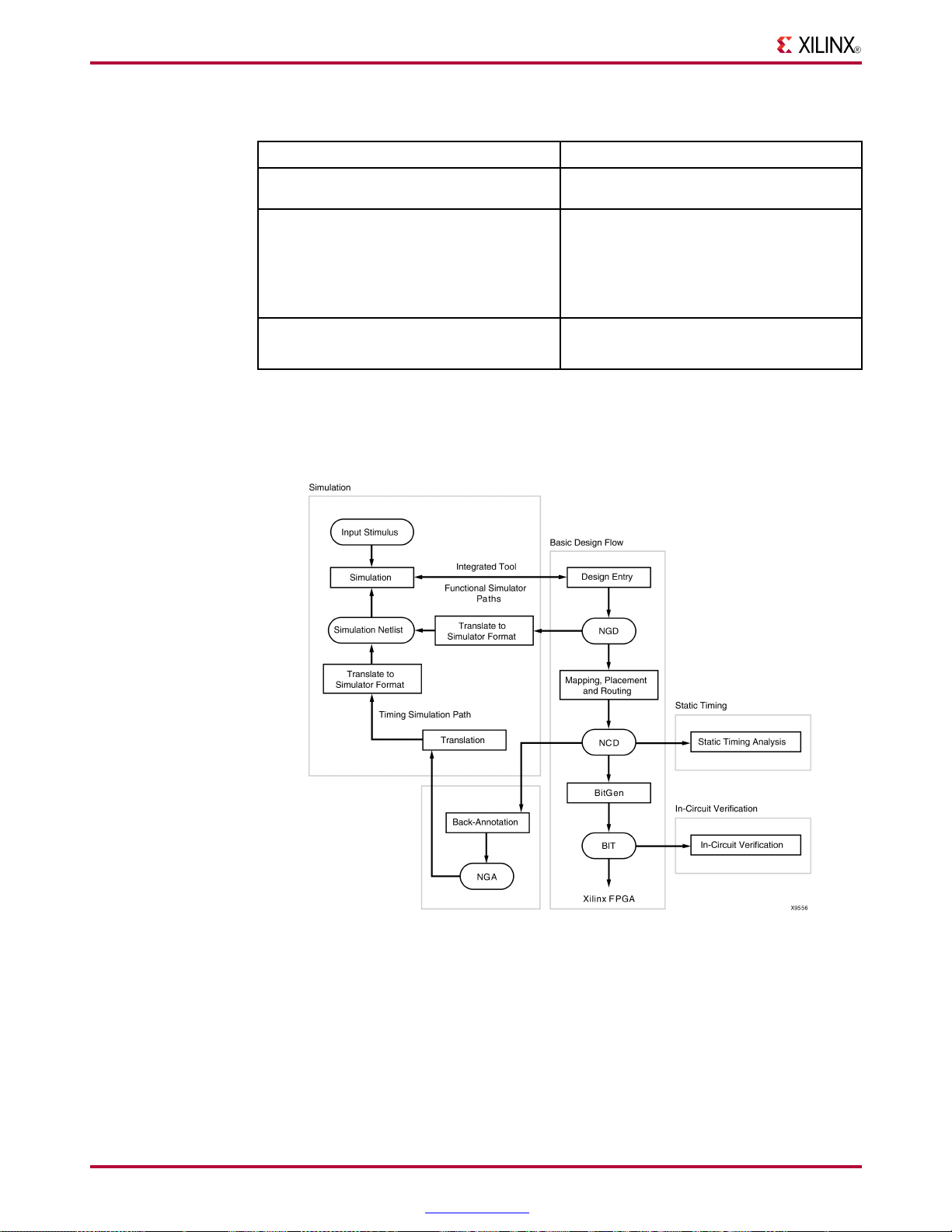

ThisgureshowsthestandardXilinxdesignow.

16w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

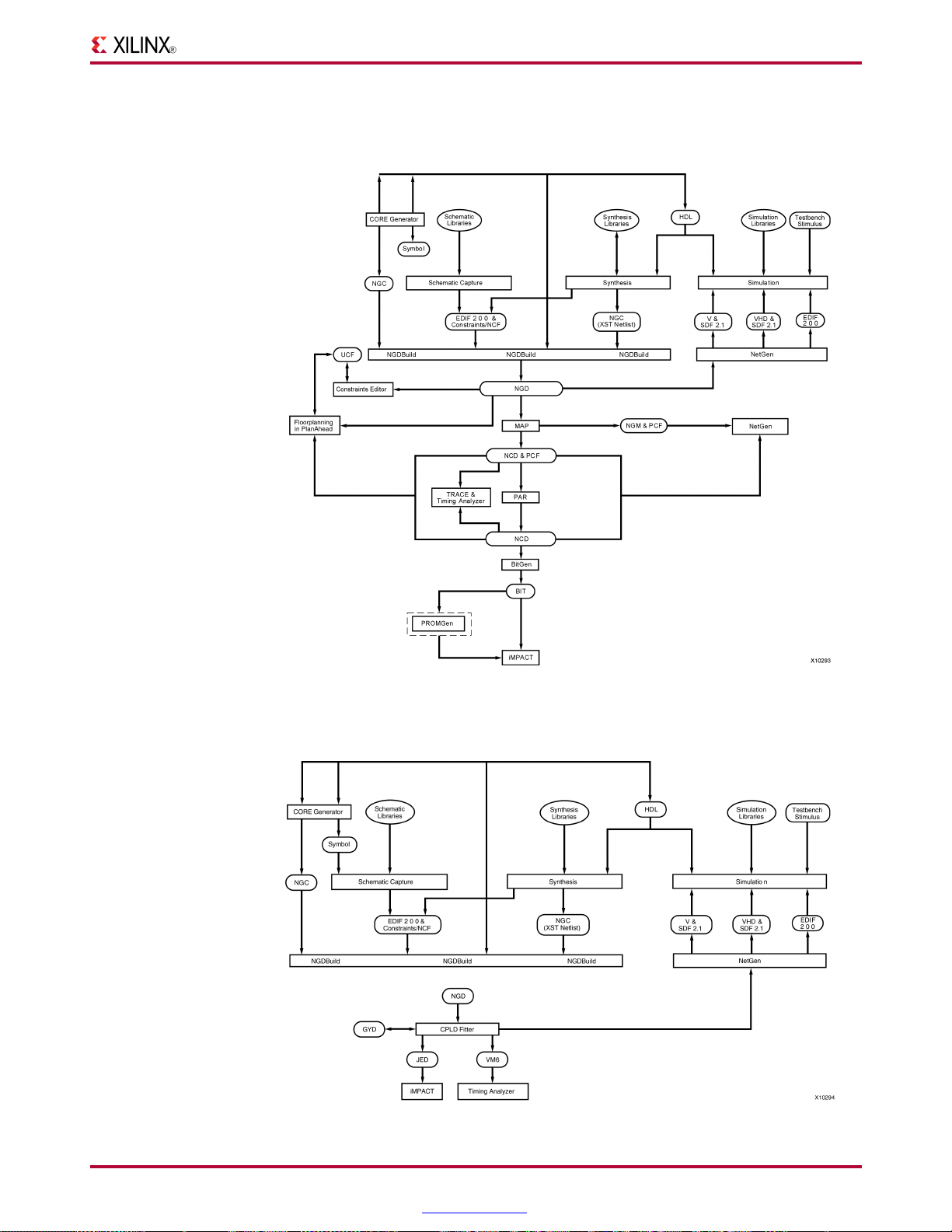

XilinxSoftwareDesignFlow(FPGAs)

ThisgureshowstheXilinxsoftwareowchartforFPGAdesigns.

Chapter2:DesignFlow

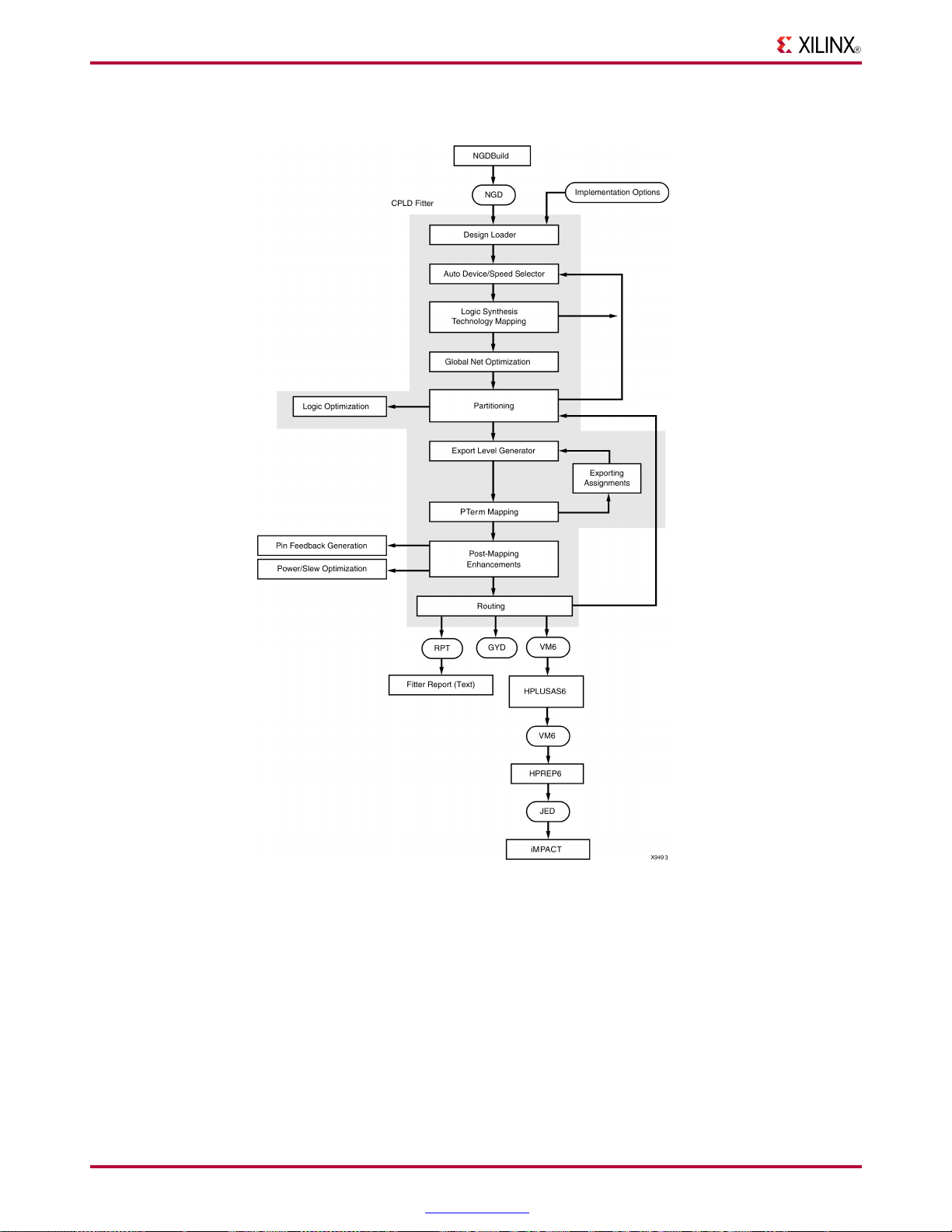

XilinxSoftwareDesignFlow(CPLDs)

ThisgureshowstheXilinxsoftwareowchartforCPLDdesigns.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 17

Chapter2:DesignFlow

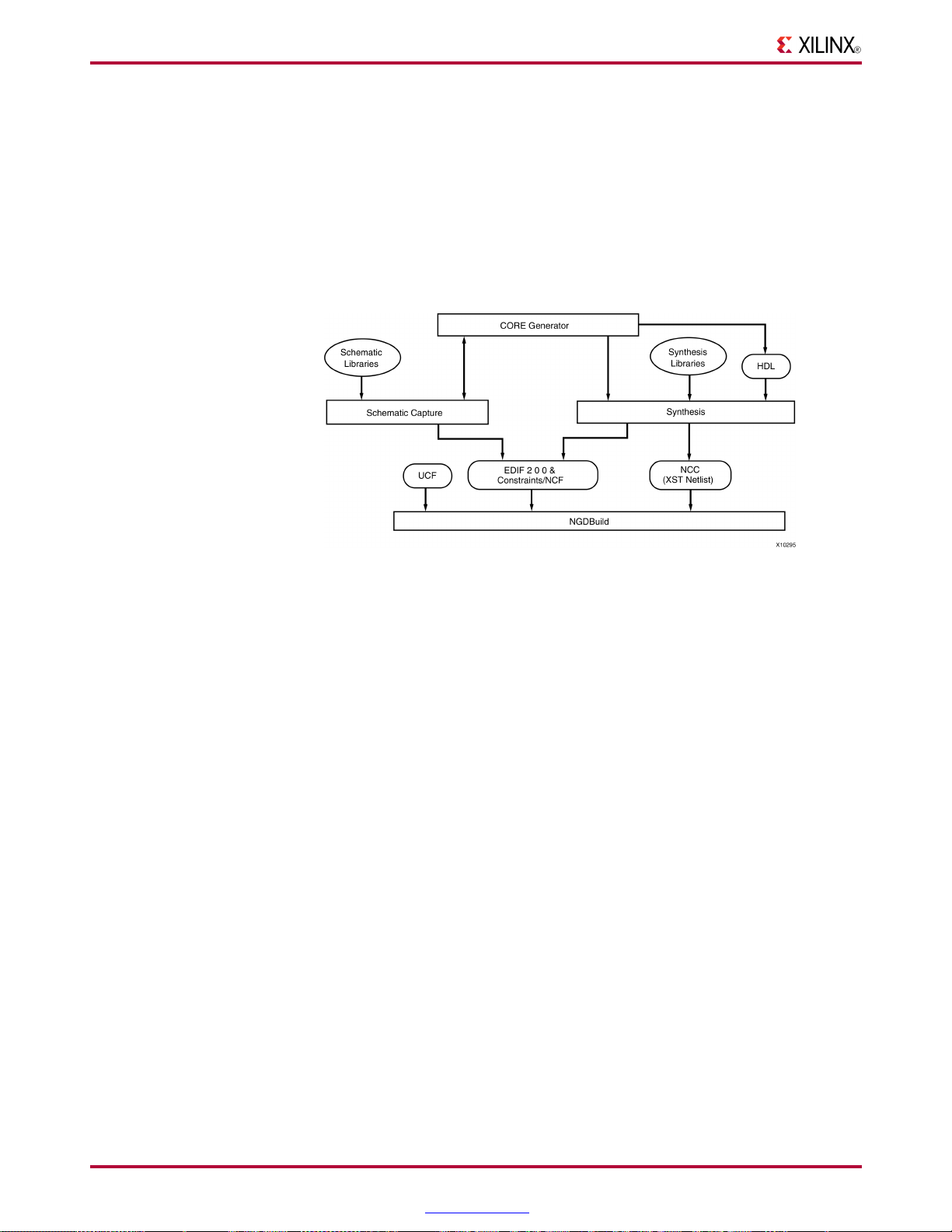

DesignEntryandSynthesis

Youcanenteradesignwithaschematiceditororatext-basedtool.Designentrybegins

withadesignconcept,expressedasadrawingorfunctionaldescription.Fromthe

originaldesign,anetlistiscreated,thensynthesizedandtranslatedintoanativegeneric

object(NGO)le.ThisleisfedintotheXilinx®softwareprogramcalledNGDBuild,

whichproducesalogicalNativeGenericDatabase(NGD)le.

Thefollowinggureshowsthedesignentryandsynthesisprocess.

DesignEntryFlow

HierarchicalDesign

DesignhierarchyisimportantinbothschematicandHDLentryforthefollowing

reasons:

•Helpsyouconceptualizeyourdesign

•Addsstructuretoyourdesign

•Promoteseasierdesigndebugging

•Makesiteasiertocombinedifferentdesignentrymethods(schematic,HDL,orstate

editor)fordifferentpartsofyourdesign

•Makesiteasiertodesignincrementally ,whichconsistsofdesigning,implementing,

andverifyingindividualpartsofadesigninstages

•Reducesoptimizationtime

•Facilitatesconcurrentdesign,whichistheprocessofdividingadesignamonga

numberofpeoplewhodevelopdifferentpartsofthedesigninparallel.

Inhierarchicaldesigning,aspecichierarchicalnameidentieseachlibraryelement,

uniqueblock,andinstanceyoucreate.Thefollowingexampleshowsahierarchical

namewitha2-inputORgateintherstinstanceofamultiplexerina4-bitcounter:

/Acc/alu_1/mult_4/8count_3/4bit_0/mux_1/or2

Xilinx®stronglyrecommendsthatyounamethecomponentsandnetsinyourdesign.

ThesenamesarepreservedandusedbyFPGAEditor.Thesenamesarealsousedfor

back-annotationandappearinthedebugandanalysistools.Ifyoudonotnameyour

componentsandnets,theSchematicEditorautomaticallygeneratesthenames.For

example,ifleftunnamed,thesoftwaremightnamethepreviousexample,asfollows:

/$1a123/$1b942/$1c23/$1d235/$1e121/$1g123/$1h57

NoteItisdifculttoanalyzecircuitswithautomaticallygeneratednames,becausethe

namesonlyhavemeaningforXilinxsoftware.

18w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Chapter2:DesignFlow

Partitions

Inhierarchicaldesignows,suchasDesignPreservationandPartialReconguration,

partitionsareusedtodenehierarchicalboundariessothatacomplexdesigncanbe

brokenupintosmallerblocks.Partitionscreateaboundaryorinsulationaroundthe

hierarchicalmodule,whichisolatesthemodulefromotherpartsofthedesign.A

partitionthathasbeenimplementedandexportedcanbere-insertedintothedesign

usingasimplecut-and-pastetypefunction,whichpreservestheplacementandrouting

resultsfortheisolatedmodule.Allofthepartitiondenitionsandcontrolsaredoneina

lecalledxpartition.pxml.Formoreinformationonusinghierarchicaldesignows

andimplementingpartitions,seetheHierarchicalDesignMethodologyGuide(UG748).

PXMLFile

Partitiondenitionsarecontainedinthexpartition.pxmlle.ThePXMLlename

iscase-sensitive,andmustbenamedxpartition.pxml.Thetoplevelmodule

ofthedesignmustbedenedasapartitioninadditiontoanyoptionallowerlevel

partitions.ThePXMLlecanbecreatedbyhand,fromscripts,orfromatoolsuchas

thePlanAhead™software.ThePXMLwillbepickedupautomaticallybytheISE®

DesignSuiteimplementationtoolswhenlocatedinthecurrentworkingdirectory.

Formoreinformationaboutusingthexpartition.pxmlle,seetheHierarchical

DesignMethodologyGuide(UG748).Anexamplexpartition.pxmlleisavailable

at%XILINX%/PlanAhead/testcases/templates(where%XILINX%isyour

installationdirectory)ifyouwishtocreateaPXMLlebyhand.

NoteAllpathsinthePXMLlemustbeabsolutepaths.

<?xmlversion="1.0"encoding="UTF-8"?>

<ProjectFileVersion="1.2"Name="Example"ProjectVersion="2.0">

<PartitionName="/top"State="implement"ImportLocation="NONE">

<PartitionName="/top/module_A"State="import"ImportLocation="/home/user/Example/import"Preserve="routing">

</Partition>

<PartitionName="/top/module_B"State="import"ImportLocation="/home/user/Example/import"Preserve="routing">

</Partition>

<PartitionName="/top/module_C"State="implement"ImportLocation="/home/user/Example/import"Preserve="placement">

</Partition>

</Partition>

</Project>

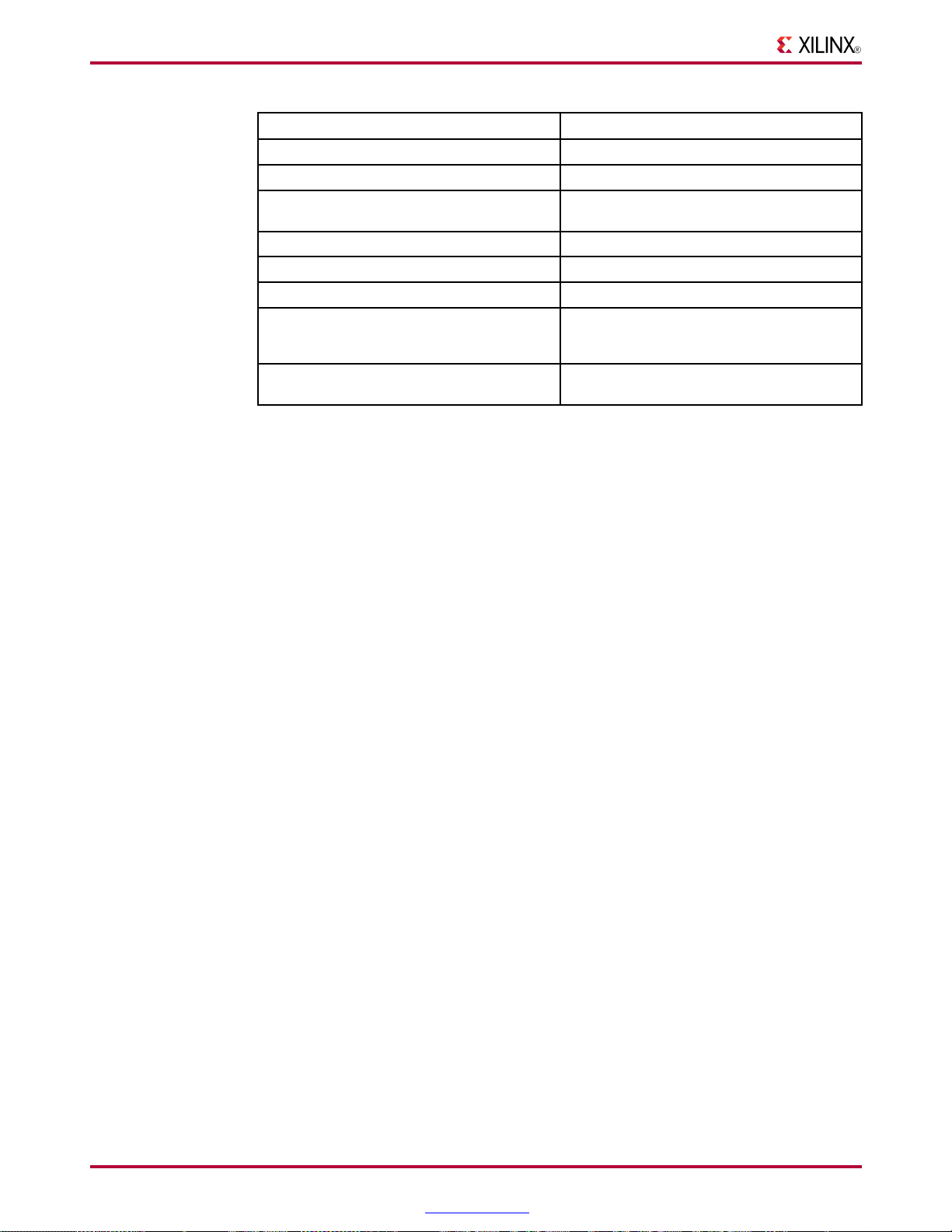

PXMLattributesforProjectdefinition

Attributename

FileVersion

Name

ProjectVersion2.0

Value

1.2

Project_Name

Description

Usedforinternalpurposes.Donotchangethis

value.

Project_Nameisuserdened.

Usedforinternalpurposes.Donotchangethis

value.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 19

Chapter2:DesignFlow

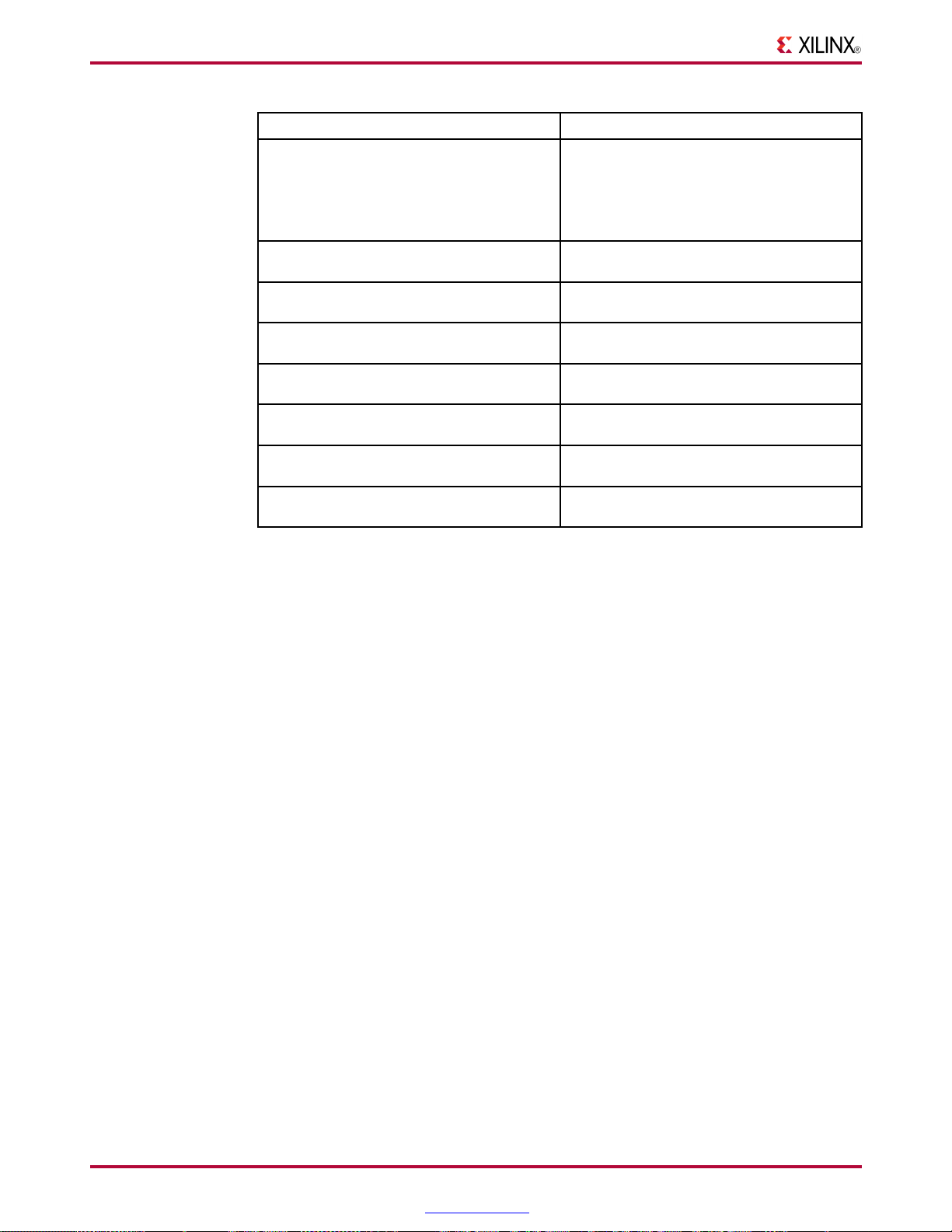

PXMLattributesforPartitiondefinition

Attributename

Name

State

ImportLocation

ImportTag

Preserve

BoundaryOpt

Value

Partition_Name

“implement”Partitionisimplementedfromscratch.

“import”

pathIgnoredifStatedoesnotequal“import.”

Partition_Name

“routing”

“placement”Placementispreservedbutroutingcanbe

“synthesis”Placementandroutingcanbemodied.

“inherit”Inheritvaluefromtheparentpartition.Thisis

“all”Enablestheimplementationtoolstodo

“none”

Description

Hierarchicalinstancenameofmoduleinwhich

thepartitionshouldbeapplied.

Partitionisimportedandpreservedaccording

tothelevelsetbyPreserve.

Thepathcanberelativeorabsolute,butthe

locationspeciedmustcontainavalid"export"

directorywhenState=import.“NONE”isa

predenedkeywordfornoimportdirectory .

Allowsapartitiontobeimportedintoa

differentlevelofhierarchythanitwasinitially

implementedin.Setthevaluetothehierarchical

instancenameofthepartitionwhereitwas

implemented.

100%placementandroutingispreserved.This

isthedefaultforthetoplevelPartition.

modied.

thedefaultforallpartitionsexceptthetoplevel

partition.

optimizationonpartitionportsconnectedto

constraintsaswellasunusedpartitionports.

Normalpartitionoptimizationrulesapply .

Optimizationisallowedonlywithinpartition

boundaries.Thisisthedefaultvalue.

SchematicEntryOverview

Schematictoolsprovideagraphicinterfacefordesignentry.Youcanusethesetoolsto

connectsymbolsrepresentingthelogiccomponentsinyourdesign.Youcanbuildyour

designwithindividualgates,oryoucancombinegatestocreatefunctionalblocks.

Thissectionfocusesonwaystoenterfunctionalblocksusinglibraryelementsandthe

COREGenerator™tool.

LibraryElements

Primitivesandmacrosarethe“buildingblocks”ofcomponentlibraries.Xilinx®

librariesprovideprimitives,aswellascommonhigh-levelmacrofunctions.Primitives

arebasiccircuitelements,suchasANDandORgates.Eachprimitivehasaunique

libraryname,symbol,anddescription.Macroscontainmultiplelibraryelements,which

canincludeprimitivesandothermacros.

YoucanusethefollowingtypesofmacroswithXilinxFPGAs:

•Softmacroshavepre-denedfunctionalitybuthaveexiblemapping,placement,

androuting.SoftmacrosareavailableforallFPGAs.

•Relationallyplacedmacros(RPMs)havexedmappingandrelativeplacement.

RPMsareavailableforalldevicefamilies,excepttheXC9500family .

20w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

HDLEntryandSynthesis

Macrosarenotavailableforsynthesisbecausesynthesistoolshavetheirownmodule

generatorsanddonotrequireRPMs.Ifyouwishtooverridethemodulegeneration,you

caninstantiatemodulescreatedusingCOREGenerator.Formostleading-edgesynthesis

tools,thisdoesnotofferanadvantageunlessitisforamodulethatcannotbeinferred.

COREGeneratorTool(FPGAsOnly)

TheXilinxCOREGeneratortooldeliversparameterizablecoresthatareoptimized

forXilinxFPGAs.Thelibraryincludescoresrangingfromsimpledelayelementsto

complexDSP(DigitalSignalProcessing)ltersandmultiplexers.Fordetails,refertothe

COREGeneratorHelp(partofISEHelp).Y oucanalsorefertotheXilinxIP(Intellectual

Property)CenterWebsiteath

solutions.Thesesolutionsincludedesignreusetools,freereferencedesigns,Digital

SignalProcessing(DSP),PCI™solutions,IPimplementationtools,cores,specialized

systemlevelservices,andverticalapplicationIPsolutions.

AtypicalHardwareDescriptionLanguage(HDL)supportsamixed-leveldescriptionin

whichgateandnetlistconstructsareusedwithfunctionaldescriptions.Thismixed-level

capabilityletsyoudescribesystemarchitecturesatahighlevelofabstractionandthen

incrementallyrenethedetailedgate-levelimplementationofadesign.

t t p : / / w w w . x i l i n x . c o m / i p c e n t e r ,whichoffersthelatestIP

Chapter2:DesignFlow

FunctionalSimulation

HDLdescriptionsofferthefollowingadvantages:

•Youcanverifydesignfunctionalityearlyinthedesignprocess.Adesignwrittenas

anHDLdescriptioncanbesimulatedimmediately .Designsimulationatthishigh

level,atthegate-levelbeforeimplementation,allowsyoutoevaluatearchitectural

anddesigndecisions.

•AnHDLdescriptionismoreeasilyreadandunderstoodthananetlistorschematic

description.HDLdescriptionsprovidetechnology-independentdocumentation

ofadesignanditsfunctionality.BecausetheinitialHDLdesigndescriptionis

technologyindependent,youcanuseitagaintogeneratethedesigninadifferent

technology,withouthavingtotranslateitfromtheoriginaltechnology .

•LargedesignsareeasiertohandlewithHDLtoolsthanschematictools.

AfteryoucreateyourHDLdesign,youmustsynthesizeit.Duringsynthesis,behavioral

informationintheHDLleistranslatedintoastructuralnetlist,andthedesignis

optimizedforaXilinx®device.XilinxsupportsHDLsynthesistoolsforseveral

third-partysynthesisvendors.Inaddition,Xilinxoffersitsownsynthesistool,Xilinx

SynthesisTechnology(XST).Formoreinformation,seetheXSTUserGuideforVirtex-4,

Virtex-5,Spartan-3,andNewerCPLDDevices(UG627)ortheXSTUserGuideforVirtex-6,

Spartan-6,and7SeriesDevices(UG687).Fordetailedinformationonsynthesis,seethe

SynthesisandSimulationDesignGuide(UG626).

Afteryoucreateyourdesign,youcansimulateit.Functionalsimulationteststhe

logicinyourdesigntodetermineifitworksproperly .Youcansavetimeduring

subsequentdesignstepsifyouperformfunctionalsimulationearlyinthedesignow.

SeeSimulationformoreinformation.

Constraints

Youmaywanttoconstrainyourdesignwithincertaintimingorplacementparameters.

Youcanspecifymapping,blockplacement,andtimingspecications.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 21

Chapter2:DesignFlow

MappingConstraints(FPGAsOnly)

BlockPlacement

YoucanenterconstraintsmanuallyorusetheConstraintsEditororFPGAEditor,which

aregraphicaluserinterface(GUI)toolsprovidedbyXilinx®.YoucanusetheTiming

AnalyzerGUIorTRACEcommandlineprogramtoevaluatethecircuitagainstthese

constraintsbygeneratingastatictiminganalysisofyourdesign.SeetheTRACEchapter

andtheonlineHelpprovidedwiththeISE®DesignSuiteformoreinformation.For

moreinformationonconstraints,seetheConstraintsGuide(UG625).

YoucanspecifyhowablockoflogicismappedintoCLBsusinganFMAPforall

Spartan®andVirtex®FPGAarchitectures.Thesemappingsymbolscanbeusedin

yourschematic.However,ifyouoverusethesespecications,itmaybedifcultto

routeyourdesign.

Blockplacementcanbeconstrainedtoaspeciclocation,tooneofmultiplelocations,or

toalocationrange.Locationscanbespeciedintheschematic,withsynthesistools,

orintheUserConstraintsFile(UCF).Poorblockplacementcanadverselyaffectboth

theplacementandtheroutingofadesign.OnlyI/Oblocksrequireplacementtomeet

externalpinrequirements.

TimingSpecifications

Youcanspecifytimingrequirementsforpathsinyourdesign.PARusesthesetiming

specicationstoachieveoptimumperformancewhenplacingandroutingyourdesign.

NetlistTranslationPrograms

NetlisttranslationprogramsletyoureadnetlistsintotheXilinx®softwaretools.

EDIF2NGDletsyoureadanElectronicDataInterchangeFormat(EDIF)200le.The

NGDBuildprogramautomaticallyinvokestheseprogramsasneededtoconvertyour

EDIFletoanNGDle,therequiredformatfortheXilinxsoftwaretools.NGCles

outputfromtheXilinxXSTsynthesistoolarereadinbyNGDBuilddirectly .

YoucannddetaileddescriptionsoftheEDIF2NGD,andNGDBuildprogramsinthe

NGDBuildchapterandtheEDIF2NGDandNGDBuildAppendix.

DesignImplementation

DesignImplementationbeginswiththemappingorttingofalogicaldesignletoa

specicdeviceandiscompletewhenthephysicaldesignissuccessfullyroutedanda

bitstreamisgenerated.Youcanalterconstraintsduringimplementationjustasyoudid

duringtheDesignEntrystep.SeeConstraintsforinformation.

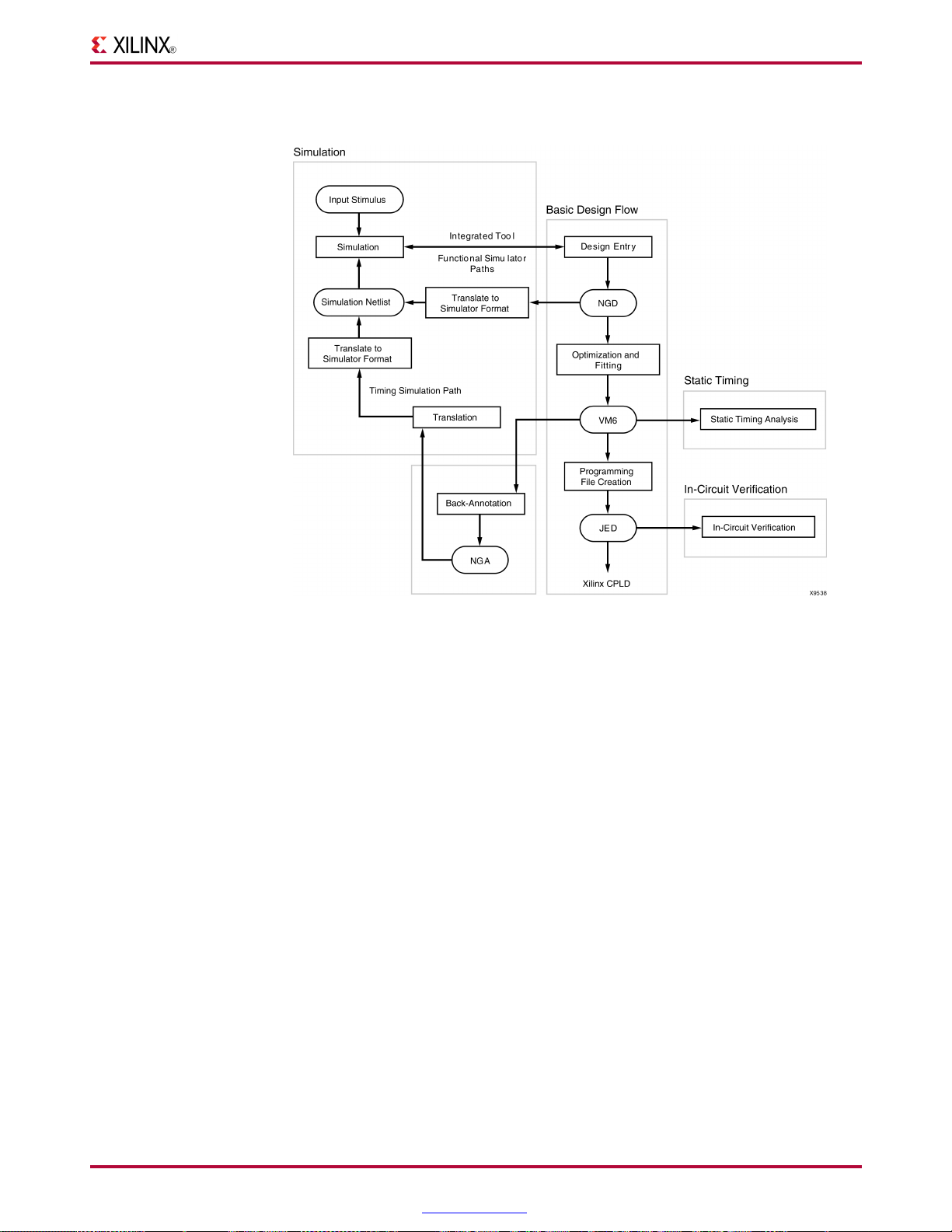

ThefollowinggureshowsthedesignimplementationprocessforFPGAdesigns:

22w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

DesignImplementationFlow(FPGAs)

Chapter2:DesignFlow

ThefollowinggureshowsthedesignimplementationprocessforCPLDdesigns:

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 23

Chapter2:DesignFlow

DesignImplementationFlow(CPLDs)

Mapping(FPGAsOnly)

ForFPGAs,theMAPcommandlineprogrammapsalogicaldesigntoaXilinx®FPGA.

TheinputtoMAPisanNGDle,whichcontainsalogicaldescriptionofthedesignin

termsofboththehierarchicalcomponentsusedtodevelopthedesignandthelower-level

Xilinxprimitives,andanynumberofNMC(hardplaced-and-routedmacro)les,each

ofwhichcontainsthedenitionofaphysicalmacro.MAPthenmapsthelogictothe

components(logiccells,I/Ocells,andothercomponents)inthetargetXilinxFPGA.

TheoutputdesignfromMAPisanNCDle,whichisaphysicalrepresentationof

thedesignmappedtothecomponentsintheXilinxFPGA.TheNCDlecanthenbe

placedandrouted,usingthePARcommandlineprogram.SeetheMAPchapterfor

detailedinformation.

24w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

NoteMAPprovidesoptionsthatenableadvancedoptimizationsthatarecapable

ofimprovingtimingresultsbeyondstandardimplementations.Theseadvanced

optimizationscantransformadesignpriortoorafterplacement.Optimizationscan

beappliedattwodifferentstagesintheXilinxdesignow.Therststagehappens

rightaftertheinitialmappingofthelogictothearchitectureslices;thesecondstageif

afterplacement.SeeRe-SynthesisandPhysicalSynthesisOptimizationsintheMAP

chapterformoreinformation.

PlacingandRouting(FPGAsOnly)

ForFPGAs,thePARcommandlineprogramtakesamappedNCDleasinput,places

androutesthedesign,andoutputsaplacedandroutedNativeCircuitDescription

(NCD)le,whichisusedbythebitstreamgenerator,BitGen.TheoutputNCDlecan

alsoactasaguidelewhenyoureiterateplacementandroutingforadesigntowhich

minorchangeshavebeenmadeafterthepreviousiteration.SeethePARchapterfor

detailedinformation.

YoucanalsouseFPGAEditortodothefollowing:

•Placeandroutecriticalcomponentsbeforerunningautomaticplaceandroutetools

onanentiredesign.

•Modifyplacementandroutingmanually.Theeditorallowsbothautomaticand

manualcomponentplacementandrouting.

Chapter2:DesignFlow

NoteFormoreinformation,seetheonlineHelpprovidedwithFPGAEditor.

BitstreamGeneration(FPGAsOnly)

ForFPGAs,theBitGencommandlineprogramproducesabitstreamforXilinx®

deviceconguration.BitGentakesafullyroutedNCDleasitsinputandproduces

acongurationbitstream,whichisabinarylewitha.bitextension.TheBITle

containsallofthecongurationinformationfromtheNCDledeningtheinternal

logicandinterconnectionsoftheFPGA,plusdevice-specicinformationfromotherles

associatedwiththetargetdevice.SeetheBitGenchapterfordetailedinformation.

AfteryougenerateyourBITle,youcandownloadittoadeviceusingtheiMPACTGUI.

YoucanalsoformattheBITleintoaPROMleusingthePROMGencommandline

programandthendownloadittoadeviceusingtheiMPACTGUI.SeethePROMGen

chapterofthisguideortheiMPACTonlinehelpformoreinformation.

DesignVerification

Designvericationistestingthefunctionalityandperformanceofyourdesign.Y oucan

verifyXilinx®designsinthefollowingways:

•Simulation(functionalandtiming)

•Statictiminganalysis

•In-circuitverication

Thefollowingtableliststhedifferentdesigntoolsusedforeachvericationtype.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 25

Chapter2:DesignFlow

VerificationTools

VerificationTypeTools

SimulationThird-partysimulators(integratedand

non-integrated)

StaticTimingAnalysisTRACE(commandlineprogram)

TimingAnalyzer(GUI)

MentorGraphicsTAUandInnovedaBLAST

softwareforusewiththeSTAMPleformat

(forI/Otimingvericationonly)

In-CircuitVericationDesignRuleChecker(commandlineprogram)

Downloadcable

Designvericationproceduresshouldoccurthroughoutyourdesignprocess,asshown

inthefollowinggures.

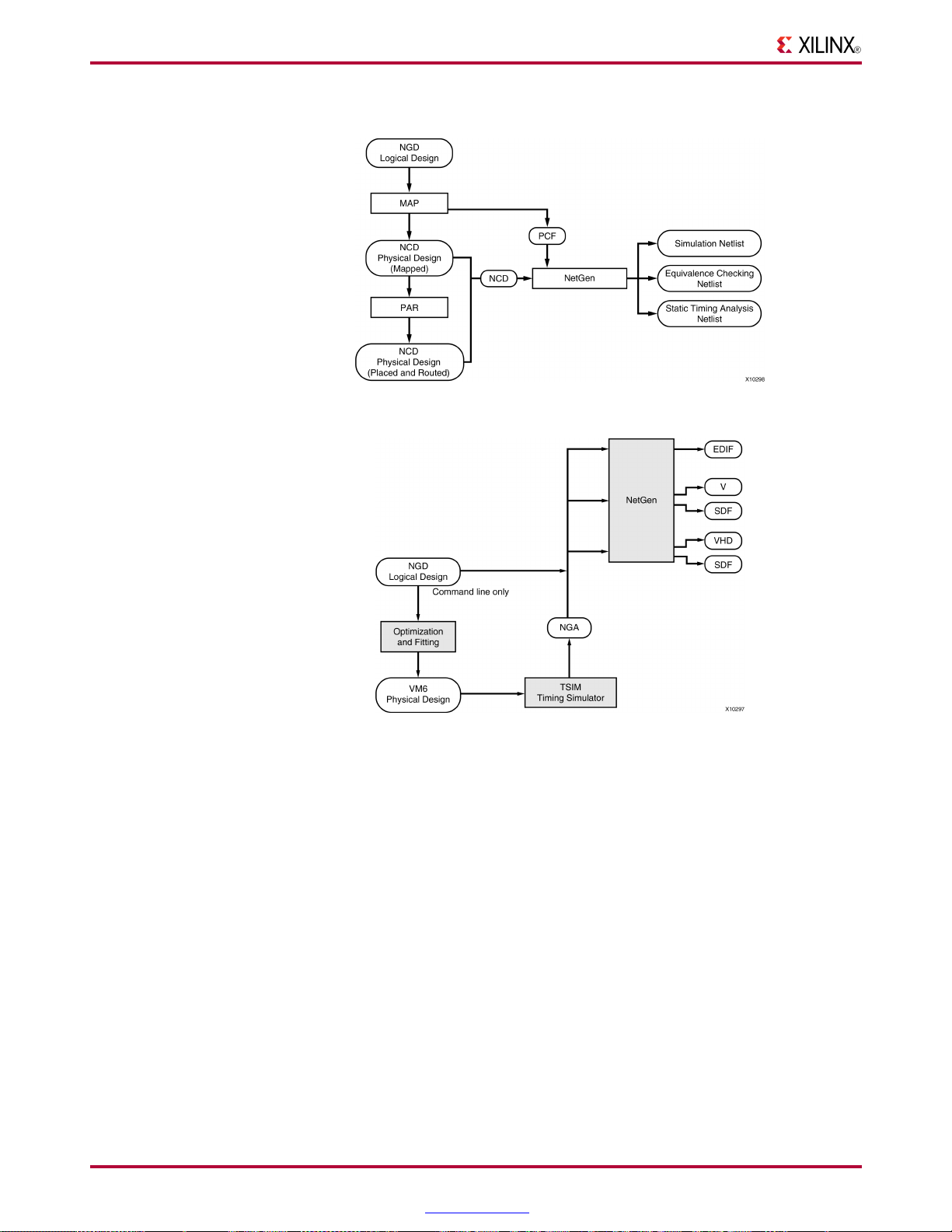

ThreeVerificationMethodsoftheDesignFlow(FPGAs)

ThefollowinggureshowsthevericationmethodsofthedesignowforCPLDs.

26w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

ThreeVerificationMethodsoftheDesignFlow(CPLDs)

Chapter2:DesignFlow

Simulation

Youcanrunfunctionalortimingsimulationtoverifyyourdesign.Thissectiondescribes

theback-annotationprocessthatmustoccurpriortotimingsimulation.Italsodescribes

thefunctionalandtimingsimulationmethodsforbothschematicandHDL-based

designs.

Back-Annotation

Beforetimingsimulationcanoccur,thephysicaldesigninformationmustbetranslated

anddistributedbacktothelogicaldesign.ForFPGAs,thisback-annotationprocessis

donewithaprogramcalledNetGen.ForCPLDs,back-annotationisperformedwith

theTSimTimingSimulator.Theseprogramscreateadatabase,whichtranslatesthe

back-annotatedinformationintoanetlistformatthatcanbeusedfortimingsimulation.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 27

Chapter2:DesignFlow

Back-AnnotationFlowforFPGAs

Back-Annotation(CPLDs)

NetGen

NetGenisacommandlineprogramthatdistributesinformationaboutdelays,setup

andholdtimes,clocktoout,andpulsewidthsfoundinthephysicalNativeCircuit

Description(NCD)designlebacktothelogicalNativeGenericDatabase(NGD)le

andgeneratesaVerilogorVHDLnetlistforusewithsupportedtimingsimulation,

equivalencechecking,andstatictiminganalysistools.

NetGenreadsanNCDasinput.TheNCDlecanbeamapped-onlydesign,ora

partiallyorfullyplacedandrouteddesign.AnNGMle,createdbyMAP ,isanoptional

sourceofinput.NetGenmergesmappinginformationfromtheoptionalNGMlewith

placement,routing,andtiminginformationfromtheNCDle.

NoteNetGenreadsanNGAleasinputtogenerateatimingsimulationnetlistfor

CPLDdesigns.

SeetheNetGenchapterfordetailedinformation.

FunctionalSimulation

Functionalsimulationdeterminesifthelogicinyourdesigniscorrectbeforeyou

implementitinadevice.Functionalsimulationcantakeplaceattheearlieststagesof

thedesignow .Becausetiminginformationfortheimplementeddesignisnotavailable

atthisstage,thesimulatorteststhelogicinthedesignusingunitdelays.

28w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

NoteItisusuallyfasterandeasiertocorrectdesignerrorsifyouperformfunctional

simulationearlyinthedesignow.

TimingSimulation

Timingsimulationveriesthatyourdesignrunsatthedesiredspeedforyourdevice

underworst-caseconditions.Thisprocessisperformedafteryourdesignismapped,

placed,androutedforFPGAsorttedforCPLDs.Atthistime,alldesigndelaysare

known.

Timingsimulationisvaluablebecauseitcanverifytimingrelationshipsanddetermine

thecriticalpathsforthedesignunderworst-caseconditions.Itcanalsodetermine

whetherornotthedesigncontainsset-uporholdviolations.

Beforeyoucansimulateyourdesign,youmustgothroughtheback-annotationprocess,

above.Duringthisprocess,NetGencreatessuitableformatsforvarioussimulators.

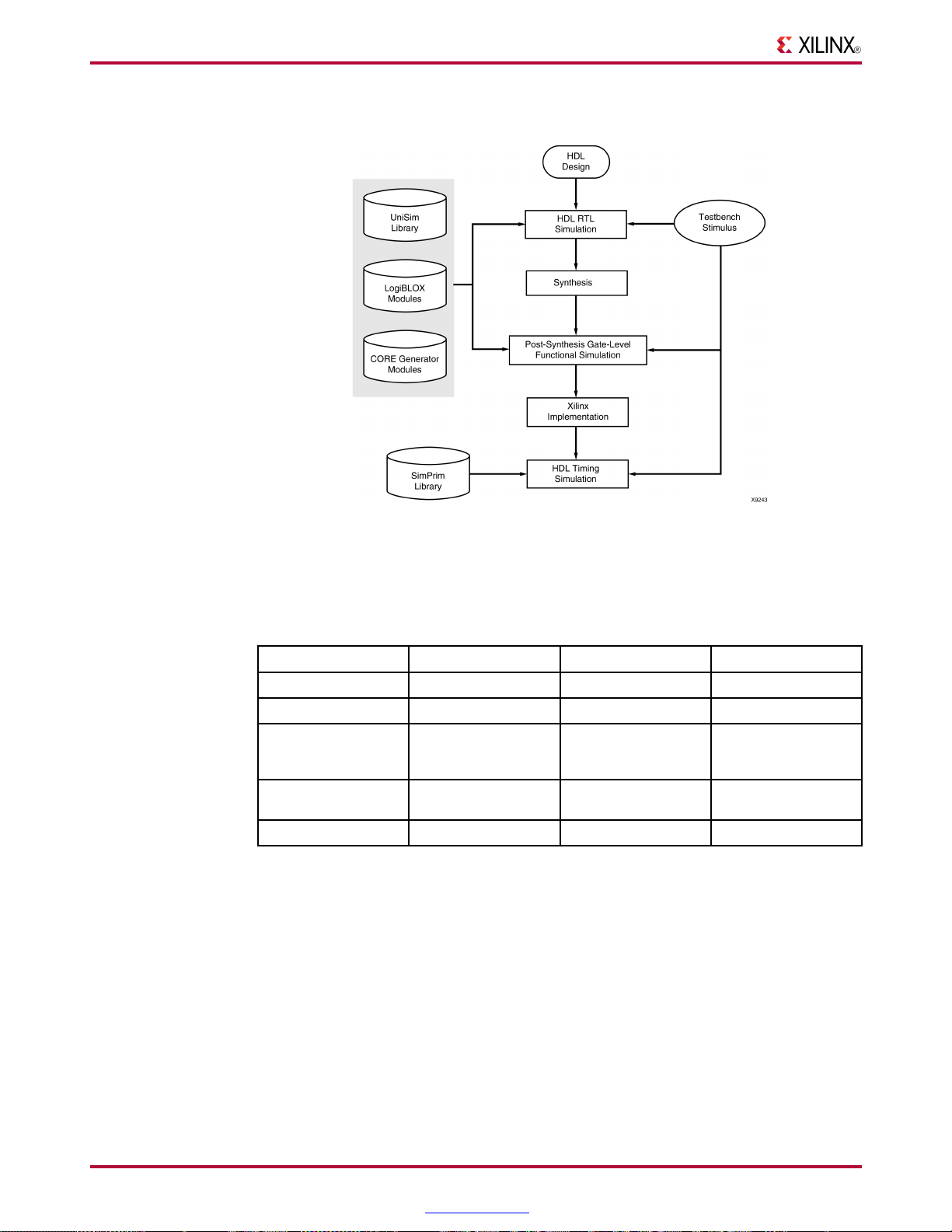

HDL-BasedSimulation

Xilinx®supportsfunctionalandtimingsimulationofHDLdesignsatthefollowing

points:

•RegisterTransferLevel(RTL)simulation,whichmayincludethefollowing:

•Post-synthesisfunctionalsimulationwithoneofthefollowing:

•Post-implementationback-annotatedtimingsimulationwiththefollowing:

Chapter2:DesignFlow

–InstantiatedUNISIMlibrarycomponents

–COREGenerator™models

–HardIP(SecureIP)

–Gate-levelUNISIMlibrarycomponents

–COREGeneratormodels

–HardIP(SecureIP)

–SIMPRIMlibrarycomponents

–HardIP(SecureIP)

–StandardDelayFormat(SDF)le

Thefollowinggureshowswhenyoucanperformfunctionalandtimingsimulation:

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 29

Chapter2:DesignFlow

SimulationPointsforHDLDesigns

Thethreeprimarysimulationpointscanbeexpandedtoallowfortwopost-synthesis

simulations.ThesepointscanbeusedifthesynthesistoolcannotwriteVHDLor

Verilog,orifthenetlistisnotintermsofUNISIMcomponents.Thefollowingtablelists

allthesimulationpointsavailableintheHDLdesignow .

FiveSimulationPointsinHDLDesignFlow

SimulationUNISIMSIMPRIMSDF

RTL

Post-Synthesis

Functional

Post-NGDBuild

(Optional)

FunctionalPost-MAP

(Optional)

Post-RouteTiming

Thesesimulationpointsaredescribedinthe“SimulationPoints”sectionoftheSynthesis

andSimulationDesignGuide(UG626).

Thelibrariesrequiredtosupportthesimulationowsaredescribedindetailin

the“VHDL/VerilogLibrariesandModels”sectionoftheSynthesisandSimulation

DesignGuide(UG626).Theowsandlibrariessupportclosefunctionalequivalenceof

initializationbehaviorbetweenfunctionalandtimingsimulations.Thisisduetothe

additionofmethodologiesandlibrarycellstosimulateGlobalSet/Reset(GSR)and

Global3-State(GTS)behavior.

X

X

X

XX

XX

XilinxVHDLsimulationsupportstheVITALstandard.Thisstandardallowsyou

tosimulatewithanyVITAL-compliantsimulator.Built-inVerilogsupportallows

youtosimulatewiththeCadenceVerilog-XLandcompatiblesimulators.XilinxHDL

simulationsupportsallcurrentXilinxFPGAandCPLDdevices.RefertotheSynthesis

andSimulationDesignGuide(UG626)forthelistofsupportedVHDLandV erilog

standards.

30w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Loading...

Loading...