UCC1919

UCC2919

UCC3919

07/99

FEATURES

•

Precision Fault Threshold

•

Charge Pump for Low RDS

ON

High Side

Drive

•

Differential Sense Inputs

•

Programmable Average Power Limiting

•

Programmable Linear Current Control

•

Programmable Fault Time

•

Fault Output Indicator

•

Manual and Automatic Reset Modes

•

Shutdown Control w/Programmable

Softstart

•

Undervoltage Lockout

• Electronic Circuit Breaker Function

3V to 8V Hot Swap Power Manager

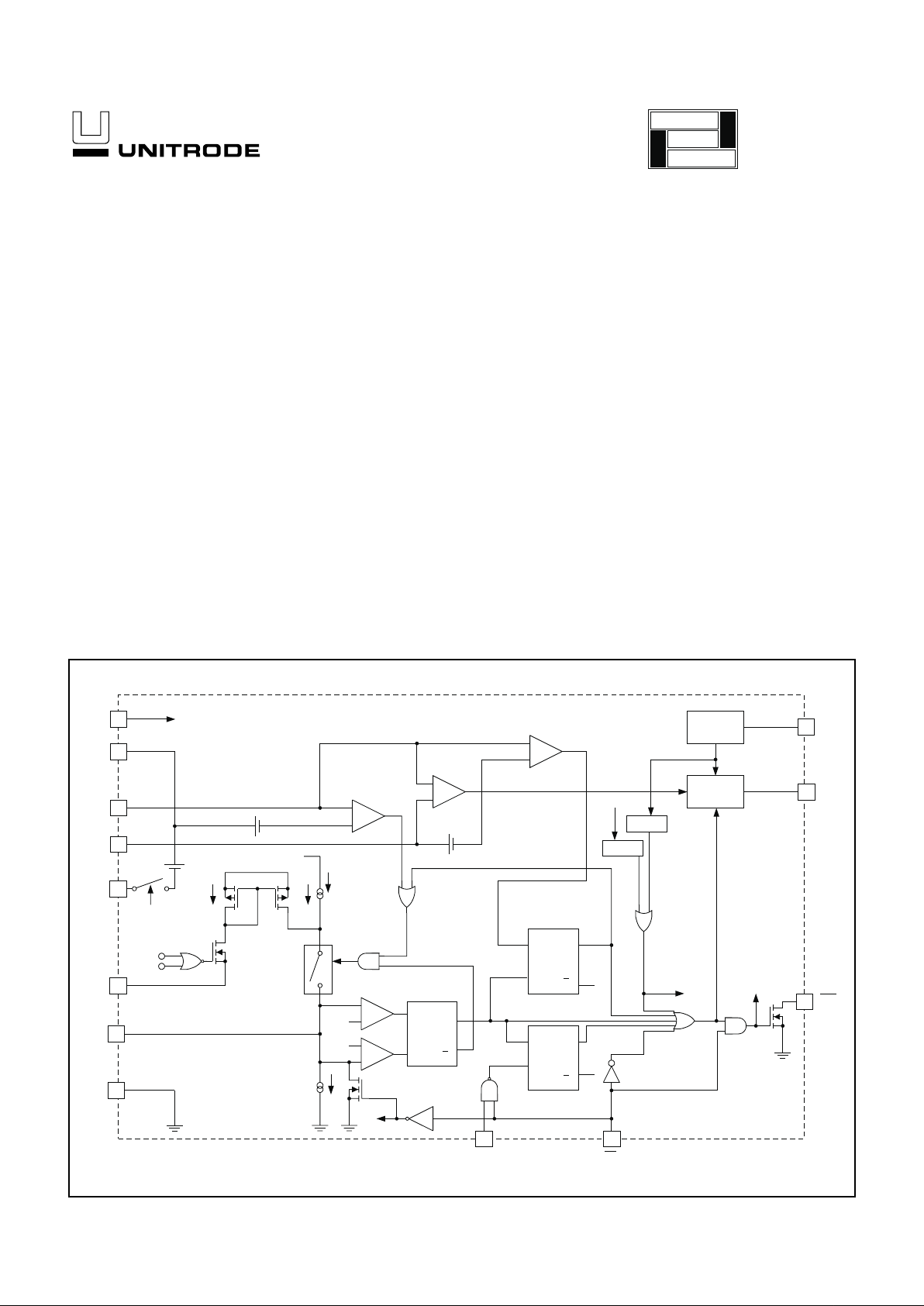

10

7

5 6

11

8

9

2

1

12

14

4

GND

CHARGE

PUMP

DRIVER

UVLO

VDD

+

–

UVLO

+

–

+

+

–

200mV

LINEAR

CURRENT

AMPLIFIER

OVERLOAD

COMPARATOR

SRQ

Q

RESET

DOMINANT

SET

DOMINANT

+

–

+

–

1.5V

0.5V

1.2µA

+

+

1.5v

13

VDD

36µA

50mV

VDD

CSP

CSN

IMAX

IBIAS

PL

CT

FLT

GATE

CAP

LR SD

UVBIAS

VDD

1X

OVERCURRENT

COMPARATOR

UVBIAS

SRQ

Q

SRQ

Q

FLT

SD

FLT

SD

1X

BLOCK DIAGRAM

UDG-98123

DESCRIPTION

The UCC3919 family of Hot Swap Power Managers provide complete

power management, hot swap, and fault handling capability. The

UCC3919 features a duty ratio current limiting technique, which pro

-

vides peak load capability while limiting the average power dissipa

tion of the external pass transistor during fault conditions. The

UCC3919 has two reset modes, selected with the TTL/CMOS com

patible L/R pin. In one mode, when a fault occurs the IC repeatedly

tries to reset itself at a user defined rate, with user defined maximum

output current and pass transistor power dissipation. In the other

mode the output latches off and stays off until either the L/R pin is re

set or the shutdown pin is toggled. The on board charge pump circuit

provides the necessary gate voltage for an external N-channel power

FET.

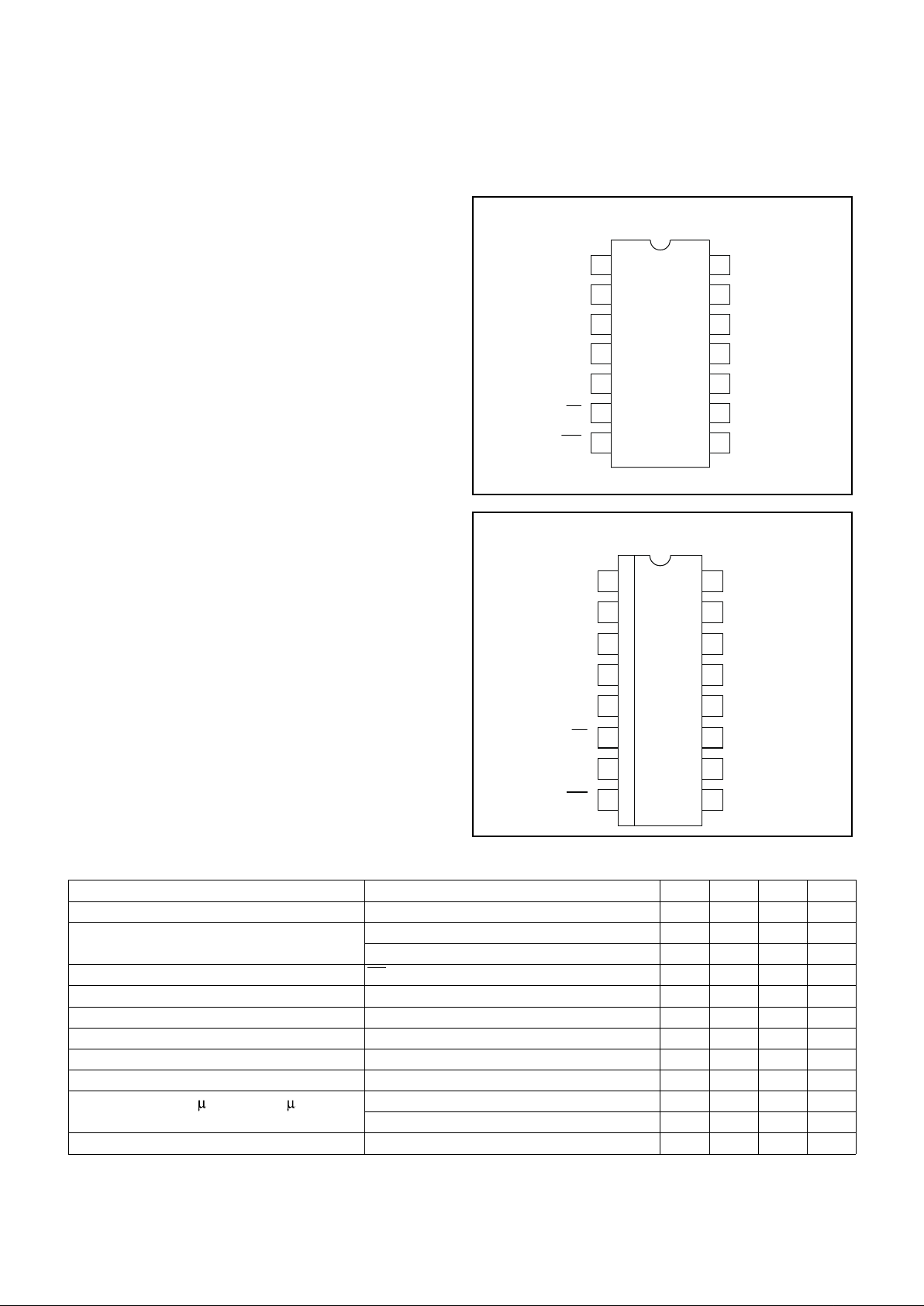

Note: Pins shown for 14-pin package.

application

INFO

available

2

UCC1919

UCC2919

UCC3919

CSN

VDD

CSP

GND

GATE

CT

PL

1

2

3

4

5

6

7

14

13

12

11

10

9

8

IBIAS

IMAX

SD

FLT

N/C

CAP

L/R

CONNECTION DIAGRAMS

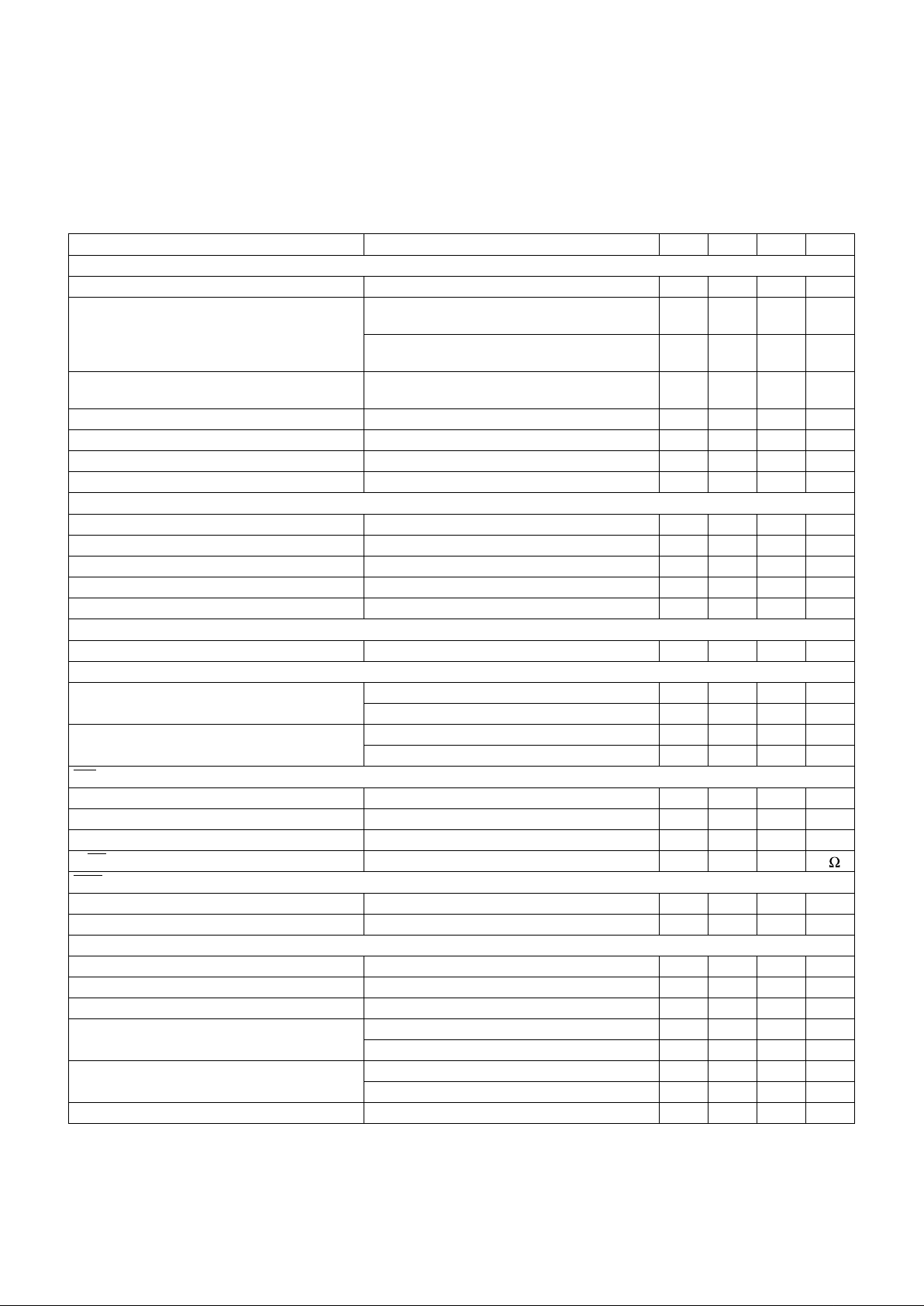

ELECTRICAL CHARACTERISTICS:

Unless otherwise specified, VDD = 5V, TA = 0°C to 70°C for the UCC3919, –40°C

to 85°C for the UCC2919 and –55°C to 125°C for the UCC1919. All voltages are with respect to GND. T

A =TJ.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Input Supply

Supply Current VDD = 3V 0.5 1 mA

VDD = 8V 1 1.5 mA

Shutdown Current SD

= 0.2V 1 7 µA

Undervoltage Lockout

Minimum Voltage to Start 2.35 2.75 3 V

Minimum Voltage after Start 1.9 2.25 2.5 V

Hysteresis 0.25 0.5 0.75 V

IBIAS

Output Voltage, (0

A < I

OUT

< 15 A) 25°C, referred to CSP 1.47 1.5 1.53 V

Over Temperature Range, referred to CSP 1.44 1.5 1.56 V

Maximum Output Current 12 mA

CSN

VDD

CSP

GND

GATE

N/C

PL

CT

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

IBIAS

IMAX

N/C

N/C

CAP

L/R

FLT

SD

DIL-14, (Top View)

N, J Packages

SOIC-16, TSSOP-16 (Top View)

D or PW Package

ABSOLUTE MAXIMUM RATINGS

VDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3V to 10V

Pin Voltage

(All pins except CAP and GATE). . . . . . –0.3V to VDD + 0.3V

Pin Voltage

(CAP and GATE) . . . . . . . . . . . . . . . . . . . . . . . . –0.3V to 15V

PL Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5mA to –10mA

IBIAS Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0mA to 3mA

Storage Temperature . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Junction Temperature. . . . . . . . . . . . . . . . . . . –55°C to +150°C

Lead Temperature (Soldering, 10sec.) . . . . . . . . . . . . . +300°C

Currents are positive into, negative out of the specified termi

-

nal. Consult Packaging Section ofDatabook for thermal limita

-

tions and considerations of package.

3

UCC1919

UCC2919

UCC3919

ELECTRICAL CHARACTERISTICS:

Unless otherwise specified, VDD = 5V, TA = 0°C to 70°C for the UCC3919, –40°C

to 85°C for the UCC2919 and –55°C to 125°C for the UCC1919. All voltages are with respect to GND. T

A =TJ.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Current Sense

Over Current Comparator Offset Referred to CSP, 3V ≤VDD ≤8V –55 –50 –45 mV

Linear Current Amplifier Offset V

IMAX

= 100mV, Referred to CSP,

3V ≤VDD ≤8V

–120 –100 –80 mV

V

IMAX

= 400mV, Referred to CSP,

3V ≤VDD ≤8V

–440 –400 –360 mV

Overload Comparator Offset V

IMAX

= 100mV, Referred to CSP,

3V ≤VDD ≤8V

–360 –300 –240 mV

CSN Input Common Mode Voltage Range Referred to VDD, 3V ≤VDD ≤8V, (Note 1) –1.5 0.2 V

CSP Input Common Mode Voltage Range Referred to VDD, 3V ≤VDD ≤8V, (Note 1) 0 0.2 V

Input Bias Current CSN 15µA

Input Bias Current CSP 100 200 µA

Current Fault Timer

CT Charge Current V

CT

= 1V –56 –35 –16 µA

CT Discharge Current V

CT

= 1V 0.5 1.2 1.9 µA

On Time Duty Cycle in Fault I

PL

= 0 1.5 3 6 %

CT Fault Threshold 1.0 1.5 1.7 V

CT Reset Threshold 0.25 0.5 0.75 V

IMAX

Input Bias Current V

IMAX

= 100mV, Referred to CSP –1 0 1 µA

Power Limiting Section

Voltage on PL I

PL

= –250µA, Referred to VDD –1.0 –1.4 –1.9 V

I

PL

= –1.5mA, Referred to VDD –0.5 –1.8 –2.2 V

On Time Duty Cycle in Fault I

PL

= –250µA 0.25 0.5 1 %

I

PL

= –1.5mA 0.05 0.1 0.2 %

SD

and L/R Inputs

Input Voltage Low 0.8 V

Input Voltage High 2V

L/R Input Current 136µA

SD

Internal Pulldown Impedance 100 270 500 k

FLT Output

Output Leakage Current VDD = 5V 10 µA

Output Low Voltage I

OUT

= 10mA 1 V

FET GATE Driver and Charge Pump

Peak Output Current V

CAP

= +15V, V

GATE

= 10V –3 –1 –0.25 mA

Peak Sink Current V

GATE

= 5V 20 mA

Fault Delay 100 300 nS

Maximum Output Voltage VDD = 3V, Average I

OUT

= 1µA 8 10 12 V

VDD = 8V, Average I

OUT

= 1µA 121416 V

Charge Pump UVLO Minimum Voltage to

Start

VDD = 3V 6.5 7.5 V

VDD = 8V 6.5 8 V

Charge Pump Source Impedance VDD = 5V, Average I

OUT

= 1µA 50 100 150 kΩ

Note 1: Guaranteed by design.Not 100% tested in production.

4

UCC1919

UCC2919

UCC3919

PIN DESCRIPTIONS

CAP: A capacitor is placed from this pin to ground to fil

-

ter the output of the on board charge pump. A .01µFto

0.1µF capacitor is recommended .

CSN: The negative current sense input signal.

CSP: The positive current sense input signal.

CT: Input to the duty cycle timer. A capacitor is con

nected from this pin to ground, setting the off time and

the maximum on time of the overcurrent protection cir

cuits.

FLT

: Fault indicator. This open drain output will pull low

under any fault condition where the output driver is dis

abled. This output is disabled when the IC is in low cur

rent standby mode.

GATE: The output of the linear current amplifier. This pin

drives the gate of an external N-channel MOSFET pass

transistor. The linear current amplifier control loop is in

ternally compensated, and guaranteed stable for output

load (gate) capacitance between 100pF and .01µF. In

applications where the GATE voltage (or charge pump

voltage) exceeds the maximum Gate-to-Source voltage

ratings (V

GS

) for the external N-channel MOSFET, a

Zener clamp may be added to the gate of the MOSFET.

No additional series resistance is required since the internal charge pump has a finite output impedance of

100k

typical.

GND: The ground reference for the device.

IBIAS: Output of the on board bias generator internally

regulated to 1.5V below CSP. A resistor divider between

this pin and CSP can be used to generate the IMAX volt

-

age. The bias circuit is internally compensated, and re

quires no bypass capacitance. If an external bypass is

required due to a noisy environment, the circuit will be

stable with up to .001µF of capacitance. The bypass

must be to CSP, since the bias voltage is generated with

respect to CSP. Resistor R2 (Figure 4) should be greater

than 50k

to minimize the effect of the finite input imped

-

ance of the IBIAS pin on the IMAX threshold.

IMAX: Used to program the maximum allowable sourcing

current. The voltage on this pin is with respect to CSP. If

the voltage across the shunt resistor exceeds this voltage

the linear current amplifier lowers the voltage at GATE to

limit the output current to this level. If the voltage across

the shunt resistor goes more than 200mV beyond this

voltage, the gate drive pin GATE is immediately driven

low and kept low for one full off time interval.

L/R: Latch/Reset. This pin sets the reset mode. If L/R is

low and a fault occurs the device will begin duty ratio cur

rent limiting. If L/R is high and a fault occurs, GATE will

go low and stay low until L/R is set low. This pin is inter

nally pulled low by a 3µA nominal pulldown.

PL: Power Limit. This pin is used to control average

power dissipation in the external MOSFET.If a resistor is

connected from this pin to the source of the external

MOSFET, the current in the resistor will be roughly proportional to the voltage across the FET. As the voltage

across the FET increases, this current is added to the

fault timer charge current, reducing the on time duty cycle from its nominal value of 3% and limiting the average

power dissipation in the FET.

SD

: Shutdown pin. If this pin is taken low, GATE will go

low, and the IC will go into a low current standby mode

and CT will be discharged. This TTL compatible input

must be driven high to turn on.

VDD: The power connection for the device.

The UCC3919 monitors the voltage drop across a high

side sense resistor and compares it against three differ

-

ent voltage thresholds. These are discussed below. Fig

ure 1 shows the UCC3919 waveforms under fault

conditions.

Fault Threshold

The first threshold is fixed at 50mV. If the current is high

enough such that the voltage on CSN is 50mV below

CSP, the timing capacitor C

T begins to charge at about

35µA if the PL pin is open. (Power limiting will be dis

cussed later). If this threshold is exceeded long enough

for C

T

to charge to 1.5V, a fault is declared and the exter

-

nal MOSFET will be turned off. It will either be latched off

(until the power to the circuit is cycled, the L/R pin is

taken low, or the SD

pin is toggled), or will retry after a

fixed off time (when C

T has discharged to 0.5V), depend

ing on whether the L/R pin is set high or low by the user.

The equation for this current threshold is simply:

I

R

FAULT

SENSE

=

005.

(1)

The first time a fault occurs, C

T is at ground, and must

charge 1.5V. Therefore:

()

tt

CF

FAULT ON

T

==

•

(sec)

.µ 15

35

(2)

APPLICATION INFORMATION

Loading...

Loading...