Texas Instruments TL16C550BFNR, TL16C550BFN, TL16C550BPTR, TL16C550BPT, TL16C550BIPT Datasheet

...

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Capable of Running With All Existing

TL16C450 Software

D

After Reset, All Registers Are Identical to

the TL16C450 Register Set

D

In the FIFO Mode, Transmitter and Receiver

Are Each Buffered With 16-Byte FIFOs to

Reduce the Number of Interrupts to the

CPU

D

In the TL16C450 Mode, Hold and Shift

Registers Eliminate the Need for Precise

Synchronization Between the CPU and

Serial Data

D

Programmable Baud Rate Generator Allows

Division of Any Input Reference Clock by 1

to (2

16

–1) and Generates an Internal 16×

Clock

D

Standard Asynchronous Communication

Bits (Start, Stop, and Parity) Added to or

Deleted From the Serial Data Stream

D

Independent Receiver Clock Input

D

Transmit, Receive, Line Status, and Data

Set Interrupts Independently Controlled

D

Fully Programmable Serial Interface

Characteristics:

– 5-, 6-, 7-, or 8-Bit Characters

– Even-, Odd-, or No-Parity Bit Generation

and Detection

– 1-, 1 1/2-, or 2-Stop Bit Generation

– Baud Generation (DC to 562 Kbit/s)

D

False-Start Bit Detection

D

Complete Status Reporting Capabilities

D

3-State Outputs Provide TTL Drive

Capabilities for Bidirectional Data Bus and

Control Bus

D

Line Break Generation and Detection

D

Internal Diagnostic Capabilities:

– Loopback Controls for Communications

Link Fault Isolation

– Break, Parity , Overrun, Framing Error

Simulation

D

Fully Prioritized Interrupt System Controls

D

Modem Control Functions (CTS, RTS, DSR,

DTR

, RI, and DCD)

D

Faster Plug-In Replacement for National

Semiconductor NS16550A

description

The TL16C550B and the TL16C550BI are functional upgrades of the TL16C450 asynchronous

communications element (ACE). Functionally identical to the TL16C450 on power up (character mode

†

), the

TL16C550B and TL16C550BI can be placed in an alternate mode (FIFO) to relieve the CPU of excessive

software overhead.

In this alternate FIFO mode, internal FIFOs are activated allowing 16 bytes (plus 3 bits of error data per byte

in the receiver FIFO) to be stored in both receive and transmit modes. To minimize system overhead and

maximize system efficiency, all logic is on the chip. Two of the TL16C450 terminal functions (RXRDY

and

TXRDY

) have been changed to allow signalling of DMA transfers.

The TL16C550B and the TL16C550BI perform serial-to-parallel conversions on data received from a peripheral

device or modem and parallel-to-serial conversion on data received from its CPU. The CPU can read and report

on the status of the ACE at any point in the ACE operation. Reported status information includes: the type of

transfer operation in progress, the status of the operation, and any error conditions encountered.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

†The TL16C550B and the TL16C550BI can also be reset to the TL16C450 mode under software control.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright 1996, Texas Instruments Incorporated

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description (continued)

The TL16C550B and the TL16C550BI ACE include programmable, on-board, baud rate generators. These

generators are capable of dividing a reference clock input by divisors from 1 to (2

16

–1) and producing a 16×

clock for driving the internal transmitter logic. Provisions are included to use this 16× clock to drive the receiver

logic. Also included in the ACE is a complete modem control capability and a processor interrupt system that

may be software tailored to user requirements to minimize the computing required to handle the

communications link.

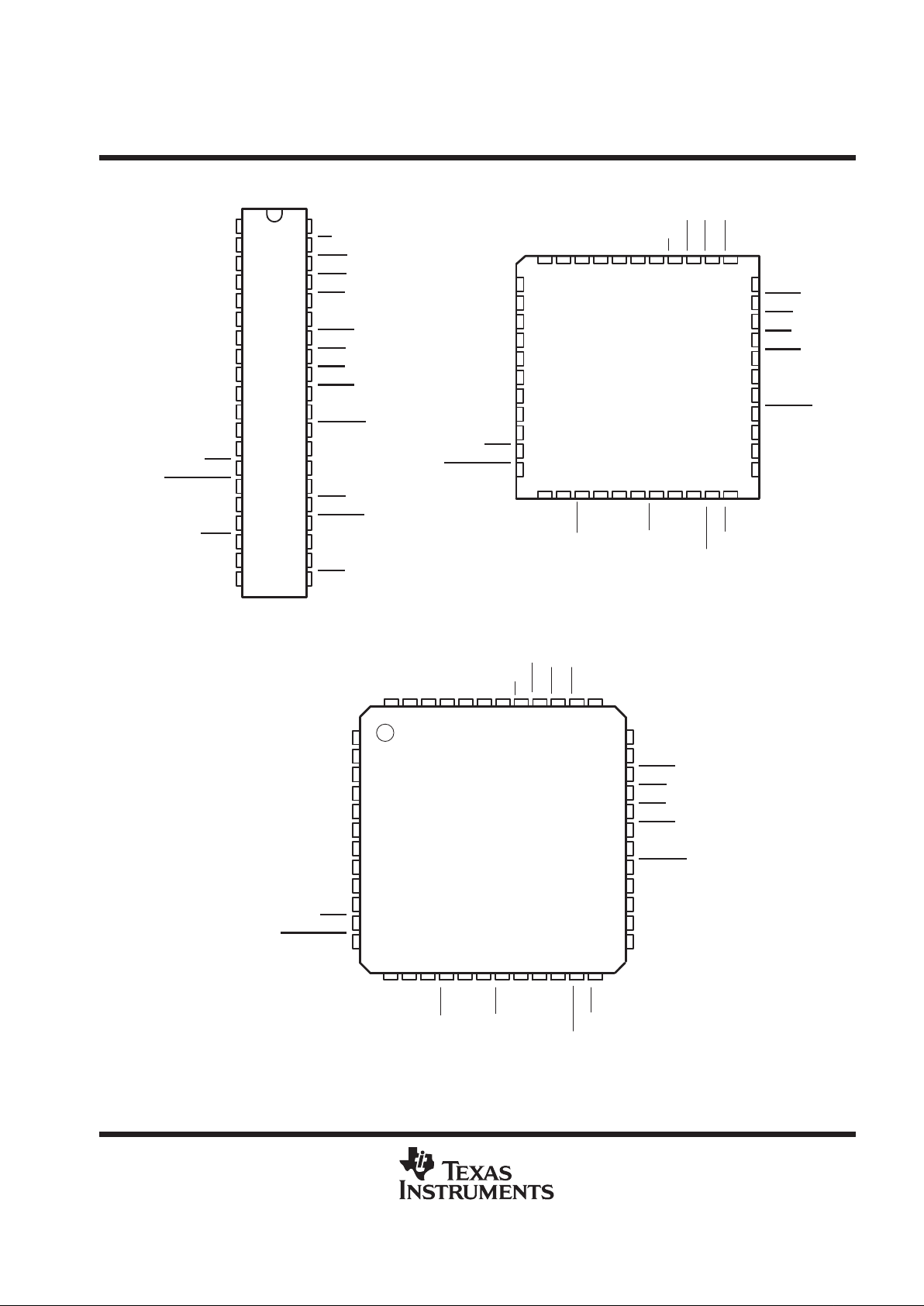

The TL16C550B is available in a 40-pin DIP (N) package, 44-pin PLCC (FN) package, and 48-pin TQFP (PT)

package. The TL16C550BI is available in a 44-pin PLCC (FN) package.

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

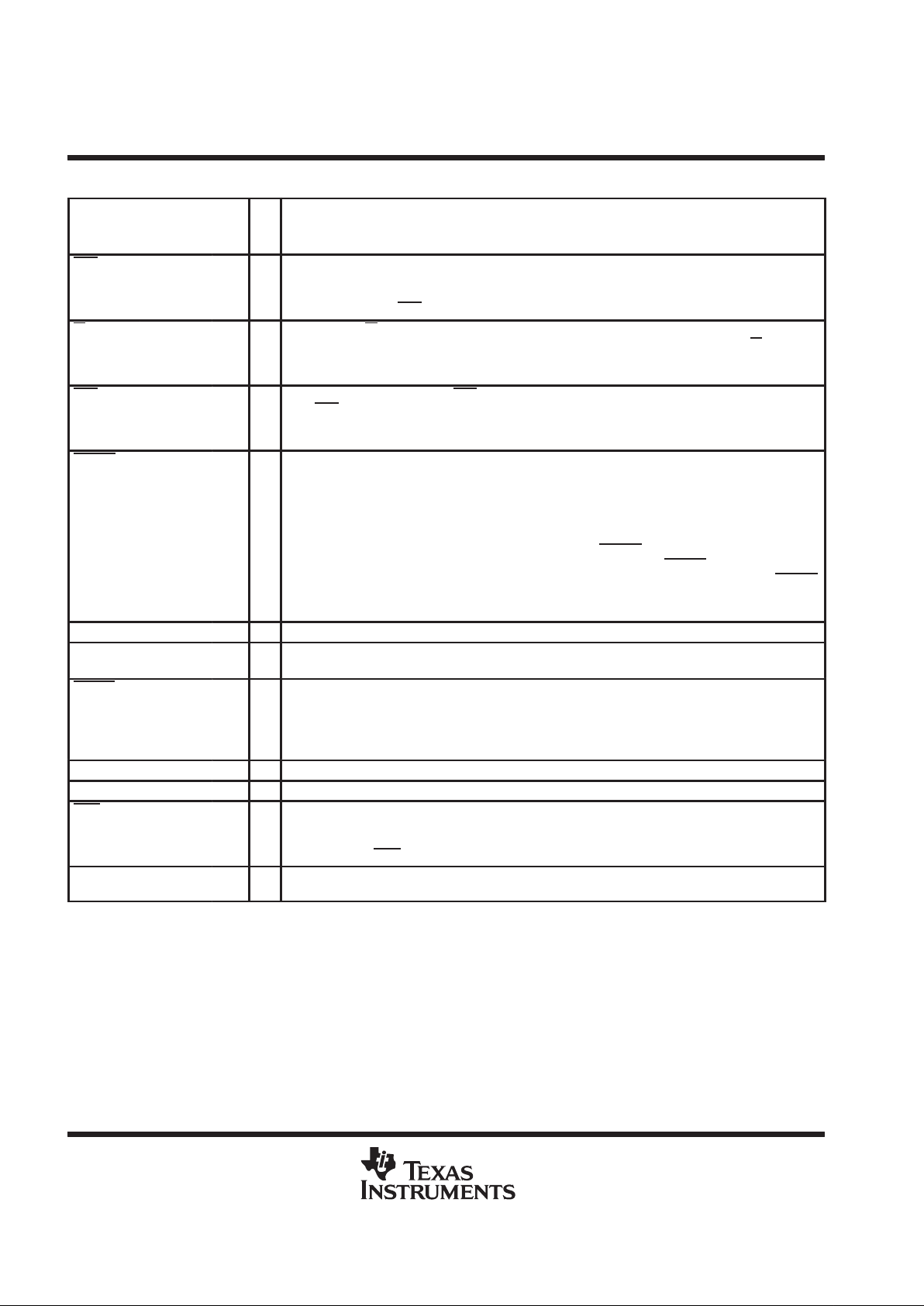

D0

D1

D2

D3

D4

D5

D6

D7

RCLK

SIN

SOUT

CS0

CS1

CS2

BAUDOUT

XIN

XOUT

WR1

WR2

V

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

V

CC

RI

DCD

DSR

CTS

MR

OUT1

DTR

RTS

OUT2

INTRPT

RXRDY

A0

A1

A2

ADS

TXRDY

DDIS

RD2

RD1

N PACKAGE

(TOP VIEW)

MR

OUT1

DTR

RTS

OUT2

NC

INTRPT

RXRDY

A0

A1

A2

39

38

37

36

35

34

33

32

31

30

29

18 19

7

8

9

10

11

12

13

14

15

16

17

D5

D6

D7

RCLK

SIN

NC

SOUT

CS0

CS1

CS2

BAUDOUT

20 21 22 23

RI

DCD

DSR

CTS

54 321644

D4D3D2D1D0NCV

RD2

DDIS

TXRDY

ADS

XIN

XOUT

WR1

WR2

NC

RD1

42 41 4043

24 25 26 27 28

NC–No internal connection

CC

V

SS

FN PACKAGE

(TOP VIEW)

14 15

NC

MR

OUT1

DTR

RTS

OUT2

INTRPT

RXRDY

A0

A1

A2

NC

36

35

34

33

32

31

30

29

28

27

26

25

16

1

2

3

4

5

6

7

8

9

10

11

12

NC

D5

D6

D7

RCLK

NC

SIN

SOUT

CS0

CS1

CS2

BAUDOUT

17 18 19 20

PT PACKAGE

(TOP VIEW)

RI

DCD

DSR

CTS

47 46 45 44 4348 42

NCD4D3D2D1

D0

DDIS

TXRDY

ADS

XOUT

WR1

WR2

RD1

RD2

NC

40 39 3841

21

22 23 24

37

13

NC

NC

V

CC

XIN

V

SS

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

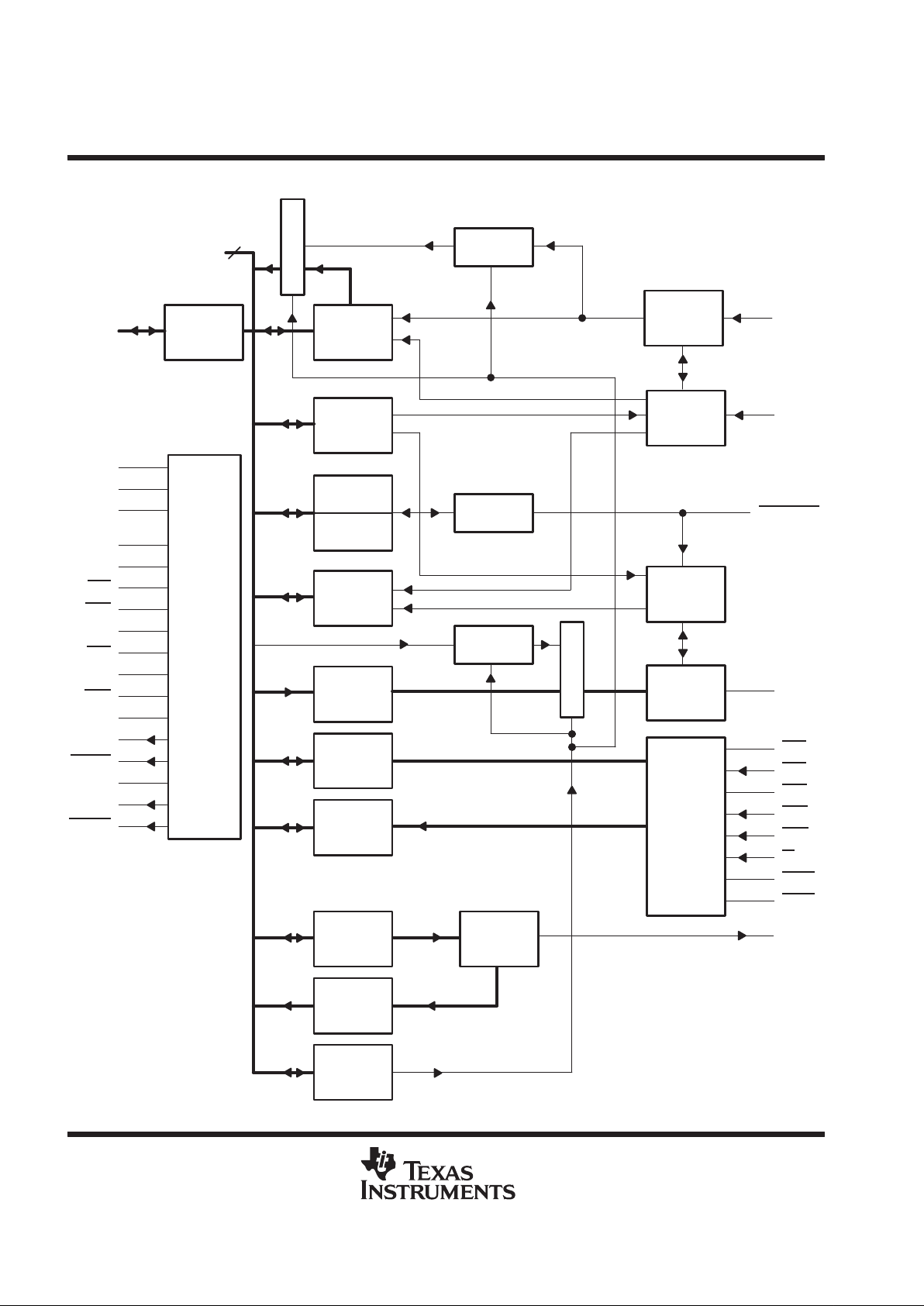

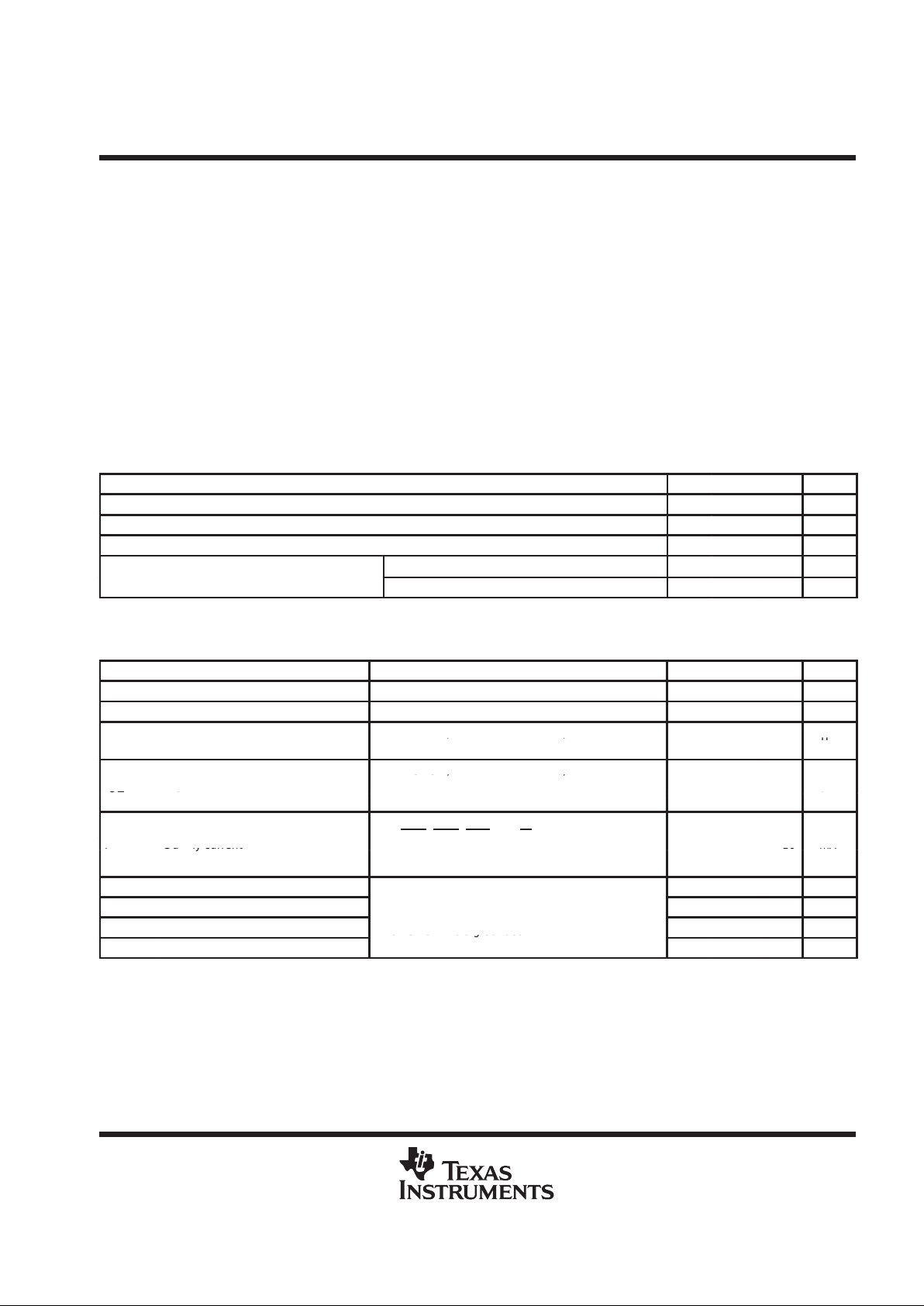

functional block diagram

Receiver

Buffer

Register

Divisor

Latch (LS)

Divisor

Latch (MS)

Baud

Generator

Receiver

FIFO

Line

Status

Register

Transmitter

Holding

Register

Modem

Control

Register

Modem

Status

Register

Line

Control

Register

Transmitter

FIFO

Interrupt

Enable

Register

Interrupt

I/O

Register

FIFO

Control

Register

Select

and

Control

Logic

Interrupt

Control

Logic

S

e

l

e

c

t

Data

Bus

Buffer

BAUDOUT

SIN

RCLK

SOUT

RTS

CTS

DTR

DSR

DCD

RI

OUT1

OUT2

INTRPT

32

36

33

37

38

39

34

31

30

11

9

10

15

12

A0

28

D7–D0

8–1

Internal

Data Bus

27

26

13

14

25

35

21

22

18

19

23

24

16

17

29

A1

A2

CS0

CS1

CS2

ADS

MR

RD1

RD2

WR1

WR2

DDIS

TXRDY

XIN

XOUT

RXRDY

S

e

l

e

c

t

Receiver

Shift

Register

Receiver

Timing and

Control

Line

Control

Register

Line

Control

Register

Modem

Control

Logic

8

Terminal numbers shown are for the N package.

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

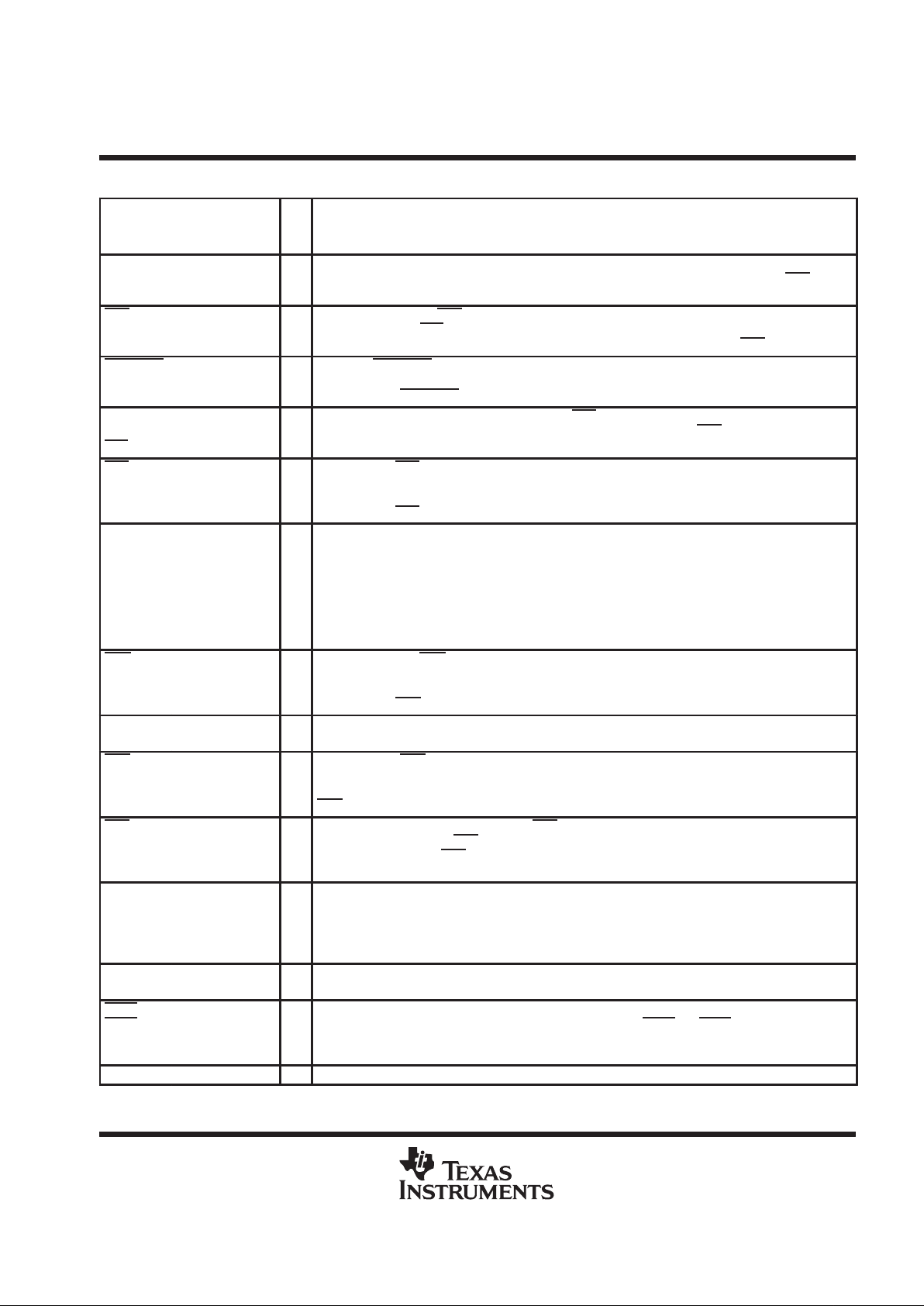

Terminal Functions

TERMINAL

NAME

NO.NNO.FNNO.

PT

I/O

DESCRIPTION

A0

A1

A2

28

27

26

31

30

29

28

27

26

I Register select. A0–A2 are used during read and write operations to select the ACE register to read

from or write to. Refer to Table 1 for register addresses, and refer to the address strobe (ADS

) signal

description.

ADS 25 28 24 I Address strobe. When ADS is active (low), the register select signals (A0, A1, and A2) and chip select

signals (CS0, CS1, CS2

) drive the internal select logic directly; when high, the register select and chip

select signals are held in the state they are in when the low-to-high transition of ADS

occurs.

BAUDOUT 15 17 12 O Baud out. BAUDOUT is a 16× clock signal for the transmitter section of the ACE. The clock rate is

established by the reference oscillator frequency divided by a divisor specified by the baud generator

divisor latches. BAUDOUT

can also be used for the receiver section by tying this output to RCLK.

CS0

CS1

CS2

12

13

14

14

15

16

9

10

11

I Chip select. When CS0 = high, CS1 = high, and CS2 = low, these three inputs select the ACE. When

any of these inputs are inactive, the ACE remains inactive. Refer to the ADS

signal description.

CTS 36 40 38 I Clear to send. CTS is a modem status signal. Its condition can be checked by reading bit 4 (CTS) of

the modem status register. Bit 0 (∆CTS) of the modem status register indicates that this signal has

changed states since the last read from the modem status register. If the modem status interrupt is

enabled when CTS

changes state, an interrupt is generated.

D0

D1

D2

D3

D4

D5

D6

D7

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

9

43

44

45

46

47

2

3

4

I/O Data bus. Eight data lines with 3-state outputs provide a bidirectional path for data, control, and status

information between the ACE and the CPU.

DCD 38 42 40 I Data carrier detect. DCD is a modem status signal. Its condition can be checked by reading bit 7 (DCD)

of the modem status register. Bit 3 (∆DCD) of the modem status register indicates that this signal has

changed states since the last read from the modem status register. If the modem status interrupt is

enabled when DCD

changes state, an interrupt is generated.

DDIS 23 26 22 O Driver disable. This output is active (high) when the CPU is not reading data. When active, this output

can disable an external transceiver.

DSR 37 41 39 I Data set ready. DSR is a modem status signal. Its condition can be checked by reading bit 5 (DSR) of

the modem status register. Bit 1 (∆DSR) of the modem status register indicates this signal has changed

states since the last read from the modem status register. If the modem status interrupt is enabled when

DSR

changes state, an interrupt is generated.

DTR 33 37 33 O Data terminal ready. When active (low), DTR informs a modem or data set that the ACE is ready to

establish communication. DTR

is placed in the active state by setting the DTR bit of the modem control

register to a high level. DTR

is placed in the inactive state either as a result of a master reset, during

loop mode operation, or clearing the DTR bit.

INTRPT 30 33 30 O Interrupt. When active (high), INTRPT informs the CPU that the ACE has an interrupt to be serviced.

Four conditions that cause an interrupt to be issued are: a receiver error, received data is available or

timed out (FIFO mode only), the transmitter holding register is empty, or an enabled modem status

interrupt. The INTRPT output is reset (deactivated) either when the interrupt is serviced or as a result

of a master reset.

MR 35 39 35 I Master reset. When active (high), MR clears most ACE registers and sets the state of various output

signals. Refer to Table 2.

OUT1

OUT2

343138353431O Outputs 1 and 2. User-designated outputs that are set to their active low states by setting their

respective modem control register bits (OUT1 and OUT2) high. OUT1

and OUT2 are set to their inactive

(high) states as a result of master reset, during loop mode operations, or by clearing bit 2 (OUT1) or

bit 3 (OUT2) of the modem control register.

RCLK 9 10 5 I Receiver clock. RCLK is the 16× baud rate clock for the receiver section of the ACE.

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Terminal Functions (Continued)

TERMINAL

NAME

NO.NNO.FNNO.

PT

I/O

DESCRIPTION

RD1

RD2

212224251920I Read inputs. When either input is active (low or high respectively) while the ACE is selected, the CPU

is allowed to read status information or data from a selected ACE register. Only one of these inputs is

required for the transfer of data during a read operation; the other input should be tied in its inactive state

(i.e., RD2 tied low or RD1

tied high).

RI 39 43 41 I Ring indicator. RI is a modem status signal. Its condition can be checked by reading bit 6 (RI) of the

modem status register. Bit 2 (TERI) of the modem status register indicates that the RI

input has

transitioned from a low to a high state since the last read from the modem status register. If the modem

status interrupt is enabled when this transition occurs, an interrupt is generated.

RTS 32 36 32 O Request to send. When active, RTS informs the modem or data set that the ACE is ready to receive

data. RTS

is set to its active state by setting the RTS modem control register bit and is set to its inactive

(high) state either as a result of a master reset or during loop mode operations or by clearing bit 1 (RTS)

of the MCR.

RXRDY 29 32 29 O Receiver ready output. Receiver direct memory access (DMA) signalling is available with this terminal.

When operating in the FIFO mode, one of two types of DMA signalling can be selected using the FIFO

control register bit 3 (FCR3). When operating in the TL16C450 mode, only DMA mode 0 is allowed.

Mode 0 supports single-transfer DMA in which a transfer is made between CPU bus cycles. Mode 1

supports multitransfer DMA in which multiple transfers are made continuously until the receiver FIFO

has been emptied. In DMA mode 0 (FCR0 = 0 or FCR0 = 1, FCR3 = 0), when there is at least one

character in the receiver FIFO or receiver holding register, RXRDY

is active low. When RXRDY has

been active but there are no characters in the FIFO or holding register, RXRDY

goes inactive (high).

In DMA mode 1 (FCR0 = 1, FCR3 = 1), when the trigger level or the timeout has been reached, RXRDY

goes active (low); when it has been active but there are no more characters in the FIFO or holding

register, it goes inactive (high).

SIN 10 11 7 I Serial data input. Input from a connected communications device

SOUT 11 13 8 O Composite serial data output. Output to a connected communication device. SOUT is set to the marking

(set) state as a result of master reset.

TXRDY 24 27 23 O T ransmitter ready output. Transmitter DMA signalling is available with this terminal. When operating in

the FIFO mode, one of two types of DMA signalling can be selected using FCR3. When operating in

the TL16C450 mode, only DMA mode 0 is allowed. Mode 0 supports single-transfer DMA in which a

transfer is made between CPU bus cycles. Mode 1 supports multitransfer DMA in which multiple

transfers are made continuously until the transmit FIFO has been filled.

V

CC

40 44 42 5-V supply voltage

V

SS

20 22 18 Supply common

WR1

WR2

181920211617I Write inputs. When either input is active (high or low respectively) and while the ACE is selected, the

CPU is allowed to write control words or data into a selected ACE register. Only one of these inputs is

required to transfer data during a write operation; the other input should be tied in its inactive state (i.e.,

WR2 tied low or WR1

tied high).

XIN

XOUT

161718191415I/O External clock. XIN and XOUT connect the ACE to the main timing reference (clock or crystal).

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage range, V

CC

(see Note 1) –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range at any input, V

I

–0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, V

O

–0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total power dissipation at (or below) 70°C 300 mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: TL16C550B 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TL16C550BI –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Case temperature for 10 seconds, T

C

: FN package 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: N or PT package 260°C. . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to VSS (ground).

recommended operating conditions

MIN NOM MAX UNIT

Supply voltage, V

CC

4.75 5 5.25 V

High-level input voltage, V

IH

2 V

CC

V

Low-level input voltage, V

IL

–0.5 0.8 V

p

p

TL16C550B 0 70 °C

O erating free-air tem erature, T

A

TL16C550BI –40 85 °C

electrical characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

V

OH

‡

High-level output voltage IOH = –1 mA 2.4 V

V

OL

‡

Low-level output voltage IOL = 1.6 mA 0.4 V

p

V

= 5.25 V , V

= 0,

IlInput current

CC

,

VI = 0 to 5.25 V,

SS

,

All other terminals floating

10µA

V

= 5.25 V

,

V

= 0

,

I

OZ

High-impedance-state output current

V

CC

5.25 V, V

SS

0,

VO = 0 to 5.25 V,

±20 µA

OZ

g

O

Chip selected in write mode or chip deselect

µ

°

V

CC

= 5.25 V,

T

A

=

25 C

,

I

Supply current

SIN, DSR, DCD, CTS, and RI at 2 V

,

10 mA

ICCSu ly current

All oth

er inputs at 0.8 V,

XTAL1 at 4 MH

z,

10

mA

No load on outputs, Baud rate = 50 kbit/s

C

i(CLK)

Clock input capacitance 15 20 pF

C

o(CLK)

Clock output capacitance

VCC = 0, VSS = 0,

°

20 30 pF

C

i

Input capacitance

f

= 1

MHz

,

T

A

=

25°C

,

All other terminals

g

rounded

6 10 pF

C

o

Output capacitance

All other terminals grounded

10 20 pF

†

All typical values are at VCC = 5 V, TA = 25°C.

‡

These parameters apply for all outputs except XOUT.

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

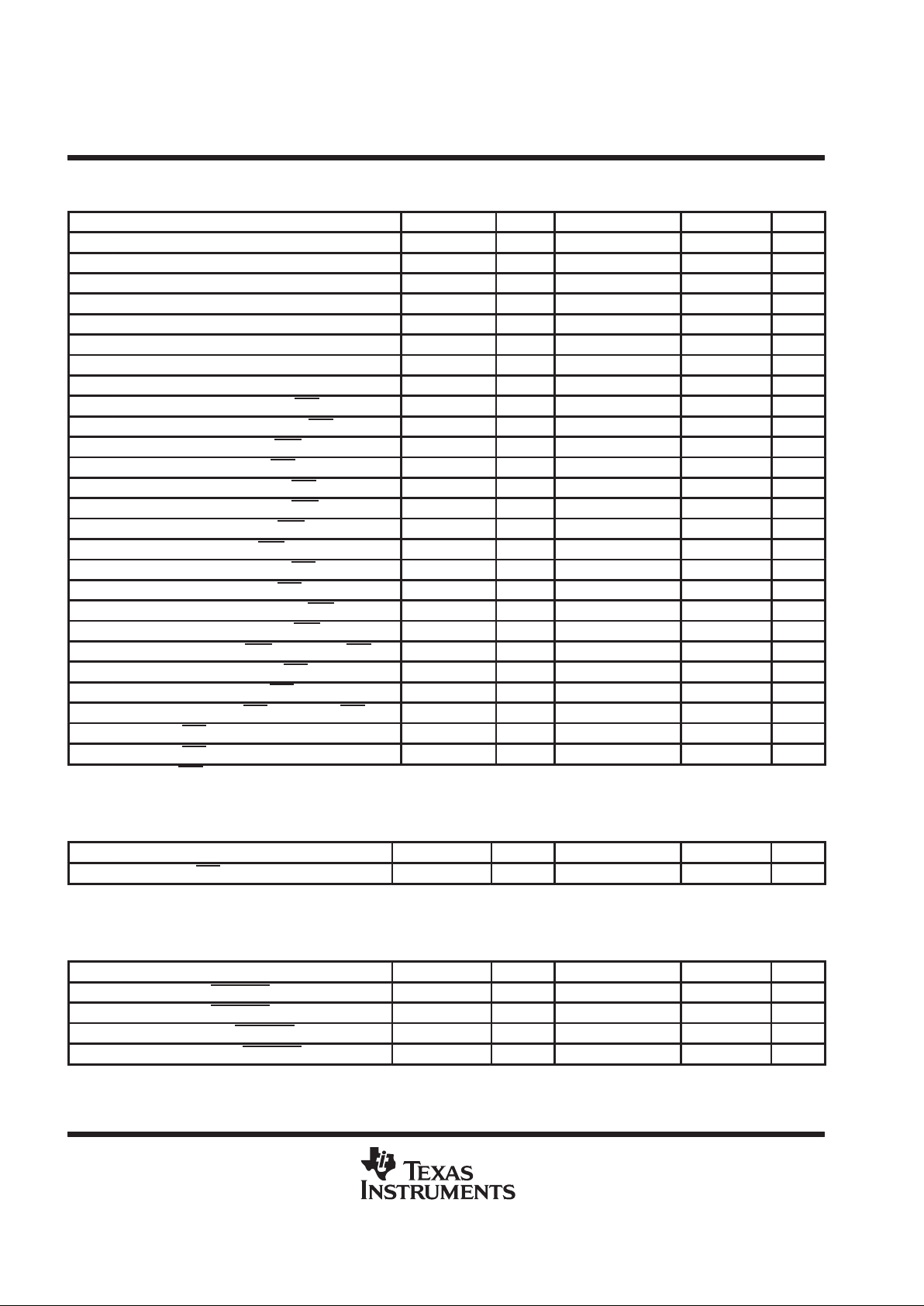

system timing requirements over recommended ranges of supply voltage and operating free-air

temperature

PARAMETER ALT. SYMBOL FIGURE TEST CONDITIONS MIN MAX UNIT

t

cR

Cycle time, read (tw7 + td8 + td9) RC 87 ns

t

cW

Cycle time, write (tw6 + td5 + td6) WC 87 ns

t

w1

Pulse duration, clock high t

XH

1 f = 9 MHz maximum 40 ns

t

w2

Pulse duration, clock low t

XL

1 f = 9 MHz maximum 40 ns

t

w5

Pulse duration, address strobe low t

ADS

2,3 9 ns

t

w6

Pulse duration, write strobe t

WR

2 40 ns

t

w7

Pulse duration, read strobe tRD 3 40 ns

t

w8

Pulse duration, master reset t

MR

1 µs

t

su1

Setup time, address valid before ADS↑ t

AS

2,3 8 ns

t

su2

Setup time, chip select valid before ADS↑ t

CS

2,3 8 ns

t

su3

Setup time, data valid before WR1↓ or WR2↑ t

DS

2 15 ns

t

h1

Hold time, address low after ADS↑ t

AH

2,3 0 ns

t

h2

Hold time, chip select valid after ADS↑ t

CH

2,3 0 ns

t

h3

Hold time, chip select valid after WR1↑ or WR2↓ t

WCS

2 10 ns

t

h4

Hold time, address valid after WR1↑ or WR2↓ t

WA

2 10 ns

t

h5

Hold time, data valid after WR1↑ or WR2↓ t

DH

2 5 ns

t

h6

Hold time, chip select valid after RD1↑ or RD2↓ t

RCS

3 10 ns

t

h7

Hold time, address valid after RD1↑ or RD2↓ t

RA

3 20 ns

t

d4

†

Delay time, chip select valid before WR1↓ or WR2↑ t

CSW

2 7 ns

t

d5

†

Delay time, address valid before WR1↓ or WR2↑ t

AW

2 7 ns

t

d6

†

Delay time, write cycle, WR1↑ or WR2↓ to ADS↓ t

WC

2 40 ns

t

d7

†

Delay time, chip select valid to RD1↓ or RD2↑ t

CSR

3 7 ns

t

d8

†

Delay time, address valid to RD1↓ or RD2↑ t

AR

3 7 ns

t

d9

Delay time, read cycle, RD1↑ or RD2↓ to ADS↓ tRC 3 40 ns

t

d10

Delay time, RD1↓ or RD2↑ to data valid t

RVD

3 CL = 75 pF 45 ns

t

d11

Delay time, RD1↑ or RD2↓ to floating data t

HZ

3 CL = 75 pF 20 ns

†

Only applies when ADS is low

system switching characteristics over recommended ranges of supply voltage and operating

free-air temperature (see Note 2)

PARAMETER ALT. SYMBOL FIGURE TEST CONDITIONS MIN MAX UNIT

t

dis(R)

Disable time, RD1↑↓ or RD2↓↑ to DDIS↑↓ t

RDD

3 CL = 75 pF 20 ns

NOTE 2: Charge and discharge time is determined by VOL, VOH, and external loading.

baud generator switching characteristics over recommended ranges of supply voltage and

operating free-air temperature, C

L

= 75 pF

PARAMETER ALT. SYMBOL FIGURE TEST CONDITIONS MIN MAX UNIT

t

w3

Pulse duration, BAUDOUT low t

LW

1 f = 9 MHz, CLK ÷ 2 80 ns

t

w4

Pulse duration, BAUDOUT high t

HW

1 f = 9 MHz, CLK ÷ 2 80 ns

t

d1

Delay time, XIN↑ to BAUDOUT↑ t

BLD

1 75 ns

t

d2

Delay time, XIN↑↓ to BAUDOUT↓ t

BHD

1 65 ns

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

receiver switching characteristics over recommended ranges of supply voltage and operating

free-air temperature (see Note 3)

PARAMETER ALT. SYMBOL FIGURE TEST CONDITIONS MIN MAX UNIT

t

d12

Delay time, RCLK to sample t

SCD

4 10 ns

t

d13

Delay time, stop to set interrupt or read

RBR to LSI interrupt or stop to RXRDY

↓

t

SINT

4,5,6,7,8 1

RCLK

cycle

t

d14

Delay time, read RBR/LSR to reset interrupt low t

RINT

4,5,6,7,8 CL = 75 pF 40 ns

NOTE 3: In the FIFO mode, the read cycle (RC) = 425 ns (minimum) between reads of the receiver FIFO and the status registers (interrupt

identification register or line status register).

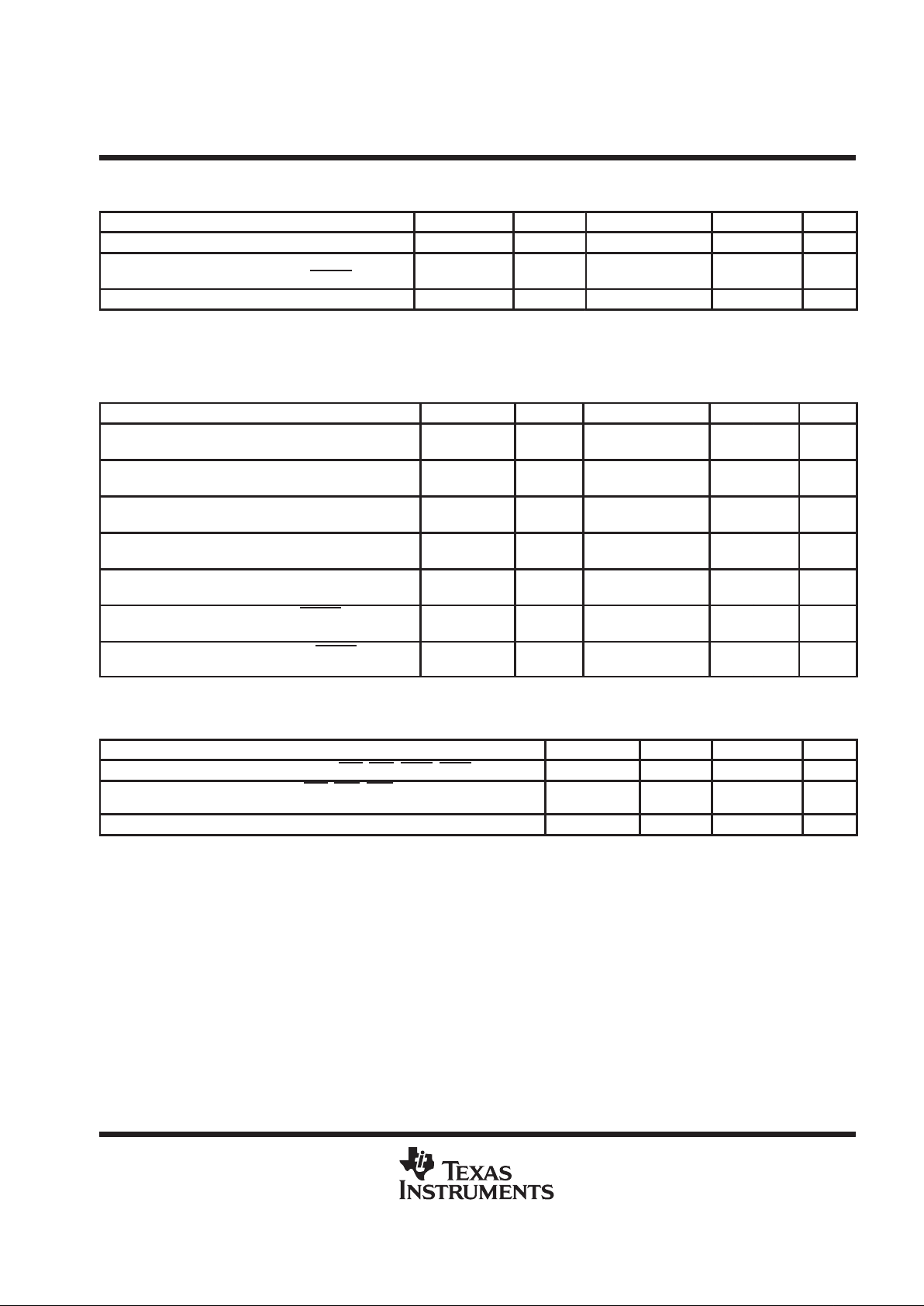

transmitter switching characteristics over recommended ranges of supply voltage and operating

free-air temperature

PARAMETER ALT. SYMBOL FIGURE TEST CONDITIONS MIN MAX UNIT

t

d15

Delay time, initial write (INTRPT low) to transmit

start (SOUT low)

t

IRS

9 8 24

baudout

cycles

t

d16

Delay time, stop (SOUT low) to interrupt (INTRPT

high)

t

STI

9 8 9

baudout

cycles

t

d17

Delay time, WR THR high to reset interrupt

(INTRPT low)

t

HR

9 CL = 75 pF 50 ns

t

d18

Delay time, initial WR THR low to THRE interrupt

(INTRPT high)

t

SI

9 16 32

baudout

cycles

t

d19

Delay time, RD IIR low to reset THRE interrupt

(INTRPT low)

t

IR

9 CL = 75 pF 35 ns

t

d20

Delay time, WR THR high to TXRDY high

(inactive)

t

WXI

10,11 CL = 75 pF 35 ns

t

d21

Delay time, start (SOUT low) to TXRDY low

(active)

t

SXA

10,11 CL = 75 pF 8

baudout

cycles

modem control switching characteristics over recommended ranges of supply voltage and

operating free-air temperature, C

L

= 75 pF

PARAMETER ALT. SYMBOL FIGURE MIN MAX UNIT

t

d22

Delay time, WR MCR low to output (RTS, DTR, OUT1, OUT2) low or high t

MDO

12 50 ns

t

d23

Delay time, modem interrupt (CTS, DSR, DCD) low to set interrupt

(INTRPT) high

t

SIM

12 35 ns

t

d24

Delay time, RD MSR low to reset interrupt (INTRPT) low t

RIM

12 40 ns

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

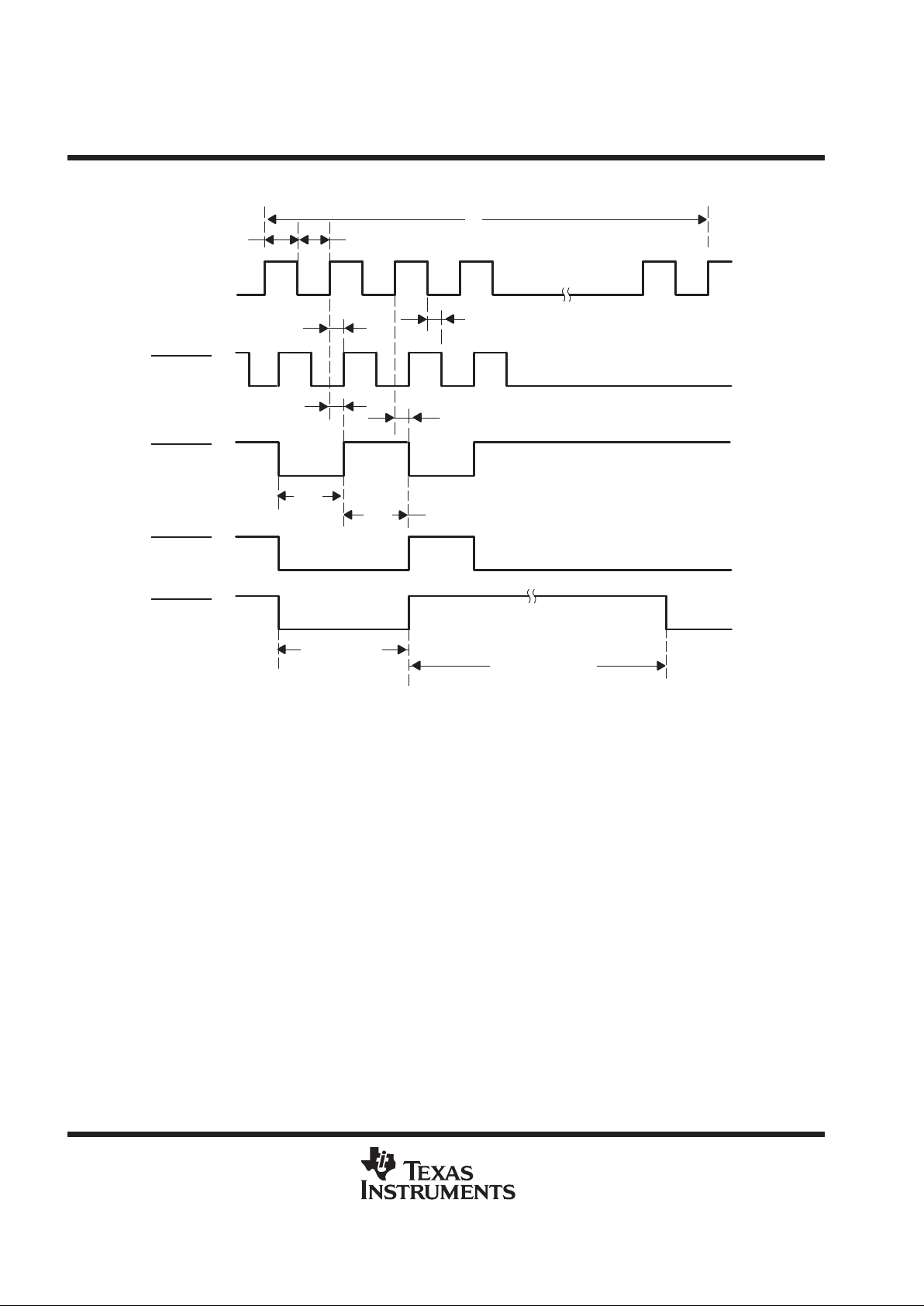

PARAMETER MEASUREMENT INFORMATION

BAUDOUT

(1/1)

XIN

BAUDOUT

(1/2)

BAUDOUT

(1/3)

BAUDOUT

(1/N)

(N > 3)

2 XIN Cycles

(N–2) XIN Cycles

t

w3

t

w4

t

d1

t

d2

t

d1

t

d2

N

t

w1

t

w2

Figure 1. Baud Generator Timing Waveforms

TL16C550B, TL16C550BI

ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS136B – JANUARY 1994 – REVISED AUGUST 1996

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

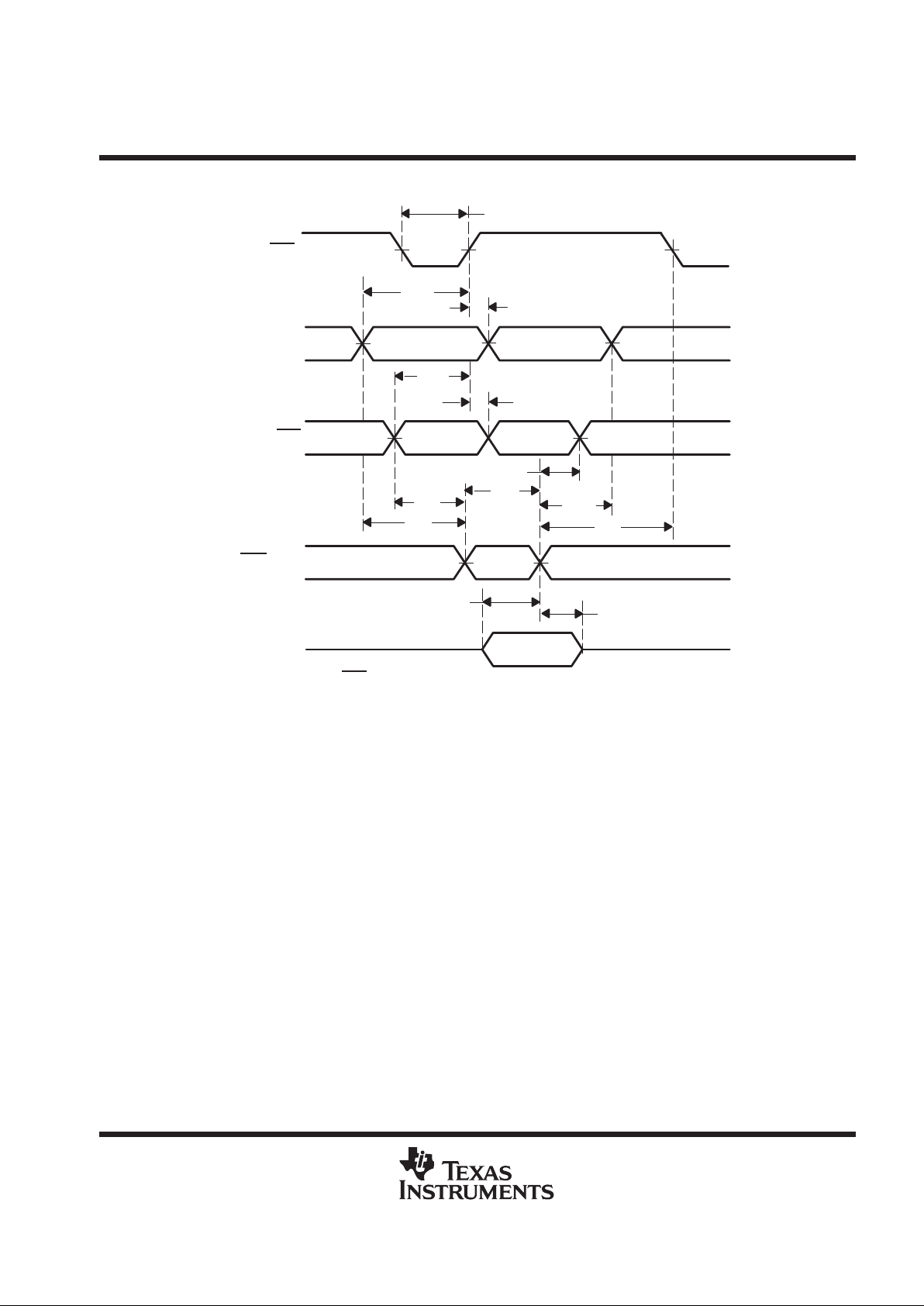

PARAMETER MEASUREMENT INFORMATION

ADS

t

w5

t

h1

t

su1

t

h2

t

su2

t

su3

t

h5

t

h3

t

w6

t

d4

t

d5

t

d6

t

h4

†

Valid Data

Valid Valid

†

Valid Valid

†

Active

A0–A2

CS0, CS1, CS2

WR1, WR2

D7–D0

50%50%

50%

50%50%

50% 50%

50% 50%

50%

†

Applicable only when ADS

is low.

Figure 2. Write Cycle Timing Waveforms

Loading...

Loading...