Page 1

MSP53C691 Speech

Synthesizer

User’s Guide

December 2000 MSDS Speech

SPSU020

Page 2

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Page 3

About This Manual

How to Use This Manual

Preface

Read This First

This user’s guide provides information on the MSP53C691 mixed signal processor. This information includes architecture overview, detailed architecture

description, assembly language instruction set, code development tools, and

customer information.

How to Use This Manual

This document contains the following chapters:

-

-

-

-

-

-

-

-

-

Chapter 1—Introduction

Chapter 2—MSP53C691 Hardware Description

Chapter 3—MSP53C691 Software Description

Chapter 4—MSP53C691 Timing Considerations

Appendix A—Designing the Master Microcontroller Software

Appendix B—FM Synthesis

Appendix C—Editing Tools and Data Preparation

Appendix D—Pitch and Speech Shifting for 6xx MELP

Appendix E—Guidelines for Optimal TI Speech

Read This First

iii

Page 4

Related Documentation From Texas Instruments

Information About Cautions

This book contains cautions.

This is an example of a caution statement.

A caution statement describes a situation that could potentially

damage your software or equipment.

The information in a caution is provided for your protection. Please read each

caution carefully.

Related Documentation From Texas Instruments

SPSS023B Data sheet, MSP50C614

SPSU014 User’s guide, MSP50C614

SPSS028A Data sheet, MSP50C604

SPSU014 User’s guide, MSP50C604

iv

Page 5

Running Title—Attribute Reference

Contents

1 Introduction 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Description 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Features 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 MSP53C691 Device 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Pin Assignments and Description 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 DAC Information 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 Algorithms Supported 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 MSP53C691 Hardware Description 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 MSP53C691 Interface Overview 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Microprocessor Interface Description 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 4-Bit Mode 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 8-Bit Mode 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Read Operation by the Master 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Write Operation by the Master 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 MSP53C691 Device Initialization 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Microprocessor Interface Timing 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 MSP53C691 Software Description 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Software Overview 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Commands and Data Streams 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Sequence of Command Codes and Data Streams 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Command Header 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Parameters 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 Return Values 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Command Codes 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Description of the Command Codes 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Command Header 1—Configure Internal Registers 3-8. . . . . . . . . . . . . . . . . . . . . .

3.5.2 Command Header 2—Set/Clear I/O Ports, PD4 Through PD7 3-10. . . . . . . . . . . .

3.5.3 Command Header 3—Read Contents of I/O Ports 3-11. . . . . . . . . . . . . . . . . . . . . .

3.5.4 Command Header 4—Start Speaking 3-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.5 Command Header 5—Stop Speaking 3-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.6 Command Header 6—Adjust the Volume 3-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.7 Command Header 7—Return Buffer Status 3-32. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.8 Command Header 8—Initiate Sleep 3-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.9 Command Header 9—Receive FM Data 3-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.10 Command Header A—Perform Speed Shift or Pitch Shift 3-33. . . . . . . . . . . . . . . .

4 MSP53C691 Timing Considerations 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 General Constraints 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter Title—Attribute Reference

v

Page 6

Running Title—Attribute Reference

4.2 MSP53C391 Timing Waveforms 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 CELP/MELP 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.2 MIX Mode 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Designing the Master Microcontroller Software A-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B FM Synthesis B-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C Editing Tools and Data Preparation C-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D Pitch and Speed Shifting for 6xx MELP D-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E Guidelines for Optimal TI Speech E-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figures

1–1 MSP53C691 Pin Assignments 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 MSP53C691 Interfacing Diagram—4-Bit Mode 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 MSP53C691 Interfacing Diagram—8-Bit Mode 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Data Transfer—Read 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Data Transfer—Write 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 MSP53C691 RESET Diagram 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Device Initialization 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Oscillator and PLL Connection 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 MSP53C691 Hardware Interface Connection 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–1 Program Flow for the Master Main Routine A-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–2 Program Flow for an ISR Tied to the Falling Edge of OUTRDY A-4. . . . . . . . . . . . . . . . . . . . . .

A–3 Program Flow for an ISR Tied to the Falling Edge of INRDY to Play Mixed Mode A-5. . . . . .

A–4 Routine for Sending Data or Commands to the Slave A-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–5 Program Flow for ISR Tied to the Falling Edge of INRDY to Play CELP/MELP Only A-7. . . .

B–1 FM Conversion Process B-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

T ables

1–1 MSP53C691 Signal Description 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Command Codes 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–1 Command Summary B-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D–1 Pitch Control D-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D–2 Speed Shifting Summary D-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

Page 7

Chapter 1

Introduction

This chapter briefly describes the features, hardware, and software of the

MSP53C691 speech synthesizer .

Topic Page

1.1 Description 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Features 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 MSP53C691 Device 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Pin Assignments and Description 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 D/A Information 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 Algorithms Supported 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction

1-1

Page 8

Description

1.1 Description

The MSP53C691 is a standard slave synthesizer from T exas Instruments that

accepts compressed speech data from other microprocessors/microcontrollers and converts it to speech. This allows the TI MSP53C691 to be used with

a master microprocessor/microcontroller in various speech products, including electronic learning aids, games, and toys. (When referring to the

MSP53C691 device in this guide, the terms slave and MSP53C691 are used

interchangeably, and the terms master and microcontroller are used interchangeably.)

The MSP53C691 supports several speech synthesis algorithms to permit

tradeoffs that meet the price performance requirements of different markets.

It also incorporates a single-channel FM synthesis routine for music generation combined with codebook-exited linear-predictive (CELP) coding or mixedexcitation linear prediction (MELP) coding.

The MSP53C691 is a special program that runs on the MSP50C604 device.

For more information about the MSP50C604, please refer to the latest version

of the MSP50C604 data sheet (literature number SPSS28A) and to the

SP50x6x User’s Guide

M

(literature number: SPSU014).

1.2 Features

-

The device incorporates a wide range of algorithms on one chip. This

range allows users to choose from low bit rate to high-quality synthesizing

routines for their application. The following algorithms are included:

J

MELP v 3.4 1.0 kbps—3.5 kbps (at 8 Khz sampling rate)

J

CELP v3.4 3.0 kbps, 3.7 kbps, 4.5 kbps, 6.2 kbps, 7.7 kbps, and

11.2 kbps (at 8 kHz sampling rate)

J

ADPCM

J

Single-channel FM synthesis

J

Single-channel FM with CELP or MELP (mixed mode)

-

Six-level digital gain control

-

Interrupt-driven data transfer for speech or command

-

Four customer-configurable I/Os

-

Option for four- or eight-bit data bus

J

Eight-bit data bus with four control lines

J

Four-bit data-bus with five control lines

-

Low power (less than 10 µA) sleep mode for long battery life

J

1-2

Three different sleep modes

Page 9

-

A choice of oscillator control

J

-

Speed and pitch shifting in MELP

-

Stops speaking at any time (only in 4-bit mode)

-

Supports sending commands to perform certain tasks while speaking

(only in 4-bit mode)

-

Operating voltage 3 V–5.2 V

-

Direct speaker drive, 32 Ω

-

Available in die form or 64-pin LQFP package option

1.3 MSP53C691 Device

The MSP53C691 is optimized to support a four-bit-wide data transfer protocol.

The MSP53C691 has two status bits and three control bits which control the

communication protocol between the master and the slave. The MSP53C691

also has one bit (data/command) which differentiates between command or

speech data feeding into the slave.

MSP53C691 Device

The internal oscillator can be controlled with a 1% resistor for low cost,

or a standard 32.768-kHz crystal for higher precision.

The MSP53C691 also supports the 8-bit wide data transfer but support for

commands is disabled. Switching between 4-bit mode or 8-bit mode is permitted between speech data files.

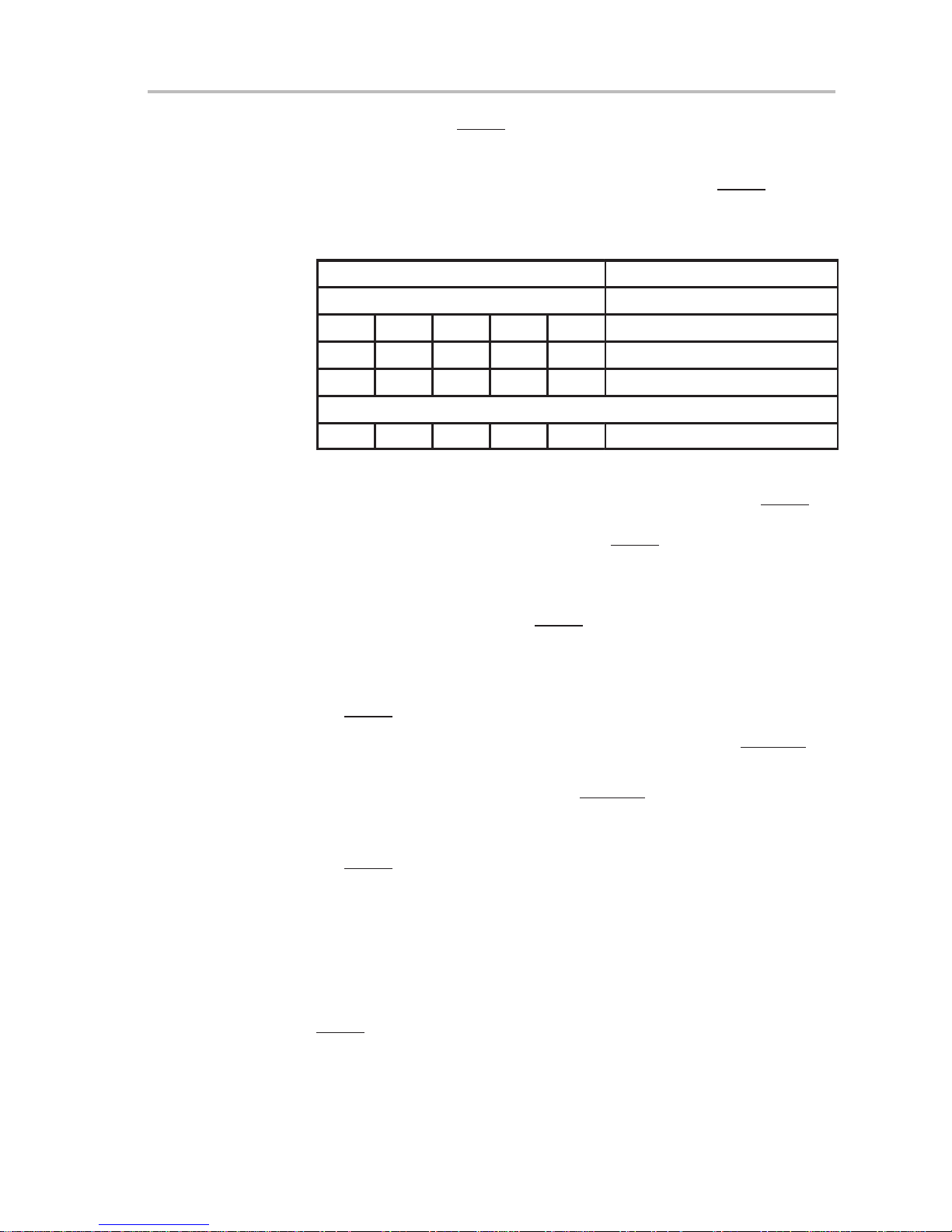

MSP53C691

(4-bit mode)

Number of data lines 4 8

Number of control lines 3 (strobe, R/W, data/command) 2 (strobe, R/W)

Number of status lines 2 (INRDY, OUTRDY) 2 (INRDY, OUTRDY)

Number of general-purpose I/O lines 4 4

Support for commands (while speaking) Yes No

MSP53C691

(8-bit mode)

Introduction

1-3

Page 10

Pin Assignments and Description

1.4 Pin Assignments and Description

Figure 1–1 shows the pin assignments for the MSP53C691. Table 1–1 provides pin functional descriptions.

Figure 1–1.MSP53C691 Pin Assignments

MSP53C691

PM PACKAGE

(TOP VIEW)

SS

NCNCNCNCNCNCNC

V

NC

NC

NC

NC

NC

NC

NC

V

SS

V

DD

V

DD

R/W

STROBE

OUTRDY

INRDY

TEST

SCANOUT

SYNC

SCANCLK

SCANIN

RESET

PLL

OSCIN

OSCOUT

V

SS

NOTE: Pin 35 is DATA4 in 8-bit mode, or DATA/COMMAND in 4-bit mode.

NC – No internal connection

63 62 61 60 5964 58

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1718 19

NC

NC

20

NC

21 22 23 24

NCNCNCNCNC

56 55 5457

25 26 27 28 29

NCNCNC

NC

53 52

51 50 49

30 31 32

NC

NC

V

DD

V

48

SS

DACP

47

V

46

DD

DACM

45

V

44

DD

PD4

43

PD5

42

PD6

41

PD7

40

DATA0

39

DATA1

38

37

DATA2

36

DATA3

35

DATA/COMMAND (DATA4)

34

DATA5

33

DATA6

DATA7

Table 1–1.MSP53C691 Signal Description

NAME

PIN

NO.

INRDY 6 6 O An output signal from the slave to the microcontroller. A low signal

OUTRDY 5 5 O An output signal from the slave to the microcontroller. A low signal

STROBE 4 4 I An input signal to the slave from the microcontroller. STROBE

R/W 3 3 I An input signal to the slave from the microcontroller. Read/write

1-4

PAD

NO.

I/O DESCRIPTION

indicates that the MSP53C691 is ready to accept data or

command. A high signal indicates that the MSP53C691 is busy

and the microcontroller must not write any data or command to it.

indicates that the MSP53C691 is ready to send data or command

to the microcontroller.

sequences read or write operations in conjunction with the R/W

signal. This signal is pulsed high-low-high for read or write

operations sequencing.

select signal which is set high for read operations or set low for

write operations by the microcontroller.

Page 11

Table 1–1. MSP53C691 Signal Description (Continued)

Pin Assignments and Description

NAME

PIN

NO.

PAD

NO.

I/O DESCRIPTION

DATA0–DATA3 39–36 25–22 I/O Data bits 0 through 3 (in 4-bit or 8-bit mode)

DATA4 or

DATA/COMMAND

35 21 I/O Data bit 4 (in 8-bit mode)

Data/command control bit (in 4-bit mode). Low signal indicates

command and high signal indicates data.

DATA5–DATA7 34–32 20–18 I/O Data bits 5 through 7 (8-bit mode only)

Not used (4-bit mode only)

PD4–PD7 43–40 29–26 I/O General-purpose I/O bus

Oscillator Reference Signals

OSCOUT 15 15 O Output of resistor/crystal oscillator

OSCIN 14 14 I Input to resistor/crystal oscillator

PLL 13 13 O Output of phase-lock-loop filter

Scan Port Control Signals‡

SCANIN 11 11 I Scan port data input

SCANOUT 8 8 O Scan port data output

SCANCLK 10 10 I Scan port clock

SYNC 9 9 I Scan port synchronization

TEST 7 7 I C604: test modes

‡NOTE: All these pins must be N.C.

DAC Sound Output

DACP 47 33 O Digital-to-analog output 1 (+) that provides direct speaker drive

capability

DACM 45 31 O Digital-to-analog output 2 (–) that provides direct speaker drive

capability

Initialization

RESET 12 12 I Device initialization

Power Signals

V

DD

V

SS

†

Marked pins are VDD and VSS connections which service the DAC circuitry. These pins tend to sustain a higher current draw .

A dedicated decoupling capacitor across these pins is therefore required.

1, 2, 31,

44, 46

16, 48,

†

49

, 64

†

1, 2, 17,

30, 32

16, 34†,

35, 36

— Processor power, +5 V nominal supply voltage

†

— Ground pin

†

Introduction

1-5

Page 12

DAC Information

1.5 DAC Information

A two-pin push pull that can directly drive a 32-Ω speaker is used in the

MSP53C691. Refer to the

literature number SPSU014, for more information on the D/A and amplifier

circuit.

1.6 Algorithms Supported

-

MELP: Data rates range from 1 kbps to ~ 3.5 kbps at an 8-kHz sample rate.

-

CELP: Data rates can be selected from 3 kbps to 11.2 kbps at an 8-kHz

sample rate.

-

ADPCM

-

FM: frequency modulation for one-channel musical instrument synthesis

-

Mix mode: one channel FM synthesis with MELP or CELP

MSP50x6x Mixed Signal Processor Users Guide

,

1-6

Page 13

Chapter 2

MSP53C691 Hardware Description

This chapter describes the MSP53C691 hardware, including interface, initialization, and timing.

Topic Page

2.1 MSP53C691 Interface Overview 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Microprocessor Interface Description 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Read Operation by the Master 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Write Operation by the Master 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 MSP53C691 Device Initialization 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Microprocessor Interface Timing 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MSP53C691 Hardware Description

2-1

Page 14

MSP53C691 Interface Overview

2.1 MSP53C691 Interface Overview

The MSP53C691 interfaces with the master microcontroller either in 4-bit or

in 8-bit mode.

The MSP53C691 and the master microcontroller transfer data across four

(DA TA0–DATA3) or eight (DATA0–DAT A7) data lines, depending upon which

mode the slave is in.

In either mode the transfer of data is controlled by the two control lines: R/W

and STROBE. When the MSP53C691 is ready to receive data from the

microcontroller, it sets INRDY low. The microcontroller sends data to the

MSP53C691 by setting R/W low and then pulsing STROBE high-low-high. The

MSP53C691 latches the data at the rising edge of the STROBE pulse. The

MSP53C691 also sets INRDY high at the rising edge of the STROBE pulse.

Setting INRDY

more data.

When the MSP53C691 is ready to send data to the microcontroller, the

MSP53C691 sets OUTRDY low . The microcontroller responds by setting R/W

high and then pulsing STROBE high-low-high. (The microcontroller latches

the data while STROBE is low.) This informs the slave that the data has been

written to the microcontroller. The MSP53C691 sets OUTRDY high at the rising edge of the STROBE pulse. Setting OUTRDY high indicates that the

MSP53C691 does not have data ready to send.

high indicates that the MSP53C691 is not ready to receive any

Both 4-bit and 8-bit modes are controlled by commands sent to the slave. A

separate bit (DA TA 4) is used in 4-bit mode to differentiate between the speech

data or command sent to the slave. This line is referred to as data/command

line. This is discussed in detail in the software overview section.

2-2

Page 15

2.2 Microprocessor Interface Description

As mentioned in section 2.1, the MSP53C691 interfaces with the master microcontroller either in 4-bit or in 8-bit mode.

2.2.1 4-Bit Mode

The interface between the microcontroller and the MSP53C691 consists of

four control lines, two status lines, and four data lines.

The control lines are:

-

STROBE

-

R/W

-

DATA/COMMAND

-

RESET

The status lines are:

-

INRDY

-

OUTRDY

The speech data or command is transferred on lines:

Microprocessor Interface Description

-

DATA0 through DATA3

Figure 2–1 shows the interfacing diagram.

Figure 2–1.MSP53C691 Interfacing Diagram—4-Bit Mode

V

V

DD

100 kΩ

each

Master MSP53C691

DATA(0–3) DATA(0–3)

Note: STROBE: Active low strobe signal from microcontroller

R/W

RESET

DATA0–DATA3 Data bits 0 through 3

PD4–PD7 General-purpose I/O bus

DACP Output to speaker/amplifier

DACM Output to speaker/amplifier

DATA/COMMAND This bit determines if the data sent by the

100 kΩ

4

Read/write signal from microcontroller

Active low reset signal from microcontroller

microcontroller is data or command.

DD

4.7 kΩ4.7 kΩ

4.7 kΩ

INRDY

OUTRDY

R/W

STROBE

DATA/COMMAND

RESET

MSP53C691 Hardware Description

2-3

Page 16

Microprocessor Interface Description

2.2.2 8-Bit Mode

The interface between the microcontroller and the MSP53C691 consists of

three control lines, two status lines, and eight data lines.

The control lines are:

-

STROBE

-

R/W

-

RESET

The status lines are:

-

INRDY

-

OUTRDY

The data/command lines are:

-

DATA0 through DATA7

Figure 2–2 shows the interfacing diagram.

Figure 2–2.MSP53C691 Interfacing Diagram—8-Bit Mode

V

DD

V

DD

100 kΩ

each

Master MSP53C691

DATA (0–7) DATA (0–7)

Note: STROBE: Active low strobe signal from microcontroller

R/W

: Read/write signal from microcontroller

RESET

INRDY

: Active low indicates that the MSP53C691 is ready to accept data.

OUTRDY

DATA0–DATA7 Data bits 0 through 7

PD4–PD7 General-purpose I/O bus

DACP Output to speaker/amplifier

DACM Output to speaker/amplifier

: Active low indicates that the MSP53C691 is ready to send data.

8

Active low reset signal from microcontroller

4.7 kΩ4.7 kΩ

4.7 kΩ

INRDY

OUTRDY

R/W

STROBE

RESET

2-4

Page 17

2.3 Read Operation by the Master

The process for the read operation by the master is the same in 4-bit and 8-bit

modes. The read operation by the master happens when the slave wants to

send something to the master. The slave initiates the read process by pulling

OUTRDY low when the slave is ready.

The following events take place during the read operation:

1) The MSP53C691 puts the data to be sent to the master on the internal bus.

2) The MSP53C691 sets OUTRDY low to indicate that it is ready to send data

to the microcontroller.

Read Operation by the Master

3) The microcontroller sets R/W

4) The microcontroller sets STROBE low. The data is available on the external data-bus at this point.

5) The microcontroller reads the data from the bus.

6) The microcontroller sets STROBE high. The MSP53C691 also pulls

OUTRDY

high at the rising edge of STROBE.

7) The data is taken off from the external data-bus after STROBE

The microcontroller must latch or read in the data while STROBE is low. When

the microcontroller sets STROBE

to indicate that the data has been successfully transferred.

Figure 2–3 shows the sequence of events of the read operation.

Figure 2–3.Data Transfer—Read

a) Sequence of events for a single read operation:

OUTRDY

R/W

high to indicate a read operation.

goes high.

high, the MSP53C691 sets OUTRDY high

STROBE

DATA

COMMAND/DATA

b) Read—Two speech data transfer sequences:

OUTRDY

R/W

STROBE

DATA

COMMAND/DATA

MSP53C691 Hardware Description

2-5

Page 18

Write Operation by the Master

2.4 Write Operation by the Master

The process for the write operation by the master is the same in 4-bit and 8-bit

modes. The write operation by the master happens when the slave is ready

to request data or command from the master. The slave initiates the write process by pulling INRDY

The following events take place during the write operation:

low when the slave is ready to receive data.

1) The MSP53C691 sets INRDY

from the microcontroller.

2) The microcontroller sets R/W low to indicate a write operation.

3) The microcontroller puts the data in the external data-bus.

4) The microcontroller sets STROBE low after the data is valid.

5) The microcontroller sets STROBE high after a minimum of 300 ns. The

MSP53C691 also pulls INRDY high at the rising edge of STROBE.

6) The data is latched in the MSP53C691 at the rising edge of STROBE.

When the microcontroller sets STROBE

high to indicate that the MSP53C691 is not ready to receive any more data.

Figure 2–4.Data Transfer—Write

a) Sequence of events for a single write operation

R/W

STROBE

INRDY

low to indicate that it is ready to receive data

high, the MSP53C691 sets INRDY

COMMAND/DATA

b) Write—Two speech data transfer sequences

STROBE

COMMAND/DATA

2-6

DATA

R/W

INRDY

DATA

Page 19

2.5 MSP53C691 Device Initialization

The RESET pin is configured as an external interrupt (see Figure 2–5). It

provides the means for hardware initialization of the device. When the RESET

pin is held low, the device assumes a deep sleep state and various registers

are initialized. After the RESET pin is taken high, the device gets initialized and

pulls INRDY low when the slave is ready to receive the oscillator selection

command (see the

oscillator selection command). The oscillator selection command (0xB) is sent

through the DATA0–3 line while setting the DATA4 line low (indicating that it

is a command). When the slave receives the oscillator selection command

(0xB), it pulls INRDY low again to request the parameter (0x1 or 0x2) for the

command. After the parameter is received by the slave, it goes through the rest

of the initialization process and pulls INRDY

stabilized and the slave is ready to receive data/command.

Note:

If the slave does not receive the oscillator selection command as the first

command when INRDY goes low for the first time, or if the slave does not

receive the subsequent parameters for the oscillator control command (0x1

or 0x2), the slave resets itself again.

Software Description

MSP53C691 Device Initialization

chapter for a description of the

low when the oscillator is

Figure 2–5.MSP53C691 RESET Diagram

MSP53C691

RESET

The MSP53C691 is considered to be properly initialized after the following

events take place:

1) The microcontroller sets RESET

2) The microcontroller sets STROBE high throughout the initialization process.

3) The microcontroller sets RESET high.

4) The microcontroller waits for INRDY

5) The microcontroller sets R/W low.

1 kΩ

V

DD

100 kΩ

low.

to go low.

1 µF

6) The microcontroller puts 0xB (oscillator control command) on the data-bus

7) The microcontroller pulls STROBE low, waits for a minimum of 300 ns,

(DATA0–3) and sets the DATA4 (DATA/COMMAND) line low.

then pulls STROBE

high again.

MSP53C691 Hardware Description

2-7

Page 20

Microprocessor Interface Timing

8) The slave latches the command on the rising edge of STROBE.

9) The slave pulls INRDY low again to request the parameter for the oscillator

control command.

10) The master sets R/W low.

11) The master puts the command parameter for the oscillator control command (0x1 or 0x2, see Table 3–1 for details) on the data-bus

(DATA0–DATA3) and sets the DATA4 (DATA/COMMAND) line low.

12) The microcontroller pulls STROBE low, waits for a minimum of 300 ns,

then pulls STROBE high again.

13) The slave latches the command parameter on the rising edge of STROBE.

14) The slave completes the rest of the initialization process and pulls INRDY

low when ready to receive new command. See Figure 2–6 for a timing diagram of the initialization process.

Figure 2–6.Device Initialization

RESET

INRDY

STROBE

R/W

DATA(0–3)

DATA4

2.6 Microprocessor Interface Timing

The MSP53C691 has a self-contained clock generation system. This flexible

clock generation system enables the software to control the clock over a wide

frequency range. The implementation uses a phase-locked-loop (PLL) circuit

that drives the processor clock to a selectable frequency between the

minimum and maximum ranges. Selectable frequencies for the processor

clock are spaced by 65.536 kHz. The PLL clock-reference is also selectable.

between a resistor-trimmed oscillator or a crystal-referenced oscillator, see

Figure 2–2. Internal and periphery clock sources are controlled separately to

provide different levels of power management. Figures 2–3 and 2–4 illustrate

the timing diagram for write and read operations.

B

0×1 or 0×2

2-8

Page 21

Figure 2–7. Oscillator and PLL Connection

a) Crystal Oscillator Operation Connections

MSP50C691

OSCIN OSCOUT PLL

10 Mن

32.768 kHz†

Microprocessor Interface Timing

10 Mن

†

Keep these components as close as possible to the OSCIN, OSC

22 pF†

b) Resistor Trim Operation Connections

MSP50C691

OSCIN OSCOUT PLL

R

(RTO)

†

Keep these components as close as possible to the OSCIN, OSC

470 kΩ 1%†

=

22 pF†

, and PLL pins.

OUT

, and PLL pins.

OUT

C

(PLL)

C

= 3300 pF†

(PLL)

= 3300 pF†

MSP53C691 Hardware Description

2-9

Page 22

2-10

Page 23

Chapter 3

MSP53C691 Software Description

This chapter overviews the software and describes the commands used to

program the MSP53C691.

Topic Page

3.1 Software Overview 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Commands and Data Streams 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Sequence of Command Codes and Data Streams 3-3. . . . . . . . . . . . . . . .

3.4 Command Codes 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Description of the Command Codes 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

MSP53C691 Software Description

3-1

Page 24

Software Overview

3.1 Software Overview

The MSP53C691 is a slave device that is controlled using a formatted

communications sequence that transfers commands and data streams from

the master microcontroller. The commands are combined at the top level into

several main groups (command header). Each main group has sublevels

(level 1 and level 2) that may require several parameters, depending upon the

group.

3.2 Commands and Data Streams

Two types of communications are sent to the MSP53C691: speech data

streams and commands (with parameters). The command headers and the

level 1 and level 2 parameters are always sent to the MSP53C691 a nibble at

a time through data lines DATA0–DATA3. However, the speech data is sent

over the four-bit data lines (DATA0–DATA3) in four-bit mode, while speech

data is sent over the eight-bit data lines (DATA0–7) in eight-bit mode. When

sending speech data in four-bit mode, the DA TA4 (DATA/COMMAND) line is

always pulled high to differentiate speech data from a command. The DA TA4

(DA T A/COMMAND) line is always pulled low while sending commands to the

MSP53C691. In four-bit mode, commands can be sent to the MSP53C691 at

the beginning of a speech file or at any other time while speaking. In eight-bit

mode, commands can only be sent to the MSP53C691 at the beginning of

each speech file. Support for commands while speaking a phrase is not available in eight-bit mode; it is only available after speaking of a phrase is complete.

-

The DA T A/COMMAND line defines what type of information is being sent

(data or command) to the MSP53C691. The command or speech data

sent to the MSP53C691 is distinguished by the following state of the

DATA/COMMAND line.

J

Data = 1

J

Command = 0

-

A data stream or speech data is sent to the MSP53C691 to provide the

data file for speaking.

-

Command codes are sent to the MSP65C691 to control functions such as

speaking start or stop, toggle I/O, volume control, oscillator control, configure internal registers, etc. See Table 3–1 for a complete list of command

codes.

3-2

Page 25

Sequence of Command Codes and Data Streams

Note:

Throughout the rest of the chapter it is assumed that data from the

MSP53C691 is always read four nibbles at a time. The MSP53C691 pulls

OUTRDY low when it wants to send a nibble to the master (read from the

MSP53C691). It is also assumed that the data is sent to the MSP53C691

from the master only when the MSP53C691 pulls INRDY

low. In four-bit

mode, the DA T A4 (DA TA/COMMAND) bit is low when a command or its parameters are written to the MSP53C691, and the DATA4 (DATA/COMMAND) bit is high when the speech or FM data is written to the MSP53C691.

While sending speech or command in four-bit mode, the data is always sent

most-significant nibble first and least-significant nibble last.

All commands and their parameters are sent with a four-bit interface. Commands and their parameters are sent to the slave through data lines

DATA0–DATA3 while DATA4 (DATA/COMMAND) line is set low.

The procedures for reading from or writing to the MSP53C691 are described

in the

Hardware Description

chapter.

3.3 Sequence of Command Codes and Data Streams

The sequence for sending the command codes and data streams is as follows:

-

The sequence for the command codes consists of a command header, a

level 1, and, sometimes, a level 2 parameter. The command header controls the operation performed by the MSP53C691. Level 1 and level 2 are

two levels of command information that further define the command code.

Each nibble of the command code is sent along with a 0 in the DA TA/COMMAND line to indicate that it is a command. Refer to section 3.3.2,

ters

-

3.3.1 Command Header

The command header is the first information of the command code sequence

sent to the MSP53C691. The command header controls the operation being

performed by the MSP53C691. The MSP53C691 recognizes the following

command headers:

and Table 3–1,

Data streams are speech data sent to the MSP53C691 from speech files

processed by the SDS6000 (see Appendix C for details). Each nibble of

the speech data is sent along with a 1 on the DA TA/COMMAND line to indicate that it is speech data.

Command Codes

for additional information.

Parame-

-

-

-

-

-

Command header 1—Configure internal registers

Command header 2—Set/Clear I/O ports PD4 through PD7

Command header 3—Read contents of I/O ports

Command header 4—Start speaking

Command header 5—Stop speaking

MSP53C691 Software Description

3-3

Page 26

Sequence of Command Codes and Data Streams

-

Command header 6—Adjust volume

-

Command header 7—Return status of data buffers

-

Command header 8—Initiate sleep mode

-

Command header 9—Receive FM data (while speaking in FM only or in

mix mode)

-

Command header A—Perform speed/pitch shift

-

Command header B—Set up oscillator

The command headers are sent to the MSP53C691 in four-bit nibbles with a

0 in the DATA4 line in either four-bit or eight-bit mode.

CAUTION

Support for sending commands while speaking is not available in

eight-bit mode. In eight-bit mode, commands can be sent to the slave

between speaking phrases.

3.3.2 Parameters

3.3.3 Return Values

For the command codes, there are two types of parameters that are sent to

the MSP53C691 after sending the command header: level 1 and, if required,

level 2. Level 1 and level 2 are levels of command information that further

defines the command code. For example, if the command header is

Volume

(one nibble command code 0x6), then the level 1 parameter (one

Adjust the

nibble, 0x1 through 0x6) defines what level the volume is being set to (that is,

low, medium, or high). Also, if the command header is

Registers

(one nibble command code 0x1), then the level 1 parameter defines

Configure Internal

which internal register address to write to (two nibbles specifying the address

of the register). The level 2 parameter is the data written to the internal register

(four nibbles specifying the word to be written in the register). All the command

headers and Level 1 and level 2 parameters are sent to the MSP53C691 a

nibble at a time with the DATA4 (DATA/COMMAND) bit set low. While

interleaving commands between speech data, it is advisable to send all the

nibbles of the command (command header, level 1, and level 2 parameters,

if applicable) before sending more speech data or commands. Refer to

Table 3–1,

Command Codes

, for additional information.

The MSP53C691 can return values to the microcontroller when required. The

MSP53C691 sends return values to the master either to respond to a command, to return error codes, or to provide its current status. The values returned vary in content, depending on the command code initiated and on the

status of the MSP53C691. The following is a list of returned values from the

MSP53C691:

3-4

Page 27

Command Codes

Returned Values Description

0x0055 Returned when the MSP53C691 successfully plays a speech file. In mix mode,

0x0055 is returned when the MSP53C691 has finished playing both the FM and

the speech file.

0x0054 Returned in mix mode when the MSP53C691 has successfully finished playing

a speech file and is waiting to start a new file or for the FM to finish playing.

0x0053 Returned in mix mode when the MSP53C691 has successfully finished playing

an FM file and is waiting for the speech file to finish playing.

0x9999

Returned when an error is encountered. This error is returned when either:

• An invalid command header or and invalid level 1 or level 2 parameter is

issued by the master.

• An invalid port address to be written to or to be read from is specified.

• An invalid file format is encountered while playing multiple files In mix mode.

0x1234 Returned when there is an error recognizing the header byte in the speech file

or the stack is overflowed

0x0N23 Returned (in mix mode or while speaking FM only) when the FM buffer becomes

nearly empty and FM data is needed to fill up the FM buffer . N denotes the number of FM bytes needed to fill up the FM buffer.

CAUTION

The MSP53C691 waits until all of the four nibbles have been sent to the

microcontroller. If the microcontroller delays in reading the data from the

MSP53C691, the speech operation can be interrupted. Therefore, the

microcontroller must read the data as soon as the OUTRDY goes low.

3.4 Command Codes

The valid command codes are described in Table 3–1 and paragraph 3.5.

Command codes include the command header (one nibble), level 1

parameters (one or two nibbles), and, sometimes, level 2 (four nibbles)

parameters. As shown in Table 3–1, there are occasions when values are

returned to the slave as a result of the command that is initiated. These return

values are always four nibbles in size and are sent over the DATA0–DATA3

data lines.

In four-bit mode, the commands (command header and level 1 and level 2

parameters) are sent to the MSP53C691 four bits (a nibble) at a time with

DA TA4 set to 0 for every transmitted nibble. In four-bit mode, commands can

be sent while speaking a phrase, but in eight-bit mode commands can only be

sent between speaking phrases. After receiving the command to speak in 8-bit

mode, the slave expects speech data in 8–bits. No other command can be sent

to the slave during speaking. The slave goes to the 4-bit mode to receive

MSP53C691 Software Description

3-5

Page 28

Command Codes

further commands after finishing speaking (either in 4-bit or in 8-bit mode). All

commands require at least one nibble of level 1 parameter. There are some

commands that require more than one nibble of level 1 parameter. Some

commands require more than one nibble of level 2 parameter. Some

commands return four nibbles back to the master in response. For example,

a return buffer status (command code 0x7) followed by a level 1 parameter

(0x1 for non-FM buffer) returns four nibbles reporting the number of bytes left

to fill up the buffer back to the master.

See section 3.5, Description of the Command Codes, for a description of each

command.

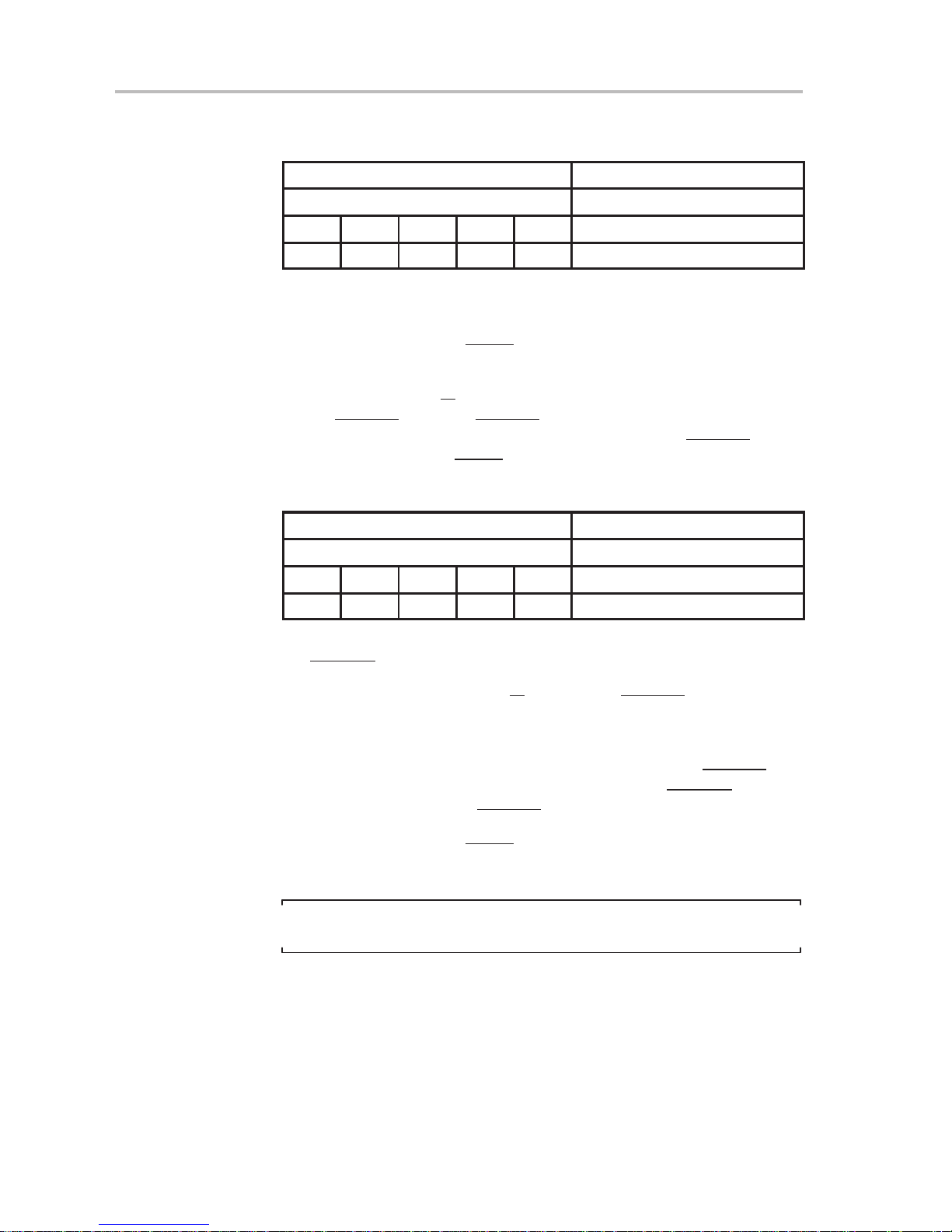

Table 3–1.Command Codes

Command

Header

1 N1N

2 N None None Upper four bits for port D

3 N1N

4 1 None None Speak CELP, MELP, or ADPCM in four-bit data transfer

4 2 None None Speak CELP, MELP, or ADPCM in eight-bit data transfer

4 3 None None Test mode

4 4 none None Play FM (Music) in four-bit mode only

4 5 none None Speak mixed mode in four-bit mode only (FM +

4 6 None None Speak multiple phrases in mix mode—see the details

4 7 None None Play sinewave in test mode at 1 kHz

5 1 none None Stop speaking all (in mix or nonmix mode)

5 2 None None Stop speaking CELP/MELP only in mix mode

5 3 None None Stop speaking FM only in mix mode

Note: Each nibble is sent to the master with DATA4 bit set to 0, indicating that it is a command.

N—Represents one nibble.

N1N2N3N4—Represents four nibbles, with N1 being the first nibble sent and N4 being the 4th nibble sent (MSB and LSB).

The numbers in the box represent the actual value of the nibble sent to the MSP53C691.

Parameters

Level 1 Level 2

Port

address

PD4–PD7

Port

address

2

2

V alue to

be written

N1N2N3N

None N1N2N3N

Return

Values

Configure Internal Registers

None Write to internal registers for configuration

4

Set/Clear I/O Ports, PD4 Through PD7

(Note: Configuration of port D4–7 as output is required)

Read Contents of I/O Ports

Value

4

Start Speaking

under the discussion of the command

Stop Speaking

Returns the port value

Description

CELP/MELP)

3-6

Page 29

Command Codes

Table 3–1. Command Codes (Continued)

Adjust the Volume

6 1 none none Level 1 (lowest volume)

6 2 none none Level 2

6 3 none none Level 3

6 4 none none Level 4

6 5 none none Level 5

6 6 none none Level 6 (highest volume)

Command

Header

7 1 None N1N2N3N

7 2 None N1N2N3N4Returns the number of bytes required to fill up the FM

8 1 None None Light sleep (see Table 2–3 of SPSU014)

8 2 None None Mid sleep (see Table 2–3 of SPSU014)

8 3 None None Deep sleep (see Table 2–3 of SPSU014)

9 N None None Receive FM data

A 0 N1N2N3N

A 1 N1N2N3N

A 2 N1N2N3N

A 3 None None Reserved (TI test code)

B 1 None None Crystal mode

B 2 None None Resistor trim mode

Parameters

Level 1 Level 2

Return

Values

Description

Return Status of Data Buffers

Returns the number of bytes required to fill up the

4

CELP/MELP buffer

Initiate Sleep Mode

Wake-up from sleep mode can be performed by putting

dummy data in the bus and pulsing STROBE

Receive FM Data

N = number of FM bytes the master is going to send

Perform Speed/Pitch Shift

None Slow down MELP

4

None Speed up MELP

4

None Pitch shift in MELP

4

Oscillator Control

buffer

Note: Each nibble is sent to the master with DATA4 bit set to 0, indicating that it is a command.

N—Represents one nibble.

N1N2N3N4—Represents four nibbles, with N1 being the first nibble sent and N4 being the 4th nibble sent.

The numbers in the box represent the actual value of the nibble sent to the MSP53C691.

MSP53C691 Software Description

3-7

Page 30

Description of the Command Codes

3.5 Description of the Command Codes

3.5.1

Command Header 1—Configure Internal Registers

This command is used to configure the MSP53C691 internal registers. Certain

values in certain registers are not allowed to be modified (see note at the end

of this section). Attempting to modify these values when writing to those registers has no effect. The command header for configuring internal registers for

the MSP53C691 is one nibble long and of value 1 as shown. This header is

sent across the four data lines. The sequence of events to configure the internal registers is as follows:

1) The MSP53C691 pulls INRDY

2) The master sends the command header 0x1 over the data lines.

Write Operation to Configure Internal Registers

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 0 1

3) The MSP53C691 pulls INRDY low again to request level 1 parameters.

The level 1 parameter that defines the address of the internal register is

two nibbles long in this case, see the following examples:

Most significant (first nibble) Least significant ( Second nibble)

X X

low to request a command or data.

Data Lines

4) The master sends the two nibbles back to back in response to the two

consecutive lowerings of INRDY.

Note:

When sending the two nibbles that make up the address of the register, send

the first nibble (most significant) first.

Example 1: To configure pins 7 and 5 of port D as outputs and pins 6 and 4

as inputs, we need to write to the port D control register. The address for the

register to be configured is 0x1C, then the two nibbles (8 bits) are written as

1C:

MSB LSB

7 6 5 4 3 2 1 0

0 0 0 1 1 1 0 0

Perform the following write operation by writing the two nibbles (8 bits) MSB

first, as shown. The two nibbles are written one nibble at a time—in each case

the DATA4 bit is pulled low, indicating that a command is being sent.

3-8

Page 31

Description of the Command Codes

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 0 1 Firstst nibble sent

Least Significant

0 1 1 0 0 Second nibble sent

5) After the level 1 parameters are received, the MSP53C691 pulls INRDY

low again requesting the data to be written to the registers. The data is 16

bits long and is transferred to the MSP53C691 a nibble at a time (most-significant nibble first). The master must send four nibbles (for 16-bit data)

back to back in response to four consecutive lowerings of INRDY

.

Note:

The data to be written to the configuration registers is always 16 bits long.

If there are less than 16 bits to be written to the registers, then there should

be leading zeroes to make it 16 bits long.

Example 2: The value to be written to the internal register is 0xA0, then the

four nibbles (16 bits) are written as 0x00A0:

MSB LSB

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0

Perform the following write operation by writing the four nibbles (16 bits) MSB

first, as shown. The four nibbles are written one nibble at a time with the DA TA4

line set to 0, indicating that a command parameter is being sent.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 0 0 First nibble sent

0 0 0 0 0 Second nibble sent

0 1 0 1 0 Third nibble sent

Least Significant

0 0 0 0 0 Fourth nibble sent

NOTE:

-

Do not write to the following addresses:

J

Port A

H

Data, address 0x00

H

Control, address 0x04

MSP53C691 Software Description

3-9

Page 32

Description of the Command Codes

J

J

J

J

J

J

Port B

H

Data, address 0x08

H

Control, address 0x0C

Port C

H

Data, address 0x10

H

Control, address 0x14

Port D (PD0 – PD3)

H

Data, address 0x18

H

Control, address 0x1C

Port E

H

Data, address 0x20

H

Control, address 0x24

Port F

H

Data, address 0x28

Port G

H

Data, address 0x2C

J

Timer 1 period and countdown register, address 0x3A and 0x3B

J

Timer 2 period and countdown register, address 0x3E and 0x3F

Note: Refer to Table 2–2 in SPSU014 for a complete listing of the port

addresses.

3.5.2 Command Header 2—Set/Clear I/O Ports, PD4 Through PD7

This command can be used to pull a general-purpose I/O pin low or high. The

PD4–7 pins are defined as general-purpose I/O pins in the MSP53C691.

Before sending the command, it is necessary to configure the port pins to the

appropriate state (INPUT or OUTPUT) by configuring the internal control

registers. This command causes the following sequence of events:

1) The MSP53C691 pulls INRDY

master sends the command header 0x2 for toggling I/O ports PD4 through

PD7 of the MSP53C691 as shown in the following table:

WRITE OPERATION TO TOGGLE I/O PORTS

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 1 0

low requesting command or data. The

DATA LINES

2) The MSP53C691 pulls INRDY low again to receive the level 1 parameter.

The level 1 parameter for this command is only one nibble long and is

effectively written to the upper four bits of the port (PD4–PD7). This onenibble parameter defines which pins are being toggled (see examples

below).

3-10

Page 33

Example 1: If PD5 is toggled high, then the one nibble level 1 parameter is

written as 0010; this sets PD5 high.

PINS

PD7 PD6 PD5 PD4

0 0 1 0

Example 2: If none of the pins are toggled high, then the one nibble parameter

is written as 0000; this sets PD4 through PD7 low.

PINS

PD7 PD6 PD5 PD4

0 0 0 0

Note:

Port D must be set as output mode first with the configure register command

for the toggle I/O command to work properly.

3.5.3 Command Header 3—Read Contents of I/O Ports

This command can be used to read back the contents of a port. The command

header for this command is one nibble long and the level 1 parameter

specifying the address of the port to be read is two nibbles long. This command

causes the following sequence of events:

Description of the Command Codes

1) The MSP53C691 pulls INRDY

low to request a command or data.

2) The master sends the command header 0x3 to read the port as follows:

WRITE OPERATION FOR READ CONTENTS OF I/O PORTS

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 1 1

3) The MSP53C691 pulls INRDY low again to receive the level 1 parameters.

The level 1 parameter is two nibbles long and defines the address of the

port, see the following example:

Most significant ( first nibble) Least Significant ( second nibble)

X X

4) The master sends the two nibbles in response to the two consecutive lowerings of INRDY.

Note:

When sending the two nibbles, send first nibble (most-significant nibble) first.

Example 1: To read port D pins 7–4, we need to read the port D data register.

The address for the port to be read is 0x18, then the two nibbles (8 bits) are

written as 0x18:

MSP53C691 Software Description

3-11

Page 34

Description of the Command Codes

MSB

7 6 5 4 3 2 1 0

0 0 0 1 1 0 0 0

LSB

Perform the following write operation by writing the two nibbles (8 bits) MSB

first, as shown. The two nibbles are written one nibble at a time with the DA TA4

line pulled low in each case, indicating that a command is being sent.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 0 1 First nibble sent

Least Significant

0 1 0 0 0 Second nibble sent

5) After the command header and all the parameters are received, the command is executed by setting OUTRDY

low and the four nibbles of data contained in the port register are sent (MSB first, LSB last) to the microcontroller.

6) After receiving the level 1 command parameter (port address), the

MSP53C691 pulls OUTRDY low four times to return the contents of the

port to the master. Each lowering of OUTRDY transfers a nibble

(DA TA0–DA T A3) to the master—the first being the most-significant nibble.

CAUTION

The MSP53C691 waits until all of the four nibbles have been sent to the

microcontroller. If the microcontroller delays in reading the data from the

MSP53C691, the speech operation can be interrupted. Therefore, the

microcontroller must read the data as soon as the OUTRDY goes low.

7) The MSP53C691 pulls INRDY low again to request new data or command.

Note: The contents of the following port addresses can be read:

-

Port A

J

Data register (address 0x00)

J

Control register (address 0x04)

3-12

Page 35

-

FUNCTIONS

Port C

J

Data register (address 0x10)

J

Control register (address 0x14)

-

Port D

J

Data register (address 0x18)

J

Control register (address 0x1C)

-

DAC

J

Data register (address 0x30)

J

Control register (address 0x34)

-

IntGenCtrl register (address 0x38)

-

Interrupt flag register (address 0x39)

Note: Refer to Table 2–2 in SPSU014 for a complete listing of the port

addresses.

3.5.4 Command Header 4—Start Speaking

This command is used to command the MSP53C691 to start speaking. This

command has several level 1 parameters to describe the mode in which the

MSP53C691 speaks. The command header is one nibble long and is written

0100 as shown in the following table. The DA TA4 bit is low while sending this

nibble.

Description of the Command Codes

WRITE OPERATION FOR START SPEAKING

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 1 0 0

The command header 0100 is followed by a level 1 parameter that is one

nibble long and instructs the MSP53C691 to perform the functions defined in

the following table:

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 0 1 Speak CELP, MELP, or ADPCM in

four-bit data transfer mode

0 0 0 1 0 Speak CELP, MELP, or ADPCM in

eight-bit data transfer mode

0 0 0 1 1 Test mode (nibble in = nibble out)

0 0 1 0 0 Play FM (music) in four-bit data

transfer mode

0 0 1 0 1 Speak mixed mode in four-bit data

transfer mode (FM + CELP/MELP)

0 0 1 1 0 Speak multiple files in mix mode

MSP53C691 Software Description

3-13

Page 36

Description of the Command Codes

The different modes of speaking are described in detail in the following

subsections.

3.5.4.1 Speaking CELP, MELP, ADPCM in Four-Bit Data Transfer Mode

Commands and data are sent over a four-bit interface. When data is sent over

the DATA0 through DATA3 lines, DATA4 (pin 35) becomes the

DATA/COMMAND control line. The DATA/COMMAND line defines whether

the information on DA TA0 through DA T A3 is data or commands. When DA T A0

through DATA3 and DATA/COMMAND bits are received, the MSP53C691

analyzes the DATA/COMMAND bit to determine if the information is data or

commands being received on DATA0 through DATA3 lines.

DATA/COMMAND LINE DESCRIPTION

Set to 0 Command sent to the MSP53C691

Set to 1 Data sent to the MSP53C691

The following typical sequence of events takes place while playing CELP,

MELP, or ADPCM in four-bit mode:

1) The MSP53C691 pulls INRDY low and waits for a command from the

master.

2) The master sends the command header 0x4 (command header for speaking in four-bit mode) on the data bus. Note that writing 0x04 to the data bus

ensures that the DATA4 line is low, indicating that value on data lines

DATA0–DATA3 is a command.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 1 0 0 First command header sent

3) After receiving the header, the MSP53C691 pulls INRDY low again and

waits for the level 1 parameter from the master.

4) The master sends the level 1 command parameter 1 to indicate the four-bit

transfer mode for CELP, MELP, or ADPCM.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 0 1 Level 1 parameter sent

5) The MSP53C691 interprets the command and initializes itself to get ready

to speak.

6) The MSP53C691 pulls INRDY low, indicating that it is ready to receive

more commands or speech data.

3-14

Page 37

Description of the Command Codes

7) The master can now start sending speech data from a file in response to

each lowering of INRDY . Note that, while sending speech data, the DA T A4

line must be high, indicating that speech data is being sent. For example,

to send the speech data byte 0x24 to the MSP53C691, the master must

put 0x12 on the data bus in response to the lowering of INRDY

. When the

MSP53C691 is again ready to receive the next nibble, the master puts

0x14 on the data bus again.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

1 X X X X First nibble sent

1 X X X X Second through X nibble sent

Least Significant

1 X X X X Last nibble sent

8) The master can send a command (such as volume control)-between the

speech data while sending speech data. In this case the master first sends

the command header nibble of the command in response to INRDY low

and then sends the required level 1 and/or level 2 parameter nibbles in response to each consecutive lowering of INRDY

. Note that the master must

ensure that the DA TA4 line is also low , indicating that the value in data lines

DATA0–DATA3 is a command. If the master starts sending a command,

then it must send all the parameters of the command back to back in response to each lowering of INRDY before reverting back to sending the

rest of the speech file data again.

9) After sending the last nibble of speech data, the master can send dummy

data (0xFF) to the slave in response to each consecutive lowering of

INRDY until the slave detects the end-of-speech data.

10) When the MSP53C691 detects the end-of-speech, it pulls OUTRDY low.

1 1) The master must then read the data from the bus. Note that only the lower

four bits of the bus are valid data. OUTRDY goes low three more times,

sending a total of four nibbles (0, 0, 5, and 5) if speaking of the phrase was

successful.

12) INRDY goes low again, indicating that the MSP53C691 is ready to receive

a new command.

3.5.4.2 Speaking CELP, MELP, ADPCM in 8-Bit Data Transfer Mode

Data is sent over an eight-bit interface (DA T A0–DAT A7). Sending commands

while speaking is not supported in this mode. When the speaking of a phrase

is finished, the master can again send any command over the DA T A0–DA T A3

lines along with pulling DATA4 line low in response to the next lowering of

. In other words, the MSP53C691 goes back to the four-bit mode after

INRDY

it finishes speaking a phrase in eight-bit mode. The master must send the

command header (4) and level 1 parameter (2) to speak a phrase again in

eight-bit mode.

MSP53C691 Software Description

3-15

Page 38

Description of the Command Codes

While sending a command in between phrases, the master must make sure

that the DATA4 bit is low.

The following is a typical sequence of events that takes place while playing

CELP, MELP, or ADPCM in eight-bit mode:

1) The MSP53C691 pulls INRDY

low and waits for a command from the

master.

2) The master sends the command header 0x04 to the MSP53C691. Note

that writing 0x04 on the data bus ensures that the DA TA4 line is also low,

indicating that the value on data lines DATA0–DATA3 is a command.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 1 0 First command header sent

3) After receiving the command header, the MSP53C691 again pulls INRDY

low and waits for the level 1 parameter from the master.

4) The master sends 0x2 as the level 1 parameter to indicate the eight-bit

transfer mode for CELP, MELP, or ADPCM as follows:

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 1 0 Level 1 parameter sent

5) The MSP53C691 interprets the command and initializes itself to get ready

to speak.

6) The MSP53C691 pulls INRDY low, indicating that it is ready to receive

speech data.

7) The master can now start sending speech data from a file in response to

each lowering of INRDY over the whole eight-bit data bus (DA TA0 through

DA TA7).

Most Significant

DATA LINES

DATA7 DATA6 DATA5 DATA4 DATA3 DATA2 DATA1 DATA0

X X X X X X X X First byte sent

8) The master can not send a command while sending speech data in eightbit mode. The master has to send the speech data in response to each

lowering of INRDY

by putting eight-bit speech data on the bus.

9) After finishing sending the last byte of speech data, the master can send

dummy data (0xFF) to the slave to respond to each consecutive lowering

of INRDY

until the slave detects the end-of-speech.

3-16

Page 39

Description of the Command Codes

10) When the MSP53C691 detects the end-of-speech, it pulls OUTRDY low.

1 1) The master then must read the data from the bus. Note that only the lower

four bits of the bus are valid data. OUTRDY goes low three more times after that, sending a total of four nibbles (0, 0, 5, and 5) if the speaking of the

phrase was successful.

3.5.4.3 Test Mode

12) INRDY

goes low, indicating that the MSP53C691 is ready to receive a new

command. At this point the slave changes back to four-bit mode. Now the

master can send any command to the slave on the four-bit data bus

(DA T A0–DA T A3) with the DA T A4 line pulled low . If the master must speak

again in eight-bit mode, repeat Steps 1 through 12.

Note:

The eight-bit interface is recommended for ADPCM.

The eight-bit interface does not support any interleaved commands (STOP,

volume control, etc.). Hold RESET low to stop speaking in the middle of a

phrase.

A header byte is embedded in the speech data to indicate which algorithm

(MELP, CELP, etc.) to speak. When a certain mode of data transfer is selected (four-bit or eight-bit), the first few bytes of the speech file set up the

MSP53C691 to play the speech file at the proper speed for the synthesizer

algorithm. After the speech file is finished, the MSP53C691 goes back to running at 8 MIPS.

If the test mode is selected, data is transferred to and from the MSP53C691

(one nibble at a time). The MSP53C691 device receives one nibble of data and

then sets OUTRDY low, meaning that the MSP53C691 is ready to send data.

The MSP53C691 then sends the same nibble of data back to the

microcontroller. INRDY is then set low , meaning that the MSP53C691 is ready

to receive more data.

The following is a typical sequence of events for the test mode:

1) The MSP53C691 pulls INRDY

2) The master sends the command header 0x4 on the data bus. Note that

3) After receiving the header, the MSP53C691 pulls INRDY low again and

low and waits for a command from the

master.

writing 0x4 to the data bus ensures that the DA TA4 line is low, indicating

that the value on data lines DATA0–DATA3 is a command.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 1 0 0 First command header sent

waits for a level 1 parameter from the master.

MSP53C691 Software Description

3-17

Page 40

Description of the Command Codes

4) The master sends 0x03 to the MSP53C691 as the level 1 parameter to indicate the test mode.

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 0 1 1 Level 1 parameter sent

5) The MSP53C691 interprets the command and initializes itself to get ready

to go to the test mode.

6) The MSP53C691 pulls INRDY low, indicating that it is ready to receive test

data.

7) The master pulls R/W low, puts a nibble of test data on the bus, and pulses

the STROBE. When the STROBE is pulled low and then back to high, the

data is latched into the MSP53C691 at the rising edge of STROBE

MSP53C691 pulls INRDY high. Note that the data is sent on

DATA0–DATA3 lines only.

Most Significant

DATA LINES

and the

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

X X X X X First nibble sent

8) When the data is latched into the MSP53C691, the MSP53C691 pulls

OUTRDY low.

9) The master then must pull R/W high and pull STROBE low.

10) The master then must read the data from data lines DAT A4–DA TA7. Note

that only the upper four bits of the bus (DATA4–DATA7) are valid data

echoed back to the master. After that the master must pull STROBE high,

indicating that the data has been read from the bus. OUTRDY goes high

at the rising edge of the STROBE

1 1) The MSP53C691 pulls INRDY

.

low again for the next data and the process

repeats.

Note:

The only way to get out of the test mode is to reset the device.

3-18

Page 41

Description of the Command Codes

3.5.4.4 Playing Single Channel FM Synthesis in Four-Bit Transfer Mode

The MSP53C691 can play single-channel FM in four-bit transfer mode.

Sending commands to perform other functions (volume control, toggle I/O,

etc.) is also supported in this mode. The FM data is supplied to the

MSP53C691 from the master over the four-bit data lines (DA TA0–DA T A3). The

DATA/COMMAND line is pulled high while transferring FM data. The

MSP53C691 sends a request back to the master (by pulling OUTRDY

transferring four nibbles to the master) whenever it needs more FM data. The

master then must send a command back to the MSP53C691 informing how

many bytes of FM data are going to be sent. Then the master can send the

promised number of bytes to the MSP53C691 in response to each lowering

of INRDY

. The following is a typical sequence of events for FM transfer:

1) The MSP53C691 pulls INRDY low and waits for a command from the master.

2) The master sends the command header 0x04 to the MSP53C691. Note

that writing 0x04 to the data bus ensures that the DA TA4 line is low , indicating that the value on data lines DATA0–DATA3 is a command.

Most Significant

low and

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 1 0 0 First command header sent

3) After receiving the header, the MSP53C691 pulls INRDY low to expect the

level 1 parameter from the master.

4) The master sends 0x4 as the level 1 parameter to indicate four-bit transfer

mode for playing FM.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 0 1 0 0 Level 1 parameter sent

5) The MSP53C691 interprets the command and initializes itself to get ready

to speak FM.

6) The MSP53C691 pulls OUTRDY low, indicating that it must send a nibble

back to the master.

7) The master reads the data from the bus (DATA0–DATA3).The

MSP53C691 pulls OUTRDY low three more times to send a total of four

nibbles. The four nibbles sent to the master are 1, 8, 2, and 3 respectively .

The 1 and 8 are interpreted as 18H (24 decimal) bytes needed to fill up the

FM buffer initially . The 2 and 3 are interpreted as 23, characterizing the FM

data request to the master.

MSP53C691 Software Description

3-19

Page 42

Description of the Command Codes

DATA3 DATA2 DATA1 DATA0

0 0 0 1 First nibble sent

1 0 0 0 Second nibble sent

0 0 1 0 Third nibble sent

Least Significant

0 0 1 1 Fourth nibble sent

8) The MSP53C691 then pulls INRDY low to indicate that it is ready to receive FM data.

9) The master can now start sending FM data from a file in response to each

lowering of INRDY. Note that while sending speech FM, the DATA4 line

should be high indicating that FM data is being sent. For instance, to send

the FM data byte 0x38 to the MSP53C691, the master must put 0x13 on

the data bus in response to lowering of INRDY

again ready to receive the next nibble, the master puts 0x18 on the data

bus.

Most Significant

DATA LINES

. When the MSP53C691 is

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

1 X X X X First nibble sent

1 X X X X Second through X nibbles sent

Least Significant

1 X X X X Last (24X2=48th) nibble sent

Note:

It is very important to note that the master must send the exact number of FM

data bytes initially requested by the MSP53C691 while filling up the buffer.

If the master has finished sending the exact number of FM data bytes as

requested by the MSP53C691 to initially fill up the buffer and the

MSP53C691 has pulled INRDY

low to request more data or command, the

master can either send a command to perform any task (volume control,

toggle I/O, etc.) or send a dummy command (0x00) if it does not want to send

a valid command.

10) The MSP53C691 starts playing FM after the buffer is filled (that is, the first

24 (decimal) bytes from the file have been received). The MSP53C691

continues to pull INRDY low and waits for a command from the master.

The master can either send a valid command to fulfill the request, or a

dummy command if it doesn’t have any more commands to send.

3-20

Page 43

Description of the Command Codes

1 1) When the MSP53C691 needs more FM data, it pulls OUTRDY low to send

a nibble back to the master. The master must read the nibble from the bus.

The MSP53C691 pulls OUTRDY low three more times to transfer a total

of four nibbles to the master. The four nibbles sent this time are 0, X, 2, and

3. The nibble X is interpreted as the number of FM data bytes requested

by the MSP53C691. The 2 and 3 characterize the request for FM data.

Most Significant

DATA LINES

DATA3 DATA2 DATA1 DATA0

0 0 0 1 First nibble sent

X X X X Second nibble sent

0 0 1 0 Third nibble sent

Least Significant

0 0 1 1 Fourth nibble sent

12) The MSP53C691 pulls INRDY low after sending the four nibbles requesting the FM data from the master.

13) The master must send 9 as a command (0x09), letting the MSP53C691

know that master is going to send FM data.

Most Significant

DATA LINES

DATA4 DATA3 DATA2 DATA1 DATA0

0 1 0 0 1 Command header sent

14) After receiving the 9 command, the MSP53C691 lowers INRDY again. In