Page 1

HCD-V5500

SERVICE MANUAL

• HCD-V5500 is the deck, CD section

in MHC-V5500/V7700AV.

Manufactured under license from Dolby Laboratories

Licensing Corporation.

“DOLBY” and the doub le-D symbol a are trademarks

of Dolby Laboratories Licensing Corporation.

CD CD Mechanism Type CDM38-5BD21

Section Base Unit Name BU-5BD21

Tape deck Model Name Using Similar Mechanism HCD-V8800

Section T ape Transport Mechanism T ype TCM-220WR2E

E Model

Chinese Model

Model Name Using Similar Mechanism HCD-V8800

Optical Pick-up Type KSS-213B/S-N

VIDEO CD/CD player section

System Compact disc and digital

audio system

Laser Semiconductor laser

(λ=780nm)

Emission duration:

continuous

Laser output Max.44.6 µW*

*This output is the value

measured at a distance of

200 mm from the

objective lens surface on

the Optical Pick-up Block

with 7 mm aperture.

Audio

Frequency response 2 Hz - 20 kHz(±0.5 dB)

Wavelength 780 - 790 nm

Signal-to-noise ratio More than 90 dB

Dynamic range More than 90 dB

Video

Color system format NTSC, PAL

SPECIFICATIONS

CD OPTICAL DIGITAL OUT

(Square optical connector jack, rear panel)

Wavelength 600 nm

Output Level –18 dBm

Tape player section

Recording system 4-track 2-channel stereo

Frequency response 60 - 13,000 Hz (±3 dB),

(DOLBY NR OFF) using

Sony TYPE I cassette

60 - 14,000 Hz (±3 dB),

using Sony TYPE II

cassette

Design and specifications are subject to change

without notice.

MICROFILM

STEREO CASSETTE DECK CD PLAYER

Page 2

TABLE OF CONTENTS

1. SERVICING NOTE

······················································ 3

2. GENERAL ······································································ 4

3. DISASSEMBLY

3-1. Back Panel, CD Block Removal········································· 5

3-2. Cassette Lid (A)/(B) Assy, Mechanism Deck Removal ···· 5

3-3. Main Board, Resistor Board, Video Board,

Video In Board, Front Panel Assy Removal ······················· 6

4. TEST MODE ·································································· 7

5. ADJUSTMENTS

5-1. Mechanical Adjustment ······················································ 8

5-2. Electrical Adjustment ························································· 8

6. DIAGRAMS

6-1. Block Diagram — CD Section — ···································· 13

6-2. Block Diagram — Video Section — ································ 15

6-3. Block Diagram — Deck/System Control Section — ······· 17

6-4. Circuit Boards Location ··················································· 19

6-5. Schematic Diagram — Audio Section —························· 20

6-6. Printed Wiring Board — Audio Section —······················ 23

6-7. Printed Wiring Board — Video Section — ······················ 26

6-8. Schematic Diagram — Video Section — ························· 29

6-9. Schematic Diagram — Main Section — ·························· 33

6-10. Printed Wiring Board — Main Section — ······················· 37

6-11. Printed Wiring Board — CD Panel Section — ················ 40

6-12. Schematic Diagram — CD Panel Section — ··················· 43

6-13. Printed Wiring Board — BD Section — ·························· 45

6-14. Schematic Diagram — BD Section — ····························· 47

6-15. Schematic Diagram — Motor Section — ························ 49

6-16. Printed Wiring Board — Motor Section —······················ 51

6-17. IC Block Diagrams ··························································· 53

6-18. IC Pin Functions ······························································· 57

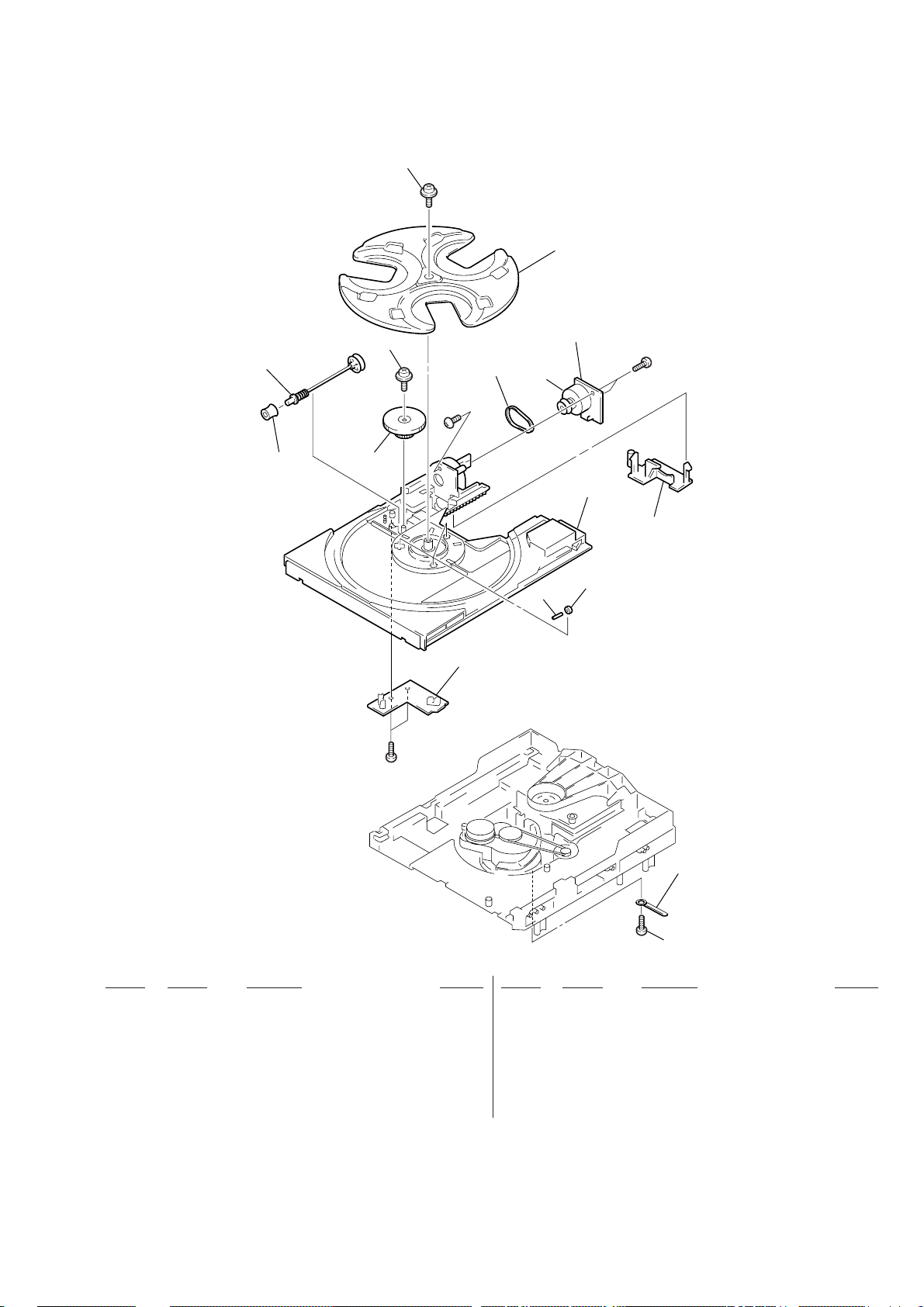

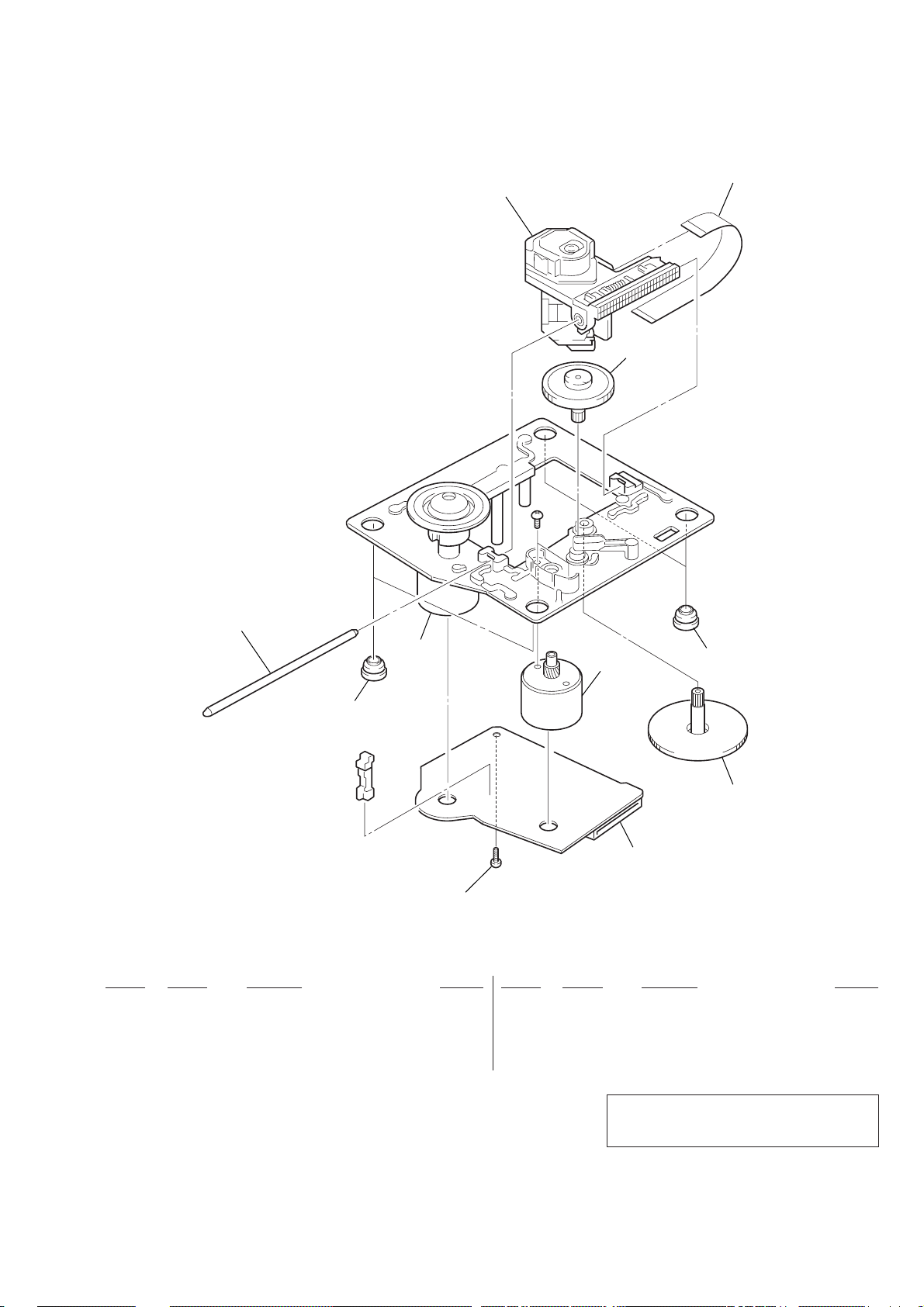

7. EXPLODED VIEWS

7-1. MAIN SECTION ····························································· 69

7-2. FRONT PANEL SECTION ·············································· 70

7-3. CD MECHANISM DECK SECTION

(CDM38-5BD21) ····························································· 71

7-4. CD MECHANISM DECK SECTION-2

(CDM38-5BD21) ····························································· 72

7-5. BASE UNIT SECTION (BU-5BD21) ····························· 73

7-6. TAPE MECHANISM DECK SECTION-1

(TCM-220WR2E) ···························································· 74

7-7. TAPE MECHANISM DECK SECTION-2

(TCM-220WR2E) ···························································· 75

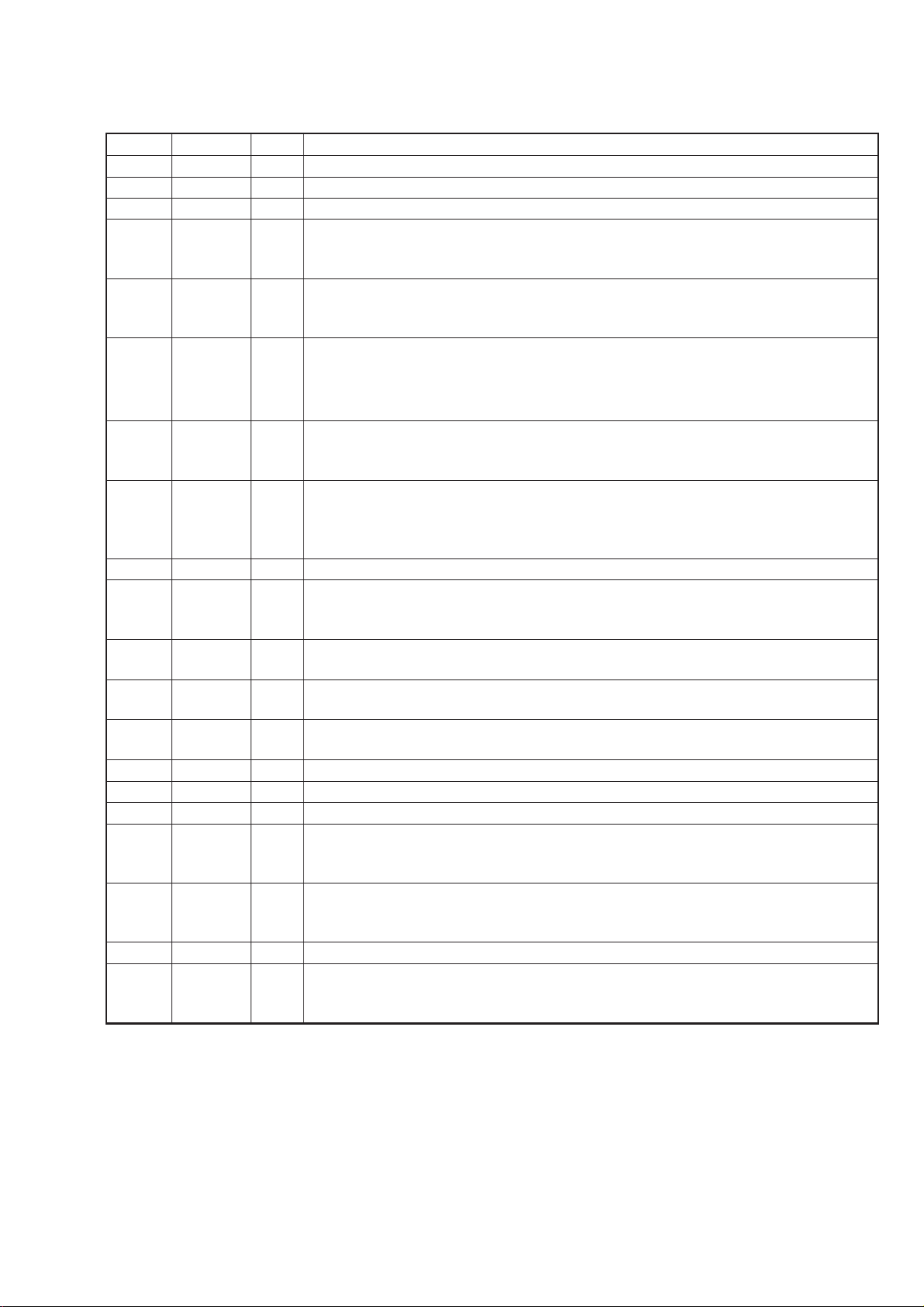

8. ELECTRICAL PARTS LIST ··································· 76

— 2 —

Page 3

SECTION 1

H

VIDEO board

TP709 (LED)

Oscilloscope

+

_

SERVICING NOTE

SELF-DIAGNOSIS

This model has the self-diagnosis function for the VIDEO and

AUDIO decoder sections.

Immediately after the power on, the self-diagnosis function searches

each operation of IC’s around the mechanism control microcomputer

(IC701).

The results can be checked by connecting an oscilloscope to TP709

(LED) of the VIDEO board.

Oscilloscope (Waveform) Symptom

H

No error

L

Light

Note: The LED for check (D701) is mounted to some sets

(FORMER TYPE). In this case, confirm the lighting

condition of LED.

[VIDEO BOARD] (SIDE A)

1 time blinking

2 time blinking

3 time blinking

H

External SRAM (IC751)

L

error

H

MPEG decoder (IC201)

L

error

DRAM (IC251)

error

L

D701

IC771

[VIDEO BOARD] (SIDE B)

TP709 (LED)

IC751

X901

IC251

— 3 —

Page 4

SECTION 2

GENERAL

@ª

@•

@¶

3

12 5 7 8 9 !¡

@§

4

@∞

6

@¢

@£

@™

@¡

@º

!º

!ª

!¶

!•

!™

!£

!¢

!∞

!§

1 DISC SKIP EX-CHANGE Button

(CD)

2 0 Button (CD)

3 PREV Button (CD)

4 NEXT Button (CD)

5 ) Button (CD)

6 RETURN Button (CD)

7 DISC 1 Button (CD)

8 DISC 2 Button (CD)

9 DISC 3 Button (CD)

!º SELECT Button (CD)

#º

!¡ 6 OPEN/CLOSE Button (CD)

!™ ·P CD NON-STOP Button (CD)

!£ p Button (CD)

!¢ · Button [B] (DECK)

!∞ ª Button [B] (DECK)

!§ π Button [B] (DECK)

!¶ ) Button [B] (DECK)

!• 0 Button [B] (DECK)

!ª DIRECTION MODE Button

(DECK)

@º PAUSE Button (DECK)

@¡ REC Button (DECK)

@™ HI-SPEED DUBBING Button

(DECK)

@£ CD SYNCHRO Button (DECK)

@¢ DOLBY NR Button (DECK)

@∞ ) Button [A] (DECK)

@§ 0 Button [A] (DECK)

@¶ π Button [A] (DECK)

@• ª Button [A] (DECK)

@ª · Button [A] (DECK)

#¡

#º OPTICAL DIGITAL OUT

#¡ SYSTEM CONTROL CONNECTOR

#™ SYSTEM SELECT SWITCH

#™ #£

#¢ #∞

#£ VIDEO IN JACK

#¢ MONITOR OUT JACK

#∞ S VIDEO JACK

— 4 —

Page 5

SECTION 3

0

DISASSEMBLY

Note : Follow the disassembly procedure in the numerical order given.

3-1. BACK PANEL, CD BLOCK REMOVAL

9

CD block

8

Screw

+BVTP 3

×

10

CASE

Unscrew the fi ve case attachment in the screws (case)

(M3 × 8) × 4, (+BV 3 × 8) × 1 and remove the case.

3

Back panel

1

Screw

+BVTP 3

2

Screw

+BVTP 3

×

1

×

8

7

Screw

+BVTP 3

3-2. CASSETTE LID (A)/(B) ASSY, MECHANISM DECK REMOVAL

1

Press the EJECT button and open the cassette lid.

Mechanism Deck (TCM-220WR2E)

7

+BVTP 2.6

6

Screw

4

5

CN112 (9 pin)

CN111 (8 pin)

×

10

×

8

1

Screw

+BVTP 3

Flat wire (19 core)

2

×

10

1

3

1

8

6

Screw

+BVTT 3

— 5 —

4

Flat wire (11 core)

5

Flat wire (21 core)

×

8

Page 6

3-3. MAIN BOARD, RESISTOR BOARD, VIDEO BOARD, VIDEO IN BOARD ,

d

FRONT PANEL ASSY REMOVAL

6

3

Screw

+BVTP 3

7

Bracket V (T)

9

VIDEO board

7

Bracket V (B)

×

10

Screw

+BVTP 3

×

10

8

Screw

+BVTP 3

5

!£

+BVTP 3

×

8

!º

Screw

+BVTP 3

Screw

4

×

8

×

8

!¡

VIDEO IN board

!™

Bracket (BP)

!¢

Bracket (H/S)

!∞

Resistor board

1

2

Front panel assy

Screw

+BVTP 3

×

8

• Tray (Slide) getting out procedure on the power supply is OFF

Rotate the BU CAM assembly in the direction of the arrow and pull out the slide.

!§

Screw

+BVTP 3

!¶

Main boar

×

8

Tray (Slide)

1

BU CAM assy

— 6 —

Page 7

SECTION 4

TEST MODE

VIDEO CD COLOR-BARS MODE

On this mode, the data of the color-bars signal as a picture signal

and the 1kHz sine wave signal as a sound signal are output by the

mechanism control microcomputer (IC701) for video CD signal

check. When measurement of the voltage and waveform on the

VIDEO board, perform it in this mode.

For reference, the color-bars signal can be observed at J9001

(VIDEO OUT) and the sound signal can be observed at J101

(VIDEO (AUDIO) OUT) using an oscilloscope.

1. Connect the lead wire to both ends of the land of SL701 (CAL

BAR) of the VIDEO board.

2. Turn the power on. Press FUNCTION button to select CD.

3. After 2 or 3 seconds later, connect the lead wire.

4. After measuring, remove the lead wire connected.

Note : The 1kHz sine wave is not outputted when the CD is played

once, but it is not error.

[VIDEO BARD ] (SIDE B)

SL703 (AFADJ)

SL702 (ADJ)

IC751

IC251

SL701 (CAL BAR)

— 7 —

Page 8

SECTION 5

ADJUSTMENTS

5-1. MECHANICAL ADJUSTMENT

PRECAUTION

1. Clean the following parts with a denatured-alcohol-moistened

swab:

record/playback head pinch roller

erase head rubber belts

capstan idlers

2. Demagnetize the record/playback head with a head

demagnetizer.

3. Do not use a magnetized screwdriver for the adjustments.

4. After the adjustments, apply suitable locking compound to the

parts adjusted.

5. The adjustments should be performed with the rated power

supply voltage unless otherwise noted.

• T orque Measurement

Mode Torque Meter Meter Reading

Forward CQ-102C

Forward

Back Tension (0.028 – 0.083 oz•inch)

Reverse CQ-102RC

Reverse

Back Tension (0.028 – 0.083 oz•inch)

FF, REW CQ-201B

CQ-102C

CQ-102RC

36 to 61g•cm

(0.50 – 0.84 oz•inch)

2 to 6g•cm

36 to 61g•cm

(0.50 – 0.84 oz•inch)

2 to 6g•cm

61 to 143g•cm

(0.85 – 1.99 oz•inch)

5-2. ELECTRICAL ADJUSTMENT

DECK SECTION

1. The adjustment should be performed in the publication.

(Be sure to make playback adjustment at first.)

2. The adjustment and measurement should be performed for both

L-CH and R-CH.

• Switch position

DOLBY NR switch : OFF

FUNCTION button : OFF

EFFECT switch : OFF

DBFB switch : OFF

3. Deck section electrical adjustments are made in test mode by

press key switch same time CD STOP DECK A ST OP and

DECK B STOP button.

4. Input point and output level measurement point.

• T ape Tension Measurement

Mode Tension Meter Meter Reading

Forward CQ-403A

Reverse CQ-403R

more than 100 g (3.53 oz)

more than 100 g (3.53 oz)

• Test Tape

Tape Signal Used for

P-4-A100 10 kHz, –10 dB

P-4-L300 315 Hz, 0dB Level Adjustment

WS-48B 3 kHz, 0dB Tape Speed Adjustment

0 dB=0.775V

Record/Playback Head Azimuth Adjustment

DECK A DECK B

Procedure:

1. Forward Playback mode

Reverse Playback mode

Head Azimuth Adjustment

— 8 —

Page 9

2. Turn the adjustment screw for the maximum output levels. If

t

these levels do not match, turn the adjustment screw until both

of output levels match together within 1 dB.

3. Playback Mode

Tape Speed Adjustment DECK A DECK B

Note: Start the T ape Speed adjustment as belo w after setting to the

test mode.

Set to test mode. (Press key switch same time CD STOP

DECK A STOP and DECK B STOP button.)

Test mode off. (Power off.)

Procedure:

• Perform high speed adjustment before normal speed adjustment.

Mode: Playback

4. Change the playback mode and repeat the steps 1 to 3.

5. After the adjustment, lock the adjustment screw with suitable

locking compound.

Adjustment Location:

— Record/playback head (Deck A and B) —

Speed

*High

Normal

Deck

A

B

A

B

Adjustment

RV652

RV652

RV651

RV651

Frequency counter

5,910 to 6,090 Hz

2,910 to 3,090 Hz

* Continue to press HIGH SPEED DUBBING switch (S259) in

playback mode : High speed playback.

Frequency difference between the beginning and the end of the

tape should be within ± 3%.

Frequency difference between deck A and deck B the beginning

of the tape should be within 1.5 %.

Adjustment Location: AUDIO board (See page 10)

Sample Value of Wow and flutter

W.RMS (JIS) within 0.3%

(test tape: WS-48B)

Playback level Adjustment DECK A DECK B

Procedure:

— FWD playback Mode —

test tape

P-4-L300

(315 Hz, 0 dB)

VTVM

set

Output level measurement poin

(See page 8)

+

–

Deck A is RV311 (L-CH) and RV411 (R-CH), Deck B is RV301

(L-CH) and RV401 (R-CH) so that adjustment within adjustment

level as follows.

Adjustment Level:

LINE OUT level : –8.2 to –7.2 dB (301.5 to 338.3 mV)

Level Difference between Channels : within 0.5 dB

Confirm the OUTPUT level does not change in playback mode

while changing the mode from playback to stop several times.

Adjustment Location: AUDIO board (See page 10)

— 9 —

Page 10

Record Bias Adjustment DECK B

)

Procedure:

1. Record mode

1) 315 Hz

2) 10 kHz

AF OSC

attenuator

50.1mV (–23.8dBs)

set

blank tape

CS-123

Adjustment Level:

OUTPUT level: –23.8 dB ± 1.0 dB (56.1 to 44.6 mV)

Adjustment Location: MAIN board

Adjustment Location :

[AUDIO BOARD] — Component Side —

RV301 : Playback Level (Deck B L-CH)

RV401 : Palyback Level

(Deck B R-CH)

RV651 : Tape Speed (Normal)

Input point (See page 8)

2. Mode: Playback

3. Confirm playback the signal recorded in step 1 become

adjustment level as follows.

4. If these levels do not adjustment level, adjustment the RV341

(L-CH) and RV441 (R-CH) to repeat steps 1 and 4.

Adjustment level: Playback output of 315 Hz to playback output

of 10 kHz: 0 ± 1.0 dB (0 ± 4.5mV).

Adjustment Location: AUDIO board

Record Level Adjustment DECK B

Procedure:

1. Record mode

RV341 : Record Bias (L-CH)

RV441 : Record Bias (R-CH)

RV411 : Playback Level (Deck A R-CH)

[MAIN BOARD] — Component Side —

RV451 Record Level (R

CNB108

RV401 Record Level (L)

RV652 : Tape Speed

(Hight)

RV311 : Playback Level

(Deck A L-CH)

2. Playback mode

3. Confirm playback the signal recorded in step 1 become

adjustment level as follows.

4. If these levels do not adjustment level, adjustment the RV401

(L-CH) and RV451 (R-CH) to repeat steps 1 and 4.

— 10 —

Page 11

CD SECTION

BD board

Oscilloscope

TP (RF)

TP (VC)

Note :

1. CD Block is basically designed to operate without adjustment.

Therefore, check each item in order given.

2. Use YEDS-18 disc (3-702-101-01) unless otherwise indicated.

3. Use an oscilloscope with more than 10MΩ impedance.

4. Clean the object lens by an applicator with neutral detergent

when the signal level is low than specified value with the

following checks.

S Curve Check

Oscilloscope

BD board

TP (FE)

TP (VC)

RF Level Check

Procedure :

1. Connect oscilloscope to test point TP (RF) on BD board.

2. Turned Power switch on.

3. Put disc (YEDS-18) in to play the number five track.

4. Confirm that oscilloscope waveform is clear and check RF

signal level is correct or not.

Note : A clear RF signal waveform means that the shape “◊” can

be clearly distinguished at the center of the waveform.

RF signal waveform

Procedure :

1. Connect oscilloscope to test point TP (FE) on BD board.

2. Connect between test point TP (FEI) and TP (VC) by lead wire.

3. Turned Power switch on.

4. Put disc (YEDS-18) in and turned Power switch on again and

actuate the focus search. (actuate the focus search when disc

table is moving in and out.)

5. Check the oscilloscope waveform (S-curve) is symmetrical

between A and B. And confirm peak to peak level within 3 ± 1

Vp-p.

S-curve waveform

Symmetry

A

Within 3

B

±

1 Vp-p

6. After check, remove the lead wire connected in step 2.

Note : • Try to measure several times to make sure than the ratio

of A : B or B : A is more than 10 : 7.

• Take sweep time as long as possible and light up the

brightness to obtain best waveform.

VOLT/DIV : 200mV

TIME/DIV : 500ns

Level : 1.3 Vp-p

+0.25

–0.20

— 11 —

Page 12

RF PLL Free-run Frequency Check

r

r

Procedure :

1. Connect frequency counter to TP (PLCK) with lead wire.

VIDEO SECTION

Frequency adjustment

BD baord

TP (PLCK)

frequency counte

2. Turned Power switch on.

3. Put the disc (YEDS-18) in to play the number five track.Conf irm

that reading on frequency counter is 4.3218 MHz.

Adjustment Location :

[BD BOARD] — SIDE A —

(FEI)

(FE)

(TE)

(PLCK)

IC103

(RF)

(VC)

1. Connect the frequency counter to check point of the VIDEO

board.

frequency counte

VIDEO board

TP410 (DCLK)

2. Adjust CT401 of the VIDEO board so that the frequency counter

read 13.5 MHz ± 40 Hz at STOP condition.

[VIDEO BOARD] — SIDE B —

SL703 (AFADJ)

SL702 (ADJ)

IC751

IC251

SL701 (CAL BAR)

CT401

Frequency

TP410 (DCLK)

IC101

— 12 —

Page 13

6-1. BLOCK DIAGRAM — CD SECTION —

HCD-V5500

SECTION 6

DIAGRAMS

OPTICAL PICK-UP

BLOCK (KSS-213B/S-N)

LASER

DIODE

POWER

PD

LD

DETECTOR

E

AC

BD

F

TRACKING

COIL

FOCUS

COIL

IC107

RF AMP

APC LD

2

AMP

1

3

4

SUMMING

5

6

TRACKING

8

9

FOCUS/TRACKING COIL DRIVE

SPINDLE/SLED MOTOR DRIVE

1

2

16

17

13

12

27

26

AMP

ERROR

AMP

IC103

RF

FOCUS

ERROR

BUFFER

19

RF

RF FQ

16

AMP

AMP

VC

IC102

15

13

1110

VC

12

4

5

19

20

10

9

23

24

INTEGRATOR

INTE-

GRATOR

LD

LD

DRIVE

Q101

4

1

VC

T+

T–

F+

F–

M102

SLED

M

MOTOR

M101

SPINDLE

M

MOTOR

DIGITAL SERVO

DIGITAL SIGNAL PROCESSOR

IC101

ASY0

39

RF AC

36

ASY1

ASYMMETRY

38

CORRECTION

RF DC

26

TE

27

28

29

4

6

8

10

2

100

96

SE

FE

TFDR

TRDR

FFDR

FRDR

SRDR

SFDR

MDP

A/D

CONVERTER

MIRR

DFCT

FOK

DETECTOR

62

XTAL

CLOCK

GENERATOR

DIGITAL

PLL

EFM

DEMODULATOR

SYNC

PROTECTOR

TIMING

GENERATOR 1

CLV SERVO

PROCESSOR

1B TIMS

OVERSAMPLING

FILTER

NOISE

SHAPER

REGISTER

CORRECTOR

GENERATOR 2

MIX

FOK

DFCT

MIRR

SERVO DSP

FOCUS

SERVO

TRACKING

SERVO

SLED

SERVO

PWM

GENERATOR

TRACKING

PWM

GENERATOR

FOCUS

PWM

GENERATOR

SLED

PWM

GENERATOR

ERROR

TIMING

DATA BUS

PRIORITY

EMCODER

ADDRESS

GENERATOR

32K

RAM

D/A

DATA

PROCESSOR

79 54

MUTE

+5V

MD2

70

DOUT

DIGITAL

OUT

PEAK

DETECTOR

SERIAL/PARALLEL

PROCESSOR

GFS

S STOP

99

+5V

SERVO

INTERFACE

S101

LIMIT

SWITCH

SUBCODE

P-W

PROCESSOR

SUBCODE

Q

PROCESSOR

INTERFACE

SEQUENCER

CPU

SERVO

AUTO

EXCK

SBSO

SUBQ

SQCK

SCLK

DATA

LRCK

BCLK

SCOR

WFCK

DATA

SENS

C2PO

DFCT

MIRR

XRST

71

76

75

77

78

83

46

45

47

74

73

86

XLT

87

CLK

88

80

56

FOK

93

92

91

81

DIGITAL

OUT

OPTICAL

1

LDON

384BD

EXCK

SUBQ

SUBQ

SQCK

SCLK

ADATA

LRCK

BCLK

SCOR

B

DATA

VIDEO

XLT

SECTION

CLK

(Page 15 )

SENS

C2PO

XRST

AMUTE

16

15MUTE

• SIGNAL PATH

: CD

: DIGITAL OUT

: VIDEO

— 13 — — 14 —

Page 14

HCD-V5500

6-2. BLOCK DIAGRAM — VIDEO SECTION —

BUFFER

X202

X201

9

8

7

6

5

IC501 (1/2)

XTL0O

2

XTL01

3

106

XTL2O

107

XTL2I

73

DATA

78

CLK

74

AMUTE

11

SQCK

10

SUBQ

77

SCLK

XLT

76

75

LDON

71

SCOR

62

SENS

RESET

48

112

11

111

12

110

13

109

14

103

15

100

101

102

D-RAM INTERFACE

38–43 46–55•

2–5 7–10 35–38 40–43

•

•

•

DQ1

A0

I/O8

I/O1

2–10 21 23–25

•11–13 15–19

21–29 • 31–3513 – 20

D7

D0

CD-ROM

DECODER

MPEG

AUDIO

DECODER

17–21 23 24 32 33••••

18–21 24–28•

A0

DQ16

D-RAM

IC251

S-RAM

IC751

A12

••

55

A0

A12

B

CD

SECTION

(Page 14 )

IC501

(2/2)

B

CD

SECTION

(Page 14 )

16

BCK

ADATA

LRCK

C2PO

384FS

ADATA

LRCK

BCLK

DATA

CLK

AMUTE

384FS

416

384FS

DATA

CLK

AMUTE

SQCK

SUBQ

SCLK

XLT

LDON

SCOR

SENS

XRST

28.63636MHz

45.1584MHz

MPEG DECODER

IC201

SYNC GENERATOR

HOST INTERFACE

5 6•• •119 120

D0

D7

XTCS

AS

VIDEO

POSTPROCESSOR

&

A0

A3

XHCS

3735

7–13 16

301516 31

W

LCAS

UCAS

IC772

WE

CE1

272022

6

54

3

12

13

40

MECHA CONTROL

IC701

MPEG

VIDEO

DECODER

EACH CIRCUIT BLOCK

•

IC771

A17

MPEG

SYSTEM

DECODER

34

A8

RAS

OE

8

10 9

11

12

41 54 56 43 70 7 8

RD

A18

XWR

10BIT VIDEO D/A CONVERTER

IC401

NOISE REDUCTION

IC301

OSD B

OSD G

OSD R

XOSDEN

VSYNC

HSYNC

DCLK

SYSTEM SELECT

1

4

Y

•

6

9

11

C

18

18

17

16

15

19

20

CK 1/2 Q

1 5

S601

RGB-YUV

CONV.

TIMING

GEN.

98 10097

HSYNC

OUTPUT

CONT.

SYNC

CONT.

PAL

AUTO

NTSC

VSYNC

34

35

36

37

44

18

43

DCLK

DCLKI

CMD0

CMD1

CMD2

CMD3

SACK

QINT

MREQ

NOISE

REDUSER

MEMORY

CONT.

OSD

IC271

VIDEO

RAM

DATA

SEL.

6.75MHz

CD-XRST

YUV-RGB

CONV.

DRAM

IF

DATA INPUT

SHIFT

RESISTOR

DISPLAY

POSITION

CONT.

OSC

8

IIC INTERFACE

IC901

1

60

4

•

67

51

58

NR-XCS

29

MCLK

30

MDATA

31

RESET

4

MDATA

3

OS-XLAT

2

MCLK

1

MDATA

X2

X1

111052

X901

5MHz

MCLK

OS-XLAT

RESET

IIC-DATA

IIC-CLK

68494847

6

9

11

18

NR-XCS

13.5MHZ

15

55

56

DEMPX, LEVEL

TRANSLATOR

INTERPOLTATOR

CLOCK GENARATOR

3

X401

27MHz

CT401

XRST

&

IC402

56

4

384FS

ADATA

LRCK

BCLK

DATA

CLK

DF-XLAT

AMUTE

LPF

LPF

DELAY

56

1/2

DCLK

BUFFER

IC181

13

4

1

MODULATOR

SYNC

SLOPE

GEN.

SYNC GEN.

&

TIMING CONT.

XRST

XVRST

FID

6

11

11

12

6

10

3

3

4

5

2

Y, C/Y, U, V

SELECTOR

&

INTER-

POLATOR

CLOSED

SUB

CAPTION

CARRIER

ENCODER

GEN.

SIO & I2O-BUS

CONT.

49 504859 60625557 51

VSYNC

HSYNC

VDAC-XLAT

CLK

DATA

• R CH: Same as L ch

• SIGNAL PATH

: VIDEO

: Y

: CHROMA

: CD

DIGITAL FILTER & D/A CONVERTER

IC101

TIMING

CIRCUIT

INPUT PLM

MODE

CONV.

D/A

CLOCK

GENERATOR

MUTE

CIRCUIT

71

Y0-Y7

74

Y

•

76

80

C0-C7

63

C

70

XSGRST

97

95

HSYNC

92

VSYNC

93

FID

94

DCLK

89

XOSDEN

56

OSD B

57

OSD G

58

OSD R

59

XRST

118

117115116114

XHDT

XHIRQ

CLOCK

GENERATOR

IC272

1

WAIT

XHIRQ

EXTAL

VDAC-XLAT

XTAL

5251

X701

10MHz

CMD0

CMD1

DF-XLAT

CMD2

CMD3

MREQ

SACK

QINT

NPIN

2

3

4

5

6

72

64

WR

V

Y

C

24

29325

INT

1

VIDEO AMP

IC451

5 7

3

Y/C AMP

IC452

1

3

2

21

22

2

27

3

25

16

18

CD FUNC

L CH

XRST

IIC-DATA

IIC-CLK

7

1

7

IC601

SELECTOR

33.8688MHz

ACTIVE LPF

IC102

16 7

R CH

(Page 17)

S VIDEO OUT

Q601

X101

A

MAIN

SECTION

4

J603

3

J601

MONITOR OUT

VIDEO IN

— 15 — — 16 —

Page 15

6-3. BLOCK DIAGRAM — DECK/SYSTEM CONTROL SECTION — 6-4. CIRCUIT BOARDS LOCATION

(B)

IC853

Q852

IC852

46

55

56

57

37

37

75

76

11

10

87

88

89

90

91

92

93

81

80

.

79

.

78

96

61

60

64

63

REG

REG

REG

CD POWER

IIC DATA

IIC CLK

XRST

CD FUNC

DISC SENS

TBL SENS

X1

X2

PB A/B

EQ H/N

BIAS

REC MUTE

NR ON/OFF

R/P PASS

LM ON/OFF

OUT OPEN

E1

E2

E3

TC RELAY

TBL R

TBL L

LOAD IN

LOAD OUT

REG

IC851

-7.5V

IC101

SYSTEM CONTROL

A PLAY SW

A HALF SW

B HALF SW

B PLAY SW

CAP M ON/OFF

-REG

Q855

RESET

KEY A

LED7

LED20

KEY B

A SHUT

B SHUT

TRG LOW

B TRG

A TRG

CAP M H/L

REC/PB

HEAD

(A DECK)

REC/PB

HEAD

(B DECK)

ERASE

+12V

+7V

A +7.5V

+5V

Q104

A +5V

D +5V

Q102

SWITCH

Q105

IC701

MOTOR DRIVE

OUT2

OUT1

IC801

MOTOR DRIVE

OUT2

OUT1

Q103

SWITCH

Q106

Q701

X101

5MHz

S801

OPEN SW

S851

ROTARY

ENCODER

6

IN2

3

IN1

2

R IN

F IN

10

L CH

A

REC

PB

10

RV401

REC(L)

LEVEL

22 A7.5V

IIC DATA

CD FUNC

9

IIC CLK

XRST

DOLBY

B

DOL

PAS

NORM/CROM/METAL

PB A/B

NORM/HIGH

BIAS ON/OFF

RM ON/OFF

NR ON/OFF

REC PB/PASS

LM ON/OFF

A120/70

D +5V

IC703

DISC

SENSOR

REC

6

PB

8

12

14

16

17

18

19

20

13

15

TURN

MOTOR

SLIDE

MOTOR

IC702

TABLE

SENSOR

S1005

A CrO2

DET

S1008

B CrO2

DET

2

M701

M

7

4

M801

M

7

VIDEO

SECTION

(Page 16 )

IC401

RV311

PB(L)

HP101

R CH

HRPE101

R CH

R CH

HEAD

16

3

5

PB EQ

AMP

IC611

PB EQ

AMP

IC601

RV341

REC

BIAS

Signal path

: CD

: PB(DECK A)

: PB(DECK B)

: REC(DECK B)

1

7

C331,L331

BIAS

TRAP

RV301

LEVEL

LEVEL

PB(L)

1

2

3

Q621,622

IC602

REC/PB SWITCH

BIAS

OSC

4

R CH

+7.5V

Q623

DOLBY NR/REC EQ AMP

2

A

B

4

REC

11

EQ

NORM

29

BIAS

CROM

SW

28

70

120

CD L

2

REC L

6

CNB108

7

SYSTEM

12

CONTROL1

14

AC

TO STR-W550

11

CNP701

AC

15

RECT

Q901-904

PB L

IIC DATA

IIC CLK

SENSOR BOARD

MOTOR BOARD

CD PANEL BOARD

RESET

3

15

IC103

LED1

LED6

LED

2

DRIVE

Q201-204

7

Q219,220

S251-266

FUNCTION

29

KEY

73

.

72

.

70

LED

DRIVE

65

.

Q205-218

53

49

.

S270-282

41

FUNCTION

30

KEY

S1001

A PLAY

94

26

97

28

95

27

85

84

83

86

82

+5V

S1004

A HALF

+5V

S1007

B HALF

S1002

B PLAY

+5V

SWITCH

Q410,411

CAPSTAN

MOTOR

SWITCH

Q405,408

SWITCH

Q409

+5V

1

D201-210

D211-227

TC (A) BOARD

+5V

+5V

SPEED

CONTROL

Q651

RV651

TAPE

SPEED

(NOMAL)

Q1001

ROTATION

DET A

S1006

REC A

S1009

REC B

Q1002

ROTATION

DET B

4

6

5

IC402

TRIGGER

MOTOR DRIVE

VZ

OUT1

IN2

OUT2

IN1

RV652

TAPE

SPEED

(HIGH)

2

M2

TRIGGER

M

MOTOR

10

M1

CAPSTAN

M

MOTOR

LEAF SWITCH BOARD

TC PANEL BOARD

— 17 — — 18 — — 19 —

CONNECTOR BOARD

AUDIO BOARD

MOTOR (TURN) BOARD

VIDEO BOARD

TC

BOARD

HCD-V5500

BD BOARD

MOTOR (SLIDE) BOARD

VIDEO IN BOARD

RESISTOR BOARD

MAIN BOARD

Page 16

HCD-V5500

6-17. IC BLOCK DIAGRAMS

IC101 CXD2545Q IC103 CXA1821M-T6

EXCK

SQSO

SQCK

MUTE

SENS

XRST

DIRC

SCLK

DFSW

ATSK

DATA

XLAT

CLOK

COUT

ADD

MIRR

DFCT

FOK

FSW

MON

MDP

MDS

LOCK

SRON

SRDR

SFON

TFDR

TRON

TRDR

TFON

FFDR

FRON

FRDR

FFON

VCO0

VCO1

TEST

DVSS

TES2

TES3

VPCO

VCKI

AVDD

IGEN

AVSS

ADIO

SFDR

100

1

4

5

10

11

12

13

14

15

16

17

18

PDO

19

20

21

22

23

24

RFC

25

SLED PWM

GENERATOR

2

3

TRACKING PWM

GENERATOR

6

7

8

9

FOCUS PWM

GENERATOR

MIRR

DFCT

A/D

CONVERTER

SWITCH

BUFFER

TE

SERVO DSP

&

FE

SE

PWM GENERATOR

FOK DETECTOR

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42

RFDC

SLED

SERVO

TRACKING

SERVO

FOCUS

SERVO

4

VC

SSTP

3

FILO

PROCESSOR

SHAPER

18-TIMES

OVER SAMPLING

FILTER

DIGITAL

PLL

VARI-PITCH

DOUBLE SPEED

FILI

PCO

CLV

NOISE

ADD

D/A

DIGITAL

PROCESSOR

ASYE

7980818292 91 90 89 88 87 86 85 84 83

DETECTOR

SUBCODE

PROCESSOR

PEAK

Q

SERIAL

PARALLEL

PROCESSOR

43 44 45

93949596979899

CPU

CPU

INTERFACE

INTERFACE

SERVO

AUTO

SEQUENCER

SERVO

MICRO PROGRAM

INTERFACE

CPU

ADDRESS

INTERFACE

GENERATOR

PRIORITY

CPU

ENCODER

INTERFACE

ERROR

CPU

CORRECTOR

INTERFACE

CPU

TIMING

INTERFACE

GENERATOR 2

CPU

ASYMMETRY

INTERFACE

CORRECTION

BIAS

AVSS

RFAC

ASYI

CLTV

32K RAM

CPU

EFM

INTERFACE

DEMODULATOR

MUX

REGISTER

ASYO

AVDD

PSSL

WDCK

LRCK

767778

SUBCODE

P-W

PROCESSOR

TIMING

GENERATOR 1

SYNC

PROTECTOR

DIGITAL

OUT

CLOCK

GENERATOR

46 — 50

DA16|DA12

1

LD VCCVCC

75

SBSO

SCOR

74

WFCK

73

EMPH

72

D OUT

71

70

MD2

C16M

69

68

C4M

67

FSTO

FSTI

66

DVSS

65

XTSL

64

XTAO

63

62

XTAI

61

DA01

|

|

51

DA11

2

PD LD ON

3

A LC/PD

4

B RFE

5

C RFO

D FE

6

VEE FE BIAS

VEE

7

VC

8

F TE

9

E VC

VC

EI EO

10

VCC

VREF

VEE

VC

RF SUMMING AMP

IC201 CXD1852AQ

VDD

DCLK

B/Cb7

B/Cb6

B/Cb5

B/Cb4

B/Cb3

B/Cb2

B/Cb1

B/Cb0

G/Y7

G/Y6

G/Y5

90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61

G/Y4

VEE

VC

VEE

G/Y3

VSS

APC LD AMP

FOCUS ERROR AMP

TRACKING ERROR AMP

VC

VC

VCC

VDD

G/Y2

G/Y1

G/Y0

RF EQ AMP

VC

VC BUFFER

R/Cr7

R/Cr6

R/Cr5

R/Cr4

R/Cr3

VC

R/Cr2

R/Cr1

20

19

18

17

16

15

14

13

12

11

R/Cr0

XVOE

VSS

IC101 CXD8567AM

28

PLMPLM

CLOCK

GENERATOR

D Vdd 2

27

26

25

24

23

22

21

20

19

18

17

16

15

1INIT

SYSM L1 (+)

2

ATT A Vdd L

3

SHIFT L2 (+)

4

MODES/P

LATCH A Vss L

5

256FSO X Vss

6

TEST1 512IN

7

D Vss X OUT

8

MCKSEL X Vdd

9

XBCK A Vss R

10

DATA R2 (+)

11

LRCK A Vdd R

12

MUTE L R1 (+)

13

MUTE R D Vdd 1

14

MUTE

TIMING CIRCUIT

ATT

CIRCUIT

DC

DITHER

FIR3FIR2FIR1

AC

DITHER

SAMPLE

HOLD (X1)

3RD ORDER

NOISE SHAPER

IIR

— 53 — — 54 —

91VSS

92HSYNC

93VSYNC

94FID/FHREF

95CBLNK/FSC

96CSYNC

97XSGRST

98CLK0O

CLOCK

99DOUT

DATO

100

101

LRCO

102

BCKO

103

FSXI

104

VDD

105

VSS

106

XTL2O

CLOCK

107

XTL2I

108

VDD

109

C2PO

110

LRCI

111

DATI

112

BCKI

113

DOIN

114

XHCS

115

XHDT

116

XRW

117

XHIRQ

118

XRST

RESET

119

HA0

120

HA1

123456789101112131415161718192021222324252627282930

VSS

CLOCK

XTLOO

XTLO1

VDD

CD-ROM

DECODER

INTERFACE

HA2

HA3

HOST

HD0

HD1

HD2

VIDEO POSTPROCESSOR

SYNC GENERATOR

MPEG

AUDIO

DECODER

EACH

CIRCUIT

BLOCK

HD3

HD4

HD5

HD6

VDD

&

SYSTEM

DECODER

D-RAM

INTERFACE

VSS

HD7

MPEG

MA3

MA4

MA2

MA5

60 VDD

59 OSDR

58 OSDG

57 OSDB

56 XOSDEN

55 MD15

54 MD0

53 MD14

52 MD1

TEST

51 MD13

50 MD2

49 MD12

48 MD3

47 MD11

46 MD4

45 VSS

44 VDD

43 MD10

42 MD5

41 MD9

40 MD6

39 MD8

38 MD7

37 XCAS0

36 XCAS2/MA9

35 XMWE

34 XRAS

33 MA8

32 MA7

31 VSS

TDI

VST

TDO

TENAI

MPEG

VIDEO

DECODER

BC

VSS

MA1

MA6

MA0

TCKI

Page 17

IC271 BU6257AFV-E2

CLK

CS

DATA

RESET

VDD

CKOUT

OSCOUT

OSCIN

TEST

VSS

1

PROTECTION

SIZE

SIZE

SIZE

DATA INPUT

SHIFT REGISTER

HORIZONTAL

ADDRESS

REGISTER

POSITION ADDRESS

VERTICAL

ADDRESS

COUNTER

VERTICAL

POSITION

COUNTER

WRITE

ADDRESS

COUNTER

COUNTER

VERTICAL

ADDRESS

COUNTER

DATA SELECTOR

CHARACTER

GENERATOR

ROM

12X18-BIT

X255-WORD

2

3

REGISTER

4

5

6

7

8

OSCILLATION

CIRCUIT

9

10

HORIZONTAL HORIZONTAL HORIZONTAL

COUNTER COUNTER

VERTICAL

COUNTER

TEST

CIRCUIT

CHARACTERCHARACTER

DATA

3-BIT

x

288

WORD

BACKGROUND

CONTROL

REGISTER

DATA

CIRCUIT

VIDEO RAM

COLOR

DATA

3-BIT

x

288

WORD

CHARACTER

DISPLAY

CONTROL

DATA

REGISTER

DATA

8-BIT

x

288

WORD

20

HSYNC

19

VSYNC

18

VB

17

VG

16

VR

15

VBLK

14

VC2

OUTPUT CONTROL

13

BLK2

12

VC1

11

BLK1

IC301 CXD1854Q

CBLNKO79VSYNCO78HSYNCO77VSS576BO775BO674BO573BO472BO371BO270BO169BO068VDD367Y/GO766Y/GO665Y/GO564Y/GO463Y/GO362Y/GO261Y/GO160Y/GO059VDD258C/RO757C/RO656C/RO555C/RO454C/RO353C/RO252C/RO151C/RO0

80

CSYNCO

81

82HAPGAIN0

83HAPGAIN1

84TEST

85TEN

86HAPBPF0

87IFSEL1

88HAPBPF1

89NRON

90LEVEL0

91LEVEL1

92FNR UFRZ

93XRST

94VSS7

95CSYNCI

96CBLNKI

97VSYNCI

98HSYNCI

99VDD5

100DCLKI

1

2

BI73BI64BI55BI46BI37BI28BI19BI0

VSSO

TIMING

GENERATOR

8 8 8

YUV-RGB

CONVERSION

Y

B-Y

C/R-Y

NOISE

REDUCER

C/R-Y

RGB-YUV

CONVERSION

8

10

11

VSS1

Y/GI712Y/GI613Y/GI514Y/GI415Y/GI316Y/GI217Y/GI118Y/GI0

Y

B-Y

8 8

MICRO COMPUTER

INTERFACE

D-RAM

MEMORY

CONTROLLER

19

20

VSS2

C/RI721C/RI622C/RI523C/RI424C/RI325C/RI226C/RI127C/RI0

28

29

VDD0

XCS

50 VSS4

49 VCPT

48 VCP

47 HVCCT

46 HVCC

45 ADVS

44 ADVD

43 CORON

42 BLCKST3

41 VSS3

40 BLCKST2

39 BLCKST1

38 BLCKST0

37 VDD1

36 BLCKSIZE

35 BLCKNR1

34 BLCKNR0

33 SXP COM

32 SDO

31 SDI

30

XSCK

— 55 —

Page 18

IC401 CXD1913Q

10bit

DAC

10bit

DAC

10bit

DAC

-

XTEST1

XTEST336TD835TD934VDD33TD1O

37-39

32 CO

31 AVSS3

30 AVDD3

29 YO

28 AVSS2

27 AVDD2

26 VG

25 VB

24 COMPO

23 AVSS1

22 AVDD1

21 VREF

20 IREF

XVRST50XCS49SCK48SI

51

52

F1

53VDD

54XTEST4

55XRST

56SYSCLK

57PDCLK

1/2

58VSS

59VSYNC

60HSYNC

61SO

62FID

63VDD

64XIICEN

4 4

1-4

-

Y7

Y4

3

BURST FLAG

SYNC Gen.

and

Timing Controller

SIO and I2O-Bus

Controller

Dempx,

Level

Translator

and

Interpolator

4 : 2 : 2 to

8

5

6-9

-

Y3

VSS

4 : 4 : 4

8

10

11-18

-

C7

C0

Y0

VDD

CSYNC

Sub Carrier

Gen.

Closed Caption Encoder

(for NTSC)

Y

U

V

Delay

LPF

LPF

VSS

47

SYNC Slope

Gen.

CHROMA

Modulator

19

VSS

TDO45TCK44TMS43TDI42VDD41TRST40VSS

46

TEST MODE

Y, C/

Y, U, V

selector and

Interpolator

IC272 TC7W74F

VCC

8

1

CK

7

2

D

Q

6

5

RSQ

QDC

3

4

Q

GND

CLR

PR

IC601 uPC1330HA

2

1

SW R1 GND SW P1

3

INVERTER

COMPARATER

5 6 7 8 9

4

CONT GND VCC SW P2 GND

SW R2

IC701 M54641L

VCC VCC

1

REG

IN1

IN2

INPUT

3

AMP.

CONTROL

INPUT

6

AMP.

4

GND

IC801 BA6286N

GND

RIN

VREF

OUT2

RNF

GND

OUT1

VM

VCC

FIN

8

REFERENCE

5

POWER

AMP.

POWER

AMP.

1

2

3

4

5

6

7

8

9

10

TSD

OUT2

2

OUT1

7

POWER

SAVE

CONTROL

LOGIC

— 56 —

Page 19

6-18. IC PIN FUNCTIONS

• IC101 SYSTEM CONTROL (UPD780016YGF-016-3BA)/MAIN board

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

Pin Name

NC

LED 1

LED 2

LED 5

LED 6

LED 3

LED 4

NC

T est

X2

X1

Vdd

XT2

XT1

Reset

NC

NC

SCOR

SOFT TEST

AC CUT

NC

NC

Vdd

AVdd

ADJ

A SHUT

B SHUT

B-HALF

KEY A

KEY B

KEY C

ADJ 2

AVSS

SQ DATA IN

NO USE

SQ CLK

CD-FUNC

NC

NC

VSS

LED 20

SENSE2

COM D IN

COM D OUT

COM CLK

CD POWER

CD DATA

CD CLK

LED 19

LED 18

I/O

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Not used.

O

O

O

O

O

O

O

I

I

I

O

I

I

I

I

I

I

I

I

I

O

I

O

O

O

O

O

LED control.

LED control.

LED control.

LED control.

LED control.

LED control.

Not used.

Ground.

X’tal (5MHz).

X’tal (5MHz).

5V.

Not used.

Not used.

Reset signal input.

Not used.

Not used.

CD Q data request.

Soft operation check port.

AC power supply check.

Not used.

Not used.

5V.

5V.

CD adjustment port.

Reel pulse detection.

Reel pulse detection.

Cassette half detection.

Key input.

Key input.

Key input.

Not used.

Ground.

CD data input.

Not used.

Clock for data input.

Not used.

Ground.

Ground.

Ground.

Not used.

BD status input.

Ground.

Not used.

Not used.

CD power.

CD data output.

CD clock.

LED control.

LED control.

Description

— 57 —

Page 20

Pin No.

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

Pin Name

LED 17

LED 16

LED 15

IIC-TEMP

IIC DATA

IIC CLK

XRST

XLAT

FOCUS SW

TBL L

TBL R

TRAY LED

LOAD OUT

LOAD IN

LED 14

LED 13

LED 12

LED 11

LED 10

LED 9

Vss

LED 8

LED 7

SENS

DISC SENS

T-SENS

UPSW

ENC3

ENC2

ENC1

OUT OPEN

CAP M H/N

A TRG

B TRG

TRG LOW

CAP M ON/OFF

PB A/B

EQ H/N

BIAS

REC MUTE

NR ON/OFF

R/P PASS

LM-ON/OFF

A PLAY SW

B PLAY SW

TC RELAY

A HALF

POWER

NC

NC

I/O

O

O

O

—

I/O

I/O

O

O

O

O

O

—

O

O

O

O

O

O

O

—

O

O

—

O

O

O

O

O

O

O

O

O

O

I/O

O

O

—

—

—

Description

LED control.

LED control.

LED control.

Not used.

Communciation data.

Comunicaton clock.

CD reset.

CD latch.

Focus switch.

Table-L.

Table-R.

Not used.

Load out.

I

I

I

I

I

I

I

I

I

I

I

Load in.

LED control.

LED control.

LED control.

LED control.

LED control.

LED control.

Ground.

LED control.

LED control.

BD status input.

Disc sensor.

Table sensor.

Not used.

Encoder input for CDM38.

Encoder input for CDM38.

Encoder input for CDM38.

Encoder input for CDM38.

Capstan motor H/N selection.

Mechanism timing output control.

Mechanism timing output control.

Mechanism timing output control.

Capstan motor ON/OFF switch.

Playback A/B selection.

Equalizer H/L selection.

Bias ON/OFF.

REC mute.

NR ON/OFF.

REC/PB/PASS select.

TC mute.

Mechanism PLAY switch.

Mechanism PLAY switch.

Head selection.

Cassette half detection.

Not used.

Not used.

Not used.

— 58 —

Page 21

• IC201 MPEG DECODER (CXD1852AQ)/VIDEO board

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

Pin Name

VSS

XTL0O

XTL0I

VDD

HA2

HA3

HD0

HD1

HD2

HD3

HD4

HD5

HD6

VDD

VSS

HD7

MA3

MA4

MA2

MA5

MA1

VSS

MA6

MA0

BC

TCKI

TDI

TENAI

TDO

VST

VSS

MA7

MA8

XRAS

XMWE

XCAS2/MA9

XCAS0

MD7

MD8

MD6

I/O

—

Ground

O

Video decoder master clock pin. Input the XTL0I clock or connect an oscillator between XTL0I and XTL0O.

I

The recommended frequencies are 27MHz, 28.6363MHz (NTSC 8fsc), and 35.4686 MHz (PAL 8fsc).

—

+5V power supply

I

Address input pin. In some cases, serves as the control signal and data input according to the setting

I

of the control mode.

I/O

I/O

I/O

I/O

Data input/output

I/O

I/O

I/O

—

+5V power supply

—

Ground

I/O

Data input/output

O

O

Address signal pin. Connect to the DRAM address pin with the same number.

O

O

O

—

Ground

O

Address signal pin. Connect to the DRAM address pin with the same number

O

I

I

I

For test (Not used)

I

I

I

For test (Connect to ground)

—

Ground

O

Address signal pin. Connect to the DRAM address pin with the same number.

O

RAS signal pin. Connect to the RAS pin of the DRAM. Same for the 256Kw × 16b, 256Kw × 16b × 2,

O

and 512Kw × 8b × 2 DRAM structures.

O

WE signal pin. Connect to the WE pin of the DRAM.

CAS signal. Connect to the CAS pin of the DRAM so as to control the lower bytes of the upper word (256K to

O

512K-1) for the 256Kw × 16b ¥ 2 DRAM structure. / Address signal pin. Connect to the DRAM address pin with

the same number. (Not used)

CAS signal. Connect to the CAS pin of the DRAM so as to control the lower bytes (MD0 to MD7) for 256Kw ×

O

16b and 512Kw × 8b × 2 DRAM structures, and to control the lower bytes of the lower word (0 to 256K-1) for

the 256Kw × 16b × 2 DRAM structure.

I/O

Data input/output signal pin. Connect to the DRAM data pin so that the lower and upper bytes of the data

I/O

correspond to the CAS0 to CAS3 controls.

I/O

Description

.

— 59 —

Page 22

Pin No.

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

Pin Name

MD9

MD5

MD10

VDD

VSS

MD4

MD11

MD3

MD12

MD2

MD13

MD1

MD14

MD0

MD15

XOSDEN

OSDB

OSDG

OSDR

VDD

VSS

XVOE

R/Cr0

R/Cr1

R/Cr2

R/Cr3

R/Cr4

R/Cr5

R/Cr6

R/Cr7

G/Y0

G/Y1

G/Y2

VDD

VSS

G/Y3

G/Y4

G/Y5

G/Y6

G/Y7

I/O

I/O

Data input/output signal pin. Connect to the DRAM data pin so that the lower and upper bytes of

I/O

the data correspond to the CAS0 to CAS3 controls.

I/O

—

+5V power supply

—

Ground

I/O

I/O

I/O

I/O

I/O

Data input/output signal pin. Connect to the DRAM data pin so that the lower and upper bytes of

I/O

the data correspond to the CAS0 to CAS3 controls.

I/O

I/O

I/O

I/O

I

OSD enable signal

I

OSD data input pin. When the XOSDEN input is “L”, the color registered in the register specified by

I

this 3 inputs (3 bits) is output as the image data.

I

—

+5V power supply

—

Ground

Video output enable signal pin. When set to “L”, enables the image data output and DCLK output. When set to

I

“H”, disables (high impedance). Output control can also be performed by writing in the register. (Connected to

ground)

O

O

O

O

Output pin of the R or Cr signal of the image data. MSB is R/Cr7. Synchronizes with DCLK.

O

O

O

O

O

O

Output pin of the G or Y signal of the image data. MSB is G/Y7. Synchronizes with DCLK.

O

—

+5V power supply

—

Ground

O

O

Output pin of the G or Y signal of the image data. MSB is G/Y7. Synchronizes with DCLK.

O

O

O

Description

— 60 —

Page 23

Pin No.

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

Pin Name

B/Cb0

B/Cb1

B/Cb2

B/Cb3

B/Cb4

B/Cb5

B/Cb6

B/Cb7

DCLK

VDD

VSS

HSYNC

VSYNC

FID/FHREF

CBLNK/FSC

CSYNC

XSGRST

CLK0O

DOUT

DATO

LRCO

BCKO

FSXI

VDD

VSS

I/O

O

O

O

O

Output pin of the B or Cb signal of the image data. MSB is B/Cb7. Synchronizes with DCLK. (Not used)

O

O

O

O

Dot clock (DCLK) signal pin. The DCLK frequency is normally 13.5MHz. The DCLK can be input from this pin

I

or can be made by frequency-dividing (1/integer) the clock input from XTL0I.

—

+5V power supply

—

Ground

Horizontal sync signal pin. When using the built-in sync generator, a signal is made by frequency-dividing the

I

dot clock (DCLK). Serves as the input when not using the built-in sync generator.

Vertical sync signal pin. When using the built-in sync generator, a signal is made by frequency-dividing the

I

DCLK. Serves as the input when not using the built-in sync generator.

Field determination signal. Odd field correspond to “H” and even field correspond to “L”. Serves as an output

when the built-in sync generator is used, and as an input when not.

I

/ Signal obtained by frequency-dividing the clock input from XTL0I or XTLI. When the input clock is 8 fsc, it

can be used as the horizontal sync signal phase comparison reference signal.

Composite blanking signal pin. Serves as an output when the built-in sync generator is used, and as an input

I

when not. / Signal obtained by frequency-dividing the clock input from XTL0I or XTLI. When the input clock is

8 fsc, it can be used as the fsc signal.

O

Composite sync signal pin. A signal is made by frequency-dividing the DCLK. Cannot be input. (Not used)

I

Sync generator reset signal pin. The signal generator is initialized by setting this pin to “L”.

Outputs the frequency-divided clock of the clock input to XTL0I. The frequency dividing ratio can be selected

O

from 1/2, 1/4, and 1/8. (Not used)

O

Digital output (Not used)

O

Audio serial data output to Audio D/A converter (IC101)

O

LR clock output to Audio D/A converter (IC101)

O

Bit clock output to Audio D/A converter (IC101)

I

Input 384fs (16.9344MHz) or 768fs (33.8688MHz).

—

+5V power supply

—

Ground

Description

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

XTL2O

XTL2I

VDD

C2PO

LRCI

DATI

BCKI

DOIN

XHCS

XHDT

HRW

XHIRQ

XRST

HA0

HA1

O

CD-ROM decoder, audio decoder master clock. Input a clock to the XTL21 or connect an oscillator between

XTL2I and XTL2O. The recommended frequency is 45 MHz. This clock is for the internal circuit. Does not

I

synchronize with inputs and outputs.

—

+5V power supply

I

C2 pointer input (CXD2545Q)

I

LR clock input (CXD2545Q)

I

Serial data input (CXD2545Q)

I

Bit clock input (CXD2545Q)

I

Digital input signal (Not used)

I

Register access chip select signal pin.

I/O

Data acknowledge/wait signal pin for DMA transmission, register access, transparent memory access.

I

Register access control signal pin.

O

Interrupt request signal

I

Hardware reset input pin. When set to “L”, all registers and operations are reset and initialized.

I

Address input pin. In some cases, serves as the control signal and data input according to the setting

I

of the control mode.

— 61 —

Page 24

• IC301 NOISE REDUCTION (CXD1854Q)/VIDEO board

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

Pin Name

VSS

BI7

BI6

BI5

BI4

BI3

BI2

BI1

BI0

VSS

Y/GI7

Y/GI6

Y/GI5

Y/GI4

Y/GI3

Y/GI2

Y/GI1

Y/GI0

VSS

C/RI7

C/RI6

C/RI5

C/RI4

C/RI3

C/RI2

C/RI1

C/RI0

VDD

XCS

XSCK

SDI

SDO

SXP COM

BLCKNR0

BLCKNR1

BLCKSIZE

VDD

BLCKST0

BLCKST1

BLCKST2

VSS

BLOCKST3

CORON

ADVD

ADVS

HVCC

HVCCT

VCP

VCPT

VSS

I/O

—

Ground

I

[MSB]

I

I

I

B input 0–7 (Connect to ground)

I

I

I

I

[LSB]

—

Ground

I

[MSB]

I

I

I

G (Y) input 0–7

I

I

I

I

[LSB]

—

Ground

I

[MSB]

I

I

I

R (Cb/Cr) input 0–7

I

I

I

I

[LSB]

—

Power supply (+5V)

I

Chip select input from IIC interface (IC901)

I

Serial clock input from IIC interface (IC901)

I

Serial data input from IIC interface (IC901)

O

Serial data output. (Not used)

I

Serial/parallel select

I

NR effect level control input

I

NR effect level control input

I

Block size select input

—

Power supply (+5V)

I

RAS signal for DRAM (Connected to ground)

I

CAS signal for DRAM (Connected to ground)

I

Write enable signal for DRAM (Connected to ground)

—

Ground

I

DRAM data input (Connected to ground)

I

DRAM data input (Connected to +5V)

I

DRAM data input (Connected to +5V)

I

DRAM data input (Connected to ground)

I

DRAM data input (Not used)

I

DRAM data input (Connected to +5V)

I

DRAM data input (Not used)

I

DRAM data input (Connected to ground)

—

Ground

Description

— 62 —

Page 25

Pin No.

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

Pin Name

C/RO0

C/RO1

C/RO2

C/RO3

C/RO4

C/RO5

C/RO6

C/RO7

VDD

Y/GO7

Y/GO6

Y/GO5

Y/GO4

Y/GO3

Y/GO2

Y/GO1

Y/GO0

VDD

BO0

BO1

BO2

BO3

BO4

BO5

BO6

BO7

VSS

HSYO

VSYO

CBLO

CSYO

HAPGAIN0

HAPGAIN1

TEST

TEN

HAPBPF0

IFSEL 1

HAPBPF1

NRON

LEVEL 0

LEVEL 1

FNR UFRZ

XRST

VSS

CSYI

CBLI

VSYI

HSYI

VDD

DCLKI

I/O

O

[MSB]

O

O

O

R (Cb/Cr) output 0–7

O

O

O

O

[LSB]

—

Power supply (+5V)

O

[MSB]

O

O

O

G (Y) output 0–7

O

O

O

O

[LSB]

—

Power supply (+5V)

O

[MSB]

O

O

O

B output 0–7 (Not used)

O

O

O

O

[LSB]

—

Ground

O

H SYNC output (Not used)

O

V SYNC output (Not used)

O

Composit blanking output (Not used)

O

Composit SYNC output (Not used)

I

Profile cooperation effect level control

I

Profile cooperation effect level control

I

Test pin (Connect to ground)

I

Test pin (Connect to +5V)

I

Profile cooperation correction band control

I

Matrix select Y/C, RGB (Connect to ground)

I

Profile cooperation correction band control

I

Noise reducer on/off (L: off, H: on)

I

Noise reducer level select

I

0: weak –3: strong (Not used)

I

NR feedback coefficient user processor select (Connect to +5V)

I

Power on reset

—

Ground

I

Composit SYNC input (Connect to ground)

I

Composit blanking input (Connect to +5V)

I

V SYNC input

I

H SYNC input

—

Power supply (+5V)

I

Dot clock input (13.5MHz)

Description

— 63 —

Page 26

• IC401 10 BIT VIDEO D/A CONVERTER (CXD1913Q)/VIDEO board

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

Pin Name

Y7

Y6

Y5

Y4

VSS

Y3

Y2

Y1

Y0

VDD

C7

C6

C5

C4

C3

C2

C1

C0

VSS

IREF

VREF

AVDD1

AVSS1

COMPO

VB

VG

AVDD2

AVSS2

YOUT

AVDD3

AVSS3

COUT

TD10

VDD

TD9

TD8

XTEST1

XTEST2

XTEST3

VSS

TRST

VDD

TDI

TMS

I/O

I

8-bit pixel data input pins (PD0 to 7).

I

When control register bit “PIF MODE”=“0”, serve as input pins for multiplexed Y, Cb, Cr signals.

I

When control register bit “PIF MODE”=“1”, serve as input pins for Y signal.

I

—

Digital ground

I

8-bit pixel data input pins (PD0 to 7).

I

When control register bit “PIF MODE”=“0”, serve as input pins for multiplexed Y, Cb, Cr signals.

I

When control register bit “PIF MODE”=“1”, serve as input pins for Y signal.

I

—

Digital power supply

I

I

8-bit pixel data input pins/test data bus.

I

When control register bit “PIF MODE”=“0”, these input pins cannot be used.

I

When control register bit “PIF MODE”=“1”, serve as input pins for multiplexed Cb, Cr signals.

I

In the test mode, used for internal circuit test data bus.

I

The test mode is allowed to use only for device vendors.

I

I

—

Digital ground

O

Reference current output pin. Connect a resistor ×16 times (“16R”) of the output resistance value “R”

I

Voltage reference input pin. Sets the output full-scale value

—

Analog power supply

—

Analog ground

10-bit D/A converter output.

O

When control register bit “YC/YUV”=“1”, outputs the composite signal.

When control register bit “YC/YUV”=“0”, outputs the color difference (V) signal.

I

Connect to Vss with an approx. 0.1 µF capacitor

I

Connect to AVDD with an approx. 0.1 µF capacitor

—

Analog power supply

—

Analog ground

O

10 bit D/A converter output. (Luminance (Y) signal output.)

—

Analog power supply

—

Analog ground

10-bit D/A converter output.

O

When control register bit “YC/YUV”=“1”, outputs the chroma (C) signal.

When control register bit “YC/YUV”=“0”, outputs the color difference (U) signal.

Test data bus. In the test mode, used for internal circuit test data bus.

O

The test mode is allowed to use only for device vendors (Not used).

—

Digital power supply

O

Test data bus. In the test mode, used for internal circuit test data bus.

O

The test mode is allowed to use only for device vendors (Not used)

I

Test mode control input pin. Pulled-up.

I

When these pins are “H”, CXD1913Q is not in the test mode.

I

The test mode is allowed to use only for device vendors

—

Digital ground

I

Test mode reset input pin. During power on/reset, set to “L” for more than 40 clocks (SYSCLK) (Not used)

—

Digital power supply

I

Test mode control input pin. (Not used)

I

Description

— 64 —

Page 27

Pin No.

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

Pin Name

TCK

TDO

VSS

SI

SCK

XCS

XVRST

F1

VDD

XTEST4

XRST

SYSCLK

PDCLK

VSS

VSYNC

HSYNC

SO

FID

VDD

XIICEN

I/O

I

Test mode control input pin. Fix at “H”

O

Test data bus pin. (Not used)

—

Digital ground

Description

The functions of this pin are selected by Pin 64 XIICEN.

I

When the XIICEN pin is “H”, sets into the SONY SIO mode, and becomes the SI serial data input pin.

When the XIICEN pin is “L”, sets into the I2C-BUS mode, and becomes the SDA input/output pin

The functions of this pin are selected by Pin 64 XIICEN.

I

When the XIICEN pin is “H”, sets into the SONY SIO mode, and becomes the SCK serial clock input pin.

When the XIICEN pin is “L”, sets into the I2C-BUS mode, and becomes the SCL input pin

The functions of this pin are selected by Pin 64 XIICEN. Pulled-up.

When the XIICEN pin is “H”, sets into the SONY SIO mode, and becomes the XCK chip select input pin.

I

When the XIICEN pin is “L”, sets into the I

2

C-BUS mode, and becomes the SA slave address selection input

signal which selects the I2C-BUS slave address

Active “L” vertical sync reset input pin. Pulled-up.

I

Used for synchronizing external vertical sync and internal vertical sync.

When XVRST is “L”, the internal digital sync generator is reset according to the F1 state

Field ID input pin.

When externally synchronizing with the XVRST signal, the field to be reset is determined by this signal.

I

“H” indicates the first field.

“L” indicates the second field

—

Digital power supply

Test mode control input pin. Pulled-up.

I

When these pins are “H”, CXD1913Q is not s test mode.

The test mode is allowed to use only for device vendors

System reset input pin when active “L”.

I

During power on/reset, set to “L” for more than 40 clocks (SYSCLK)

I

System clock input pin.

To generate the correct sub carrier frequency, precisely 27MHz is required

13.5MHz pixel data clock output pin. This clock is obtained by 1/2 frequency-dividing SYSCLK.

O

Used only in the 16-bit pixel data mode

—

Digital ground

O

V.sync signal output

O

H.sync signal output

The functions of this pin are selected by Pin 64 XIICEN.

O

When the XIICEN pin is “H”, sets into the SONY SIO mode, and becomes the S0 serial-out output pin.

When the XIICEN pin is “L”, this pin is not used and sets into high impedance (Not used)

Field ID output.

O

When control register bit “FDS”=“1”, “L” indicates the first field and “H” indicates the second field.

When control register bit “FDS”=“0”, “H” indicates the first field and “L” indicates the second field

—

Digital power supply

Serial interface mode selection input pin. Pulled-up.

I

When “L”, Pins 48 to 50, and 61 set into the I

2

C-BUS mode.

When “H”, Pins 48 to 50, and 61 set into the SONY SOP mode

— 65 —

Page 28

• IC701 MECHANISM CONTROL (HD6433032SK12F)/VIDEO board

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13 to 20

21

22 to 29

30

31 to 35

36 to 39

40, 41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

Pin Name

CMD0

CMD1

CMD2

CMD3

SACK

QINT

VDAC-XLAT

DF-XLAT

P90/TXD

SUBQ

SQCK

VSS

D0 to D7

VCC

A0 to A7

VSS

A8 to A12

A13 to A16

A17, A18

A19

W AIT

MD0

MD1

φ

STBY

RESET

NM1

VSS

EXT AL

XT AL

VCC

AS

RD

WR

RESO

A VSS

TEST0

TEST1

TE

SENS

DA C-SELECT

NPIN

VSS

VREQ

VREF

I/O

I/O

Input/output terminal exchanging data bus 0 with IIC interface (IC901)

I/O

Input/output terminal exchanging data bus 1 with IIC interface (IC901)

I/O

Input/output terminal exchanging data bus 2 with IIC interface (IC901)

I/O

Input/output terminal exchanging data bus 3 with IIC interface (IC901)

O

Outputs command acknowledge to IIC interface (IC901)

O

Outputs command output pulses to IIC interface (IC901)

O

Serial data latch pulse output to Video D/A converter (IC401)

O

Serial data latch pulse output to Audio D/A converter (IC101)

—

Not used

I

Sub Q 80bit input (CXD2545Q)

O

SQSO readout clock output (CXD2545Q)

—

Ground

I/O

Data bus input/output (IC201, 751)

—

Connect to the power supply (+5V)

O

Address bus output (IC201, 751)

—

Ground

O

Address bus output (IC201, 751)

O

Address bus output (Not used)

O

Addres bus output (IC772)

O

Address bus output (Not used)

I

BUS control wait input (IC201)

I

Operation mode setting terminal (Connected to +5V)

I

Operation mode setting terminal (Connected to ground)

O

System clock output (Not used)

Shifts to the hardware standby mode when the standby terminal becomes “Low”.

I

(Unable to use H level fixed) (Connected to +5V)

I

Set into reset when the reset input pin becomes “Low”. (IC901)

I

Requests mask disable interruption. (Unable to use H level fixed) (Connected to +5V)

—

Ground

I

Connected to the Crystal oscillator. The EXTAL pin is also able to input external clocks. (10 MHz)

I

Connected to the Crystal oscillator. (10 MHz)

—

Power supply (+5V)

O

When the address strobe pin is “Low”, indicates that address outputs on the address bus are valid. (IC772)

O

When the read pin is “Low”, indicates that the external addresses space is in the read state. (IC201, 751)

When the read pin is “Low”, indicates that the external addresses space is in the write state and the data bus are

O

valid. (IC201, 751)

O

Reset output (Not used)

—

A/D converter (Pin62-69) ground

I

Color-bar test input (“L” = test)

I

AFADJ test input (“L” = test)

I

ADJ test input (“L” = test)

I

Internal state (SENSE) monitor input (CXD2545Q)

I

Audio D/A converter select mode setting terminal (Connected to +5V)

I

NTSC/PAL output mode setting terminal (0V : NTSC, 1.5V : AUTO, 3V : PAL)

—

Ground

I

Not used

I

A/D converter (Pin62-69) reference voltage input (Connected to +5V)

Description

— 66 —