Page 1

Hand–Held Terminal

(Catalog Number 1747–PT1)

User Manual

ALLEN–BRADLEY

Page 2

Important User Information

Solid state equipment has operational characteristics differing from those of

electromechanical equipment. “Safety Guidelines for the Application,

Installation and Maintenance of Solid State Controls” (Publication SGI-1.1)

describes some important differences between solid state equipment and

hard–wired electromechanical devices. Because of this difference, and also

because of the wide variety of uses for solid state equipment, all persons

responsible for applying this equipment must satisfy themselves that each

intended application of this equipment is acceptable.

In no event will the Allen-Bradley Company be responsible or liable for

indirect or consequential damages resulting from the use or application of

this equipment.

The examples and diagrams in this manual are included solely for illustrative

purposes. Because of the many variables and requirements associated with

any particular installation, the Allen-Bradley Company cannot assume

responsibility or liability for actual use based on the examples and diagrams.

No patent liability is assumed by Allen-Bradley Company with respect to use

of information, circuits, equipment, or software described in this manual.

Reproduction of the contents of this manual, in whole or in part, without

written permission of the Allen-Bradley Company is prohibited.

Throughout this manual we use notes to make you aware of safety

considerations.

ATTENTION: Identifies information about practices or

circumstances that can lead to personal injury or death, property

!

damage, or economic loss.

Attentions help you:

• identify a hazard

• avoid the hazard

• recognize the consequences

Important: Identifies information that is especially important for successful

application and understanding of the product.

PLC, PLC 2, PLC 3, and PLC 5 are registered trademarks of Allen-Bradley Company, Inc.

SLC, SLC 100, SLC 500, SLC 5/01, SLC 5/02, PanelView, RediPANEL, and Dataliner are trademarks of Allen-Bradley Company, Inc.

IBM is a registered trademark of International Business Machines, Incorporated.

Page 3

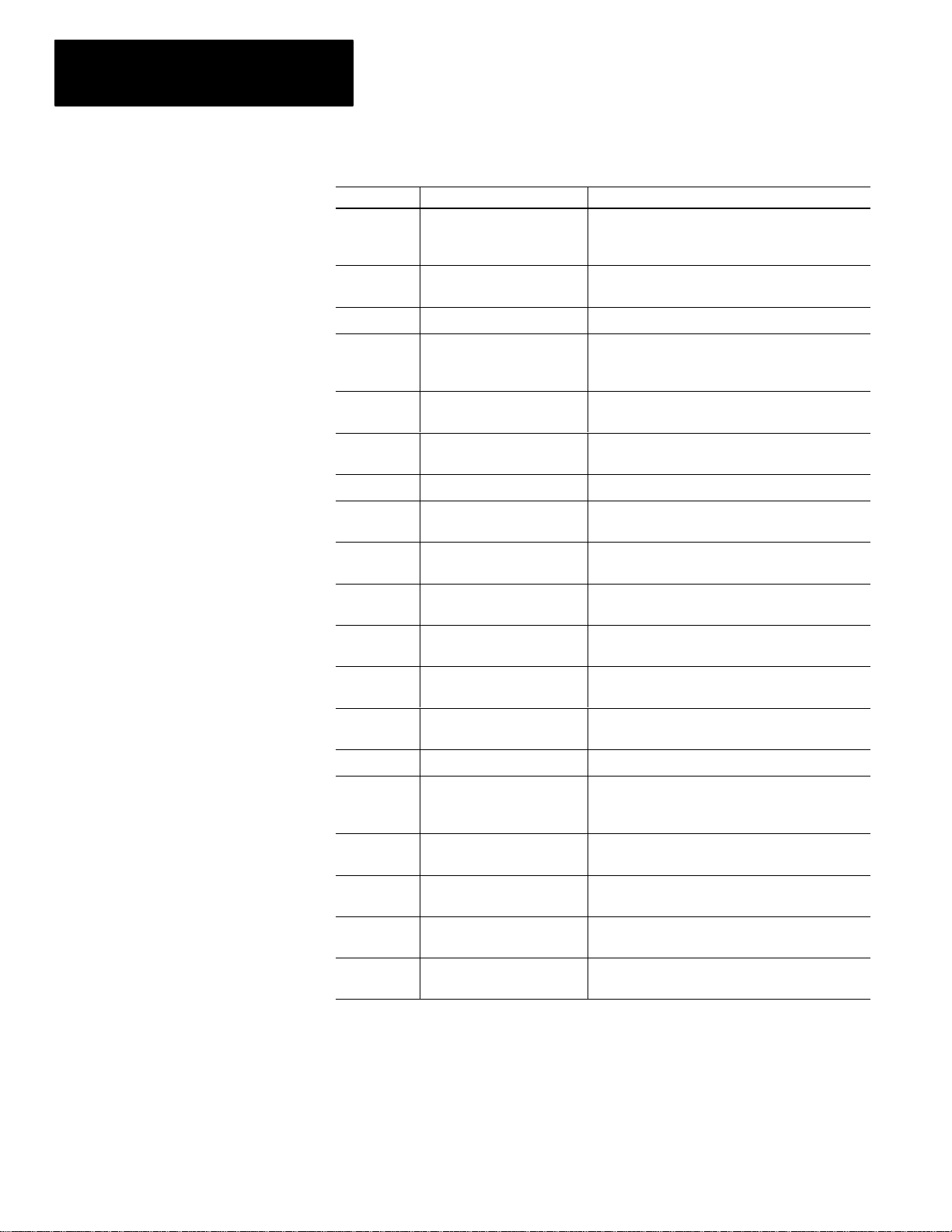

Summary of Changes

Summary of Changes

The information below summarizes the changes to this manual since the last

printing as 1747–809 in July 1989, which included the supplement

40063–079–01(A) from October 1990.

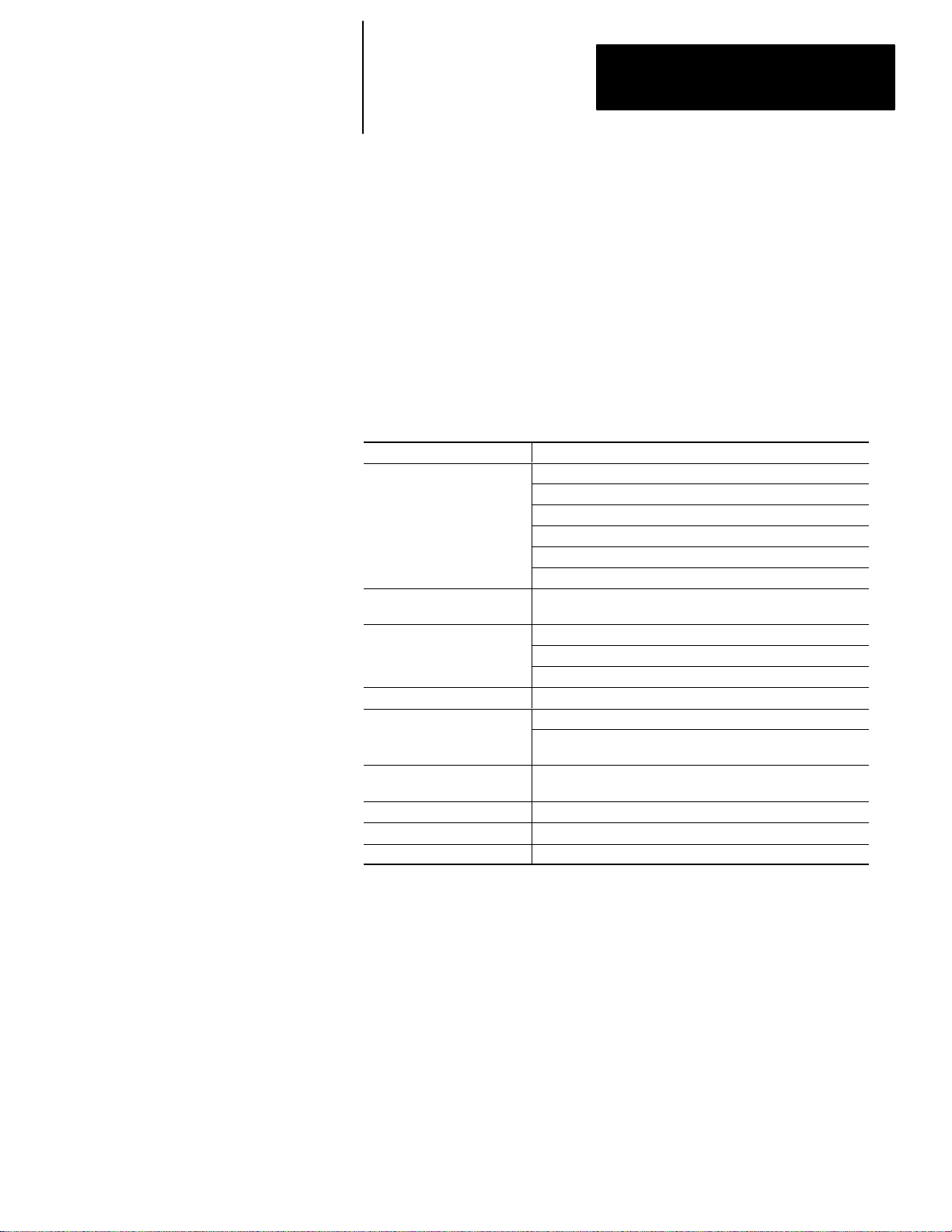

New Information

The table below lists sections that document new features and additional

information about existing features, and shows where to find this new

information.

For This New Information See Chapter

4 – Data File Organization and Addressing

6 – Creating a Program

Using the HHT with an SLC

Using the HHT with an SLC

5/02 (in general)

32–Bit Addition and

Subtraction

Index Register

Index Register

DH–485 devices 9 – Configuring Online Communication

User Fault Routine

Selectable Timed Interrupts

I/O Interrupts 31 – Understanding I/O Interrupts – SLC 5/02 Processor Only

Instruction Execution Times C – Memory Usage, Instruction Execution Times

Scan Time Worksheets D – Estimating Scan Time

8 – Saving and Compiling a Program

14 – Using EEPROMs and UVPROMs

15 – Instruction Set Overview

27 – The Status File

20 – Math Instructions

22 – File Copy and File Fill Instructions

23 – Bit Shift, FIFO, and LIFO Instructions

24 – Sequencer Instructions

28 – Troubleshooting Faults

29 – Understanding the User Fault Routine – SLC 5/02

Processor Only

30 – Understanding Selectable Timed Interrupts – SLC 5/02

Processor Only

Page 4

Page 5

Table of Contents

Hand–Held T erminal

User Manual

Preface

Who Should Use this Manual P–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Purpose of this Manual P–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents of this Manual P–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Related Documentation P–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Common Techniques Used in this Manual P–4. . . . . . . . . . . . . . . . . . . . . . . . . .

Allen–Bradley Support P–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Local Product Support P–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Product Assistance P–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Your Questions or Comments on this Manual P–5. . . . . . . . . . . . . . . . . . . . . .

Features, Installation,

Powerup

The Menu Tree

Chapter 1

HHT Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installing the Memory Pak, Battery, and Communication Cable 1–3. . . . . . . . . . .

HHT Powerup 1–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HHT Display Format 1–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The Keyboard 1–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Menu Function Keys (F1, F2, F3, F4, F5) 1–9. . . . . . . . . . . . . . . . . . . . . . . . .

Data Entry Keys 1–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Auto Shift 1–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Cursor Keys 1–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ZOOM and RUNG Keys 1–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 2

Using the HHT Menu 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Progressing through Menu Displays 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . .

The ENTER Key 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The ESCAPE Key 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The Main Menu 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Main Menu Functions 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SELFTEST, [F1] 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TERMINAL, [F2] 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PROGRAM MAINTENANCE, [F3] 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . .

UTILITY, [F5] 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The Menu Tree 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HHT Function Keys and Instruction Mnemonics 2–11. . . . . . . . . . . . . . . . . . . . . .

Function Keys 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instruction Mnemonics 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

i

Page 6

Table of Contents

Hand–Held T erminal

User Manual

Understanding File

Organization

Data File Organization and

Addressing

Chapter 3

Program, Program Files, and Data Files 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . .

Program 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Program Files 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Files 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Downloading Programs 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Uploading Programs 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using EEPROM and UVPROM Memory Modules for Program Backup 3–4. . . .

Chapter 4

Data File Organization 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data File Types 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Addressing Data Files 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data File 2 – Status 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Files 0 and 1 – Outputs and Inputs 4–4. . . . . . . . . . . . . . . . . . . . . . . . .

Data File 3 – Bit 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data File 4 – Timers 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data File 5 – Counters 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data File 6 – Control 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data File 7 – Integer 4–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Indexed Addressing

SLC 5/02 Processors Only 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Offset Value (S:24 Index Register ) 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating Data for Indexed Addresses 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . .

Crossing File Boundaries 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Monitoring Indexed Addresses 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Effects of File Instructions on Indexed Addressing 4–15. . . . . . . . . . . . . . . . . .

Effects of Program Interrupts on Index Register S:24 4–15. . . . . . . . . . . . . . . .

File Instructions – Using the File Indicator # 4–16. . . . . . . . . . . . . . . . . . . . . . . . .

Bit Shift Instructions 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Sequencer Instructions 4–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

File Copy and File Fill Instructions 4–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating Data 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating Data for Indexed Addresses 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . .

Deleting Data 4–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Program Constants 4–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

M0 and M1 Data Files – Specialty I/O Modules 4–21. . . . . . . . . . . . . . . . . . . . . .

Addressing M0–M1 Files 4–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Restrictions on Using M0-M1 Data File Addresses 4–21. . . . . . . . . . . . . . . . . .

Monitoring Bit Instructions Having M0 or M1 Addresses 4–22. . . . . . . . . . . . . .

ii

Page 7

Table of Contents

Hand–Held T erminal

User Manual

Transferring Data Between Processor Files and M0 or M1 Files 4–23. . . . . . . . .

Access Time 4–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Minimizing the Scan Time 4–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Capturing M0–M1 File Data 4–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Specialty I/O Modules with Retentive Memory 4–26. . . . . . . . . . . . . . . . . . . . .

G Data Files – Specialty I/O Modules 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Editing G File Data 4–28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ladder Program Basics

Chapter 5

Ladder Programming 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A 1–Rung Ladder Program 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Logical Continuity 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Series Logic 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example – Series Inputs 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Parallel Logic 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example – Parallel Inputs 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Branching 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example – Parallel Input Branching 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Branching 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example – Parallel Output Branching 5–5. . . . . . . . . . . . . . . . . . . . . . . . .

Example – Parallel Output Branching with Conditions (SLC 5/02 Only) 5–6. .

Nested Branching 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example – Nested Input and Output Branches 5–6. . . . . . . . . . . . . . . . . . .

Example 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A 4–Rung Ladder Program 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Application Example 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Cycle (Simplified) 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

When the Input Goes True 5–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

When the Input Goes False 5–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating a Program

Chapter 6

Creating a Program Offline with the HHT 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . .

Clearing the Memory of the HHT 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Configuring the Controller 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Configuring the Processor 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Configuring the I/O 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Configuring Specialty I/O Modules – (SLC 5/02 Specific) 6–5. . . . . . . . . . . .

Naming the Ladder Program 6–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Naming Your Main Program File 6–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Passwords 6–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Passwords 6–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Master Passwords 6–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Removing and Changing Passwords 6–13. . . . . . . . . . . . . . . . . . . . . . . . . . . .

iii

Page 8

Table of Contents

Hand–Held T erminal

User Manual

Creating and Editing

Program Files

Chapter 7

Creating and Deleting Program Files 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating a Subroutine Program File using the Next Consecutive File Number 7–1

Creating a Subroutine Program File using a Non–Consecutive File Number 7–2

Deleting a Subroutine Program File 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Editing a Program File 7–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ladder Rung Display 7–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering a Rung 7–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering an Examine if Closed Instruction 7–6. . . . . . . . . . . . . . . . . . . . . .

Entering an Output Energize Instruction 7–7. . . . . . . . . . . . . . . . . . . . . . . .

Adding a Rung with Branching 7–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Adding a Rung to a Program 7–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering a Parallel Branch 7–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Inserting an Instruction Within a Branch 7–12. . . . . . . . . . . . . . . . . . . . . . . .

Modifying Rungs 7–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Adding an Instruction to a Rung 7–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modifying Instructions 7–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changing the Address of an Instruction 7–16. . . . . . . . . . . . . . . . . . . . . . . .

Changing an Instruction T ype 7–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modifying Branches 7–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Extending a Branch Up 7–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Extending a Branch Down 7–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appending a Branch 7–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Delete and Undelete Commands 7–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Deleting a Branch 7–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Deleting an Instruction 7–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Copying an Instruction from One Location to Another 7–30. . . . . . . . . . . . . .

Deleting and Copying Rungs 7–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Abandoning Edits 7–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The Search Function 7–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Searching for an Instruction 7–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Searching for an Address 7–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Searching for a Particular Instruction with a Specific Address 7–40. . . . . . . .

Reversing the Search Direction 7–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Searching for Forced I/O 7–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Searching for Rungs 7–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating and Deleting Program Files 7–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating Data Files 7–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Deleting Data Files 7–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

Page 9

Table of Contents

Hand–Held T erminal

User Manual

Saving and Compiling a

Program

Configuring Online

Communication

Chapter 8

Saving and Compiling Overview 8–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Saving a Program 8–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Available Compiler Options 8–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[F1] Future Access (All Processors) 8–3. . . . . . . . . . . . . . . . . . . . . . . . . . .

[F2] Test Single Rung (SLC 5/02 Specific) 8–4. . . . . . . . . . . . . . . . . . . . . .

[F3] Index Checks (Index Across Files) (SLC 5/02) 8–5. . . . . . . . . . . . . . . .

[F4] File Protection (SLC 5/02) 8–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Viewing Program Memory Layout 8–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 9

Online Configuration 9–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Exceptions 9–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The Who Function 9–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Diagnostics 9–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Attach 9–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Exception 9–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Node Configuration 9–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Consequences of Changing a Processor Node Address 9–9. . . . . . . . . . . .

Entering a Maximum Node Address 9–10. . . . . . . . . . . . . . . . . . . . . . . . . .

Changing the Baud Rate 9–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Set and Clear Ownership 9–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Recommendations When Using DH–485 Devices 9–12. . . . . . . . . . . . . . . . . . .

Downloading/Uploading a

Program

Processor Modes

Chapter 10

Downloading a Program 10–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Uploading a Program 10–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 11

Processor Modes 1 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Program Mode 11–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Test Mode 11–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changing Modes 11–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changing the Mode 1 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

Page 10

Table of Contents

Hand–Held T erminal

User Manual

Monitoring Controller

Operation

Chapter 12

Monitoring a Program File 12–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

True/False Indication 12–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Monitoring Data Files 12–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Files 12–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Accessing Data Files 12–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Option 1 12–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Option 2 12–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Option 3 12–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Option 4 12–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Monitoring a Data File 12–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data File Displays 12–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output File (O0) 12–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input File (I1) 12–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Data File (S2) 12–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bit Data File (B3) 12–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Data File (T4) 12–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Counter Data File (C5) 12–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Control Data File (R6) 12–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Integer Data File (N7) 12–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Online Data Changes 12–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The Force Function

Using EEPROMs and

UVPROMs

Chapter 13

Forcing I/O 13–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Forcing an External Input 13–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

To Close an External Input Circuit 13–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

To Close and Open an External Circuit 13–4. . . . . . . . . . . . . . . . . . . . . . . . . .

Searching for Forced I/O 13–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Forcing an External Output 13–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Forces Carried Offline 13–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 14

Using an EEPROM Memory Module 14–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transferring a Program to an EEPROM Memory Module 14–1. . . . . . . . . . . . . .

Transferring a Program from an EEPROM Memory Module 14–3. . . . . . . . . . . .

EEPROM Burning Options 14–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Burning EEPROMs for a SLC 5/01 Processor or Fixed Controller 14–5. . . . . . . .

Burning EEPROMs for a SLC 5/02 Processor 14–5. . . . . . . . . . . . . . . . . . . . .

Burning EEPROMS for SLC Configurations 14–6. . . . . . . . . . . . . . . . . . . . . . .

UVPROM Memory Modules 14–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

Page 11

Table of Contents

Hand–Held T erminal

User Manual

Instruction Set Overview

Bit Instructions

Chapter 15

Instruction Classifications 15–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bit Instructions – Chapter 16 15–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer and Counter Instructions – Chapter 17 15–2. . . . . . . . . . . . . . . . . . . .

I/O Message and Communications Instructions – Chapter 18 15–3. . . . . . . .

Comparison Instructions – Chapter 19 15–4. . . . . . . . . . . . . . . . . . . . . . . . .

Math Instructions – Chapter 20 15–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Move and Logical Instructions – Chapter 21 15–6. . . . . . . . . . . . . . . . . . . . .

File Copy and File Fill Instructions – Chapter 22 15–6. . . . . . . . . . . . . . . . . .

Bit Shift, FIFO, and LIFO Instructions – Chapter 23 15–7. . . . . . . . . . . . . . . .

Sequencer Instructions – Chapter 24 15–7. . . . . . . . . . . . . . . . . . . . . . . . . .

Control Instructions – Chapter 25 15–8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Proportional Integral Derivative Instruction – Chapter 26 15–9. . . . . . . . . . . .

Instruction Locator 15–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 16

Bit Instructions Overview 16–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Examine if Closed (XIC) 16–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Examine if Open (XIO) 16–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Energize (OTE) 16–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Latch (OTL), Output Unlatch (OTU) 16–5. . . . . . . . . . . . . . . . . . . . . . . . .

One-Shot Rising (OSR) 16–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instruction Parameters 16–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer and Counter

Instructions

Chapter 17

Timer and Counter Instructions Overview 17–1. . . . . . . . . . . . . . . . . . . . . . . . . . .

Indexed Word Addresses 17–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Data File Elements, Timebase, and Accuracy 17–2. . . . . . . . . . . . . . . . . . .

Timebase 17–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Accuracy 17–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer On-Delay (TON) 17–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Bits 17–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Off-Delay (TOF) 17–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Bits 17–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Retentive Timer (RTO) 17–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Bits 17–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Count Up (CTU) and

Count Down (CTD) 17–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Bits 17–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

High–Speed Counter (HSC) 17–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instruction Parameters 17–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Application Example 17–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reset (RES) 17–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

Page 12

Table of Contents

Hand–Held T erminal

User Manual

I/O Message and

Communication

Instructions

Chapter 18

Message Instruction (MSG) 18–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Related Status File Bits 18–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Available Configuration Options 18–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 18–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Control Block Layout 18–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MSG Instruction Status Bits 18–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Successful MSG Instruction Timing Diagram 18–8. . . . . . . . . . . . . . . . . . . .

MSG Instruction Error Codes 18–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Application Examples 18–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example 1 18–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example 2 – Program File 2 of SLC 5/02 Processor 18–11. . . . . . . . . . . . . . .

Example 2 – Program File 2 of SLC 5/01 Processor at Node 3 18–12. . . . . . . .

Example 3 18–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Service Communications (SVC) 18–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Immediate Input with Mask (IIM) 18–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 18–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Immediate Output with Mask (IOM) 18–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 18–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O Event-Driven Interrupts 18–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O Interrupt Disable and Enable (IID, IIE) 18–18. . . . . . . . . . . . . . . . . . . . . .

Reset Pending I/O Interrupt (RPI) 18–18. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 18–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O Refresh (REF) 18–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Comparison Instructions

viii

Chapter 19

Comparison Instructions Overview 19–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Indexed Word Addresses 19–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Equal (EQU) 19–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 19–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Not Equal (NEQ) 19–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 19–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Less Than (LES) 19–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 19–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Less Than or Equal (LEQ) 19–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 19–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Greater Than (GRT) 19–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 19–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Greater Than or Equal (GEQ) 19–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 19–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Masked Comparison for Equal (MEQ) 19–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 19–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Limit Test (LIM) 19–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 13

Table of Contents

Hand–Held T erminal

User Manual

Entering Parameters 19–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

True/False Status of the Instruction 19–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Instructions

Chapter 20

Math Instructions Overview 20–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 20–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Overflow Trap Bit, S:5/0 20–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register, S:14 and S:13 20–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Indexed Word Addresses 20–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Add (ADD) 20–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Subtract (SUB) 20–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

32-Bit Addition and Subtraction–Series C and Later SLC 5/02 Processors 20–5. . .

Bit S:2/14 Math Overflow Selection 20–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example of 32-Bit Addition 20–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Multiply (MUL) 20–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Divide (DIV) 20–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Double Divide (DDV) 20–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Negate (NEG) 20–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clear (CLR) 20–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Convert to BCD (TOD) 20–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 20–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register (When Used) 20–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Convert from BCD (FRD) 20–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 20–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register (When Used) 20–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ladder Logic Filtering of BCD Input Devices 20–16. . . . . . . . . . . . . . . . . . . . . .

ix

Page 14

Table of Contents

Hand–Held T erminal

User Manual

Decode 4 to 1 of 16 (DCD) 20–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 20–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Square Root (SQR) 20–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Scale Data (SCL) 20–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 20–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 20–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register 20–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Typical Application – Converting Degrees Celsius to Degrees Fahrenheit 20–23. .

Move and Logical

Instructions

Chapter 21

Move and Logical Instructions Overview 21–1. . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 21–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Indexed Word Addresses 21–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 21–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Overflow Trap Bit, S:5/0 21–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Math Register, S:13 and S:14 21–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Move (MOV) 21–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 21–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 21–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Masked Move (MVM) 21–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 21–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 21–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation 21–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

And (AND) 21–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 21–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Or (OR) 21–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 21–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Exclusive Or (XOR) 21–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 21–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Not (NOT) 21–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Arithmetic Status Bits 21–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

File Copy and File Fill

Instructions

x

Chapter 22

File Copy and Fill Instructions Overview 22–1. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Effect on Index Register in SLC 5/02 Processors 22–1. . . . . . . . . . . . . . . . . . .

File Copy (COP) 22–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 22–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

File Fill (FLL) 22–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 22–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 15

Table of Contents

Hand–Held T erminal

User Manual

Bit Shift, FIFO, and LIFO

Instructions

Sequencer Instructions

Chapter 23

Bit Shift, FIFO, and LIFO Instructions Overview 23–1. . . . . . . . . . . . . . . . . . . . . .

Effect on Index Register in SLC 5/02 Processors 23–1. . . . . . . . . . . . . . . . . . .

Bit Shift Left (BSL), Bit Shift Right (BSR) 23–2. . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 23–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Effect on Index Register in SLC 5/02 Processors 23–3. . . . . . . . . . . . . . . . . . .

Operation – Bit Shift Left 23–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation – Bit Shift Right 23–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FIFO Load (FFL), FIFO Unload (FFU) 23–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 23–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Bits 23–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation 23–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Effects on Index Register S:24 23–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SLC 5/02 Processors Only 23–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LIFO Load (LFL), LIFO Unload (LFU) 23–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 23–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation 23–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Effects on Index Register S:24 23–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 24

Control Instructions

Sequencer Instructions Overview 24–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Applications Requiring More than 16 Bits 24–1. . . . . . . . . . . . . . . . . . . . . . . . .

Effect on Index Register in SLC 5/02 Processors 24–1. . . . . . . . . . . . . . . . . . .

Sequencer Output (SQO), Sequencer Compare (SQC) 24–2. . . . . . . . . . . . . . . . .

Entering Parameters 24–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Bits of the Control Element 24–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation – Sequencer Output 24–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Effect on Index Register in SLC 5/02 Processors 24–5. . . . . . . . . . . . . . . . . . .

Operation – Sequencer Compare 24–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Effect on Index Register in SLC 5/02 Processors 24–6. . . . . . . . . . . . . . . . . . .

Sequencer Load (SQL) 24–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 24–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Bits 24–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation 24–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Effect on Index Registers in SLC 5/02 Processors 24–9. . . . . . . . . . . . . . . . . .

Chapter 25

Control Instructions Overview 25–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Jump to Label (JMP) 25–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 25–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Label (LBL) 25–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 25–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Jump to Subroutine (JSR) 25–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xi

Page 16

Table of Contents

Hand–Held T erminal

User Manual

Nesting Subroutine Files 25–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 25–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Subroutine (SBR) 25–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Return from Subroutine (RET) 25–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Master Control Reset (MCR) 25–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Temporary End (TND) 25–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Suspend (SUS) 25–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 25–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Selectable Timed

Interrupt (STI) 25–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Selectable Timed Interrupt Disable and Enable (STD, STE) 25–11. . . . . . . . . . . .

Selectable Timed Interrupt Start (STS) 25–11. . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Subroutine (INT) 25–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PID Instruction

Chapter 26

Proportional, Integral, Derivative (PID) 26–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The PID Concept 26–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The PID Equation 26–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Entering Parameters 26–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Control Block Layout 26–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PID Instruction Flags 26–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Runtime Errors 26–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PID and Analog I/O Scaling 26–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Online Data Changes 26–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using Scaled V alues 26–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changing Values in the Manual Mode 26–15. . . . . . . . . . . . . . . . . . . . . . . . . . .

Application Notes 26–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input/Output Ranges 26–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Scaling to Engineering Units 26–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Zero-crossing Deadband DB 26–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Alarms 26–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Limiting with Anti-reset Windup 26–18. . . . . . . . . . . . . . . . . . . . . . . . . .

The Manual Mode 26–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Feed Forward 26–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Time Proportioning Outputs 26–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PID Tuning 26–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Procedure 26–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The Status File

xii

Chapter 27

Status File Functions 27–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status File Display –SLC 5/02 Processors 27–32. . . . . . . . . . . . . . . . . . . . . . . . . .

Status File Display – SLC 5/01 and Fixed Processors 27–33. . . . . . . . . . . . . . . . . .

Page 17

Table of Contents

Hand–Held T erminal

User Manual

Troubleshooting Faults

Understanding the User

Fault Routine – SLC 5/02

Processor Only

Chapter 28

Troubleshooting Overview 28–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User Fault Routine Not in Effect 28–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User Fault Routine in Effect – SLC 5/02 Processors Only 28–1. . . . . . . . . . . . .

Status File Fault Display 28–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Error Code Description, Cause, and Recommended Action 28–2. . . . . . . . . . . . . .

Powerup Errors 28–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Going–to–Run Errors 28–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Runtime Errors 28–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User Program Instruction Errors 28–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O Errors 28–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 29

Overview of the User Fault Routine 29–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status File Data Saved 29–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Recoverable and Non–Recoverable User Faults 29–1. . . . . . . . . . . . . . . . . . . . .

Recoverable User Faults 29–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Non-Recoverable User Faults 29–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating a User Fault Subroutine 29–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Application Example 29–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Understanding Selectable

Timed Interrupts – SLC 5/02

Processor Only

Chapter 30

STI Overview 30–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Basic Programming Procedure for the STI Function 30–1. . . . . . . . . . . . . . . . .

Operation 30–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

STI Subroutine Content 30–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Occurrences 30–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Latency 30–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Priorities 30–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status File Data Saved 30–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

STI Parameters 30–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

STD and STE Instructions 30–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

STD/STE Zone Example 30–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

STS Instruction 30–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

INT Instruction 30–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiii

Page 18

Table of Contents

Hand–Held T erminal

User Manual

Understanding I/O

Interrupts – SLC 5/02

Processor Only

HHT Messages and Error

Definitions

Number Systems, Hex Mask

Chapter 31

I/O Overview 31–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Basic Programming Procedure for the I/O Interrupt Function 31–1. . . . . . . . . . .

Operation 31–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Subroutine (ISR) Content 31–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Occurrences 31–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Latency 31–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Priorities 31–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status File Data Saved 31–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O Interrupt Parameters 31–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IID and IIE Instructions 31–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IID/IIE Zone Example 31–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RPI Instruction 31–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix A

Appendix B

Binary Numbers B–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Positive Decimal Values B–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Negative Decimal Values B–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BCD Numbers B–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hexadecimal Numbers B–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hex Mask B–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Usage, Instruction

Execution Times

Estimating Scan Time

xiv

Appendix C

Memory Usage C–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fixed and SLC 5/01 Processors C–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SLC 5/02 Processor C–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix D

Events in the Operating Cycle D–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Scan Time Worksheets D–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Defining Worksheet Terminology D–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Worksheet A — Estimating the Scan Time of Your Fixed Controller D–3. . . .

Worksheet B — Estimating the Scan Time of Your 1747–L511 or 1747–L514

Processor D–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Worksheet C — Estimating the Scan Time of Your 1747–L524 Processor D–5

Example Scan Time Calculation D–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example: Worksheet B – Estimating the Scan Time of a 1747–L514 Processor

Application D–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 19

Preface

Who Should Use this Manual

A–B

P

Preface

Read this preface to familiarize yourself with the rest of the manual. This

preface covers the following topics:

• who should use this manual

• the purpose of this manual

• conventions used in this manual

• Allen–Bradley support

Use this manual if you are responsible for designing, installing,

programming, or troubleshooting control systems that use Allen–Bradley

small logic controllers.

You should have a basic understanding of SLC 500 products. If you do not,

contact your local Allen–Bradley representative for information on available

training courses before using this product.

Purpose of this Manual

We recommend that you review The Getting Started Guide for HHT, catalog

number 1747–NM009 before using the Hand–Held Terminal (HHT).

This manual is a reference guide for technical personnel who use the

Hand–Held Terminal (HHT) to develop control applications. It describes

those procedures in which you may use an HHT to program an SLC 500

controller.

This manual:

• explains memory organization and instruction addressing

• covers status file functions and individual instructions

• gives you an overview of ladder programming

• explains the procedures you need to effectively use the HHT

P–1

Page 20

Preface

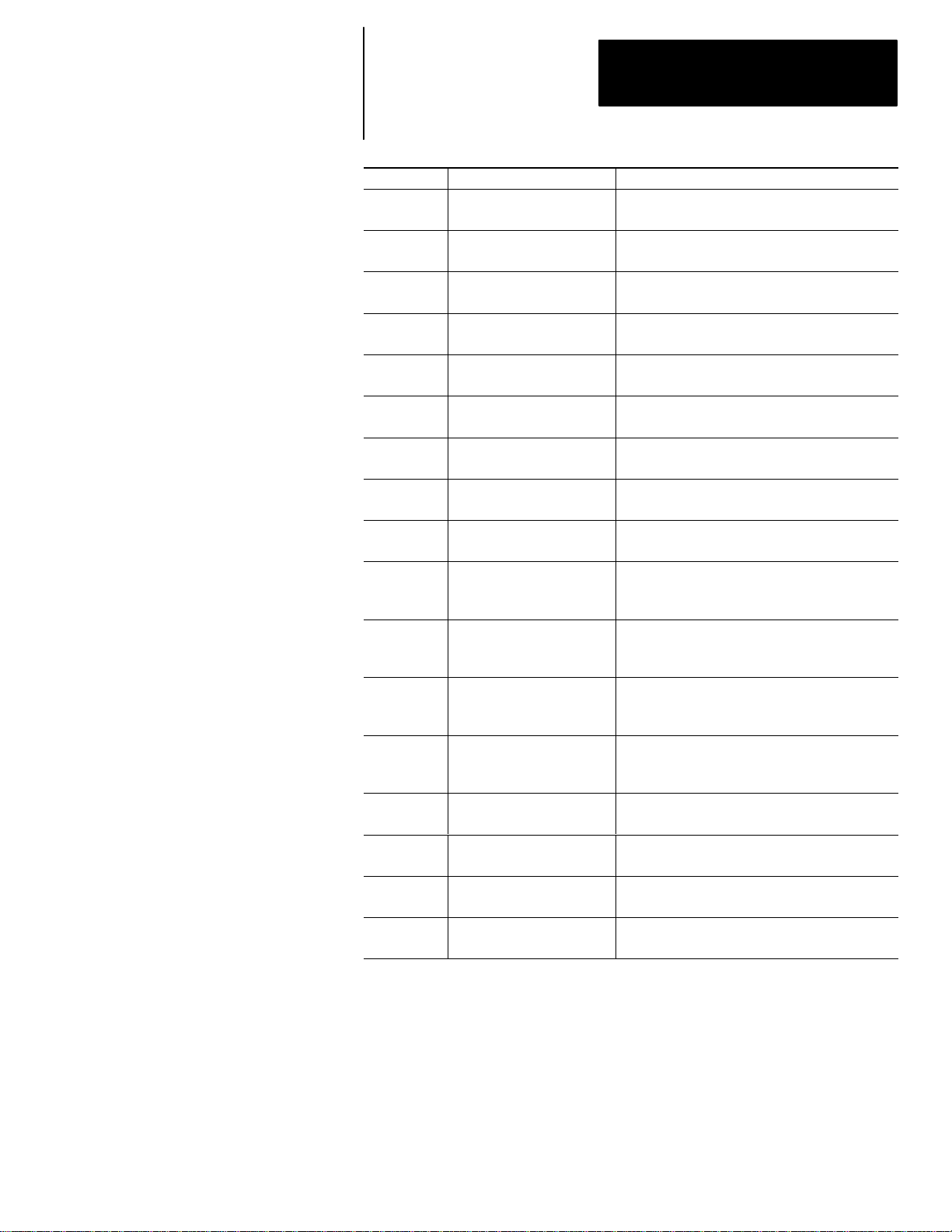

Contents of this Manual

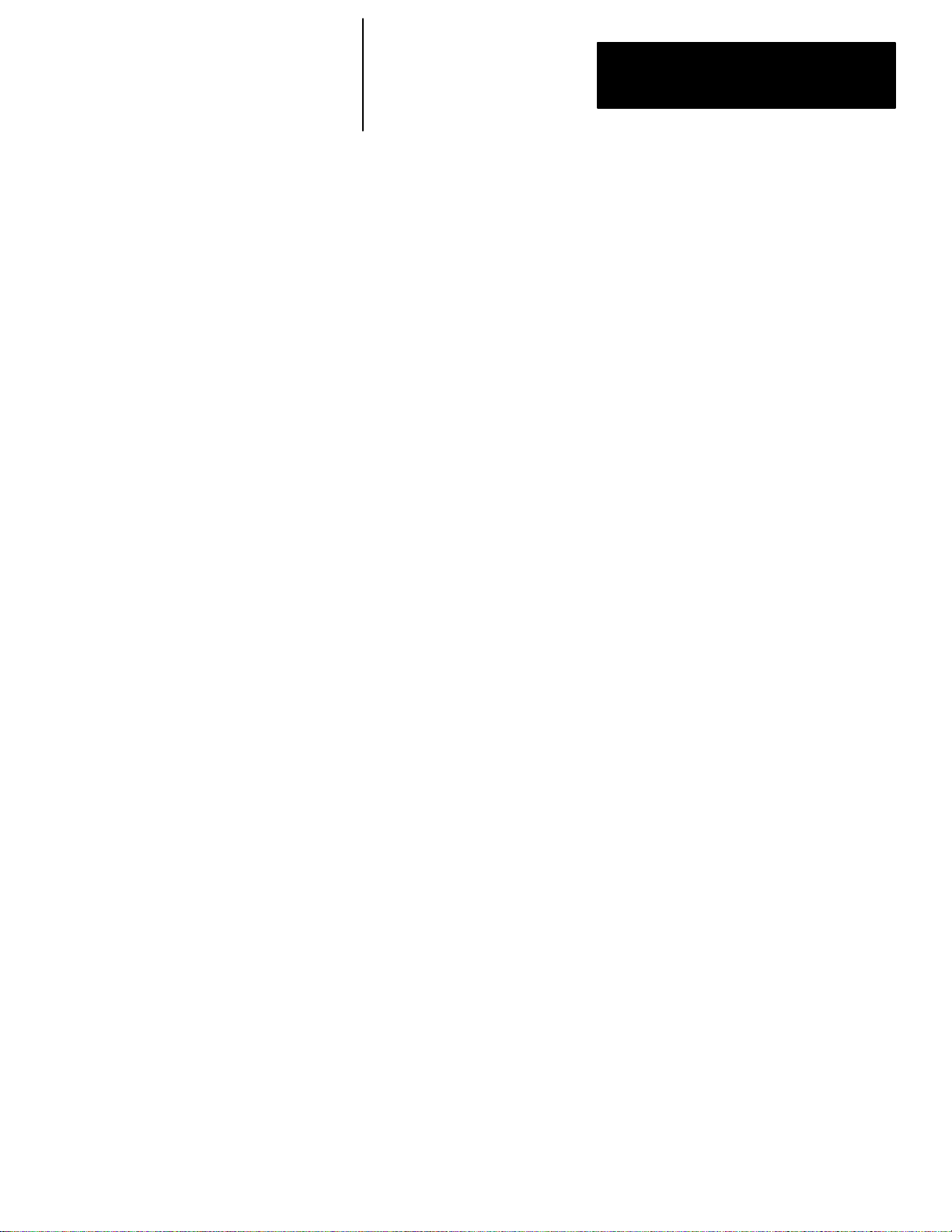

Chapter

Preface

Title Contents

Describes the purpose, background, and scope of

this manual. Also specifies the audience for whom

this manual is intended.

1

2 The Menu Tree Guides you through the HHT display menu tree.

3

4

5 Ladder Program Basics

6 Creating a Program Steps you through creation of a program.

7

8

9

10

11 Processor Modes

12

13 The Force Function Explains and demonstrates the force function.

Features, Installation,

Powerup

Understanding File

Organization

Data File Organization and

Addressing

Creating and Editing Program

Files

Saving and Compiling a

Program

Configuring Online

Communication

Downloading/Uploading a

Program

Monitoring Controller

Operation

Introduces you to the Hand–Held Terminal (HHT).

Defines programs, program files, and data files,

explaining how programs are created, stored, and

modified.

Provides details on data files, covering file formats

and how to create and delete data.

Explains ladder programming. Includes examples

of simple rungs and 4–rung programs.

Shows you how to create and edit a program, and

use the search function.

Covers the procedures used to compile and save a

program.

Describes online communication between the HHT

and SLC 500.

Provides the procedures for downloading and

uploading.

Describes the different operating modes a

processor can be placed in while using the HHT.

Briefly covers how to monitor controller operation.

P–2

14

15 Instruction Set Overview

16 Bit Instructions

17

18

Using EEPROMs and

UVPROMs

Timer and Counter

Instructions

I/O Message and

Communication Instructions

Provides procedures for transferring a program

to/from an EEPROM. Briefly covers using

UVPROMs.

Gives you a brief overview of the instruction set with

cross references for detailed information.

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

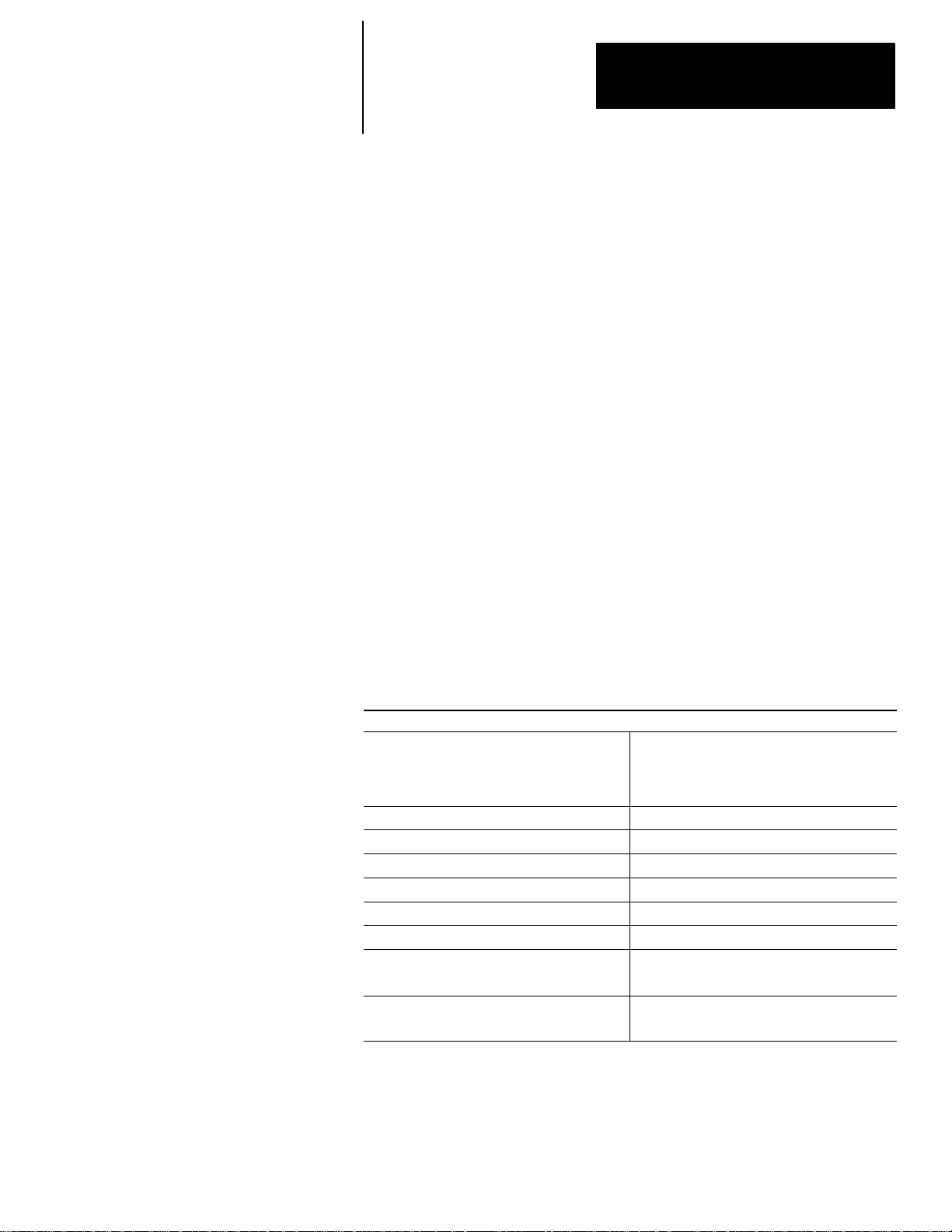

Page 21

Preface

Chapter

19 Comparison Instructions

20 Math Instructions

21

22

23

24 Sequencer Instructions

25 Control Instructions

26 PID Instruction

27 The Status File

28 Troubleshooting Faults

Move and Logical

Instructions

File Copy and File Fill

Instructions

Bit Shift, FIFO, and LIFO

Instructions

Title Contents

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

Provides detailed information about these

instructions.

Covers the status file functions of the fixed, SLC

5/01, and SLC 5/02 processors.

Explains the major error fault codes by indicating

the probable causes and recommending corrective

action.

Understanding the User Fault

29

30

31

Appendix A

Appendix B Number Systems, Hex Mask

Appendix C

Appendix D Estimating Scan Time

Routine–SLC 5/02 Processor

Only

Understanding Selectable

Timed Interrupts–SLC 5/02

Processor Only

Understanding I/O

Interrupts–SLC 5/02

Processor Only

HHT Messages and Error

Definitions

Memory Usage, Instruction

Execution Times

Covers recoverable and non–recoverable user

faults.

Explains the operation of selectable timed

interrupts.

Explains the operation of I/O interrupts.

Provides details about the messages that appear

on the prompt line of the HHT display.

Explains the different number systems needed to

use the HHT.

Covers memory usage and capacity.

Provides worksheets and examples for estimating

scan time.

P–3

Page 22

Preface

Related Documentation

The following documents contain additional information concerning

Allen–Bradley SLC and PLC products. To obtain a copy, contact your local

Allen–Bradley office or distributor.

For Read this Document

An overview of the SLC 500 family of products SLC 500 System Overview 1747–2.30

A description on how to install and use your Modular SLC 500

programmable controller

A description on how to install and use your Fixed SLC 500

programmable controller

A procedural manual for technical personnel who use APS to develop

control applications

A reference manual that contains status file data, instruction set, and

troubleshooting information about APS

An introduction to APS for first–time users, containing basic concepts but

focusing on simple tasks and exercises, and allowing the reader to begin

programming in the shortest time possible

A procedural and reference manual for technical personnel who use the

APS import/export utility to convert APS files to ASCII and conversely

ASCII to APS files

An introduction to HHT for first–time users, containing basic concepts but

focusing on simple tasks and exercises, and allowing the reader to begin

programming in the shortest time possible

A complete listing of current Automation Group documentation, including

ordering instructions. Also indicates whether the documents are

available on CD–ROM or in multi–languages.

Installation & Operation Manual for Modular Hardware

Style Programmable Controllers

Installation & Operation Manual for Fixed Hardware Style

Programmable Controllers

Allen–Bradley Advanced Programming Software (APS)

User Manual

Allen–Bradley Advanced Programming Software (APS)

Reference Manual

Getting Started Guide for APS 1747–NM001

APS Import/Export User Manual 1747–NM006

Getting Started Guide for HHT 1747–NM009

Automation Group Publication Index SD499

Document

Number

1747–NI002

1747–NI001

1747–NM002

1747–NR001

A glossary of industrial automation terms and abbreviations Allen–Bradley Industrial Automation Glossary ICCG–7.1

Common Techniques Used in this Manual

The following conventions are used throughout this manual:

• Bulleted lists such as this one provide information, not procedural steps.

• Numbered lists provide sequential steps or hierarchical information.

• Italic type is used for emphasis.

• Text in this font indicates words or phrases you should type.

• Key names match the names shown and appear in bold, capital letters

within brackets (for example,

P–4

[ENTER]).

Page 23

Preface

Allen–Bradley Support

Allen–Bradley offers support services worldwide, with over 75 Sales/Support

Offices, 512 authorized Distributors and 260 authorized Systems Integrators

located throughout the United States alone, plus Allen–Bradley

representatives in every major country in the world.

Local Product Support

Contact your local Allen–Bradley representative for:

• sales and order support

• product technical training

• warranty support

• support service agreements

Technical Product Assistance

If you need to contact Allen–Bradley for technical assistance, please review

the information in the Troubleshooting Faults, chapter 28, first. Then call

your local Allen–Bradley representative.

Your Questions or Comments on this Manual

If you have any suggestions for how this manual could be made more useful

to you, please send us your ideas on the enclosed reply card.

If you find a problem with this manual, please notify us of it on the enclosed

Publication Problem Report.

P–5

Page 24

Page 25

Chapter

1

Features, Installation, Powerup

This chapter introduces you to the Hand–Held Terminal (HHT) hardware. It

covers:

• HHT features

• installing the memory pak, battery, and communication cable

• powerup

• display format

• the keyboard

HHT Features

The Hand–Held Terminal is used to:

• configure the SLC 500 fixed, SLC 5/01, and SLC 5/02 controllers

• enter/modify a user program

• download/upload programs

• monitor, test, and troubleshoot controller operation

You can use the HHT as a standalone device (for remote programming

development with 1747–NP1 or NP2 power supply), point–to–point

communication (one HHT to one controller), or on a DH–485 network

(communicate with up to 31 nodes over a maximum of 4,000 feet or 1219

meters). When equipped with a battery (1747–BA), the HHT retains a user

program in memory for storage and later use.

Specifications:

Environmental conditions

Operating temperature

Storage temperature

Humidity rating 5 to 95% (non–condensing)

Display 8 line x 40 character super–twist nematic LCD

Keyboard 30 keys

Operating Power 0.105 Amps (max.) at 24 VDC

Communications DH–485

Certification UL listed, CSA approved

Memory Retention with Battery 2 years

Compatibility

Dimensions

0 to +40° C (+32° to +104° F)

–20° to +65° C (–4° to +149° F)

Fixed, SLC 5/01, SLC 5/02

Not SLC 5/03

201.0 mm H x 193.0 mm W x 50.8 D

(7.9 in H x 7.6 in W x 2.0 in D)

1–1

Page 26

Chapter 1

Features, Installation, Powerup

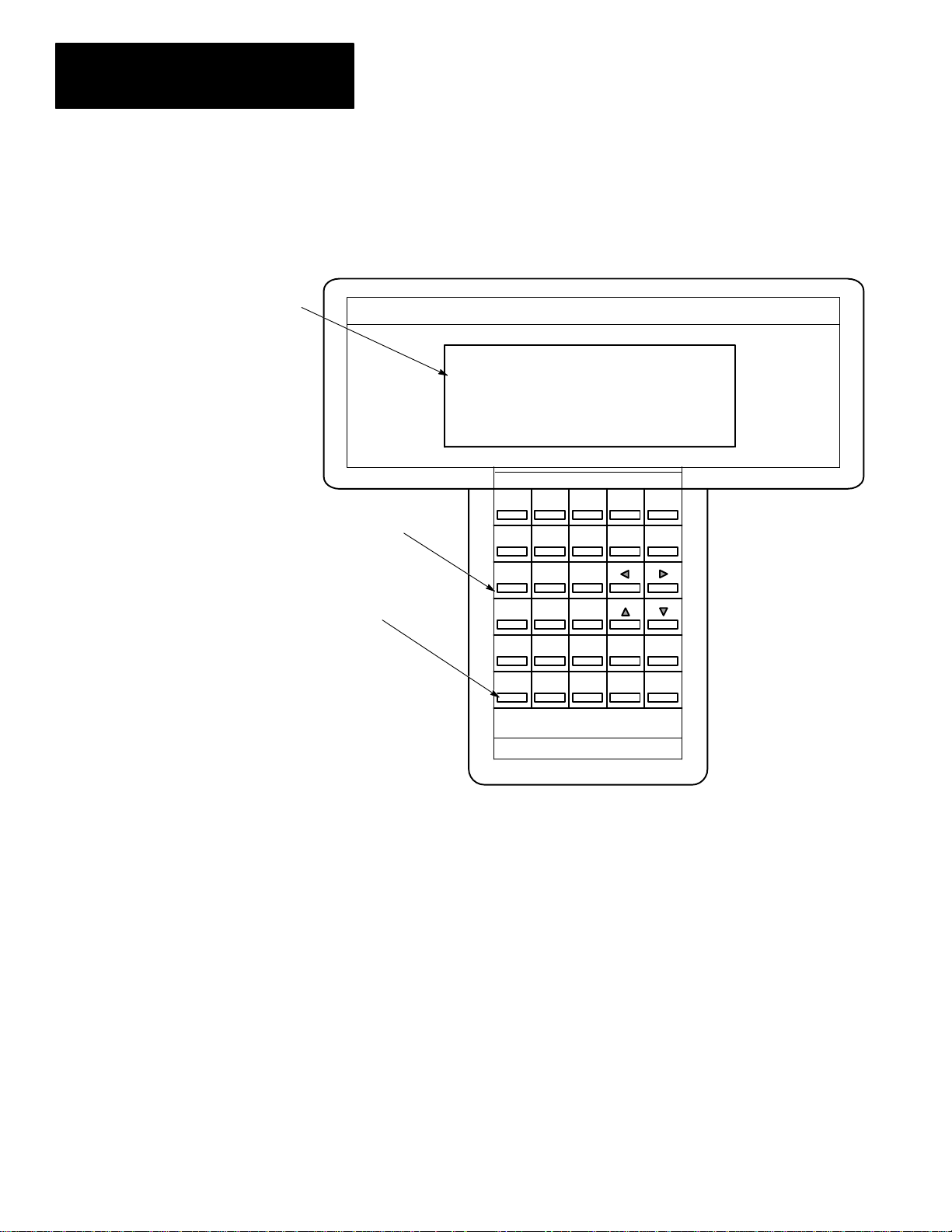

Display Area

The HHT is menu–driven. The display area accommodates 8 lines by 40

characters. You can display up to five rungs of a user program. When

monitoring a program ONLINE, in the Run mode, instructions in a ladder

diagram are intensified to indicate “true” status. A zoom feature is included

to give immediate access to instruction parameters.

SLC 500 PROGRAMMING SOFTWARE Rel. 2.03

Calculator–style,

Color–coded Keyboard

Keys operate with motion and

tactile response.

Allen–Bradley Company Copyright 1990

1747 – PTA1E

All Rights Reserved

PRESS A FUNCTION KEY OFL

SELFTEST TERM PROGMAINT UTILITY

F1 F2 F3 F4 F5

F1 F2

NO

PRE/LEN

ACC/POS

A

7

D

4

T

1

#

0

F3 F4 F5

S

I

U

C

B

9

8

F

E

6

5

M

R

3

2

.

–

:/

SPACE

SHIFT

ESC

ZOOMRUNG

ENTER

1–2

Page 27

Chapter 1

Features, Installation, Powerup

Installing the Memory Pak, Battery, and Communication Cable

The HHT (with communication cable), memory pak, and battery are supplied

separately. Install each as follows:

1. Install the memory pak first. The English version is catalog number

1747–PTA1E.

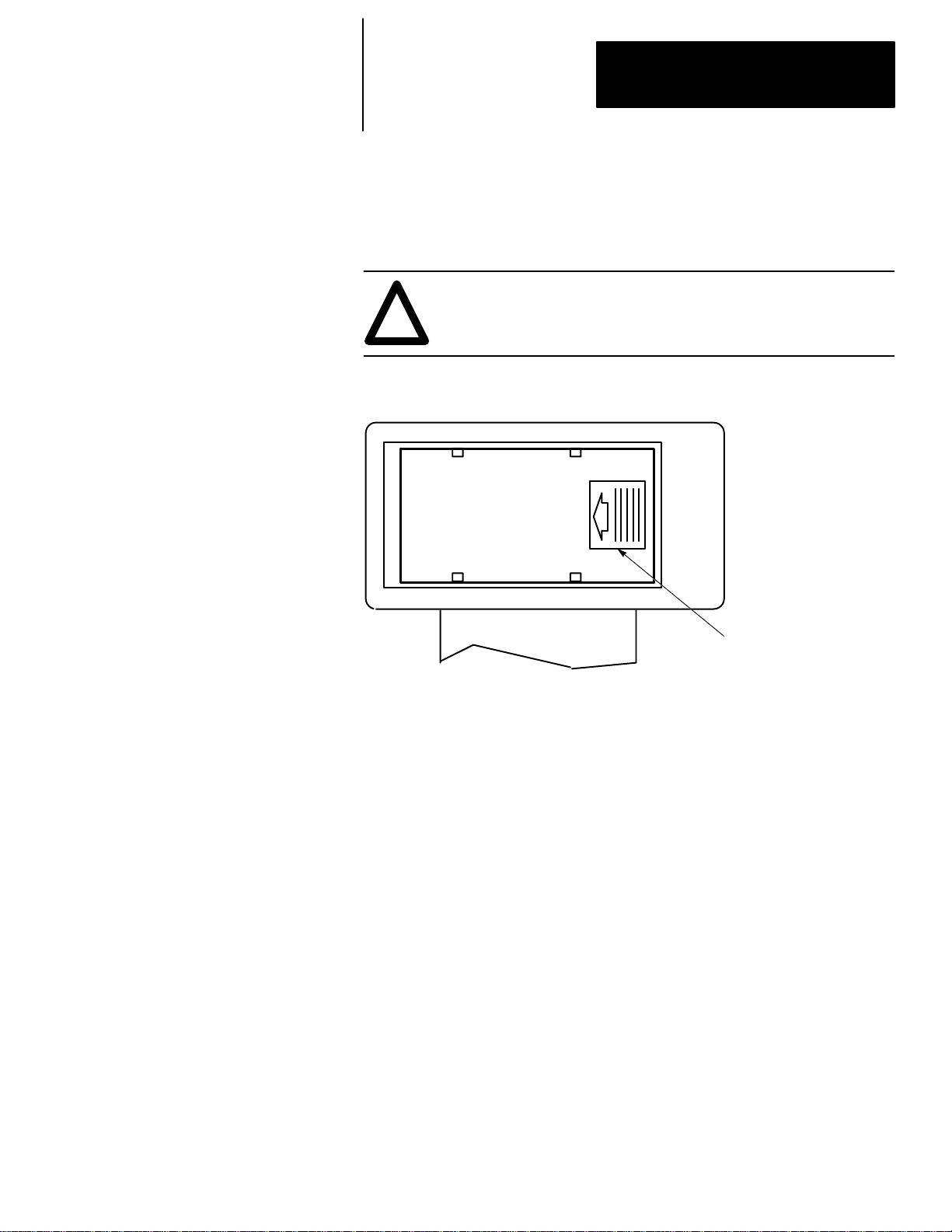

ATTENTION: The memory pak contains CMOS devices. Wear

a grounding strap and use proper grounding procedures to guard

!

against damage to the memory pak from electrostatic discharge.

a. To install the memory pak, remove the cover from the back of the

HHT.

Backside of HHT

Slide cover to the left. Lift off cover.

1–3

Page 28

Chapter 1

Features, Installation, Powerup

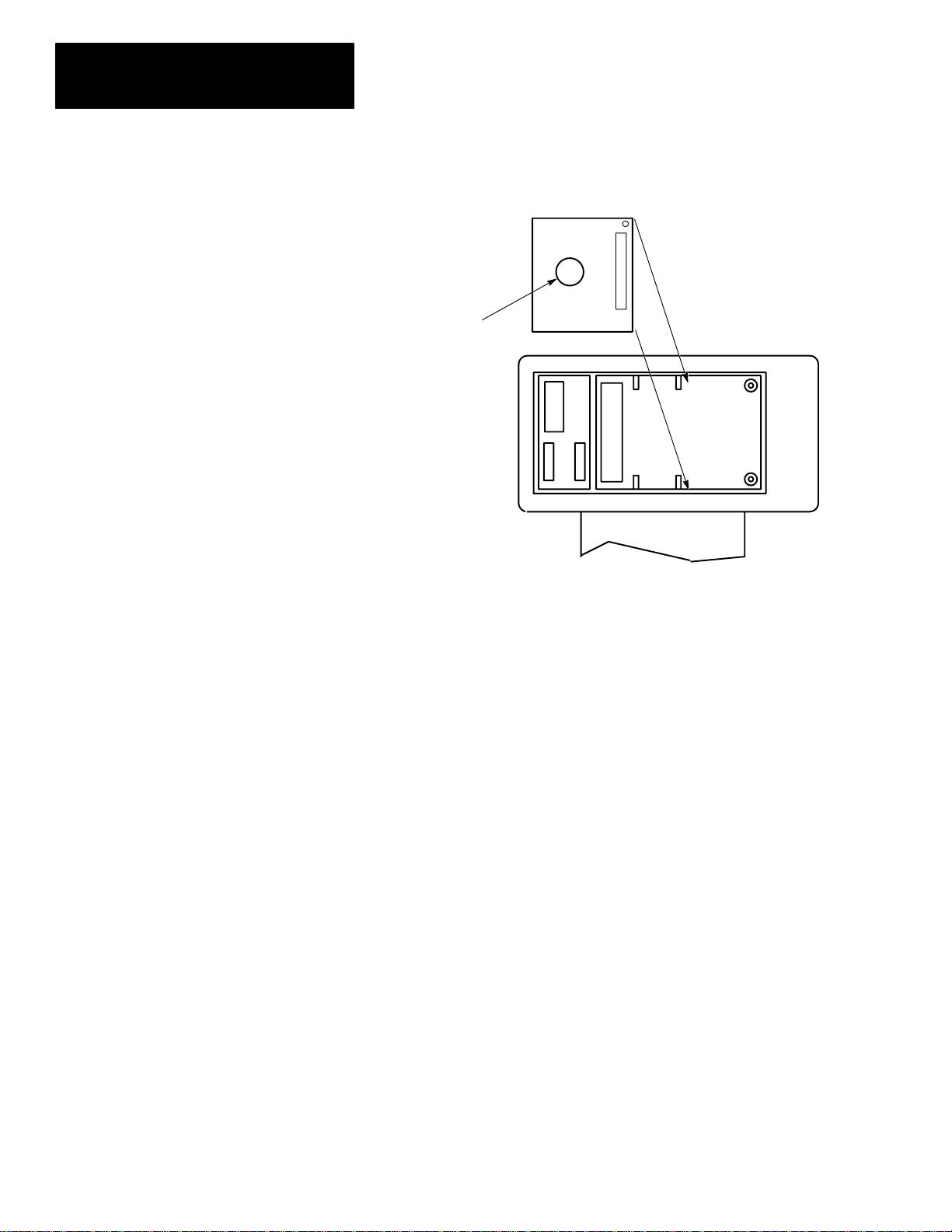

b. Insert the memory pak in its compartment as indicated in the following

figure:

After the memory pak

is in the compartment,

press down on handle

to secure connector in

socket.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Backside of HHT

1–4

Page 29

Chapter 1

Features, Installation, Powerup

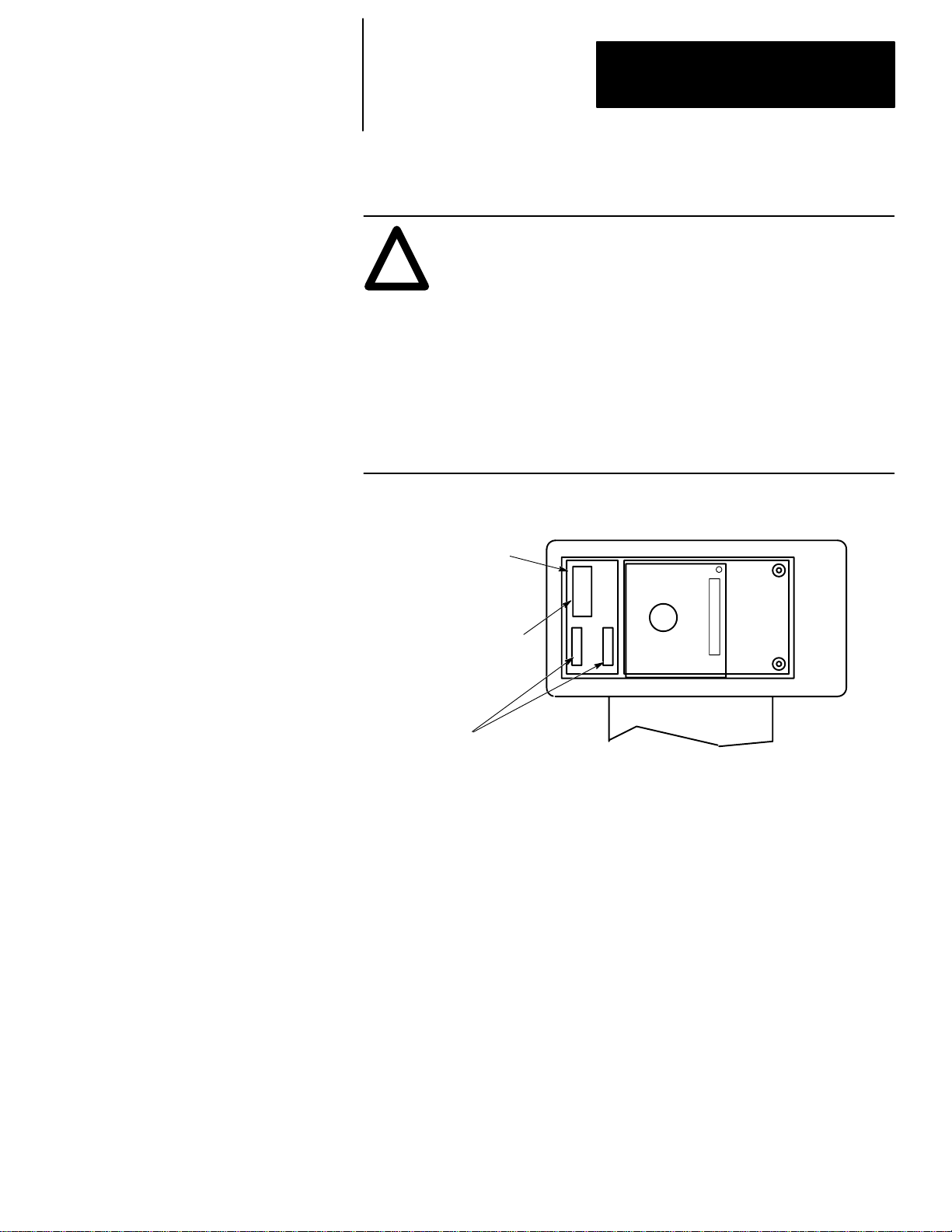

2. Install the battery, catalog number 1747–BA. The battery compartment is

next to the memory pak compartment.

ATTENTION: The letter B appears flashing on the prompt line

of the HHT display if the battery is not installed correctly or the

!

battery power is low; in addition, each time you power up, the

self–diagnostic is interrupted, and the prompt BATTERY TEST

FAILED appears.

To prevent this from happening, leave the “battery low defeat

jumper” inserted in the battery socket. The HHT is functional,

but your user program is cleared from memory when you

de–energize the HHT. If you do not download the user program

to the processor before you de–energize the HHT, your program

will be lost.

a. Remove the jumper from the battery socket, then connect the battery

as shown in the figure below:

Battery Compartment

Plug battery connector

into socket (red wire up).

Secure battery

between clips.

b. Replace the cover.

.

.

Backside of HHT

1–5

Page 30

Chapter 1

Features, Installation, Powerup

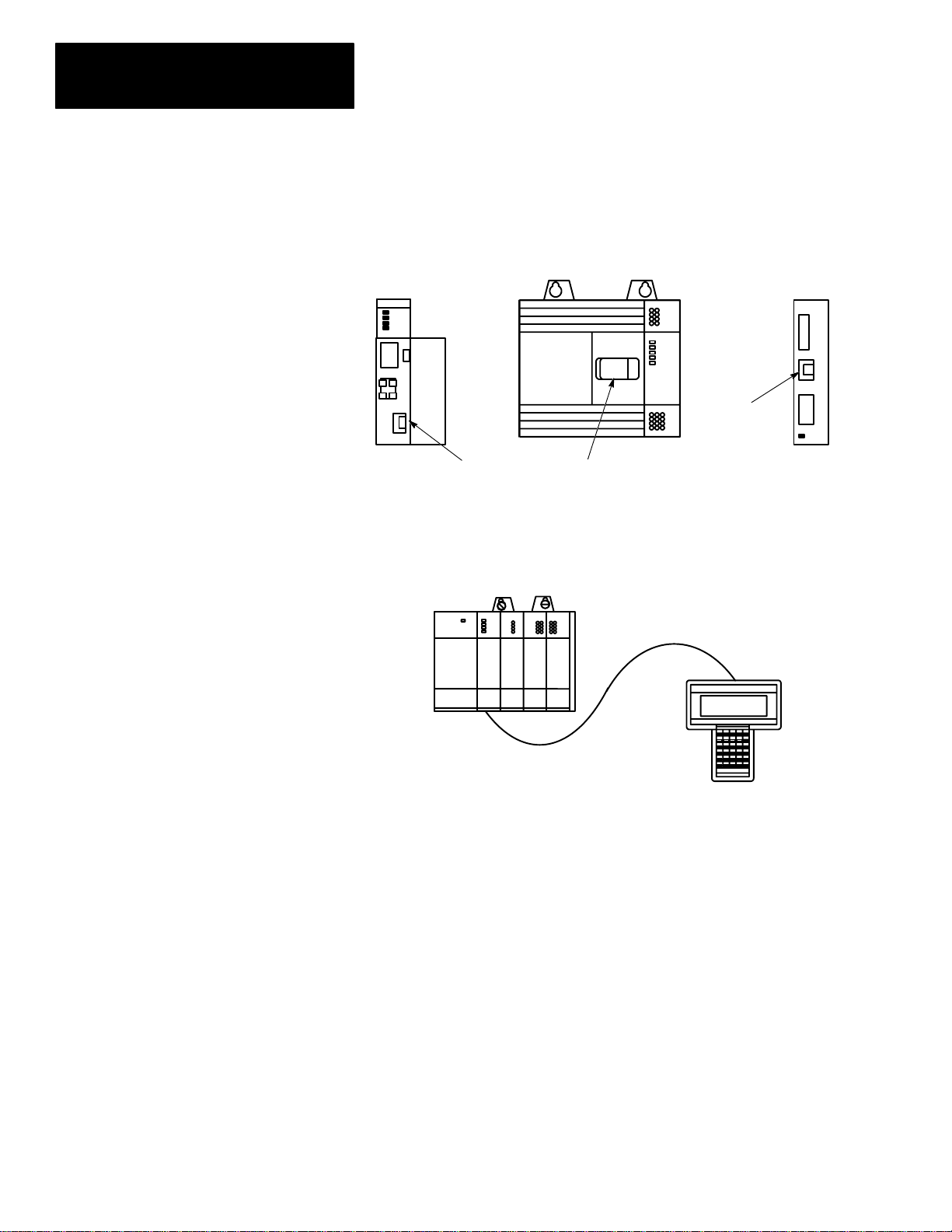

3. Locate the communication port on the SLC 500 controller, or peripheral

port on the 1747–AIC Link Coupler. The figure below shows where it is

located on the different devices:

Processor Module

(Modular Controller)

(Cover Open)

SLC 500 Fixed Controller

(Peripheral Port)

(Communication Port)

Isolated Link

Coupler

The connectors are keyed. Connect one end of the 1747–C10

communication cable to the top of the HHT. The other connector plugs

into the communication port on the SLC 500 controllers or the peripheral

port on the 1747–AIC.

1747–C10 Cable

1–6

SLC Controller

(Modular)

HHT

If you are using a 1747–NP1 wall mount power supply or a 1747–NP2

desktop power supply, plug the communication cable connector into the

socket provided.

Page 31

Chapter 1

Features, Installation, Powerup

HHT Powerup

After you install the memory pak and battery, and plug in the cable, you can

test the operation of the HHT by applying power to the SLC 500 controller

or plugging in the external power supply such as the 1747–NP1 or –NP2.

When the HHT is energized, it performs a series of diagnostic tests. When

the selftest is successfully completed, the following display appears:

SLC 500 PROGRAMMING SOFTWARE Rel. 2.03

Allen–Bradley Company Copyright 1990

PRESS A FUNCTION KEY

SELFTEST TERM PROGMAINT

F1 F2 F3 F4 F5

1747 – PTA1E

All Rights Reserved

OFL

UTILITY

If any of the tests fail, the failure is indicated by the appropriate message on

the display. For a detailed list of HHT messages and error definitions, refer

to appendix A in this manual.

After powerup, you may perform any of five diagnostic tests using the

selftest function. Press

[F1], SELFTEST. The following display appears:

SLC 500 SELFTEST UTILITY

DISPLAY

F1 F2 F3 F4 F5

KEYPAD RAM ROM WTCHDOG

OFL

From this menu, you may choose the test you wish to perform. Press [ESC]

to return to the previous screen.

1–7

Page 32

Chapter 1

Features, Installation, Powerup

HHT Display Format

Display Area

Prompt/Data Entry/Error Area

Menu tree functions

are directly accessible.

Select menu function keys

with [F1] to [F5] keys.

The HHT display format consists of the following:

• display area

• prompt/data entry/error message area

• menu tree functions

The figure below indicates what appears in these areas. To access this

particular screen, press

File Name: 101 Prog Name: 1492

File Name Type Size(Instr)

0 System *

1 Reserved *

2 101 Ladder *

CHG_NAM CRT_FIL EDT_FIL DEL_FIL MEM_MAP >

F1 F2 F3 F4 F5

[F3], PROGMAINT.

Indicates that the HHT is offline.

When online, the node address and

processor mode are shown.

OFL

When the > symbol is present, pressing [ENTER]

toggles additional menu functions.

1–8

Page 33

Chapter 1

Features, Installation, Powerup

The Keyboard

F1 F2

NO

PRE/LEN

ACC/POS

A

7

D

4

T

1

#

0

F3 F4 F5

S

I

U

C

B

9

8

F

E

6

5

M

R

3

2

.

–

:/

SPACE

SHIFT

ESC

ZOOMRUNG

ENTER