PRELIMINARY DATA SHEET

DATA SHEET

BIPOLAR ANALOG + DIGITAL INTEGRATED CIRCUIT

µµµµ

PB1005K

REFERENCE FREQUENCY 16.368 MHz, 2ND IF FREQUENCY 4.092 MHz

RF/IF FREQUENCY DOWN-CONVERTER +

PLL FREQUENCY SYNTHESIZER IC FOR GPS RECEIVER

DESCRIPTION

The µPB1005K is a silicon monolithic integrated circuit for GPS receiver. This IC is designed as double

conversion RF block integrated RF/IF down-converter + PLL frequency synthesizer on 1 chip.

The µPB1005K features 36-pin plastic QFN, fixed prescaler and supply voltage. The 36-pin plastic QFN package

is suitable for high density surface mounting. The fixed division internal prescaler is needless to input serial counter

data. Supply voltage is 3 V. Thus, the µPB1005K can make RF block fewer components and lower power

consumption.

This IC is manufactured using NEC’s 20 GHz fT NESATTMIII silicon bipolar process. This process uses direct

silicon nitride passivation film and gold electrodes. These materials can protect the chip surface from pollution and

prevent corrosion/migration. Thus, this IC realizes excellent performance, uniformity and reliability.

FEATURES

• Double conversion : f

• Integrated RF block : RF/IF frequency down-converter + PLL frequency synthesizer

• High-density surface mountable : 36-pin plastic QFN (6.0 × 6.0 × 0.95 mm)

• Needless to input counter data : fixed division internal prescaler

• VCO side division :÷ 200 (÷ 25, ÷ 8 serial prescaler)

• Reference division :÷ 2

• Supply voltage : VCC = 2.7 to 3.3 V

• Low current consumption : ICC = 45.0 mA TYP.@VCC = 3.0 V

• Gain adjustable externally : Gain control voltage pin (control voltage up vs. gain down)

APPLICATION

• Consumer use GPS receiver of reference frequency 16.368 MHz, 2nd IF frequency 4.092 MHz

ORDERING INFORMATION

Part Number Package Supplying Form

µ

PB1005K-E1 36-pin plastic QFN Embossed tape 12 mm wide.

REFin

= 16.368 MHz, f

2ndIFout

= 4.092 MHz

Pin 1 is in pull-out direct i on.

Qty 2.5 kp/reel.

Remark

Document No. P14016EJ1V0DS00 (1st edition)

Date Published November 1999 N CP(K)

Printed in Japan

To order evaluation samples, please contact your local NEC sales office. (Part number for sample

order:

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

PB1005K)

µ

Caution Electro-static sensitive device

©

1999

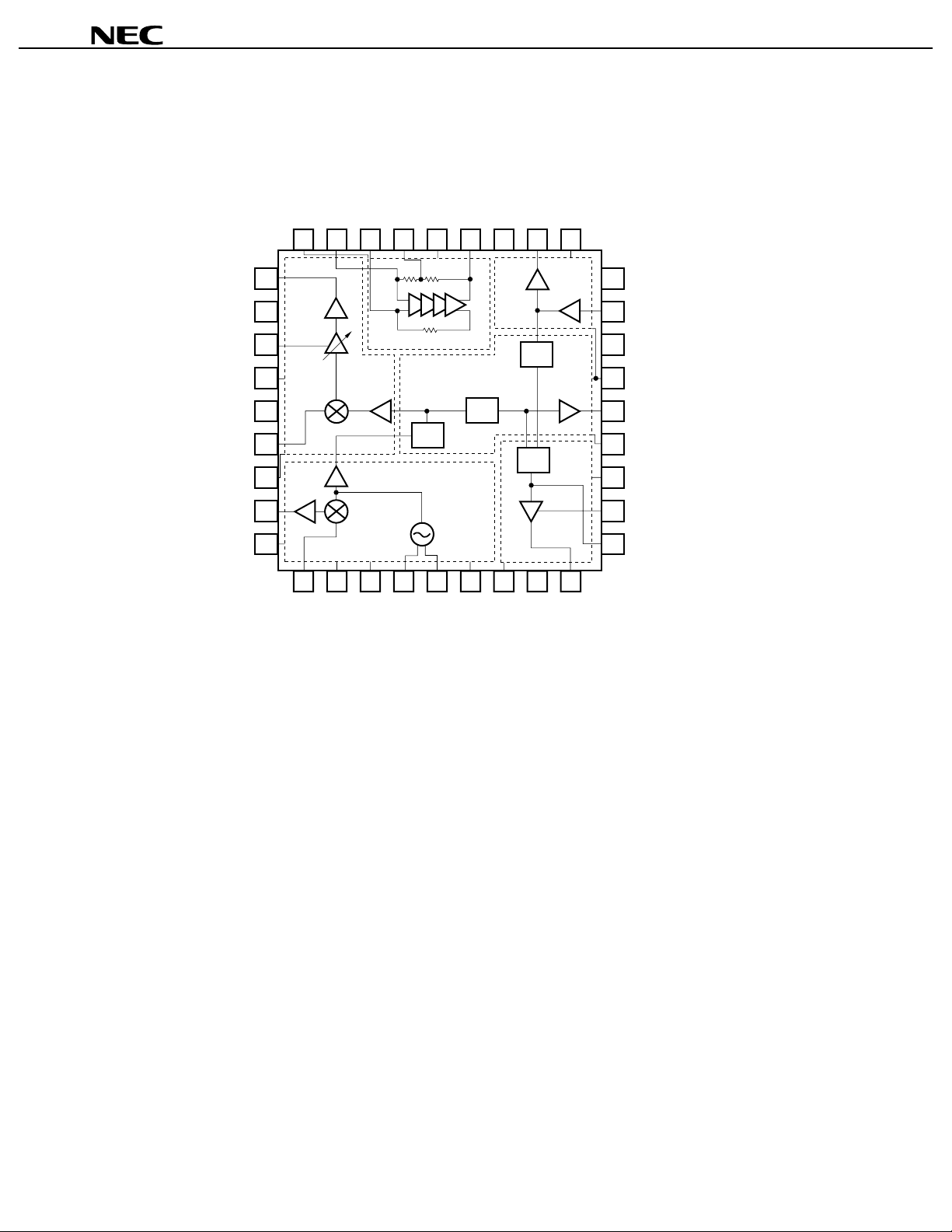

PIN CONNECTION AND INTERNAL BLOCK DIAGRAM

µµµµ

PB1005K

2ndIFin2

2ndIFin1

GND

(2ndIF-AMP)

27

26 25 24 23 22 21

IF-MIXout

(IF-MIX)

(IF-MIX)

IF-MIXin

(IF-MIX)

RF-MIXout

(RF-MIX)

28

29

N.C. REFin

GC

V

30

CC

V

31

N.C.

32

33

GND

34

35

V

CC

36

123456789

CC

V

GND

RF-MIXin

(RF-MIXin)

(1stLO-OSC)

CC

2ndIFbypass

V

(2ndIF-AMP)

÷

25

1stLO-OSC1

1stLO-OSC2

2ndIFout

N.C.

÷

8

CC

V

GND

(1stLO-OSC)

(phase detector)

÷

PD

20

2

CC

V

REFout

19

N.C.

PD-Vout3

(reference block)

18

N.C.

17

16

N.C.

GND

15

(divider block)

14

LOout

CC

V

13

(divider block)

GND

12

(Phase detector)

11

PD-Vout1

10

PD-Vout2

2

Preliminary Data Sheet P14016EJ1V0DS00

µµµµ

PB1005K

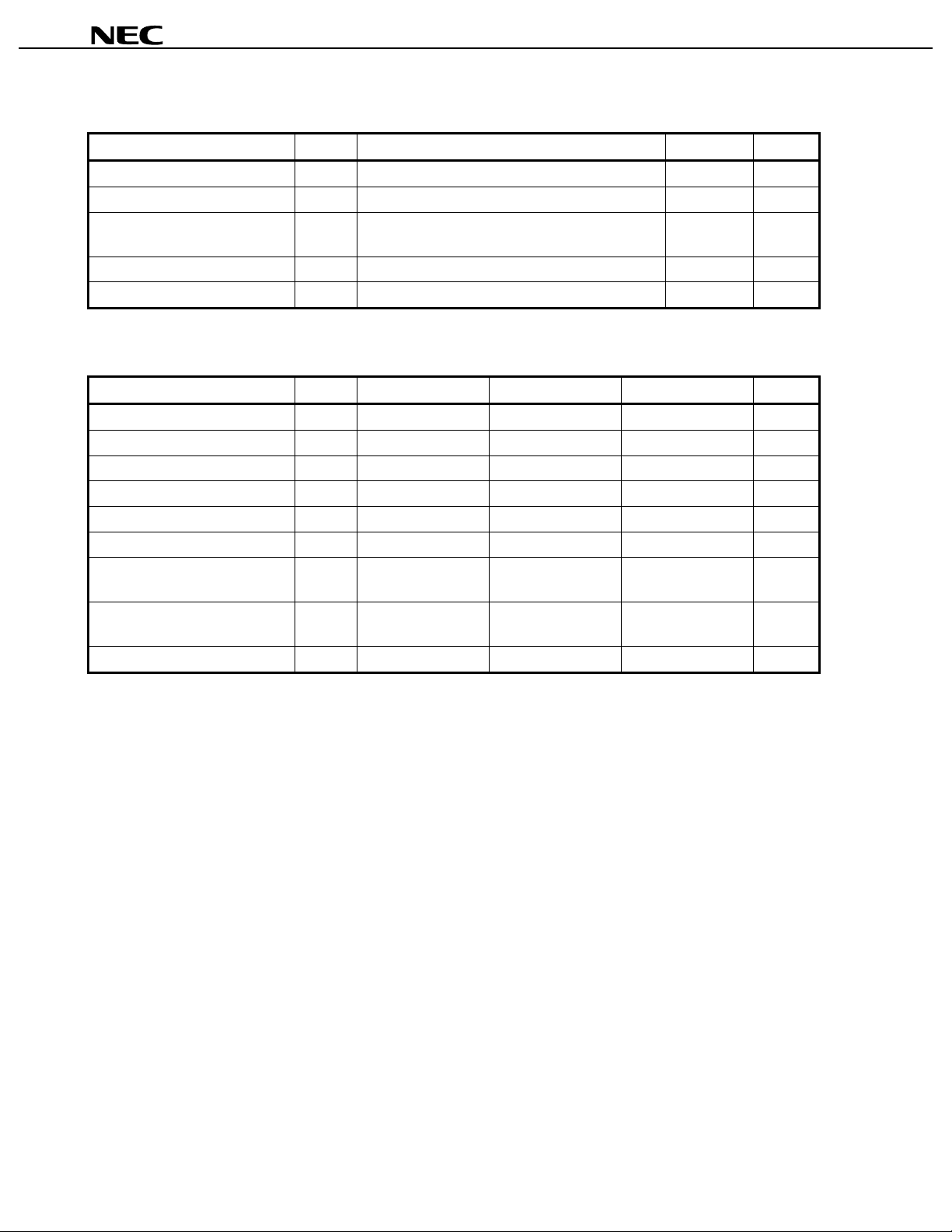

PRODUCT LINE-UP (TA = +25

Type Part Number

General

Purpose

Wideband

Separate

PC2756T 6-pin minimold

µ

PC2756TB

µ

PC2753GR IF down-convert er wi th gain

µ

IC

Clock

PB1003GS RF/IF down-converter

µ

Frequency

Specific

1 chip IC

PB1004GS

µ

PB1005GS

µ

PB1005K

µ

Notice

Typical performance. Please refer to ELECTRICAL CHARACTERISTICS in detail.

(Frequency unit: MHz)

RF down-converter with osc. Tr

control amplifier

+ PLL synthesizer

REF = 18.414

1stIF = 28.644/2ndIF = 1.023

RF/IF down-converter

+ PLL synthesizer

REF = 16.368

1stIF = 61.380/2ndIF = 4.092

C, VCC = 3.0 V)

°°°°

Functions

To know the associated products, please refer to their latest data sheets.

SYSTEM APPLICATION EXAMPLE

CC

V

(V)

2.7 to 3.3

2.7 to 3.3

2.7 to 3.3

2.7 to 3.3

2.7 to 3.3

CC

I

(mA)

CG

(dB)

Package Status

6.0 14

6-pin super minimold

6.5 60 to 79 20-pin plastic SSOP

(225 mil)

37.5 72 to 92

30-pin plastic SSOP

(300 mil)

37.5 72 to 92

45.0 72 to 92

36-pin plastic QFN

Available

Discontinued

Available

GPS receiver RF block diagram

60f0

BPF

IF-MIX

out

RF-MIX

1575.42 MHz

from

Antenna

LNA 1540f

µ

PC2749TBe.g.

BPF

0

1540f

0

OSC

RF-MIX

1600f

0

1stLO-OSC21stLO-OSC1

IF-MIX

1/25 1/8 P D

Caution This diagram schematically shows only the

This diagram does not present the actual application circuits.

0

40f

LOOP

AMP

8f0

LPF

V

CC

2ndlFbypass

2ndlF-Amp

1/2

REF

16f0

TCXO

16.368 MHz

IF-MIXout 2ndlFin1

in

V

GC

64f0

8f0

LOOUT

PB1005K’s internal functions on the system.

µµµµ

• f0 = 1.023 MHz in the diagram.

• PB1005K is in .

µ

2ndlFin2

4f0

16f

0

4.092 MHz

Buff

16.368 MHz

Buff

to Demodulator

to Demodulator

Preliminary Data Sheet P14016EJ1V0DS00

3

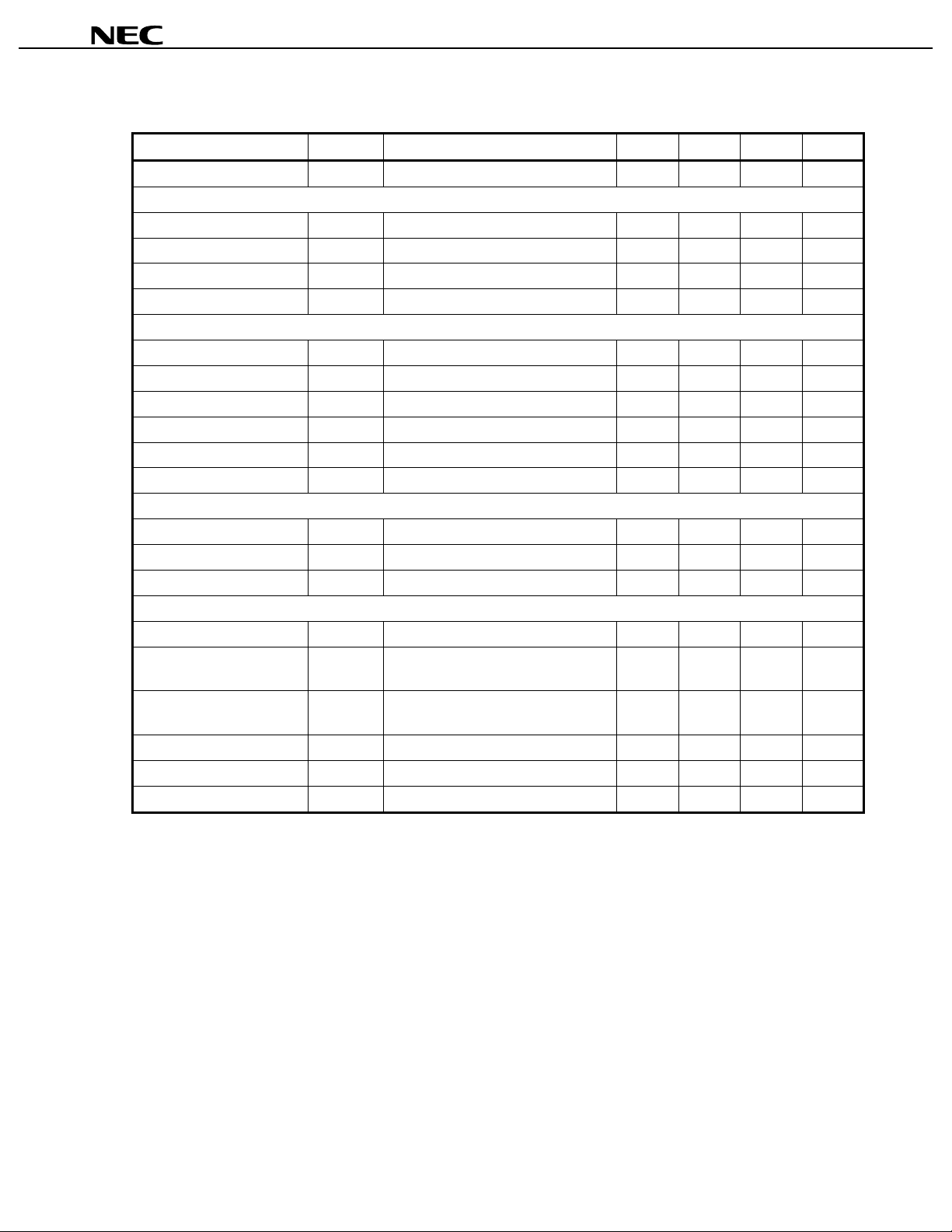

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Conditions Rating Unit

µµµµ

PB1005K

Supply Voltage V

Total Circuit Current I

Power Dissipation P

CC

TA = +25 °C3.6V

CC

TA = +25 °C 120 mA

D

Mounted on double-sided copper clad

50 × 50 × 1.6 mm epoxy glass P WB (T

Operating Ambient Temperature T

Storage Temperature T

A

stg

RECOMMENDED OPERATING RANGE

Parameter Symbol MIN. TYP. MAX. Unit

RFin

1stLOin

1stIFin

2ndLOin

2ndIFin

2ndIFout

f

REFin

REFout

f

LOout

CC

A

Supply Voltage V

Operating Ambient Temperature T

RF Input Frequency f

1st LO Oscillating Frequency f

1st IF Input Frequency f

2nd LO Input Frequency f

2nd IF Input/output Frequency f

Reference Input/output Frequency f

LO Output Frequency f

430 mW

A

= +85 °C)

40 to +85

−

55 to +150

−

C

°

C

°

2.7 3.0 3.3 V

40 +25 +85

−

1575.42

C

°

MHz

1616.80 1636.80 1656.80 MHz

61.38

65.472

4.092

16.368

8.184

MHz

MHz

MHz

MHz

MHz

4

Preliminary Data Sheet P14016EJ1V0DS00

µµµµ

PB1005K

ELECTRICAL CHARACTERISTICS (Unless otherwise specified TA = +25

C, VCC = 3.0 V)

°°°°

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Total Circuit Current ICCtotal ICC1 + ICC2 + ICC3 + ICC4 32.0 45.0 60.0 mA

RF Down-converter Block (f

RFin

= 1575.42 MHz, f

1stLOin

= 1636.80 MHz, P

LOin

= −10 dBm, ZS = ZL = 50 Ω)

Circuit Current 1 ICC1 No Signals 6.0 10.0 14.0 mA

RF Conversion Gain CG

RF-SSB Noise Figure NF

Maximum IF Output P

IF Down-converter Block (f

O(sat)RF

1stIFIn

= 61.38 MHz, f

RF

RF

RFin

P

= −40 dBm 12.5 15.5 18.5 dB

RFin

P

= −40 dBm 7.0 10.0 13.0 dB

RFin

P

= −10 dBm

2ndLOIn

= 65.472 MHz, ZS = 50 Ω, ZL = 2 kΩ)

5.5

−

2.5 +0.5 dBm

−

Circuit Current 2 ICC2 No Signals 3.4 5.3 7.2 mA

IF Conversion Voltage Gain CG

IF-SSB Noise Figure NF

Maximum 2ndIF Output P

O(sat)IF

Gain Control Voltage V

Gain Control Range D

2nd IF Amplifier (f

2ndIF

= 4.092 MHz, ZS = 50 Ω, ZL = 2 kΩ)

(GV)IF

IF

GC

GC

at Maximum Gain, P

at Maximum Gain, P

at Maximum Gain, P

Voltage at Maximum Gain CG

1stIFin

P

= −50 dBm 20

1stIFin

= −50 dBm 38 41 44 dB

1stIFin

= −50 dBm 8.5 11.5 14.5 dB

1stIFin

= −20 dBm

IF

9.5

−

6.5

−

3.5 dBm

−

1.0 V

Circuit Current 3 ICC3 No Signals 1.55 2.40 3.25 mA

Voltage Gain G

Output Power P

2ndIFout

V

2ndIFin

P

= −60 dBm 37 40 43 dB

2ndIFin

P

= −30 dBm

−

14.5

−

11.5

−

8.5 dBm

PLL Synthesizer Block

Circuit Current 4 ICC4 PLL All Block Operati ng 18.5 28.5 38.5 mA

Phase Comparing

PD

f

PLL Loop 8.0 8.184 8.4 MHz

Frequency

Reference Input Minimum

V

REFin

ZL = 10 kΩ//20 pF

Note

200

Level

Loop Filter Output Level (H) V

Loop Filter Output Level (L) V

Reference Output Swing V

LP(H)

LP(L)

REFout

ZL = 10 kΩ//2 pF

Note

2.8

1.0

0.4 V

mV

V

dB

P-P

V

P-P

Impedance of measurement equipment

Note

Preliminary Data Sheet P14016EJ1V0DS00

5

Loading...

Loading...