1

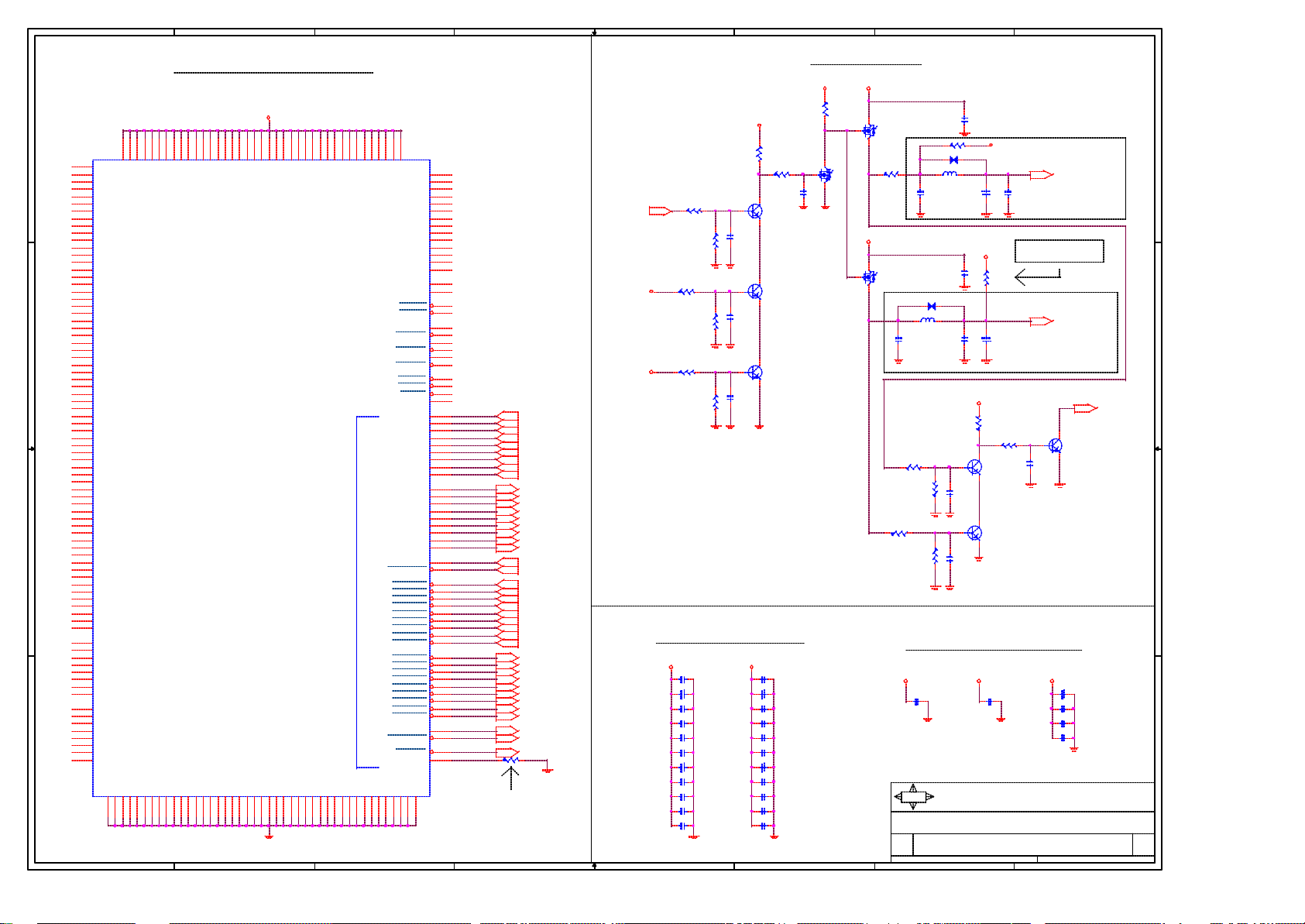

Cover Sheet 1

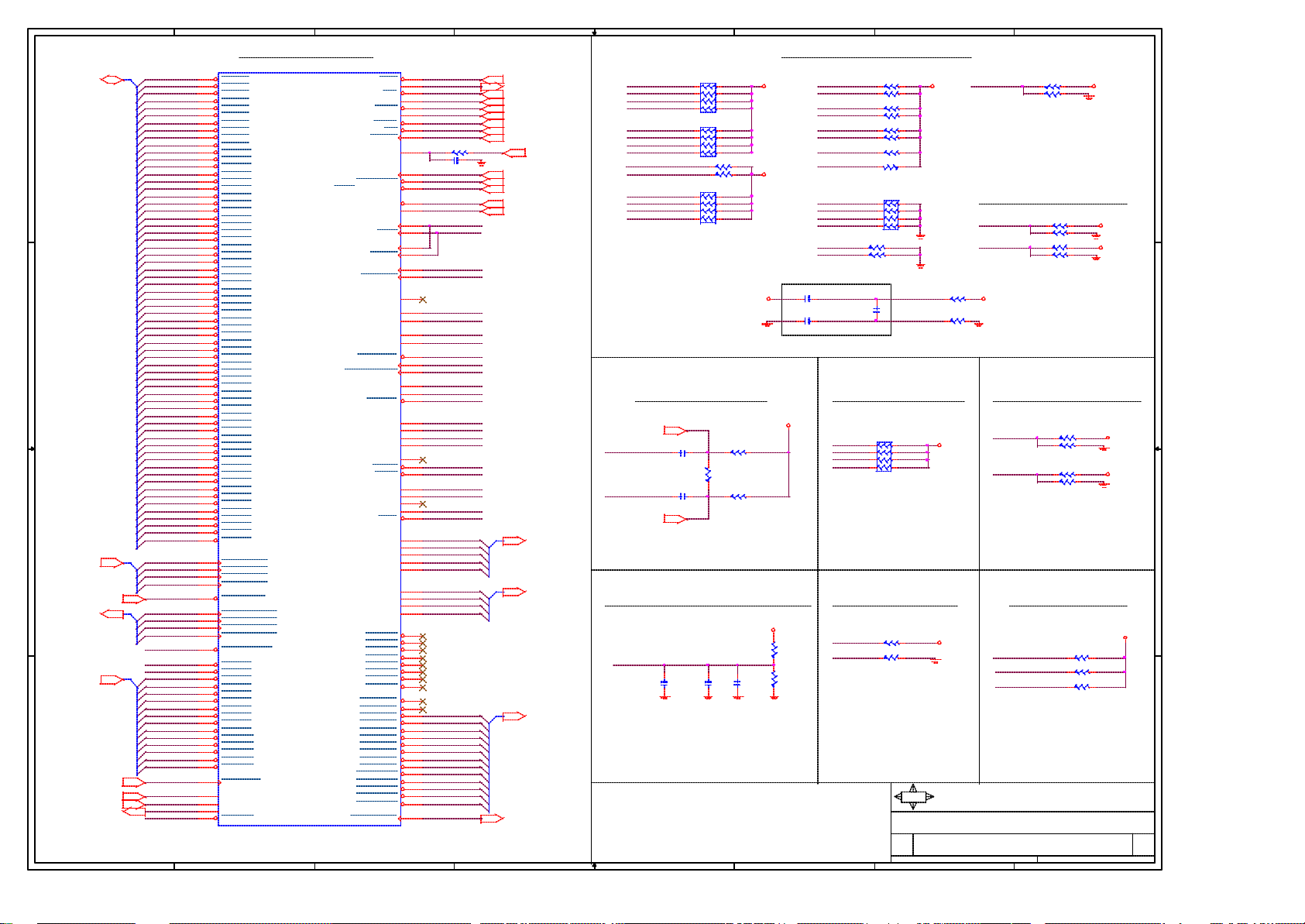

Block Diagram

2

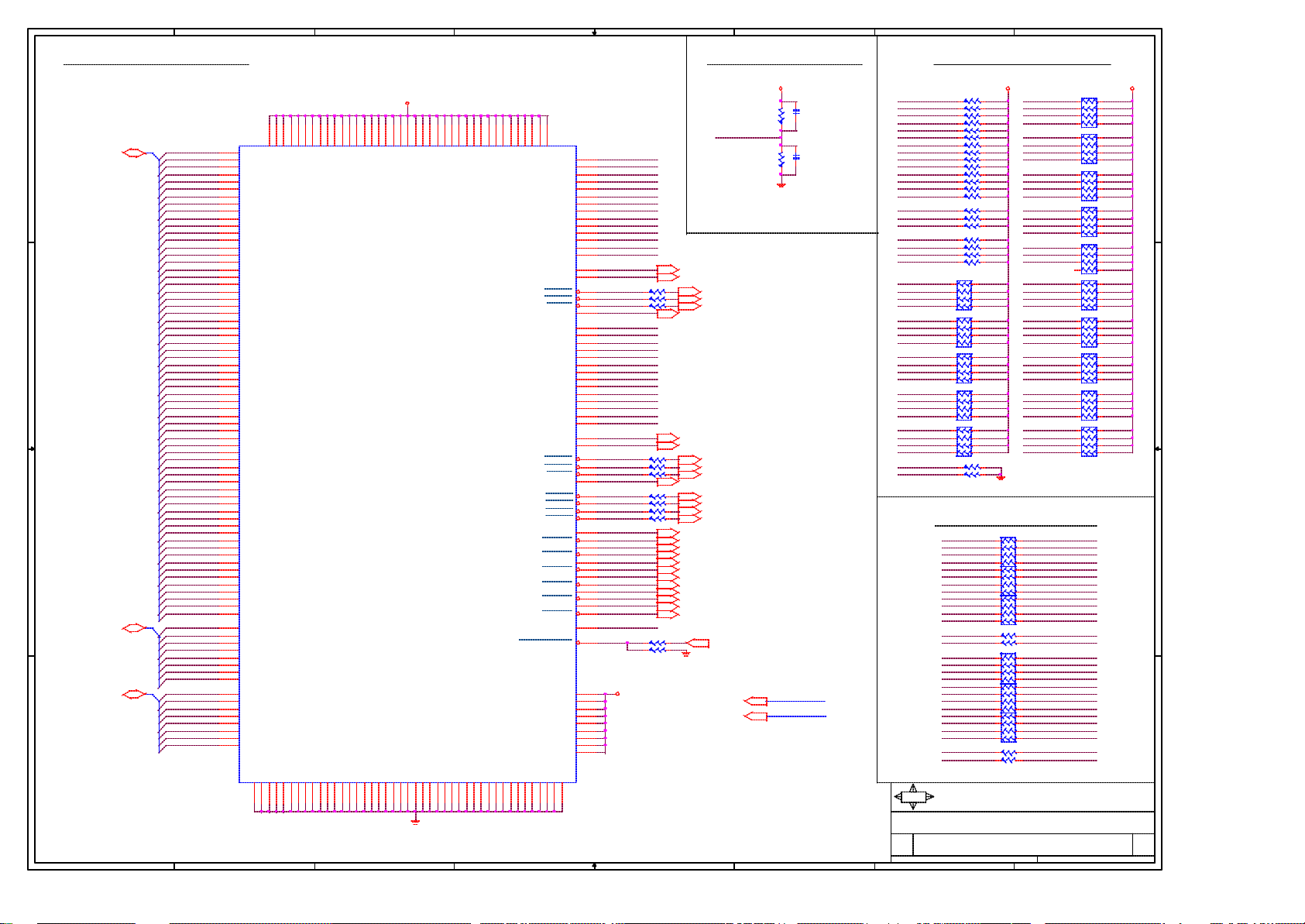

3AMD 462pins SocketA CPU - Signals

(MS-6595)

Nvidia (R) Crush17/18(nForce IGP 64) + MCP2/2H Chipset

Version: 0B

AMD Althon/Duron/Morgan/Palomino Socket 462 Processor

AMD 462pins SocketA CPU - Power 4

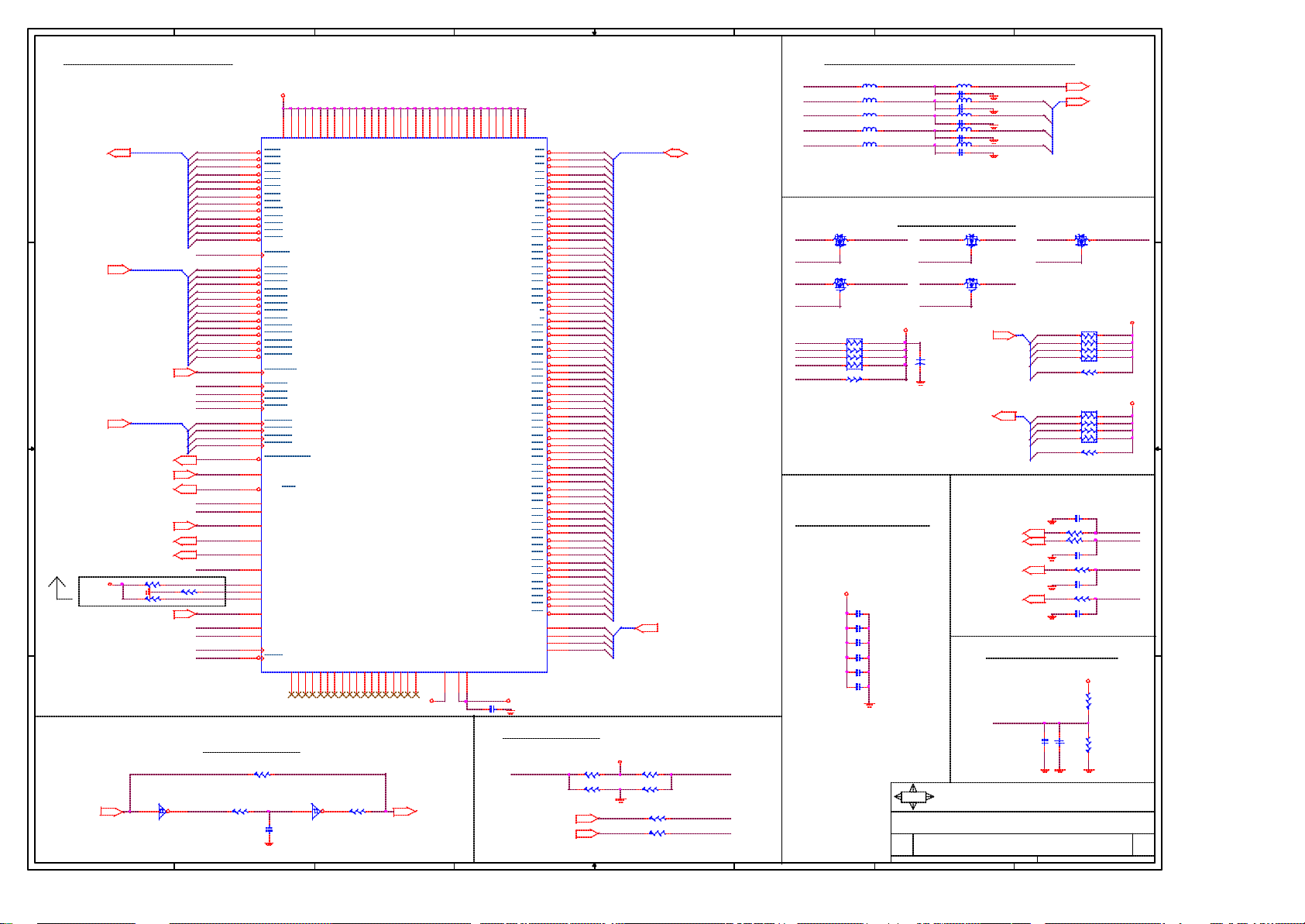

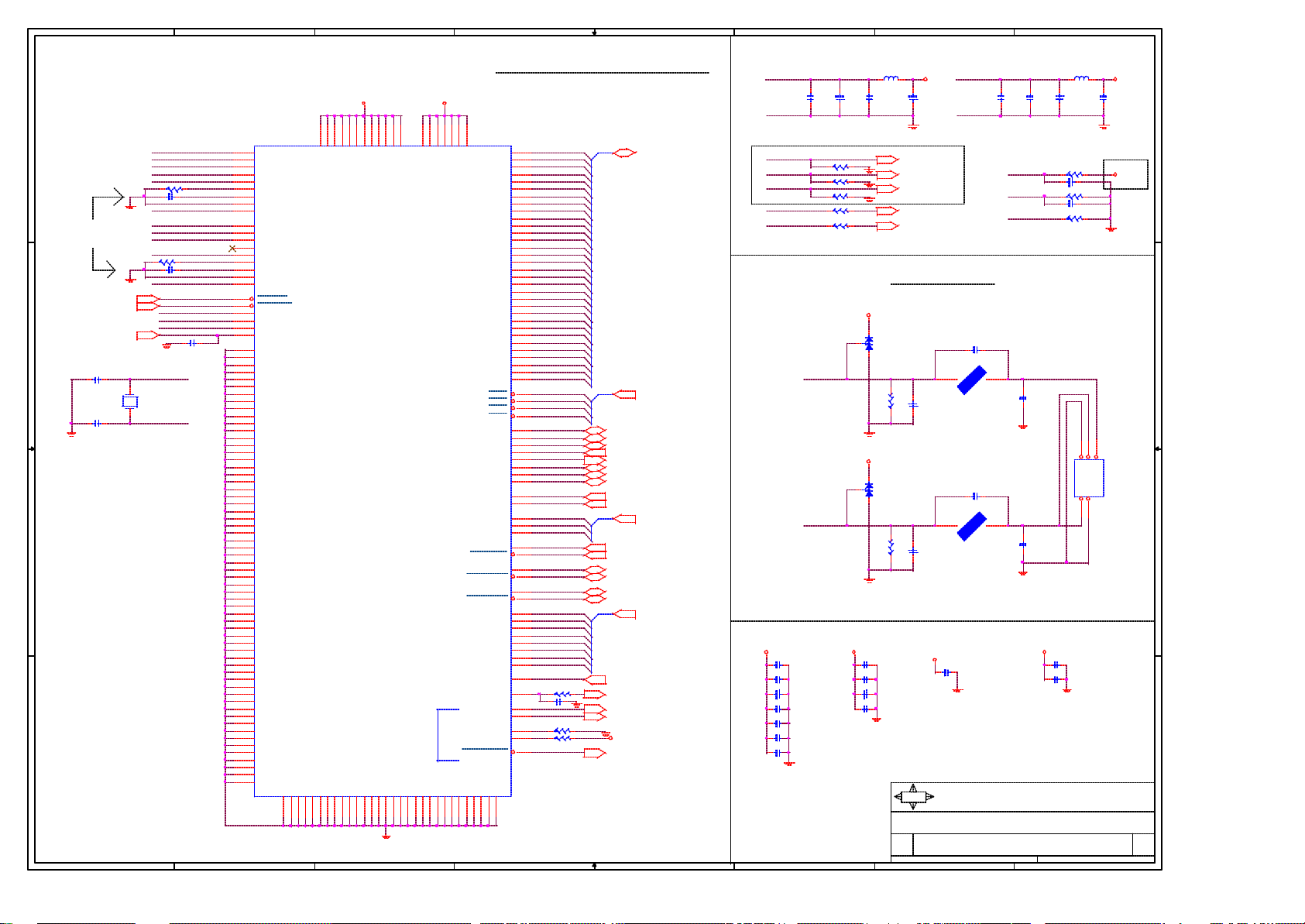

CRUSH17/18 - Host & VID Signals 5

CRUSH17/18 - Memory-A & LDT & PLL Signals 6

CRUSH17/18 - Memory-B Signals 7

CPU:

AMD Duron/Morgan 1.2G&1.3G

AMD Althon/Palomino 1500 - 1.333G/266MHz

AMD Althon/Palomino 1600 - 1.400G/266MHz

AMD Althon/Palomino 1700 - 1.467G/266MHz

CRUSH17/18 - AGP & VIDEO Signals

MCP2 - CPU & PCI & LDT & IDE Signals

MCP2 - MAC & USB & LPC & AC'97 Signals

LPC I/O - W83627HF

AC97 Audio - ALC202A

A A

MII LAN & LPC Flash EEPROM

8

9

10

11

12

13

AMD Althon/Palomino 1800 - 1.533G/266MHz

AMD Althon/Palomino 1900 - 1.600G/266MHz

AMD Althon/Palomino 2000 - TBD

System Chipset:

Nvidia nForce IGP 64 (North Bridge)

MCP2/2H Wep (South Bridge)

On Board Chipset:

DDR System Memory

AGP 3.0 Slot, LDT Regulator & COM2 15

PCI Slots

ATA33/66/100 IDE & Video Connectors

14

16

17

BIOS -- LPC EEPROM

AC'97 Codec -- ALC202A

LPC Super I/O -- W83627HF-AW

LAN -- ICS1893 PHY

I1394 -- FW803 PHY

FAN & USB Connectors

18

Expansion Slots:

I1394 PHY & Connectors

ATX & Front Panel

ACPI (MS5) Controller

VRM 9.0 - ST6917B

GPIO

Power Delivery Map & MANUAL

Revision History 1

19

20

21

22

23

24

25

AGP 3.0 SLOT * 1

PCI2.2 SLOT * 3

PWM Controller:

ST6917B

ACPI:

MS5

1

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

COVER SHEET

(MS-6595)

1 25Monday, July 08, 2002

0A

1

VRM 9.2

ST6917B

2-Phase PWM

AGP 3.0

Connector

Analo g

Video

4X / 8X

462-Pin Socket Proc essor

K7 FSB

CRUSH 18

64bit DDR

Block Diagram

2 DDR

DIMM

Modules

(1+1)

Out

LDT Link

IDE Prim ary

UltraDMA 33/66/100/133

PCI CNTRL

PCI Slot 1

PCI Slot 2

PCI Slot 3

IDE Seco ndary

MCP-2

A A

USB Port 0

PCI ADDR/DATA

USB Port 1

USB Port 2

USB

LPC Bus

USB Port 3

USB Port 4

LPC SIO

USB Port 5

ALC202A

AC'97 Link

W83627HF-AW

AC'97 Codec

FW802A

1394a PHY

1394a

MII

Flash

Keyboard

Mouse

Floopy Parallel Seria l

10/100BaseT

ICS1893

MSI

Title

Size Document Number Rev

1

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Joey Lee

H/W Project Engineer : Richard Shih

BLOCK DIAGRAM

(MS-6595)

2 25Monday, July 08, 2002

OA

8

SDATA#[0..63]{5}

D D

C C

B B

DICLK#[0..3]{5}

DIVAL#{5}

DOCLK#[0..3]{5}

AIN#[2..14]{5}

A A

AICLK#{5}

CFWDRST{5}

CONNECT{5}

PROCRDY{5}

8

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

DICLK#0

DICLK#1

DICLK#2

DICLK#3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

DOVAL#

AIN#0

AIN#1

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

FILVAL#

AG33

AG37

AG35

7

CPU SIGNAL BLOCK

U13A

AA35

SDATA0

W37

SDATA1

W35

SDATA2

Y35

SDATA3

U35

SDATA4

U33

SDATA5

S37

SDATA6

S33

SDATA7

AA33

SDATA8

AE37

SDATA9

AC33

SDATA10

AC37

SDATA11

Y37

SDATA12

AA37

SDATA13

AC35

SDATA14

S35

SDATA15

Q37

SDATA16

Q35

SDATA17

N37

SDATA18

J33

SDATA19

G33

SDATA20

G37

SDATA21

E37

SDATA22

G35

SDATA23

Q33

SDATA24

N33

SDATA25

L33

SDATA26

N35

SDATA27

L37

SDATA28

J37

SDATA29

A37

SDATA30

E35

SDATA31

E31

SDATA32

E29

SDATA33

A27

SDATA34

A25

SDATA35

E21

SDATA36

C23

SDATA37

C27

SDATA38

A23

SDATA39

A35

SDATA40

C35

SDATA41

C33

SDATA42

C31

SDATA43

A29

SDATA44

C29

SDATA45

E23

SDATA46

C25

SDATA47

E17

SDATA48

E13

SDATA49

E11

SDATA50

C15

SDATA51

E9

SDATA52

A13

SDATA53

C9

SDATA54

A9

SDATA55

C21

SDATA56

A21

SDATA57

E19

SDATA58

C19

SDATA59

C17

SDATA60

A11

SDATA61

A17

SDATA62

A15

SDATA63

W33

SDATAINCLK0

J35

SDATAINCLK1

E27

SDATAINCLK2

E15

SDATAINCLK3

AN33

SDATAINVAL

AE35

SDATAOUTCLK0

C37

SDATAOUTCLK1

A33

SDATAOUTCLK2

C11

SDATAOUTCLK3

AL31

SDTATOUTVAL

AJ29

SADDIN0

AL29

SADDIN1

SADDIN2

AJ37

SADDIN3

AL35

SADDIN4

AE33

SADDIN5

AJ35

SADDIN6

SADDIN7

AL33

SADDIN8

AN37

SADDIN9

AL37

SADDIN10

SADDIN11

AN29

SADDIN12

AN35

SADDIN13

AN31

SADDIN14

AJ33

SADDINCLK

AJ21

CLKFWDRST

AL23

CONNECT

AN23

PROCRDY

AJ31

SFILLVAL

N12-4620011-F02

**All CPU interface are 2.5V tolerant**

7

462-Pin Socket

6

A20M

FERR

INIT

INTR

IGNNE

NMI

RESET

SMI

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

ZN

ZP

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

Part 1

DBRDY

DBREQ

FLUSH

TCK

TDI

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

6

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

A20M#

FERR#

CPUINIT#

INTR

IGNNE#

NMI

CPURST#

SMI#

STPCLK#

R29 22

C49 X_10p

APICCLK_CPU

APICD0#

APICD1#

COREFB#

COREFB

CPUCLK_R

CPUCLK#_R

CLKOUT

CLKOUT#

VREFMODE

VREF_SYS

ZN

ZP

PLLBP#

PLBYCLK

PLBYCLK#

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

DBREQ#

FLUSH#

CPU_TCK

CPU_TDI

CPU_TMS

CPU_TRST#

VIDA0

VIDA1

VIDA2

VIDA3

VIDA4

FID0

FID1

FID2

FID3

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

CPU_OK

5

A20M# {9}

FERR# {9}

CPUINIT# {9}

INTR {9}

IGNNE# {9}

NMI {9}

CPURST# {5,9}

SMI# {9}

STPCLK# {9}

CPU_OK {5,20,21}

APICCLK_CPU {5}

APICD0# {9}

APICD1# {9}

COREFB# {22}

COREFB {22}

VIDA[0..4] {5}

FID[0..3] {5}

AOUT#[2..14] {5}

AOCLK# {5}

5

4

3

2

CPU PULL-UP / DOWN BLOCK

NMI

INTR

SMI#

CPUINIT#

STPCLK#

A20M#

IGNNE#

CPURST#

PLLTEST#

DBREQ#

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R15 680

R19 680

RN12

1 2

3 4

5 6

7 8

510

RN3

680

RN6

680

VCORE

AIN#0

R101 270

AIN#1

R95 270

PLLMON1

R52 56

PLLMON2

R44 56

FLUSH#

R20 680

PLLBP#

R90 680

CPU_OK

R31 270

FERR#

R7 680

SCANCLK2

SSHIFTEN

SINTVAL

SCANCLK1

FILVAL#

DOVAL#

X_4.7u-0805(S/S)C598 R42 10K

1 2

3 4

5 6

7 8

R115 270

R109 270

RN13

270

X_4.7u-0805(S/S)C600

COREFB

COREFB#

Put in Solder

CPU SYSCLK BLOCK CPU K7CLKOUT BLOCK

VCORE

CPUCLK_R

CPUCLK#_R

CPUCLK#{5}

CPUCLK{5}

680pC89 R67 60.4RST

R68

301RST

680pC105

R69 60.4RST

CPU Clock Multiplier

FID2

1 2

FID1

FID0

FID3

CFID[3:0] => CPU Clock Multiplier

3 4

5 6

7 8

RN4

680

CLOSE SOCKET462

CPU SYSCLK REFERNCE BLOCK

VCORE

VREF_SYS

0.5 * VCORE

C64

C58

10u-0805

0.1u

CLOSE SOCKET462

4

C59

0.047u

R50

110RST

R49

110RST

CPU ZN / ZP BLOCK

ZN

ZP

CLOSE SOCKET462

match the transmission line

Push-pull compensation circuit

3

R39 40.2RST

R38 56.2RST

MSI

Title

Size Document Number Rev

Date: Sheet of

VREFMODE

VCORE VCOREVCORE

R34 X_1K

R36 270

VREFMODE=Low=No voltage scaling

CPU K7 EMI termination

PLBYCLK

PLBYCLK#

VCOREVCORE

R48 0X_4.7u-0805(S/S)C601

VCORE

R65 100

R64 100

R57 100

R54 100

CLKOUT

R78 100

R77 100

CLKOUT#

R74 100

R73 100

* Trace lengths of CLKOUT and

CLKOUT# are between 2" and

3"

CPU APIC BLOCK

VCORE

APICD0#

APICD1#

APICCLK_CPU

MICRO-STAR INt'L CO., LTD.

AMD Socket462 CPU (Signal)

(MS-6597)

2

1

VCORE

VCORE

R11 330

R13 330

R174 X_453RST

3 25Monday, July 08, 2002

1

VCORE

VCORE

VCC2_5

0A

8

7

6

5

4

3

2

1

CPU VOLTAGE BLOCK

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

D D

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VSS1

VSS2

VSS3

H14

H18

H22

H26

VCC_CORE5

VSS4

VSS5

M30P8R30T8V30X8Z30

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

F30

F8

H10

H28

H30

H32

H6

H8

K30

K8

AG15

AG29

AJ7

AL7

AN7

G25

G17

G9

N7

Y7

AG7

C C

B B

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VSS6

VSS7

VSS8

VSS9

VSS10

AF14

AF18

AF22

AF26

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VSS11

VSS12

VSS13

VSS14

VSS15

AB8

AF12

AF16

AF20

AF24

AM34

AK36

AK34

AK30

AK26

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

AM36

AK32

AK28

AK24

AK20

AK22

AK18

AK14

AK10

AL5

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VSS22

VSS23

VSS25

VSS26

AK16

AK12

AK4

AK2

AH36

AH26

AM30

AH22

AH18

AH14

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

AM32

AH34

AH32

AH28

AH24

AH10

AH4

AH2

AF36

AF34

AD6

AM26

AD4

AD2

AB36

AB34

AB32Z6Z4Z2X36

X34

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

462-Pin Socket

Part 2

VSS33

VSS34

VSS35

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

AH20

AH16

AH12

AF4

AF2

AD36

AD34

AD32

AB6

AB4

AB2

Z36

Z34

Z32X6AM28X4X2

AM22

X32V6V4V2T36

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VSS51

VSS52

VSS53

VSS54

V36

V34

V32T6T4T2R36

T34

T32R6R4R2AM18

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

R34

AM24

P36

P34

P32M4M6M2K36

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VSS61

VSS62

VSS63

VSS64

R32P6P4P2M36

K34

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

M34

M32K6K4K2AM20

K32H4H2

AM14

F36

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VSS71

VSS72

VSS73

VSS74

H36

H34

F26

F22

F34

F32

F28

F24

F20

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

F18

F14

F10F6F4F2AM16

F16

F12

D32

D28

AM10

VCC_CORE79

VCC_CORE80

VCC_CORE81

VCC_CORE82

VSS81

VSS82

VSS83

VSS84

D36

D34

D30

D24

D20

D16

D12D8D4D2B36

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

D26

D22

D18

D14

D10D6B34

B32

AM2

B28

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VSS91

VSS92

VSS93

VSS94

VSS95

AM12

B30

B26

B22

B24

B20

B16

VCC_CORE94

VCC_CORE95

VCC_CORE96

VSS96

VSS97

VSS98

B18

B14

B10B6B2

B12B8B4

AJ5

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

AM4

AK6

AM6

VCCA_PLLVCORE

0 ~ 100 mA (50mA)

2.25 ~ 2.75 V

AC7

AJ23

VCC_Z

VCC_A

AA31

NC1

AC31

NC2

AE31

NC3

AG23

NC6

AG25

NC7

AG31

NC8

AG5

NC9

AJ11

NC10

AJ15

NC11

AJ17

NC12

AJ19

NC13

AJ27

NC15

AL11

NC16

AN11

NC17

AN9

NC18

G11

NC19

G13

NC20

G27

NC21

G29

NC22

G31

NC23

J31

NC24

J5

NC25

L31

NC27

N31

NC28

Q31

NC29

S31

NC30

S7

NC31

U31

NC32

U7

NC33

W31

NC34

W7

NC35

Y31

NC36

Y5

NC37

AG19

NC42

G21

NC43

AG21

NC44

G19

NC45

AN27

AL27

AN25

AL25

VSS_Z

AE7

U13B

N12-4620011-F02

C24

X_1000p

VCCA_PLL trace length from the regulator to

the PGA must less be 0.75"

Place all filters close to the PGA

Keep all power and signal trace away from

the regulator

Place a cut in GND plane around the

VCCA_PLL regulator circuit

U13C

AO1

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

N12-4620011-F02

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

YY10

AO2

AO3

AO4

YY1

YY2

YY3

YY4

YY5

YY6

YY7

YY8

YY9

For 1.5GHz CPU Fan Holes

THERMDP# {11}

THERMDN# {11}

YY24

YY23

YY22

YY21

YY20

YY19

YY18

YY17

YY16

YY15

YY14

YY13

YY12

YY11

XX1

XX2

CPU DECOUPLING CAPACITORS

VCORE VCORE VCORE VCOREVCORE VCORE VCORE

C97

39p

C98

39p

C169

39p

C31

39p

C180

39p

C127

39p

C85

39p

C176

39p

C45

A A

39p

C161

39p

C181

39p

C192

39p

C50

39p

C142

39p

C587

39p(S/S)

C586

39p(S/S)

C611

39p(S/S)

C591

39p(S/S)

C592

39p(S/S)

C593

39p(S/S)

C594

39p(S/S)

C595

39p(S/S)

C599

39p(S/S)

Put around inside plane of SocketA

on Bottom side

EMI Decoupling

C597

39p(S/S)

C602

39p(S/S)

C613

39p(S/S)

C605

39p(S/S)

C606

39p(S/S)

C607

39p(S/S)

C608

39p(S/S)

C609

39p(S/S)

C610

39p(S/S)

C614

39P(S/S)

C615

39p(S/S)

C588

39p(S/S)

C596

39p(S/S)

C620

39p(S/S)

C622

39p(S/S)

C621

39p(S/S)

VCORE

C618

56p(S/S)

C590

56p(S/S)

C604

56p(S/S)

C616

56p(S/S)

C619

56p(S/S)

C603

56p(S/S)

C617

56p(S/S)

C589

56p(S/S)

C612

56p(S/S)

VCC5 VCC3

C242 0.1u

C12 0.1u

C529 0.1u

C10 0.1u

C123

0.22u

C150

0.22u

C68

0.22u

C100

0.22u

C80

0.22u

C154

0.22u

C144

0.22u

C117

0.22u

C61

0.22u

C101

0.22u

C60

0.22u

C145

0.22u

C63

0.22u

C125

0.22u

C148

0.22u

C90

0.22u

C94

0.22u

C149

0.22u

C74

0.22u

C62

0.22u

VCC3 VCORE

VCC5 VCORE

C103

0.22u

C152

0.22u

C151

0.22u

C75

0.22u

C147

0.22u

C106

0.22u

C99

0.22u

C55

0.22u

C102

0.22u

C116

0.22u

C20 0.1u

C107 0.1u

C213 0.1u

VCC2_5

C6

0.1u

C17

0.1u

C22

0.1u

C347

0.1u

C26

0.1u

VCC5

C146

1 2

3 4

5 6

7 8

RN16

100

2.50V Reference

VR1

SC431CSK

Put inside SocketA

8

7

6

5

4

3

CPU PLL VOLTAGE BLOCK

(40mils trace / 60 mils space)

VCC_PLL

C138

39p

2

C157

0.1u

3 1

MSI

Title

Size Document Number Rev

Date: Sheet of

L6 80-0805

R91

039p

R97

X_0

Used when spec changed

C137

1000p

EC14

4.7u-0805

MICRO-STAR INt'L CO., LTD.

AMD Socket462 CPU (Power)

(MS-6597)

2

2.5V

Max 150 mA

Design for 100 mA

C131

C124

39p

39p

4 25Monday, July 08, 2002

1

VCCA_PLL

0B

8

CRUSH 18 HOST SIGNALS

D D

AIN#[2..14]{3} SDATA#[0..63] {3}

AOUT#[2..14]{3}

C C

DOCLK#[0..3]{3}

B B

Place close to C18

VCORE

A A

SLP_S3#{10,21} DLY_S3# {11}

8

AIN#[2..14]

AOUT#[2..14]

AOCLK#{3}

DOCLK#[0..3]

DIVAL#{3}

CPU_OK{3,20,21}

CPURST#{3}

PROCRDY{3}

CFWDRST{3}

CONNECT{3}

R792 45.3RST

R794 51.1RST

SS_CLKIN{10}

CPUREF_NB

R793 51.1RST

U24A

74LCX14-SOIC14

SLP_S3 DLY_S3

1 2 R506 X_8.2K R511 X_0

7

AIN#2

AC2

AF3

AG3

AC1

AE2

AD2

AF1

AH3

AF2

AE3

AH1

AH2

AG2

AF5

D1

D2

C4

C1

E3

A2

E4

A1

A3

E5

B3

C2

B2

D3

AE6

V5

T5

N6

AD3

AB5

N5

H4

AJ2

AJ3

AH5

AP9

AN9

AF4

AG5

AD4

AK2

AH6

AM6

AG6

AN8

AN3

AN4

AF6

AG4

AIN2

AIN3

AIN4

AIN5

AIN6

AIN7

AIN8

AIN9

AIN10

AIN11

AIN12

AIN13

AIN14

AINCLK

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

AOUT9

AOUT10

AOUT11

AOUT12

AOUT13

AOUT14

AOUTCLK

DICLK0

DICLK1

DICLK2

DICLK3

DOCLK0

DOCLK1

DOCLK2

DOCLK3

CPU_SDINVLD

CPU_PWRGD

CPU_RST

CPU_APIC_CLK_R

MCP_APIC_CLK_R

PROCRDY

CPU_CLKFWDRST

CPU_CONNECT

CPU_VREF

CPU_COMP

CPU_CAL_PU

CPU_CAL_PD

SSCLK_IN

BSEL0

BSEL1

HCLK

HCLK

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

SAICLK#

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

AOCLK#

SDICLK#0

SDICLK#1

SDICLK#2

SDICLK#3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

ACLK_CPU

ACLK_MCP

FSB_SEL0

FSB_SEL1

CCLK

CCLK#

S3 Delay Block

R501 0

7

BELONG TO CLKFWD GROUP[SADDIN] MATCH W/IN +/-10MILS OF GROUP 5/15, CLK:10/30

BELONG TO CLKFWD GROUP[SADDOUT] MATCH W/IN +/-10MILS OF GROUP 5/15, CLK:10/30

VCORE

AK5

AK4

AJ6

VTT

VTT

VTT

BELONG TO CLKFWD GROUP;MATCHED TO INDIVIDUAL CLKFWD GROUP

RESPECTIVELY.[SDATA0], [SDATA1], [SDATA2],[SDATA3] W/IN+/-10MILS OF GROUP

AJ5

AL6

AL5

AL4

AL3

AL2

AL1

AK6

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

HOST INTERFACE

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

C3L5H5M4U5W3R4V4AA6D5Y5J4M6

U24B

74LCX14-SOIC14

3 4

(3VDUAL)(3VDUAL)

C582

X_0.01u

6

AJ4

AM5

AM4

AM3

AM2

AM1

M9N9AD9

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

CRUSH18

PART 1

NC

AD5

AK3

AJ1

AE5

R5

6

P9R9T9U9V9

AE9

VTT

VTT

VTT

VTT

VTT

VDD_2P5

AM9

AL7

W9Y9AA9

VTT

VTT

VTT

VTT

VDD_3P3

VDD_3P3

AL8

C673 0.1u(S/S)

5

U26A

AB9

AC9

J12

J13

J14

SDATA#[0..63]

SDATA#0

AA3

D0

VTT

VTT

VTT

VTT

VTT

VTT

SDATA#1

V3

D1

SDATA#2

V2

D2

SDATA#3

W2

D3

SDATA#4

U3

D4

SDATA#5

U2

D5

SDATA#6

T3

D6

SDATA#7

T2

D7

SDATA#8

Y1

D8

SDATA#9

AC3

D9

SDATA#10

AA2

D10

SDATA#11

AB3

D11

SDATA#12

Y3

D12

SDATA#13

Y2

D13

SDATA#14

AB2

D14

SDATA#15

U1

D15

SDATA#16

R2

D16

SDATA#17

R3

D17

SDATA#18

P1

D18

SDATA#19

L3

D19

SDATA#20

K3

D20

SDATA#21

L1

D21

SDATA#22

K2

D22

SDATA#23

L2

D23

SDATA#24

P3

D24

SDATA#25

M3

D25

SDATA#26

N3

D26

SDATA#27

P2

D27

SDATA#28

N2

D28

SDATA#29

M2

D29

SDATA#30

J2

D30

SDATA#31

J3

D31

SDATA#32

W6

D32

SDATA#33

U4

D33

SDATA#34

T6

D34

SDATA#35

P5

D35

SDATA#36

L6

D36

SDATA#37

M5

D37

SDATA#38

R6

D38

SDATA#39

K5

D39

SDATA#40

Y4

D40

SDATA#41

AA5

D41

SDATA#42

AA4

D42

SDATA#43

Y6

D43

SDATA#44

U6

D44

SDATA#45

W5

D45

SDATA#46

L4

D46

SDATA#47

P4

D47

SDATA#48

F2

D48

SDATA#49

J5

D49

SDATA#50

G5

D50

SDATA#51

F1

D51

SDATA#52

F4

D52

SDATA#53

E2

D53

SDATA#54

G6

D54

SDATA#55

F5

D55

SDATA#56

H3

D56

SDATA#57

J6

D57

SDATA#58

H1

D58

SDATA#59

H2

D59

SDATA#60

G3

D60

SDATA#61

H6

D61

SDATA#62

G2

D62

SDATA#63

F3

CPU_FID0

CPU_FID1

CPU_FID2

CPU_FID3

CRUSH18

VCC3VCC2_5

D63

FID0

AC5

FID1

AC6

FID2

AD6

FID3

AC4

FSB Selection

VCORE

FSB_SEL1 FSB_SEL0

R798 1.2K

R127 X_10K

B_SEL1{10}

B_SEL0{10}

5

B_SEL1

B_SEL0

R120 X_1.2K

R111 10K

R799 X_10K

R124 X_10K

4

FID[0..3] {3}

FSB_SEL1

FSB_SEL0

4

070702

3

2

SYSTEM DATA-IN-CLK NOISE L/C BLOCK

SAICLK#

SDICLK#0

SDICLK#1 SICLK#1

L79 10nH L80 10nH

SDICLK#2

L81 10nH

SDICLK#3 DICLK#3

SICLK#

L76 10nHL75 10nH

C849 5p

SICLK#0

L78 10nHL77 10nH

C850 5p

C648 5p

SICLK#2

L82 10nH

C649 5p

SICLK#3

L84 10nHL83 10nH

C650 5p

CLK must less DATA 1.5inchs

(Place in middle of Bus)

VID Selector Block

VIDB0

BASS0

BASS1

BASS0

BASS1

BASS3

BASS2

BASS4

VCC2_5

VIDB3

BASS3

VIDB4

BASS4

+

EC4

10u-16V

VIDA0 VIDB2

Q1

YFET-NDS7002AS

VIDA1VIDB1

Q2

YFET-NDS7002AS

12

RN1

34

4.7K

56

78

R3 4.7K

VIDA[0..4]{3}

VIDB[0..4]{11,22}

VIDA3

Q4

YFET-NDS7002AS

VIDA4

Q8

YFET-NDS7002AS

Place close to C18

C18 Decoupling Caps

VCORE

C662

0.1u(S/S)

C664

0.1u(S/S)

C666

0.1u(S/S)

C668

0.1u(S/S)

C670

0.1u(S/S)

C855

1u-0805(S/S)

MSI

Title

Size Document Number Rev

3

Date: Sheet of

APICCLK_CPU{3}

APICCLK_MCP{9}

CPUCLK{3}

CPUCLK#{3}

C18 VREF Volatge

CPUREF_NB

MICRO-STAR INt'L CO., LTD.

Crush18 Host & VID Signals

(MS-6595)

2

DICLK#0

DICLK#1

DICLK#2

BASS2

VIDA0

VIDA1

VIDA3

VIDA2

VIDA4

R5 10K

VIDB0

VIDB1

VIDB2

VIDB3

VIDB4

R1 4.7K

C651 10p

R789 22

R790 22

C652 10p

R791 22

C655 10p

R795 22

C660 10p

Set PO_VREF to

50% of VCORE

C680

C679 R797

0.1u1000p

H/W Project Leader : Joey Lee

H/W Project Engineer : Richard Shih

1

AICLK# {3}

DICLK#[0..3] {3}

Q3

YFET-NDS7002AS

VCORE

R796

121RST

121RST

5 25Monday, July 08, 2002

1

VIDA2

12

RN7

34

10K

56

78

78

RN2

56

4.7K1234

ACLK_CPU

ACLK_MCP

CCLK

CCLK#

VCC2_5

VCC3

0A

8

7

6

5

4

3

2

1

CRUSH 18 MEMORY A SIGNALS

MEM_STR

D D

C C

W31

AC31

AD32

W32

B B

AA33

AB31

AD33

AE31

AH31

AG31

AE32

AD31

AF31

AH32

AB32

AF33

AC33

AG32

A A

A8

A11

A14

A17

A20

A23

A26

A29D8D11

D14

D17

D20

D23

D26

D29

E29

E30

E31

E36

F33

H36

K33

K36

N33

N36

T33

T36

W33

W36

AB33

AB36

AE33

VCCM

VCCM

GND

GND

K6

VCCM

VCCM

GND

GND

L32

AE36

VCCM

VCCM

VCCM

GND

GND

GND

L36N1N4P6P32

D6

MA_D0

E6

MA_D1

E8

MA_D2

D9

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

LDT Signals

GND

GND

GND

GND

GND

GND

F31

F36

G31G4H31

H33K1K4

VCCM

GND

MA_D3

C5

MA_D4

D7

MA_D5

F8

MA_D6

E10

MA_D7

D10

MA_D8

F11

MA_D9

F14

MA_D10

D16

MA_D11

F9

MA_D12

D12

MA_D13

F13

MA_D14

E14

MA_D15

F16

MA_D16

F17

MA_D17

E20

MA_D18

E22

MA_D19

D15

MA_D20

D18

MA_D21

E19

MA_D22

D21

MA_D23

F23

MA_D24

F24

MA_D25

D28

MA_D26

F27

MA_D27

D24

MA_D28

E23

MA_D29

F26

MA_D30

D27

MA_D31

J32

MA_D32

G33

MA_D33

K31

MA_D34

M32

MA_D35

H32

MA_D36

J31

MA_D37

J33

MA_D38

L31

MA_D39

R32

MA_D40

N31

MA_D41

V32

MA_D42

U33

MA_D43

M31

MA_D44

P31

MA_D45

V33

MA_D46

V31

MA_D47

MA_D48

Y31

MA_D49

MA_D50

MA_D51

MA_D52

Y33

MA_D53

MA_D54

MA_D55

MA_D56

MA_D57

MA_D58

MA_D59

MA_D60

MA_D61

MA_D62

MA_D63

F7

MA_DQM0

D13

MA_DQM1

F19

MA_DQM2

F25

MA_DQM3

K32

MA_DQM4

T32

MA_DQM5

MA_DQM6

MA_DQM7

E7

MA_DQS0

E11

MA_DQS1

E17

MA_DQS2

D25

MA_DQS3

L33

MA_DQS4

U31

MA_DQS5

MA_DQS6

MA_DQS7

GND

GND

GND

GND

GND

GND

GND

A9

A12

A15

A18

A21

A24

A27B1D4

8

CRUSH18

PART 2

SYSTEM MEMORY A

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

D32

D33E1E9

E12

E15

E18

E21

E24

E27

E33F6F29

F30

7

AH33

AH36A5C33

VCCM

GND

VCCM

VCCM

VCCM

MA_CLK0

MA_CLK0

MA_CLK1

MA_CLK1

MA_CLK2

MA_CLK2

MA_CKE0

LDT_RXD0

LDT_RXD1

LDT_RXD2

LDT_RXD3

LDT_RXD4

LDT_RXD5

LDT_RXD6

LDT_RXD7

LDT_RXD8

LDT_TXD0

LDT_TXD1

LDT_TXD2

LDT_TXD3

LDT_TXD4

LDT_TXD5

LDT_TXD6

LDT_TXD7

LDT_TXD8

LDT_RXCLK

LDT_RXCLK

LDT_RXD0

LDT_RXD1

LDT_RXD2

LDT_RXD3

LDT_RXD4

LDT_RXD5

LDT_RXD6

LDT_RXD7

LDT_RXD8

LDT_TXD0

LDT_TXD1

LDT_TXD2

LDT_TXD3

LDT_TXD4

LDT_TXD5

LDT_TXD6

LDT_TXD7

LDT_TXD8

LDT_TXCLK

LDT_TXCLK

LDT_RST

LDT_RSET

GND

GND

GND

P36T1T4

6

AK33

MAA0

MAA1

VCCM

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MA_BA0

MA_BA1

MA_CS0

MA_CS1

MA_RAS

MA_CAS

MA_WE

GND

U32

GND

U36

U26B

GND

E32

E28

F28

E25

E26

D22

F22

F20

F21

D19

F32

F18

E16

F10

N32

G32

R31

T31

D30

D31

F12

E13

AA31

AA32

M33

R33

P33

F15

AR25

AL25

AN27

AR28

AT26

AR24

AR27

AM28

AP28

AT34

AN31

AP31

AL29

AL26

AT32

AP30

AT29

AN30

AN26

AN25

AP25

AM25

AM27

AP27

AR26

AP24

AT27

AN28

AR29

AT35

AP32

AR31

AL28

AL27

AR32

AR30

AT30

AN29

AT33

AR33

AR9

AT36

CRUSH18

LDT_RSET

LDT_RXD0 {9}

LDT_RXD1 {9}

LDT_RXD2 {9}

LDT_RXD3 {9}

LDT_RXD4 {9}

LDT_RXD5 {9}

LDT_RXD6 {9}

LDT_RXD7 {9}

LDT_RXD8 {9}

LDT_TXD0 {9}

LDT_TXD1 {9}

LDT_TXD2 {9}

LDT_TXD3 {9}

LDT_TXD4 {9}

LDT_TXD5 {9}

LDT_TXD6 {9}

LDT_TXD7 {9}

LDT_TXD8 {9}

LDT_RX_CLK {9}

LDT_RX_CLK# {9}

LDT_RXD#0 {9}

LDT_RXD#1 {9}

LDT_RXD#2 {9}

LDT_RXD#3 {9}

LDT_RXD#4 {9}

LDT_RXD#5 {9}

LDT_RXD#6 {9}

LDT_RXD#7 {9}

LDT_RXD#8 {9}

LDT_TXD#0 {9}

LDT_TXD#1 {9}

LDT_TXD#2 {9}

LDT_TXD#3 {9}

LDT_TXD#4 {9}

LDT_TXD#5 {9}

LDT_TXD#6 {9}

LDT_TXD#7 {9}

LDT_TXD#8 {9}

LDT_TX_CLK {9}

LDT_TX_CLK# {9}

LDT_RST# {9}

R804 49.9RST

Place close to C18

5

R480 10KST

PWOK{20}

R488

14.7KST

R481 4.75KST Q41

VCORE

R490

30.1KST

R478 12.1KST

VDD

R487

30.1KST

Decoupling capacitors

MEM_STR

4

C683

0.1u

C685

0.1u

C690

0.1u

C695

0.1u

C700

0.1u

C705

0.1u

C707

0.1u

C709

0.1u

C711

0.1u(S/S)

C715

0.1u

C717

0.1u

5VSB

R479

10K

C574

1u

C571

2.2u

C572

1u

MEM_STR

YFET-NDS7002AS

R483 4.7K

Q43

2N3904S

2N3904S

Q42

2N3904S

PLL Delay Block

+12V

R507

10K

Q40

C573

1000p

C684

0.1u

C686

0.1u

C691

0.1u

C696

0.1u

C701

0.1u

C706

0.1u

C708

0.1u

C710

0.1u

C714

0.1u

C716

0.1u

C718

0.1u

3

VCC3

C575

1000p

R414 X_0

CP13 X_COPPER

FB9 X_80-0805

C494

C488

0.1u

4.7u-0805

C585

1000p

C270

VCC3

R505

4.7K

C576

0.33u

C561

0.33u

VCC3

VDD_PLL_NB

R508 1K

Q45

2N3904S

Q39

2N3904S

3VDUAL

C492

0.1u

Pop R800 for A2

R800

X_0

C259

0.1u4.7u-0805

CLOSE TO C18

VDD_PLL_MCP {9}

CLOSE TO MCP2

VDD_PLL_NB {8}

Q38

2N3904S

C579

1u

R411 0

VCC3

R510 56.2KST

Q37

YFET-NDS7002AS

Q44

YFET-NDS7002AS

CP8 X_COPPER

FB5 X_80-0805

C281

0.1u

R486 18.7KST

R495

10KST

R512

30.1KST

C18 Decoupling capacitors

VDDQ

C702

0.1u

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Crush18 Memory-A & LDT & PLL Delay Signals

2

MEM_STRVDDQ

0.1u(S/S)

H/W Project Leader : Joey Lee

H/W Project Engineer : Richard Shih

(MS-6595)

C689

0.1uC693

C694

0.1u

C699

0.1u

C704

0.1u

6 25Monday, July 08, 2002

PLL_RST {20}

0A

1

8

7

6

5

4

3

2

1

CRUSH 18 MEMORY SIGNALS

VDD

U26D

J15

J16

J17

J18

J19

J20

J21

J22

J23

AH25

P28

R28

T28

U28

V28

W28

Y28

AA28

AB28

AC28

AH22

AH23

AR36

N28

AD28

AE28

AH24

J24

J25

M28

AJ31

AJ32

AK31

AK32

AL30

AL31

AL32

AL33

VDD

GND

U15

VDD

GND

U16

VDD

VDD

VDD

VDD

VDD

MB_CKE0

MC_CKE0

MB_CLK0

MB_CLK0

MB_CLK1

MB_CLK1

MB_CLK2

MB_CLK2

MC_CLK0

MC_CLK0

MC_CLK1

MC_CLK1

MC_CLK2

MC_CLK2

M_STR_ENABLE

GND

GND

GND

GND

GND

U17

U18

U19

U20

5

AM30

MB_A0

VDD

MB_A1

MB_A2

MB_A3

MB_A4

MB_A5

MB_A6

MB_A7

MB_A8

MB_A9

MB_A10

MB_A11

MB_A12

MB_A13

MB_BA0

MB_BA1

MB_RAS

MB_CAS

MB_WE

MC_A0

MC_A1

MC_A2

MC_A3

MC_A4

MC_A5

MC_A6

MC_A7

MC_A8

MC_A9

MC_A10

MC_A11

MC_A12

MC_A13

MC_BA0

MC_BA1

MC_RAS

MC_CAS

MC_WE

MB_CS0

MB_CS1

MC_CS0

MC_CS1

M_VERF

GND

U21

U22

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

U23

GND

E34

B35

D34

A33

B32

C28

C30

B24

B26

B23

F34

C22

B18

C9

M35

G34

R35

W34

T35

C17

E35

B36

A35

B33

A32

B28

C29

C25

C26

B22

F35

B21

B19

B9

N34

G35

R34

W35

U34

B17

V35

Y35

V34

Y34

C35

C36

C14

B14

AF35

AF34

D35

D36

C13

B13

AG35

AG34

AJ33

AG33

AM31

AM32

AM33

AN32

AN33

AP33

AP34

AR34

AR35

CRUSH18

MA_RB0

MA_RB1

MA_RB2

MA_RB3

MA_RB4

MA_RB5

MA_RB6

MA_RB7

MA_RB8

MA_RB9

MA_RB10

MA_RB11

MA_RB12

MA_RB13

R826 0

R827 0

R828 0

MA_RC0

MA_RC1

MA_RC2

MA_RC3

MA_RC4

MA_RC5

MA_RC6

MA_RC7

MA_RC8

MA_RC9

MA_RC10

MA_RC11

MA_RC12

MA_RC13

R829 0

R830 0

R832 0

R834 0

R835 0

R836 0

R837 0

MCLK_B0

MCLK_B#0

MCLK_B1

MCLK_B#1

MCLK_B2

MCLK_B#2

MCLK_C0

MCLK_C#0

MCLK_C1

MCLK_C#1

MCLK_C2

MCLK_C#2

DDR_VREF_C18

PRST#1

R839 3.3K

R841 10K

VDD

4

D D

C C

B B

A A

MDQ_B[0..63]{14}

MDQM_B[0..7]{14}

MDQS_B[0..7]{14}

8

MDQ_B0

MDQ_B1

MDQ_B2

MDQ_B3

MDQ_B4

MDQ_B5

MDQ_B6

MDQ_B7

MDQ_B8

MDQ_B9

MDQ_B10

MDQ_B11

MDQ_B12

MDQ_B13

MDQ_B14

MDQ_B15

MDQ_B16

MDQ_B17

MDQ_B18

MDQ_B19

MDQ_B20

MDQ_B21

MDQ_B22

MDQ_B23

MDQ_B24

MDQ_B25

MDQ_B26

MDQ_B27

MDQ_B28

MDQ_B29

MDQ_B30

MDQ_B31

MDQ_B32

MDQ_B33

MDQ_B34

MDQ_B35

MDQ_B36

MDQ_B37

MDQ_B38

MDQ_B39

MDQ_B40

MDQ_B41

MDQ_B42

MDQ_B43

MDQ_B44

MDQ_B45

MDQ_B46

MDQ_B47

MDQ_B48

MDQ_B49

MDQ_B50

MDQ_B51

MDQ_B52

MDQ_B53

MDQ_B54

MDQ_B55

MDQ_B56

MDQ_B57

MDQ_B58

MDQ_B59

MDQ_B60

MDQ_B61

MDQ_B62

MDQ_B63

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

AB34

AC34

AB35

AC35

AD34

AE34

AJ35

AK35

AD35

AE35

AJ34

AK34

AL36

AM34

AN35

AP35

AL34

AL35

AM35

AP36

AA34

AH34

AM36

AA35

AH35

AN36

B4

MB_D0

C6

MB_D1

B7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

AP29

GND

AT11

GND

GND

AT14

GND

AT17

GND

AT20

VDD

GND

AT24

U14

MB_D2

B8

MB_D3

A4

MB_D4

B5

MB_D5

C7

MB_D6

C8

MB_D7

C10

MB_D8

C11

MB_D9

C16

MB_D10

B16

MB_D11

B10

MB_D12

C12

MB_D13

C15

MB_D14

B15

MB_D15

C19

MB_D16

C20

MB_D17

C24

MB_D18

C27

MB_D19

C18

MB_D20

B20

MB_D21

B25

MB_D22

B27

MB_D23

B29

MB_D24

B30

MB_D25

C34

MB_D26

B34

MB_D27

A30

MB_D28

C31

MB_D29

A34

MB_D30

A36

MB_D31

H34

MB_D32

J35

MB_D33

L34

MB_D34

N35

MB_D35

H35

MB_D36

J34

MB_D37

L35

MB_D38

M34

MB_D39

P35

MB_D40

U35

MB_D41

MB_D42

MB_D43

P34

MB_D44

T34

MB_D45

MB_D46

MB_D47

MB_D48

MB_D49

MB_D50

MB_D51

MB_D52

MB_D53

MB_D54

MB_D55

MB_D56

MB_D57

MB_D58

MB_D59

MB_D60

MB_D61

MB_D62

MB_D63

A6

MB_DQM0

B12

MB_DQM1

C23

MB_DQM2

C32

MB_DQM3

K35

MB_DQM4

MB_DQM5

MB_DQM6

MB_DQM7

B6

MB_DQS0

B11

MB_DQS1

C21

MB_DQS2

B31

MB_DQS3

K34

MB_DQS4

MB_DQS5

MB_DQS6

MB_DQS7

GND

GND

GND

GND

GND

GND

V6W1W4

Y32

Y36

AB1

7

CRUSH18

PART 4

SYSTEM MEMORY B

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AB4

AB6

AC32

AC36

AE1

AE4

AF32

AF36

AH4

AJ36

AM8

AM11

AM14

AM17

AM20

AM23

AM26

AM29

AN34

6

GND

AP4

GND

AP26

DDR REFENCE VOLTAGE

MEM_STR

R787

121RST

DDR_VREF_C18

R788

121RST

Put near pin AJ33 of C18

30mils Trace/45mils Space

MBA_B0 {14}

MBA_B1 {14}

MRAS_B# {14}

MCAS_B# {14}

MWE_B# {14}

MCKE_B {14}

MBA_C0 {14}

MBA_C1 {14}

MRAS_C# {14}

MCAS_C# {14}

MWE_C# {14}

MCKE_C {14}

MCS_B#0 {14}

MCS_B#1 {14}

MCS_C#0 {14}

MCS_C#1 {14}

MCLK_B0 {14}

MCLK_B#0 {14}

MCLK_B1 {14}

MCLK_B#1 {14}

MCLK_B2 {14}

MCLK_B#2 {14}

MCLK_C0 {14}

MCLK_C#0 {14}

MCLK_C1 {14}

MCLK_C#1 {14}

MCLK_C2 {14}

MCLK_C#2 {14}

PCIRST#0 {9,11}

MA_B[0..13]{14}

MA_C[0..13]{14}

MA_B[0..13]

MA_C[0..13]

C719

0.1u

C720

0.1u

3

Title

Size Document Number Rev

Date: Sheet of

DDR Terminational Resisitors

MDQ_B16

R805 100

MDQ_B17

R806 100

MDQ_B18

R807 100

MDQ_B19

R808 100

MDQ_B20

R809 100

MDQ_B21

R810 100

MDQ_B22

R811 100

MDQ_B23

R812 100

MDQ_B41

R813 100

MDQ_B42

R814 100

MDQ_B45

R815 100

MDQ_B46

R816 100

MDQ_B52

R817 100

MDQ_B53

R818 100

MDQS_B2

R819 100

MDQS_B3

R820 100

MDQS_B5

R821 100

MDQM_B1

R822 100

MDQM_B2

R823 100

MDQM_B3

R824 100

MDQM_B5

R825 100

MDQ_B24

1 2

MDQ_B28

MDQ_B29

MDQ_B25

MDQ_B30

MDQ_B26

MDQ_B27

MDQ_B31

MDQ_B32

MDQ_B36

MDQ_B33

MDQ_B37

MDQS_B4

MDQ_B34

MDQM_B4

MDQ_B38

MDQ_B39

MDQ_B35

MDQ_B40

MDQ_B44

MCKE_C

MCKE_B

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R831 100

R833 100

RN104

100

RN106

100

RN108

100

RN110

100

RN112

100

DDR Dampping Resisitors

MA_B0

7 8

MA_C0

5 6

MA_B10

3 4

MA_C10

1 2

MA_C2

7 8

MA_B2

5 6

MA_B1

3 4

MA_C1

1 2

MA_B5

7 8

MA_C5

5 6

MA_C6

3 4

MA_B6

1 2

R838 0

R840 0

MA_B4 MA_RB4

7 8

MA_C3

5 6

MA_C4

3 4

MA_B3

1 2

MA_B7

7 8

MA_C7

5 6

MA_C8

3 4

MA_B8

1 2

MA_C11

7 8

MA_B11

5 6

MA_C9

3 4

MA_B9

1 2

R842 0

R843 0

MSI

MICRO-STAR INt'L CO., LTD.

Crush18 Memory-B Signals

(MS-6595)

2

MDQ_B14

1 2

MDQ_B15

MDQ_B10

MDQ_B11

MDQ_B0

MDQ_B4

MDQ_B1

MDQS_B0

MDQ_B5

MDQ_B6

MDQM_B0

MDQ_B2

MDQ_B7

MDQ_B3

MDQ_B8

MDQ_B9

MDQS_B1

MDQ_B13

MDQ_B12

MDQ_B43

MDQ_B47

MDQ_B48

MDQ_B49

MDQ_B55

MDQM_B6

MDQ_B54

MDQS_B6

MDQ_B61

MDQ_B60

MDQ_B50

MDQM_B7

MDQ_B51

MDQ_B63

MDQ_B62

MDQ_B56

MDQ_B57

MDQ_B58

MDQS_B7

MDQ_B59

MA_RB0

MA_RC0

RN114

MA_RB10

0

MA_RC10

MA_RC2

MA_RB2

RN115

MA_RB1

0

MA_RC1

MA_RB5

MA_RC5

RN116

MA_RC6

0

MA_RB6

MA_RC12MA_C12

MA_RC13MA_C13

MA_RC3

RN117

MA_RC4

0

MA_RB3

MA_RB7

MA_RC7

RN118

MA_RC8

0

MA_RB8

MA_RC11

MA_RB11

RN119

MA_RC9

0

MA_RB9

MA_B12MA_RB12

MA_B13MA_RB13

H/W Project Leader : Joey Lee

H/W Project Engineer : Richard Shih

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

7 25Monday, July 08, 2002

1

RN78

100

RN100

100

RN101

100

RN102

100

RN103

100

RN105

100

RN107

100

RN109

100

RN111

100

RN113

100

VTT_DDR2VTT_DDR2

0A

8

7

6

5

4

3

2

1

CRUSH 18 AGP & VIDEO SIGNALS

VDDQ VCC3

AN21

AN18

AN15

AN12

AT12

AT15

AT18

AT21

AT23

AH19

AH20

AH21

AH12

AH13

VDDQ

VDDQ

AGP 8X

GND

GND

P19

P20

P21

GND

P22

GND

P23

VCC3

VCC3

GND

GND

T14

AH14

VCC3

GND

T15

D D

Place close to C18

PCIRST#0{9,11}

PIRQ#E{15,16}

C C

B B

A A

VDD_PLL_NB{6}

Y7

YCRY27H-D

20pC738

20pC741

8

R847 124RST

C732 0.01u

R853 124RST

C735 0.01u

XTAL_IN_27M

XTAL_OUT_27M

VSYNC

HSYNC

RED_A

BLUE_A

GREEN_A

RSETA

DVREFA

GND_DACA

VDD_DACA

VSYNC_B

HSYNC_B

TV_C

TV_Y

RSETB

DVREFB

GND_DACB

VDD_DACB

PCIRST#0

PIRQ#E

XTAL_IN_27M

XTAL_OUT_27M

TEST

VDD_PLL_NB

1000pC736

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

AC23

AR6

AT6

AT1

AT2

AT3

AT4

AR3

AR5

AT5

AP5

AN5

AN2

AP1

AR1

AP2

AP3

AN1

AR2

AP8

AP7

AN6

AP6

AM7

AR4

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y22

Y23

R14

R15

R16

R17

R18

R19

R20

R21

R22

R23

V14

V15

V16

V17

V18

V19

V20

V21

V22

V23

7

DACA_VSYNC

DACA_HSYNC

DACA_RED

DACA_BLUE

DACA_GREEN

DACA_RESET

DACA_VREF

DACA_GND

DACA_VDD

DACB_VSYNC

DACB_HSYNC

DACB_RED

DACB_BLUE

DACB_GREEN

DACB_RESET

DACB_VREF

DACB_GND

DACB_VDD

PCI_RST

INTR_OUT

XTAL_IN

XTAL_OUT

TEST

VDD_PLL

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

W14

GND

W15

GND

W16

GND

W17

GND

W18

GND

W19

VDDQ

VDDQ

GND

GND

W20

VDDQ

GND

W21

VDDQ

VDDQ

VDDQ

VDDQ

CRUSH18

PART 3

AGP 8X,

VIDEO

GND

GND

GND

GND

W22

W23

P14

P15

P16

VDDQ

VDDQ

GND

GND

P17

VDDQ

GND

P18

6

AH15

VCC3

GND

T16

AH16

T17

AH17

AH18

VCC3

VCC3

VCC3

G_FRAME

G_DEVSEL

G_SBSTBF

G_SBSTBS

G_ADSTBF0

G_ADSTBS0

G_ADSTBF1

G_ADSTBS1

G_CAL_PU

G_CAL_PD

G_GC_8XDET

GND

GND

GND

T18

T19

T20

U26C

GBE0

GBE1

GBE2

GBE3

G_IRDY

G_TRDY

G_REG

G_GNT

G_STOP

G_PAR

G_RBF

G_WBF

G_ST0

G_ST1

G_ST2

G_SBA0

G_SBA1

G_SBA2

G_SBA3

G_SBA4

G_SBA5

G_SBA6

G_SBA7

G_VREF

G_CLK

G_DBI1

G_DBI0

GND

GND

T21

T22

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

GND

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

T23

GND

CRUSH18

AN23

AM24

AL24

AL23

AM22

AN22

AM21

AL22

AM19

AL19

AN19

AM18

AL18

AN17

AL16

AN16

AR22

AR21

AP21

AP20

AR20

AP19

AR19

AP18

AR16

AP16

AR15

AP15

AR14

AP14

AP13

AR13

AL20

AM16

AP22

AR18

AR23

AP23

AM15

AT9

AR10

AL15

AL14

AL17

AP11

AL10

AP10

AR11

AL9

AM12

AL12

AL21

AN20

AR17

AP17

AN11

AM10

AL11

AN10

AL13

AM13

AN14

AN13

AN24

AR8

AR12

AP12

AR7

AN7

AT8

5

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

ST0

ST1

ST2

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

R856 22

R857 51.1

R858 51.1

AGP_8XDET

10pC761

GAD[0..31] {15}

GC_BE#[0..3] {15}

GFRAME# {15}

GIRDY# {15}

GTRDY# {15}

GREQ# {15}

GGNT# {15}

GSTOP# {15}

GDEVSEL# {15}

GPAR {15}

RBF# {15}

WBF# {15}

ST[0..2] {15}

SB_STB {15}

SB_STB# {15}

AD_STB0 {15}

AD_STB#0 {15}

AD_STB1 {15}

AD_STB#1 {15}

SBA[0..7] {15}

AGPVERF_NB {15}

AGPCLK {15}

DBIH {15}

DBIL {15}

VDDQ

AGP_8XDET{15}

4

VDD_DACA VDD_DACB

C721 C722

GND_DACA

1000p

L85

80-0805

C723 C726

0.1u 4.7u-0805

C724

0.1u 1000p

070702

RED_A

GREEN_A

BLUE_A

HSYNC

VSYNC

R844 X_75RST

R845 X_75RST

R848 X_75RST

R850 33

R852 33

CRT_R {17}

CRT_G {17}

CRT_B {17}

CRT_HSYNC {17}

CRT_VSYNC {17}

TV OUT Circuit

VCC3

D27

2

BAV99

3

BAV99

1

R854

C740

75

270p

VCC3

D28

2

3

1

R855

C744

75

270p

VDD

C747

0.1u

C770

0.1u

C772

0.1u

C773

0.1u

MSI

Title

Size Document Number Rev

Date: Sheet of

2

TV_Y

TV_C CHROMA

VDD VDD

C749

0.1u(S/S)

C754

0.1u(S/S)

C759

0.1u(S/S)

C748

0.1u(S/S)

C753

0.1u(S/S)

C758

0.1u(S/S)

C766

0.1u(S/S)

3

L86

GND_DACB

C737 22p

L87

1 2

1.8u-10%_0805

C742 22p

L88

1 2

1.8u-10%_0805

C725 C728

HSYNC_B

VSYNC_B

TEST

D2x3-1:6-BK-A

C745

0.1u(S/S)

MICRO-STAR INt'L CO., LTD.

80-0805

C727

0.1u

R846 1.21K

C731 22p

R849 1.21K

C734 22p

R851 10K

LUMA

C739

330p

JTV1

C743

330p

VCC3

C751

0.1u(S/S)

C756

0.1u

H/W Project Leader : Joey Lee

H/W Project Engineer : Richard Shih

Crush18 AGP & VIDEO Signals

(MS-6595)

8 25Monday, July 08, 2002

VCC3VCC3

0.1u4.7u-0805

070502

VCC3

2531

2531

4

4

0A

1

Loading...

Loading...