5

4

3

2

1

D D

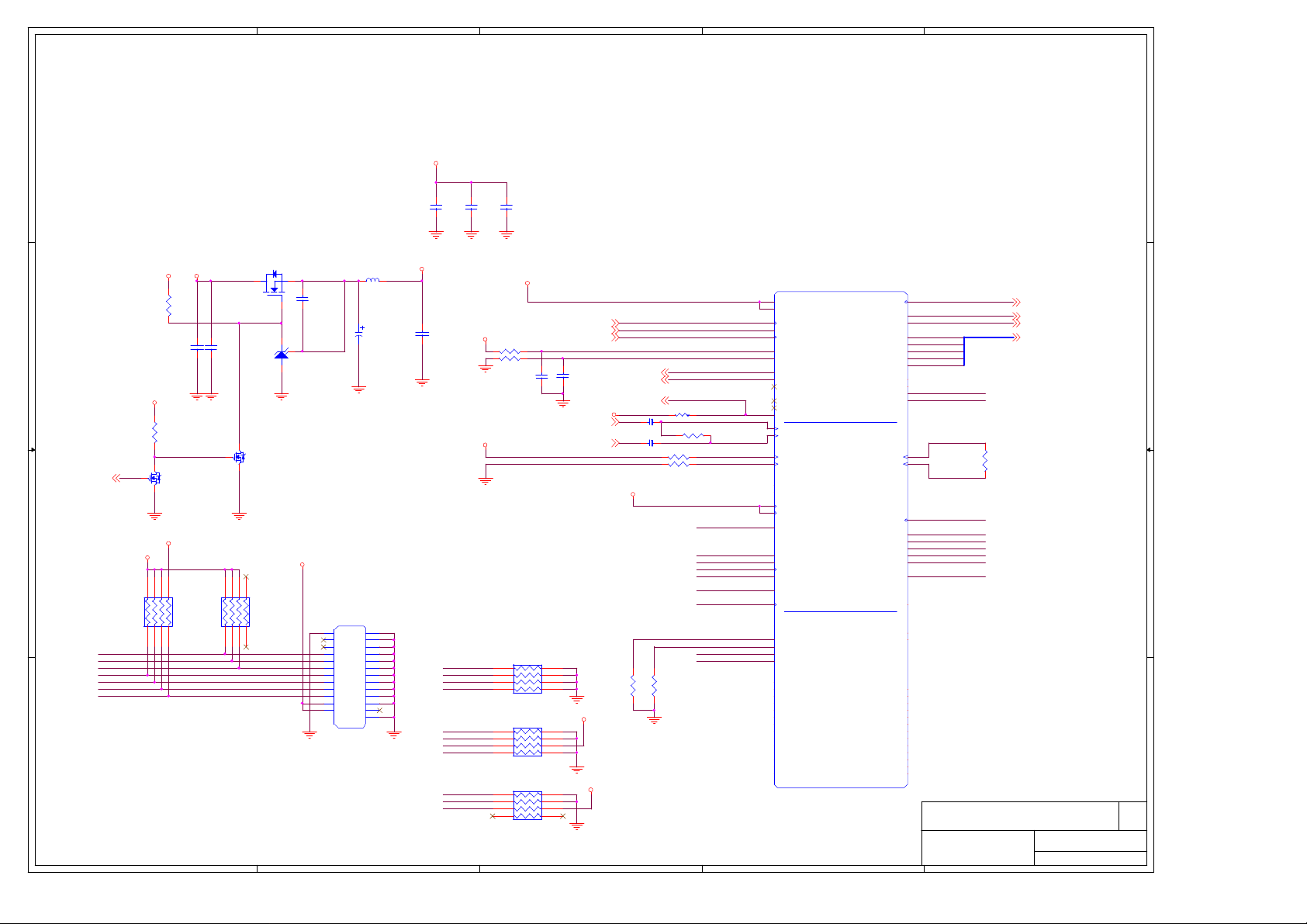

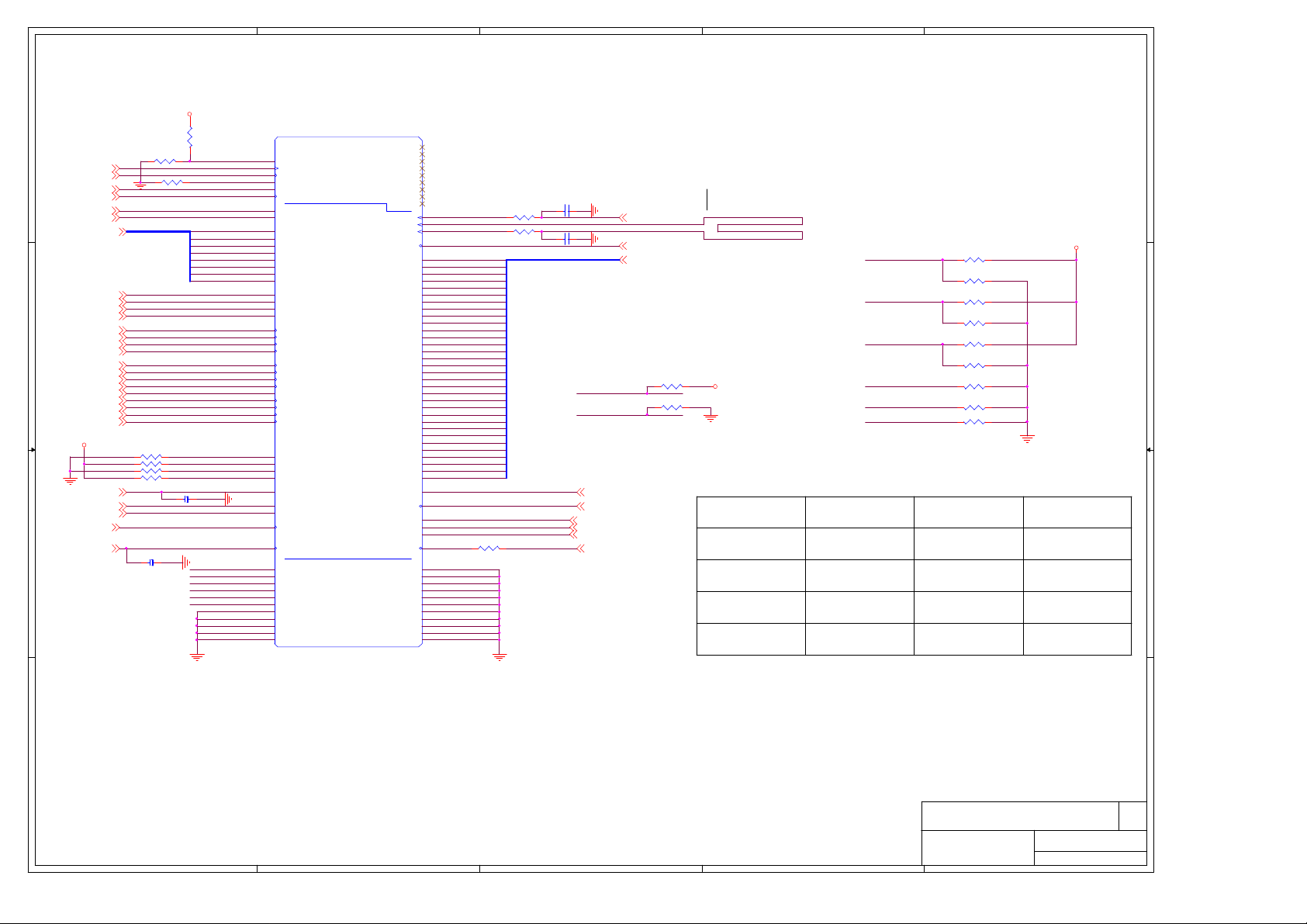

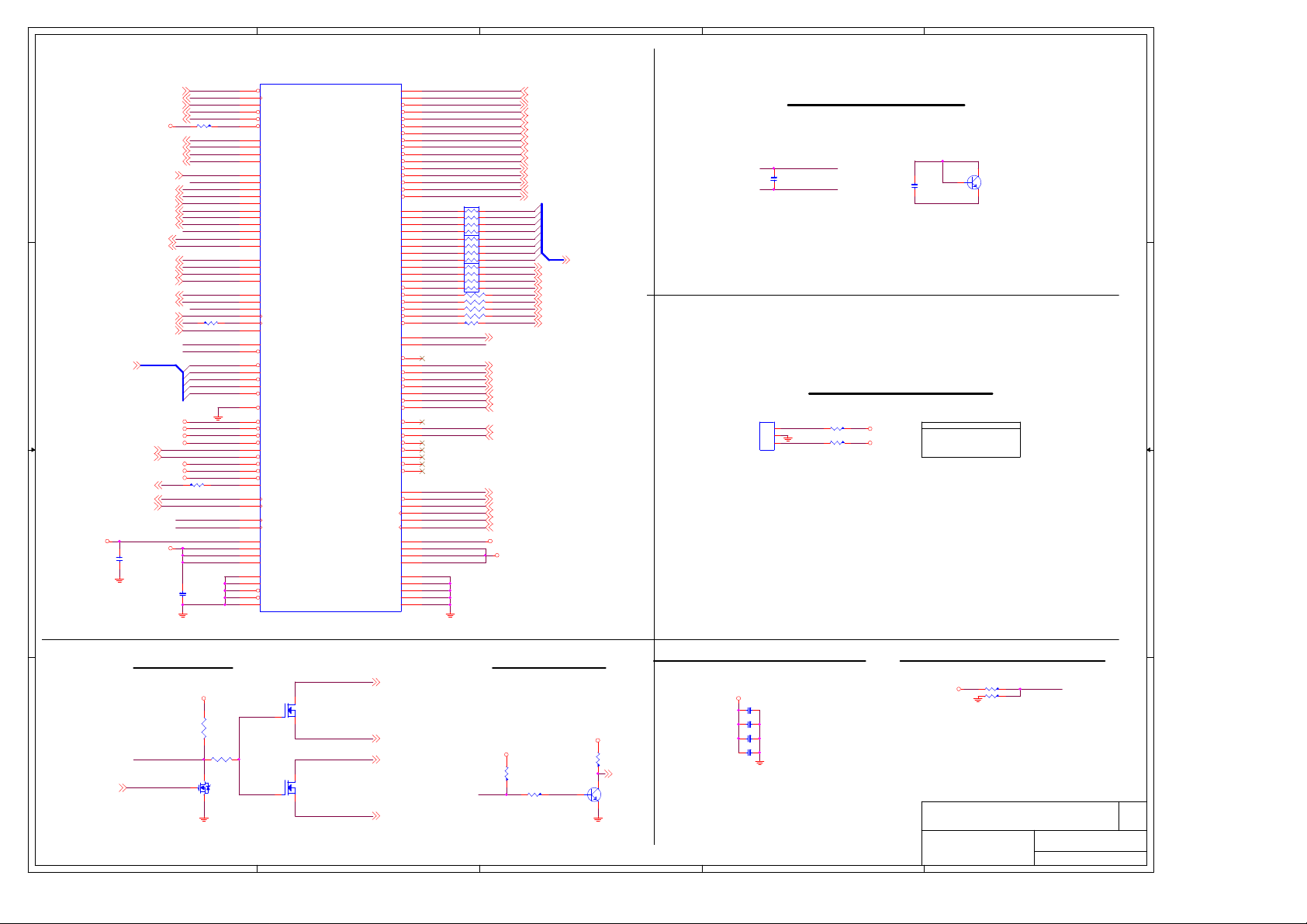

MS-6589 uATX

Title Page

Cover Sheet 1

Block Diagram

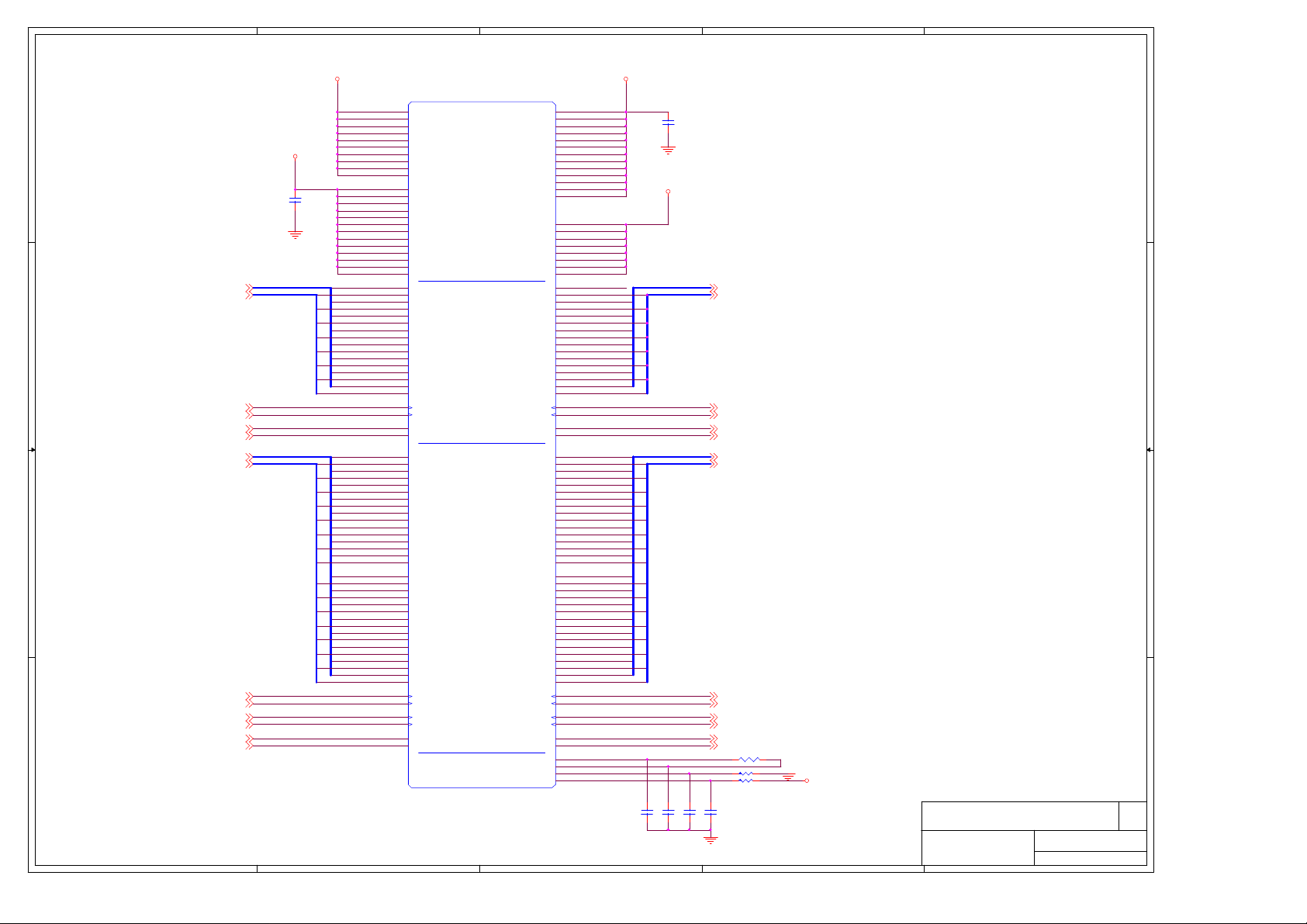

AMD Clawhammer

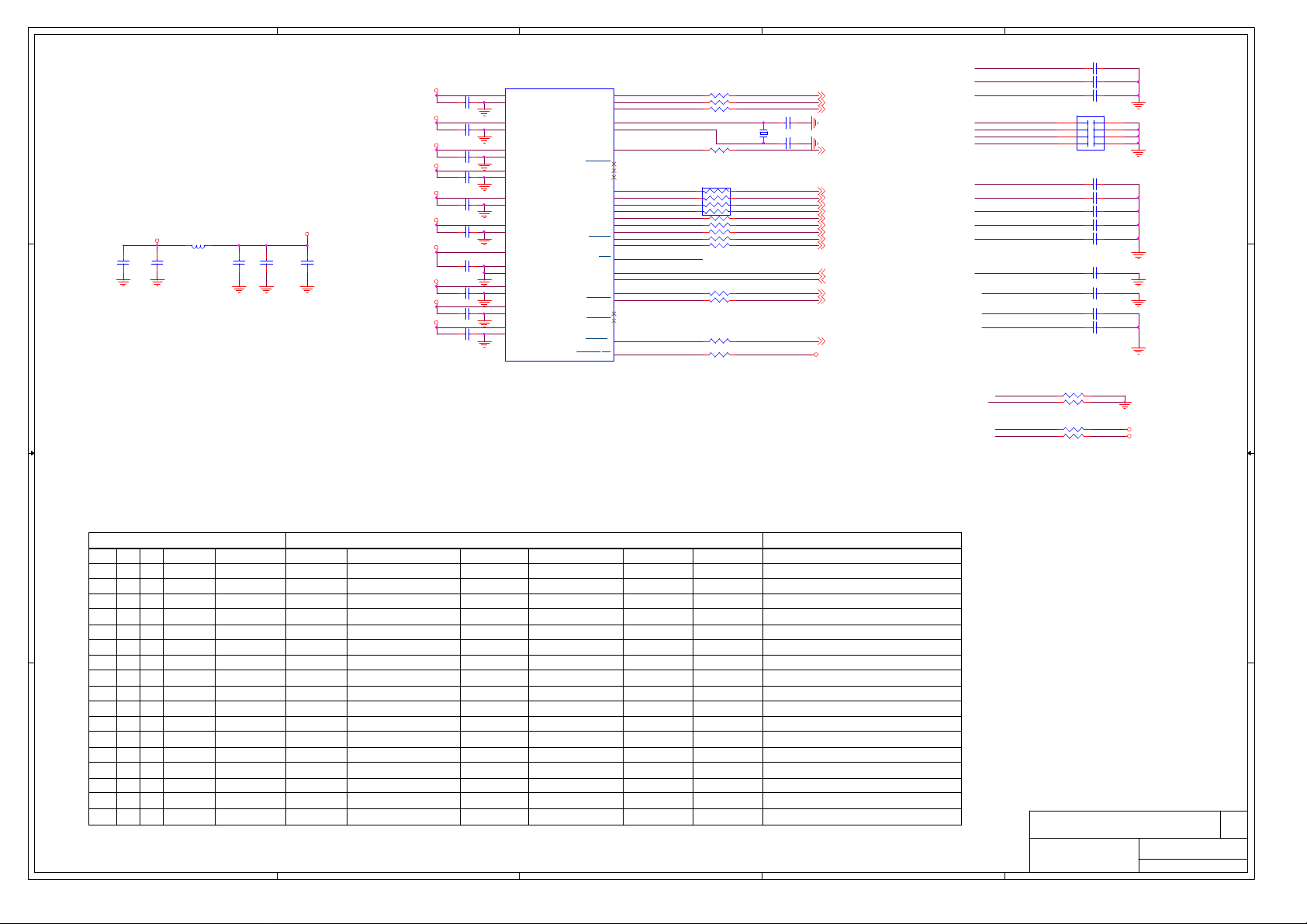

Clock Synthesizer 7

AMD Lokar

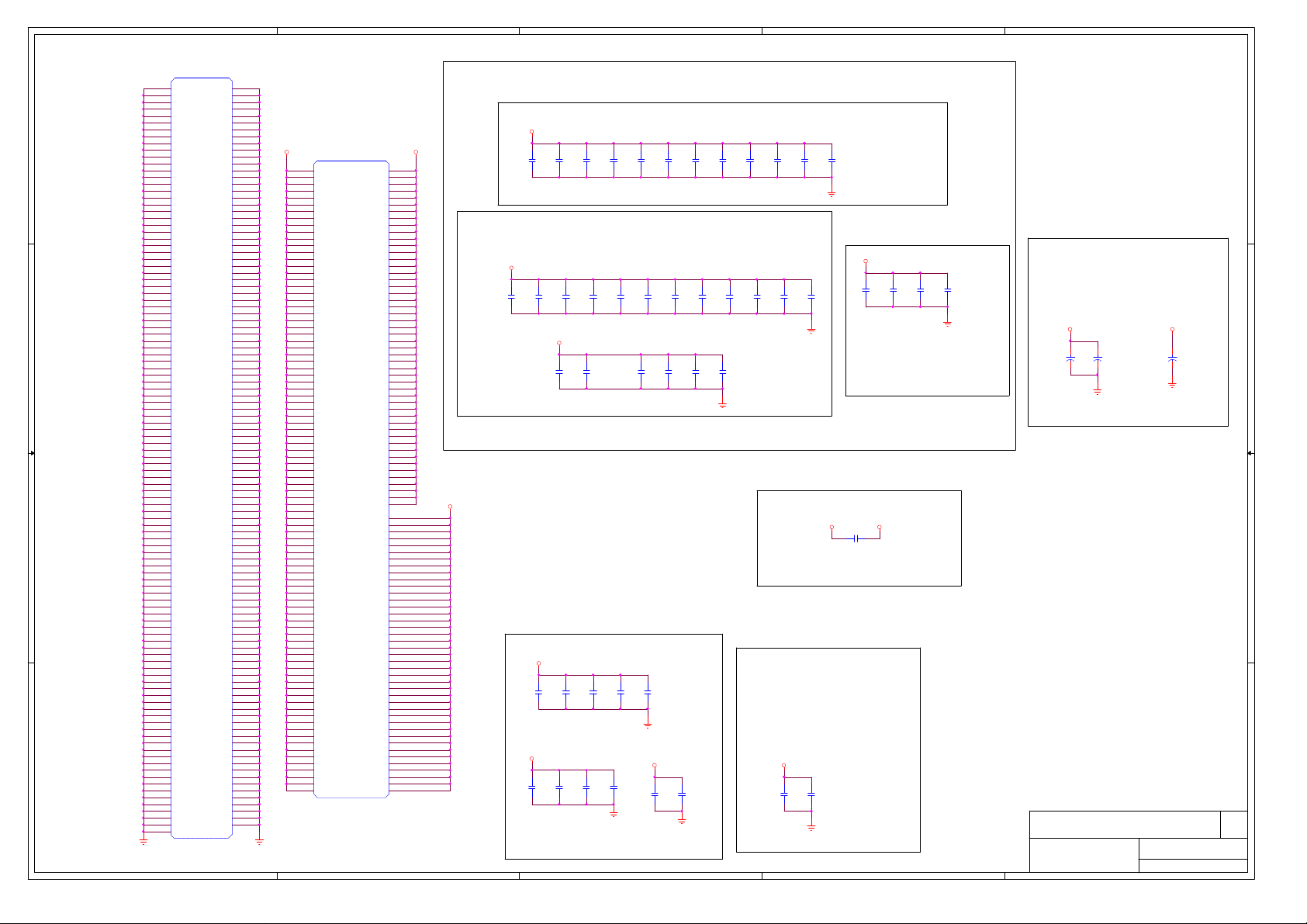

System Memory

DDR Terminations

C C

AGP 8X SLOT 15

AMD Thor

PCI Connectors

AC'97 Codec

AUDIO PORT

Gigabit LAN

USB Port

IDE Connectors

LPC I/O & H/W mornitor

System ROM

B B

Dual Power & AGP Power

PWROK & USB PWR & ATX CONN.

Front Panel and FAN

Pull-up resistors

BULK / Decopuling

K8 Core Power

NEC USB 2.0 Controller

Menu Parts

2

3History

4,5,6

8,9,10

11,12

13,14

16,17,18

19,20

21

22

23

24

25

26

27

28I/O Connectors

29DDR Power & HT Power

30

31

32

33

34

35

36

37

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

1

Cover Sheet

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

1 36

of

Rev

20

5

D D

32

25

VCC

VDD

1

U24_1

VPP

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RFU

CE

GND

GND1

27

3

4

5

6

7

8

9

2

VCCA

CLK

MODE

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

RESET_L

WE_L

OE_L

C C

31

29

30

10

11

12

23

24

B B

4

PCB

21

20

19

18

17

15

14

13

22

28

16

26

_

JAUD1(5-6)

1

2

JC-D2-GN-SB

JBAT1(1-2)

1

2

JC-D2-GN-SB

3

COM1

COMPORT

JAUD1(3-4)

1

2

JC-D2-GN-SB

JROM(1-2)

1

2

JC-D2-GN-SB

VBAT1-1

HS1

_

2

1

HS2

_

A A

Title

Size Document Number Rev

5

4

3

Date: Sheet of

<Title>

<Doc> <RevCode>

A

2

1 1Thursday, August 22, 2002

1

5

4

3

2

1

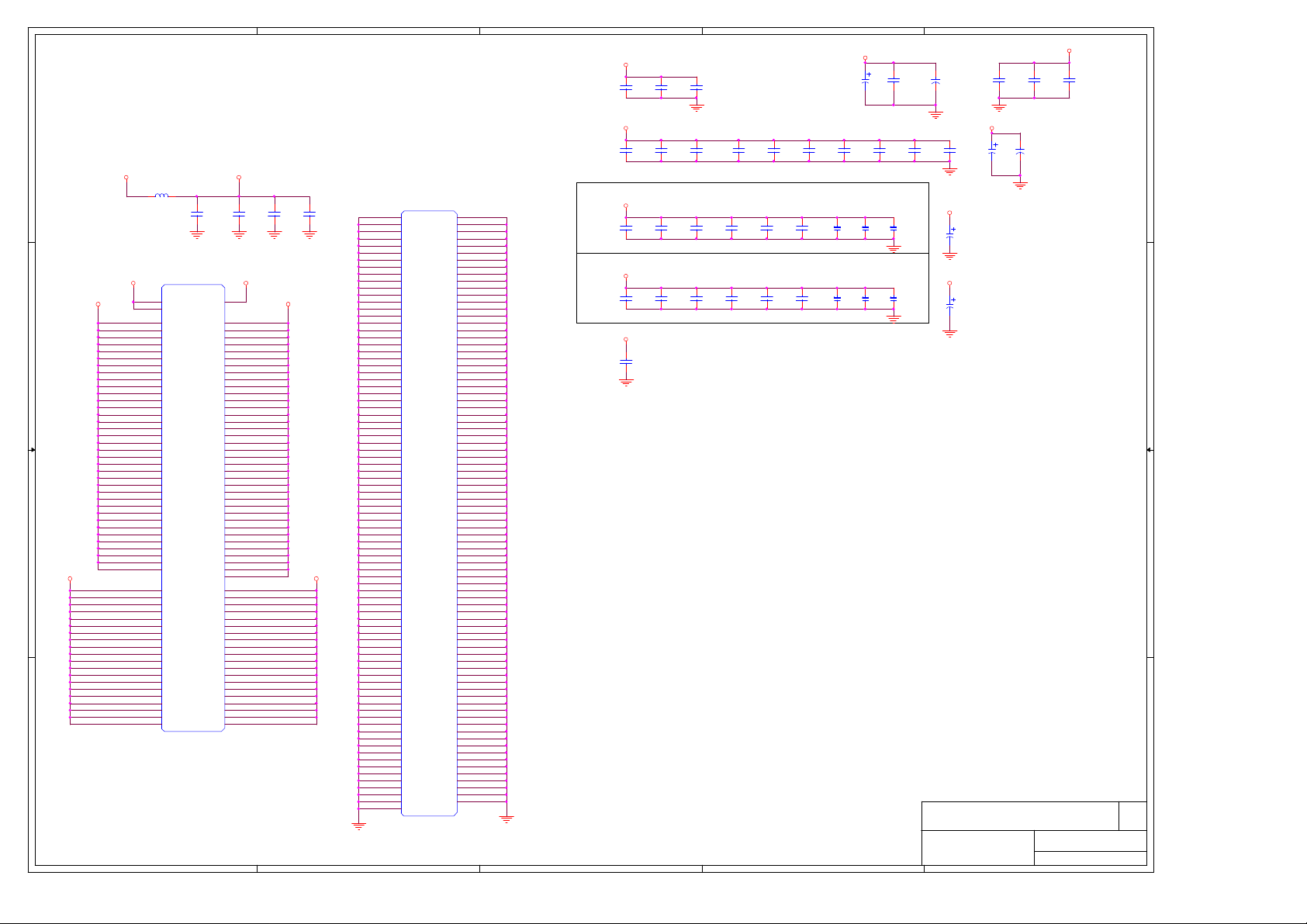

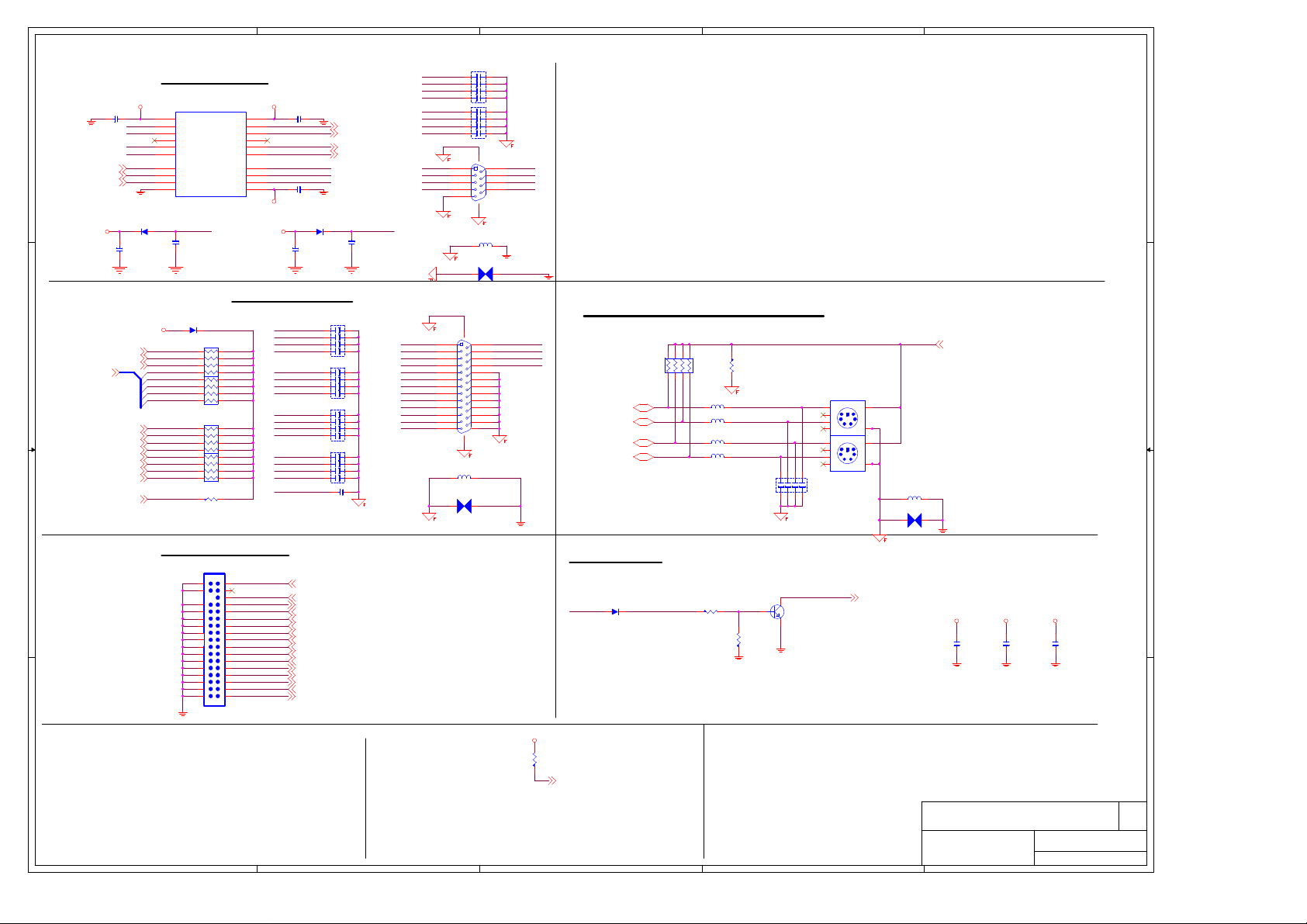

Block

Diagram

D D

System Functional Blocks

Clock Generator

Clawhammer

Power Supplies

C C

B B

System Management

BCM5702

NEC USB2.0

PCI Slots x4

32b/33MHz

LINK 0

LINK 1

IN

IN

16x16

OUT

Lokar

8x8

OUT

Thor

Unbuffered

DDR333 SDRAM

8X AGP Port

EIDE (ATA/133) x2

USB 2.0 x6

USB Ports: 2 to backplane,

4 to header

AC'97 Audio

ATX P.S.U

VCC

VCC5_SB

VCC3

+12V

ISL6525

MOSFET

YLT1084

+

MOSFET

ISL6525

LM358MX

(OP + MOS)

TL431L

ISL6569

78L05

VDD_18

VCC5_DUAL

VCC3_SB

VDD_12_A

VDD_15

VDDA_PLL

VDD_CORE

+5VR

ISL6525

VDD18_SB

EZ1117A

TL431L

VDD_25_SB

VTT_DDR_SUS

VDD_25_SUS

SWITCH

(45N02)

VDD_25

Power up:

1. VDDA_PLL after POK vaild.

LPC ROM

A A

5

LPC

LPC Super I/O

Floppy Disk Drive

PS/2 Keyboard & Mouse

Parallel & Serial Port

4

3

2. VDDA_PLL before VDD_CORE.

3. VDD_25_SUS before VDD_CORE.

4. VTT_DDR_SUS before VDD_CORE.

5. VTT_DDR_SUS before or with VDD_25_SUS.

6. VDD_18 before VDD_12.

7. VDD_CORE before VDD_12.

Power down:

1. VDD_12 before VDD_CORE.

2. VDD_CORE before VDD_25_SUS.

3. VDD_25_SUS before or with VTT_DDR_SUS.

4. VDD_12 before or with VDD_18.

5. VDD_CORE before or with VDDA_PLL.

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

Block Diagram

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

2 36

Rev

20

of

5

4

3

2

1

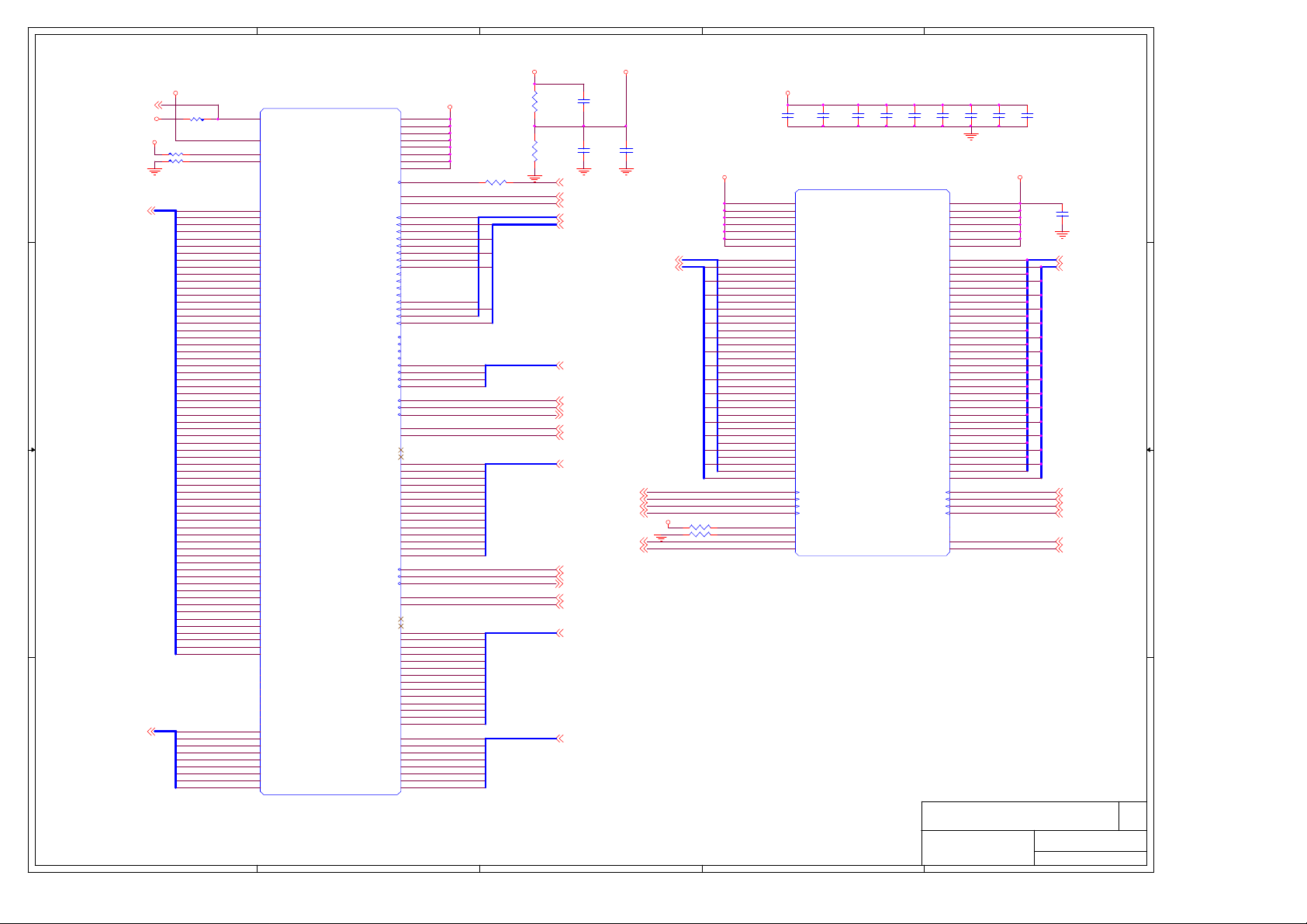

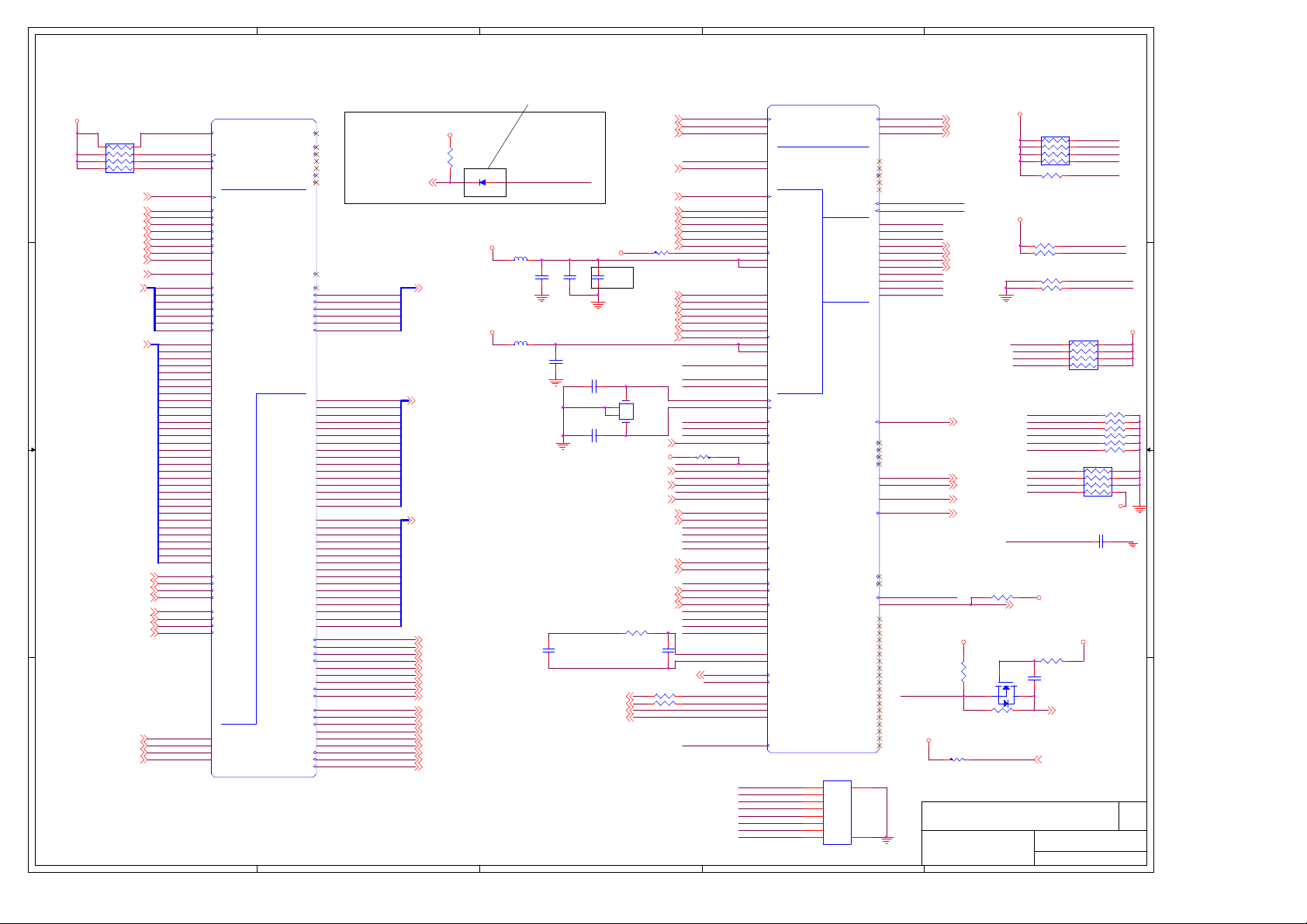

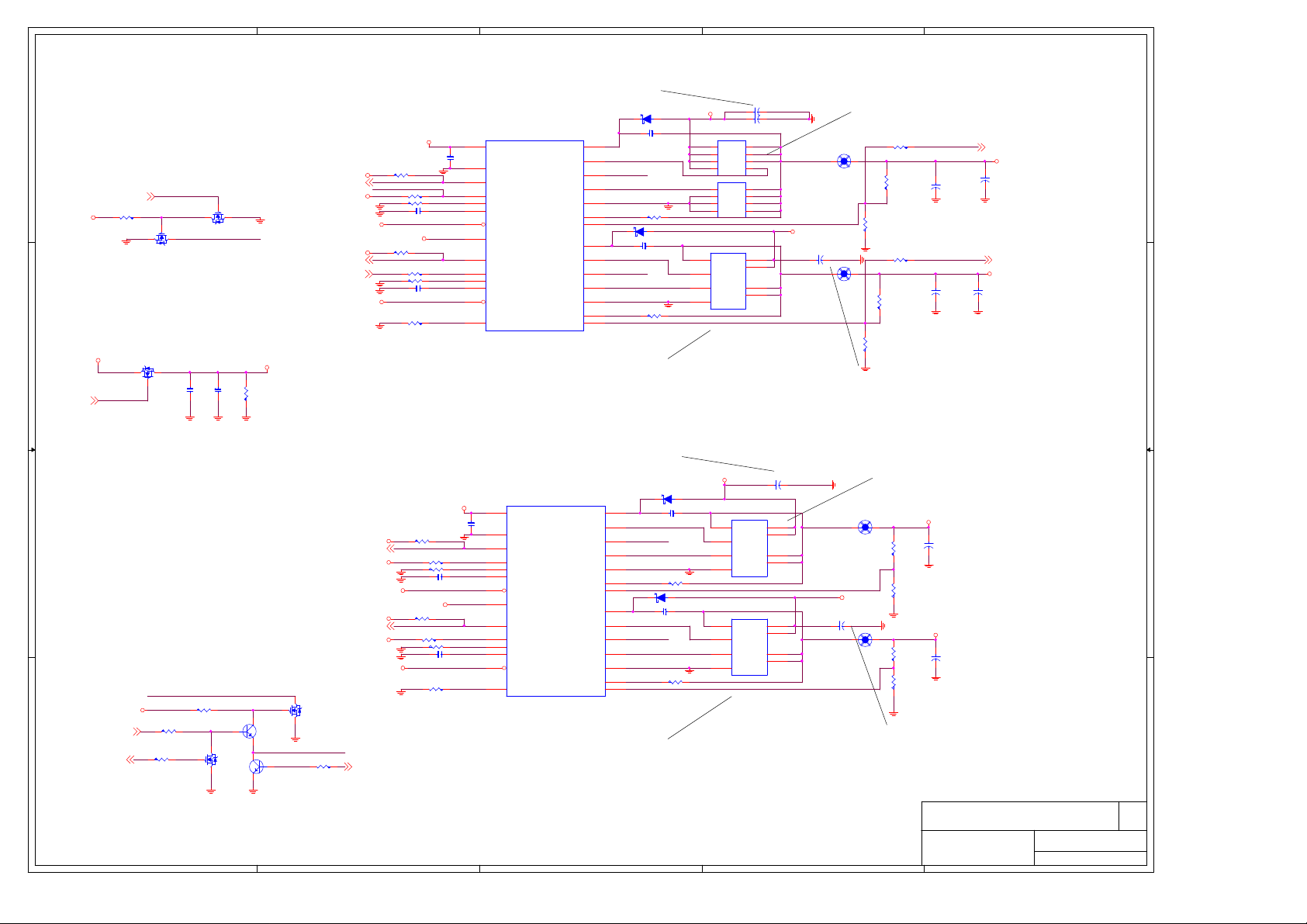

MS-6589 Rev.0A to Rev.2.0

1. Add NEC USB2.0 controller.

4. Remove F customer SPEC.

6. For AGP 8X Vref, AMD8151 output Vref=480mV, so, we need add extra Vref circurt show on page 15.

7. AGP feedback and main clock need to add a 33 ohms series resistor and a 10pF cap to implement SI and EMI.

D D

8. USB dual power fix.

C C

B B

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

GPIO Spec.

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

3 36

1

Rev

20

of

5

4

3

2

1

VREF_DDR_CLAWVDD_25_SUS

VREF_DDR_CLAW

VTT_SENSE29

VTT_DDR_SUS

D D

VDD_25_SUS

R556 51

R3 44.2RST

R4 34.8RST

MEMZN

MEMZP

AE13

AG12

D14

C14

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

U1B

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MD63

MD[63..0]14

C C

B B

-MDQS[8..0]14

A A

5

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

-MDQS8

-MDQS7

-MDQS6

-MDQS5

-MDQS4

-MDQS3

-MDQS2

-MDQS1

-MDQS0

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AH13

AJ13

A16

B15

A12

B11

A17

A15

C13

A11

A10

C7

C11

C5

G2

G1

G3

M1

W1

W3

AC1

AC3

W2

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

A13

C2

AA1

AG1

AH7

A14

D1

AB1

AJ2

AJ8

B9

A6

A9

A5

B5

A4

E2

E1

A3

B3

E3

F1

L3

L1

J2

L2

Y1

R1

A7

H1

T1

A8

J1

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

MEMORY INTERFAC E

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

RSVD_MEMADDA15

RSVD_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

4

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

VTT_DDR_SUS

MEMRESET

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

-MCS3

-MCS2

-MCS1

-MCS0

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

MCKE0

MCKE1

-MSRASA

-MSCASA

R5 X_0

-MCS[3..0]

R1

100RST

R2

100RST

MEMRESET_L 11,12

MCKE0 11,12,13

MCKE1 11,12,13

MEMCLK_H[7..0] 11,12,13

MEMCLK_L[7..0] 11,12,13

-MCS[3..0] 11,12,13

-MSRASA 11,13

-MSCASA 11,13

-MSWEA 11,13

MEMBANKA1 11,13

MEMBANKA0 11,13

MAA[13..0] 11,13

-MSRASB 12,13

-MSCASB 12,13

-MSWEB 12,13

MEMBAKB1 12,13

MEMBAKB0 12,13

MAB[13..0] 12,13

MEMCHECK[7..0] 14

C1

104P

C2

C746

104P

1000P

VDD_12_A

R6 49.9RST

R7 49.9RST

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CADIN_H[0..15]8

L0_CADIN_L[0..15]8 L0_CADOUT_L[0..15] 8

L0_CLKIN_H18

L0_CLKIN_L18

L0_CLKIN_H08

L0_CLKIN_L08

L0_CTLIN_H08

L0_CTLIN_L08

3

VLDT0

VDD_12_A

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

C810

0.22u

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

2

C811

C812

0.22u

0.22u

U1A

HYPER TRANSPORT - LINK0

C814

C813

0.22u

0.22u

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C815

0.22u

C816

0.22u

C817

0.22u

C818

0.22u

VLDT0

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2L0_CADIN_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

C747

4.7u/1206

L0_CADOUT_H[0..15] 8

L0_CLKOUT_H1 8

L0_CLKOUT_L1 8

L0_CLKOUT_H0 8

L0_CLKOUT_L0 8

L0_CTLOUT_H0 8

L0_CTLOUT_L0 8

Micro Star Restricted Secret

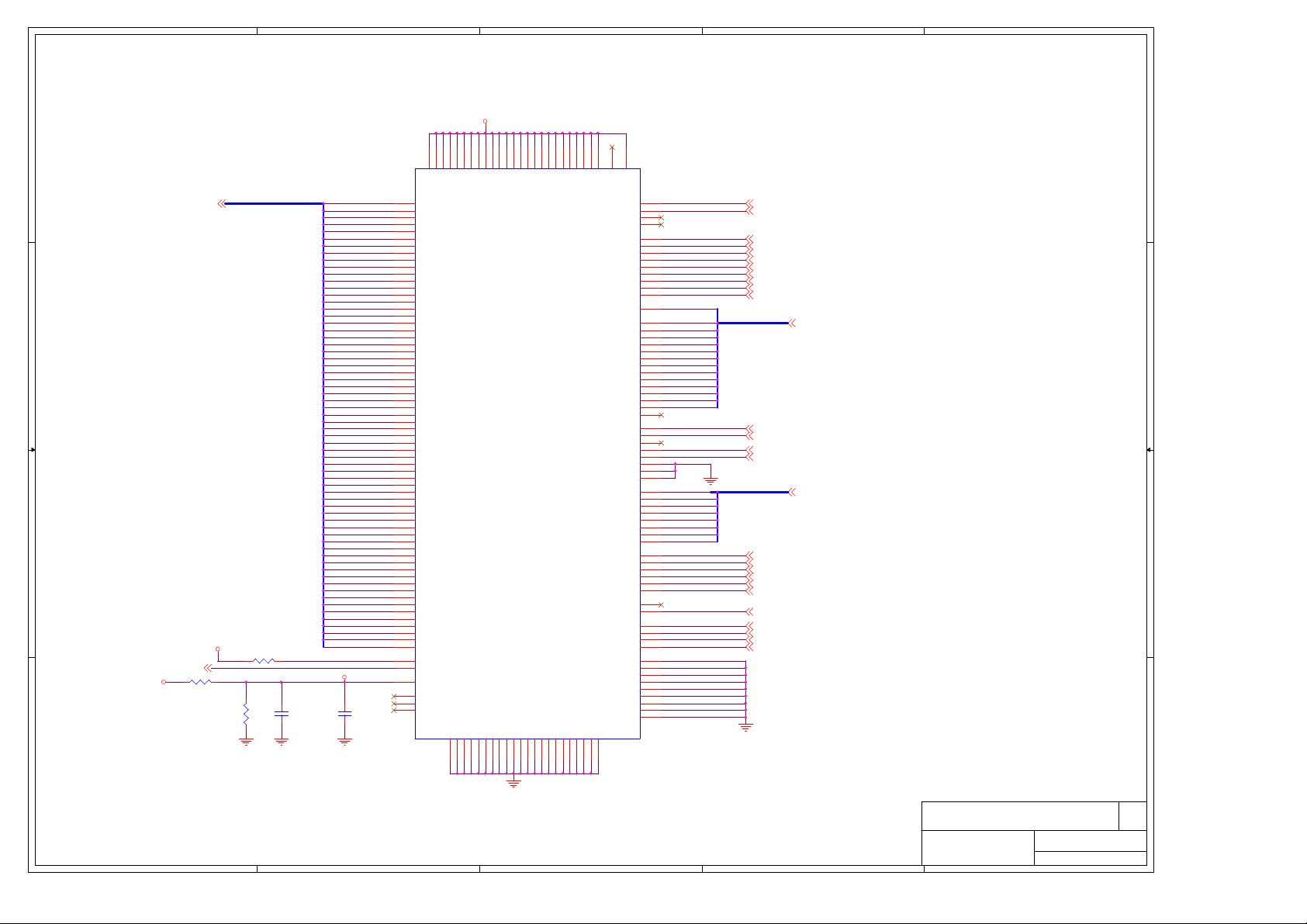

K8 DDR & HT

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

4 36

1

Rev

20

of

5

4

3

2

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

1

Place al filters close to the PGA.

Keep all power and signal trce away from

D D

VCCA_PLL

C5

C4

39P

3300p

C6

0.22u

the VR1.

Place a cut in the GND plane around the

VCCA_PLL regulator circuit.

Q1

VCCA_CTRL

C10

39P

123456

NDS351AN-S-SOT23

D

78

RN121

X_8P4R-1K

S

G

2

YREG431LS

3 1

VDD_25

VCCA_PL

VCCA_REF

VR1

C7

1000P

1

3

5

7

9

11

13

15

17

19

21

23

FB33

A

C748

JHDT

KEY

X_ASP-68200-07

+12V

VCC3

R9

1K

C C

VDD_PWGD_231,35

YFET-NDS7002AS

B B

DBREQ_L

DBRDY

TCK

TMS

TDI

TRST_L

TDO

A A

VCC5_SB

Q91

VDD_25_SUS

VDD_25

123456

5

C9

4.7u/0805

R747

1K

PLL_CTRL

Q90

YFET-NDS7002AS

HDT Connectors

78

RN120

X_8P4R-1K

100u/10V

4

180nH/1210

2

4

6

8

10

12

14

16

18

20

22

24

26

VCCA_PLL

C8

4.7u/0805

VDD_25_SUS

NC_AJ18

NC_AG17

NC_AF21

NC_AF22

NC_C19

NC_D20

NC_C18

NC_D18

NC_C21

NC_B19

NC_A19

VLDT0

R11 44.2RST

R12 44.2RST

VCCA_PLL

C11

1000P

RN122

8P4R-1K

RN123

8P4R-1K

RN124

8P4R-1K

LAYOUT: Route VDDA trace approx.

50 mils wide (use 2x25 mil traces to

exit ball field) and 500 mils long.

RESET_CPU_L16

ALL_POWERGOOD9,17,31

HTSTOP_L9,16

3

COREFB35

COREFB_L35

VDDIO_SENSE29

C13 3900P

C14 3900P

VTT_DDR_SUS

R14 1K

R16 1K

R26

1K

R557 51

R27

1K

12

34

56

78

12

34

56

78

12

34

56

78

C12

1000P

VDD_25_SUS

CPUCLK0_H7

CPUCLK0_L7

VDD_25

VDD_25

L0_REF1

L0_REF0

VDDIO_SENSE

CLKIN_H

R13 169RST

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

CLKIN_L

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

AG15

AH17

AJ28

AE23

AF23

AF22

AF21

AE21

A23

A24

B23

C16

C15

E20

E17

B21

A21

C18

A19

A28

AA2

AG2

B18

AH1

C20

AG4

AG6

AE9

AG9

C1

J3

R3

D3

C6

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VTT_A5

VTT_B5

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY1

KEY0

NC_AE23

NC_AF23

NC_AF22

NC_AF21

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

U1C

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

A20

A26

A27

AG13

AF14

AG14

AF15

AE15

AG18

AH18

AG17

AJ18

VID4

VID3

VID2

VID1

VID0

NC_AG17

NC_AJ18

THERMTRIP_CPU_L 17

THERMDA_CPU 26

THERMDC_CPU 26

VID[4..0] 26,35

LAYOUT: Route FBCLKOUT_H/L

FBCLKOUT_H

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

TDO

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

Title

Document Number

FBCLKOUT_L

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

G_FBCLKOUT_H

G_FBCLKOUT_L

2

differentially with 20/8/5/8/20

spacing and trace width.

R15

80.6RST

Micro Star Restricted Secret

K8 HDT & MISC

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

5 36

1

of

Rev

20

5

U1E

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

AA10

AE16

AA20

AC20

AE20

AG20

AJ20

AD21

AG21

AG29

AA22

AC22

AG22

AH22

AJ22

AB23

AD23

AG23

AA24

AC24

AG24

AJ24

AD26

AF26

AH26

AB17

AD17

AA18

AC18

AB19

AD19

AF19

D2

VSS10

AF2

VSS11

W6

VSS12

Y7

VSS13

AA8

VSS14

AB9

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

G20

VSS22

R20

VSS23

U20

VSS24

W20

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

D21

VSS31

F21

VSS32

H21

VSS33

K21

VSS34

M21

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

G22

VSS44

J22

VSS45

L22

VSS46

N22

VSS47

R22

VSS48

U22

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

D23

VSS56

F23

VSS57

H23

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

G24

VSS68

J24

VSS69

N24

VSS70

R24

VSS71

U24

VSS72

W24

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

C25

VSS79

B26

VSS80

D26

VSS81

H26

VSS82

M26

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

C27

VSS89

B28

VSS90

D28

VSS91

G28

VSS92

F15

VSS187

H15

VSS188

VSS206

VSS207

B16

VSS208

G18

VSS209

VSS210

VSS211

D19

VSS212

F19

VSS213

H19

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

N20

VSS222

GROUND

5

D D

C C

B B

A A

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

GNDGND

VDD_CORE

AC15

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

AA21

AC21

AB22

AD22

AA23

AC23

AB24

AD24

AH24

AE25

U1D

L7

VDD1

VDD2

H18

VDD3

B20

VDD4

E21

VDD5

H22

VDD6

J23

VDD7

H24

VDD8

F26

VDD9

N7

VDD10

L9

VDD11

V10

VDD12

G13

VDD13

K14

VDD14

Y14

VDD15

VDD16

G15

VDD17

J15

VDD18

VDD19

H16

VDD20

K16

VDD21

Y16

VDD22

VDD23

G17

VDD24

J17

VDD25

VDD26

VDD27

VDD28

F18

VDD29

K18

VDD30

Y18

VDD31

VDD32

VDD33

VDD34

E19

VDD35

G19

VDD36

VDD39

VDD38

J19

VDD37

F20

VDD40

H20

VDD41

K20

VDD42

M20

VDD43

P20

VDD44

T20

VDD45

V20

VDD46

Y20

VDD47

VDD48

VDD49

G21

VDD50

J21

VDD51

L21

VDD52

N21

VDD53

R21

VDD54

U21

VDD55

W21

VDD56

VDD57

VDD58

F22

VDD59

K22

VDD60

M22

VDD61

P22

VDD62

T22

VDD63

V22

VDD64

Y22

VDD65

VDD66

VDD67

E23

VDD68

G23

VDD69

L23

VDD70

N23

VDD71

R23

VDD72

U23

VDD73

W23

VDD74

VDD75

VDD76

B24

VDD77

D24

VDD78

F24

VDD79

K24

VDD80

M24

VDD81

P24

VDD82

T24

VDD83

V24

VDD84

Y24

VDD85

VDD86

VDD87

VDD88

VDD89

K26

VDD90

P26

VDD91

V26

VDD92

POWER

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

4

VDD_25_SUS

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

of HT link, and 12 along

VDD_CORE

3

EMI

VDD_CORE

C22

6.8pF

6.8pF

6.8pF

C25

C24

C23

6.8pF

C27

6.8pF

6.8pF

C28

6.8pF

C26

LAYOUT: Place 6 EMI capsalong bottom right side of Clawhammer, 2 in middle

X_6.8pF/BOT

C71

<nopop>

X_6.8pF/BOT

0.22u

C96

X_0.22uF

C51

X_6.8pF/BOT

C97

<nopop>

GND

hammer.

C52

X_6.8pF/BOT

C72

<nopop>

X_6.8pF/BOT

<nopop>

X_0.22uF

<nopop>

VDD_CORE

C44

X_6.8pF/BOT

bottom left side of Claw-

C47

C46

X_6.8pF/BOT

VDD_CORE

C67

LAYOUT: Place beside processor.

VDD_25_SUS

C39

C38

0.22u

VDD_25_SUS

C62

C61

4.7u/0805

X_6.8pF/BOT

C68

<nopop>

X_6.8pF

0.22u

C63

4.7u/0805

C48

X_6.8pF/BOT

C40

4.7u/0805

C49

X_6.8pF/BOT

<nopop>

C41

0.22u

C64

GND

X_6.8pF/BOT

C70

0.22u

VDD_25_SUS

4.7u/0805

3

C50

C43

GND

LAYOUT: Place 1 capacitor every 1-1.5"

along VDD_CORE perimiter.

C30

6.8pF

C54

X_6.8pF/BOT

<nopop>

X_6.8pF/BOT

C33

6.8pF

X_6.8pF/BOT

C55

6.8pF

X_6.8pF/BOT

6.8pF

C56

GND

C29

C53

X_6.8pF/BOT

C73

GND

C34

LAYOUT: Place on backside of processor.

VDD_25_SUS VTT_DDR_SUS

LAYOUT: Place beside DDR slots.

VDD_25_SUS

C66

C65

4.7u/0805

GND

2

C37

6.8pF

GND

VDD_CORE

C76

C75

C74

1000P

1000P

X_6.8pF/BOT

LAYOUT: Place 1000pF capacitors

between VRM & CPU.

C132

X_0.22uF

<nopop>

4.7u/0805

2

1

NOTE: Populate 270uF

caps or 100uF caps

C77

1000P

1000P

GND

in these footprints.

VDD_25_SUS

+

EC26

100u-16V

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

+

EC27

100u-16V

GND

Micro Star Restricted Secret

K8 POWER & GND

VDD_25_SUS

EC28

100u-16V

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

1

+

GND

6 36

of

Rev

20

5

4

3

2

1

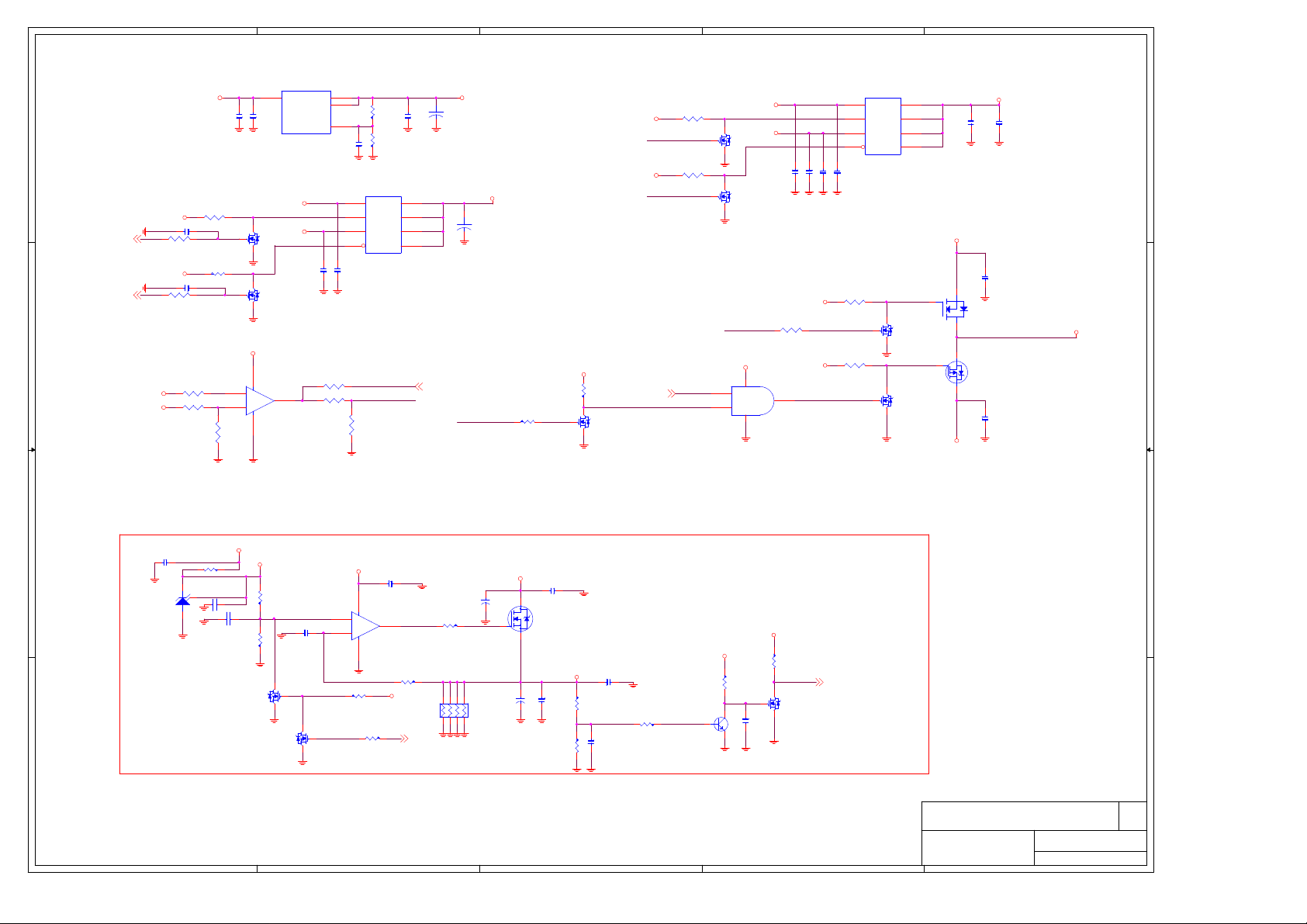

Clock Synthesizer

CLKVCC3

C133 104P

CLKVCC3

C135 104P

D D

C143

4.7u/0805

CLKVCC3

C144

104P

VCC3

FB1 120S/0805

C141

C140

104P

39P

C C

C142

39P

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

C139 104P

C147 104P

C149 104P

C150 104P

C151 104P

C152 104P

C153 104P

C154 104P

U6

46

VDD_46

47

VSS_47

2

VDD_2

5

VSS_5

32

VDDF

33

VSSF

PCI33_HT66_1/PCI33_HT66SEL1

9

VDD_9

10

VSS_10

16

VDD_16

15

VSS_15

19

VDD_19

20

VSS_20

29

VDD_29

30

VSS_30

27

VSS_27

38

VDD_38

39

VSS_39

35

VDD_35

34

VSS_34

43

VDDA

42

VSSA

PCI33_HT66_0/PCI33_HT66SEL0

PCI33_HT66_2

PCI33_HT66_3

PCI_SEL/PCI33_F

PCI33_6/PCISTOP

24_48MHZ/SEL

CY28331

FS0/REF0

FS1/REF1

FS2/REF2

XOUT

48MHZ/FS3

PCI33_0

PCI33_1

PCI33_2

PCI33_3

PCI33_4

PCI33_5

PCI33_7

SDATA

SCLK

CPUT_0

CPUC_0

CPUT_1

CPUC_1

SRESET/PD

X1

14.318MHZ

SB_OSC14

CODEC_14

SIO_14M

C134 10P

C137 10P

USBCLK

PCICLK1

PCICLK2

PCICLK4

PCICLK3

SB_PCLK

FWH_PCLK

SIO_PCLK

USB_PCLK

LAN_PCLK

HTCLK

SB_OSC14 16

CODEC_14 21

SIO_14M 26

USBCLK 17

PCICLK1 19

PCICLK2 19

PCICLK4 20

PCICLK3 20

SB_PCLK 17

FWH_PCLK 27

SIO_PCLK 26

USB_PCLK 36

LAN_PCLK 23

SMBDATA1 11,12,26,33

SMBCLK1 11,12,26,33

CPUCLK0_H 5

CPUCLK0_L 5

HTCLK 9

CLKVCC3

FS0

1

FS1

48

FS2

45

CLKX1

3

XIN

CLKX2

4

48MHz

31

7

8

11

R_PCICLK1

13

R_PCICLK2

14

R_PCICLK3

17

R_PCICLK4

18

R_PCLCLKF

23

R_PCICLK5

21

R_PCICLK6

22

R_PCICLK7

24

R_PCICLK8

12

SEL_24

28

SMBDATA1

26

SMBCLK1

25

R_CPU_CLK

41

-R_CPU_CLK

40

37

36

HT_66

6

SPREAD

44

R40 33

R41 33

R47 33

R42 33

RN1 8P4R-33

7 8

5 6

3 4

1 2

R630 33

R38 33

R37 33

R46 33

R39 33

R48 15RST

R49 15RST

R43 22

R55 10K

SIO_14M

SB_OSC14

CODEC_14

PCICLK1

PCICLK2

PCICLK4

PCICLK3

SIO_PCLK

FWH_PCLK

SB_PCLK

USB_PCLK

LAN_PCLK

USBCLK

HTCLK

CPUCLK0_H

CPUCLK0_L

SEL_24

R_PCLCLKF

FS2

FS1

C863 X_5P

C859 X_5P

C860 X_5P

CN25

X_8P4C-22P

C902 X_5P

C903 X_5P

C904 X_5P

C861 X_5P

C862 X_5P

C952 X_5P

C865 X_5P

C136 X_5P

C138 X_5P

R50 X_10K

R51 10K

R52 X_10K

R53 X_10K

12

34

56

78

CLKVCC3

CLKVCC3

Input Configuration

FS0

1

0

1

0

1

0

1

1

0

X

X

X

X

X

X

X

X

PCI_HT#

X

X

X

X

X

1

0

X

0

1

X

X

0

0

1

1

5

FS1

B B

FS2

1

1

1

1

1

0

1

0

1 -

0

1

0

0

0

0

0

0

X

X

X

X

X

X

X

A A

X

X

X

X

X

X

X

X 24 or 48100,133.33,166.66,200

PCISTOP#

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

0

1

Clock Generator Output

24_48SEL#

X

X

X

X

CPU (MHz)

200

166.66

133.330

100

X

X

X

X

X

X

X

1

0

X

X

X

- -

X1 input

X1 input

Hi-Z

100,133.33,166.66,200

100,133.33,166.66,200

100,133.33,166.66,200

100,133.33,166.66,200

100,133.33,166.66,200

100,133.33,166.66,200

100,133.33,166.66,200X

X

PCI33 (MHz)

33.33

33.33

33.33

33.33

-

PCI33_HT66 (MHz)

33.33 or 66.66

33.33 or 66.66

33.33 or 66.66

33.33 or 66.66

-

X1/6

X1/6

Hi-Z

33.33

33.33

33.33 24

33.33

0

33.33

0

33.33

4

X1/6

X1/3

Hi-Z

66.66

33.33

33.33 or 66.66

33.33 or 66.66

66.66

66.66

0

33.33

24_48 (MHz)

24 or 48

24 or 48

24 or 48

24 or 48

-

0

0

Hi-Z

24 or 48

24 or 48

48

24 or 48

24 or 48

24 or 48

3

14.318 (MHz)

14.318

14.318

14.318

14.318

-X

0

0

Hi-Z

14.318

14.318

14.318

14.318

14.318

14.318

14.318

14.318

Comment

Normal Hammer operation

Reserved

Athlon compatible

Athlon compatible

Reserved

Reserved

Bypass mode

Bypass mode

Tri-state mode

33.33 vs. 66.66 MHz output select

33.33 vs. 66.66 MHz output select

24 vs. 48 MHz output select

24 vs. 48 MHz output select

PCISTOP vs. 33.33/66.66 MHz selects

PCISTOP vs. 33.33/66.66 MHz selects

PCISTOP vs. 33.33/66.66 MHz selects

PCISTOP vs. 33.33/66.66 MHz selects

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Clock Synthesizer

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

1

7 36

of

Rev

20

5

4

3

2

1

VDD_12_A VDD_12_A1

J17

VLDT0_A10

H18

VLDT0_A9

H19

VLDT0_A8

H20

VLDT0_A7

D D

L1_CADIN_H[0..7]16

L1_CADIN_L[0..7]16

Link 1 Is Lokar <--> Thor

C C

L1_CLKIN_H16

L1_CLKIN_L16

L1_CTLIN_H16

L1_CTLIN_L16

L0_CADOUT_H[0..15]4

L0_CADOUT_L[0..15]4

Link 0 Is Clawhammer <--> Lokar

B B

L0_CLKOUT_H14

L0_CLKOUT_L14

L0_CLKOUT_H04

L0_CLKOUT_L04

L0_CTLOUT_H04

L0_CTLOUT_L04

A A

5

VDD_12_A0

C749

4.7u/1206

L1_CADIN_H7

L1_CADIN_L7

L1_CADIN_H6

L1_CADIN_L6

L1_CADIN_H5

L1_CADIN_L5

L1_CADIN_H4

L1_CADIN_L4

L1_CADIN_H3

L1_CADIN_L3

L1_CADIN_H2

L1_CADIN_L2

L1_CADIN_H1

L1_CADIN_L1

L1_CADIN_H0

L1_CADIN_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

G21

VLDT0_A6

F22

VLDT0_A5

E23

VLDT0_A4

D24

VLDT0_A3

C24

VLDT0_A2

B23

VLDT0_A1

H6

VLDT0_B10

G5

VLDT0_B9

G4

VLDT0_B8

F4

VLDT0_B7

G3

VLDT0_B6

F2

VLDT0_B5

E1

VLDT0_B4

D2

VLDT0_B3

C1

VLDT0_B2

B2

VLDT0_B1

J7

VLDT0_B11

J8

VLDT0_B12

J9

VLDT0_B13

R22

L1_CADIN_H7

R21

L1_CADIN_L7

T20

L1_CADIN_H6

R20

L1_CADIN_L6

U22

L1_CADIN_H5

U21

L1_CADIN_L5

V20

L1_CADIN_H4

U20

L1_CADIN_L4

V24

L1_CADIN_H3

U24

L1_CADIN_L3

V22

L1_CADIN_H2

V23

L1_CADIN_L2

Y24

L1_CADIN_H1

W24

L1_CADIN_L1

Y22

L1_CADIN_H0

Y23

L1_CADIN_L0

T22

L1_CLKIN_H0

T23

L1_CLKIN_L0

T24

L1_CTLIN_H0

R24

L1_CTLIN_L0

E14

L0_CADIN_H15

E13

L0_CADIN_L15

C15

L0_CADIN_H14

D15

L0_CADIN_L14

E16

L0_CADIN_H13

E15

L0_CADIN_L13

C17

L0_CADIN_H12

D17

L0_CADIN_L12

C19

L0_CADIN_H11

D19

L0_CADIN_L11

E20

L0_CADIN_H10

E19

L0_CADIN_L10

C21

L0_CADIN_H9

D21

L0_CADIN_L9

E22

L0_CADIN_H8

E21

L0_CADIN_L8

C14

L0_CADIN_H7

B14

L0_CADIN_L7

A16

L0_CADIN_H6

A15

L0_CADIN_L6

C16

L0_CADIN_H5

B16

L0_CADIN_L5

A18

L0_CADIN_H4

A17

L0_CADIN_L4

A20

L0_CADIN_H3

A19

L0_CADIN_L3

C20

L0_CADIN_H2

B20

L0_CADIN_L2

A22

L0_CADIN_H1

A21

L0_CADIN_L1

C22

L0_CADIN_H0

B22

L0_CADIN_L0

E18

L0_CLKIN_H1

E17

L0_CLKIN_L1

C18

L0_CLKIN_H0

B18

L0_CLKIN_L0

A14

L0_CTLIN_H0

A13

L0_CTLIN_L0

4

U2A

HYPER TRANSPORT LINK 0/1

VLDT1_A8

VLDT1_A7

VLDT1_A6

VLDT1_A5

VLDT1_A4

VLDT1_A3

VLDT1_A2

VLDT1_A1

VLDT1_A9

VLDT1_A10

VLDT1_A11

VLDT1_A12

VLDT1_A13

VLDT1_B8

VLDT1_B7

VLDT1_B6

VLDT1_B5

VLDT1_B4

VLDT1_B3

VLDT1_B2

VLDT1_B1

L1_CADOUT_H7

L1_CADOUT_L7

L1_CADOUT_H6

L1_CADOUT_L6

L1_CADOUT_H5

L1_CADOUT_L5

L1_CADOUT_H4

L1_CADOUT_L4

L1_CADOUT_H3

L1_CADOUT_L3

L1_CADOUT_H2

L1_CADOUT_L2

L1_CADOUT_H1

L1_CADOUT_L1

L1_CADOUT_H0

L1_CADOUT_L0

L1_CLKOUT_H0

L1_CLKOUT_L0

L1_CTLOUT_H0

L1_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

LDTCOMP3

LDTCOMP2

LDTCOMP1

LDTCOMP0

AA19

AB20

AB21

AA21

AB22

AA23

AC23

AB24

Y18

W17

V16

U16

T16

K18

J19

J20

J21

H22

G23

G24

F24

N20

P20

N21

N22

L20

M20

L21

L22

M23

M22

L24

M24

K23

K22

J24

K24

N24

P24

P23

P22

D11

C11

E9

E10

D9

C9

E7

E8

E5

E6

D5

C5

E3

E4

D3

C3

A11

A12

B10

C10

A9

A10

B8

C8

B6

C6

A5

A6

B4

C4

A3

A4

D7

C7

A7

A8

B12

C12

Y20

W22

W21

W20

L1_CADOUT_H7

L1_CADOUT_L7

L1_CADOUT_H6

L1_CADOUT_L6

L1_CADOUT_H5

L1_CADOUT_L5

L1_CADOUT_H4

L1_CADOUT_L4

L1_CADOUT_H3

L1_CADOUT_L3

L1_CADOUT_H2

L1_CADOUT_L2

L1_CADOUT_H1

L1_CADOUT_L1

L1_CADOUT_H0

L1_CADOUT_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

LOKAR_HTCOMP3

LOKAR_HTCOMP2

LOKAR_HTCOMP1

LOKAR_HTCOMP0

3

C750

4.7u/1206

VDD_12_A

C155

1000P

C156

1000P

C157

1000P/BOT

C158

1000P

L1_CADOUT_H[0..7] 16

L1_CADOUT_L[0..7] 16

L1_CLKOUT_H 16

L1_CLKOUT_L 16

L1_CTLOUT_H 16

L1_CTLOUT_L 16

L0_CADIN_H[0..15] 4

L0_CADIN_L[0..15] 4

L0_CLKIN_H1 4

L0_CLKIN_L1 4

L0_CLKIN_H0 4

L0_CLKIN_L0 4

L0_CTLIN_H0 4

L0_CTLIN_L0 4

R56 121RST

R57 56.2RST/BOT

R58 56.2RST

VDD_12_A

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

LOKAR HT

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

1

8 36

of

Rev

20

5

4

3

2

1

NOTE: Pulldown to enable automatic link compensation

VCC3

R59

R61 100

C159 3900P

X_100

LOKAR_CMPOVR

LOKAR_TEST

A_SBA7

A_SBA6

A_SBA5

A_SBA4

A_SBA3

A_SBA2

A_SBA1

A_SBA0

A_CALD

A_CALD_L

A_CALS

A_CALS_L

LOKAR_STRAP0

LOKAR_STRAP1

LOKAR_STRAP2

LOKAR_STRAP3

LOKAR_STRAP4

LOKAR_STRAP5

AC17

AB16

AC18

AA17

AD18

AB18

AC11

AD11

AD10

AB10

AA12

AA11

AD20

AB13

AA14

AD3

AC5

AB9

AA9

AB8

AA5

AA6

AB6

AA8

K1

K2

N2

M1

L1

L2

J1

H1

H2

G1

V1

W2

W3

N4

Y5

Y7

F1

G2

K4

H3

J4

Y11

Y8

Y9

P5

J5

L5

J3

CMPOVR

REFCLK

LDTSTOP_L

TEST

PWROK

RESET_L

A_SBSTB_P

A_SBSTB_N

A_SBA7

A_SBA6

A_SBA5

A_SBA4

A_SBA3

A_SBA2

A_SBA1

A_SBA0

A_ADSTB0_P

A_ADSTB0_N

A_ADSTB1_P

A_ADSTB1_N

A_CBE_L3

A_CBE_L2

A_CBE_L1

A_CBE_L0

A_DEVSEL_L

A_FRAME_L

A_IRDY_L

A_TRDY_L

A_PAR

A_REQ_L

A_STOP_L

A_RBF_L

A_WBF_L

A_CALD

A_CALD_L

A_CALS

A_CALS_L

A_DBIH

A_DBIL

A_TYPEDET_L

A_GC8XDET_L

STRAPL0

STRAPL1

STRAPL2

STRAPL3

STRAPL4

STRAPL5

STRAPL6

STRAPL7

STRAPL8

STRAPL9

STRAPL10

D D

HTCLK7

HTSTOP_L5,16

ALL_POWERGOOD

RESET_TNL_L16

A_SBSTB_P15

A_SBSTB_N15

A_SBA[7..0]15

A_ADSTB0_P15

A_ADSTB0_N15

A_ADSTB1_P15

A_ADSTB1_N15

A_CBE3_L15

A_CBE2_L15

VDD_15

A_TYPEDET_L15

A_GC8XDET_L15

A_CBE1_L15

A_CBE0_L15

A_DEVSEL_L15

A_FRAME_L15

A_IRDY_L15

A_TRDY_L15

A_PAR15

A_REQ_L15

A_STOP_L15

A_RBF_L15

A_WBF_L15

A_REFGC15

A_DBIH15

A_DBIL15

C C

B B

R60 100

R72 43.2RST/BOT

R73 43.2RST/BOT

R74 43.2RST/BOT

R75 43.2RST/BOT

C870 3900P

U2B

AGP8X/MISC/STRAPS

FREE2

FREE1

FREE3

FREE4

FREE5

FREE6

FREE7

A_PCLK

A_PLLCLKI

A_PLLCLKO

A_RESET_L

A_AD31

A_AD30

A_AD29

A_AD28

A_AD27

A_AD26

A_AD25

A_AD24

A_AD23

A_AD22

A_AD21

A_AD20

A_AD19

A_AD18

A_AD17

A_AD16

A_AD15

A_AD14

A_AD13

A_AD12

A_AD11

A_AD10

A_AD9

A_AD8

A_AD7

A_AD6

A_AD5

A_AD4

A_AD3

A_AD2

A_AD1

A_AD0

A_REFCGA_REFGC

A_GNT_L

A_ST2

A_ST1

A_ST0

A_MB8XDET_L

STRAPL11

STRAPL13

STRAPL14

STRAPL15

STRAPL16

STRAPL17

STRAPL18

STRAPL19

STRAPL20

STRAPL21

STRAPL22

Y4

NC0

N3

NC1

R3

K3

T3

C13

D13

E12

E11

AC19

AB15

AA15

AD19

N1

P2

P1

R1

T2

T1

U1

U2

W1

Y2

Y1

AA1

AB1

AB3

AB2

AC3

AD5

AC6

AD6

AC8

AD7

AD8

AC9

AD9

AD12

AC12

AB12

AD13

AD14

AC14

AC15

AD15

AD17AD16

L4

V3

U4

T4

W4

M3

P4

AA3

AB4

AB7

AD4

Y12

Y13

Y15

Y16

AA16

MB8X_L

AGPCLK_R

A_PLLCLKI

A_PLLCLKO

A_AD31

A_AD30

A_AD29

A_AD28

A_AD27

A_AD26

A_AD25

A_AD24

A_AD23

A_AD22

A_AD21

A_AD20

A_AD19

A_AD18

A_AD17

A_AD16

A_AD15

A_AD14

A_AD13

A_AD12

A_AD11

A_AD10

A_AD9

A_AD8

A_AD7

A_AD6

A_AD5

A_AD4

A_AD3

A_AD2

A_AD1

A_AD0

R775 X_0

R692 33

R63 33

A_MB8XDET_TNL_L

C895 10P

C896 10P

A_GC8XDET_L

A_MB8XDET_TNL_L

A_REFCG 15

A_GNT_L 15

A_ST2 15

A_ST1 15

A_ST0 15

A_MB8XDET_L 15

LAYOUT: This trace should be

the length of AGPCLK + 2500 mils.

AGPCLK 15

A_RESET_L 15

A_AD[31..0] 15

R592 1K

R593 0

VDD_15

POWER UP

HT FREQUENCY

*200 MHz

400 MHz

600 MHz

Lokar Configuration Straps

LOKAR_STRAP5

LOKAR_STRAP4

LOKAR_STRAP3

LOKAR_STRAP2

LOKAR_STRAP0

LOKAR_STRAP1

LOKAR_STRAP(5)

0

1

1800 MHz

R64 X_100/BOT

R65 100/BOT

R66 X_100/BOT

R67 100/BOT

R68 X_100

R69 100

R70 100

R71 100

R631 100

LOKAR_STRAP(4)

0

10

0

0

VDD_15

LOKAR_STRAP(3)

0

0

0

1

NOTE: Ground LOKAR_STRAP(22) through LOKAR_STRAP(6), LOKAR_STRAP(2), and

LOKAR_STRAP(0) for normal operation.

* Default frequency.

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

LOKAR AGP & MISC

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

1

9 36

Rev

20

of

5

D D

VDD_18 VDDA_18

FB34 600_0805

C781

C782

VDD_18

0.22u

C783

39P

VDD_15VDD_15

C780

AD22

M12

M14

M16

M18

N11

N13

N15

N17

N19

N23

P10

P12

P14

P16

P18

P21

R11

R13

R15

R17

R19

K16

T18

U17

U19

U23

V18

V21

W19

J15

K21

L11

L13

L15

L17

L19

M10

T6

T8

U11

U13

U7

U9

V10

V12

V14

V6

V8

W11

W13

V4

W7

W9

AA13

Y14

R4

T14

4700p

4.7u/1206

VCC3 VDDA_18

VDD_18

C C

B B

A A

AC21

AD21

AA10

U2C

VDD33_1

VDDA18

VDD33_2

B13

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VAGP1

VAGP2

VAGP3

VAGP4

VAGP5

VAGP6

VAGP7

VAGP8

VAGP9

VAGP10

VAGP11

VAGP12

VAGP13

VAGP14

VAGP15

VAGP16

VAGP17

VAGP18

VAGP19

VAGP20

POWER

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VAGP22

VAGP23

VAGP24

VAGP25

VAGP26

VAGP27

VAGP28

VAGP29

VAGP30

VAGP31

VAGP32

VAGP33

VAGP34

VAGP35

VAGP36

VAGP37

VAGP38

VAGP39

VAGP21

VAGP40

B17

B21

B5

B9

D12

D16

D20

D4

D8

F10

F12

F14

F16

F18

F20

F6

F8

G11

G13

G15

G17

G19

G7

G9

H10

H12

H14

H16

H8

J11

J13

J23

K10

K12

K14

W15

AA4

AA7

H4

K6

K8

L7

L9

M6

M8

M4

N7

N9

P6

P8

R7

R9

T10

T12

5

4

U2D

V11

VSS139

V13

VSS140

V15

VSS141

V17

VSS142

V19

VSS143

V7

VSS144

V9

VSS145

W10

VSS146

W12

VSS147

W14

VSS148

W16

VSS149

W18

VSS150

V2

VSS151

W23

VSS152

W6

VSS153

W8

VSS154

Y17

VSS155

Y19

VSS156

Y21

VSS157

AA18

VSS1

AA20

VSS2

AA22

VSS3

AA24

VSS4

AB19

VSS5

U15

VSS6

AB23

VSS7

AA2

VSS8

AC10

VSS9

AC13

VSS10

AB17

VSS11

AC20

VSS12

AC22

VSS13

AC4

VSS14

AC7

VSS15

Y3

VSS16

B11

VSS17

B15

VSS18

B19

VSS19

B3

VSS20

B7

VSS21

C2

VSS22

C23

VSS23

D1

VSS24

D10

VSS25

D14

VSS26

D18

VSS27

D22

VSS28

D23

VSS29

D6

VSS30

E2

VSS31

E24

VSS32

P3

VSS33

F11

VSS34

F13

VSS35

F15

VSS36

F17

VSS37

F19

VSS38

F21

VSS39

F23

VSS40

J6

VSS73

H5

VSS74

K11

VSS75

U5

VSS158

K5

VSS159

N5

VSS160

U3

VSS161

T5

VSS162

M5

VSS163

AB5

VSS164

V5

VSS165

AB11

VSS166

AC16

VSS167

AB14

VSS168

W5

VSS169

N12

VSS101

N14

VSS102

N16

VSS103

N18

VSS104

M2

VSS105

N6

VSS106

N8

VSS107

P11

VSS108

P13

VSS109

P15

VSS110

P17

VSS111

4

GROUND

VSS137

VSS138

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

U6

U8

P19

P7

P9

R10

R12

R14

R16

R18

R23

R6

R8

T11

T13

T15

T17

T19

R2

T21

T7

T9

U10

U12

U14

Y10

U18

F3

F5

F7

F9

G10

G12

G14

G16

G18

L3

G20

G22

R5

G6

G8

H11

H13

H15

H17

Y6

H21

H23

H24

AC2

H7

H9

J10

J12

J14

J16

J18

J22

K13

K15

K17

K19

J2

K20

K7

K9

L10

L12

L14

L16

L18

L23

L6

L8

M11

M13

M15

M17

M19

M21

M7

M9

N10

3

VDD_18

C762

C763

0.22u

C764

0.22u

0.22u

VDD_15

C771

VDD_12_A

VDD_12_A

C770

0.22u/BOT

C784

0.22u

C794

0.22u

0.22u/BOT

C785

0.22u

C795

0.22u

C772

C773

0.22u/BOT

4700p/BOT

Put on LDT pour.

C786

C787

0.22u

0.22u

Put on LDT plan.

C796

C797

0.22u

0.22u

VCC3

C804

0.22u

3

C788

X_0.22u

C798

0.22u

C774

4700p/BOT

2

C789

0.22u

C799

0.22u

2

C775

4700p

C790

0.22u

C800

0.22u

VDD_18

A

C760

C776

1500p/BOT

100u/10V

C791

0.22u

C801

X_0.22u

C761

4.7u/1206

C777

1500p/BOT

C792

0.22u

C802

X_0.22u

C160

CT21

470u/16V

VDD_15

C769

104P/BOT

A

100u/10V

+

C779

X_39P

C778

1500p/BOT

VDD_12_A

A

C793

100u/10V

VDD_12_A

A

C803

100u/10V

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

LOKAR POWER & GND

1

C161

X_104P/BOT

+

CT22

470u/16V

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

1

VDD_18

C162

X_104P/BOT

10 36

Rev

20

of

5

4

3

2

1

SYSTEM MEMORY

VDD_25_SUS

D D

738467085

108

120

148

168223054627796

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

DR_MD[63..0]12,13,14

C C

B B

VDD_25_SUS

-MSWEA4,13

VDD_25_SUS

A A

R77 1KST

DR_MD[63..0]

R76 4.7K

C163

R78

1000P

1KST

Place 104p Cap. near the DIMM

DDR_VREF

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP1

-MSWEA

C164

104P

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

VDD7

SLAVE ADDRESS = 1010000B

VSS0

VSS1

VSS2

VSS3

VSS4

3111826344250586674818993

104

112

128

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

DDR DIMM

SOCKET

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

100

116

136

143

156

164

VDDQ9

VDDQ10

VDDQ11

VDDQ12

184

PIN

VSS15

VSS16

VSS17

VSS18

124

132

139

145

172

1801582

VDDQ13

VSS19

152

160

VDDQ14

VDDQ15

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2#(DU)

NC(RESET#)

VSS20

VSS21

176

VDDID

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

CK0(DU)

CK2(DU)

CKE0

CKE1

CAS#

RAS#

184

VDDSPD

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

118

A11

115

A12

103

A13

59

BA0

52

BA1

113

BA2

92

SCL

91

SDA

181

SA0

182

SA1

183

SA2

DR_CHECK0 DR_CHECK[7..0]

44

CB0

DR_CHECK1

45

CB1

DR_CHECK2

49

CB2

DR_CHECK3

51

CB3

DR_CHECK4

134

CB4

DR_CHECK5

135

CB5

DR_CHECK6

142

CB6

DR_CHECK7

144

CB7

16

17

137

138

76

75

173

NC5

10

21

111

65

154

97

DM0

107

DM1

119

DM2

129

DM3

149

DM4

159

DM5

169

DM6

177

DM7

140

DM8

DDR1

DDRDIMM_184

-MCS0

-MCS1

-DR_MDQS0

-DR_MDQS1

-DR_MDQS2

-DR_MDQS3

-DR_MDQS4

-DR_MDQS5

-DR_MDQS6

-DR_MDQS7

-DR_MDQS8

MAA13

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

SMBCLK1

SMBDATA1

MEMCLK_H5

MEMCLK_L5

MEMCLK_H0

MEMCLK_L0

MEMCLK_H7

MEMCLK_L7

MEMRESET_L

MCKE0

MCKE1

-MSCASA

-MSRASA

-MCS0 4,13

-MCS1 4,13

-DR_MDQS0 12,13,14

-DR_MDQS1 12,13,14

-DR_MDQS2 12,13,14

-DR_MDQS3 12,13,14

-DR_MDQS4 12,13,14

-DR_MDQS5 12,13,14

-DR_MDQS6 12,13,14

-DR_MDQS7 12,13,14

-DR_MDQS8 12,13,14

MAA[14..0]

MEMBANKA0 4,13

MEMBANKA1 4,13

SMBCLK1 7,12,26,33

SMBDATA1 7,12,26,33

MEMCLK_H5 4,13

MEMCLK_L5 4,13

MEMCLK_H0 4,13

MEMCLK_L0 4,13

MEMCLK_H7 4,13

MEMCLK_L7 4,13

MEMRESET_L 4,12

MCKE0 4,12,13

MCKE1 4,12,13

-MSCASA 4,13

-MSRASA 4,13

MAA[14..0] 4,13

DR_CHECK[7..0] 12,13,14

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

System Memory : DDR DIMM 1

MS-6589

Last Revision Date:

Thursday, August 22, 2002

Sheet

1

11 36

Rev

20

of

5

SYSTEM MEMORY

4

3

2

1

D D

C165

104P

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP2

-MSWEB

C751

1000P

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

VDD_25_SUS

DR_MD[63..0]

R79 4.7K

-MSWEB4,13

DDR_VREF

DR_MD[63..0]11,13,14

C C

B B

Place 104p and 1000p Cap.

near the DIMM

A A

VDD_25_SUS

738467085

108

120

148

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

168223054627796

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

104

VDDQ6

112

VDDQ7

128

VDDQ8

136

143

VDDQ9

VDDQ10

156

184

DDR DIMM

SOCKET

SLAVE ADDRESS = 1010001B

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

3111826344250586674818993

100

116

124

132

139

164

172

1801582

VDDQ11

VDDQ12

VDDQ13

PIN

VSS17

VSS18

VSS19

145

152

160

VDDQ14

VDDQ15

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2#(DU)

NC(RESET#)

VSS20

VSS21

176

VDDID

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

CK0(DU)

CK2(DU)

CKE0

CKE1

CAS#

RAS#

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

DR_CHECK0

44

DR_CHECK1

45

DR_CHECK2

49

DR_CHECK3

51

DR_CHECK4

134

DR_CHECK5

135

DR_CHECK6

142

DR_CHECK7

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

DDR2

DDRDIMM_184

-MCS2

-MCS3

-DR_MDQS0

-DR_MDQS1

-DR_MDQS2

-DR_MDQS3

-DR_MDQS4

-DR_MDQS5

-DR_MDQS6

-DR_MDQS7

-DR_MDQS8

MAB13

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

SMBCLK1

SMBDATA1

VDD_25_SUS

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H6

MEMCLK_L6

MEMRESET_L

MCKE0

MCKE1

-MSCASB

-MSRASB

-MCS2 4,13

-MCS3 4,13

-DR_MDQS0 11,13,14

-DR_MDQS1 11,13,14