8

7

6

5

4

3

2

1

Cover Sheet

D D

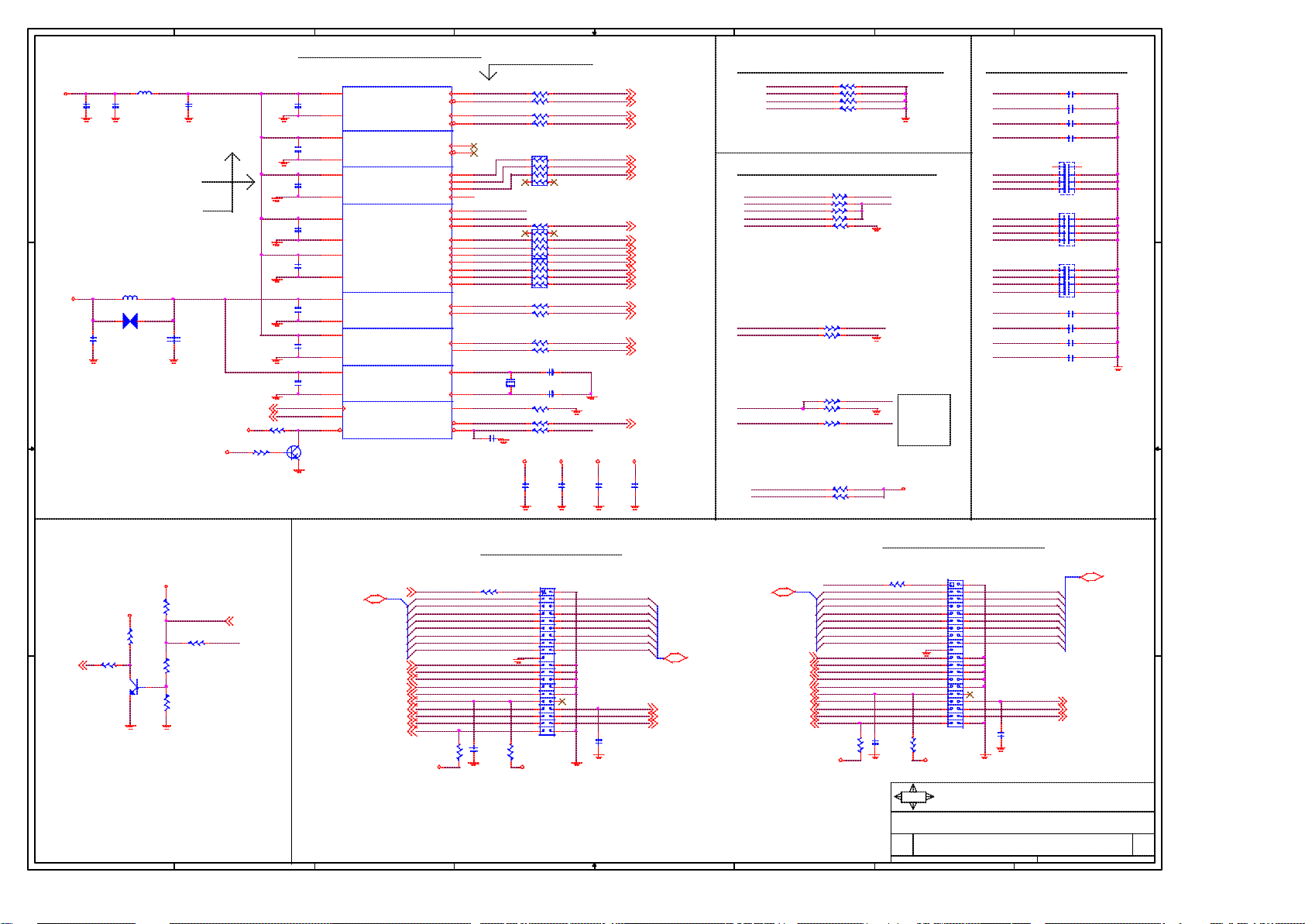

Block Diagram

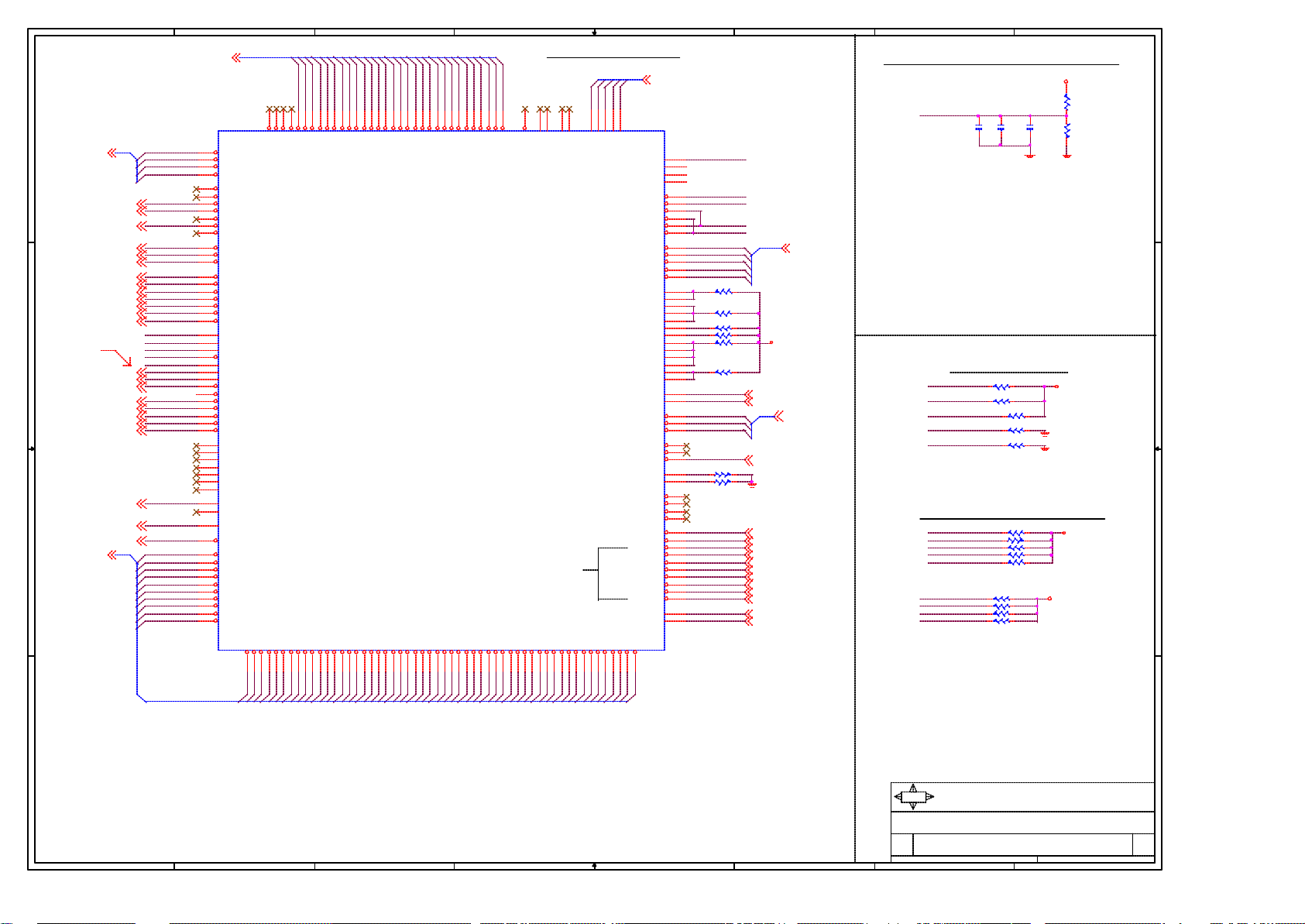

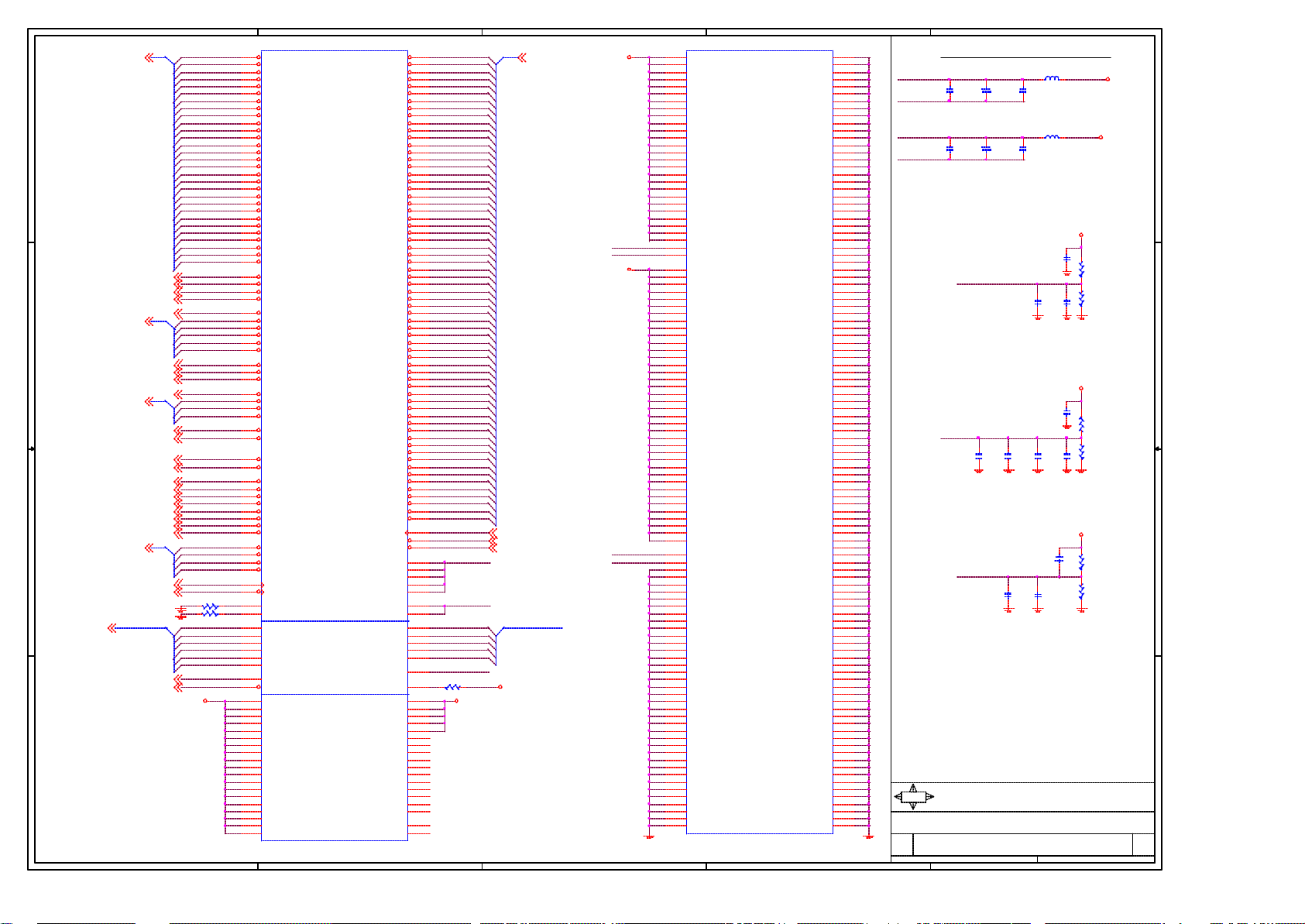

Clock CY28349 & ATA100 IDE CONNECTORS

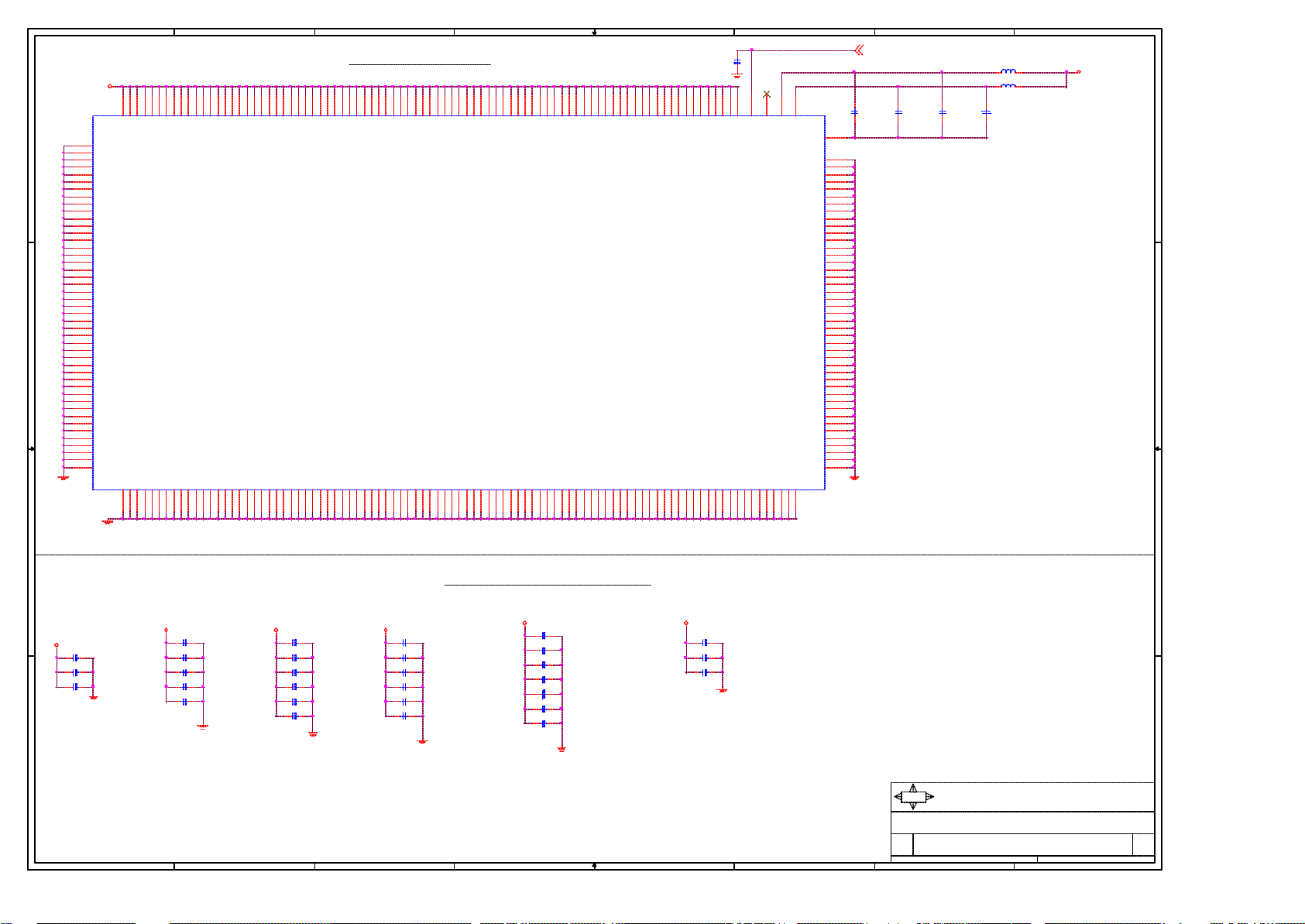

mPGA478-B INTEL CPU Sockets

INTEL Brookdale-E MCH -- North Bridge

INTEL ICH4 -- South Bridge

AC'97 Codec and Audio Connector & Internal Speaker

1

2

3

4 - 5

6 - 7

8 - 9

10LPC I/O W83627HF-AW

11

MS-6579

Version 1.0

INTEL (R) Brookdale-E Chipset

Willamette/Northwood 478pin mPGA-B Processor Schematics

CPU:

Willamette/Northwood mPGA-478B Processor

System Brookdale-E Chipset:

INTEL MCH (North Bridge) +

INTEL ICH4 (South Bridge)

C C

FWH

DDR DIMMM1,2

DDR Damping & DDR Termination

AGP 4X SLOT (1.5V) 15

PCI SLOT 1 & 2 & 3

IO CONNECTOR

USB CONNECTOR

B B

Front Panel & Connectors & FAN

ACPI Controller (MS-5)

12

13

14

16

17

18

19

20

On Board Chipset:

BIOS -- FWH

LPC Super I/O -- W83627HF-AW

Clock Generator -- CY28349/CY28323

AC'97 Codec -- AvanceLogic AC202A/AD1981A

Onboard Lan Chipset-- RealTek RTL8101L

Expansion Slots:

AGP2.0 SLOT * 1

L6719B CPU Power ( PWM )-VRM9.0

Realtek RTL8101L LAN

Jumper Setting & Manual Parts

21

22

23

PCI2.2 SLOT * 3

Platform:

Micro ATX

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

2

MICRO-STAR

COVER SHEET

MS-6579

1 25Tuesday, April 30, 2002

1

1.0

8

D D

AGP

4X(1.5V)

AGP CONN

7

Power

Supply

CONN

AGP 4X

(1.5V)

6

VRM

9.0

4X (66MHz) AGP

(593PINS/FCBGA)

5

(478PINS)

Willamette/Northwood

Socket (mPGA478-B)

(400/533MHz)

Scalable Bus

MCH: Memory

Controller HUB

4

3

2

1

(100/133MHz)

(100/133MHz)

CK408 Clock

Scalable Bus/2

(200/266MHz)

DDR DIMM 1:2

( 66MHz X 4 )

HUB Interface

(14.318MHz)

C C

ICH4: I/O

IDE CONN 1&2

USB Port 0:5

(360PINS/EBGA)

(48MHz)

LPC Bus AC Link

Controller HUB

(33MHz)

(33MHz)

FWH: Firmware HUB

LPC SIO

PCI (33MHz)

PCI Lan /

RealTek

8101L

AC '97 Audio

Codec

PCI Slots 1:3

RJ-45

Connector

Line Out

MIC In

B B

PS2 Mouse &

Keyboard

Parallel (1)

Serial (1)

Floppy Disk

Drive CONN

Audio In

Line In

CD-ROM

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

2

MICRO-STAR

BLOCK DIAGRAM

MS-6579

2 25Tuesday, April 30, 2002

1

1.0

8

VCC3

CB140

104P

D D

* Put GND copper under Clock Gen.

connect to every GND pin

* 40 mils Trace on Layer 4

with GND copper around

it

* put close to every power pin

*

Trace Width 7mils.

*

Same Group spacing 15mils

*

Different Group spacing 30mils

*

Differentical mode spacing 7mils on itself

VCC3

C C

FB20 80_0805

CB189 X_10pC174

104P

filtering from 10K~1M

FB22 X_80_0805

CP12 X_COPPER

CB147

104P

CB146

106P/0805

VDDA3V

CB151

106P/0805

VCCP

SMBCLK_ISO{10,13,20}

SMBDATA_ISO{10,13,20}

VCC3

7

R295 10K

R285 220

CLOCK GENERATOR BLOCK

CB163

104P

CB165

104P

CB145

104P

CB144

104P

CB148

104P

C181

C195

103P

C189

103P

Q29

2N3904S

U12

39

CPU_VDD

36

CPU_GND

46

MREF_VDD

43

MREF_GND

29

3V66_GND

9

PCI_VDD

5

PCI_GND

18

PCI_VDD

13

PCI_GND

24

48_VDD

21

48_GND

2

REF_VDD

47

REF_GND

34

CORE_VDD

33

CORE_GND

26

SCLK

25

SDATA

19

VTT_GD#

CY28349/CY28323

VCC3V

SMBCLK_ISO

SMBDATA_ISO

6

CPUCLK0

CPUCLK0#

CPUCLK1

CPUCLK1#

CPUCLK2

CPUCLK2#

3V66_48/SEL66_48#

FS2/PCI0

FS3/PCI1

SEL48_24#/PCI2

FS4/PCI3

FS0/48MHz

FS1/24_48MHz

MUL0/REF0

MUL1/REF1

RESET#

PWR_DN#

3V66_03V66_VDD

3V66_1

3V66_2

PCI4

PCI5

PCI6

PCI7

PCI8

PCI9

IREF

5

*Trace < 0.5"

8P4R-33

22PC191

22PC188

VCC3V

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

MCH_66

ICH_66

AGPCLK

PCICLK0

PCICLK1

PCICLK2

SIO_PCLK

LAN_PCLK

FWH_PCLK

ICH_PCLK

ICH_48

SIO_24

ICH_14

CODEC_14

Iref = 2.32mA

CPU0

41

40

38

37

45

44

3132

30

28

27

6

7

8

10

11

12

14

15

16

17

22

23

48

1

3

X1

4

X2

35

20

42

C184

R240 27.4RST

CPU0#

R241 27.4RST

CPU1

R242 27.4RST

CPU1#

R243 27.4RST

RN51

1 2

3 4

5 6

7 8

FS2

FS3

SEL48_1

R273 X_33

FS4

FS0

FS1

MUL0

MUL1

X1

X2

PWR_DN#

7 8

RN57

5 6

8P4R-33

3 4

1 2

7 8

RN58

5 6

8P4R-33

3 4

1 2

R264 33

R254 33103P

R238 33

R265 33

X1 14M-32pf-HC49S-D

R244 475RST

R274 33

R239 1K

X_1u-0603

VCC3 VCC3 VCC3 VCC3

4

CPUCLK {4}

CPUCLK# {4}

MCHCLK {6}

MCHCLK# {6}

MCH_66 {6}

ICH_66 {9}

AGPCLK {15}

PCICLK3 {16}

PCICLK0 {16}

PCICLK1 {16}

PCICLK2 {16}

SIO_PCLK {10}

LAN_PCLK {22}

FWH_PCLK {12}

ICH_PCLK {8}

ICH_48 {9}

SIO_24 {10}

ICH_14 {9}

CODEC_14 {11}

FP_RST# {9,19,20}

3

Shut Source Termination Resistors

CPUCLK

R227 49.9RST

CPUCLK#

R233 49.9RST

MCHCLK

R234 49.9RST

MCHCLK#

R232 49.9RST

Trace less 0.2"

49.9ohm for 50ohm M/B impedance

CLOCK STRAPPING RESISTORS

FS0

FS3

FS2

FS4

FS1

R263 1K

R266 10K

R272 10K

R277 10K

R253 X_10K

1 1 1 1 1

SEL48_1

SEL48_1

MUL0

MUL1

R267 X_10K

R276 X_10K

0 Set Pin 23

24MHz for ICS

R237 X_10K

R230 10K

R255 10K

VCC3V

VCC3V

FSB (MHz)FS4 FS3 FS2 FS1 FS0

100 MHz1 1 1 0 1

133 MHz

VCC3V

VCC3V

VCC3V

MUL 1:0

0 0 4X

0 1 5X

1 0 6X

1 1 7X

2

1

Pull-Down Capacitors

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

AGPCLK

ICH_66

MCH_66

PCICLK3

PCICLK0

PCICLK1

PCICLK2

SIO_PCLK

LAN_PCLK

FWH_PCLK

ICH_PCLK

ICH_14

SIO_24

ICH_48

CODEC_14

Ioh=6*Iref

Voh=0.71V

used only for EMI issue

X_10pC173

X_10pC177

X_10pC178

2

4

6

8

7

5

3

1

2

4

6

8

Trace less 0.2"

1

CN10

3

X_8P4C-10P

5

7

8

CN11

6

X_8P4C-10P

4

2

1

CN12

3

X_8P4C-10P

5

7

10PC172

X_10PC180

X_10PC194

X_10PC196

CB158

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

104P

C98

473P

CB142

104P

PD_DET {9}

PD_A2 {9}

PD_CS#3 {9}

PDD[8..15] {9}

CB141

CB166

104P

104P

B B

400MHz/ 533 MHz PSB SELECTION

ST1{7,15}

R163

1K

Q20

2N3904SBE

VCC_AGP

C

R162

1K

VCC3

R25

1K

R252 10K

R124

1.5K

R125

1.5K

BSEL0 {4}

FS1

PDD[0..7]{9}

PD_DREQ{9}

PD_IORDY{9}

PD_DACK#{9}

HD_RST#

HD_RST#{20}

PDD7

PDD6

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

PD_IOW#{9}

PD_IOR#{9}

IRQ14{8}

PD_A1{9}

PD_A0{9}

PD_CS#1{9}

PD_LED{19}

BSEL0="0" FOR 100 PSB, "1" FOR 133 PSB

ST1="1" FOR 100 PSB, "0" FOR 133 PSB

A A

VCC5

4.7K

PRIMARY IDE BLOCK

PRIMAR1

YJ220-CB-1

13 14

17 18

19

21

23

25

27

29

31

33

35

37

R114

10K

VCC3

1

3 4

5 6

7 8

91110

R189 33

C106

X_220P

2

12

1615

22

24

26

28

30

32

34

36

38

4039

ATA100 IDE CONNECTORS

8

7

6

5

4

SMBCLK_ISO

SMBDATA_ISO

SDD[0..7]{9}

* Trace Width : 5mils

* Trace Spacing : 7mils

* Length(longest)-Length(shortest)<0.5"

* Trace Length less than 5"

R245 4.7K

R246 4.7K

HD_RST#

SDD7

SDD6

SDD5

SDD4

SDD3

SDD2

SDD1

SDD0

SD_DREQ{9}

SD_IOW#{9}

SD_IOR#{9}

SD_IORDY{9}

SD_DACK#{9}

IRQ15{8}

SD_A1{9}

SD_A0{9}

SD_CS#1{9}

SD_LED{19}

R93

4.7KR97

VCC5

3

VCC3

SECONDARY IDE BLOCK

SECON1

MSI

R113

10K

YJ220-CW-1

1

2

3 4

5 6

7 8

91110

12

13 14

1615

17 18

19

22

21

24

23

26

25

28

27

30

29

32

31

34

33

36

35

38

37

4039

VCC3

CLOCK GEN & ATA100 IDE

2

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

C97

473P

MICRO-STAR

MS-6579

SD_DET {9}

SD_A2 {9}

SD_CS#3 {9}

3 25Tuesday, April 30, 2002

1

R187 33

C107

X_220P

Title

Size Document Number Rev

Date: Sheet of

SDD[8..15] {9}

1.0

8

D D

HDBI#[0..3]{6}

HDEFER#{6}

C PU_TMPA;VTIN_GND

C C

Trace : 10 mil

width 10mil space

B B

CPU_TMPA{10}

VTIN_GND{10}

THERMTRIP#{8}

PROCHOT#{9}

CPURST#{6}

HD#[0..63]{6}

HDBI#0

HDBI#1

HDBI#2

HDBI#3

FERR#{8}

STPCLK#{8}

HINIT#{8}

HDBSY#{6}

HDRDY#{6}

HTRDY#{6}

HADS#{6}

HLOCK#{6}

HBNR#{6}

HIT#{6}

HITM#{6}

HBPRI#{6}

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

IGNNE#{8}

HSMI#{8}

A20M#{8}

SLP#{8}

BSEL0

BSEL0{3}

CPU_GD

CPU_GD{9}

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HA#[3..31]{6}

AF26

AB26

AE21

AF24

AF25

AB23

AB25

AA24

AA22

AA25

E21

G25

P26

V21

AC3

AA3

W5

AB2

G1

G4

G2

A22

AD2

AD3

AD6

AD5

Y21

Y24

Y23

W25

Y26

W26

V24

U3A

V6

B6

Y4

H5

H2

J6

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A7

7

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

V22

U21

6

HA#8

HA#22

HA#25

HA#23

HA#26

HA#27

HA#28

HA#30

HA#29

HA#31

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

R21

N25

HA#24

A24#

D39#

N26

A23#

D38#

M26

HA#21

A22#

D37#

N23

HA#20

A21#

D36#

M24

HA#19

A20#

D35#

P21

HA#18

A19#

D34#

N22

HA#17

A18#

D33#

M23

HA#16

A17#

D32#

H25

A16#

D31#

HA#15

K23

HA#14

A15#

D30#

J24

HA#13

A14#

D29#

L22

HA#12

A13#

D28#

M21

HA#11

A12#

D27#

H24

HA#10

A11#

D26#

G26

HA#9

A10#

D25#

L21

A9#

D24#

D26

HA#7

A8#

D23#

F26

A7#

D22#

HA#6

E25

HA#5

A6#

D21#

F24

HA#4

A5#

D20#

F23

HA#3

A4#

D19#

G23

A3#

D18#

5

CPU SIGNAL BLOCK

AE25A5A4

AD26

DBR#

VCC_SENSE

VSS_SENSE

Differential

Host Data

Strobes

D17#

D16#

D15#

D14#

D13#

D12#

D11#

E24

H22

D25

J21

D23

C26

H21

G22

AC26

ITP_CLK1

ITP_CLK0

D10#

D9#

D8#

B25

C24

C23

D7#

VID4

AE1

B24

VID3

AE2

VID4#

VID3#

D6#

D5#

D22

VID2

AE3

C21

VID1

AE4

VID2#

VID1#

D4#

D3#

A25

VID0

AE5

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

A23

B22

B21

VID[0..4] {10,21}

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

D0#

PGA-S478-F02

4

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

GTLREF1

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

R28 51

R24 51

R67 51

R72 51

R61 51

R13 51

HRS#2

HRS#1

HRS#0

R23 51.1RST

R66 51.1RST

VCCP

CPUCLK# {3}

CPUCLK {3}

HRS#[0..2] {6}

HBR#0 {6}

* Short trace

HADSTB#1 {6}

HADSTB#0 {6}

HDSTBP#3 {6}

HDSTBP#2 {6}

HDSTBP#1 {6}

HDSTBP#0 {6}

HDSTBN#3 {6}

HDSTBN#2 {6}

HDSTBN#1 {6}

HDSTBN#0 {6}

NMI {8}

INTR {8}

3

HREQ#[0..4] {6}

2

CPU GTL REFERNCE VOLTAGE BLOCK

VCCP

GTLREF1

C47

220P

2/3*Vccp

CB56

104P

C62

105P

R63

49.9RST

R62

100RST

Every pin put one 220pF cap near it.

Trace Width 10mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU ITP BLOCK

ITP_TMS

ITP_TDO

ITP_TDI

ITP_TRST#

ITP_TCK

R14 39

R15 75

R17 150

R30 680

R16 27

VCCP

ALL COMPONENTS CLOSE TO CPU

CPU STRAPPING RESISTORS

PROCHOT#

CPU_GD

HBR#0

CPURST#

THERMTRIP#

BPM#0

BPM#1

BPM#4

BPM#5

R6 62

R71 300

R42 150

R70 51

R43 62

R26 51

R27 51

R29 51

R12 51

VCCP

VCCP

1

HD#53

HD#48

HD#51

HD#50

HD#49

HD#52

A A

8

7

HD#41

HD#45

HD#39

HD#42

HD#44

HD#43

HD#40

HD#47

HD#46

HD#38

HD#32

HD#29

HD#31

HD#26

HD#30

HD#28

HD#27

HD#34

HD#37

HD#35

HD#33

HD#36

6

HD#25

HD#19

HD#23

HD#22

HD#24

HD#20

HD#18

HD#21

HD#17

HD#10

HD#14

HD#16

HD#15

HD#12

HD#13

5

HD#11

HD#5

HD#8

HD#7

HD#9

HD#0

HD#2

HD#4

HD#3

HD#1

HD#6

MSI

Title

Size Document Number Rev

4

3

Date: Sheet of

2

MICRO-STAR

INTEL mPG478 CPU1

MS-6579

4 25Tuesday, April 30, 2002

1

1.0

8

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

VCC

VSS

AD18

VCC

VSS

AD21

VCC

VSS

AD23

VCC

VSS

AD4

VCC

VSS

AD8

VCC

VSS

AE11

AA16

VCC

VSS

AE13

U3B

VCC

VCC

D D

D10

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

C C

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AA18

VCC

VSS

AE15

AA8

VCC

VSS

AE17

VCC

VSS

AB11

VCC

VSS

AE19

AB13

VCC

VSS

AE22

AB15

VCC

VSS

AE24

7

AB17

VCC

VSS

AE26

AB19

VCC

VSS

AE7

AB7

AE9

AB9

VCC

VSS

AF1

VCC

VSS

AC10

VCC

VSS

AF10

AC12

VCC

VSS

AF12

AC14

VCC

VSS

AF14

AC16

VCC

VSS

AF16

AC18

VCC

VSS

AF18

AC8

VCC

VSS

AF20

CPU VOLTAGE BLOCK

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

6

AE14

AE16

VCC

VCC

VSS

VSS

B26B4B8

AE18

VCC

VSS

AE20

VCC

VSS

C11

AE6

C13

VCC

VSS

AE8

C15

AF11

VCC

VSS

C17C2C19

AF13

VCC

VSS

VCC

VSS

AF15

VCC

VSS

AF17

C22

AF19

AF2

AF21

AF5

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

C25C5C7C9D12

AF7

VCC

VSS

VCC

VSS

AF9

D14

B11

VCC

VSS

D16

5

B13

B15

B17

B19B7B9

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

D18

D20

D21D3D24D6D8E1E11

VCC

VSS

VCC

VSS

C10

VCC

VSS

C12

VCC

VSS

VCC

VSS

C14

C16

VCC

VSS

E13

C18

VCC

VSS

E15

C20C8D11

VCC

VCC

VSS

VSS

E17

E19

VCC

VSS

E23

D13

VCC

VSS

E26

D15

VCC

VSS

E4

D17

D19D7D9

VCC

VCC

VSS

VSS

E7E9F10

VCC

VSS

VCC

VSS

F12

E10

VCC

VSS

F14

VCC

VSS

E12

VCC

VSS

F16

4

E14

E16

VCC

VCC

VSS

VSS

F18F2F22

E18

VCC

VSS

E20E8F11

VCC

VCC

VSS

VSS

F25F5F8

104P

F13

VCC

VSS

G21G6G24

C25

F15

F17

VCC

VCC

VSS

VSS

G3H1H23

VCC

VSS

3

2

1

VCC_VID {20}

L6 4.7u-10%

L5 4.7u-10%

AF4

VCC-VID

VSS

VSS

H26H4J2

AE23

AF3

VCC-IOPLL

VCC-VIDPRG

VSS

VSS

VSS

VSS

J22

J25J5K21

AD20

VSSA

VCCA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-F02

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

C55

226P/1206

C59

X_106P/1206

C60

226P/1206

Keep the 22uF cap within 0.6"

of the CPU pin.

Trace Width 12mils, Space 10mils.

C54

X_106P/1206

F19

F9

VCC

VCC

VSS

VSS

VCCP

B B

CPU DECOUPLING CAPACITORS

VCCP

CB52

226P/1206

CB35

226P/1206

CB53

106P/1206

A A

8

CB39

X_106P/1206

CB40

226P/1206

CB24

226P/1206

CB51

106P/1206

106P/1206

CB28

106P/1206

CB37

226P/1206

CB20

226P/1206

CB44

106P/1206

CB46

226P/1206

CB38

226P/1206

7

X_106P/1206

CB43

226P/1206

CB16

106P/1206

CB36

106P/1206 CB25

CB41

226P/1206

CB32

226P/1206

6

VCCP VCCPVCCP

CB47

226P/1206CB23

CB45

226P/1206

CB17

106P/1206

CB27

226P/1206

106P/1206CB22

CB31

226P/1206

CB26

226P/1206

5

VCCPVCCP

C27

X_106P/1206

C49

X_106P/1206

C45

106P/1206

MSI

Title

Size Document Number Rev

4

3

Date: Sheet of

2

MICRO-STAR

INTEL mPGA478-B CPU2

MS-6579

5 25Tuesday, April 30, 2002

1.0

1

5

HBR#0{4}

HITM#{4}

HIT#{4}

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

R92 24.9RST

R110

HL0

HL1

HL2

HL3

HL4

HL5

VCCP

HA#[3..31]{4}

D D

HBNR#{4}

HBPRI#{4}

HLOCK#{4}

HADS#{4}

HREQ#[0..4]{4}

C C

HDEFER#{4}

HRS#[0..2]{4}

B B

Trace 10 mils &

7mils space < 0.5"

HL[0..10]{8}

A A

HTRDY#{4}

HDBSY#{4}

HDRDY#{4}

HADSTB#0{4}

HADSTB#1{4}

HDSTBN#0{4}

HDSTBP#0{4}

HDSTBN#1{4}

HDSTBP#1{4}

HDSTBN#2{4}

HDSTBP#2{4}

HDSTBN#3{4}

HDSTBP#3{4}

HDBI#[0..3]{4}

MCHCLK{3}

MCHCLK#{3}

HL[0..10]

HL_STB{8}

HL_STB#{8}

5

24.9RST

AE11

AD11

AC15

AC16

AD15

AC13

AB18

AB20

AC19

AD18

AD20

AE19

AE21

AF18

AF20

AG19

AG21

AG23

AJ19

AJ21

AJ23

U6A

T4

HA3#

T5

HA4#

T3

HA5#

U3

HA6#

R3

HA7#

P7

HA8#

R2

HA9#

P4

HA10#

R6

HA11#

P5

HA12#

P3

HA13#

N2

HA14#

N7

HA15#

N3

HA16#

K4

HA17#

M4

HA18#

M3

HA19#

L3

HA20#

L5

HA21#

K3

HA22#

J2

HA23#

M5

HA24#

J3

HA25#

L2

HA26#

H4

HA27#

N5

HA28#

G2

HA29#

M6

HA30#

L7

HA31#

V7

BR0#

W3

BNR#

Y7

BPRI#

W5

HLOCK#

V3

ADS#

U6

HREQ0#

T7

HREQ1#

R7

HREQ2#

U5

HREQ3#

U2

HREQ4#

Y5

HIT#

Y3

HITM#

Y4

DEFER#

U7

HTRDY#

W2

RS0#

W7

RS1#

W6

RS2#

V5

DBSY#

V4

DRDY#

R5

HAD_STB0#

N6

HAD_STB1#

AD4

HD_STBN0#

AD3

HD_STBP0#

AE6

HD_STBN1#

AE7

HD_STBP1#

HD_STBN2#

HD_STBP2#

HD_STBN3#

HD_STBP3#

AD5

DBI0#

AG4

DBI1#

AH9

DBI2#

DBI3#

J8

BCLK

K8

BCLK#

AC2

H_RCOMP0

H_RCOMP1

P25

HI0

P24

HI1

N27

HI2

P23

HI3

M26

HI4

M25

HI5

N25

HI_STB

N24

HI_STB#

M8

VTT

U8

VTT

AA9

VTT

AB8

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

RG82845

HOST

HUB LINK

POWER

4

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

RSTIN#

CPURST#

H_VREF0

H_VREF1

H_VREF2

H_VREF3

H_VREF4

H_SWNG0

H_SWNG1

HI_REF

HL_RCOMP

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD7

RSVD8

RSVD9

4

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

66IN

HI10

NC0

NC1

HI6

HI7

HI8

HI9

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AD7

AC7

AC6

AC3

AC8

AE2

AG5

AG2

AE8

AF6

AH2

AF3

AG3

AE5

AH7

AH3

AF4

AG8

AG7

AG6

AF8

AH5

AC11

AC12

AE9

AC9

AE10

AD9

AG9

AC10

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

P22

J27

AE17

M7

R8

Y8

AB11

AB17

AA7

AD13

L28

L27

M27

N28

M24

P26

R145 40.2RST

P27

L25

L29

M22

N23

N26

G9

G10

H6

J25

J23

G16

G17

H7

H27

K23

K25

AD26

AD27

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HVREF

HSWNG

HL6

HL7

HL8

HL9

HL10

HUB_MREF

VCC1_8

HD#[0..63] {4}

MCH_66 {3}

PCIRST#1 {12,20}

CPURST# {4}

HL[0..10]

VCC1_8

3

VCC_AGP

V_DIMM

3

VTT1

VTT2

VTT_GND1

VTT_GND2

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

AD12

AD14

AD16

AD19

AD22

AE18

AE20

AE29

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG18

AG20

AG22

AH19

AH21

AH23

AJ11

AJ13

AJ15

AJ17

AJ27

U6C

R22

VCC1_5

R29

U22

U26

W22

W29

N14

N16

P13

P15

P17

R14

R16

T15

U14

U16

T13

T17

A5

A9

A13

A17

A21

A25

C1

C29

D7

D11

D15

D19

D23

D25

F6

F10

F14

F18

F22

G1

G4

G29

H8

H10

H12

H14

H16

H18

H20

H22

H24

J5

J7

K6

K22

K24

K26

L23

U13

U17

AE1

AE4

AF5

AF7

AF9

AG1

AJ3

AJ5

AJ7

AJ9

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

RG82845

POWER

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

2

A3

A7

A11

A15

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J26

J29

K5

K7

K27

L1

L4

L6

L8

L22

L24

L26

M23

N1

N4

N8

N13

N15

N17

N22

N29

P6

P8

P14

P16

R1

R4

R13

R15

R17

R26

T6

T8

T14

T16

T22

U1

U4

U15

U29

V6

V8

V22

W1

W4

W8

W26

Y6

Y22

AA1

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

2

Title

Size Document Number Rev

Date: Sheet of

MCH REFERENCE BLOCK

VTT1

VTT_GND1

VTT2

VTT_GND2

Trace/Space=5/10mils <1.5"

Place 1 Cap. as Close as possible to

every pin of MCH

Trace width use 12 mils and 10mils space < 3"

Place 1 Cap. as Close as possible to

every pin of MCH

Trace width use 12 mils and 10mils space < 3"

Place 0.01uF Cap. as Close as possible to MCH

Trace width use 12 mils and 10mils space < 3"

MSI

CB92

104P

CB93

104P

HVREF

C122

104P

HSWNG

HUB_MREF

C127

X_106P/1206

C129

226P/1206

C89

104P

C137

103P

1

L11 4.7u-10%

C130

226P/1206

L12 4.7u-10%

C126

X_106P/1206

C103

104P

C111

C112

103P

103P

C83

104P

C90

C88

104P

VCC1_8

C143

X_103P

C138

104P

MICRO-STAR

BROOKDALE-E MCH1

MS-6579

1

VCCP

VCCP

6 25Tuesday, April 30, 2002

R108

301RST

R111

150RST

R86

49.9RST

R85

100RST103P

R152

150RST

R149

150RST

VCC_AGP

VCC_AGP

1.0

1" trace

D D

C C

B B

A A

GC_BE#[0..3]{15}

5

MD[0..63]{14}

1" Trace

GAD[0..31]{15}

5

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

AA28

AB25

AB27

AA27

AB26

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

AA23

G28

F27

C28

E28

H25

G27

F25

B28

E27

C27

B25

C25

B27

D27

D26

E25

D24

E23

C22

E21

C24

B23

D22

B21

C21

D20

C19

D18

C20

E19

C18

E17

E13

C12

B11

C10

B13

C13

C11

D10

E10

E11

G5

G3

R27

R28

T25

R25

T26

T27

U27

U28

V26

V27

T23

U23

T24

U24

U25

V24

Y27

Y26

Y23

V25

V23

Y25

C9

D8

E8

B9

B7

C7

C6

D6

D4

B3

E6

B5

C4

E5

C3

D3

F4

F3

B2

C2

E2

H3

U6B

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

RCVENIN#

RCVENOUT#

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE0#

G_C/BE1#

G_C/BE2#

G_C/BE3#

RG82845

AGP

Tri-Stated

during

RSTIN#

assertion

DDR

4

SM_RCOMP

SD_REF0

SD_REF1

G_FRAME#

G_IRDY#

G_TRDY#

G_DEVSEL#

G_STOP#

G_REQ#

G_GNT#

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

AGPREF

G_RCOMP

TESTIN#

4

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

SCS#0

SCS#1

SCS#2

SCS#3

SCB0

SCB1

SCB2

SCB3

SCB4

SCB5

SCB6

SCB7

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SCK0

SCK#0

SCK1

SCK#1

SCK2

SCK#2

SCK3

SCK#3

SCK4

SCK#4

SCK5

SCK#5

SCKE0

SCKE1

SCKE2

SCKE3

SRAS#

SCAS#

SWE#

SBS0

SBS1

G_PAR

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

PIPE#

RBF#

WBF#

3

DDRMA0

E12

DDRMA1

F17

DDRMA2

E16

DDRMA3

G18

DDRMA4

G19

DDRMA5

E18

DDRMA6

F19

DDRMA7

G21

DDRMA8

G20

DDRMA9

F21

DDRMA10

F13

DDRMA11

E20

DDRMA12

G22

CS#0

E9

CS#1

F7

CS#2

F9

CS#3

E7

CB0

C16

CB1

D16

CB2

B15

CB3

C14

CB4

B17

CB5

C17

CB6

C15

CB7

D14

SDQS0

F26

SDQS1

C26

SDQS2

C23

SDQS3

B19

SDQS4

D12

SDQS5

C8

SDQS6

C5

SDQS7

E3

SDQS8

E15

DCLK0

E14

F15

J24

G25

G6

G7

G15

G14

E24

G24

H5

F5

G23

E22

H23

F23

F11

G8

G11

G12

G13

J28

J9

J21

Y24

W27

W24

W28

W23

W25

AG24

AH25

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AF27

AF26

AG25

ST0

AF24

ST1

AG26

ST2

R24

R23

AC27

AC28

AF22

AE22

AE23

AA21

AD25

R147 40.2RST

H26

DCLK0 {13}

DCLK#0

DCLK#0 {13}

DCLK1

DCLK1 {13}

DCLK#1

DCLK#1 {13}

DCLK2

DCLK2 {13}

DCLK#2

DCLK#2 {13}

DCLK3

DCLK3 {13}

DCLK#3

DCLK#3 {13}

DCLK4

DCLK4 {13}

DCLK#4

DCLK#4 {13}

DCLK5

DCLK5 {13}

DCLK#5

DCLK#5 {13}

DDRCKE0

DDRCKE1

DDRCKE2

DDRCKE3

RASA#

CASA#

WEA#

BS0

BS0 {13,14}

BS1

BS1 {13,14}

R146 30.1RST

SM_REF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

104PC136

CS#[0..3]

CB[0..7]

RASA# {13,14}

CASA# {13,14}

WEA# {13,14}

104P_X7RCB101

GFRAME# {15}

GIRDY# {15}

GTRDY# {15}

GDEVSEL# {15}

GSTOP#{15}

GPAR {15}

GREQ# {15}

GGNT# {15}

SB_STB{15}

SB_STB#{15}

GAD_STB0{15}

GAD_STB#0{15}

GAD_STB1{15}

GAD_STB#1{15}

PIPE# {15}

RBF# {15}

WBF# {15}

AGPREF {15}

DDRMA[0..12] {13,14}

CS#[0..3] {13,14}

CB[0..7] {14}

SDQS[0..8] {14}

DDRCKE0 {13,14}

DDRCKE1 {13,14}

DDRCKE2 {13,14}

DDRCKE3 {13,14}

DDR_VTT

SBA[0..7] {15}

ST[0..2] {3,15}

3

VCCP

CB83

104P

CB87

104P

CB89

103P

CB213

104P

CB214

104P

CB86

106P/1206

CB84

106P/1206

SOLDER SIDE COMPONENT

2

MCH REFERENCE VOLTAGE

DIMMREF

SM_REF

5020

C248

X_0.1u

C147

104P

MCH DECOUPLING CAPACITOR

VCC1_8 V_DIMM

CB100

104P

CB99

104P

VCCP

VCC_AGP

CB203

X_0.1u

CB207

X_0.1u

CB205

X_0.1u

CB211

X_0.1u

CB206

X_0.1u

CB210

X_0.1u

2

VCC_AGP

CB102

104P

CB103

104P

CB106

104P

CB98

104P

CB91

104P

+

CT25

470u_10V

5020

CB209 X_0.1u

V_DIMM

5020

5020

5020

5020

5020

5020

Title

Size Document Number Rev

Date: Sheet of

CB208

X_0.1u

CB204

X_0.1u

1

AGPREF

5020

5020

MICRO-STAR

BROOKDALE-E MCH2

MS-6579

1

CB85

104P

CB97

104P

CB90

104P

CB79

104P

CB72

104P

CB81

104P

CB76

104P

7 25Tuesday, April 30, 2002

1.0

Loading...

Loading...