8

7

6

5

4

3

2

1

MS-6541

D D

Cover Sheet

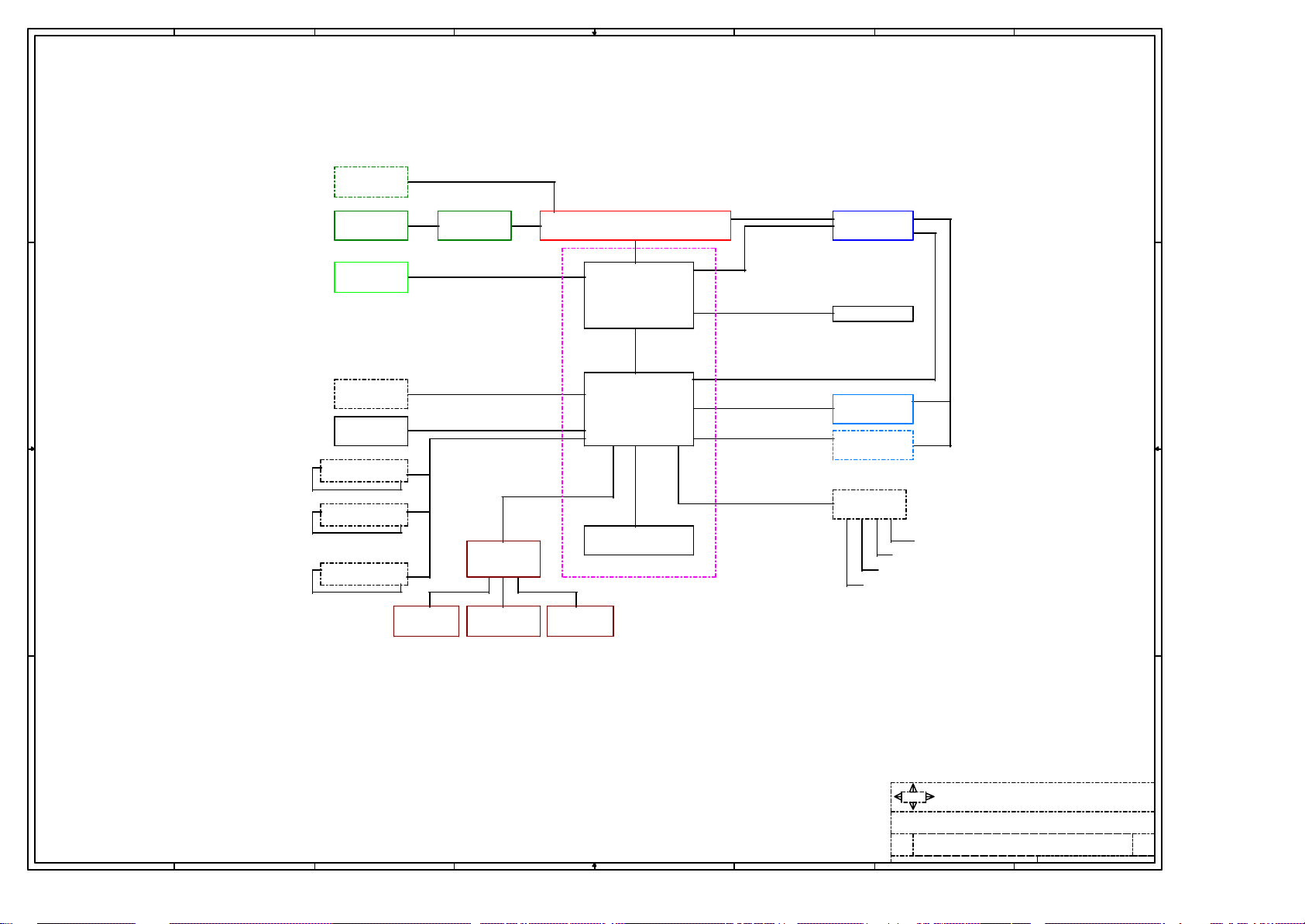

Block Diagram

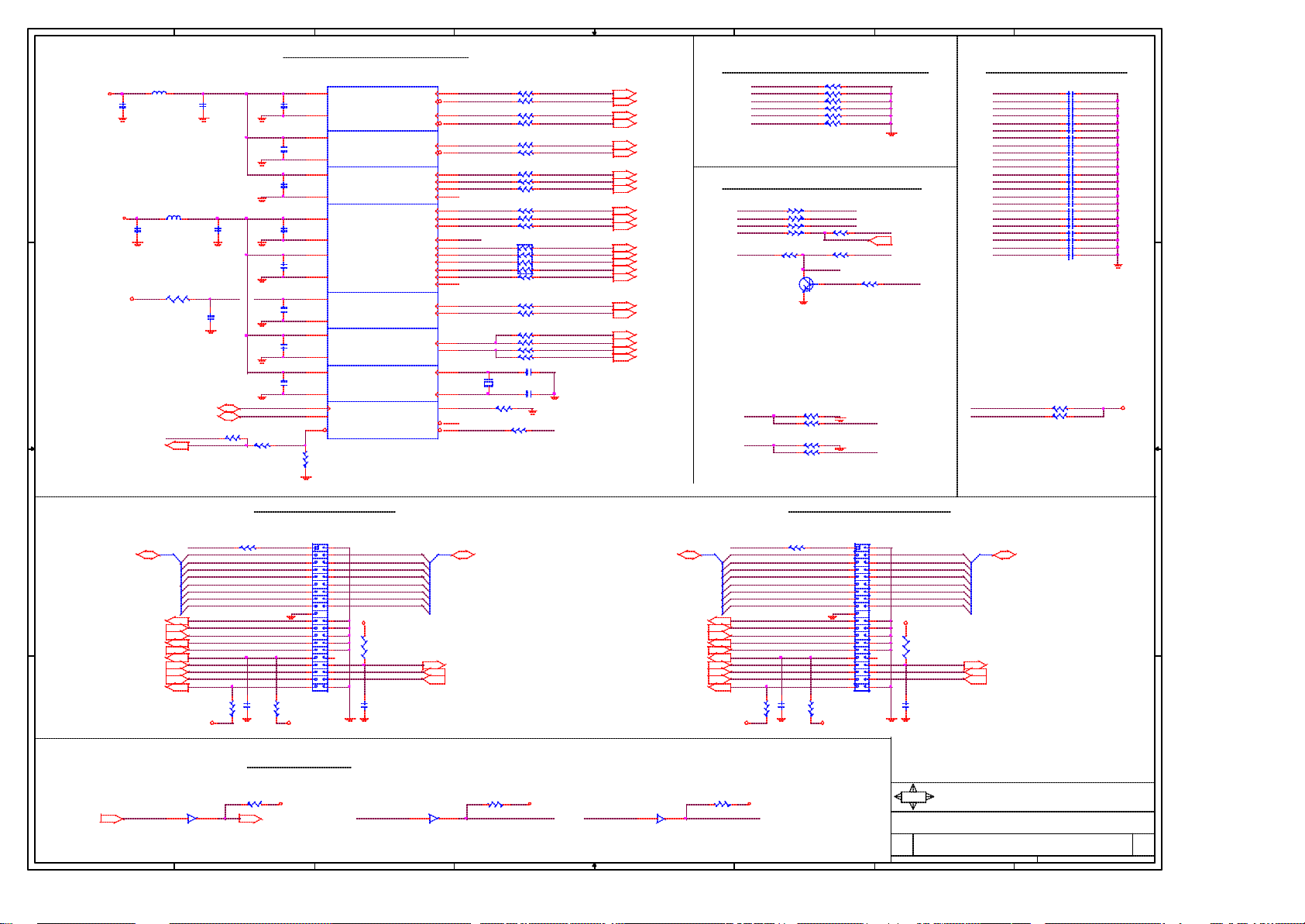

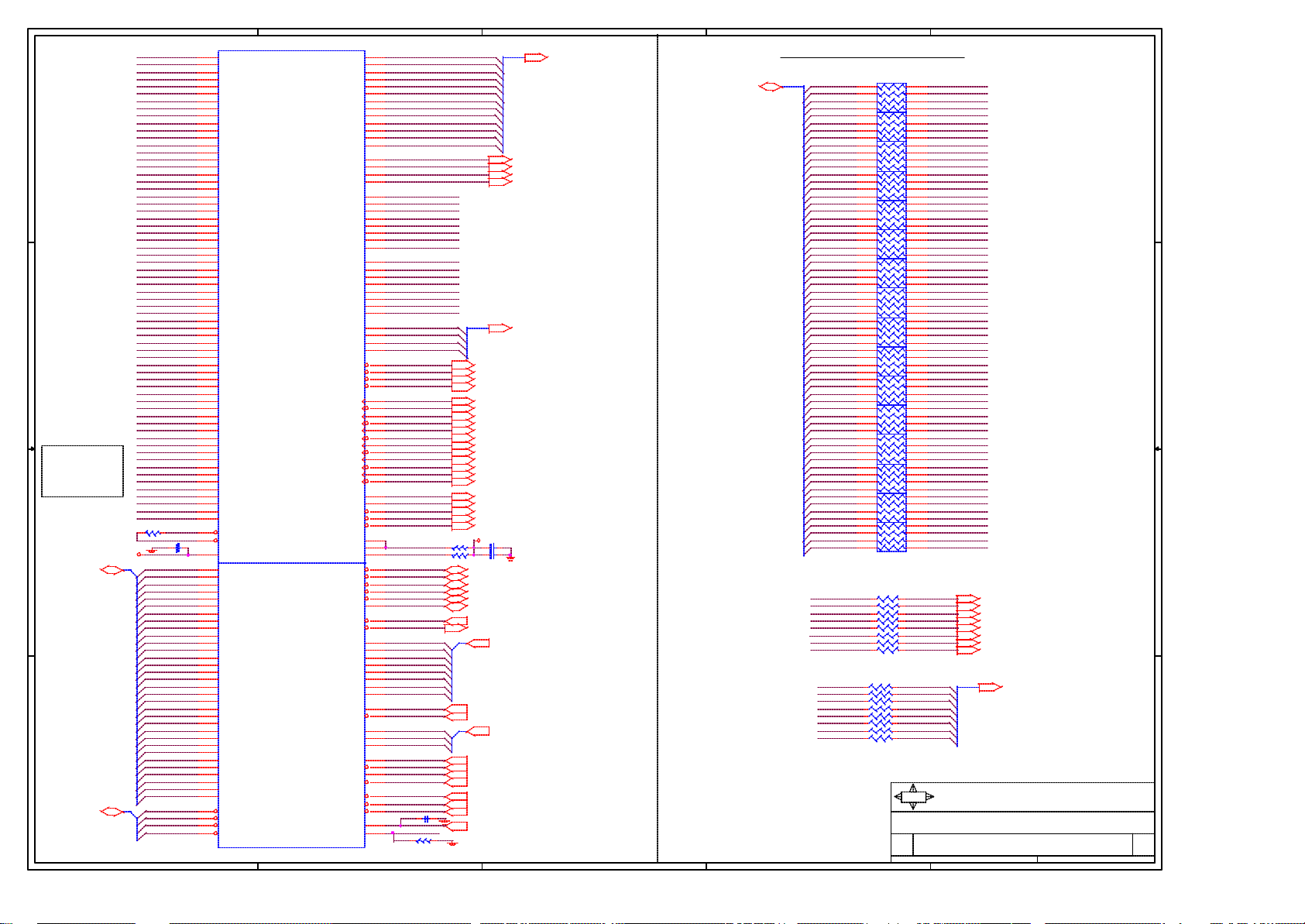

Clock CY28323 & ATA100 IDE CONNECTORS

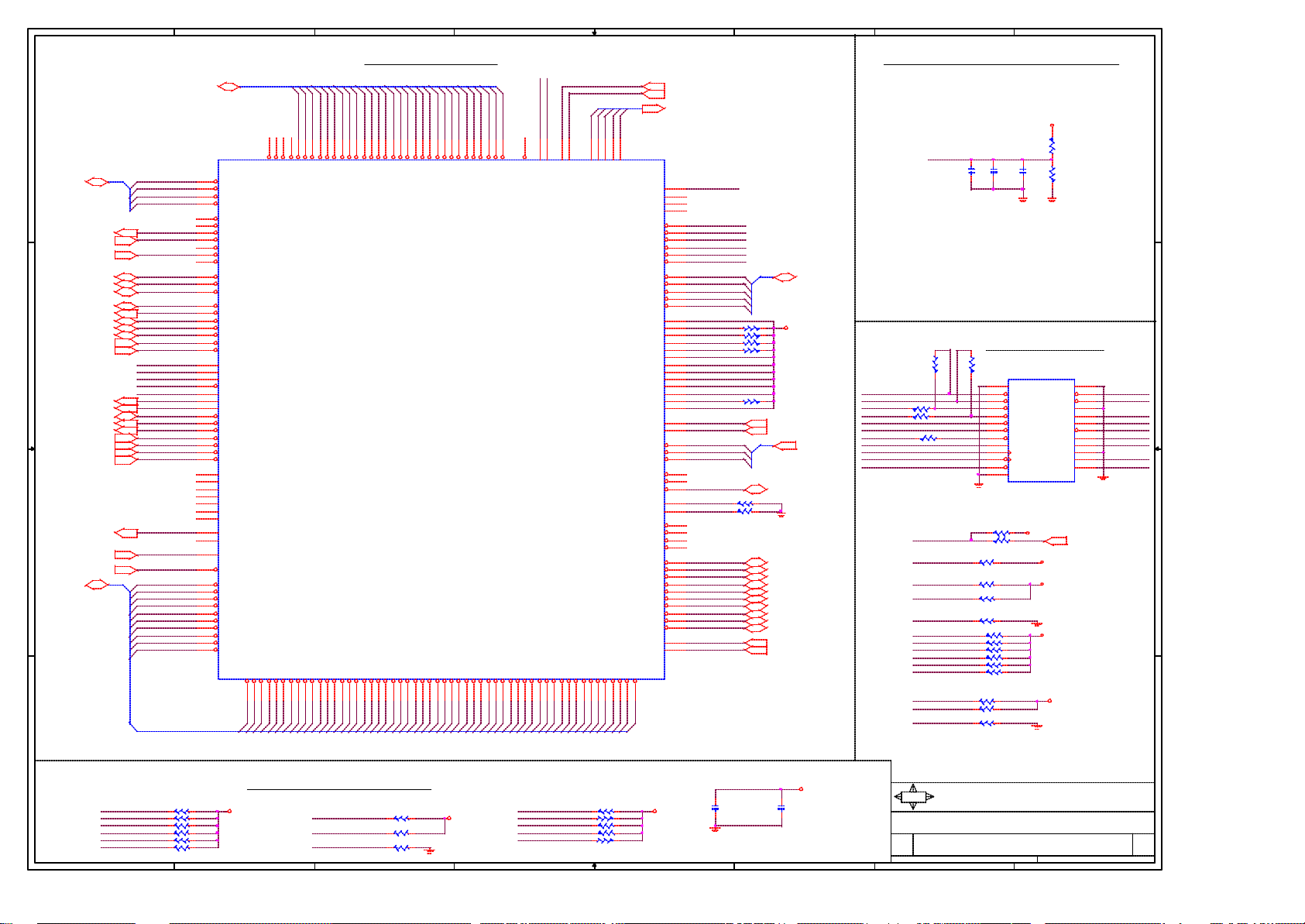

mPGA478-B INTEL CPU Sockets

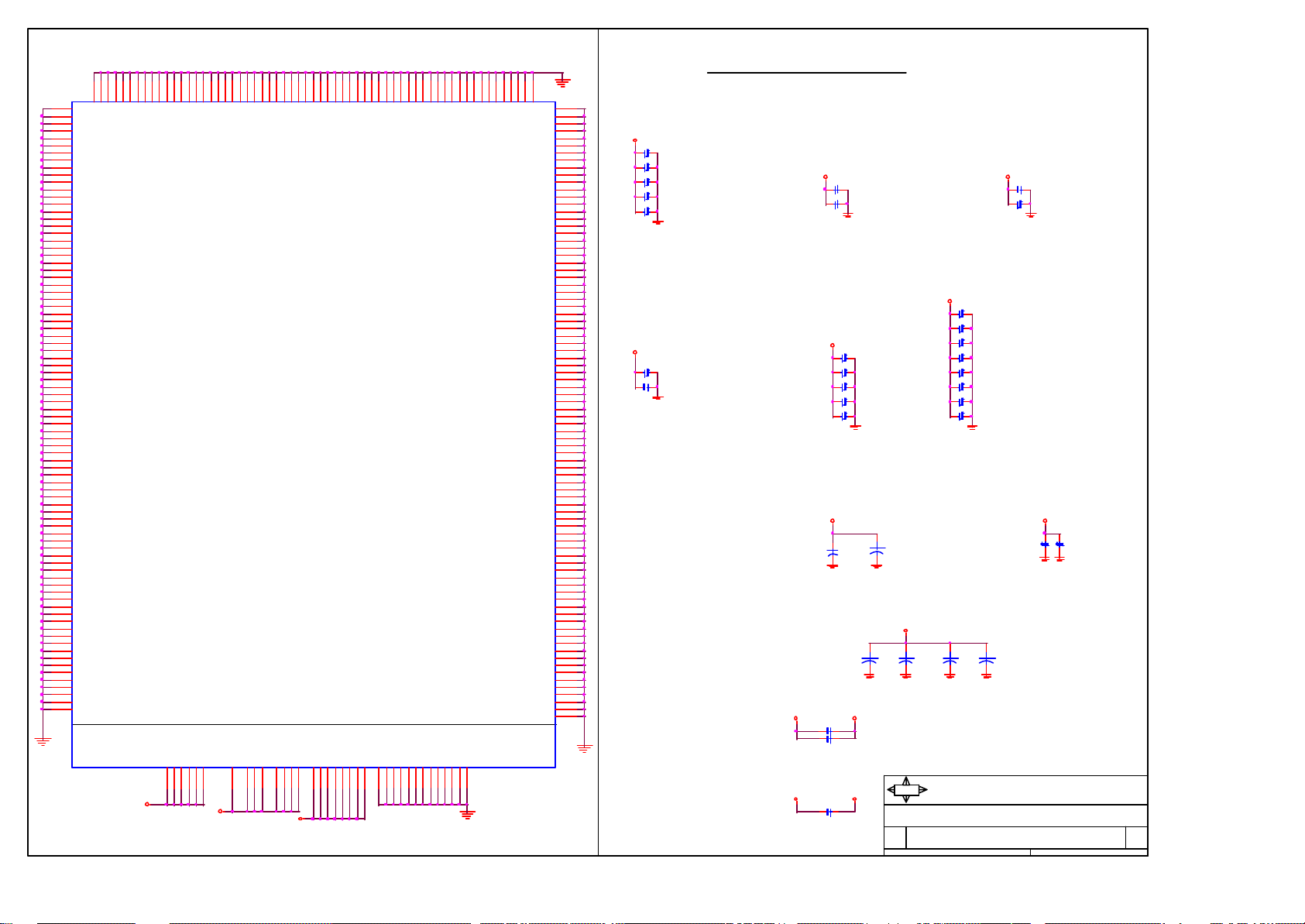

INTEL Brookdale-G GMCH -- North Bridge

1

2

3

4 - 5

6 - 8

INTEL (R) Brookdale-G Chipset

Willamette/Northwood 478pin mPGA-B Processor Schematics

CPU:

Willamette/Northwood mPGA-478B Processor

System Brookdale-G Chipset:

Micro-ATX

INTEL GMCH (North Bridge) +

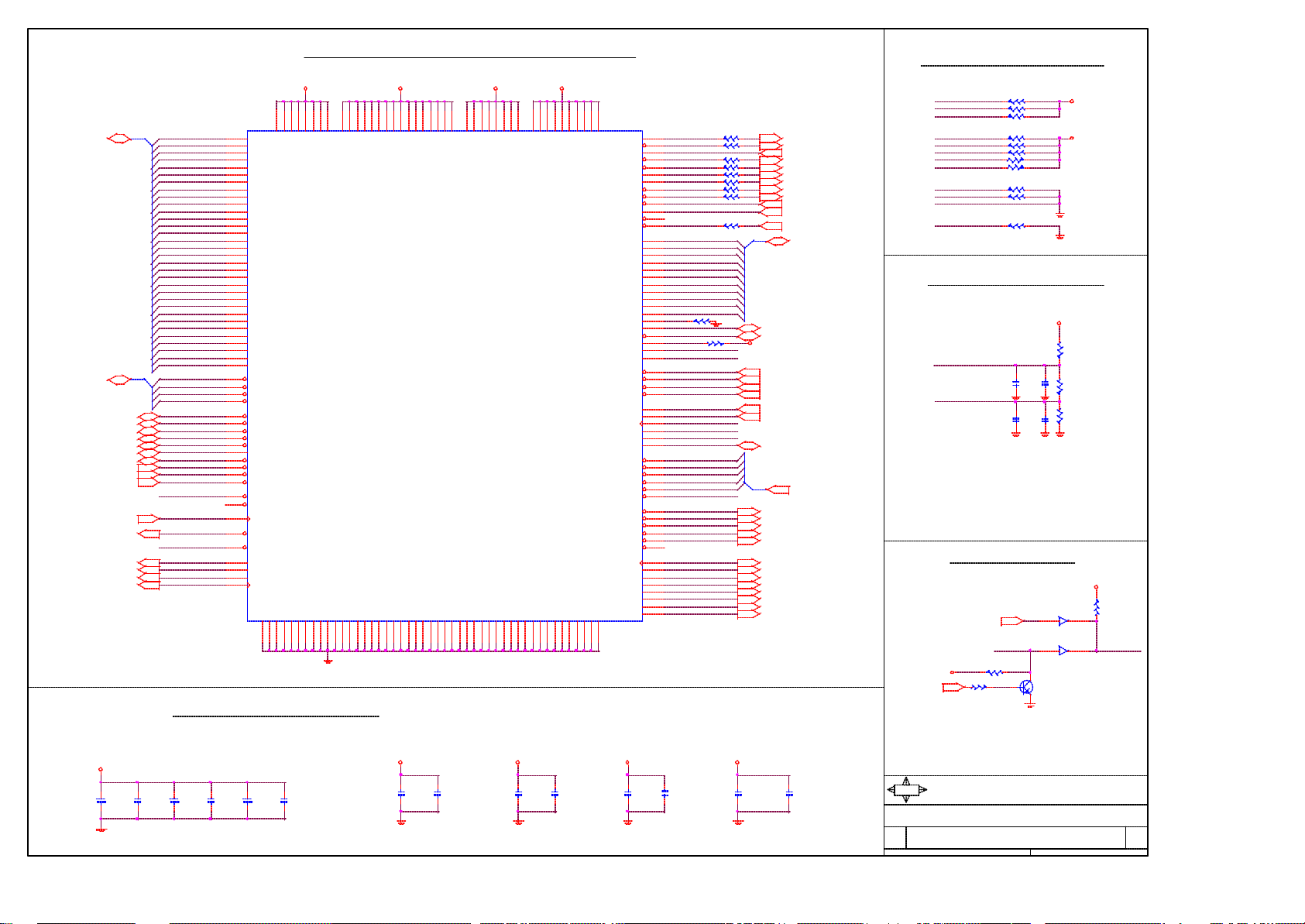

INTEL ICH4 -- South Bridge

LPC I/O -- LPC47B367

C C

AC'97 Codec AD1981/1885 & Internal Speaker

9-10

11

12

INTEL ICH4 (South Bridge)

On Board Chipset:

BIOS -- FWH

FWH -- BIOS & SMBus Isolation

DDR DIMM1&2 and DDR Terminator Resistor

AGP Slot

PCI SLOT 1 & 2 & 3

IO Connectors

USB Connectors

Front Panel & ATX Connectors

B B

13

14-15

16

17

18

19

20

AC'97 Codec -- AD1981/1885

LPC Super I/O -- LPC47B367

Clock Generation -- CY28323

LAN -- Intel KINNERITH controller

Expansion Slots:

PCI2.2 SLOT * 3

PCI Extender Connector * 1

Votlage Regulator

DDR REGULATOR

Intersil HIP6301V+HIP6601A/02A-- CPU Power

21

22

23

PCI Extender & Front Audio Connector 24

LAN KINNERITH 10/100/Mbit Controller

VGA Connector

Manual Part

A A

8

7

6

25

26

27

28-29GPIO SETTTING

5

4

3

MSI

Title

Size Document Number Rev

Date: Sheet of

2

MICRO-STAR

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

COVER SHEET

MS-6541I1

1 29Tuesday, March 05, 2002

1

0AE0

8

D D

7

6

5

4

3

2

1

ITP Port

VCC12 Power

Supply CONN

VRM 9.2 CK408 Clock

Willamette/Northwood

Socket (mPGA478-B)

(100/133MHz)

Scalable Bus

(100/133MHz)

AGP 4X (1.5V)

VGA CONN

C C

4X (66MHz) AGP

GMCH: Graphic &

Memory

Controller HUB

HUB Interface

(200/266 MHz)

DDR DIMM1,2

(14.318MHz)

Hardware

Monitor

IDE CONN 1&2

USB Port 0:1

USB Back Panel

USB Port 2:3

USB Back Panel

B B

USB Port 4:5

USB Front Panel

PS2 Mouse &

Keyboard

SM Bus

ATA33/ATA66/ATA100

(48MHz)

LPC Bus

SMC I/O

LPC47M133

Parallel (1)

Serial (2)

ICH4: I/O

Controller HUB

(33MHz)

FWH: Firmware HUB

Brookdale -G Chipset

Floppy Disk

Drive

(33MHz)

PCI (33MHz)

PCI (33MHz)

AC Link

PCI Slots 1:3

LAN Controller

AC '97 Audio

Codec

MIC In

Line In

Line Out

CD-ROM (Option)

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

2

MICRO-STAR

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

BLOCK DIAGRAM

MS-6541I1

2 29Tuesday, March 05, 2002

1

0AE0

8

7

6

5

4

3

2

1

CLOCK GENERATOR BLOCK

Shut Source Termination Resistors

U1

39

CPU_VDD

CB2

0.1u

36

CPU_GND

46

MREF_VDD

CB3

0.1u

43

MREF_GND

CB4

0.1u

29

3V66_GND

9

PCI_VDD

CB6

0.1u

5

PCI_GND

18

PCI_VDD

CB5

0.1u

13

PCI_GND

24

48_VDD

C24

0.01u

21

48_GND

2

REF_VDD

C27

0.01u

47

REF_GND

34

CORE_VDD

C26

0.01u

33

CORE_GND

26

SCLK

25

SDATA

19

VTT_GD#

CYPRESS CY28323/ICS 950208, 950213

R39

X_1K

CPU0#

CPU1#

CPU2/CPU_STP#

CPU2#/PCI_STP#

3V66_03V66_VDD

3V66_1

3V66_2

3V66_3

FS2/PCI_F0

FS3/PCI_F1

MODE/PCI_F2

FS4/PCI0

FS0/48MHz

FS1/24_48MHz

MUL0/REF0

MUL1/REF1

PWR_DN#

CPU0

CPU1

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

IREF

RST#

CPU0

41

CPU0#

40

CPU1

38

CPU1#

37

CPU2 ITP_CLK

45

CPU2#

44

3V66_0

3132

3V66_1

30

28

27

6

7

PCI_F2

8

FS4

10

PCI1

11

RN2

12

PCI3

33

14

PCI4

15

PCI5

16

17

22

23

48

1

3

X1

4

X2

35

20

42

R643 33

FS0

FS1

MUL0

MUL1

CLK_X1

X1 14M-32pf-HC49S-D

CLK_X2

32pF

IREF

R28 475_1%

Iref = 2.32mA

R37 1K

R2 27.4_1%

R4 27.4_1%

R10 27.4_1%

R12 27.4_1%

R765 27.4_1%

R766 27.4_1%

R13 33

R508 33

R588 33

R20 33

R15 33

R16 33

7 8

5 6

3 4

1 2

R26 33

R27 33

R808 X_33

R24 33

R25 33

R799 33

10u-12060.1u

SMBDATA_ISO(13)

CB273

10u-1206

CB311

10u-0805

SMBCLK_ISO(13)

VCC3V

CB275

CLK_VCC3

R30 2.2K

VCC3V

VCC3VAVCC3VA

SMBCLK_ISO

SMBDATA_ISO

R9 1K

VTT_GD#

CB7

filtering from 10K~1M

VCC3

VCC3

-PWRGD_30MS(11)

FB1 80S/0805

FB2 80S/0805

CB1

0.1u

for good filtering from 10K~1M

R757 10

VCC3

D D

C C

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

ITP_CLK#

MCH_66

ICH_66

AGPCLK3V66_2

ICH_PCLKFS2

SIO_PCLKFS3

FWH_PCLK

PCICLK0

PCICLK1PCI2

PCICLK2

PCICLK3

PCICLK4

ICH_48

DOT_CLK

BITCLK_14

SIO_14

ICH_14

CODEC_14

22pC23

22pC25

VCC3VPWR_DN#

CPUCLK (4)

CPUCLK# (4)

MCHCLK (6)

MCHCLK# (6)

ITP_CLK (4)

ITP_CLK# (4)

MCH_66 (6)

ICH_66 (10)

AGPCLK (16)

ICH_PCLK (9)

SIO_PCLK (11)

FWH_PCLK (13)

PCICLK0 (17)

PCICLK1 (17)

PCICLK2 (17)

PCICLK3 (24)

PCICLK4 (24)

ICH_48 (10)

DOT_CLK (6)

BITCLK_14 (10)

SIO_14 (11)

ICH_14 (10)

CODEC_14 (12)

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

ITP_CLK

ITP_CLK#

Trace less 0.2"

49.9ohm for 50ohm M/B impedance

CLOCK STRAPPING RESISTORS

FS4 VCC3V

FS3 VCC3V

FS1

R767 10K

FS0

R768 10K R642 1.5K

X_2N3904S

FS4 FS3

1 1

1 1

MUL0

MUL1

R1 49.9_1%

R3 49.9_1%

R5 49.9_1%

R7 49.9_1%

R763 49.9_1%

R764 49.9_1%

R639 10K

R640 10K

R641 10K

Q66

VCC3VFS2

R18 1.5K

Q66_C

Q66_B BSEL0

BSEL0="0" FOR 100 PSB, "1" FOR 133 PSB

FS2 FS1 FS0

VCC3V

VCC3V

R644 X_1K

CPU (MHz)

1 0 1 100 MHz

1 1 1 133 MHz

R31 X_1K

R727 10K

R509 X_1K

R36 10K

VCC3V

VCC3V

BSEL0 (4)

MUL 1:0 0 0 4X

0 1 5X

1 0 6X

1 1 7X

Pull-Down Capacitors

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

ITP_CLK

ITP_CLK#

MCH_66

ICH_66

AGPCLK

ICH_PCLK

FWH_PCLK

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

SIO_PCLK

ICH_14

SIO_14

ICH_48

DOT_CLK

CODEC_14

BITCLK_14

used only for EMI issue

Trace less 0.2"

SMBCLK_ISO

SMBDATA_ISO

R29 4.7K

R32 4.7K

X_10pC1

X_10pC2

X_10pC3

X_10pC4

X_10pC324

X_10pC325

X_10pC7

X_10pC8

X_10pC9

X_10pC10

X_10pC11

X_10pC13

X_10pC14

X_10pC15

X_10pC12

X_10pC309

X_10pC16

10pC18

10pC19

X_10pC20

X_10pC21

10pC327

X_10pC328

VCC3

PRIMARY IDE BLOCK SECONDARY IDE BLOCK

PRIMAR1

R48

10K

VCC3

YJ220-CB-1

1

3 4

5 6

7 8

91110

13 14

17 18

19

21

23

25

27

29

31

33

35

37

2

PDD8

PDD9

PDD10

PDD11

PDD12

12

PDD13

PDD14

1615

PDD15

VCC5 VCC5

22

24

26

28

R645

30

20K

32

34

36

38

4039

C30

X_4700p

6

B B

A A

PDD[0..7](10)

PD_DREQ(10)

PD_IOW#(10)

PD_IOR#(10)

PD_IORDY(10)

PD_DACK#(10)

IRQ14(9)

PD_A1(10)

PD_CS#1(10) PD_CS#3 (10)

PD_LED(20)

PCIRST#(9)

PCIRST# PCIRST#

8

PDD7

PDD6

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

R47

C29

4.7K

VCC5 VCC5VCC3

220p

RESET BLOCK

U2A

1 2

DM7407-SOIC14

(VCC5_SB) (VCC5_SB)

R51 330

PCIRST#1 (6,11,13)

7

PRIMAR1_1HD1_RST#

R43 33 R44 33

ATA100 IDE CONNECTORS

PDD[8..15] (10)

ATADET0(11)

PD_A2 (10)PD_A0(10)

U2B

3 4

DM7407-SOIC14

R52 1K

HD2_RST#

5

VCC5

PCIRST# HD1_RST#

SECON1

HD2_RST#

R53 1K

SDD7

SDD6

SDD5

SDD4

SDD3

SDD2

SDD1

SDD0

R49

C31

4.7K

220p

VCC5

3

SDD[0..7](10)

SD_DREQ(10)

SD_IOW#(10)

SD_IOR#(10)

SD_IORDY(10)

SD_DACK#(10)

IRQ15(9)

SD_A1(10)

SD_A0(10)

SD_CS#1(10) SD_CS#3 (10)

SD_LED(20)

U2E

11 10

DM7407-SOIC14

(VCC5_SB)

4

SECON_1

R50

10K

VCC3

YJ220-CW-1

1

3 4

5 6

7 8

91110

13 14

17 18

19

21

23

25

27

29

31

33

35

37

2

SDD8

SDD9

SDD10

SDD11

SDD12

12

SDD13

SDD14

1615

SDD15

22

24

26

28

R646

30

20K

32

34

36

38

4039

C32

X_4700p

MSI

Title

Clock CY28323 & ATA100 IDE CONNECTORS

Size Document Number Rev

Date: Sheet of

2

* Trace Width : 5mils

* Trace Spacing : 7mils

* Length(longest)-Length(shortest)<0.5"

* Trace Length less than 5"

SDD[8..15] (10)

ATADET1(11)

SD_A2 (10)

MICRO-STAR

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

MS-6541I1

3 29Tuesday, March 05, 2002

1

0AE0

8

7

6

5

4

3

2

1

CPU GTL REFERNCE VOLTAGE BLOCKCPU SIGNAL BLOCK

VID0

AE5

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

A23

B22

B21

HD#0

HD#2

HD#1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

D0#

ITP_CLK# (3)

ITP_CLK (3)

VID[0..4] (11,23)

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

SOCKET478

GTLREF1

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI1

HRS#2

HRS#1

HRS#0

COMP1

COMP0

R59 51

R60 51

R61 51

R62 51

R592 51

R64 51.1_1%

R65 51.1_1%

* Short trace

HREQ#[0..4] (6)

VCCP

CPUCLK# (3)

CPUCLK (3)

HRS#[0..2] (6)

HBR#0 (6)

HADSTB#1 (6)

HADSTB#0 (6)

HDSTBP#3 (6)

HDSTBP#2 (6)

HDSTBP#1 (6)

HDSTBP#0 (6)

HDSTBN#3 (6)

HDSTBN#2 (6)

HDSTBN#1 (6)

HDSTBN#0 (6)

NMI (9)

INTR (9)

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

ITP_TCK

ITP_CLK

ITP_CLK#

BPM#5

C323

220p

2/3*Vccp

GTLREF1

Every pin put one 220pF cap near it.

Trace Width 7mils, Space 10mils.

Keep the voltage divider within

1.5" of the GETREF pin.

CPU ITP BLOCK

-C_BMP2

-C_BMP3

-ITP_RSTCPURST#

R770

X_0

R774 150

R775 0

R776 150

R777 1.5K

R778 49.9_1%

R779 X_220

R780 51

R781 51

R782 51

R783 51

R784 51

R785 51

R74 39

R76 75

R77 27

R769

X_0

R771 0

R772 0

R773 0

-ITP_DBR

-ITP_DBA

ITP_VCC

-ITP_RST

ITP_FBI

BPM#4

BPM#5

BPM#2

BPM#3

BPM#1

BPM#0

ITP_TMS

ITP_TDO

ITP_TCK

VCCP

R54

49.9_1%

C35

1u-0805

VCC3

TRST#

VCC3

VCCP

VCCP

DBA#

DBR#

GND

TMS

GND

VCCP

R55

100_1%

TDI

LPC_MR# (11)

C34

0.1u

JTAG1

1 2

GND GND

3

BPM#0

5

BPM#1

7

BPM#2

9

BPM#3

11

BPM#4

13

BPM#5

15 16

RESET# TCK

17 18

FBO FBI

19

BCLK

21 22

BCLK# VCC

23 24

BPM5DR# TDO

25

GND

JTAG

-ITP_DBA

4

-ITP_DBR

6

8

ITP_TDI

10

ITP_TMS

12

ITP_TRST#

14

ITP_TCK

ITP_FBI

20

ITP_VCC

ITP_TDO

HA#[3..31](6)

HA#8

HA#22

HA#25

HA#23

HA#26

HA#27

HA#28

HA#30

HA#29

D D

HINV#[0..3](6)

FERR#(9)

STPCLK#(9)

HINIT#(9)

HDBSY#(6)

HDRDY#(6)

HTRDY#(6)

HADS#(6)

HLOCK#(6)

HBNR#(6)

HITM#(6)

C C

B B

HBPRI#(6)

HDEFER#(6)

CPU_TEM+(11)

CPU_TEM-(11)

TRMTRIP#(9,11)

SKTOCC#(11)

PROCHOT#(10,11)

IGNNE#(9)

HSMI#(9)

A20M#(9)

SLP#(9)

BSEL0(3,6)

CPU_GD(10)

CPURST#(6)

HD#[0..63](6)

HINV#0

HINV#1

HINV#2

HINV#3

HINIT#

HIT#(6)

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

TRMTRIP#

SKTOCC#

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

AF26

AB26

AE21

AF24

AF25

AB23

AB25

AA24

AA22

AA25

E21

G25

P26

V21

AC3

AA3

W5

AB2

G1

G4

G2

A22

AD2

AD3

AD6

AD5

Y21

Y24

Y23

W25

Y26

W26

V24

U3A

V6

B6

Y4

H5

H2

J6

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A7

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

V22

HD#53

HA#31

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

U21

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

R21

HD#52

HD#51

HD#48

HD#50

HD#49

HD#41

HD#47

HD#46

HD#45

HD#42

HD#44

HD#43

HD#40

HA#24

A25#

D40#

N25

HD#39

A24#

D39#

N26

HD#38

A23#

D38#

M26

HD#37

HA#21

A22#

D37#

N23

HD#36

HA#20

A21#

D36#

M24

HD#35

HA#19

A20#

D35#

P21

HD#34

HA#18

A19#

D34#

N22

HD#33

HA#17

A18#

D33#

M23

HD#32

HA#16

A17#

D32#

H25

HD#31

A16#

D31#

HA#15

K23

HD#30

HA#14

A15#

D30#

J24

HD#29

HA#13

A14#

D29#

L22

HD#28

HA#12

A13#

D28#

M21

HD#27

HA#11

A12#

D27#

H24

HD#26

HA#10

A11#

D26#

G26

HD#25

HA#9

A10#

D25#

L21

HD#24

A9#

D24#

D26

HD#23

HA#7

A8#

D23#

F26

HD#22

HA#6

A7#

D22#

E25

HD#21

HA#5

A6#

D21#

F24

HD#20

HA#4

A5#

D20#

F23

HD#19

HA#3

A4#

D19#

G23

HD#18

A3#

D18#

E24

HD#17

AE25A5A4

D17#

D16#

H22

D25

HD#16

DBR#

D15#

HD#15

J21

HD#14

NC_VCC_SENSE

D14#

D23

HD#13

NC_VSS_SENSE

AD26

AC26

ITP_CLK1

ITP_CLK0

VCC_SENSE

VSS_SENSE

D13#

D12#

D11#

D10#

D9#

C26

H21

G22

B25

C24

HD#8

HD#9

HD#10

HD#11

HD#12

D8#

C23

HD#7

D7#

VID4

AE1

B24

HD#6

VID3

AE2

VID4#

VID3#

D6#

D5#

D22

HD#5

VID2

AE3

C21

HD#4

VID1

AE4

VID2#

VID1#

D4#

D3#

A25

HD#3

A A

BPM#4

BPM#5

BPM#2

BPM#3

BPM#1

BPM#0

8

R82 51

R85 51

R87 51

R88 51

R787 51

R788 51

CPU STRAPPING RESISTORS

VCCP

7

ITP_TDI

-ITP_DBR

ITP_TRST#

ALL COMPONENTS CLOSE TO CPU

PROCHOT#

R79 150 R80 300

R786 X_150

R83 680

6

VCCP

CPU_GD

HBR#0

CPURST#

HINIT#

5

R78 62

R81 150

R84 51

R86 X_300

VCCP

CB9

0.1u

ALL COMPONENTS CLOSE TO CPU

4

CB10

0.1u

VCCP

3

MSI

Title

Size Document Number Rev

Date: Sheet of

mPGA478-B INTEL CPU SOCKET Part1

2

MICRO-STAR

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

MS-6541I1

4 29Tuesday, March 05, 2002

1

0AE0

8

D D

AA11

AA13

AA15

AA17

AA19

AA23

C C

B B

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC22

AC25

VCCP

A10

A12

A14

A16

A18

VSS

AD10

VCC

VSS

AD12

VCC

VSS

AD14

VCC

VSS

AD16

VCC

VSS

AD18

AD21

A20A8AA10

VCC

VCC

VSS

VSS

AD4

AD23

U3B

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA4

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

VSS

AB6

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

AC2

VSS

VSS

VSS

AC5

VSS

AC7

VSS

AC9

VSS

AD1

VSS

VCC

VSS

AD8

AA12

VCC

VSS

AE11

VCC

VSS

AA14

VCC

VSS

AE13

AA16

VCC

VSS

AE15

AA18

VCC

VSS

AE17

7

AA8

VCC

VSS

AE19

AB11

VCC

VSS

AE22

CPU VOLTAGE BLOCK

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AC16

VCC

VSS

AF18

AC18

VCC

VSS

AF20

AC8

AF6

VCC

VSS

AD11

VCC

VSS

AF8

AD13

VCC

VSS

B10

AD15

VCC

VSS

B12

AD17

VCC

VSS

B14

AD19

VCC

VSS

B16

AD7

B18

6

AD9

VCC

VSS

B20

VCC

VSS

AE10

VCC

VSS

B23

AE12

AE14

VCC

VCC

VSS

VSS

B26B4B8

AE16

VCC

VSS

AE18

VCC

VSS

C11

AE20

VCC

VSS

C13

AE6

C15

AE8

VCC

VSS

C17C2C19

AF11

VCC

VSS

AF13

VCC

VSS

AF15

VCC

VSS

C22

AF17

AF19

AF2

AF21

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

C25C5C7C9D12

AF5

VCC

VSS

VCC

VSS

AF7

D14

AF9

VCC

VSS

D16

5

CB228 X_0.1u

VCC5

R811 X_5.1K

CB315 X_0.1u

VCCVID_GD(23)

B11

B13

B15

B17

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

D18

D20

D21D3D24D6D8E1E11

B19B7B9

VCC

VCC

VSS

VSS

VCC

VSS

C10

VCC

VSS

VCC

VSS

C12

VCC5

C14

VCC

VSS

E13

C16

VCC

VSS

E15

EN

C18

VCC

VSS

E17

C20C8D11

VCC

VCC

VSS

VSS

E19

4

U42

1

VIN

VOUT

2

GND

3 4

EN POK

X_TTPM0125

D13

D15

D17

D19D7D9

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

E23

E7E9F10

F12

E4

E26

VCC

VSS

F14

E10

VCC

VSS

F16

5

E12

VCC

VCC

VSS

VSS

F18F2F22

E14

E16

VCC

VSS

E18

VCC

VSS

F25F5F8

E20E8F11

VCC

VCC

VSS

VSS

VCC_VID

VCC

VCC

VSS

VSS

G21G6G24

+

EC1

ELS10/16

F13

F15

F17

VCC

VCC

VSS

VSS

G3H1H23

VCC

VSS

3

2

CPU_IOPLL

CPU_VCCA

10u-1206

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

CB312

YREG431L

3 1

VR8

CB316

0.1u

F19

AF4

F9

VCC

VCC

VCC-VID

VSS

VSS

VSS

VSS

VSS

H26H4J2

AE23

AF3

VCC-IOPLL

VCC-VIDPRG

VSS

VSS

VSS

VSS

J22

J25J5K21

1u-0603

AD20

VSSA

VCCA

SOCKET478

C331

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

2

RN75

330

C39

22u-1206

VSSA

22u-1206

Keep the 22uF cap within 0.6"

of the CPU pin.

Trace Width 12mils, Space 10mils.

VCC5

78

56

34

12

L23 4.7uH-1206

L24 4.7uH-1206

CB313

10u-1206

C40

CB317

0.1u

1

VCCP

CPU DECOUPLING CAPACITORS

VCCP VCCP

A A

CB12

10u-1206

CB19

10u-1206

CB26

10u-1206

CB33

10u-1206

CB40

10u-1206

CB47

10u-1206

CB53

10u-1206

Place 14 pcs 1206 size cap

north side of processor

8

CB13

10u-1206

CB20

10u-1206

CB27

10u-1206

CB34

10u-1206

CB41

10u-1206

CB48

10u-1206

CB54

10u-1206

CB14

10u-0805

CB21

10u-0805

CB28

10u-0805

CB35

10u-0805

CB42

10u-0805

CB49

10u-0805

CB55

10u-0805

CB18

10u-0805

CB25

10u-0805

PLACE CAPS WITHIN CPU CAVITY

7

VCCPVCCP VCCP

6

CB15

10u-0805

CB22

10u-0805

CB29

10u-0805

CB36

10u-0805

CB43

10u-0805

CB50

10u-0805

CB56

10u-0805

CB59

10u-0805

CB32

10u-0805

VCCP

Place these caps on south

side of processor

CB39

10u-0805

CB46

10u-0805

CB52

10u-0805

CB57

10u-0805

CB60

10u-0805

CB58

10u-0805

5

CB16

0.1u

CB24

0.1u

CB31

0.1u

4

VCCP

+

+

Solder side

3

CT4

X_150u-2.5V

CT5

X_150u-2.5V

MSI

Title

Size Document Number Rev

Date: Sheet of

2

C41 0.1u

VCCP

C42 X_0.1u

VCCP

MICRO-STAR

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

mPGA478-B INTEL CPU Part2

MS-6541I1

VCC5

/N

VCC5

5 29Tuesday, March 05, 2002

1

0AE0

5

HA#[3..31](4) HD#[0..63] (4)

* Length must be matched

within +/-0.1"of the Strobe

Signals

D D

HBR#0(4)

HBNR#(4)

HBPRI#(4)

HLOCK#(4)

HADS#(4)

HREQ#[0..4](4)

C C

HIT#(4)

HITM#(4)

HDEFER#(4)

HTRDY#(4)

HRS#[0..2](4)

HDBSY#(4)

HDRDY#(4)

HADSTB#0(4)

HADSTB#1(4)

HDSTBN#0(4)

HDSTBP#0(4)

HDSTBN#1(4)

HDSTBP#1(4)

HDSTBN#2(4)

HDSTBP#2(4)

HDSTBN#3(4)

HDSTBP#3(4)

B B

HINV#[0..3](4)

MCHCLK(3)

MCHCLK#(3)

R94 24.9_1%

R95 24.9_1%

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HINV#0

HINV#1

HINV#2

HINV#3

HY_RCOMP

HX_RCOMP

U4A

W31

HA3#

AA33

HA4#

AB30

HA5#

V34

HA6#

Y36

HA7#

AC33

HA8#

Y35

HA9#

AA36

HA10#

AC34

HA11#

AB34

HA12#

Y34

HA13#

AB36

HA14#

AC36

HA15#

AC31

HA16#

AF35

HA17#

AD36

HA18#

AD35

HA19#

AE34

HA20#

AD34

HA21#

AE36

HA22#

AF36

HA23#

AE33

HA24#

AF34

HA25#

AG34

HA26#

AG36

HA27#

AE31

HA28#

AH35

HA29#

AG33

HA30#

AG31

HA31#

U33

BREQ0#

T34

BNR#

M34

BPRI#

T35

HLOCK#

T36

ADS#

V36

HREQ0#

AA31

HREQ1#

W33

HREQ2#

AA34

HREQ3#

W35

HREQ4#

P36

HIT#

M36

HITM#

N36

DEFER#

V30

HTRDY#

R36

RS0#

U34

RS1#

P34

RS2#

U31

DBSY#

U36

DRDY#

AB35

HAD_STB0#

AF30

HAD_STB1#

N31

HD_STBN0#

L31

HD_STBP0#

G33

HD_STBN1#

J34

HD_STBP1#

C30

HD_STBN2#

E29

HD_STBP2#

D25

HD_STBN3#

E25

HD_STBP3#

N33

DINV_0#

C35

DINV_1#

B33

DINV_2#

C26 H30

DINV_3# HD_VREF0

K30

HCLKP

J31

HCLKN

V35

HY_RCOMP

B28

HX_RCOMP

HOST

Trace 10 mils & 7mils space < 0.5"

BAV99

HL0

HL1

HL2

HL3

HL4

HL5

3

D2

HL[0..5](9)

HL_STB(9)

HL_STB#(9)

A A

CRT_B(26)

CRT_B#(26)

CRT_G(26)

CRT_G#(26)

CRT_R(26)

CRT_R#(26)

VCC_AGP

BAV99

D1

5

AA7

HI0

AB8

AC7

AC5

AD8

AF4 AD3

AD4

AC4

G15

H16

E15

F16

C15

D16

2

2

2

3

3

1

1

1

HUB LINK

HI1

HI2

HI3

HI4

HI5 HI_REF

HI_STBS

HI_STBF

VGA

Brookdale_MCH

D3

BAV99

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

4

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

GCLKIN

RSTIN#

CPURST#

PWROK

HD_VREF1

HD_VREF2

HA_VREF

HCC_VREF

HY_SWNG

HX_SWNG

HI_SWING

HL_RCOMP

DDCA_DATA

DDCA_CLK

HSYNC

VSYNC

DREFCLK

REFSET

4

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

3

HD#0

T30

HD#1

R33

HD#2

R34

HD#3

N34

HD#4

R31

HD#5

L33

HD#6

L36

HD#7

P35

HD#8

J36

HD#9

K34

HD#10

K36

HD#11

M30

HD#12

M35

HD#13

L34

HD#14

K35

HD#15

H36

HD#16

G34

HD#17

G36

HD#18

J33

HD#19

D35

HD#20

F36

HD#21

F34

HD#22

E36

HD#23

H34

HD#24

F35

HD#25

D36

HD#26

H35

HD#27

E33

HD#28

E34

HD#29

B35

HD#30

G31

HD#31

C36

HD#32

D33

HD#33

D30

HD#34

D29

HD#35

E31

HD#36

D32

HD#37

C34

HD#38

B34

HD#39

D31

HD#40

G29

HD#41

C32

HD#42

B31

HD#43

B32

HD#44

B30

HD#45

B29

HD#46

E27

HD#47

C28

HD#48

B27

HD#49

D26

HD#50

D28

HD#51

B26

HD#52

G27

HD#53

H26

HD#54

B25

HD#55

C24

HD#56

B23

HD#57

B24

HD#58

E23

HD#59

C22

HD#60

G25

HD#61

B22

HD#62

D24

HD#63

G23

AE7

RSTIN#

PWROK

HL6

HL7

HL8

HL9

HL10

HUB_MREF

HI_SWING

HL_RCOMP

R99 2.7K

R100 2.7K

3VDDCDA

3VDDCCL

HSYNC

VSYNC

DOT_CLK

REFSET

R593 0

R819 33

X_10pC294

HVREF

HSWNG

R98

R594 47

R595 47

R103 121_1%

68.1_1%

AJ31

D22

E7

H24

D27

AD30

P30

Y30

H28

AE4

HI6

AE5

HI7

AF3

HI8

AE2

HI9

AF2

HI10

AD2

AC2

C7

D7

B7

C6

D14

B16

MCH_66 (3)

PCIRST#1 (3)

CPURST# (4,11)

PWR_GD (20)

Trace 10 mils &

7mils space < 0.5"

VCC_AGP

VCC3

BSEL0(4)

3VDDCDA (26)

3VDDCCL (26)

3V_HSYNC (26)

3V_VSYNC (26)

DOT_CLK (3)

VCC_AGP MEM_STR

HL[6..10] (9)

VCCA_SM

VCC_AGP

VCC_AGP

VCCA_DPLL

VCC3

R101 8.2K

R102

8.2K

3

CB71 0.1u

U4C

A3

VCC_AGP

A7

C1

D4

D6

G1

K6

L1

L9

P6

R1

R9

T14

V14

W9

Y14

V6

AD6

AC9

AB14

AC1

AE3

W19

Y19

AA19

T20

W20

AB20

U21

W21

AA21

T22

V22

Y22

AB22

A9

B9

C9

D9

E9

B10

C10

D10

F10

H10

A11

B11

C11

D11

E11

G11

J11

B12

C12

D12

F12

H12

G13

J13

H14

P14

J15

P15

P18

AB18

AB16

AA17

Y16

W18

W17

V19

V16

U19

U17

T18

T16

P17

P16

AG2 AT20

AG1

AD14

A15

B14

A13

C14

B15

B6

PSBSEL

Y3

Y2

AA2

AA4

AA3

AA5

W7

Y4

Y8

A37

AB2

AB3

POWER

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_HI

VCC_HI

VCC_HI

VCC_HI

VCC_HI

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA_SM VCCQ_SM

VCCA_SM

VCC_HI

VCCA_DAC

VCCA_DAC

VCCA_DPLL

VSSA_DAC

VSSA_DAC

VCC_GPIO

PSBSEL

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

Other

Brookdale_MCH

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VCCA_FSB

VCCQ_SM

VCCQ_SM

VTT_DECAP

VTT_DECAP

VTT_DECAP

VTT_DECAP

VTT_DECAP

2

AH8

AK8

AG9

AJ9

AL9

AD22

AM22

AJ23

AL37

AU9

AK10

AD24

AJ11

AL11

AU25

AM26

AU13

AM14

AJ27

AJ1

AL1

AJ15

AP15

AU29

AH2

AJ2

AK2

AL2

AM30

AH3

AJ3

AK3

AL3

AH4

AJ4

AK4

AL4

AU17

AD18

AJ5

AL5

AU5

AM18

AJ19

AK32

AU33

AH6

AK6

AD20

AP20

AG7

AJ7

AL7

AP7

B18

C18

D18

H18

B19

C19

D19

E19

G19

J19

B20

C20

D20

F20

H20

P20

P22

P24

T24

V24

AB24

F18

Y24

A17

AT21

AU21

G37

L37

R37

AC37

A31

A2

NC

A36

NC

AH34

NC

AJ35

NC

AT1

NC

AT37

NC

AU1

NC

AU2

NC

AU36

NC

AU37

NC

B1

NC

B37

NC

2

VCCP

VCCA_FSB

VCCQ_SM

VTT_CAP1

VTT_CAP2

VTT_CAP3

VTT_CAP4

VTT_CAP5

Place <0.1"

Title

Size Document Number Rev

Date: Sheet of

GMCH REFERENCE BLOCK

VCCA_FSB

VCCA_DPLL

VCCA_SM

VCCQ_SM

Place Cap. as Close as possible to

GMCH

CB66 0.1u

CB67 0.1u

CB68 0.1u

CB69 0.1u

CB70 0.1u

Place 0.01uF Cap. as Close as possible to

GMCH< 0.25"

Trace width 12 mils & 10mils space

MSI

Brookdale-G GMCH-1 (HOST & HI & VGA)

CB62

0.1u_X7R

+

CB63

C46

X_0.1u

680uF

CB64

0.1u_X7R

CB270

0.1u_X7R

HSWNG

HVREF

, Trace width 12 mils & 10mils space

Keep the voltage divider within 3" of the

GMCH pin.

HI_SWING

HUB_MREF

1

L25 0.82uH_0603

C284

22u-1206

L26

L26_1

10uH-0805

L27 1uH-0805

CT10

+

100u_25V

L28 0.68uH-0805

C285

4.7u-0805

C285_2

R520

1

VCCP

R89

301 1%

C48

0.01u

C50

0.1u

MICRO-STAR

R90

150 1%

VCCP

R91

49.9_1%

R92

100_1%

C52

0.01u

C53

0.01u

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

MS-6541I1

1

I=30mA

R605

I=35mA

I=500mA

I=150mA

C47

0.01u

C51

0.1u

C54

0.1u

6 29Tuesday, March 05, 2002

1

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

MEM_STR

R93

226_1%

R96

100_1%

R97

100_1%

0AE0

5

MDQ0

MDQ1

MDQ2

MDQ3

MDQ4

MDQ5

MDQ6

MDQ7

MDQ8

MDQ9

MDQ10

R118

X_0_Solder

MDQ11

MDQ12

MDQ13

MDQ14

MDQ15

MDQ16

MDQ17

MDQ18

MDQ19

MDQ20

MDQ21

MDQ22

MDQ23

MDQ24

MDQ25

MDQ26

MDQ27

MDQ28

MDQ29

MDQ30

MDQ31

MDQ32

MDQ33

MDQ34

MDQ35

MDQ36

MDQ37

MDQ38

MDQ39

MDQ40

MDQ41

MDQ42

MDQ43

MDQ44

MDQ45

MDQ46

MDQ47

MDQ48

MDQ49

MDQ50

MDQ51

MDQ52

MDQ53

MDQ54

MDQ55

MDQ56

MDQ57

MDQ58

MDQ59

MDQ60

MDQ61

MDQ62

MDQ63

5

SRC_O#

SRC_I#

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

D D

C C

Trace lengh

must as short

as possible

for SRCVEN

Trace width 12

mil with 12 mil

space for

SM_VREF.

B B

A A

DDR_VREF

GAD[0..31](16)

GC_BE#[0..3](16)

AR10

AP10

AT11

AT13

AT14

AT10

AR12

AR14

AP14

AT15

AP16

AT18

AT19

AR16

AT16

AP18

AR20

AR22

AP22

AP24

AT26

AT22

AT23

AT25

AR26

AP26

AT28

AR30

AP30

AT27

AR28

AT30

AT31

AR32

AT32

AR36

AP35

AP32

AT33

AP34

AT35

AN36

AM36

AK36

AJ36

AP36

AM35

AK35

AK34

AK24

AL23

AN4

AP2

AT3

AP5

AN2

AP3

AR4

AT4

AT5

AR6

AT9

AT6

AP6

AT8

AP8

W4

W5

U4B

V4

V2

U5

U4

U2

V3

T2

T3

T4

R2

R5

R7

T8

P3

P8

K4

K2

J2

M3

L5

L4

H4

G2

K3

J4

J5

J7

H3

K8

G4

R4

N4

M2

H2

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SRCVEN_OUT#

SRCVEN_IN#

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE0#

G_C/BE1#

G_C/BE2#

G_C/BE3#

DDR

AGP

Brookdale_MCH

SCMDCL_K0

SCMDCLK_0#

SCMDCLK_1

SCMDCLK_1#

SCMDCLK_2

SCMDCLK_2#

SCMDCLK_3

SCMDCLK_3#

SCMDCLK_4

SCMDCLK_4#

SCMDCLK_5

SCMDCLK_5#

SMX_RCOMP

SMX_RCOMP

SMY_RCOMPSM_VREF

G_DEVSEL#

AGP_RCOMP

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

SMAB1

SMAB2

SMAB4

SMAB5

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

SCKE0

SCKE1

SCKE2

SCKE3

SCS0#

SCS1#

SCS2#

SCS3#

SBA_0

SBA_1

SRAS#

SCAS#

SWE#

G_FRAME#

G_IRDY#

G_TRDY#

G_STOP#

G_PAR

G_REQ#

G_GNT#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

PIPE#

RBF#

WBF#

AGP_VREF

4

MSDQS0

MSDQS1

MSDQS2

MSDQS3

MSDQS4

MSDQS5

MSDQS6

MSDQS7

MSDM0

MSDM1

MSDM2

MSDM3

MSDM4

MSDM5

MSDM6

MSDM7

MSCKE0

MSCKE1

MSCKE2

MSCKE3

MSCS0#

MSCS1#

MSCS2#

MSCS3#

DCLK0

DCLK0#

DCLK1

DCLK1#

DCLK2

DCLK2#

DCLK3

DCLK3#

DCLK4

DCLK4#

DCLK5

DCLK#5

MSBS0

MSBS1

MRAS#

MCAS#

MWE#

SMX_RCOMP

SMY_RCOMP

R120 30.1_1%

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

CB72 0.1u

R121 40.2_1%

Place < 0.5"

DDRMAA0

DDRMAA1

DDRMAA2

DDRMAA3

DDRMAA4

DDRMAA5

DDRMAA6

DDRMAA7

DDRMAA8

DDRMAA9

DDRMAA10

DDRMAA11

DDRMAA12

DDRMAB1

DDRMAB2

DDRMAB4

DDRMAB5

R119

30.1_1% C56 0.1uC55 0.1u

MSCS0# (14,15)

MSCS1# (14,15)

MSCS2# (14,15)

MSCS3# (14,15)

DCLK0 (14)

DCLK0# (14)

DCLK1 (14)

DCLK1# (14)

DCLK2 (14)

DCLK2# (14)

DCLK3 (14)

DCLK3# (14)

DCLK4 (14)

DCLK4# (14)

DCLK5 (14)

DCLK5# (14)

MSBS0 (14)

MSBS1 (14)

MRAS# (14,15)

MCAS# (14,15)

MWE# (14,15)

VTT_DDR

GFRAME#(16)

GIRDY# (16)

GTRDY# (16)

GDEVSEL# (16)

GSTOP# (16)

GPAR (16)

GREQ# (16)

GGNT# (16)

SBA[0..7] (16)

SB_STB (16)

SB_STB#(16)

ST[0..2](16)

GAD_STB0(16)

GAD_STB#0 (16)

GAD_STB1(16)

GAD_STB#1 (16)

PIPE# (16)

RBF# (16)

WBF# (16)

AGPREF (16)

DDRMAB1 (14,15)

DDRMAB2 (14,15)

DDRMAB4 (14,15)

DDRMAB5 (14,15)

MSCKE[0..3] (14,15)

C57 0.1u

AL25

AN25

AP23

AK20

AL19

AL17

AP19

AP17

AN17

AK16

AK26

AL15

AN15

AP25

AN23

AN19

AK18

AR2

AT7

AT12

AT17

AR24

AT29

AT34

AL36

AP4

AR8

AP12

AR18

AT24

AP28

AR34

AL34

AP13

AN13

AK14

AL13

AL29

AP31

AK30

AN31

AL21

AK22

AN11

AP11

AM34

AL33

AP21

AN21

AP9

AN9

AP33

AN34

AN27

AP27

AK28

AN29

AP29

AF10

AD16

AJ34AM2

M4

N7

N5

N2

P2

P4

D5

B5

C3

C2

D3

D2

E4

E2

F3

F2

F4

E5

C4

ST0

B4

ST1

B3

ST2

V8

U7

M8

L7

H8

G7

G5

W2

AGP_RCOMP

L2

4

3

DDRMAA[0..12] (14,15)

Trace width 12 mil

with 10 mil space.

Place 0.1uF <1" to GMCH

3

2

1

DDR SERIAL RESISTORS

DDRMD1

RN3 10

DDRMD[0..63](14,15)

DDRMD5

DDRMD4

DDRMD0

DDRMD3

DDRMD7

DDRMD6

DDRMD2

DDRMD13

DDRMD12

DDRMD9

DDRMD8

DDRMD11

DDRMD10

DDRMD15

DDRMD14

DDRMD21

DDRMD17

DDRMD16

DDRMD20

DDRMD23

DDRMD19

DDRMD22

DDRMD18

DDRMD29

DDRMD28

DDRMD24

DDRMD31

DDRMD27

DDRMD30

DDRMD26

DDRMD37

DDRMD33

DDRMD36

DDRMD32

DDRMD35

DDRMD39

DDRMD38

DDRMD34

DDRMD41

DDRMD45

DDRMD44

DDRMD40

DDRMD47

DDRMD43

DDRMD46

DDRMD42

DDRMD53

DDRMD52

DDRMD49

DDRMD48

DDRMD51

DDRMD50

DDRMD55

DDRMD54

DDRMD57

DDRMD61

DDRMD56

DDRMD60

DDRMD59

DDRMD63

DDRMD58

DDRMD62

MSDM0 SDM0

MSDM1

MSDM2

MSDM3

MSDM4

MSDM5

MSDM6

MSDM7

MSDQS0

MSDQS1

MSDQS2

MSDQS3

MSDQS4

MSDQS5

MSDQS6

MSDQS7

2

7 8

5 6

3 4

1 2

RN5 10

7 8

5 6

3 4

1 2

RN7 10

7 8

5 6

3 4

1 2

RN9 10

7 8

5 6

3 4

1 2

RN10 10

7 8

5 6

3 4

1 2

RN12 10

7 8

5 6

3 4

1 2

RN13 10

7 8

5 6

3 4

1 2

RN14 10

7 8

5 6

3 4

1 2

RN15 10

7 8

5 6

3 4

1 2

RN16 10

7 8

5 6

3 4

1 2

RN18 10

7 8

5 6

3 4

1 2

RN20 10

7 8

5 6

3 4

1 2

RN21 10

7 8

5 6

3 4

1 2

RN22 10

7 8

5 6

3 4

1 2

RN23 10

7 8

5 6

3 4

1 2

RN24 10

7 8

5 6

3 4

1 2

R609 10

R610 10

R611 10

R612 10

R613 10

R614 10

R615 10

R616 10

R110 10

R111 10

R112 10

R113 10

R114 10

R115 10

R116 10

R117 10

MSI

Title

Size Document Number Rev

Date: Sheet of

MDQ1

MDQ5

MDQ4

MDQ0

MDQ3

MDQ7

MDQ6

MDQ2

MDQ13

MDQ12

MDQ9

MDQ8

MDQ11

MDQ10

MDQ15

MDQ14

MDQ21

MDQ17

MDQ16

MDQ20

MDQ23

MDQ19

MDQ22

MDQ18

MDQ25DDRMD25

MDQ29

MDQ28

MDQ24

MDQ31

MDQ27

MDQ30

MDQ26

MDQ37

MDQ33

MDQ36

MDQ32

MDQ35

MDQ39

MDQ38

MDQ34

MDQ41

MDQ45

MDQ44

MDQ40

MDQ47

MDQ43

MDQ46

MDQ42

MDQ53

MDQ52

MDQ49

MDQ48

MDQ51

MDQ50

MDQ55

MDQ54

MDQ57

MDQ61

MDQ56

MDQ60

MDQ59

MDQ63

MDQ58

MDQ62

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDM0 (15)

SDM1 (15)

SDM2 (15)

SDM3 (15)

SDM4 (15)

SDM5 (15)

SDM6 (15)

SDM7 (15)

Brookdale-G GMCH-2 (DDR & AGP)

SDQS[0..7] (14,15)

MICRO-STAR

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

MS-6541I1

1

7 29Tuesday, March 05, 2002

0AE0

AA18

AL31

AR31

AU31

AB32

AD32

AF32

AH32

AB19

AD19

AR19

AM32

AJ33

AN33

AR33

AA20

AM20

AB21

AD21

AJ21

AR21

U18

V18

Y18

F32

H32

K32

M32

P32

T32

V32

Y32

AM4

A5

C5

AG5

AN5

AR5

P19

T19

A33

C33

F6

H6

M6

T6

Y6

AB6

AF6

AM6

U20

V20

Y20

A21

B21

C21

D21

E21

G21

J21

D34

W34

A35

E35

G35

J35

L35

AN7

AR7

AU7

B8

C8

D8

F8

P21

T21

V21

Y21

F22

H22

U22

W22

U29R29

J29

L29

N29

U4D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSVSS

FOOTPRINT REV1.5

C29

A29

VSS

U3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AT2E3G3J3L3N3R3

VSS

VSS

GMCH DECOUPLING CAPACITOR

C17

D17

E17

G17

J17

T17

V17

AH30

C31

AC3

AG3

AM3

AN3

AR3

AU3

AB4

AG4

Y17

AB17

AD17

AJ17

AR17

AR9

AM10

AR23

AU23

F24

R24

VSS

VSS

VSS

VSS

VSS

VSS

U24

VSS

AM24

VSS

VSS

A25

AC24

VSS

AA24

VSS

W24

VSS

VSS

B17

AM16

VSS

AA16

VSS

W16

VSS

AJ29

AR29

F30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U16

VSS

W3

VSS

VSS

AG29

VSS

AE29

VSS

AC29

VSS

AA29

VSS

W29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA22

N35

R35

U35

AA35

AC35

AE35

AG35

AL35

AN35

AR35

AU35

B36

W36

AF8

AM8

G9

J9

N9

U9

AA9

AE9

A23

C23

D23

J23

P23

AD23

AH36

AT36

C37

E37

J37

U37

AA37

AE37

AG37

AJ37

C25

AN37

AR37

AR11

AU11

J25

AJ25

AR25

F26

AK12

AM12

B13

C13

D13

E13

A27

C27

J27

AJ13

AR13

F14

R14

U14

W14

AA14

AC14

AL27

AR27

AU27

F28

AM28

E1

J1

N1

U1

AA1

AE1

AN1

AR1

B2

D15

AD15

AR15

AU15

N37

C16

VCC_AGP

C58

Pin A5

0.1u

CB74

Pin J1

0.1u

CB75

Pin E1

0.1u

CB77

Pin N1

0.1u

CB80

Pin U1

0.1u

Place decoupling cap

close to GMCH AGP

Interface < 0.1"

VCC_AGP

CB73

0.1u

C142

0.01u

Place decoupling cap

close to GMCH Core

Logic Interface <

0.1"

VCC_AGP

CB76

Pin AA1

0.1u

CB79

Pin AE1

0.1u

Place decoupling cap

close to GMCH

Hub-Link Interface<

0.1"

VCCP

CB84

0.1u

CB86

0.1u

CB89

0.1u

CB91

0.1u

CB93

0.1u

Place decoupling cap

close to GMCH CPU

Interface < 250mil

in the Vtt corridor

VCC_AGP

+

CT11

1000UF_6V

Place Bulk cap for Core Logic,

AGP & Hub Link Interface

MEM_STR

+

CT13

470u

+

CT72

470u

Place Bulk cap between

GMCH & DIMM slot

VCC5

0.1uC67

0.1uC69

MEM_STR

+

MEM_STR

Place decoupling cap

close to GMCH Memory

Interface < 0.1", with

18 mil trach width

+

CT14

470u

VCC_AGP

C137

0.01u

CB88

0.1u

Place decoupling cap

close to GMCH DAC

Interface< 0.1"

CB81

Pin AL37

0.1u

CB82

Pin AU33

0.1u

CB83

Pin AU29

0.1u

CB85

Pin AU25

0.1u

CB87

0.1u

Pin AU17

CB90

Pin AU13

0.1u

CB92

0.1u

Pin AU9

CB94

0.1u

Pin AU5

VCCP

CT15

470u

CB276

10u-1206

+

CT16

470u

CB277

10u-1206

Pin B14

Pin A15

MEM_STR

VCCSM

AH26

AH22

VCCSM

VCCSM

AH18

AH14

VCC_AGP

VCCSM

VCCSM

VCCSM

AH12

AH10

VCCAHI

AD10

VCCAGP

VCCAGP

AB10

V10

VCCAGP

P10

K10

VCC

VCCP

K12

VCC

K14

VCC

K16

VCC

VTTFSB

K18

K20

VTTFSB

VTTFSB

VTTFSB

K22

K26

VTTFSB

M28

T28

VTTFSB

VTTFSB

VTTFSB

Y28

AD28

VSS

AH24

VSS

AH20

VSS

AH16

Y10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T10

M10

K24

K28

P28

V28

AB28

AF28

AH28

VCC5 VCC3

0.1uC77

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

Broodale GMCH(VSS)

MS-6541I1

8 29Tuesday, March 05, 2002

0AE0

AD[0..31](17,24)

C_BE#[0..3](17,24)

DEVSEL#(17,24)

FRAME#(17,24)

IRDY#(17,24)

TRDY#(17,24)

STOP#(17,24)

PAR(17,24)

PLOCK#(17)

SERR#(17,24)

PERR#(17,24)

PME#(16,17,24)

ICH_PCLK(3)

PCIRST#(3)

EE_EECS(25)

EE_DIN(25)

EE_DOUT(25)

EE_SHCLK(25)

Pin A1 Pin H1

VCC3

Pin A4

CB103

0.1u

0.1u

ICH4 PCI / HUB LINK / CPU / LAN / INTERRUPT SIGNALS

VCC_AGP VCC3_SB

K12

K18

K22

P10

T18

U19

VCC1_5

VCC1_5

VCC1_5

GND3

GND4

GND5

A20

A22A4AA12

VCC1_5

VCC1_5

VCC1_5

GND6

GND7

GND8

AA16

V14A5AC17

VCC1_5

VCC1_5

GND9

GND10

AA22

AA3

AA9

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

LAN_RST#

EE_EECS

EE_DIN

EE_DOUT

EE_SHCLK

H5

J3

H3

K1

G5

J4

H4

J5

K2

G2

L1

G4

L2

H2

L3

F5

F4

N1

E5

N2

E3

N3

E4

M5

E2

P1

E1

P2

D3

R1

D2

P4

J2

K4

M4

N4

M3

F1

L5

F2

F3

G1

M2

K5

L4

W2

B5

E8

P5

U5

Y5

D10

D11

A8

C12

K10

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE0#

C/BE1#

C/BE2#

C/BE3#

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

PLOCK#

SERR#

PERR#

PME#

GPIO0/REQA#

GPIO16/GNTA#

PCICLK

PCIRST#

LAN_RST#

EE_CS

EE_DIN

EE_DOUT

EE_SHCLK

GND1

GND2

A1

A16

A18

ICH4 DECOUPLING CAPACITORS

Pin AC10

Pin T1

0.1u

CB105

0.1u

Pin AC18

0.1u

CB107

0.1u

VCC3_3

GND11

GND12

AB20

AB7

AC8B2H18H6J1

VCC3_3

VCC3_3

VCC3_3

GND13

GND14

GND15

AC1

AC10

AC14

VCC3_3

VCC3_3

VCC3_3

GND16

GND17

GND18

AC18

AC23

VCC3

J18K6M10

VCC3_3

VCC3_3

GND19

GND20

AC5

B12

P12P6U1

VCC3_3

GND21

B16

B18

VCC3_3

VCC3_3

GND22

GND23

B20

B22B9C15

V10

V16

VCC3_3

VCC3_3

VCC3_3

GND24

GND25

GND26

V18

VCC3_3

GND27

C17

C19

VCC1_5SB

E20

E13

E12

VCCSUS1_5

VCCSUS1_5

VCCSUS1_5

GND28

GND29

GND30

GND31

C21

C23C6D1

F14

G18R6T6

VCCSUS1_5

VCCSUS1_5

VCCSUS1_5

GND32

GND33

GND34

D12

D15

D17

U6

E11

F10

VCCSUS1_5

VCCSUS1_5

VCCSUS3_3

VCCSUS3_3

GND35

GND36

GND37

GND38

GND39

D19

D21

D23D4D8

F15

F16

F17

F18

K14V7V8

VCCSUS3_3

VCCSUS3_3

VCCSUS3_3

VCCSUS3_3

VCCSUS3_3

GPIO1/REQB#/REQ5#

GPIO17/GNTB#/GNT5#

GND43

GND40

GND41

GND42

GND44

E14

D22

E10

E16

V9

CPUSLP#

VCCSUS3_3

VCCSUS3_3

VCCSUS3_3

STPCLK#

A20GATE

THRMTRIP#

HI_SWING

LAN_RSTSYNC

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_TXD0

LAN_TXD1

LAN_TXD2

GND45

GND46

GND47

E17

E18

E19

HL_STB#

HLCOMP

APICCLK

LAN_CLK

Place one 0.1u close to ICH4 <100 mil

Pin K23 Pin C23 Pin A16 Pin AC1Pin T23 Pin N23 Pin C22 Pin C22

VCC_AGP

CB96

0.1uCB104

CB99

0.1uCB102

VCC_AGP VCC_AGP

C83

CB97

0.1u

0.1u

FOR Core Logic FOR Hub Interface FOR PLL

A20M#

FERR#

IGNNE#

INIT#

INTR

NMI

SMI#

RCIN#

HI10

HI11

HI_STB

HIREF

PIRQA#

PIRQB#

PIRQC#

PIRQD#

IRQ14

IRQ15

APICD0

APICD1

SERIRQ

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

INT-82801DB

ICH4 STRAPPING RESISTORS

FERR#

R123 62

TRMTRIP#

R124 62

TRIP#_R

U5A

A20M#_R

SLP_R

FERR#

IGNNE#_R

HINIT#_R

INTR_R

NMI_R

HSMI#_R

STPCLK#_R

KB_RST#

A20GATE#

TRIP#_R

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HL11

R521

HLCOMP

HI_ISWING

HUB_IREF

APICCLK

APIC_D0

APIC_D1

SERIRQ

PREQ#0

PREQ#1

PREQ#2

PREQ#3

PREQ#4

REQB#REQA#

PGNT#0

PGNT#1

PGNT#2

PGNT#3

PGNT#4

ELAN_CLK

ELAN_SYNC

ELAN_RXD0

ELAN_RXD1

ELAN_RXD2

ELAN_TXD0

ELAN_TXD1

ELAN_TXD2

R632 62

R633 62

R634 62

R635 62

R636 62

R637 62

R122 62

R638 62

R733 X_0

60.4_1%

R130 68.1_1%

A20M# (4)

SLP# (4)

FERR# (4)

IGNNE# (4)

HINIT# (4,13)

INTR (4)

NMI (4)

HSMI# (4)

STPCLK# (4)

KB_RST# (11)

A20GATE#(11)

TRMTRIP#(4,11)

HL[0..10] (6)

This resistor less than 0.5"

from ICH use 15 mils trace

HL_STB (6)

HL_STB# (6)

VCC_AGP

INTA# (16,17,24)

INTB# (16,17)

INTC# (17,24)

INTD# (17)

IRQ14 (3)

IRQ15 (3)

SERIRQ (11)

PREQ#[0..4] (17,24)

PGNT#0 (17)

PGNT#1 (17)

PGNT#2 (17)

PGNT#3 (24)

PGNT#4 (24)

ELAN_CLK (25)

ELAN_SYNC (25)

ELAN_RXD0 (25)

ELAN_RXD1 (25)

ELAN_RXD2 (25)

ELAN_TXD0 (25)

ELAN_TXD1 (25)

ELAN_TXD2 (25)

ICH4 REFERENCE VOLTAGE

Place Cap. as Close as possible to ICH4 < 0.25"

Trace width use 12 mils and 10mils space

VCC3_SB

LAN_DIS(11)

2N3904S

AB23

U21

AA21

W21

V22

AB22

V21

W23

V23

U22

Y22

U23

NC

W20

L19

HI0

L20

HI1

M19

HI2

M21

HI3

P19

HI4

R19

HI5

T20

HI6

R20

HI7

P23

HI8

L22

HI9

N22

K21

P21

N20

R23

R22

M23

D5

C2

B4

A3

AC13

AA19

J19

H19

K20

J22

B1

A2

B3

C7

B6

A6

C1

E6

A7

B7

D6

C5

C11

B11

A10

A9

A11

B10

C10

A12

R822 62

SERIRQ

R125 8.2K

KB_RST#

R126 10K

A20GATE#

R127 10K

REQA#

R131 10K

REQB#

R132 10K

APIC_D0

R128 10K

APIC_D1

R129 10K

APICCLK

EE_DOUT

R133 X_10K

HI_ISWING

HUB_IREF

0.01u

C80

C81

0.01u

C79

0.1u

C82

0.1u

LAN Disable Circuit

RSMRST#(11)

LAN_DIS#

R569 8.2K

Q58_B

R570

Q58

10K

If LAN_DIS="L", LAN_RST#=RSMRST#,

If LAN_DIS="H", LAN_RST#="L"

MSI

MICRO-STAR

Brookdale-G ICH4 PCI & HI & LAN

H/W Project Leader : Joey Lee

H/W Project Engineer : Daniel Lee

MS-6541I1

CB95

0.1u

0.01u

C140

VCC1_5SB

CB100

0.1u

CB101

0.1uCB106

Title

Size Document Number Rev

Date: Sheet of

VCC_AGP

R135

226_1%

R136

100_1%

R137

100_1%

U2C

5 6

DM7407-SOIC14

U2F

13 12

DM7407-SOIC14

9 29Tuesday, March 05, 2002

VCCP

VCC3

VCC3_SB

R522

1K

LAN_RST#

0AE0

Loading...

Loading...