A

B

C

D

E

Last Schematic Update Date:

4 4

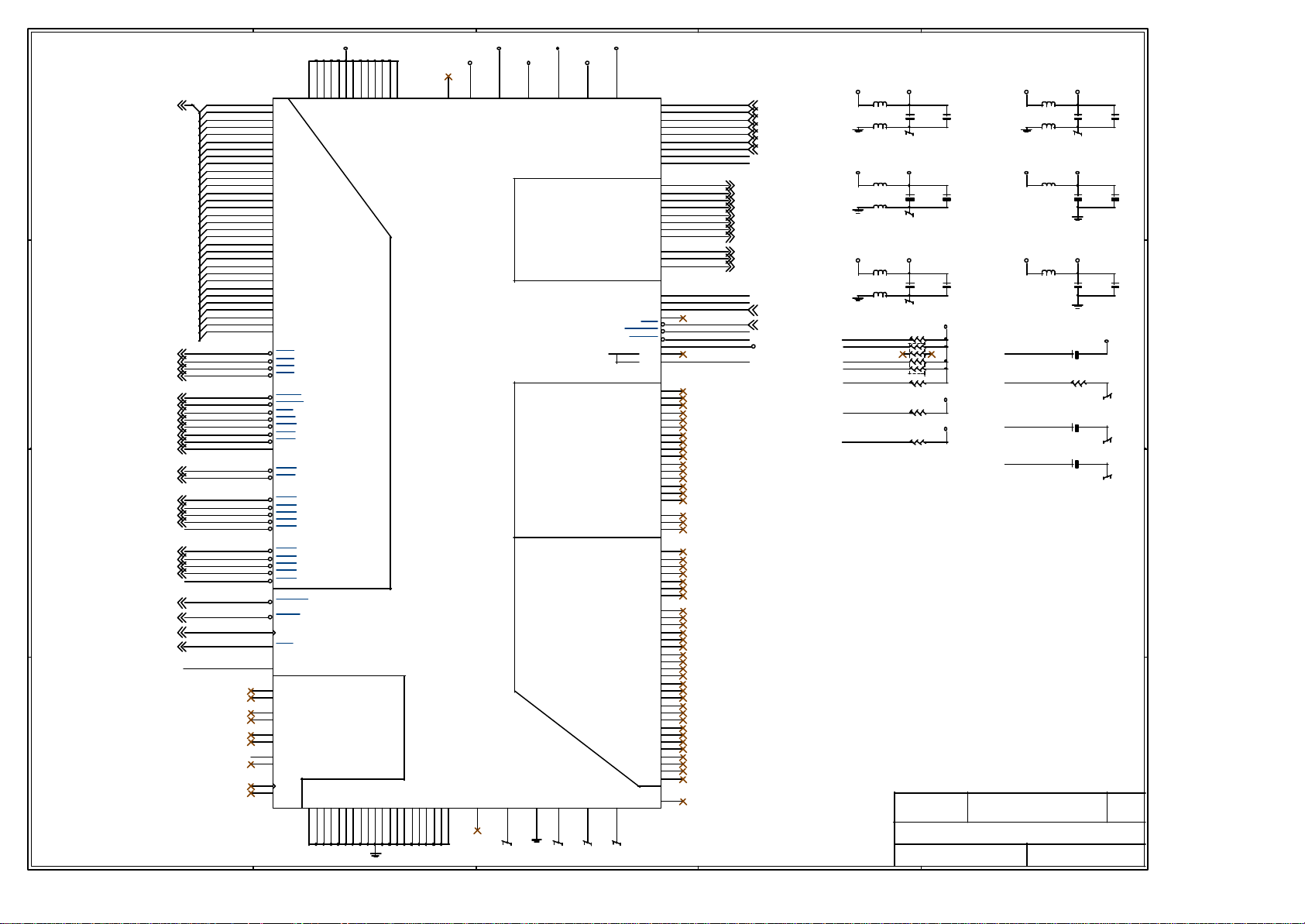

MS-6537

CPU: AMD Socket-462 Processor

System Chipset: VIA KLE133 (North)

3 3

Expansion:

PCI*1 ( With Riser card to Extend to 2)

On Board Device:

2 2

7/25/2001

Version 0A

VT82C686B (South)

AC97 Codec VT1612A

AC97 Codec VT1612A

TITLE

COVER SHEET

AMD-K7 SOCKET-A

NORTH BRIDGE (VIA VT8361)

SOUTH BRIDGE (VIA VT82C686B)

CLOCK SYNTHESIZER

SDRAM DIMMS

PCI SLOTS

TV-OUT

AC'97 CODEC

Audio Port / Audio Amp.

USB HUB & USB Connector

IDE Connector / FAN

COM/LPT PORTS, RI, WOL, WOM & FAN

VGA / PS2 Keyboard & Mouse Connector

VRM 9.0

LINEAR REGULATOR & STR

FRONT PANEL

RTL8100 LAN CHIPSET

SHEET

1

2,3

4,5,6

7,8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

ERP BOM Function Description

1394 TI TSB43AB22

BYPASS CAPACITORS

BLOCK DIAGRAM

GPIO SPEC

MS-6537

History I

1 1

Title

Micro-Star

Document Number

Last Revision Date:

A

B

C

D

MS-6537

Cover Page

Sheet of

E

Rev

00A

29Wednesday, July 25, 2001

1

A

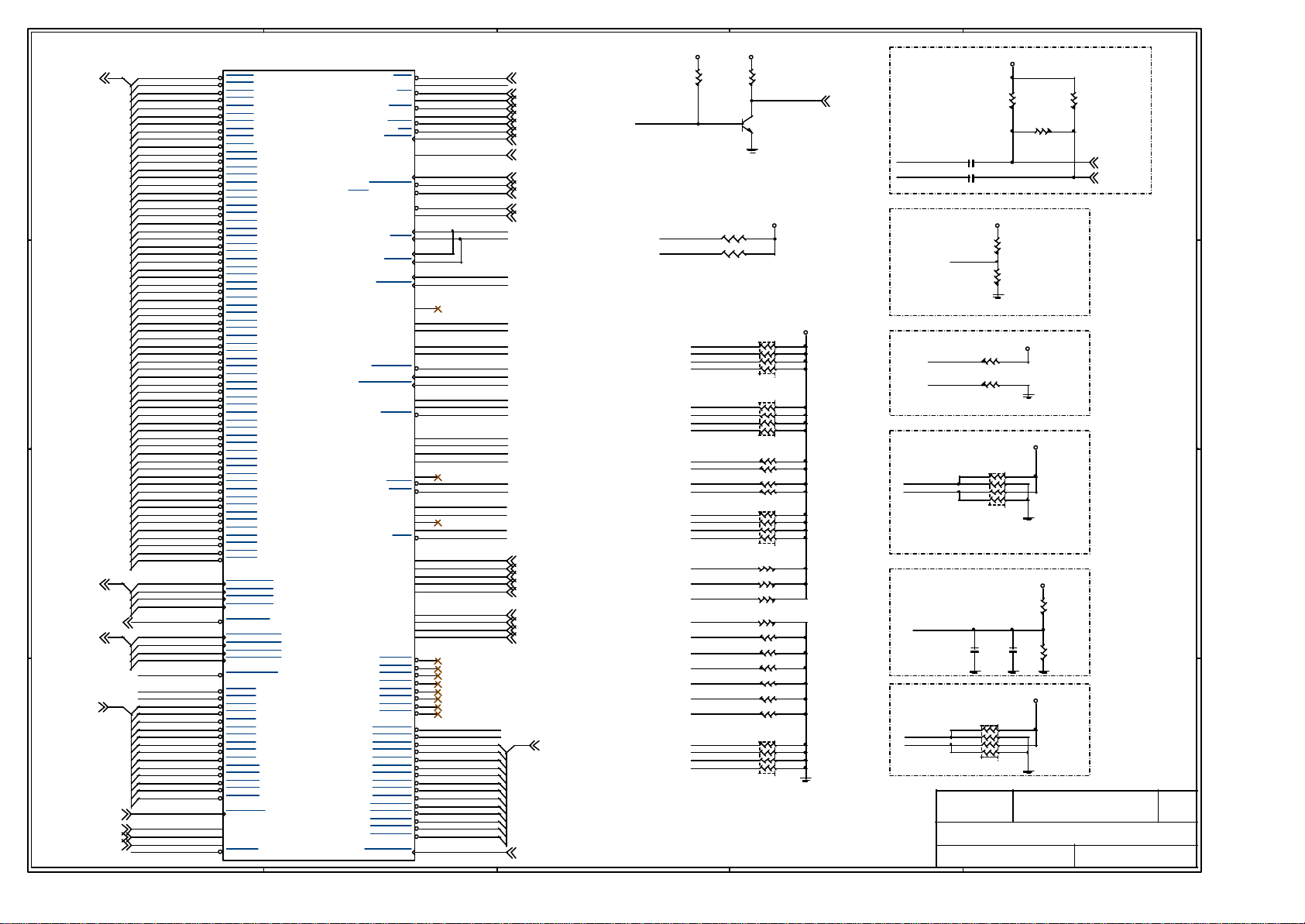

-SDATA[0:63]4

4 4

3 3

2 2

-DICLK[0:3]4

-DIVAL4

-DOCLK[0..3]4

-SDATA0

-SDATA1

-SDATA2

-SDATA3

-SDATA4

-SDATA5

-SDATA6

-SDATA7

-SDATA8

-SDATA9

-SDATA10

-SDATA11

-SDATA12

-SDATA13

-SDATA14

-SDATA15

-SDATA16

-SDATA17

-SDATA18

-SDATA19

-SDATA20

-SDATA21

-SDATA22

-SDATA23

-SDATA24

-SDATA25

-SDATA26

-SDATA27

-SDATA28

-SDATA29

-SDATA30

-SDATA31

-SDATA32

-SDATA33

-SDATA34

-SDATA35

-SDATA36

-SDATA37

-SDATA38

-SDATA39

-SDATA40

-SDATA41

-SDATA42

-SDATA43

-SDATA44

-SDATA45

-SDATA46

-SDATA47

-SDATA48

-SDATA49

-SDATA50

-SDATA51

-SDATA52

-SDATA53

-SDATA54

-SDATA55

-SDATA56

-SDATA57

-SDATA58

-SDATA59

-SDATA60

-SDATA61

-SDATA62

-SDATA63

-DICLK0

-DICLK1

-DICLK2

-DICLK3

-DIVAL

-DOCLK0

-DOCLK1

-DOCLK2

-DOCLK3

-DOVAL

-AIN[2:14]4

1 1

-AICLK4

CFWDRST4

CONNECT4

PROCDRY4

A

-AIN0

-AIN1

-AIN2

-AIN3

-AIN4

-AIN5

-AIN6

-AIN7

-AIN8

-AIN9

-AIN10

-AIN11

-AIN12

-AIN13

-AIN14

CFWDRST

CONNECT

PROCRDY

-FILVAL

AA35

W37

W35

AA33

AE37

AC33

AC37

AA37

AC35

Q37

Q35

G33

G37

G35

Q33

W33

AN33

AE35

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

Y35

U35

U33

S37

S33

Y37

S35

N37

J33

E37

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

E9

A13

C9

A9

C21

A21

E19

C19

C17

A11

A17

A15

J35

E27

E15

C37

A33

C11

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

B

A20M

FERR

INIT

INTR

IGNNE

NMI

RESET

SMI

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TCK

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

B

ZN

ZP

TDI

CPU1A

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

YSKT462P-I

-A20M

FERR

-INIT

INTR

-IGNNE

NMI

-CPURST

-SMI

-STPCLK

APICCLK

APICD0

APICD1

COREFBCOREFB+

CPUCK

-CPUCK

CLKOUT

-CLKOUT

VREFMODE

VREF_SYS

ZN

ZP

-PLLBP

PLLBPCLK

-PLLBPCLK

PLLMON1

PLLMON2

-PLLTEST

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

-DBREQ

-FLUSH

TCK

TDI

TMS

-TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

-AOUT0

-AOUT1

-AOUT2

-AOUT3

-AOUT4

-AOUT5

-AOUT6

-AOUT7

-AOUT8

-AOUT9

-AOUT10

-AOUT11

-AOUT12

-AOUT13

-AOUT14

-AOCLK

-A20M 8

-INIT 8

INTR 8

-IGNNE 8

NMI 8

-CPURST 8

-SMI 8

-STPCLK 8

CPU_PG 21

APICCLK 9

APICD0 8

APICD1 8

COREFB- 19

COREFB+ 19

VID0 19

VID1 19

VID2 19

VID3 19

VID4 19

FID0 3

FID1 3

FID2 3

FID3 3

-AOUT[2:14] 4

-AOCLK 4

C

VCC_CORE

VCC3

R18

680

R7

4.7K

-FERR

FERR

C

B

E

Q3

2N3904S

VCC2_5

APICD0

R6 1K

APICD1

R5 1K

D

-FERR 8

Near socket-A

CPUCK

-CPUCK

104PC54

104PC48

VREFMODE

VCC_CORE

VCC_CORE

R69

X_1K

NOPOP

R57

270

R78

60.4RST

X_301RST

E

R72

60.4RST

R76

CPUCLK 9

-CPUCLK 9

VREFMODE=Low=No voltage scaling

VCC_CORE

-IGNNE

-CPURST

-A20M

-STPCLK

INTR

-INIT

NMI

-SMI

-FLUSH

-PLLBP

PLLMON1

PLLMON2

TMS

TCK

TDI

-TRST

-PLLTEST

-DBREQ

COREFB+

COREFB-

-AIN0

-AIN1

-AOUT0

-AOUT1

-DOVAL

-FILVAL

SCANCLK2

SINTVAL

SSHIFTEN

SCANCLK1

C

RN6

1

3

5

7

8P4R-680

RN7

7

5

3

1

8P4R-680

R27 680

R88 680

R63 56

R64 56

RN2

1

3

5

7

8P4R-510

R13 510

R8 510

R55 10K

R58 10K

R91 270

R99 270

R37 X_1K

R65 X_1K

R102 270

R94 270

RN1

1

3

5

7

8P4R-270

2

4

6

8

ZN

ZP

8

6

4

2

Push-pull compensation circuit

VCC_CORE

R9 40.2RST

R2 40.2RST

VCC_CORE

RN10

1

-CLKOUT

CLKOUT

2

4

6

8

Trace lengths of CLKOUT and

-CLKOUT are between 2" and

3"

VREF_SYS is set at 50%

of VCC_CORE ot CPU

3

5

7

8P4R-100

2

4

6

8

VCC_CORE

R70

100RST

VREF_SYS

CB1

CM1

105P

R66

100RST

104P

VCC_CORE

RN8

1

PLLBPCLK

2

4

6

8

-PLLBPCLK

Micro-Star

Document Number

Last Revision Date:

D

Monday, July 23, 2001

3

5

7

8P4R-100

2

4

6

8

Title

MS-6537

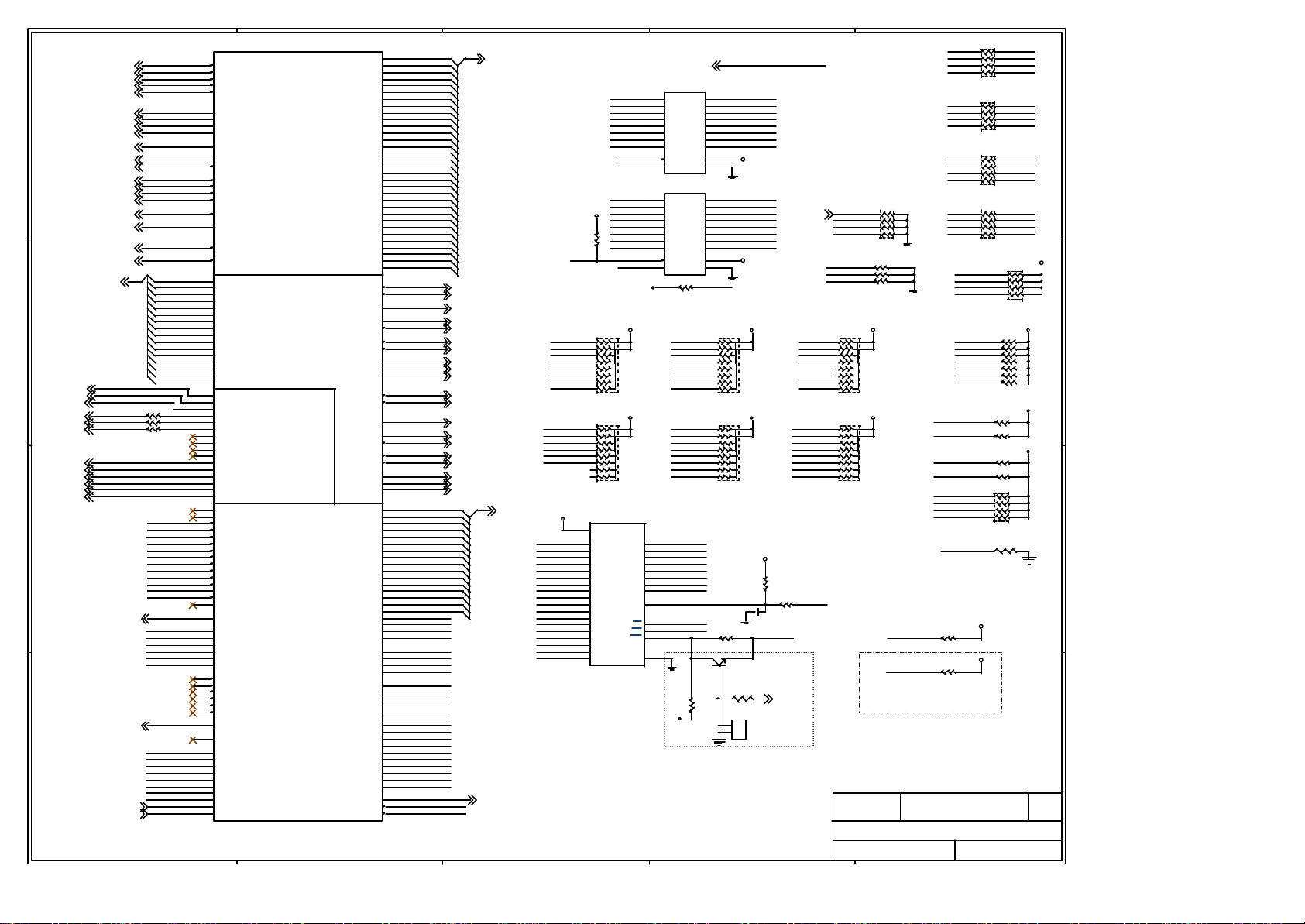

PPGA-462 CPU (Signal)

E

Sheet of

2

Rev

00A

29

A

VCC3

RN4

8P4R-680

FID3

12

FID2

34

FID1

56

FID0

78

FID[0..3] From

FID3 2

FID2 2

FID1 2

FID0 2

Processor

4 4

3 3

2 2

RN5

8P4R-4.7K

78

56

34

12

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AK8

AM8

AN7

G25

G17

AG7

AG15

AG29

AA7

AG9

AG17

AG27

G15

G23

AH6

AJ9

AL9

F30

H10

H28

H30

H32

K30

AJ7

AL7

F8

H6

H8

K8

G9

N7

Y7

G7

Q7

BASS0

BASS2

BASS1

BASS3

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

KEY

KEY

KEY

KEY

KEY

KEY

KEY

KEY

AMD

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VSS1

VSS2

VSS3

VSS4

VSS5

H14

H18

H22

H26

M30P8R30T8V30X8Z30

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VSS6

VSS7

VSS8

VSS9

AF14

AF18

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VSS10

VSS11

VSS12

VSS13

AB8

AF12

AF16

AF22

AF26

AM34

AK36

AK34

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VSS14

VSS15

VSS16

VSS17

VSS18

AF20

AF24

AM36

AK32

AK28

B

BASS0

FID0

BASS1

FID1

AK30

AK26

AK22

AK18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VSS19

VSS20

VSS21

VSS22

AK24

AK20

AK16

AK12

B

E C

Q4

2N3904S

B

E C

Q7

2N3904S

AK14

AK10

AL5

AH26

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VSS23

VSS25

VSS26

VSS27

VSS28

AK4

AK2

AH36

AM32

AM30

AH22

AH18

AH14

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VSS29

VSS30

VSS31

VSS32

AH34

AH32

AH28

AH24

AH10

AH4

AH2

AF36

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VSS33

VSS34

VSS35

VSS37

AH20

AH16

AH12

AF4

AF34

AD6

AM26

AD4

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VSS38

VSS39

VSS40

VSS41

AF2

AD36

AD34

AD32

AD2

AB36

AB34

AB32Z6Z4Z2X36

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VSS42

VSS43

VSS44

VSS45

AB6

AB4

AB2

Z36

VCC_CORE

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VSS46

VSS47

VSS48

VSS49

Z34

Z32X6AM28X4X2

C

BASS2

FID2

BASS3

FID3

X34

AM22

X32V6V4V2T36

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VSS50

VSS51

VSS52

VSS53

V36

V34

E C

Q8

2N3904S

E C

Q6

2N3904S

T34

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VSS54

VSS55

VSS56

VSS57

V32T6T4T2R36

B

B

T32R6R4R2AM18

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VSS58

VSS59

VSS60

VSS61

VSS62

R34

AM24

R32P6P4P2M36

NB_FID2 5NB_FID0 5

NB_FID3 5NB_FID1 5

P36

P34

P32M4M6M2K36

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VSS63

VSS64

VSS65

VSS66

M34

NB_FID[0..3] To

North Bridge

Strapping

K34

K32H4H2

AM14

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

M32K6K4K2AM20

VSS73

H36

H34

F26

F36

F34

F32

F28

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VSS74

VSS75

VSS76

VSS77

VSS78

F22

F18

F14

F10F6F4F2AM16

F24

F20

F16

F12

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VSS79

VSS80

VSS81

VSS82

D

D32

D28

AM10

D24

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VSS83

VSS84

VSS85

VSS86

D36

D34

D30

D26

FID Codes

Four-Bit

FID

0000

0001

0010

0011

0100

0101

0110

0111

D20

D16

D12D8D4D2B36

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VSS87

VSS88

VSS89

VSS90

VSS91

D22

D18

D14

D10D6B34

Four-Bit

Clock

11.0

11.5

12.0

12.5

5.0

5.5

6.0

6.5 10.5

B32

AM2

B28

B24

B20

B16

B12B8B4

AJ5

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

B14

B10B6B2

AM4

VSS103

AK6

AM12

B30

B26

B22

B18

FID MultiplierMultiplier

1000

1001

1010

1011

1100

1101

1110

1111

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS104

AM6

VCCA_PLL

AC7

AJ23

VCC_Z

VCC_A

NC1

NC2

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

VSS_Z

AE7

Clock

7.0

7.5

8.0

8.5

9.0

9.5

10.0

CPU1B

YSKT462P-I

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

E

THERMDP 16

R71

0

R67

0

VCC_PLLVCCA_PLLVCC

1 1

These 16 locations are

for processor type

keying for forwards and

backwards compatibility.

These key pins should be

treated as NC pins.

A

AMD Socket-A processors will

not implement a pin at location

AH6. When a socket that does

not provide a pin hole at

location AH6 is used a non-AMD

PGA370 part will not fit into

the Socket-A.

B

RN9 8P4R-100

1 2

3 4

5 6

7 8

C57

X_39P

C74

X_39P

SC431S

D3

(2.5V Output)

0

2

R104

X_105P

3 1

NOPOP

C

R85 0 R34 10

CB3R96

C81

X_39P

C78

X_39P

104P

C14

X_39P

C9

X_39P

To PWROK

circuit

Title

Micro-Star

Document Number

Last Revision Date:

D

Monday, July 23, 2001

MS-6537

PPGA-462 CPU (Power & GND)

Sheet of

E

Rev

00A

29

3

A

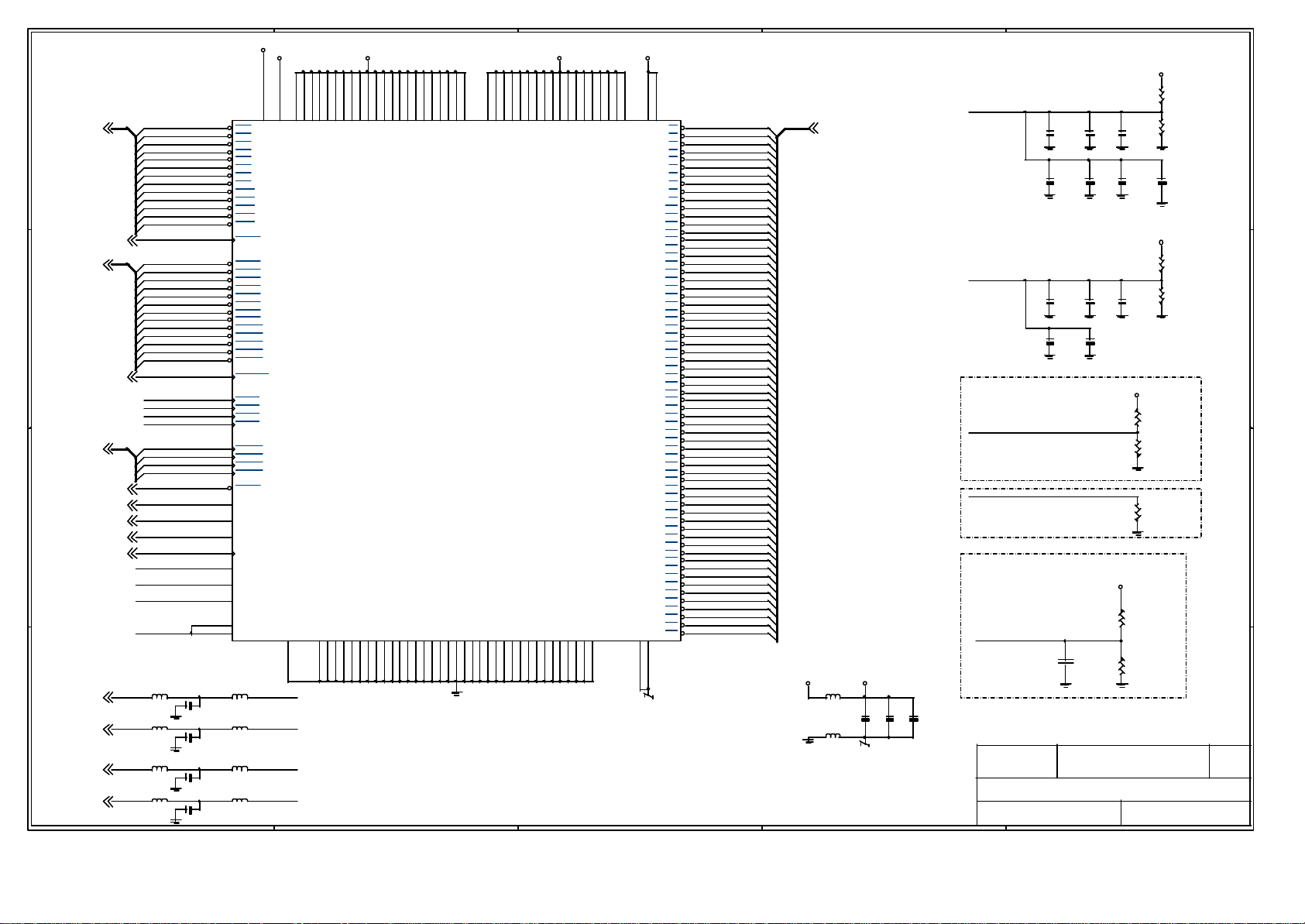

-AIN[2:14]2

4 4

-AICLK2

-AOUT[2:14]2

3 3

-AOCLK2

-DOCLK[0..3]2

-DIVAL2

CFWDRST2

2 2

1 1

CONNECT2

PROCDRY2

HCLK9

-DICLK02

-DICLK12

-DICLK22

-DICLK32

-AIN2

-AIN3

-AIN4

-AIN5

-AIN6

-AIN7

-AIN8

-AIN9

-AIN10

-AIN11

-AIN12

-AIN13

-AIN14

-AICLK

-AOUT2

-AOUT3

-AOUT4

-AOUT5

-AOUT6

-AOUT7

-AOUT8

-AOUT9

-AOUT10

-AOUT11

-AOUT12

-AOUT13

-AOUT14

-AOCLK

NDICLK0

NDICLK1

NDICLK2

NDICLK3

-DOCLK0

-DOCLK1

-DOCLK2

-DOCLK3

HCLK

PLLTEST

S2KCOMP

CLK_VREF

S2K_VREF

FB57

10nH

FB55

10nH

FB54

10nH

FB16

10nH

A

C327

5P

C326

5P

C325

5P

C117

5P

G24

G26

G25

C26

E23

E24

C25

E26

F24

D24

F25

D25

F26

D26

E10

C13

C18

A24

C15

D17

C23

F23

H26

H22

H23

F11

F21

E8

C5

B5

D8

C6

C7

D5

A7

A4

E7

A5

D7

B6

E6

B9

A6

A3

C4

C3

VCC_CORE

AIN2

AIN3

AIN4

AIN5

AIN6

AIN7

AIN8

AIN9

AIN10

AIN11

AIN12

AIN13

AIN14

AINCLK

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

AOUT9

AOUT10

AOUT11

AOUT12

AOUT13

AOUT14

AOUTCLK

DICLK0

DICLK1

DICLK2

DICLK3

DOCLK0

DOCLK1

DOCLK2

DOCLK3

DINVAL

CFWDRST

CONNECT

PROCRDY

HCLK

PLLTEST

S2KCOMP

CLKVREF

S2KVREF

S2KVREF

FB59

10nH

FB58

10nH

FB56

10nH

FB18

10nH

G22

VTS2K

NDICLK0-DICLK0

NDICLK1-DICLK1

NDICLK2-DICLK2

NDICLK3-DICLK3

VCC2_5

F22D6D9

VDS2K

VSS2K

G21

VTT

VTT

D12

D15

D18

D21

D23

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

B7

B10

B13

B16

B

VCC_CORE

J11

J12

J15

VTT

J16L9L18M9M18R9R18T9T18

VCC25

VCC25

VCC25

F7

F12

F15

F16F8F19

F20

G23

H21

J13

J14

J17

J18

J22

K18

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

S2K (CPU) Interface

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

B19

B22

B25

E25F6F9

F10

F13

F14

F17

F18

H25

K21

L11

L12

L13

L14

L15

L16

M11

M12

B

VCC2_5 AVDD6

VCC25

VCC25

VCC25

VCC25

VCC25

VCC25

VCC25

VCC25

GND

GND

GND

GND

GND

GND

GND

GND

M13

M14

M15

M16

N11

N12

N13

N14

V11

VCC25

VCC25

GND

GND

N15

V12

N16

V15

VCC25

VCC25

GND

V16

AA17

VCC25

VCC25

AA18

VCC25

C

J21

AGND6

J23

K23

AGND6

C

K22

AVDD6

AVDD6

AGND6

D

S2K_VREF is set at 50%

of VCC_CORE to NB

U8A

-SDATA0

D10

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

E9

B11

A10

C11

E11

D11

C12

A11

C8

C10

A8

C9

A9

B8

E12

B12

A12

A14

D13

C16

D14

E14

E16

A13

A15

B15

C14

B14

E13

E15

A16

B17

B18

E18

C20

E19

E20

C19

D20

E17

C17

D16

A17

D19

A18

A20

A19

B23

B24

C24

E21

A25

D22

B26

A26

B21

B20

A22

A21

A23

E22

C22

C21

VT8361A1

-SDATA1

-SDATA2

-SDATA3

-SDATA4

-SDATA5

-SDATA6

-SDATA7

-SDATA8

-SDATA9

-SDATA10

-SDATA11

-SDATA12

-SDATA13

-SDATA14

-SDATA15

-SDATA16

-SDATA17

-SDATA18

-SDATA19

-SDATA20

-SDATA21

-SDATA22

-SDATA23

-SDATA24

-SDATA25

-SDATA26

-SDATA27

-SDATA28

-SDATA29

-SDATA30

-SDATA31

-SDATA32

-SDATA33

-SDATA34

-SDATA35

-SDATA36

-SDATA37

-SDATA38

-SDATA39

-SDATA40

-SDATA41

-SDATA42

-SDATA43

-SDATA44

-SDATA45

-SDATA46

-SDATA47

-SDATA48

-SDATA49

-SDATA50

-SDATA51

-SDATA52

-SDATA53

-SDATA54

-SDATA55

-SDATA56

-SDATA57

-SDATA58

-SDATA59

-SDATA60

-SDATA61

-SDATA62

-SDATA63

60S/0805

60S/0805

-SDATA[0:63] 2

AVDD6VCC2_5

FB17

FB19

AGND6

Host

C110 CM3

105P

CT3

475P/0805102P

S2K_VREF

CLK_VREF is set at 1.15V

with VCC3 voltage

divider

CLK_VREF

PLLTEST

S2KCOMP

Place HCLK pull-up close to North

Bridge within one inch.

HCLK

1/2 VCC_CORE

C112 R119

BC7

103P

1.15V

C121 CT4

104P

BC8

103P 103P

(S2K_COMP)

Title

Micro-Star

Document Number

Last Revision Date:

D

Tuesday, July 24, 2001

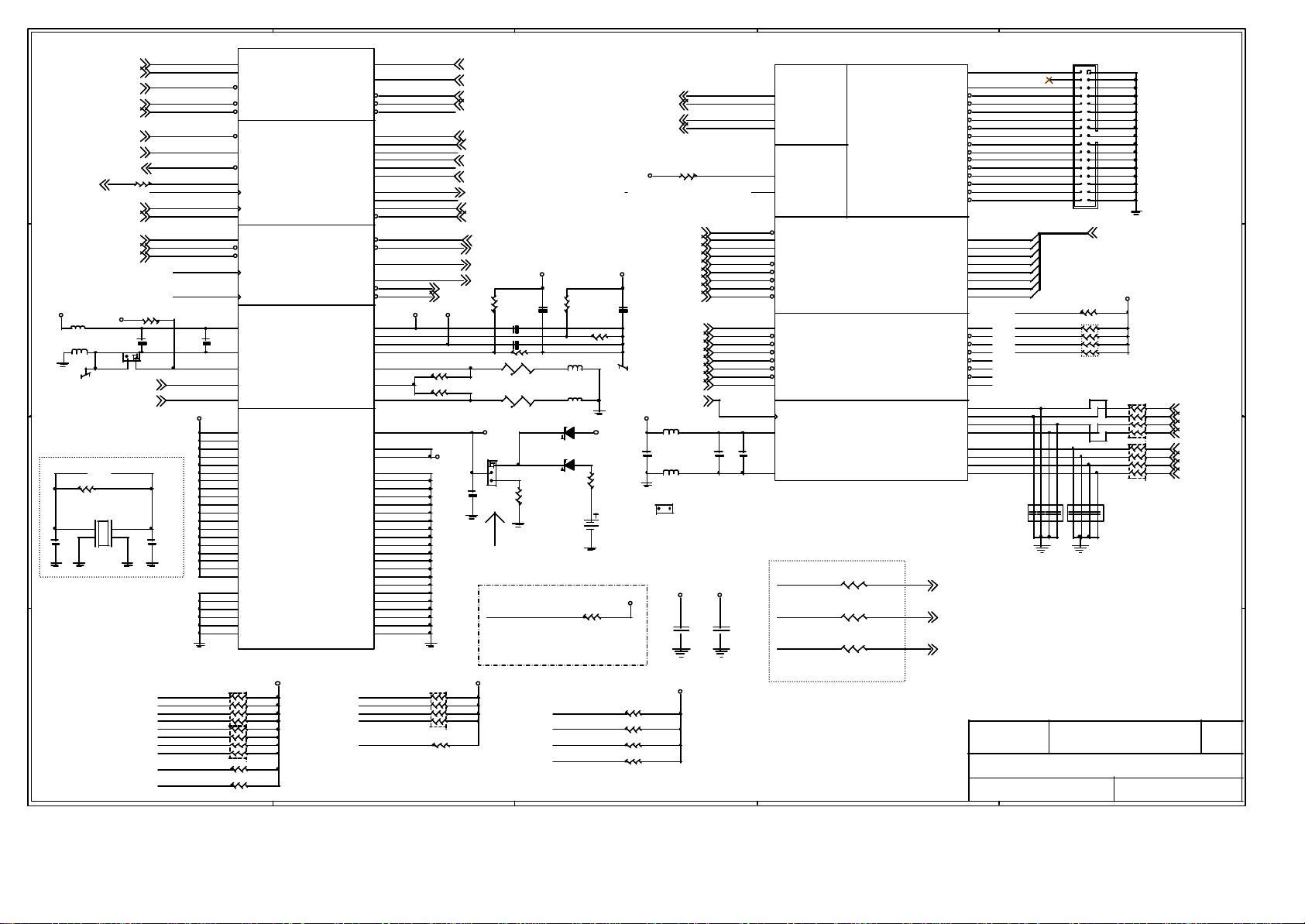

NORTH BRIDGE VT8361 (S2K)

C109

39P

BC4

104P

C122

104P

BC9

(0805 package)

VCC3

C116

X_5p

MS-6537

E

VCC_CORE

CT2

475P/0805104P

BC5

103P

VCC3

475P/0805

VCC_CORE

R134

4.7K

R141

X_4.7K

R131

56.2RST

R129

82RST

R125

121RST

Sheet of

E

BC6

104P

R120

75RST

75RST

R132

10KST

R133

5.36KST

4

Rev

00A

29

A

B

C

D

E

4 4

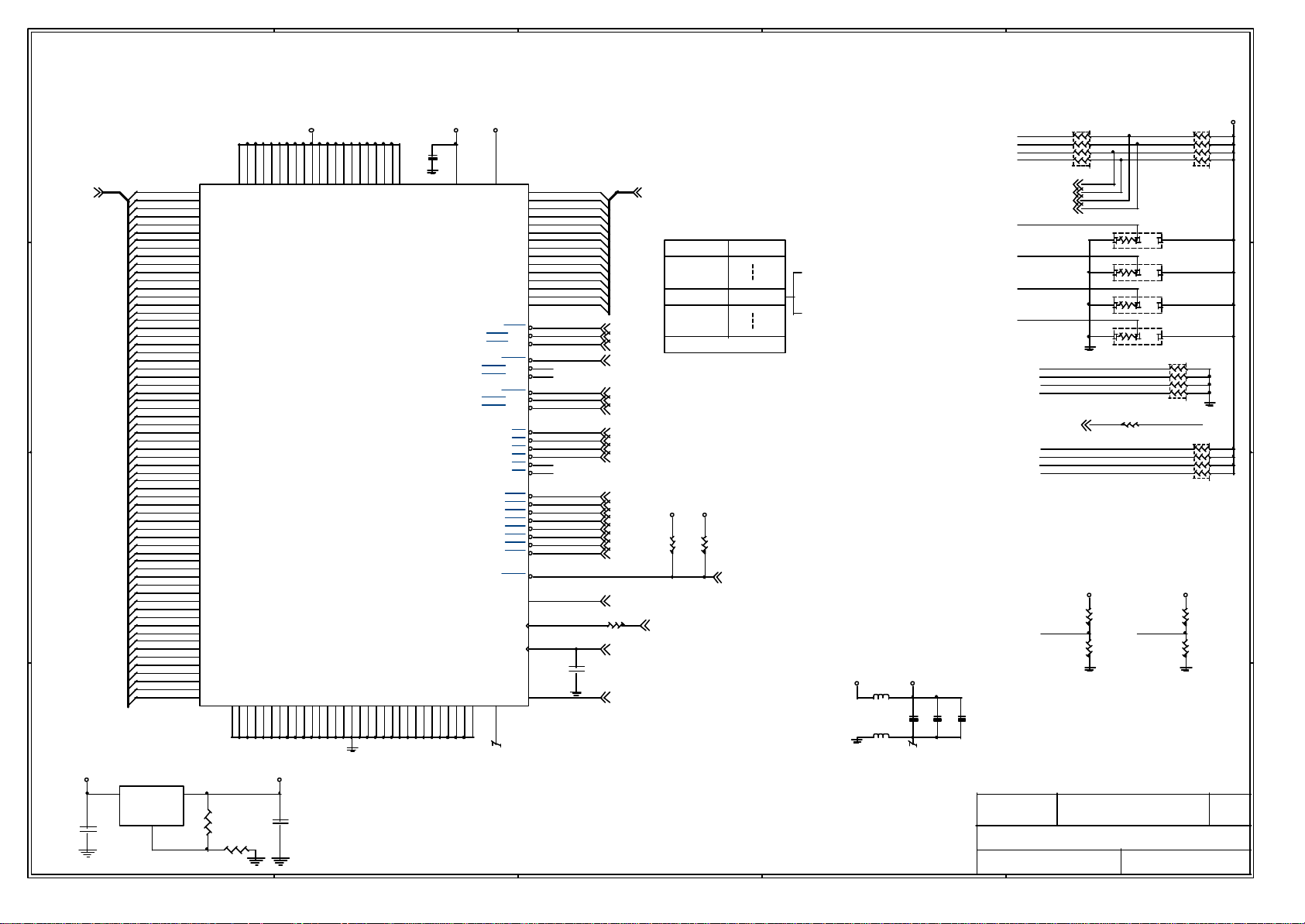

N18

N21

R171

49.9

R172

49.9

P18

VCC3

VCC3

GND

GND

GND

L21

M21

M24

R24

MD0

MD[0:63]10

3 3

2 2

1 1

V_DIMM

VR3

LT1084S-SOT89-0.8A

3 2

VIN VOUT

C156

4.7u-0805

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

J26

MD0

J24

MD1

K25

MD2

L26

MD3

L24

MD4

M25

MD5

N26

MD6

L22

MD7

N22

MD8

N24

MD9

P26

MD10

R25

MD11

T25

MD12

T23

MD13

U26

MD14

U24

MD15

AF25

MD16

AE24

MD17

AD23

MD18

AE23

MD19

AF22

MD20

AF21

MD21

AD20

MD22

AE20

MD23

AC20

MD24

AB18

MD25

AC19

MD26

AF19

MD27

AE18

MD28

AD17

MD29

AF17

MD30

AB17

MD31

J25

MD32

K26

MD33

K24

MD34

L25

MD35

M26

MD36

N25

MD37

L23

MD38

M23

MD39

M22

MD40

N23

MD41

P25

MD42

R26

MD43

T26

MD44

T22

MD45

U25

MD46

V26

MD47

AE25

MD48

AF24

MD49

AF23

MD50

AE22

MD51

AE21

MD52

AC21

MD53

AF20

MD54

AB20

MD55

AB19

MD56

AC18

MD57

AD19

MD58

AE19

MD59

AF18

MD60

AE17

MD61

AC17

MD62

AF16

MD63

ADJ

1

A

VCC3

P21U9U18

U21V9V10

V13

V14

V17

V18

V21

AA7

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

Memory Interface

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

T21

V24

W21

Y21

AA19

AA24

AD18

AD21

AD24

P11

P12

P13

VSUS

C147

4.7u-0805

AA11

VCC3

GND

P14

AA12

VCC3

GND

P15

AA15

VCC3

GND

P16

AA16

VCC3

GND

R11

VCC3

GND

Near NB

AA20

AA21

VCC3

VCC3

GND

GND

GND

R12

R13

R14

B

CM6

102P

GND

GND

GND

R15

R16

T11

T12

GND

VSUS

GND

T13

AC15

VSUS25

GND

T14

T15

SRASB/CKE5

SRASC/CKE4

SCASB/CKE3

SCASC/CKE1

GND

GND

T16

AVDD5

R23

MA0

MA1

AVDD5

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SWEA

SWEBCKE2

SWECCKE0

SRASA

SCASA

CS0

CS1

CS2

CS3

CS4

CS5

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

SUSST

PWROK

MCLK

MCLKF

VID

AGND5

R21

AGND5

AC22

AC23

AB22

AB23

AA22

AA23

Y22

W24

Y23

W22

V22

V23

U22

U23

AA26

AB21

Y24

Y26

AD22

P24

Y25

AC25

P23

P22

AB26

AB25

AE26

AA25

AD25

AF26

W25

W26

AB24

AC24

V25

W23

AC26

AD26

AD15

AE15

T24

R22

H24

VT8361A1

U8B

DCLK_O

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

-SWE

-SRAS

-SCAS

R142 33

C127

X_5p

MA[0:14] 10

-SWE 10

-CKE2 10

-CKE0 10

-SRAS 10

-SCAS 10

-CKE3 10

-CKE1 10

-CS0 10

-CS1 10

-CS2 10

-CS3 10

DQM0 10

DQM1 10

DQM2 10

DQM3 10

DQM4 10

DQM5 10

DQM6 10

DQM7 10

PWROK 8,20,21

DCLKO 9

DCLKI 9

VID 19

C

1

0

1

0

1

0

1

0

Strength

Level

Strongest

Weakest

Strength

LevelDrive High

Strongest

Weakest

R170

X_10K

-NBSUSST 8

MA[13:12]

Drive High

1

1

0

0

MA[10:9]

1

1

0

0

MA[13,12,10,9] = 1100

=> Auto Mode

SB3V VCC3

R159

10K

Power Up Strappings :

SWE, SRAS, MA[1:0] => CPU Clock Divider

0000 11

0001 11.5

0010 12

0011 12.5

0100 5

0101 5.5

0110 6

0111 6.5

MA[13:12] => PMOS Output Driving Strength

00~10 - Manual Strapping Mode

11 - Auto Mode

MA[10:9] => NMOS Output Driving Strength

00 - Auto Mode

01~11 - Manual Strapping Mode

MA[8],MA[6] => Graphics Power On Strapping

00 - Normal Operation

01 - Graphic Standalone Simulation Mode

1X - NB + Graphic Simulation Mode

MA[11] => North Bridge S2K DQ Select

0 - Center DQ (Default)

1 - Edge DQ

MA[14] => CPU Clock Frequency

0 - 100MHz (Default)

1 - 133MHz

MA[5] => LCD Select

0 - LCD off

1 - LCD on

MA[4:2] => Panel Type Select

000 - TFT 10 x 7 - 18

001 - TFT 12 x 10 - 18 +18

010 - TFT 8 x 6 - 18

011 - TFT 10 x 6 - 18

100 - TFT 10 x 7 - 16

101 - TFT 10 x 6 - 24

110 - TFT 8 x 6 - 16

111 - TFT 10 x 7 - 24

MA[7] => Graphics Test Mode

0 - Normal Mode (Default)

1 - Test Mode Enable

-SCAS => Strapping Information Select

1 - From Boot ROM

0 - From Hardware Strapping pins

60S/0805

60S/0805

1000 7

1001 7.5

1010 8

1011 8.5

1100 9

1101 9.5

1110 10

1111 10.5

MA5,MA6,MA8 TO GND

MA9,MA10,MA12,MA13

TO Resistor

AVDD5VCC2_5

FB10

FB11

D

C38

102P

AGND5

Memory

CM2

105P

CT1

475P/0805

Micro-Star

Document Number

Last Revision Date:

Monday, July 23, 2001

RN14

8P4R-10K

MA1

1

MA0

-SRAS

-SWE

MA9

MA10

MA12

MA13

NB_FID23

NB_FID33

NB_FID13

NB_FID03

2

3

4

5

6

7

8

MA11

MA8

MA6

MA5

MA5

MA4

MA3

MA2

Title

R122

X_10K

R114

10K

R140

10K

133_-1009

MA7 -SCAS

MS-6537

NORTH BRIDGE VT8361 (DRAM)

E

RN13

8P4R-10K

R123(2-3)

2

10K

13

(2-3)

R124(2-3)

2

10K

(2-3)

13

R127(1-2)

2

10K

(1-2)

13

R130(1-2)

2

10K

(1-2)

13

RN17

1

3

5

7

8P4R-10K

MA14

X_8P4R-10K

VCC3VCC3

Sheet of

5

VCC3

1

2

3

4

5

6

7

8

2

4

6

8

RN16

1

2

3

4

5

6

7

8

R107

X_10K

R105

10K

Rev

00A

29

A

VCC3

B

ADVDD_V2

ADVDD_V1 AVDD_V2PLLVCC

C

AVDD_V3 AVDD_V1

D

E

VCC2_5 AVDD_V2AVDD_V1

60S/0805

60S/0805

60S/0805

60S/0805

60S/0805

60S/0805

FB34

FB35

FB22

FB21

AGND_V3

FB37

FB32

-WSC

IMIIN

-SUSPEND

-ENTEST

-GNT4

-REQ4

DFTIN

PLLVCC

R163 4.7K

R169 8.2K

R175 2.2K

R150 2.2K

VCC2_5 VCC2_5

C180

102P

C130

102P

C174

102P

PLLGND

1

3

5

7

CM8

105P

CM4

105P

CM9

105P

VCC3

2

4

6

8

VCC

VCC_CORE

RN20

8P4R-4.7K

Micro-Star

Document Number

Last Revision Date:

D

Monday, July 23, 2001

NORTH BRIDGE VT8361 (PCI & Graphics)

GREEN

HSYNC

AVDD_V1

VSYNC

COMP

IRSET

TVHS

TVVS

TVCLK

SUSPEND

ENTEST

IMIIN

CAPD0

CAPD1

CAPD2

CAPD3

CAPD4

CAPD5

CAPD6

CAPD7

CAPD8

CAPD9

CAPD10

CAPD11

CAPD12

CAPD13

CAPD14

CAPD15

CAPHS

CAPVS

CAPCLK

ENPBLT

ENPVEE

ENPVDD

SFCLK

AGND_V1

RED

BLUE

SDA

SCL

TVD0

TVD1

TVD2

TVD3

TVD4

TVD5

TVD6

TVD7

VLF1

VLF2

XTLI

XTLO

INTA

5VSF

IMIO

FLM

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PD8

PD9

PD10

PD11

PD12

PD13

PD14

PD15

PD16

PD17

PD18

PD19

PD20

PD21

PD22

PD23

DE

NC

LP

U8C

C2

D3

D2

E2

E1

F2

F3

E4

E3

V1

V2

U5

V3

T5

U4

T6

U2

V5

W3

V4

Y3

AA2

Y4

W4

W5

F5

F4

U6

M2

M3

R6

T2

T1

R5

R2

R4

R1

R3

P5

P2

P3

P4

N5

N2

N1

N4

T3

U1

U3

G1

H5

F1

G4

H3

G3

G5

G2

H2

H1

J2

J1

H4

K6

J4

J3

L5

K2

J5

K1

K3

L6

L2

K5

L1

L3

M6

K4

M4

M5

M1

AC3

VT8361A1

AR

AG

AB

HSYNC

VSYNC

SDA

SCL

COMP

IRSET

TVD0

TVD1

TVD2

TVD3

TVD4

TVD5

TVD6

TVD7

VLF1

VLF2

GUICLK

-INTR_A

-SUSPEND

-ENTEST

IMIIN

AR 18

AG 18

AB 18

HSYNC 18

VSYNC 18

SDA 18

SCL 18

TVD0 12

TVD1 12

TVD2 12

TVD3 12

TVD4 12

TVD5 12

TVD6 12

TVD7 12

TVHS 12

TVVS 12

TVCLK 12

GUICLK 9

-INTR_A 7,11

VCC

AD3

VCC3

GND

AA13

GND

AA14

GND

AD4

GND

AD7

GND

AD10

GND

AD13

AB2

GND

AF1

A2B2G6H6J9

A_D0

A_D[0:31]7,11,22,23

4 4

3 3

2 2

1 1

C_-BE07,11,22,23

C_-BE17,11,22,23

C_-BE27,11,22,23

C_-BE37,11,22,23

-FRAME7,11,22,23

-DEVSEL7,11,22,23

-IRDY7,11,22,23

-TRDY7,11,22,23

-STOP7,11,22,23

-PLOCK11

-SERR7,11,22,23

PAR7,11,22,23

-PCIREQ7

-PCIGNT7

-REQ011

-REQ111

-REQ2

-REQ211,23

-REQ3

-REQ311,22

-REQ4

-GNT011

-GNT111

-GNT211,23

-GNT311,22

-GNT4

-CLKRUN8

-PCIRST7,11

NPCLK9

-WSC8

A

NPCLK

-WSC

DFTIN

A_D1

A_D2

A_D3

A_D4

A_D5

A_D6

A_D7

A_D8

A_D9

A_D10

A_D11

A_D12

A_D13

A_D14

A_D15

A_D16

A_D17

A_D18

A_D19

A_D20

A_D21

A_D22

A_D23

A_D24

A_D25

A_D26

A_D27

A_D28

A_D29

A_D30

A_D31

AC13

AD14

AF14

AB13

AF13

AE14

AE13

AD12

AE12

AC12

AF12

AC11

AB14

AD11

AB12

AF11

AC8

AC9

AB9

AC6

AE8

AF8

AD8

AC7

AF7

AD6

AF6

AE6

AB7

AB6

AF5

AD5

AC14

AB11

AB8

AE7

AF9

AB10

AE9

AD9

AC10

AF10

AE10

AE11

AD16

AF15

AE4

AE5

AC5

AE2

AC4

AB5

AF4

AF3

AE3

AF2

AB15

AB16

AC16

AE16

AA4

AA3

AA5

AB4

AB3

AD2

AD1

AC2

AC1

E5

Y5

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE0

CBE1

CBE2

CBE3

FRAME

DEVSEL

IRDY

TRDY

STOP

LOCK

SERR

PAR

PREQ

PGNT

REQ0

REQ1

REQ2

REQ3

REQ4

GNT0

GNT1

GNT2

GNT3

GNT4

PCLKRUN

RESET

PCLK

WSC

DFTIN

TA+

TA-

TB+

TB-

TC+

TC-

TD+

TD-

TCLK+

TCLK-

LVDS

Interface

J10K9L4N9P9T4W6

VCC3

VCC3

VCC3

VCC3

VCC3

PCI

Interface

GND

GND

GND

GND

GND

B3B4D4J6N3N6P1P6V6

VCC3

GND

VCC3

GND

VCC3

GND

B

VCC3

GND

AA6

VCC3

GND

AA8

VCC3

GND

AA9

Y6

VCC3

GND

AA10

LVDSVCC

GND

PLLVCC

LVDSGND

AB1

W1

D1

ADVDD_V2

ADVDD_V1

TV Out

Interface

TV In

Interface

Panel

Interface

PLLGND

AGND_V4

AE1

A1

AGND_V3 AGND_V1AGND_V2

PLLGND

C1

Y2

AVDD_V3

Panel

Interface

AGND_V3

B1

AA1

C

W2

AVDD_V2

AGND_V2

Y1

Title

60S/0805

60S/0805

60S/0805

60S/0805

VCC2_5

FB36

FB31

VCC2_5VCC2_5

FB23

FB33

COMP

IRSET

VLF1

VLF2

MS-6537

Sheet of

E

C182

102P

AGND_V2AGND_V1

ADVDD_V1AVDD_V3

C133

102P

ADVDD_V2

C179

102P

AVDD_V3

104PC131

R149 374RST

AGND_V3

560PC181

AGND_V1

560PC163

AGND_V2

6

CM10

105P

CM5

105P

CM7

105P

Rev

00A

29

A

U16A

FRAME#

IRDY#

TRDY#

STOP#

DEVSEL#

C_BE0#

C_BE1#

C_BE2#

C_BE3#

IDSEL

PAR

SERR#

PIRQA#

PIRQB#

PIRQC#

PIRQD#

PCIRST#

PCICLK

PREQ#

PGNT#

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

BITCLK

SDIN0

SDIN1

SYNC

SDOUT

ACRST#

JBY

JBX

JAY

JAX

JAB2

JAB1

JBB2

JBB1

MSO

MSI

B2

AEN

H2

BALE

F2

SBHE#

E3

REFRESH#

D1

IOR#

C2

IOW#

U4

MEMR#

V4

MEMW#

A1

SMEMR#

B1

SMEMW#

F3

IOCS16#

F1

MEMCS16#

A2

IOCHRDY

F4

IOCHCK/GPI0

H1

TC

J1

RSTDRV

L3

DREQ0/GPI16

E2

DREQ1/GPI17

D3

DREQ3/GPI18

M1

DREQ5/GPI19

M5

DREQ6/GPI20

N4

DREQ7/GPI21

L2

DACK0#/GPO16

E1

DACK1#/GPO17

D2

DACK3#/GPO18

L4

DACK5#/GPO19

M3

DACK6#/GPO20

N2

DACK7#/GPO21

E4

OSC

H5

BCLK

G4

IRQ3

G3

IRQ4

G2

IRQ5

G1

IRQ6/GPI4/SLPBTN#

F5

IRQ7

H4

IRQ9

K3

IRQ10

K4

IRQ11

L1

IRQ14

K5

IRQ15

VT82C686B

PCI INTERFACE

IDE INTERFACE

GAME PORT

& AC'97

ISA INTERFACE

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

-SBHE

-REFRESH

-IOR

-IOW

-MEMR

-MEMW

-SMEMR

-SMEMW

-IOCS16

-MEMCS16

IOCHRDY

-IOCHK

RSTDRV

DREQ0

DREQ1

DREQ3

DREQ5

DREQ6

DREQ7

-SLPBTN

IRQ3

IRQ4

IRQ5

IRQ7

IRQ9

IRQ10

IRQ11

IRQ14

IRQ15

SYNC

SDOUT

-ACRST

W18

W15

W16

W17

F18

F19

F20

G17

G16

J19

G20

F17

C19

C20

G19

G18

A16

D17

C17

B17

B16

E16

L18

L19

P16

P18

P20

R17

R19

T16

T18

T20

T19

T17

R20

R18

R16

P19

P17

N20

V17

Y17

V16

Y16

U15

U14

Y15

V15

T15

U16

Y18

Y19

-FRAME6,11,22,23

-IRDY6,11,22,23

-TRDY6,11,22,23

-STOP6,11,22,23

-DEVSEL6,11,22,23

C_-BE06,11,22,23

C_-BE16,11,22,23

C_-BE26,11,22,23

4 4

3 3

BITCLK13

AC_SYNC13

AC_SDO13

AC_-RST13

JAB214

JAB114

JBB214

JBB114

MSO14

MSI14

2 2

1 1

C_-BE36,11,22,23

A_D186,11,22,23

PAR6,11,22,23

-SERR6,11,22,23

-INTR_A6,11

-INTR_B11

-INTR_C11,23

-INTR_D11,22

-PCIRST6,11

SPCLK9

-PCIREQ

-PCIREQ6

-PCIGNT

-PCIGNT6

PDD[0:15]16

BITCLK

SDIN0

SDIN013

SDIN1

SDIN113

RN35A

1 2

3 4

RN35B

RN35C 5 6

JAB2

JAB1

JBB2

JBB1

MSO

MSI

RSTDRV16

SIO_OSC9

IRQ1416

IRQ1516

A

8P4R-0

B

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PDIOR#

PDIOW#

PIORDY

PDREQ

PDACK#

PDCS1#

PDCS3#

PDA0

PDA1

PDA2

SDIOR#

SDIOW#

SIORDY

SDREQ

SDACK#

SDCS1#

SDCS3#

SDA0

SDA1

SDA2

SA0/SDD0

SA1/SDD1

SA2/SDD2

SA3/SDD3

SA4/SDD4

SA5/SDD5

SA6/SDD6

SA7/SDD7

SA8/SDD8

SA9/SDD9

SA10/SDD10

SA11/SDD11

SA12/SDD12

SA13/SDD13

SA14/SDD14

SA15/SDD15

SA16

SA17

SA18

SA19

LA20

LA21

LA22

LA23

SD10

SD11

SD12

SD13

SD14

SD15

XDIR/PCS0#/GPO12

XOE#/GPO13

ROMCS#

B

C

A_D0

L17

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

L16

K20

K19

K18

K17

K16

J20

J18

J17

J16

H20

H19

H18

H17

H16

F16

E20

E19

E18

E17

D20

D19

D18

B20

A20

A19

B19

A18

B18

C18

A17

N17

N18

N16

N19

M20

L20

M16

M17

M19

M18

W19

W20

V20

Y20

V19

U17

U18

U19

V18

U20

W1

V2

V1

U3

U2

U1

T4

T3

T2

T1

R5

R4

R3

R2

R1

P5

P4

P3

K2

K1

J5

J4

J3

J2

Y1

Y2

W2

Y3

W3

V3

Y4

W4

L5

M2

M4

N1

N3

N5

P1

P2

T5

U5

C1

SA16

SA17

SA18

SA19

SA20

SA21

SA22

SA23

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

SUSLED

-SOE

-ROMCS

A_D1

A_D2

A_D3

A_D4

A_D5

A_D6

A_D7

A_D8

A_D9

A_D10

A_D11

A_D12

A_D13

A_D14

A_D15

A_D16

A_D17

A_D18

A_D19

A_D20

A_D21

A_D22

A_D23

A_D24

A_D25

A_D26

A_D27

A_D28

A_D29

A_D30

A_D31

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

-PDIOR 16

-PDIOW 16

PIORDY 16

PDDREQ 16

-PDDACK 16

-PDCS1 16

-PDCS3 16

PDA0 16

PDA1 16

PDA2 16

-SDIOR 16

-SDIOW 16

SIORDY 16

SDDREQ 16

-SDDACK 16

-SDCS1 16

-SDCS3 16

SDA0 16

SDA1 16

SDA2 16

Setup T5 Be a GPIO

SUSLED 21

A_D[0:31] 6,11,22,23

SDD[0..15] 16

SDD[0..15]16

U25 X_74LV245ADBR

SDD7

2

A1

3

A2

4

A3

5

A4

6

A5

7

A6

8

A7

9

A8

19

G

VDD

1

DIR

GND

U26 X_74LV245ADBR

2

A1

3

A2

4

A3

5

A4

6

A5

7

A6

8

A7

9

A8

19

G

VDD

1

DIR

GND

R348

1K

SA15

SA14

SA13

SA12

SA19

SA18

SA17SA8

SA16

SD3

SD2

SD1

SD0

SD7

SD6

SD5

SD0

13

SD1

14

15

SD2

SD3

17

SD4

18

SD5SA5

19

SD6

20

21

SD7

1

24

-MEMR

-ROMCS

22

31

16

R335

1K

VCC

B1

B2

B3

B4

B5

B6

B7

B8

B1

B2

B3

B4

B5

B6

B7

B8

-MASTER

IRQ11

SA23

SA22

SA21

IRQ15

IRQ14

SA0

SA1

SA2

SA3

SA4

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA11

SA10

SA9

SA4

SA5

SA6

SA7

VCC

R349

X_10K

-SOE

32

12

11

10

27

26

23

25

28

29

30

9

8

7

6

5

4

3

2

SDD6

SDD5

SDD4

SDD3

SDD2

SDD1

SDD0

-SOE

-MASTER

SDD15

SDD14

SDD13

VCC

SDD12

SDD11

SDD10

SDD9

SDD8

-MASTER

VCC

RP8

51

2

10

3

4

6

7

8

9

10P8R-4.7K

VCC VCC

RP4

51

2

10

3

4

6

7

8

9

10P8R-4.7K

U28

VCC

A0

Q0

A1

Q1

A2

Q2

A3

Q3

A4

Q4

A5

Q5

A6

Q6

A7

Q7

A8

A9

VP

A10

A11

A12

OE

A13

CE

A14

WE

A15

A16

A17

GND

YSKT032PLCC

Bios Protection

C

18

17

16

15

14

13

12

11

20

10

18

17

16

15

14

13

12

11

20

10

RP7

2

3

4

6

7

8

9

10P8R-4.7K

RP5

2

3

4

6

7

8

9

10P8R-4.7K

R356 0

B

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

SA15

SA14

SA13

SA12

SA11

SA10

SA9

SA8

C306

105P

EC

Q32

2N3904S

R295

1K

1

2

D

VCC

RN44

-OC1

7

-OC18,15

DREQ6

DREQ0

DREQ5

VCC

51

10

51

10

VCC

R352

4.7K

-MEMW

GPOC 8

J3

YJ102

R353

X_0

SD10

SD11

SD9

SD8

SD15

SD13

SD14

SD12SD4

SA18

SA3

SA2

SA1

SA0

IRQ10

SA20

DREQ7

DREQ3

DREQ1

RP6

2

3

4

6

7

8

9

10P8R-4.7K

RP3

2

3

4

6

7

8

9

10P8R-4.7K

Micro-Star

Document Number

Last Revision Date:

D

8

5

6

3

4

1

2

8P4R-4.7K

R323 4.7K

R309 4.7K

R310 4.7K

VCC

51

10

VCC

51

10

-SLPBTN

-ROMCS

This pull-up sets the CPURST

and INIT to Slot-A/Socket-A

levels.

Title

SOUTH BRIDGE VT82C686B (PCI & SUPER I/O)

-PCIREQ

-PCIGNT

-SBHE

IOCHRDY

-MEMCS16

-IOCHK

-IOCS16

-REFRESH

SDIN1

R325 1K

R308 4.7K

MS-6537

E

RN46

1

SA0

SA1

3

SA2

5

SA3

7

8P4R-0

RN50

SA4

1

SA5

3

5

SA6

SA7

7

8P4R-0

RN53

SA11

7

SA10

5

SA9

3

SA8

1

8P4R-0

RN55

SA15

7

5

SA14

SA13

3

SA12

1

8P4R-0

IRQ9

-SMEMR

-IOW

-IOR

-MEMR

R351 4.7K

-MEMW

R357 4.7K

-SMEMW

R321 4.7K

IRQ7

R331 4.7K

IRQ4

R330 4.7K

IRQ3

R322 4.7K

IRQ5

R312 4.7K

R225 10K

R226 10K

R311 4.7K

R313 1K

RN45

1

3

5

7

8P4R-330

R243

10K

VCC3

VCC

Sheet of

E

2

SDD0

SDD1

4

SDD2

6

SDD3

8

SDD4

2

SDD5

4

6

SDD6

SDD7

8

SDD11

8

SDD10

6

SDD9

4

SDD8

2

SDD15

8

6

SDD14

SDD13

4

SDD12

2

RN49

1

3

5

7

8P4R-4.7K

7

VCC

2

4

6

8

VCCVCC VCC

VCC3

VCC

2

4

6

8

Rev

00A

29Monday, July 23, 2001

A

INTR

INTR2

NMI

NMI2

-A20M

-A20M2

-FERR2

FB40

0/0805

FB39

0/0805

HW_GND

-IGNNE2

-RSMRST20

PWROK5,20,21

-PWRBTN21

R277

10K

-CLKRUN6

VBAT

475P/0805

SMBCK9,10,12

SMBDT9,10,12

SPEAK21

CT6

4 4

-NBSUSST5

VCC3

3 3

-IGNNE

-RSMRST

-PWRBTN

-SUSST

SUS_CLK

SMBCK

SMBDT

SPEAK

-EXTSMI

-CLKRUN

XYALI

XYALO

R294

10K

CB13

104P

JCASE1

YJ102

2

1

CPUFAN16

SYSFAN16

CPUFAN

SYSFAN

VCC3

20mil Trace Width.

XYALOXYALI

R303

X_5.6M

2 2

1 1

X3

32K-12.5pf-CSA-309-D

1 2

C280

10P

34

A

C288

10P

PD33_-66

SD33_-66

SMBDT

SMBCK

-CLKRUN

GPOC

GPIOD

-SLP

GPIOA

-CPUSTP

U16C

CPU INTERFACE

W8

INTR

U7

NMI

Y7

A20M#

V7

FERR#

Y8

IGNNE#

IDE INTERFACE

V6

RSMRST#

W6

PWRGOOD

Y11

PWRBTN#

V10

SUSST1#/GPO3

T10

SUSCLK

U9

SMBCLK

T9

SMBDATA

V5

SPKR

Y10

EXTSMI#

W12

CLKRUN#

Y5

XTALI

W5

XTALO

R12

VDD_HWM

R13

VSS_HWM

V14

CHAS/GPIOC/GPIO10

U12

FAN2/GPIOB/GPIO9

N6

VCC

F7

VCC

F10

VCC

F12

VCC

F13

VCC

F14

VCC

H6

VCC

J6

VCC

K6

VCC

M6

VCC

R11

VCC

H15

VCC

J15

VCC

K15

VCC

M15

VCC

N15

VCC

R7

VCC

R8

VCC

R14

VCC

F11

GND

G6

GND

F6

GND

R6

GND

P6

GND

1

3

5

7

1

3

5

7

R249 4.7K

R271 4.7K

SUSA#/APICACK#/GPO1

MISC.

DRQ2/OC1#/SERIRQ/GPIOE

H/W MONTIOR

POWER & GROUND

VT82C686B

2

RN41

4

8P4R-4.7K

6

8

2

RN40

4

8P4R-4.7K

6

8

CPURST

STPCLK#

GPO7/SLP#

IRQ8#/GPI1

BATLOW#/GPI2

LID/APICREQ#/GPI3

PME#/THRM#/GPI5

SMBALRT#/GPI6

RING#/GPI7

SUSB#/APICCS#/GPO2

CPUSTP#/GPO4

PCISTP#/GPO5

GPIOA/GPIO8

GPIOD

DACK2#/OC0#/GPIOF

VSENSE_20

VSENSE_30

VSENSE_25

VSENSE_12

T_SENSE1

VREF_5VFAN1

T_SENSE2

VCCSUS

VCCSUS

B

-CPURST

V8

-INIT

T6

INIT

SMI#

GPO0

SUSC#

VBAT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDGND

-SMI

U6

-STPCLK

W7

-SLP

T7

PD33_-66

W11

SD33_-66

U11

-APICREQ

U10

-PME

T11

-SMBALT

W10

-RING

V11

PWRLED

T8

-SUSA

V9

W9

Y9

-CPUSTP

Y12

GPOC

V12

GPIOA

T14

GPIOD

U8

-OC1

H3

-OC0

G5

VCC_CORE

U13

W14

V13

Y14

W13

R272 10KST

T13T12

R266 10KST

Y13

VBAT

Y6

R9

R10

J9

J10

J11

J12

K9

K10

K11

K12

L6

L9

L10

L11

L12

M9

M10

M11

M12

L15

P15

G15

R15F15

-PME

-SUSST

-RING PWRLED

-EXTSMI

R273 10K

B

-CPURST 2

-INIT 2

-SMI 2

-STPCLK 2

PD33_-66 16

SD33_-66 16

-PME 11,22

-RING 17

PWRLED 21

-SUSB 20,21

-SUSC 20,21

-CPUSTP 19

GPOC 7-EXTSMI21

GPIOA 16

GPIOD 16

-OC1 7,15

1

3

5

7

-OC0 15

VCC2_5

SB3V

CB16

104P

2

4

6

8

R256

53.6KST

CM11

105P

CM12

105P

R258

10KST

RT2

t

YT103S-1N

RT1

t

YT103S-1N

D11

VBAT

1N5817S

D10

1

2

1-2 : Normal Operation (default)

2-3 : Clear CMOS

SB3VVCC3

1N4148S

3

R229

JBAT1

YJ103

1K

SPEAK

Speak = High : E nables Audio/Game port;

M uxed IDE data.

Speak = Low : Disab les Audio/Game port;

Enables dedi cated 2nd IDE data bus.

RN38

8P4R-10K

C248

104P

FB41

0/0805

FB14

0/0805

R257

16.2KST

R253

10KST

R298 1K

-SUSA

SUS_CLK-SMBALT

-APICREQ

VCC3

VCC+12V

C256

104P

HW_GND

SB3V

CB15

104P

R46

1K

YSKTBT

VCC3

R291 X_10K

R282 X_10K

R270 X_10K

R283 X_10K

C

U16B

KB/MS

KB_CLK18

KB_DATA18,21

MS_DATA18

MS_CLK18

R265

4.7K

P_-ACK17 P_PRD[0..7] 17

P_BUSY17

P_PE17

P_SLCT17

P_-ERR17

P_-INIT17

P_-AFD17

P_-SLIN17

P_-STB17

SOUT117

-DTR117

-RTS117

-CTS117

-DSR117

-DCD117

-RI117

SIN117

USBCLK9

SB3V

FB45

60S/0805

CT8

475P/0805 104P

FB46

60S/0805

JBAT1(1-2)

YJUMPER-MGBAT1

E5

KBCK

A5

KBDT/KBRC

C5

MSDT/IRQ12

D5

MSCK/IRQ1

IRRX

IRDA

D12

IRRX/GPO15

E12

IRTX/GPO14

B13

C13

D13

E13

A15

C15

C16

E15

D16

A11

D11

B11

C11

C12

A12

E11

B12

C3 B3

F9

CB14

F8

PARALLEL PORT

ACK#

BUSY

PE

SLCT

ERROR#

PINIT#

AUTOFD#

SLCTIN#

STROBE#

SERIAL PORT 1 & 2

TXD1

DTR1#

RTS1#

CTS1#

DSR1#

DCD1#

RI1#

RXD1

USB INTERFACE

USBCLK USBP0USB_VDD

USB_GND

VT82C686B

D

FLOPPY

INTERFACE

DRVDEN0

DRVDEN1

INDEX#

MTR0#

DS1#

DS0#

MTR1#

DIR#

STEP#

WDATA#

WGATE#

TRAK0#

WRTPRT#

RDATA#

HDSEL#

DSKCHG#

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

TXD2

DTR2#

RTS2#

CTS2#

DSR2#

DCD2#

RI2#

RXD2

USBP0+

USBP1+

USBP1-

USBP2+

USBP2-

USBP3+

USBP3-

DRVEN0

D9

DRVEN1

D6

-INDEX

D7

-MOA

E9

-DSB

A8

-DSA

B8

-MOB

C8

-DIR

D8

-STEP

E8

-WD

A7

-PWE

B7

-TRAK0

E7

-WP

A6

-RDATA

B6

-HEAD

C7

-DSKCHG

C6

P_PRD0

B15

P_PRD1

D15

P_PRD2

A14

P_PRD3

B14

P_PRD4

C14

P_PRD5

D14

P_PRD6

E14

P_PRD7

A13

D10

B9

E10

A9

C10

A10

C9

B10

USBP0+

A3

USBP0USBP1+

C4

USBP1-

D4

USBP2+

A4

USBP2-

B4

USBP3+

B5

USBP3-

E6

CN13

8P4C-47P

-INDEX

-TRAK0

-WP

-RDATA

-DSKCHG

87

10

12

16 15

22

24

26

28

30

32

34

YJ217-C-1

214365

FOR PC2001

SB3V SB3V

BC89

0.1u

(BOT)

SB3V

BC19

0.1u

-SUSA

SUS_CLK

-APICREQ

R281

0

R269

0

R287

0

APICD0 2

APICD1 2

-WSC 6

Title

Micro-Star

Document Number

SOUTH BRIDGE VT82C686B (IDE, PM, HWM)

Last Revision Date:

C

D

Tuesday, July 24, 2001

FDD1

2

R279 150

1 2

3 4

5 6

7 8

87

E

1

34

56

78

9

11

1314

1718

1920

21

23

25

27

29

31

33

VCC

RN42

8P4R-27

1

3

5

7

1

3

5

7

RN39

8P4R-27

214365

CN12

8P4C-47P

MS-6537

Sheet of

E

RN36

8P4R-150

2

4

6

8

2

4

6

8

USBDT2- 15

USBDT2+ 15

USBDT3- 15

USBDT3+ 15

USBDT0+ 15

USBDT0- 15

USBDT1+ 15

USBDT1- 15

8

Rev

00A

29

A

B

C

D

E

* 25 mils Trace on Layer 4

with GND copper

VCCCLKVCC3

4 4

475P/0805

3 3

CB12CT5

104P

FB38

0/0805

EC26

ELS10/16-B

6:18

APICCLK

R178

Level shift

2 2

Jumper setting:

1-2: 133Mhz

2-3: 100Mhz

JFSB1(2-3)

YJUMPER-MG

1 1

100

JFSB1

YJ103

A

around it

* put close to every power pin

12

+

CB5

104P

CB7

104P

CB10

104P

CB9

104P

CB4

104P

*Put GND copper under Clock Gen.

connect to every GND pin

R176 4.7K

VCC3

SMBDT

SMBDT8,10,12

SMBCK

SMBCK8,10,12

USBCLK8

USBHUB15

GUICLK6

APICCLK2

SIO_OSC7

VCC3

1

2

3

PCI2

SIO_OSC

GUICLK

USBCLK

APICCLK

USBHUB

R224

10K

FS3

FS1

FS0

FS2

USBHUB

SIO_OSC

7

5

3

1

RN32

8P4R-10K

R359

10K

8

6

4

2

CB6

CB8

104P

104P

R185 10

R186 10

R184 10

R183 10

R215 10

X_10PC226

X_10PC166

X_10PC171

X_10PC165

X_10PC172

VCC3

VCC3

CB11

104P

133_-100 5

B

FS0

FS1

FS2

U12

1

VDD_XTAL

6

VDD_PCI

14

VDD_PCI

19

VDD_SDRAM

30

VDD_SDRAM

36

VDD_SDRAM

42

VDD_CORE

27

VDD_24/48

3

GND

9

GND

16

GND

22

GND

33

GND

39

GND

45

GND

47

GND

41

PWRDWN

23

SDATA

24

SCLK

26

48M/FS2

25

24_48M/FS3

48

REF1/FS0

2

REF0/CPUSTP

4 5

X1 X2

ICS94215

CLKX1

C207

10P

PCI0/MODE

PCI1/FS1

SDRAMIN

SDRAM_12

SDRAM10

SDRAM11

1 2

X1 YCRY14.31818H

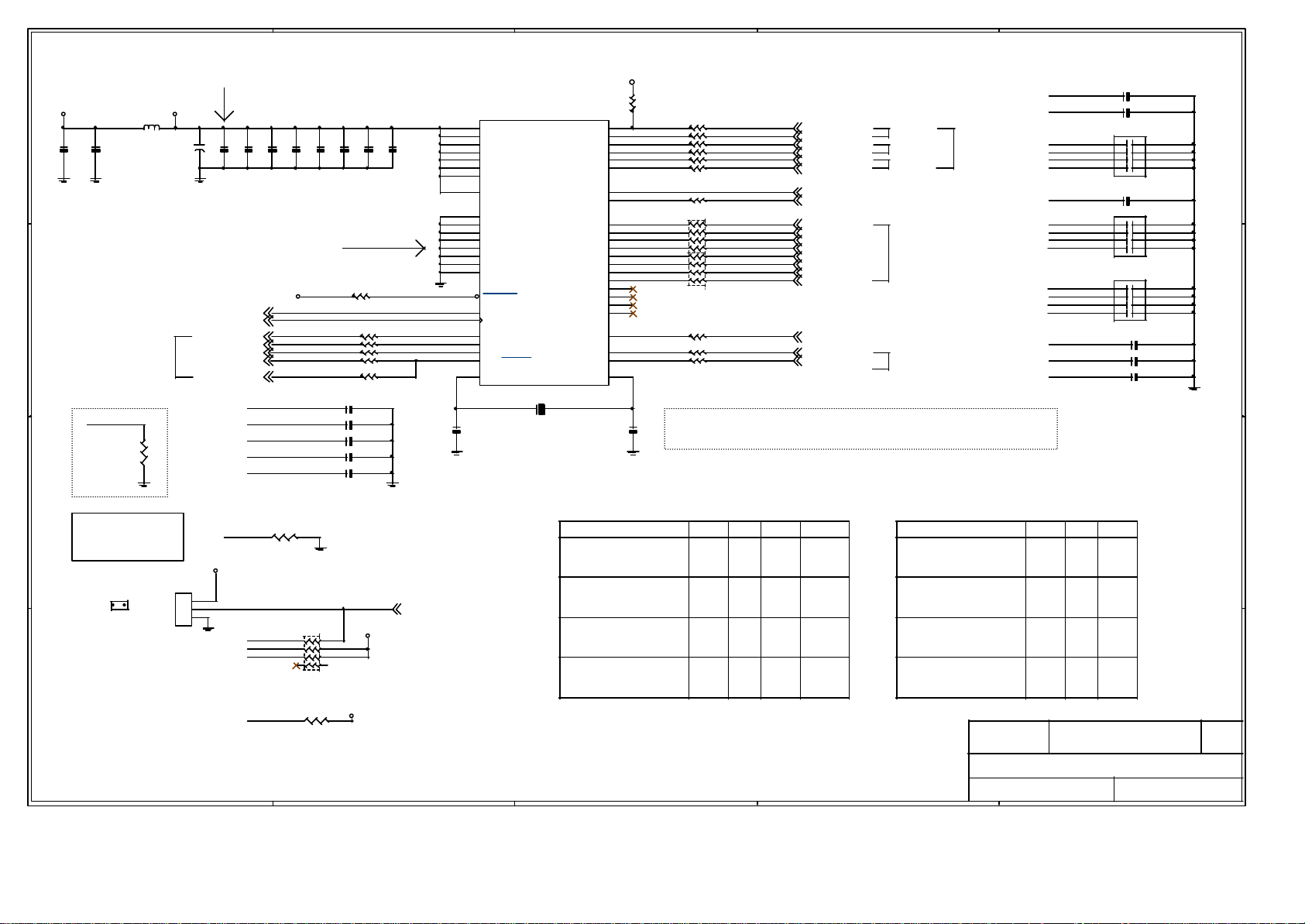

Frequency table for RTM560-141

4

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON

ON

ON

ON

ON ON

ON

ON

ON

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

SDRAM8

SDRAM9

VCC3

R223

10K

7

8

10

PCI2

11

PCI3

12

PCI4

13

PCI5

15

40

38

37

35

34

32

31

29

28

21

20

18

17

46

CPU_CS

44

CPUC0

43

CPUT0

FS3-0

3

OFF

OFF 3

OFF30ON

OFF 37.67

ON

ON

ON

ON

OFF

OFF

OFF

OFF

ON

ON

ON

R217 10

FS3 NPCLK

R218 10

PCI2

R219 10

R220 10

R221 10

R222 10

R182 33

1

RN21

3

8P4R-22

5

7

1

RN22

3

8P4R-22

5

7

H_CLK

R179 10

R180 10

R181 10

CLKX2

C192

All Clock Trace:Space = 6:18 except "C"

10P

2

1

OFF

OFF 1

OFF

ON

OFF

ON

ON

OFF

OFF

ON

OFF 3

OFF

ON

ON

OFF

OFF

OFF

ON

OFF

ON

ON

ON

OFF

OFF

OFF

ON

OFF

ON

ON

ON

SPCLK

PCICLK0

PCICLK1

1394PCLK

LANCLK

DCLKO

DCLKI

2

4

6

8

2

4

6

8

HCLKUSBCLK

-CPUCLKGUICLK

CPUCLK

PCI

CPU

33.3

133.3

75

37.5

33.3

100.2

66.8

33.4

79

39.5

36.7 OFF

110

38.3

115

120 0

133.3

33.3

83

27.7

33.3

100.2 3

33.4

66.8

124

31

129

32.3

34.5

138

143

35.8

SPCLK 7

NPCLK 6

PCICLK0 11

PCICLK1 11

1394PCLK 23

LANCLK 22

DCLKO 5

DCLKI 5

DCLK6 10

DCLK7 10

DCLK2 10

DCLK3 10

DCLK4 10

DCLK5 10

DCLK1 10

DCLK0 10

HCLK 4

-CPUCLK 2

CPUCLK 2

Spread

CPU/PCI

Spectrum 3

+/- 5%

4

2

+/- 5%

3

2

+/- 5%

2

OFF

3

3

OFF

4

OFF

4

OFF

OFF

3

3

OFF

OFF

2

OFF

4

4

OFF

OFF

OFF

4

B+3"

B

1" tolerance

B+3"

DCLKO as short as Possible

DCLKI = A+3"

A

100 mils tolerance

C+1"

CPUCLK = CPUCLK#

20:5:5:5:20

C

Frequency table for ICS94215

1

1

1

1

1

1

1

1ON

0

0

0

0

0

0

0

0

FS3-0

1

2

1

1

1

1

0

0

1

0

1

1

0

0

0

0

1

1

1

1

1

0

0 100.9

1

0

1

1

0

0

0

0

0

1

0

1+/- 5%

0

1

0

1

0

1

0

1

0

1

0

1

0

SPCLK

NPCLK

PCICLK0

PCICLK1

1394PCLK

LANCLK

DCLKI

DCLK6

DCLK7

DCLK2

DCLK3

DCLK4

DCLK5

DCLK1

DCLK0

HCLK

CPUCLK

-CPUCLK

CPU

0

133.3

117

115

113

111

110

109

107

100

105

103

102

101

95

90

Title

Micro-Star

Document Number

Last Revision Date:

C

D

Monday, July 23, 2001

X_10PC227

X_10PC228

CN11

7 8

5 6

3 4

1 2

X_8P4C-10P

47PC170

CN9

1 2

3 4

5 6

7 8

X_8P4C-10P

CN10

1 2

3 4

5 6

7 8

X_8P4C-10P

X_10PC167

10PC169

10PC168

PCI

CPU/PCI

4

33.3

39

3

38.33

3

3

37.00

36.67

36.33

3

35.67

330

33.33

4

35.00

3

34.33

33.57

3

34

3

33.6743

31.67

3

3

MS-6537

CLOCK SYNTHESIZER

Sheet of

E

Rev

00A

9

29

Loading...

Loading...