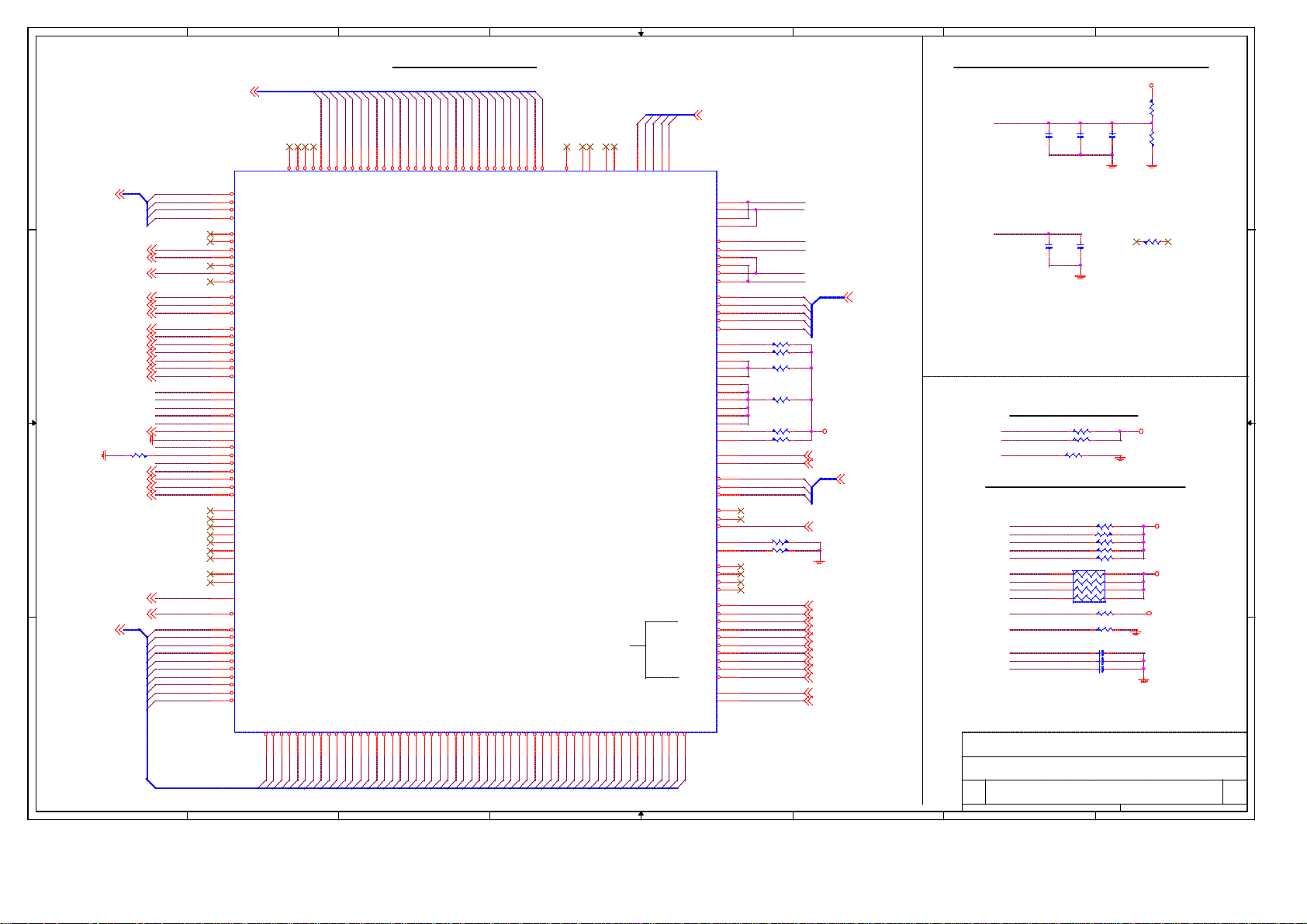

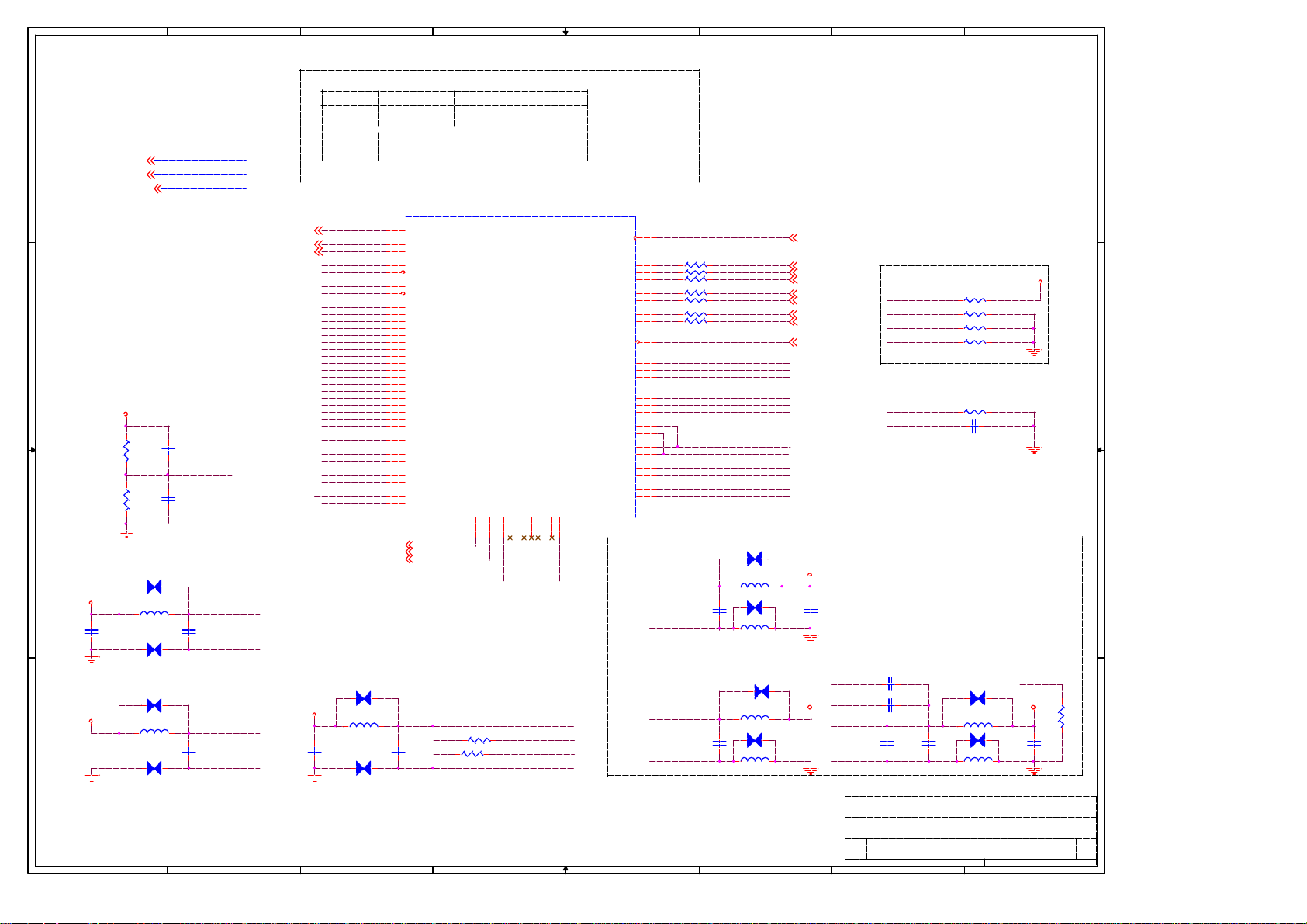

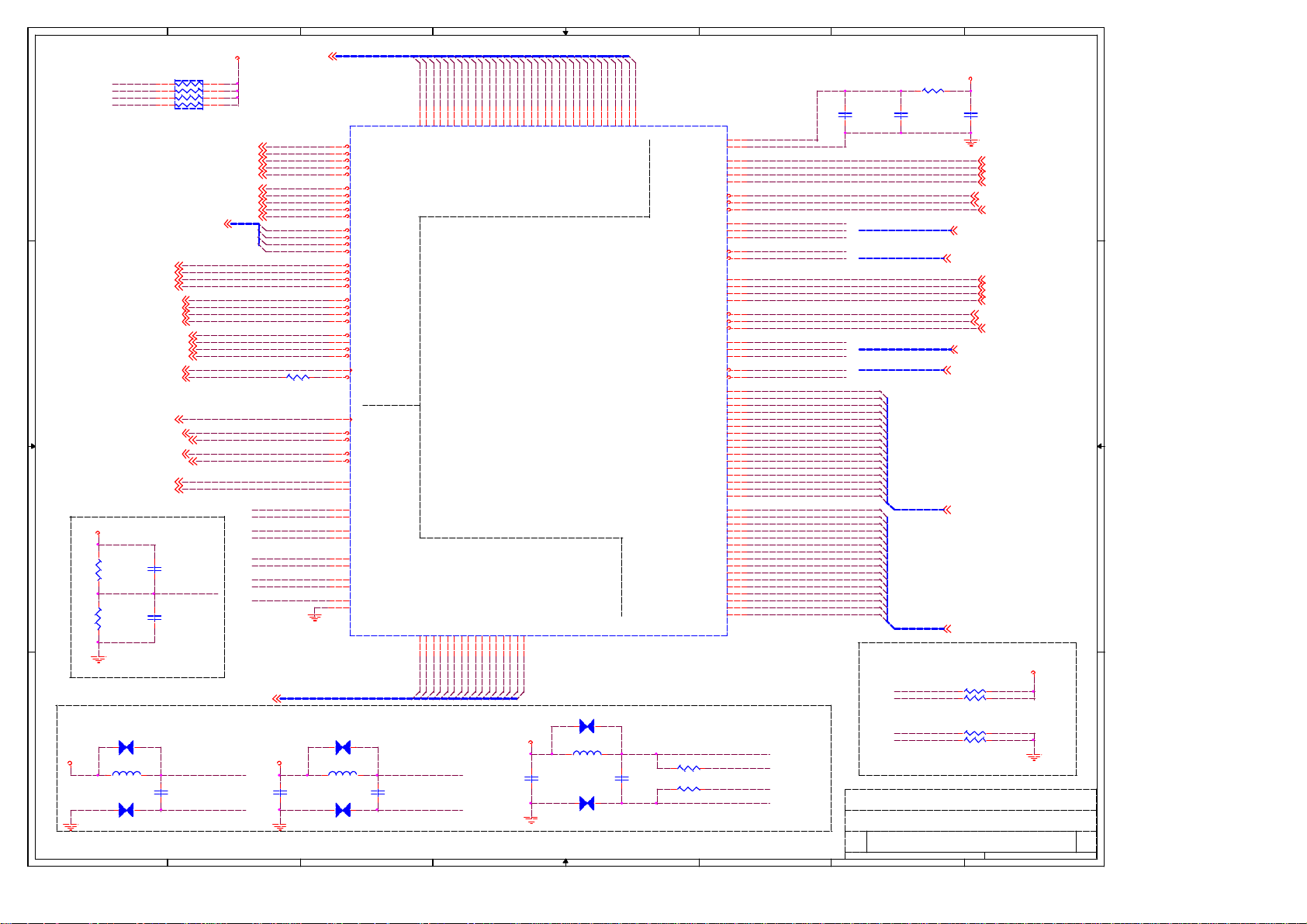

MSI MS-6535 Schematics

8

7

6

5

4

3

2

1

Cover Sheet

Block Diagram

MAIN CLOCK GEN

D D

DDR CLOCK BUFFER

mPGA478-B INTEL CPU Sockets

SIS 650 A1 NORTH BRIDGE

DDR SLOT

DDR TERMINATOR

SIS 961A2 SOUTH BRIDGE

SIS301B & DVI + TV-OUT

PCI SLOT 19

1

2

3

4

5 - 6

7- 10

11-12

12

13-16

17-18

Last Schematic Update Date:

9/13/2002 V01

VERSION:10C

MS-6535

SIS 650 CHIPSET

Willamette/Northwood 478pin mPGA-B Processor Schematics

CPU:

Willamette/Northwood mPGA-478B Processor

LAN CONTROLLER RTL8101 20

C C

IDE CONNECTOR

FRONT USB CONNECTOR

KB/MS & REAR USB CONNECTOR

AC'97 CODEC ALC201/ALC650

FRONT & REAR AUDIO CONNECTOR

LPC I/O(W83697HF)

HARDWARE MONITOR

SERIAL PORT

PARALLEL PORT

B B

FLASH MEMORY

VRM 9.X

ATX POWER CON & VGA CON

FRONT PANEL

CARDBUS OZ6933 & PCMCIA SOCKET

ACPI CONTROLLER W83302 MS-5

MEMORY STICK W83L518D & SOCKET

2-PORT 1394 - NEC72874

Decoupling Capacitor

A A

21RJ45 CONNECTOR

22

23

24

25

26

27

28

29

30

31

32

33

34

35-36

37

38

39

40

41HISTORY

System SIS650 Chipset:

SIS 650A1 (North Bridge) +

961A2 (South Bridge)

On Board Chip:

LPC Super I/O -- W83697HF

BIOS -- ISA

AC' 97 CODEC -- ALC650 Ver:D

CLOCK GENERATION -- ICS 952001

LAN -- RTL8101L

PCMCIA -- OZ6933

DVO -- SIS301B DVI + TV-OUT + 2nd CRT

1394 -- NEC72874- 2ports

MEMORY STICK -- W83L518D Ver:B

Expansion Slots:

PCI2.2 SLOT* 1 ( RISER CARD PCI*2 )

MICRO-STAR INT'L CO.,LTD.

Title

COVER PAGE

Size Document Number Rev

MS-6535 1.0C

C

8

7

6

5

4

3

Date: Sheet of

2

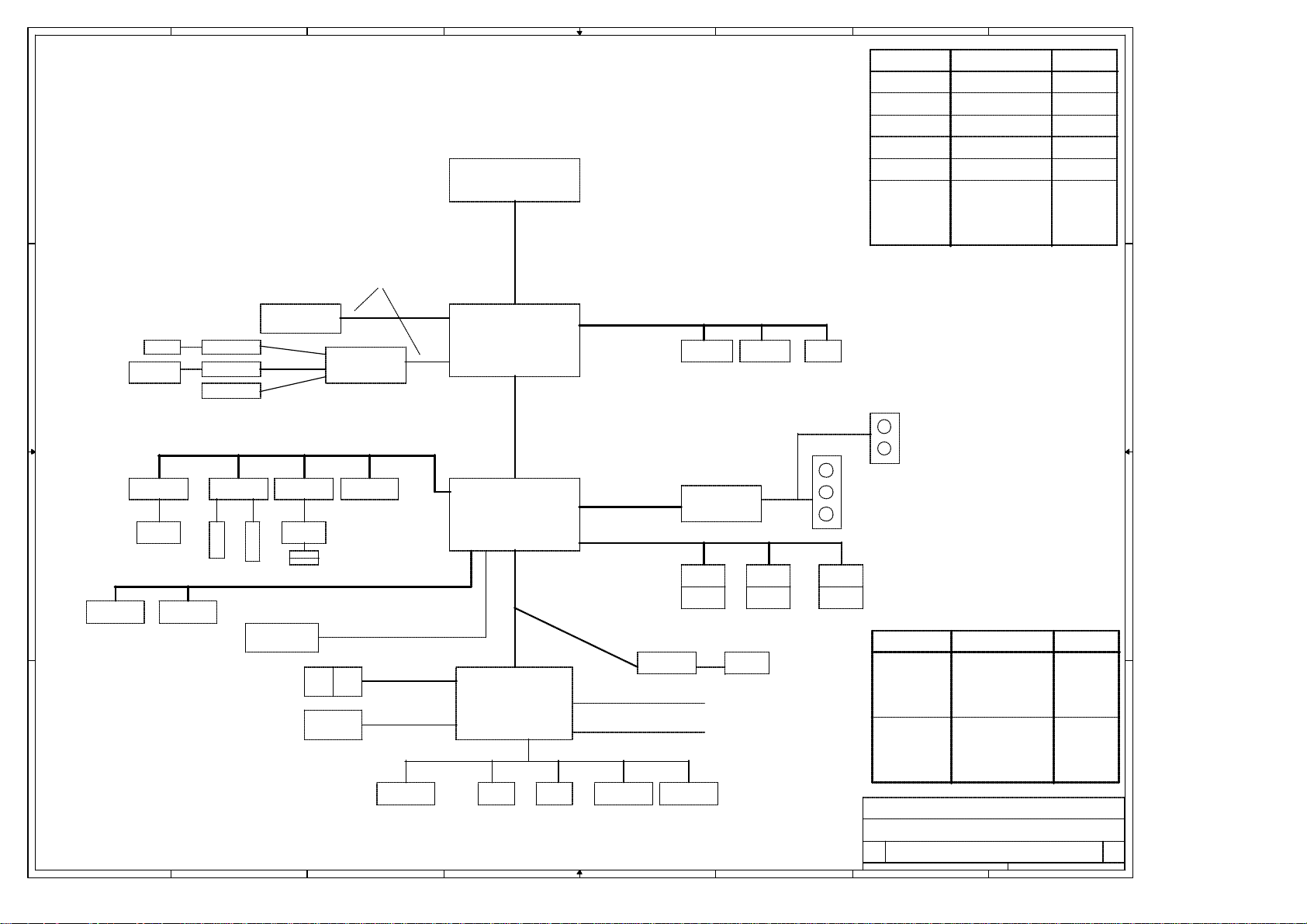

1 41Friday, September 13, 2002

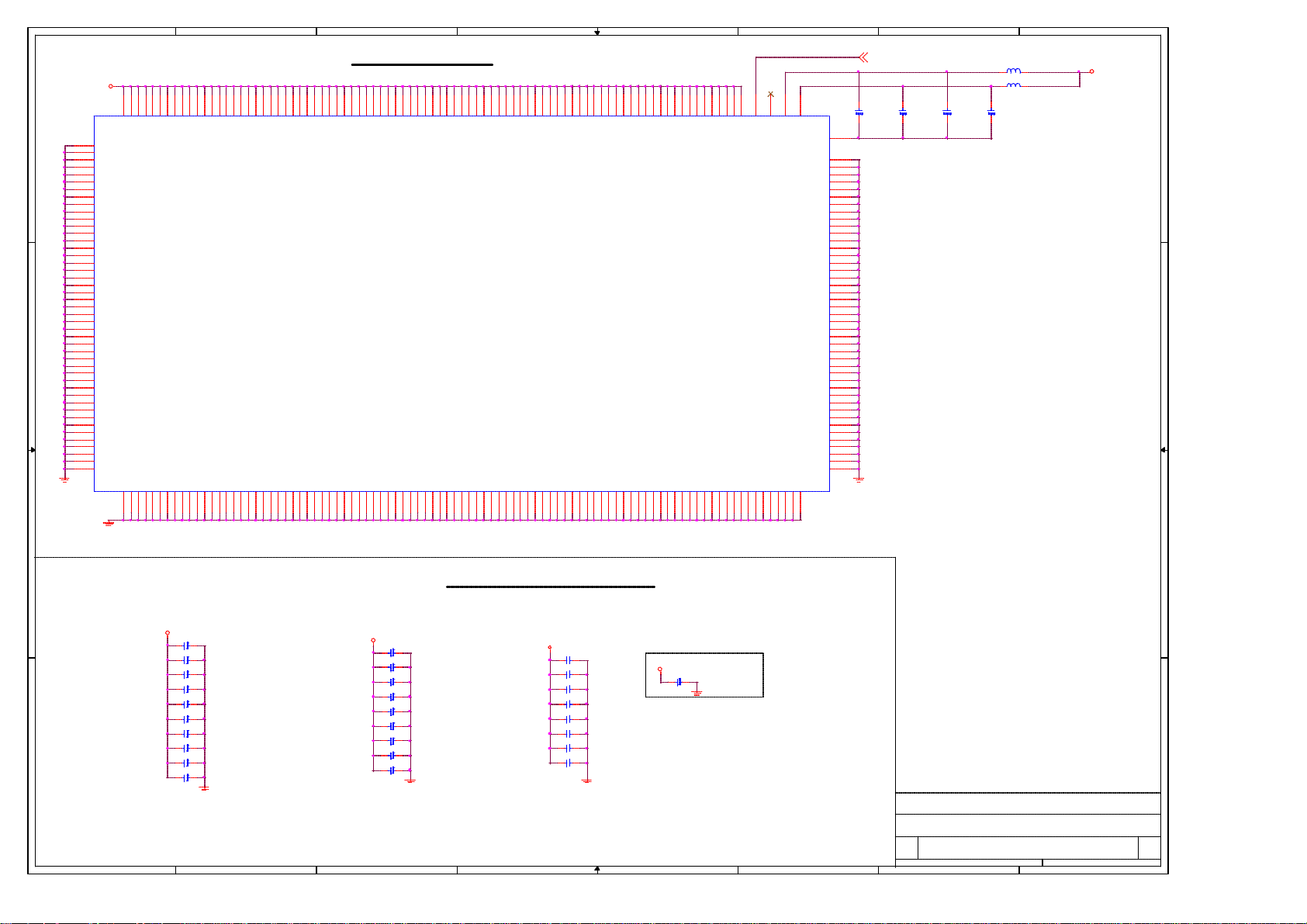

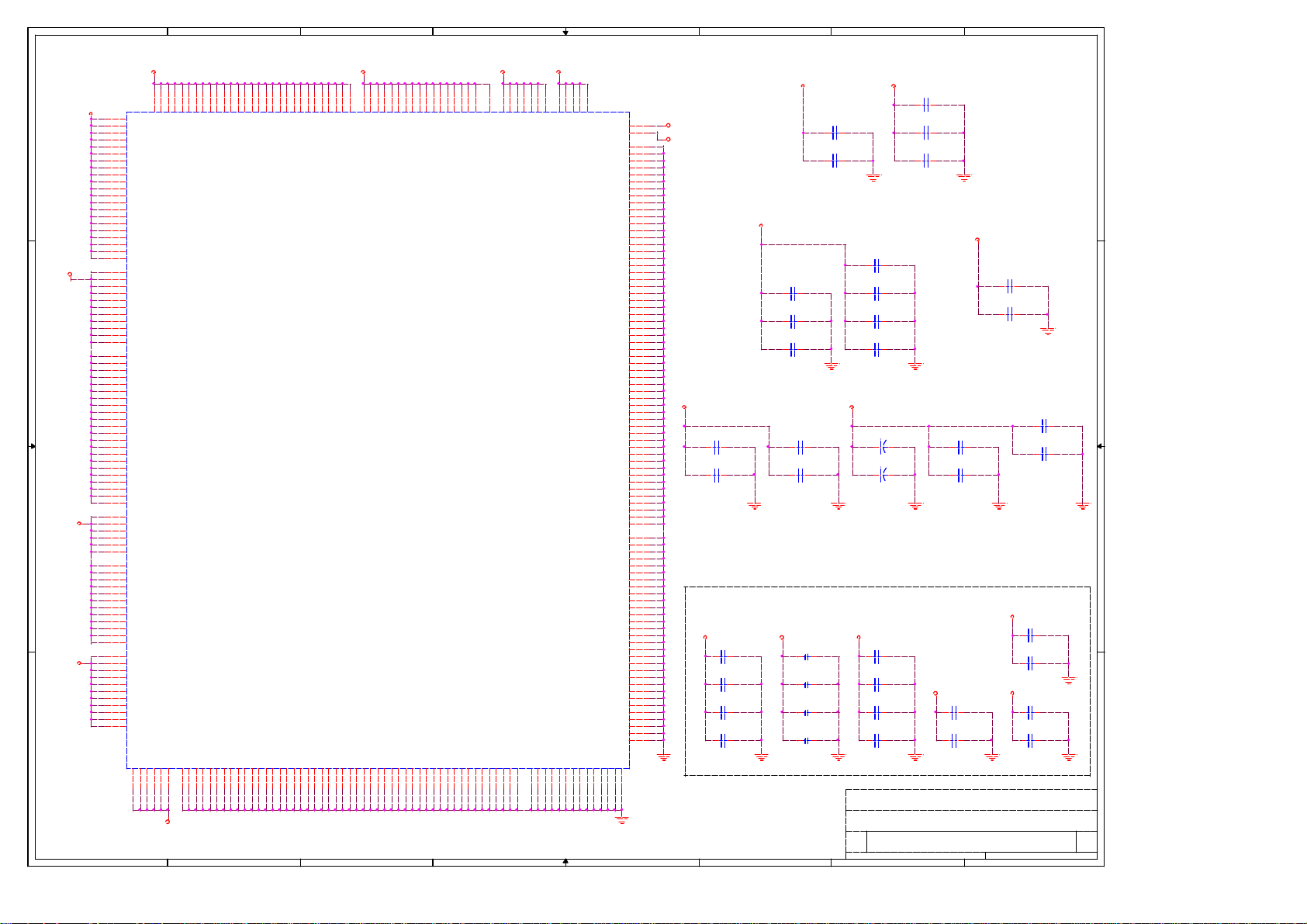

1

8

7

6

5

4

3

2

1

PCI DEVICE ROUTING TABLE

DEVICE

System Block Diagram

1394

LAN

D D

SOCKET-478

VGA

PCMCIA

PCI SLOT

INT pin IDSEL

INTD#

INTC#

AD23

AD26

INTB#MODEM

INTA#

INTB#

INTB#

AD25

AD17

INTC#

INTD#

INTA#

Host Bus

Simultaneous

display

VGA

CONNECTOR

C C

DVI-A

AV &

S-VIDEO

TMDS LCD

TV-OUT

2nd CRT

SIS301B

ENCODER

110MHz

SIS650A1

400MHz

DDR266

SSTL-2 Termination

(Only for DDR)

DIMM 1 DIMM 2

1GB / per DIMM

Rtt

FRONT

Support 6 PCI Devices

33MHz

LAN

RTL8101

RJ45

B B

IDE 1

A A

8

IDE 2

IEEE

1394

REAR

FRONT

KEYBOARD

PS/2 MOUSE

7

CARDBUS

OZ6933

PCMCIA

SOCKET

FAN1 FAN2

Legacy

ROM

PCI

SLOT 1

PS/2

6

FAN

CONTROL

ISA

GPIOs

SiS961A2

LPC Super I/O

W83697HF

COM2

HyperZip

533MB/s

AC'97

USB1.1 12MHz

LPC

Bus

VOLTAGE MONITOR

TEMPERATURE MONITOR

COM1 PARALLEL FLOPPY

5

M.S.

W83L518D

4

Audio Codec

ALC650

USB 0

USB 1

REAR

PORT

MEMORY

STICK

FRONT

USB 2

USB 3

REAR

FRONT PORT

3

Audio port

USB 4

USB 5

PCI RISER

DEVICE

PCI #1

INT pin

INTB#

INTC#

INTD#

INTA#

PCI #2

INTC#

INTD#

INTA#

INTB#

MICRO-STAR INT'L CO.,LTD.

Title

System Block Diagram

Size Document Number Rev

MS-6535 1.0C

Custom

Date: Sheet of

2

2 41Friday, September 13, 2002

IDSEL

AD17

AD18

1

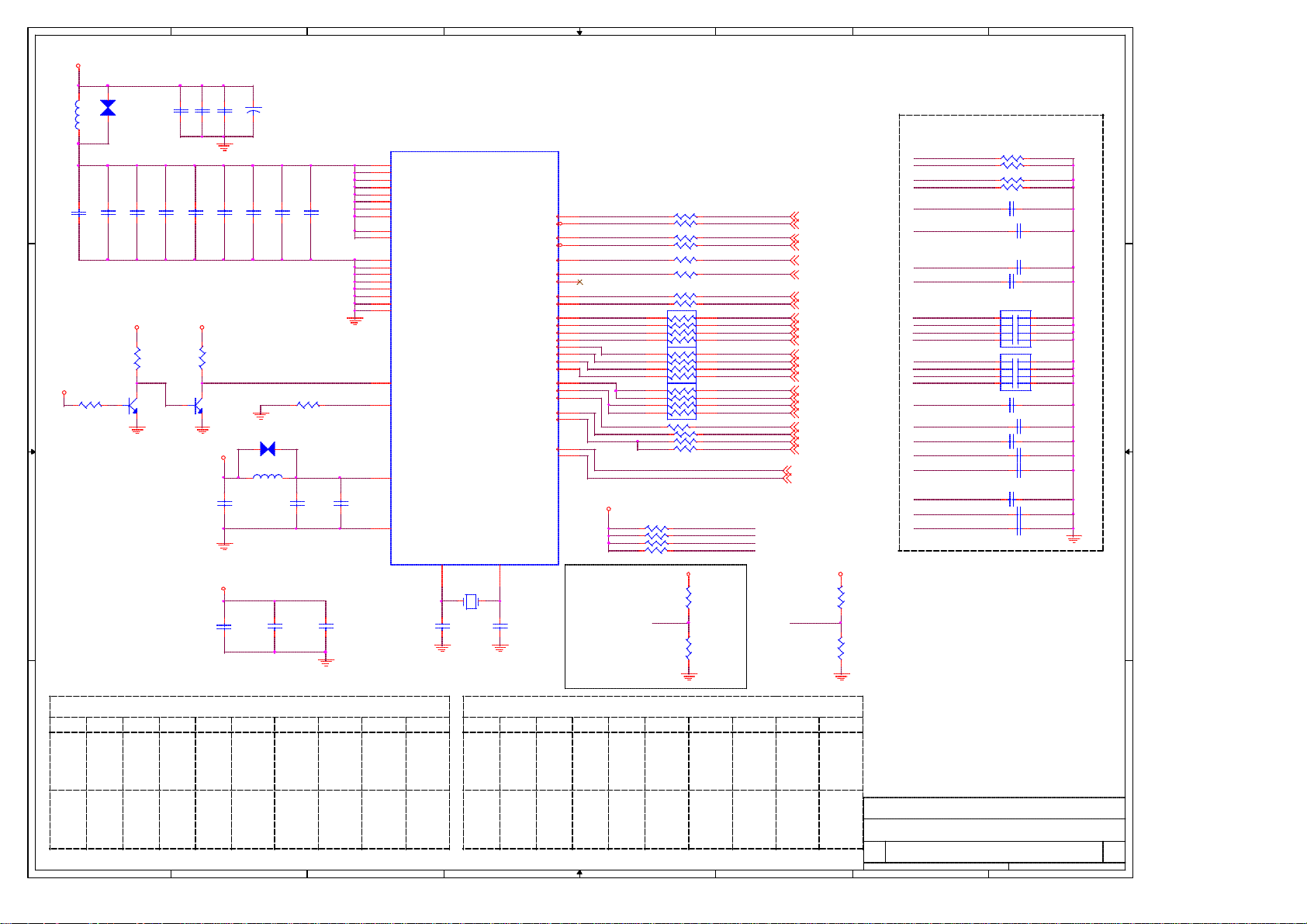

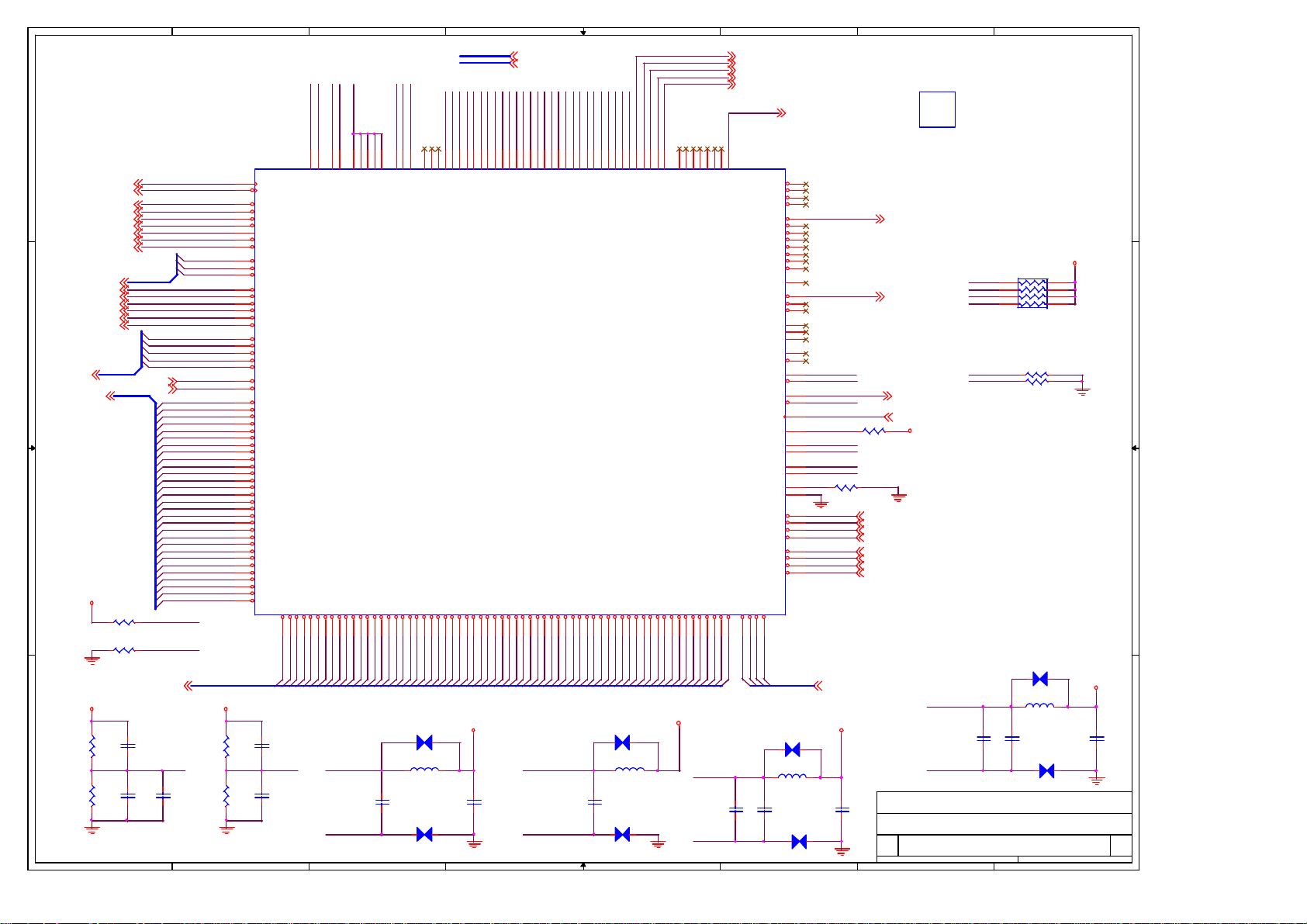

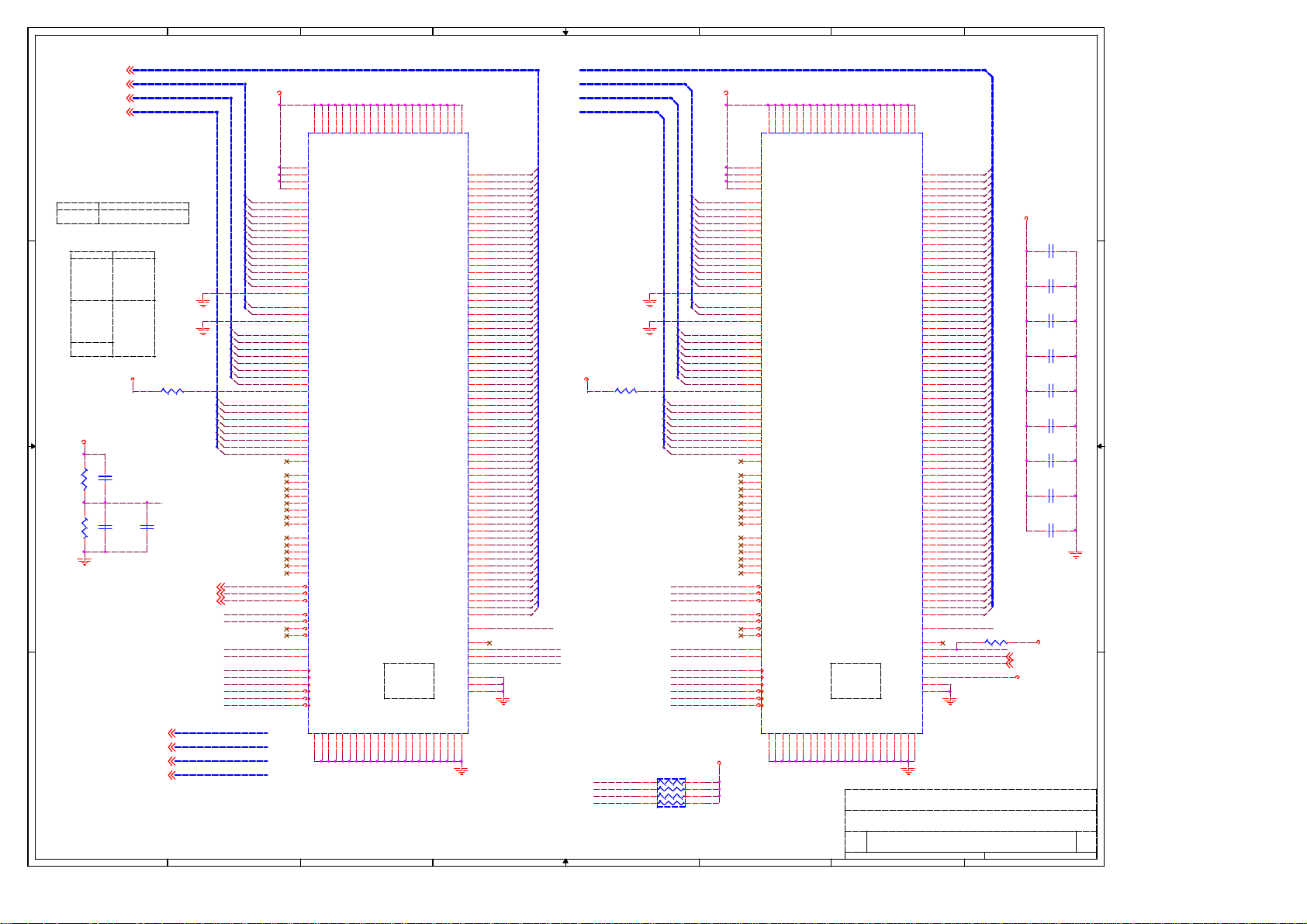

8

7

6

5

4

3

2

1

VCC3

C131

C188

C143

C121

104p

104p

R178

10K

Q10

NPN-3904LT1-S-SOT23

C1

103p

103p

C120

104p

VCC3

Q9

L13

X_80-0805

D D

CP13

X_COPPER

C132

C148

X_4.7u-0805

104p

VCC3

C C

VCCP

R179

10K

NPN-3904LT1-S-SOT23

R159

10K

103p

C167

104p

C166

104p

EC9

10u

R170

C146

104p

C163

104p

475RST

CP23 X_COPPER

VCC3

L33

X_80-0805

C197

104p

B B

C187

104p

VCC3

C198

X_4.7u-0805

C181

104p

C108

100P

Main Clock Generator

U10

ICS952001AF / ICW28342

1

VDDREF

11

VDDZ

13

VDDPCI

19

VDDPCI

28

VDD48

29

VDDAGP

42

VDDCPU

C165

100P

48

VDDSD

12

PCI_STOP#

45

CPU_STOP#

5

VSSREF

8

VSSZ

18

VSSPCI

24

VSSPCI

25

VSS48

32

VSSAGP

41

VSSCPU

46

VSSSD

33

PD#/VTT_PWRGD

38

IREF

36

VDDA

37

VSSA

XIN

6

Y3

14M-32pf-HC49S-D

C145

27p

CPUCLK0

CPUCLK#0

CPUCLK1

CPUCLK#1

AGPCLK0

AGPCLK1

PCICLK_F0/FS3

PCICLK_F1/FS4

REF0/FS0

REF1/FS1

REF2/FS2

24_48M/MULTISEL

XOUT

7

C149

27p

SDCLK

ZCLK0

ZCLK1

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

SCLK

SDATA

40

39

44

43

47

31

30

9

10

14

15

16

17

20

21

22

23

2

3

4

27

48M

26

35

34

ICS952001A : Stuff R120

ICW28342 : Stuff R119

FS3

FS4

FS0

FS1

FS2

MULTISEL

VCC3

Damping Resistors

Place near to the

Clock Outputs

R172

R171

R174 33

R173

R175

R167 22

R116

R115

RN21 33

7 8

5 6

3 4

1 2

RN19 33

7 8

5 6

3 4

1 2

RN20 33

7 8

5 6

3 4

1 2

R118

R166

R165

R164

R105 X_2.7K

R117 X_2.7K

R103 X_2.7K

R102 X_2.7K

CPUCLK0

33

CPUCLK-0

33

CPUCLK1

CPUCLK-1

33

SDCLK

22

AGPCLK0

ZCLK0

22

ZCLK1

22

33

SIO48M

22

UCLK48M

22

22

SMBCLK

SMBDAT

FS1

FS2

FS3

FS4

VCC3 VCC3

R120

4.7K

FS0 MULTISEL

R119

X_2.7K

CPUCLK0 5

CPUCLK-0 5

CPUCLK1 7

CPUCLK-1 7

SDCLK 8

AGPCLK0 7

ZCLK0 9

96XPCLK

SIOPCLK

PCICLK1

PCICLK2

CARD_CLK

1394PCLK

PCICLK5

MS_CLK

ZCLK1 13

96XPCLK 13

SIOPCLK 27

PCICLK1 19

PCICLK2 19

CARD_CLK 35

1394PCLK 39

PCICLK5 20

MS_CLK 38

REFCLK0

REFCLK0 9

REFCLK1

REFCLK1 14

APICCLK APICCLK

APICCLK 14

REFCLK3

REFCLK3 17

SCLK

SCLK 35,36

SIO48M 27

UCLK48M 15

MS_48 38

SMBCLK 4,11,14,37

SMBDAT 4,11,14,37

Frequency Selection

R162

4.7K

R163

X_0

By-Pass Capacitors

Place near to the Clock Outputs

CPUCLK0

CPUCLK-0

CPUCLK1

CPUCLK-1

SDCLK

AGPCLK0

ZCLK0

ZCLK1

PCICLK2

PCICLK1

SIOPCLK

96XPCLK

MS_CLK

PCICLK5

1394PCLK

CARD_CLK

R187

R186 49.9RST

R189

R188

C185 X_10p

C186 X_10p

C103 X_10p

C102 X_10p

CN4 X_10p

1 2

3 4

5 6

7 8

CN3 X_10p

1 2

3 4

5 6

7 8

C105 10p

REFCLK0

REFCLK1

SCLK

REFCLK3

UCLK48M

SIO48M

MS_48

C107 10p

C106 10p

C26 10p

C104 10p

C184 10p

C183 10p

C182 10p

49.9RST

49.9RST

49.9RST

SIS650 CLOCK SIS650 CLOCK

CPU PCI

FS4 FS1FS2FS3 FS0

0 0 0

0

0

0

0

0

0

A A

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

8

0 0 1

0 1 0

0 1 1

1 0 1

1 1

1 1 1

0 0 0

0 0 1

0 1 0

0 1 1

1 0 1

1 1

1 1 1

001

0

001

0

SDRAM

(MHz) (MHz) (MHz)

66.67 66.67 66.67 66.67 33.33

100

100

100

200

100

133

100

150

100

125

100

160

100

133

100

200

100

166

100

166

80.00

133

80.00

133

95.00

95.00

95.00

126

66.67

66.67

7

ZCLK

(MHz)

66.67

66.67

66.67

60.00

62.50

66.67

80.00

66.67

62.50

71.43

66.67

66.67

63.33

63.33

50.00

AGPCLK

(MHz)

66.67

66.67

66.67

60.00

62.50

66.67

66.67

66.67

62.50

83.33

66.67

66.67

63.33

63.33

50.00

6

33.33

33.33

33.33

30.00

31.25

33.33

33.33

33.33

31.25

41.67

33.33

33.33

31.67

31.67

25.00

CPU PCI

SDRAM

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

5

0 0 1

0 1 0

0 1 1

1 0 1

1 1

1 1 1

0 0 0

0 0 1

0 1 0

0 1 1

1 0 1

1 1

1 1 1

0 0 0

0

(MHz) (MHz) (MHz)

105

140

100

100

108

144

100

001

0

001

0

4

134

112

149

133

100

133

133

133

166

100

133

100

100

100

166

133

160

100

133

100

100

100

166

133

160

AGPCLK

ZCLKFS4 FS1FS2FS3 FS0

(MHz)(MHz)

70.00

67.27

72.00

67.27

74.67

66.67

66.67

66.67 66.67

80.00

80.00

83.33

80.00

100

100

100

100

3

70.00 35.00

67.27

33.63

72.00

36.00

67.27

33.63

74.67

37.33

66.67

33.33

66.67

33.33

33.33

33.33

66.67

33.33

66.67

31.25

62.50

33.33

66.67

33.33

66.67

33.33

66.67

31.25

62.50

33.33

66.67

MICRO-STAR INT'L CO.,LTD.

Title

MAIN CLOCK GEN

Size Document Number Rev

MS-6535 1.0C

Custom

Date: Sheet of

2

3 41Friday, September 13, 2002

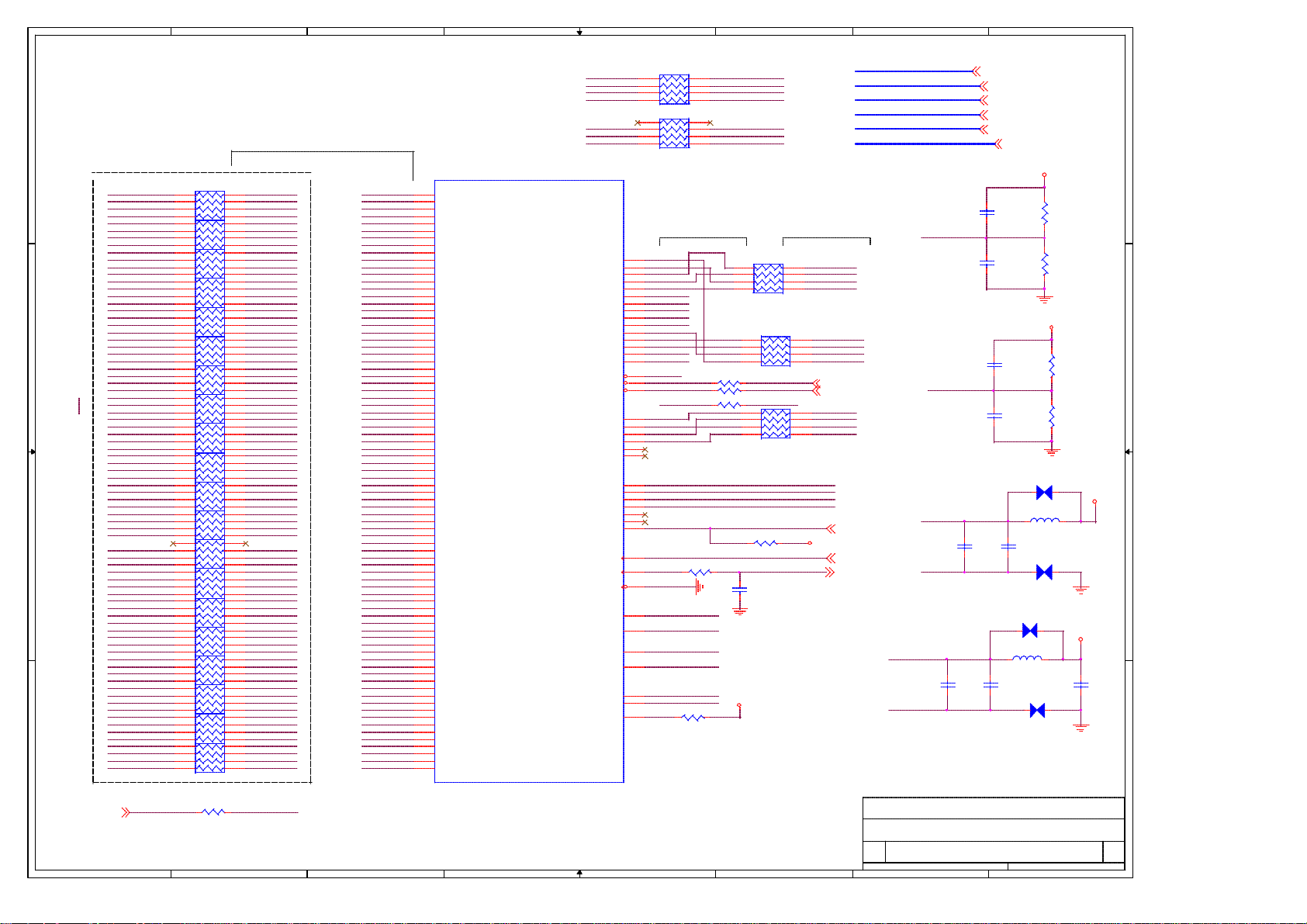

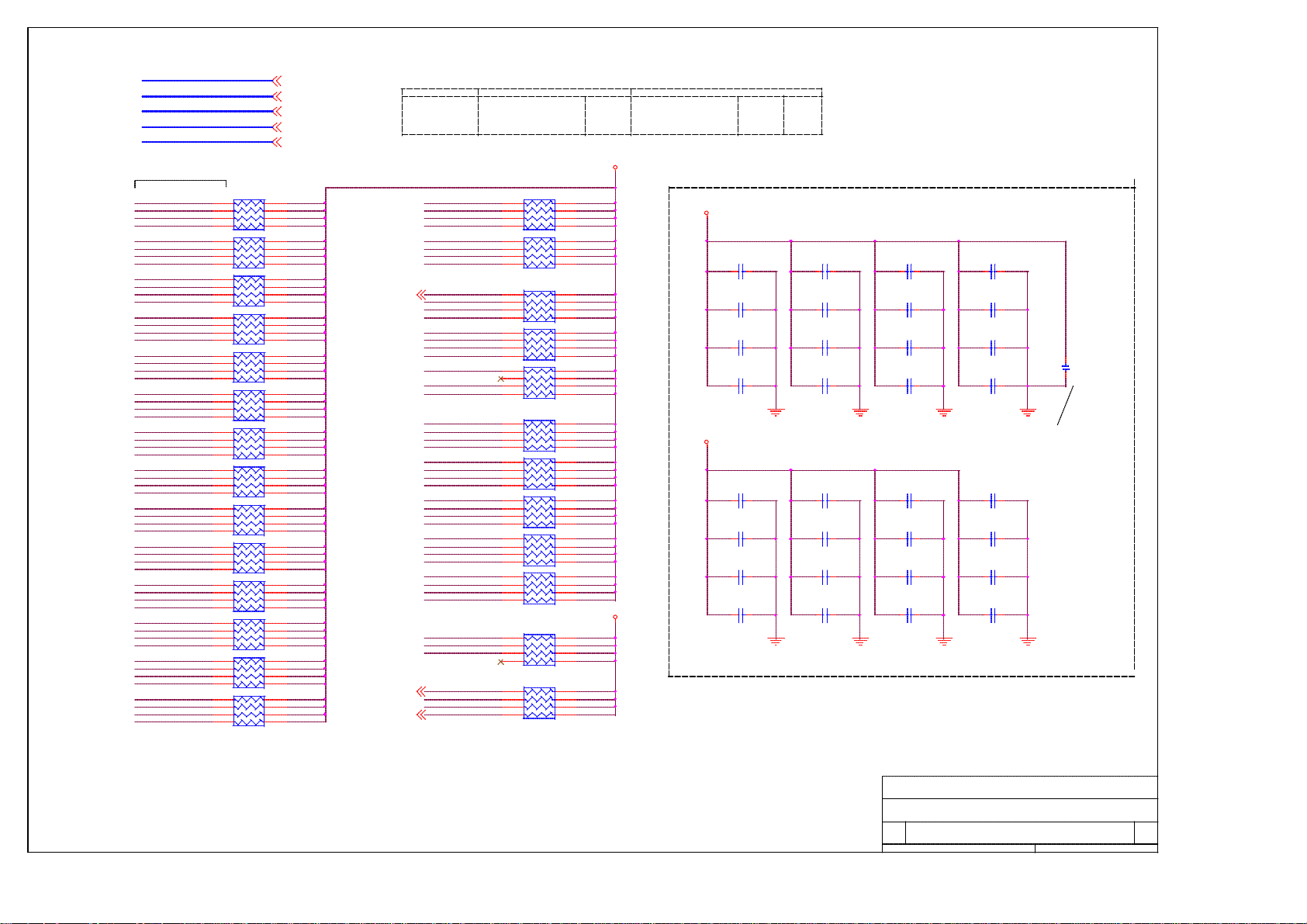

1

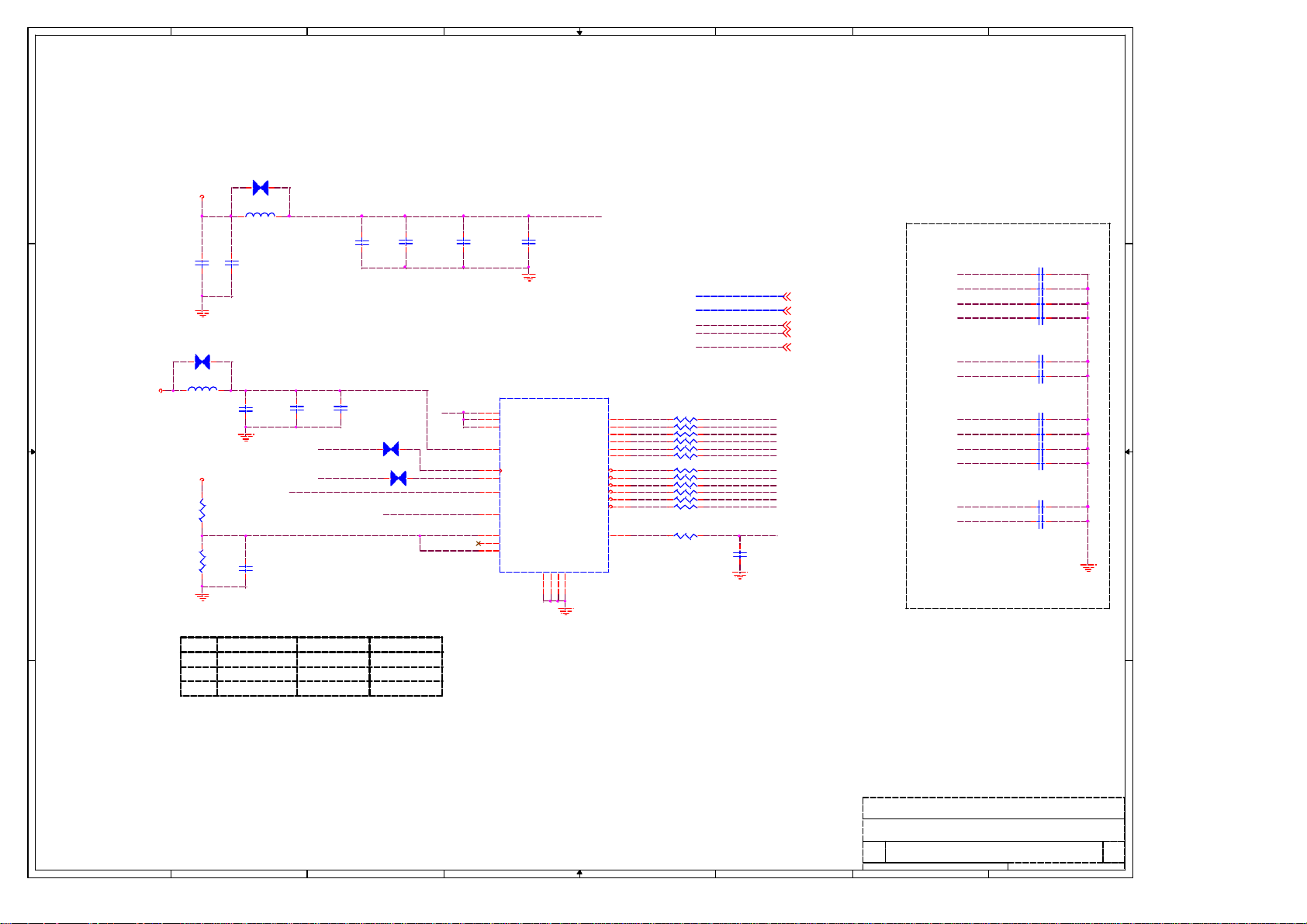

8

7

6

5

4

3

2

1

D D

CP58 X_COPPER

VCC2.5V

C429

104p

C C

B B

VCC2.5V

CP57 X_COPPER

L75

X_80-0805

VCC2.5V

C408

103p

C410

X_4.7u-0805

R390

X_10KST

R391

X_10KST C458

L77

X_80-0805

X_104p

C424

X_4.7u-0805

C412

104p

SMBCLK

SMBDAT

FWDSDCLKO

C427

103p

CP59

X_COPPER

CP60 X_COPPER

FB_OUT

1.25V

C426

104p

Clock Buffer (DDR)

(OPTIONS)

1: (ICS-93705)

CBVDD

CBVDD

C459

104p

3

12

23

10

7

22

8

20

9

18

21

C434

104p

U23

ICS93722 / ICW28352

VDD

VDD

VDD

AVDD

SCLK

SDATA

CLK_IN

FB_IN

NC

NC

NC

GND

GND

111528

6

GND

GND

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLK#0

CLK#1

CLK#2

CLK#3

CLK#4

CLK#5

FB_OUT

2

4

13

17

24

26

1

5

14

16

25

27

19

R359 0

R358

R367

R383

R378

R380 0

R360

R357

R365

R382 0

R379

R381

R384

DDRCLK[0..8]

DDRCLK-[0..8]

SMBCLK

SMBDAT

FWDSDCLKO

DDRCLK8

DDRCLK7

0

DDRCLK2

0

DDRCLK3

0

DDRCLK0

0

DDRCLK1

DDRCLK-8

0

DDRCLK-7

0

DDRCLK-2

0

DDRCLK-3

DDRCLK-0

0

DDRCLK-1

0

22

FB_OUT

C471

22p

DDRCLK[0..8] 11

DDRCLK-[0..8] 11

SMBCLK 3,11,14,37

SMBDAT 3,11,14,37

FWDSDCLKO 8

By-Pass Capacitors

Place near to the Clock Buffer

DDRCLK0

DDRCLK1

DDRCLK2

DDRCLK3

DDRCLK8

DDRCLK7

DDRCLK-0

DDRCLK-1

DDRCLK-2

DDRCLK-3

DDRCLK-8

DDRCLK-7

C465 X_10p

C467 X_10p

C452 X_10p

C470 X_10p

C415 X_10p

C414 X_10p

C466 X_10p

C468 X_10p

C437 X_10p

C469 X_10p

C416 X_10p

C413 X_10p

PART

ICW28353 ICS93722

R640

10KST

R641

10KST

C642

A A

8

104p

7

X

X

X

ICW28352

X

X

X

6

MICRO-STAR INT'L CO.,LTD.

Title

DDR CLOCK BUFFER

Size Document Number Rev

MS-6535 1.0C

Custom

5

4

3

Date: Sheet of

2

4 41Friday, September 13, 2002

1

8

7

6

5

4

3

2

1

CPU GTL REFERNCE VOLTAGE BLOCKCPU SIGNAL BLOCK

HA#[3..31]7

VID[0..4] 32

D D

C C

B B

A A

A3~A16#, HREQ#0~4 is strobed by HADSTB#0

A17~A35# is strobed by HADSTB#1

U19A

PROCHOT#

IGNNE#

SMI#

A20M#

CPUSLP#

E21

G25

P26

V21

AC3

AA3

AB2

AF26

AB26

A22

AD2

AD3

AE21

AF24

AF25

AD6

AD5

AB23

AB25

AA24

AA22

AA25

Y21

Y24

Y23

W25

Y26

W26

V24

V6

B6

Y4

W5

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A7

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

HDBI#[0..3]7

STPCLK#14

HDBSY#7

HDRDY#7

HTRDY#7

HLOCK#7

HDEFER#7

Trace : 10

mil width

10mil space

CPU_TMPA28 VCCP

R232 X_33

CPUSLP#14

CPU_GD7

CPURST#7

HD#[0..63]7

8

HDBI#0

HDBI#1

HDBI#2

HDBI#3

FERR#14

INIT#14

HADS#7

HBNR#7

HIT#7

HITM#7

HBPRI#7

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

CPU_TMPA

THERMTRIP#

IGNNE#14

SMI#14

A20M#14

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

D53#

D52#

D51#

D50#

V22

U21

V25

U23

U24

HD#53

HD#51

HD#50

HD#49

HD#52

7

A34#

A33#

D49#

D48#

U26

HD#48

HA#31

A32#

A31#

D47#

D46#

T23

T22

HD#47

HD#46

HA#30

HA#29

A30#

D45#

T25

T26

HD#45

HD#44

HA#28

A29#

D44#

R24

HD#43

HA#27

A28#

A27#

D43#

D42#

R25

HD#42

HA#25

HA#26

A26#

D41#

P24

R21

HD#41

HD#40

HA#24

A25#

A24#

D40#

D39#

N25

HD#39

HA#22

HA#23

A23#

D38#

N26

M26

HD#37

HD#38

HA#21

A22#

A21#

D37#

D36#

N23

HD#36

HA#20

HA#19

A20#

D35#

M24

P21

HD#34

HD#35

6

HA#18

A19#

D34#

N22

HD#33

HA#17

A18#

A17#

D33#

D32#

M23

HD#32

HA#15

HA#16

A16#

D31#

H25

K23

HD#30

HD#31

HA#14

A15#

D30#

J24

HD#29

HA#13

A14#

A13#

D29#

D28#

L22

HD#28

HA#11

HA#12

A12#

D27#

M21

H24

HD#26

HD#27

HA#10

A11#

A10#

D26#

D25#

G26

HD#25

HA#8

HA#9

A9#

D24#

L21

D26

HD#23

HD#24

HA#7

A8#

A7#

D23#

D22#

F26

HD#22

HA#5

HA#6

A6#

D21#

E25

F24

HD#20

HD#21

HA#4

A5#

A4#

D20#

D19#

F23

HD#19

HA#3

G23

HD#18

AE25A5A4

A3#

DBR#

Differential

Host Data

Strobes

D18#

D17#

D16#

D15#

E24

H22

D25

J21

HD#14

HD#16

HD#15

HD#17

5

VCC_SENSE

VSS_SENSE

D14#

D13#

D12#

D11#

D23

C26

H21

HD#11

HD#12

HD#13

AD26

AC26

ITP_CLK1

ITP_CLK0

D10#

D9#

D8#

G22

B25

C24

HD#8

HD#9

HD#10

D7#

C23

HD#7

VID4

AE1

VID4#

D6#

B24

HD#6

VID3

AE2

VID3#

D5#

D22

HD#5

VID2

AE3

VID2#

D4#

C21

HD#4

VID1

AE4

VID1#

D3#

A25

HD#3

AE5

A23

VID0

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

D0#

B22

B21

HD#0

HD#2

HD#1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

PGA-S478-F02

4

GTLREF1

AA21

GTLREF2

AA6

F20

F6

AB4

BPM#5

BPM#4

AA5

Y6

AC4

AB5

BPM#1

BPM#0

AC6

HREQ#4

H3

J3

HREQ#3

HREQ#2

J4

K5

HREQ#1

HREQ#0

J1

AD25

R410 56

A6

R231 56

Y3

W4

R331 56

U6

AB22

AA20

AC23

R221 56

AC24

AC20

AC21

AA2

R409 56

R225 56

AD24

AF23

AF22

F4

RS#2

RS#1

G5

F1

RS#0

V5

AC1

H6

P1

R343 49.9RST

L24

R233 49.9RST

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

D0~D15, HDBI#0 is strobed by HDSTBN/P#0

D16~D31, HDBI#1 is strobed by HDSTBN/P#1

D32~D47, HDBI#2 is strobed by HDSTBN/P#2

D48~D63, HDBI#3 is strobed by HDSTBN/P#3

CPUCLK-0 3

CPUCLK0 3

RS#[0..2] 7

HBR#0 7

* Short trace

HADSTB#1 7

HADSTB#0 7

HDSTBP#3 7

HDSTBP#2 7

HDSTBP#1 7

HDSTBP#0 7

HDSTBN#3 7

HDSTBN#2 7

HDSTBN#1 7

HDSTBN#0 7

NMI 14

INTR 14

HREQ#[0..4] 7

3

Length < 1.5inch.

GTLREF1

2/3*Vccp

C261

C260

220p

220p

Change R226 to 75 ohm for GTLREF voltage

reference from 2/3VCCP to be 3/5VCCP

Length < 1.5inch.

C316

220p

2/3*Vccp

C317

GTLREF2

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU ITP BLOCK

ITP_TMS

R337 39

ITP_TDO

R332 75

ITP_TCK

R344 27

CPU STRAPPING RESISTORS

ALL COMPONENTS CLOSE TO CPU

PROCHOT#

CPU_GD

HBR#0

CPURST#

THERMTRIP#

BPM#0

BPM#1

BPM#4

BPM#5

ITP_TDI

ITP_TRST#

CPU_GD

CPURST#

CPUSLP#

MICRO-STAR INT'L CO.,LTD.

Title

mPGA478 CPU-1

Size Document Number Rev

MS-6535 1.0C

Custom

Date: Sheet of

2

R345 62

R224 300

R290 49.9RST

R222 49.9RST

R293 62

1 2

3 4

5 6

7 8

R297 150

R330 680

VCCP

R227

49.9RST

C237

1u

X_102pC236

X_102pC234

X_223pC235

R226

75RST

R336

X_49.9RST220p

Reserved dummy PAD

VCCP

VCCP

RN4647

VCCP

VCCP

5 41Friday, September 13, 2002

1

8

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AD18

VCC

VSS

VCC

VSS

AD21

AD23

VCC

VSS

AD4

VCC

VSS

AD8

VCC

VSS

AE11

AA16

VCC

VSS

AE13

U19B

VCC

VCC

VCC

AD10

VSS

AD12

VSS

AD14

VSS

AD16

VCC

VSS

D D

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AA23

VSS

AA26

VSS

AA4

VSS

AA7

VSS

AA9

VSS

AB10

VSS

AB12

VSS

AB14

VSS

AB16

VSS

AB18

VSS

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C C

AA18

VCC

VSS

AE15

VCC

VSS

AA8

VCC

VSS

AE17

AB11

AB13

VCC

VSS

AE19

AE22

AB15

VCC

VSS

AE24

AB17

VCC

VSS

AE26

7

AB19

VCC

VSS

AE7

AB7

VCC

VSS

AE9

AB9

VCC

VSS

AF1

AC10

VCC

VSS

AF10

VCC

VSS

AC12

VCC

VSS

AF12

AC14

VCC

VSS

AF14

AC16

VCC

VSS

AF16

AC18

AF18

AC8

VCC

VSS

AF20

AD11

VCC

VSS

AF6

6

CPU VOLTAGE BLOCK

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

AE20

VCC

VSS

C11

AE6

C13

VCC

VSS

AE8

C15

AF11

VCC

VCC

VSS

VSS

C17C2C19

AF13

VCC

VSS

AF15

AF17

AF19

AF2

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

C22

C25C5C7C9D12

AF21

VCC

VSS

AF5

AF7

VCC

VSS

VCC

VSS

AF9

D14

B11

VCC

VSS

D16

5

B13

B15

B17

B19B7B9

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

D18

D20

D21D3D24D6D8E1E11

VCC

VSS

C10

VCC

VSS

VCC

VSS

C12

C14

VCC

VSS

C16

VCC

VSS

E13

C18

VCC

VSS

E15

C20C8D11

VCC

VCC

VCC

VSS

VSS

VSS

E17

E19

E23

D13

VCC

VSS

E26

D15

VCC

VSS

E4

D17

D19D7D9

VCC

VCC

VSS

VSS

E7E9F10

VCC

VSS

VCC

VSS

4

E10

E12

E14

E16

E18

E20E8F11

F13

F15

F17

F19

AF4

F9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC-VID

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F12

F14

F16

F18F2F22

F25F5F8

G21G6G24

G3H1H23

H26H4J2

AE23

AF3

VCC-VIDPRG

VSS

VSS

VSS

J22

J25J5K21

3

AD20

VCCA

VSSA

VCC-IOPLL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-F02

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

VCC_VID 37

C239

X_10u-1206

C248

X_10u-1206

2

C238

22u-1206

L44 4.7u-10%-1206

L51 4.7u-10%-1206

C249

22u-1206

1

VCCP

B B

CPU DECOUPLING CAPACITORS

VCCP

C268

10u-1206

C295

10u-1206

C281

10u-1206

C259

X_10u-1206

C276

10u-1206

C341

10u-1206

C283

10u-1206

C304

10u-1206

A A

C270

X_10u-1206

C262

10u-1206

PLACE CAPS WITHIN CPU CAVITY

8

7

VCCP

C282

10u-1206

C309

X_10u-1206

C292

X_10u-1206

C254

10u-1206

C334

X_10u-1206

C269

10u-1206

C256

X_10u-1206

C252

10u-1206

C272

X_10u-1206

VCCP

C325

10u-1206

C324

X_10u-1206

C310

X_10u-1206

C266

10u-1206

C297

10u-1206

C264

10u-1206

C288

X_10u-1206

C296

10u-1206

VCCP

C346

X_10u-1206

MICRO-STAR INT'L CO.,LTD.

Title

mPGA478 CPU-2

Size Document Number Rev

MS-6535 1.0C

Custom

6

5

4

3

Date: Sheet of

2

6 41Friday, September 13, 2002

1

8

D D

CPUCLK13

CPUCLK-13

HDEFER#5

HLOCK#5

HTRDY#5

CPURST#5

CPU_GD5

HBPRI#5

RS#[0..2]5

HADS#5

HITM#5

HIT#5

HDRDY#5

HDBSY#5

HBNR#5

C C

HREQ#[0..4]

HREQ#[0..4]5

HA#[3..31]5

B B

VCCP

VCCP VCCP

R200

A A

75RST

R204

150RST

8

CPUCLK1

CPUCLK-1

HDEFER#

HLOCK#

HTRDY#

CPURST#

CPU_GD

HBR#0

HBR#05

RS#[0..2]

HADS#

HITM#

HIT#

HDRDY#

HDBSY#

HBNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HADSTB#15

HADSTB#05

HA#[3..31]

R217

HNCOMP

20RST

R216

HPCOMP

Rds-on(p) = 56 ohm

110RST

HPCVERF = 2/3 VCCP

HD#[0..63]5

C206

X_103p

C514

X_104p

place this capacitor

under 650 solder side

HBPRI#

RS#2

RS#1

RS#0

HADSTB#1

HADSTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

C214

104p

HD#[0..63]

7

AJ26

AH26

U26

U24

V26

C20

D19

T27

U25

T24

T26

U29

V28

T28

U28

W26

V24

V27

W28

W29

W24

W25

Y27

AD24

AA24

AF26

AE25

AH28

AD26

AG29

AE26

AF28

AC24

AG28

AE29

AD28

AC25

AD27

AE28

AF27

AB24

AB26

AC28

AC26

AC29

AA26

AB28

AB27

AA25

AA29

AA28

Y26

Y24

Y28

R201

150RST

R205

75RST

7

CPUCLK

CPUCLK#

DEFER#

HLOCK#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HASTB#1

HASTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

B21

HD#63

C207

X_103p

HNCVREF

C215

103p

C1XAVSS

C1XAVDD

C4XAVSS

C4XAVDD

AH25

AJ25

AH27

AJ27

C1XAVSS

C1XAVDD

C4XAVSS

HOST

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

F19

A21

E19

D22

D20

B22

C22

B23

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

C1XAVDD

C1XAVSS

HVREF

U21

T21

HVREF0

C4XAVDD

HD#55

HD#54

HD#53

A23

D21

F22

HD#54

HD#53

HD#52

6

VAD[0..11]

VBD[0..11]

HPCOMP

HNCOMP

HNCVREF

VBD7

VBD6

VBD5

VBD4

P21

N21

J17

B20

B19

A19A7F9B7M6M5M4L3L6L4K6L2K3J3K4J2J6J4J1H6F4F1G6E3F5E2E4E1D3D4C2F7C3E6B2D5D6A3D7C5A5C6D8

ST0

ST1

ST2

AAD0

AAD1

HVREF1

HVREF2

HVREF3

HVREF4

HPCOMP

HNCOMP

HNCOMPVREF

AAD2

VBD3

AAD3

VBD2

AAD4

VBD1

AAD5

AAD6

VBD0

VAD6

AAD7

5

VAD[0..11] 17

VBD[0..11] 17

VAD5

VAD4

VAD7

AAD8

AAD9

AAD10

VAD8

AAD11

AAD12

VAD9

AAD13

VAD10

VAD11

AAD14

AAD15

AAD16

AAD17

AAD16

AAD17

AAD18

VBD11

AAD18

AAD19

VBD10

VBD8

AAD20

VBD9

AAD21

AAD22

VAD1

AAD23

VAD0

VAD2

AAD24

AAD25

650-1

HD#52

HD#51

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

HD#24

HD#23

HD#22

HD#21

HD#20

HD#19

HD#18

HD#17

HD#16

HD#15

D24

D23

C24

B24

E25

E23

D25

A25

C26

B26

B27

D26

B28

E26

F28

G25

F27

F26

G24

H24

G29

J26

G26

J25

H26

G28

H28

J24

K28

J29

K27

J28

M24

L26

K26

L25

L28

HD#51

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

HD#24

HD#23

HD#22

HD#21

HD#20

HD#19

HD#18

HD#17

HD#16

HD#15

CP54

1 2

X_COPPER

L69

X_80-0603

C362

103p

CP52

1 2

X_COPPER

6

VCC3

C4XAVDDHVREF

C376

X_1u

C4XAVSS

5

CP55

1 2

X_COPPER

L70

X_80-0603

C363

103p

CP53

1 2 CP32

X_COPPER

4

VAD3

AAD26

AAD27

AAD28

AAD29

AGP

HD#14

HD#13

HD#12

HD#11

M26

P26

L29

N24

N26

HD#14

HD#13

HD#12

HD#11

HD#10

4

AAD30

AAD31

HD#10

HD#9

M27

N28

HD#9

HD#8

VCC3

VBBLANK

VBCTL0

VBCTL1

VBHSYNC

VBVSYNC

SBA7

SBA6

HD#8

HD#7

HD#6

P27

N29

R24

HD#7

HD#6

HD#5

SBA5

SBA4

HD#5

HD#4

R28

M28

HD#4

HD#3

A4XAVDD

A4XAVSS

SBA3

HD#3

P28

HD#2

SBA2

HD#2

R26

HD#1

C7

SBA1

HD#1

R29

HD#0

VBBLANK 17

VBCTL017

VBCTL117

VBHSYNC 17

VBVSYNC 17

VBCLK

AC/BE#3

SBA0

AC/BE#2

AC/BE#1

AC/BE#0

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

AGP8XDET

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

HD#0

DBI#3

DBI#2

E21

A27

H27

HDBI#3

HDBI#2

HDBI#1

C227

104p

AREQ#

AGNT#

APAR

RBF#

WBF#

PIPE#

ADBIH

ADBIL

DBI#1

DBI#0

R25

HDBI#0

C223

103p

3

VBCLK 17

U18A

F6

F3

H4

K5

C9

A6

G2

G1

G3

G4

H5

H1

H3

E8

F8

D9

D10

B3

C4

B5

A4

K1

L1

C1

D1

B10

M1

B9

A9

B8

A8

M3

M2

F20

F23

K24

P24

F21

F24

L24

N25

SIS650GX

CP30

1 2

X_COPPER

L42

X_80-0603

1 2

X_COPPER

3

ADSTB#0

VGCLK

ADSTB#1

AGPCLK0

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

R257 8.2K

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

HDBI#[0..3] 5

2

U18-1

N.B HEAT SINK

VBCAD 17

AAD16

AAD17

2

A1XAVDD

A1XAVSS

AAD18

ADSTB0

ADSTB#0ADSTB0

ADSTB#1

RN45 X_8.2K

R243 8.2K

R234 8.2K

C224

104p

X_COPPER

C228

103p

X_COPPER

VBHCLK 17

VGCLK 17

AGPCLK0 3

R249 62

VCC3

C218

X_1u

HDSTBN#3 5

HDSTBN#2 5

HDSTBN#1 5

HDSTBN#0 5

HDSTBP#3 5

HDSTBP#2 5

HDSTBP#1 5

HDSTBP#0 5

VCC3

MICRO-STAR INT'L CO.,LTD.

Title

SIS645/650-1

Size Document Number Rev

MS-6535 1.0C

Custom

Date: Sheet of

CP29

1 2

L43

X_80-0603

1 2

CP33

1

VDDQ

12

34

56

78

VCC3

C217

X_1u

7 41Friday, September 13, 2002

1

8

7

6

5

4

3

2

1

RMA11

RMA12

RMA0

L = 1.2"

S3AUXSW# 37

SDCLK 3

FWDSDCLKO 4

RMD[0..63]

RDQM[0..7]

RDQS[0..7]

RMA[0..14]

RCS-[0..3]

CKE[0..3]

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

SDAVDD

SDAVSS

C336

104p

RMD[0..63] 11,12

RDQM[0..7] 11,12

RDQS[0..7] 11,12

RMA[0..14] 11,12

RCS-[0..3] 11,12

C329

104p

C335

X_103p

CKE[0..3] 11

VCCM

C357

X_103p

C377

103p

VCCM

C353

X_103p

C374

103p

1 2

X_COPPER

X_80-0603

C330

X_103p

1 2

X_COPPER

CP50

1 2

X_COPPER

L64

X_80-0603

CP49

1 2

X_COPPER

L62

CP48

CP47

R309

150RST

R322

150RST

R308

150RST

R321

150RST

VCC3

VCC3

C403

X_1u

MA7

MA8

MA5

MA6

RN64

RN66

MA14

MA13

D D

The L of RN to DDR1 is 0.4"

Rs place close to DDR1

RMD1 MD1 MD0

RMD5 MD5 MD1

RMD0 MD0 MD2

RMD4 MD4 MD3

RMD6 MD6 MD4

RMD2 MD2 MD5

RDQM0 DQM0 MD6

RDQS0 DQS0 MD7

RMD9 MD9 DQM0

RMD8 MD8 DQS0

RMD7 MD7 MD8

RMD3 MD3 MD9

RMD11 MD11 MD10

RMD10 MD10 MD11

RMD15 MD15 MD12

RMD14 MD14 MD13

RDQM1 DQM1 MD14 MA7

RMD13 MD13 MD15 MA8

RDQS1 DQS1 DQM1 MA9

RMD12 MD12 DQS1

RMD21 MD21 MD16

C C

B B

A A

RMD17 MD17 MD17

RMD16 MD16 MD18

RMD20 MD20 MD19

RMD22 MD22 MD20

RMD18 MD18 MD21

RDQM2

RMA9 MD23

RMD28 MD28 DQM2

RMD24 MD24 DQS2

RMD19

RMD23

RMD31

RMD27 MD27 MD27

RMD30 MD30 MD28

RMD26 MD26 MD29

RDQM3 DQM3 MD30

RDQS3 DQS3 MD31

RMD25 MD25 DQM3

RMD29 MD29 DQS3

RMD33 MD33 MD32 CKE0

RMD37 MD37 MD33 CKE1

RMD36 MD36 MD34 CKE2

RMD32 MD32 MD35 CKE3

RMD38 MD38 MD36

RMD34 MD34 MD37

RDQM4 DQM4 MD38

RDQS4 DQS4 MD39

RMD40

RMD35 MD35 MD40 SDCLK

RMD39 MD39 MD41

RDQS5 DQS5 MD42

RDQM5 DQM5 MD43

RMD41 MD41 MD44

RMD45 MD45 MD45

RMD47 MD47 MD46

RMD43 MD43

RMD42 MD42 DQS5

RMD55 MD55 MD48 SDAVSS

RDQS6 DQS6 MD49

RMD54 MD54 MD50

RDQM6 DQM6 MD51 DDRAVDD

RMD53 MD53 MD52

RMD52 MD52 MD53 DDRAVSS

RMD49 MD49

RMD48 MD48 MD55

RMD56 MD56 DQM6

RMD60 MD60 DQS6 DDRVREFA

RMD51 MD51 MD56 DDRVREFB

RMD50 MD50 MD57

RMD62 MD62

RDQM7 DQM7 MD59

RMD57 MD57

RMD61 MD61 MD61

RMD63 MD63

RMD58 MD58

RDQS7 DQS7

RN73101 2

3 4

5 6

7 8

RN72101 2

3 4

5 6

7 8

RN71101 2

3 4

5 6

7 8

RN69101 2

3 4

5 6

7 8

RN70101 2

3 4

5 6

7 8

RN67101 2

3 4

5 6

7 8

RN65101 2

3 4

5 6

7 8

RN63101 2

3 4

5 6

7 8

RN61101 2

3 4

5 6

7 8

RN62101 2

3 4

5 6

7 8

RN58101 2

3 4

5 6

7 8

RN57101 2

3 4

5 6

7 8

RN56101 2

3 4

5 6

7 8

RN53101 2

3 4

5 6

7 8

RN52101 2

3 4

5 6

7 8

RN50101 2

3 4

5 6

7 8

RN51101 2

3 4

5 6

7 8

RN49101 2

3 4

5 6

7 8

RN48101 2

3 4

5 6

7 8

1 2

3 4

RN47

5 6

10

7 8

DQM2

MA9

MD19

MD23

MD31 MD26

MD40 DQS4

L = 2"~4"

U18B

AJ23

MD0

AG22

MD1

AH21

MD2

AJ21

MD3

AD23

MD4

AE23

MD5

AF22

MD6

AF21

MD7

AD22

DQM0

AH22

DQS0/CSB#0

AD21

MD8

AG20

MD9

AE19

MD10

AF19

MD11

AE21

MD12

AD20

MD13

AD19

MD14

AH19

MD15

AF20

DQM1

AH20

DQS1/CSB#1

AF18

MD16

AG18

MD17

AH17

MD18

AD16

MD19

AD18

MD20

AD17

AF17

AJ17

AE17

AH18

AD14

AG14

AJ13

AE13

AJ15

AF14

AD13

AF13

AH13

AH14

AD10

AH10

AE9

AD8

AG10

AF10

AH9

AF9

AD9

AJ9

AH5

AG4

AE5

AH3

AG6

AF6

AF5

AF4

AH4

AJ3

AE4

AD6

AE2

AC5

AG2

AG1

AF3

AC6

AD4

AF2

AB6

AD3

AA6

AB3

AC4

AE1

AD2

AC1

AB4

AC2

MD21

MD22

MD23

DQM2

DQS2/CSB#2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB#3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB#4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB#5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB#6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB#7

650-2

MD22

MD24

MD25

DQM4

MD47RMD46 MD46

DQM5 SDAVDD

MD54

MD58

MD60

MD62RMD59 MD59

MD63

DQM7

DQS7

DQS2

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CS#0

CS#1

CS#2

CS#3

CS#4

CS#5

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

SDCLK

FWDSDCLKO

SDRCLKI

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DRAM_SEL

MA0

AH11

MA1

AF12

MA2

AH12

MA3

AG12

MA4

AD12

MA5

AH15

MA6

AF15

AH16

AE15

AD15

MA10

AF11

MA11

AG8

MA12

AJ11

MA13 RMA10

AG16

MA14

AF16

SRAS#

AH8

SCAS#

AJ7

SWE#

AH7

MD44

L = 1" ~ 3"

CS-0

AE7

CS-1

AF7

CS-2

AH6

CS-3

AJ5

AF8

AD7

AB2

AA4

AB1

Y6

AA5

Y5

Y4

AA3

R311 22

AD11

AE11

Y1

Y2

AA1

AA2

AJ19

AH2

R282 4.7K

W3

RMA7

78

RMA8

56

RMA5

34

RMA6

12

0

78

RMA14

56

RMA13

34

RDQS2

12

0

Rs place close to DDR1

L = 1"~ 3" L = 0.4" from RN to DDR1

RN60

RMA2

12

RMA3

34

RMA1

56

RMA4

78

0

RN59

12

34

56

78

0

R411 0

R412 0

R413 0

RSCAS#

RSWE#

RMD44

78

56

34

12

RSCAS# 11,12

RSWE# 11,12

RCS-0

RCS-2

RCS-1

RCS-3

RN54 0

S3AUXSW#

R286 4.7K

VCC3SBY

FWDSDCLKO

C364

X_10p

Near SIS650

VCC3SBY

SIS650GX

RSRAS#

RSRAS#11,12

8

R427 0

SRAS#

7

6

5

4

3

MICRO-STAR INT'L CO.,LTD.

Title

650GX-2

Size Document Number Rev

MS-6535 1.0C

Custom

Date: Sheet of

2

8 41Friday, September 13, 2002

1

8

7

6

5

4

3

2

1

NOTE: This page is for universal PCB design( suitable for both 645 or 650)

NB Hardware Trap Table

0

0

0

1

0

DLLEN#

E11

F10

ENTEST

ENTEST

embedded pull-low

(30~50K Ohm)

yes

yes

yes

C15

VOSCI

A12

ROUT

B13

GOUT

A13

BOUT

F13

HSYNC

E13

VSYNC

D13

VGPIO0

D12

VGPIO1

B11

INT#A

E12

CSYNC

A11

RSYNC

F12

LSYNC

E14

VCOMP

D14

VRSET

F14

VVBWN

B12

DACAVDD1

C12

DACAVSS1

C13

DACAVDD2

C14

DACAVSS2

B15

DCLKAVDD

A15

DCLKAVSS

B14

ECLKAVDD

A14

ECLKAVSS

R218

R219 0

R220

R210 33

R211 33

R213 100

R212 100

DCLKAVDD

DCLKAVSS

BOUT

W = 5mil

REFCLK0 3

ROUT 33

GOUT 33

BOUT 33

HSYNC 33

VSYNC 33

DDC1CLK 33

DDC1DATA 33

REFCLK0

0

0

VSYNC RSYNC

DDC1DATA

INTA# 13,17,19

DACAVDD1/2

DCLKAVDD

ECLKAVDD

CP26

C212

104p

1 2

X_COPPER

L38

CP28

1 2

X_COPPER

X_80-0603

X_80-0603

VCC3

C506

X_1u

L41

for 650 only

PWRGDVDDZCMP

VCC3

R214 4.7K

R215 4.7K

R206 4.7K

R207 4.7K

R209 4.7K

C320 X_104p

TRAP1

D11

TRAP1

TRAP0

E10

Default

1(DDR)

TESTMODE2

TESTMODE1

TESTMODE0

A10

F11

C11

DLLEN#

DRAM_SEL

TRAP0

D D

ZAD[0..15]13

ZSTB[0..1]13

ZSTB-[0..1]13

C C

ZAD[0..15]

ZSTB[0..1]

ZSTB-[0..1]

VCC1_8

C298

R277

X_104p

150RST

ZVREF

C289

R276

104p

150RST

TRAP1

CSYNC

RSYNC

LSYNC

ZCLK0

ZCLK03

ZUREQ

ZUREQ13

ZDREQ

ZDREQ13

ZSTB0 ROUT

ZSTB-0 GOUT

ZSTB1

ZSTB-1 HSYNC

ZAD0

ZAD1 DDC1CLK TRAP1

ZAD2

ZAD3 CSYNC

ZAD4

ZAD5 INTA# LSYNC

ZAD6

ZAD7

ZAD8 CSYNC

ZAD9 RSYNC

ZAD10 LSYNC

ZAD11

ZAD12

ZAD13 VCOMP

ZAD14 VRSET

ZAD15 VVBWN ENT EST

ZVREF

ZCMP_N

ZCMP_P DACAVSS1/2

VSSZCMP

Z1XAVDD DCLKAVSS

Z1XAVSS

Z4XAVDD ECLKAVSS

Z4XAVSS

0

enable PLL disable PLL

SDR DDR

normal NB debug mode

TV selection, NTSC/PAL(0/1) 0

enable VB

enable VGA interface

enable panel link

U18C

SIS650GX

V3

ZCLK

U6

ZUREQ

U1

ZDREQ

T3

ZSTB0

T1

ZSTB#0

P1

ZSTB1

P3

ZSTB#1

T4

ZAD0

R3

ZAD1

T5

ZAD2

T6

ZAD3

R2

ZAD4

R6

ZAD5

R1

ZAD6

R4

ZAD7

P4

ZAD8

N3

ZAD9

P5

ZAD10

P6

ZAD11

N1

ZAD12

N6

ZAD13

N2

ZAD14

N4

ZAD15

U3

ZVREF

V5

VDDZCMP

U4

ZCMP_N

U2

ZCMP_P

V6

VSSZCMP

W1

Z1XAVDD

W2

Z1XAVSS

V2

Z4XAVDD

V1

Z4XAVSS

1

VGA

Stereo

Glass

HyperZip

650-3

PCIRST#

PWROK

AUXOK

Y3W4W6

B B

CP43

C331

X_1u

1 2

X_COPPER

L57

X_80-0603

CP44

1 2

C305

104p

Z1XAVDD

Z1XAVSS

VCC3

PCIRST#117,27,37

PCIRST#1

PWRGD14,37

PWRGD

AUXOK

AUXOK14,37

X_COPPER

C220

CP31

1 2 CP24

X_COPPER

L39 X_80-0603

CP27

1 2

X_COPPER

104p

L40 X_80-0603

C278

X_1u

CP36

1 2

X_COPPER

L52

X_80-0603

CP37

1 2

X_COPPER

C273

104p

R266 56

R271 56

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

ECLKAVDD

C219

ECLKAVSS

CP41

VCC3

A A

X_COPPER

L55

X_80-0603

CP40

1 2

104p

Z4XAVDD

C299

Z4XAVSS

1 2

VCC1_8

X_COPPER

VVBWN VRSET

VCOMP

VCC3

DACAVDD1/2

DACAVSS1/2

104p

C221

104p

C222

C216

104p

1u

Near B12 pin Near C13 pin

1 2

X_COPPER

L36

X_80-0603

CP25

1 2

X_COPPER

L37 X_80-0603

VCC1_8

C263

X_1u

R203

130RST

MICRO-STAR INT'L CO.,LTD.

Title

SIS645/650

Size Document Number Rev

MS-6535 1.0C

Custom

8

7

6

5

4

3

Date: Sheet of

2

9 41Friday, September 13, 2002

1

8

7

6

5

4

3

2

1

VCCP VCC1_8 VCC3

H21

H22

J16

J20

J21

J22

K16

K17

K18

K19

K20

K21

L20

M20

N20

P20

R20

R21

T20

U20

V20

W20

Y20

Y21

AA20

AA21

AA22

AB21

AB22

L12

L14

L15

L16

L18

M11

M19

N11

P19

R11

T19

U11

V19

W11

W13

W15

W17

P11

IVDD

VSS

U17

IVDD

VSS

U18

IVDD

VSS

V12

IVDD

VSS

V13

VSS

V14

J14

PVDDZ

VSS

VSS

V15

V16

5

VCCP

A16

VTT

A17

A18

D D

VCCM

C C

VDDQ

B B

VCC1_8

A A

B16

B17

B18

C16

C17

C18

D15

D16

D17

D18

E15

E16

E17

E18

F15

F16

F17

F18

AB5

AD5

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE22

V10

V11

W18

Y10

Y12

Y14

Y16

Y18

Y19

AA8

AA9

AA10

AA13

AA14

AA15

AA16

AA17

AB8

AB9

AB13

AB17

J10

J13

K11

K13

L10

N10

W5

P10

R10

T10

T11

8

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

650-4

VSS

VSS

VSS

VSS

VSS

VSS

P16

P17

P18

R12

R13

R14

VTT

IVDD

IVDD

Power

VSS

VSS

VSS

VSS

R15

R16

R17

R18

6

T12

IVDD

VSS

T13

IVDD

VSS

T14

IVDD

VSS

T15

IVDD

VSS

T16

IVDD

VSS

T17

IVDD

VSS

T18

IVDD

VSS

U12

IVDD

VSS

U13

IVDD

VSS

U14

IVDD

VSS

U15

IVDD

VSS

U16

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

Y9

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

E5

VDDQ

E7

VDDQ

E9

VDDQ

G5

VDDQ

J5

VDDQ

L5

VDDQ

H8

VDDQ

H9

VDDQ

J8

VDDQ

J9

VDDQ

VDDQ

VDDQ

K9

VDDQ

VDDQ

VDDQ

VDDQ

N9

VDDQ

VDDQ

N5

VDDZ

R5

VDDZ

U5

VDDZ

VDDZ

P9

VDDZ

VDDZ

R9

VDDZ

VDDZ

T9

VDDZ

VDDZ

VDDZ

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L17

L19

N19

R19

U19

W19

M12

M13

M14

M15

M16

M17

M18

N12

N13

N14

N15

N16

N17

N18

P12

P13

P14

P15

VCC1_8

7

J15

OVDD

VSS

V17

K15

OVDD

OVDD

VSS

VSS

V18

K10

K12

PVDD

B25

K14

PVDD

VSS

C28

VCC3SBY

M10

PVDD

PVDD

VSS

VSS

C29

D27

W10

VSS

D28

Y11

Y13

PVDDM

PVDDM

VSS

VSS

E28

E29

Y15

Y17

PVDDM

PVDDM

VSS

VSS

AF23

AF24

AUX1.8

AUX3.3

PVDDM

VSS

VSS

AF25

AG24

VSS

AG26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH23

VSS

VSS

AH24

U18D

U10

U9

A20

A22

A24

A26

C19

C21

C23

C25

C27

E20

E22

E24

F25

H25

K25

M25

P25

T25

V25

Y25

AB25

AD25

E27

G27

J27

L27

N27

R27

U27

W27

AA27

AC27

AE27

D29

F29

H29

K29

M29

P29

T29

V29

Y29

AB29

AD29

AF29

AE24

AG25

B4

B6

C8

C10

D2

F2

H2

K2

P2

T2

V4

AD1

AF1

AC3

AE3

AG3

AG5

AG7

AG9

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AJ4

AJ6

AJ8

AJ10

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

AJ24

AG27

SIS650GX

4

VCC3SBY

VCC1_8SBY

VCC3SBY

VCCP

C286

1u

C209

1u

C358

1u

VDDQ

C231

104p

C232

104p

Place these capacitors under 650 solder

side, DO NOT stuff

C524

X_104p

C520

X_104p

C516

X_104p

C521

X_104p

VCC1_8

3

VCCP

C226

104p

C233

104p

C522

X_1u-0805

C517

X_1u-0805

C518

X_1u-0805

C519

X_1u-0805

VCCM

VCC3

C326

1u

C322

1u

C368

104p

C395

104p

C213

104p

C347

104p

C208

104p

C359

X_10u-0805

C361

X_10u-0805

VCCM

C528

X_104p

C529

X_104p

C527

X_104p

C526

X_104p

MICRO-STAR INT'L CO.,LTD.

Title

SIS645/650-4

Size Document Number Rev

MS-6535 1.0C

Custom

Date: Sheet of

C337

104p

C225

104p

VCC1_8SBY

C265

1u

C267

104p

C356

C355

104p

C375

104p

VCC3

C512

X_104p

C515

X_104p

2

VCC3SBY

VDDQ

10 41Friday, September 13, 2002

C523

X_104p

C525

X_104p

C511

X_104p

C513

X_104p

1

1u

C354

104p

8

7

6

5

4

3

2

1

RMD[0..63]8,12

RMA[0..14]8,12

RDQM[0..7]8,12

RDQS[0..7]8,12

D D

NOTE:

VDDID IS A TRAP ON THE DDR

MODULE TO INDICATE:

VDDID

OPEN

GND

MEMORY MUX TABLE:

SDR

CS0

CS1

CS2

CS3

CS4

CS5 CS5

CSB0

CSB1

CSB2

CSB3

CSB4

CSB5

C C

CSB6

CSB7

DDRVREF GEN. & DECOUPLING

VCCM

R393

75RST

R392

75RST

B B

A A

RMA[0..14] RMA[0..14]

RDQM[0..7] RDQM[0..7]

VCCM

RDQS[0..7] RDQS[0..7]

DDR1

VDDQ

VSS

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

VDDID

VSS

VSS

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

WP

SCL

SDA

SA0

SA1

SA2

VSS

15223054627796

VDDQ

VSS

3111826344250586674818993

VDDQ

RMD0

2

RMD1

4

RMD2

6

RMD3

8

RMD4

94

RMD5

95

RMD6

98

RMD7

99

RMD8

12

RMD9

13

RMD10

19

RMD11

20

RMD12

105

RMD13

106

RMD14

109

RMD15

110

RMD16

23

RMD17

24

RMD18

28

RMD19

31

RMD20

114

RMD21

117

RMD22

121

RMD23

123

RMD24

33

RMD25

35

RMD26

39

RMD27

40

RMD28

126

RMD29

127

RMD30

131

RMD31

133

RMD32

53

RMD33

55

RMD34

57

RMD35

60

RMD36

146

RMD37

147

RMD38

150

RMD39

151

RMD40

61

RMD41

64

RMD42

68

RMD43

69

RMD44

153

RMD45

155

RMD46

161

RMD47

162

RMD48

72

RMD49

73

RMD50

79

RMD51

80

RMD52

165

RMD53

166

RMD54

170

RMD55

171

RMD56

83

RMD57

84

RMD58

87

RMD59

88

RMD60

174

RMD61

175

RMD62

178

RMD63

179

DDRVREF DDRVREF

1

82

90

92

SMBDAT

91

181

182

183

VSS

DDR SDRAM DIMM

5

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

124

132

139

145

152

160

120

VDD

148

VDD

168

VDD

184

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

97

107

119

129

149

159

169

177

140

5

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

9

10

101

102

173

167

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

176

REQUIRED POWER

VDD=VDDQ

VDD!=VDDQ

DDR

CS0

CS1

CS2

CS3

CS4

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

VCCM VCCM

R371 X_8.2K R370 X_8.2K

C472

X_103p

RMA0 RMD4

RMA1 RMD5

RMA2 RMD6

RMA3 RMD7

RMA4 RMD8

RMA5 RMD9

RMA6 RMD10

RMA7 RMD11

RMA8 RMD12

RMA9 RMD13

RMA10 RMD14

RMA13 RMD15

RMA14 RMD16

RMA11 RMA11 RMD19

RMA12 RMA12 RMD20

RDQM0 RMD23

RDQM1 RMD24

RDQM2 RMD25

RDQM3 RMD26

RDQM4 RMD27

RDQM5 RMD28

RDQM6 RMD29

RDQM7 RMD30

RDQS0 RMD33

RDQS1 RMD34

RDQS2 RMD35

RDQS3 RMD36

RDQS4 RMD37

RDQS5 RMD38

RDQS6 RMD39

RDQS7 RMD40

DDRVREF

C473

C448

103p

103p

RSRAS# RSRAS# RMD59

RSRAS#8,12

RSCAS# RSCAS# RMD60

RSCAS#8,12

RSWE# RSWE# RMD61

RSWE#8,12

RCS-0 RCS-2 RMD63

RCS-1 RCS-3

CKE0 WP CKE2

CKE1 SMBCLK CKE3

DDRCLK1

DDRCLK8

DDRCLK2

DDRCLK-1

DDRCLK-8

DDRCLK-2

RCS-[0..3]8,12

DDRCLK[0..8]4

DDRCLK-[0..8]4

8

RCS-[0..3]

CKE[0..3]

CKE[0..3]8

DDRCLK[0..8]

DDRCLK-[0..8]

7

116

VDDQ

VSS

100

6

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

addr =

1010000b

VSS

VSS

VDDQ

VSS

VDDQ

VSS

RMD[0..63]

CKE2

CKE0

CKE3

CKE1

470

4

DDRCLK0

DDRCLK7

DDRCLK3

DDRCLK-0

DDRCLK-7

DDRCLK-3

RN68

1 2

3 4

5 6

7 8

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA13

RMA14

VCCM

VCCM

120

148

168

184

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

97

107

119

129

149

159

169

177

140

5

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

9

10

101

102

173

167

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

VSS

VSS

VSS

VSS

145

152

160

176

3

DDR2

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

SCL

SDA

SA0

SA1

SA2

VSS

VSS

VDDQ

WP

VSS

15223054627796

VDDQ

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

1

82

90

92

91

181

182

183

VSS

DDR SDRAM DIMM

3111826344250586674818993

RMD0

RMD1

RMD2

RMD3

RMD17

RMD18

RMD21

RMD22

RMD31

RMD32

RMD41

RMD42

RMD43

RMD44

RMD45

RMD46

RMD47

RMD48

RMD49

RMD50

RMD51

RMD52

RMD53

RMD54

RMD55

RMD56

RMD57

RMD58

RMD62

R369 4.7K

WP

SMBCLK

SMBDAT

DDR DECOUPLING,

STUFF 2, THE OTHER

RESERVED

VCCM

C441

104p

C442

104p

C440

X_104p

C444

X_104p

C445

X_104p

C446

X_104p

C449

X_104p

C447

X_104p

C443

X_104p

VCCM

SMBCLK 3,4,14,37

SMBDAT 3,4,14,37

VCCM

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

addr =

1010001b

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

116

124

132

139

MICRO-STAR INT'L CO.,LTD.

Title

DDR1 & DDR2

Size Document Number Rev

MS-6535 1.0C

Custom

Date: Sheet of

2

11 41Friday, September 13, 2002

1

SSTL-2 Termination Resistors

RMD[0..63]

RDQM[0..7]

RDQS[0..7]

RMA[0..14]

RCS-[0..3]

L = 0.4"

RMD1

RMD5

RMD0

RMD4

RMD6

RMD2

RDQM0

RDQS0

RMD9

RMD8

RMD7

RMD3

RDQM1

RMD13

RDQS1 RMD47

RMD12 RMD46

RMD11

RMD10

RMD14

RMA9

RMA13

RDQS2

RMD21

RMD17

RMA14

RMD16

RMD20

RMD19

RMD23

RMA5

RMA8

RMD27

RMD30

RMD26

RMA3

RDQM3

RMA4

RDQS3

RMD29

RMA7

RMD22

RMD18

RDQM2

RMD25

RMD28

RMA6

RMD24

RMA0

RMA1

RMA2

RMD31

RMD39

RMA11

RMD38

RMD34

RN88 47

RN87 47

RN86 47

RN85 47

RN84 47

RN82 47

RN83 47

RN80 47

RN77 47

RN78 47

RN81 47

RN79 47

RN76 47

RN99 47

RMD[0..63] 8,11

RDQM[0..7] 8,11

RDQS[0..7] 8,11

RMA[0..14] 8,11

RCS-[0..3] 8,11

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

MD/DQM(/DQS)

MA/Control

CS

CKE

RMD36

RMD32

RMA12

RMA10

RDQM4

RDQS4

RMD33

RMD37

RSRAS#

RSRAS#8,11

RMD44

RMD40

RMD35

RMD43

RMD42

RCS-3RMD15

RCS-2

RCS-0

RMD53

RMD52

RMD49

RMD48

RMD55

RDQS6

RMD54

RDQM6

RMD59

RMD63

RMD58

RDQS7

RMD56

RMD60

RMD51

RMD50

RMD62

RDQM7

RMD57

RMD61

RDQS5

RDQM5

RCS-1

RSCAS#

RSCAS#8,11

RMD41

RMD45

RSWE#

RSWE#8,11

L = 0.4" except RSC0~3 ( L=1.2" )

SDR

LV-CMOS

LV-CMOS

LV-CMOS

OD 3.3V OD 2.5V

RN101 47

RN100 47

RN98 47

RN94 47

RN96 47

RN93 47

RN92 47

RN89 47

RN91 47

RN90 47

RN95 47

RN97 47

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

DDR

Rs

SSTL-2

0/10/- 47

SSTL-2

10

SSTL-2

0

DDR_VTT

DDR_VTT

Rs

Rtt

10

0

47

0

47

DDR_VTT

DDR_VTT