5

MS-56111-0B

SHEET01:

SHEET02:

SHEET03:

D D

SHEET04:

SHEET05:

SHEET06:

SHEET07:

SHEET08:

SHEET09:

SHEET10:

SHEET11:

SHEET12:

SHEET13:

REVISION HISTORY:

C C

REV 0A : 12/8/2006 release

REV 0A-0302 : 3/2/2007 release

B B

REV 0A-0305 : 3/5/2007 release

REV 0A-0307 : 3/7/2007 release

REV 0A-0313 : 3/13/2007 release

A A

INDEX (This page)

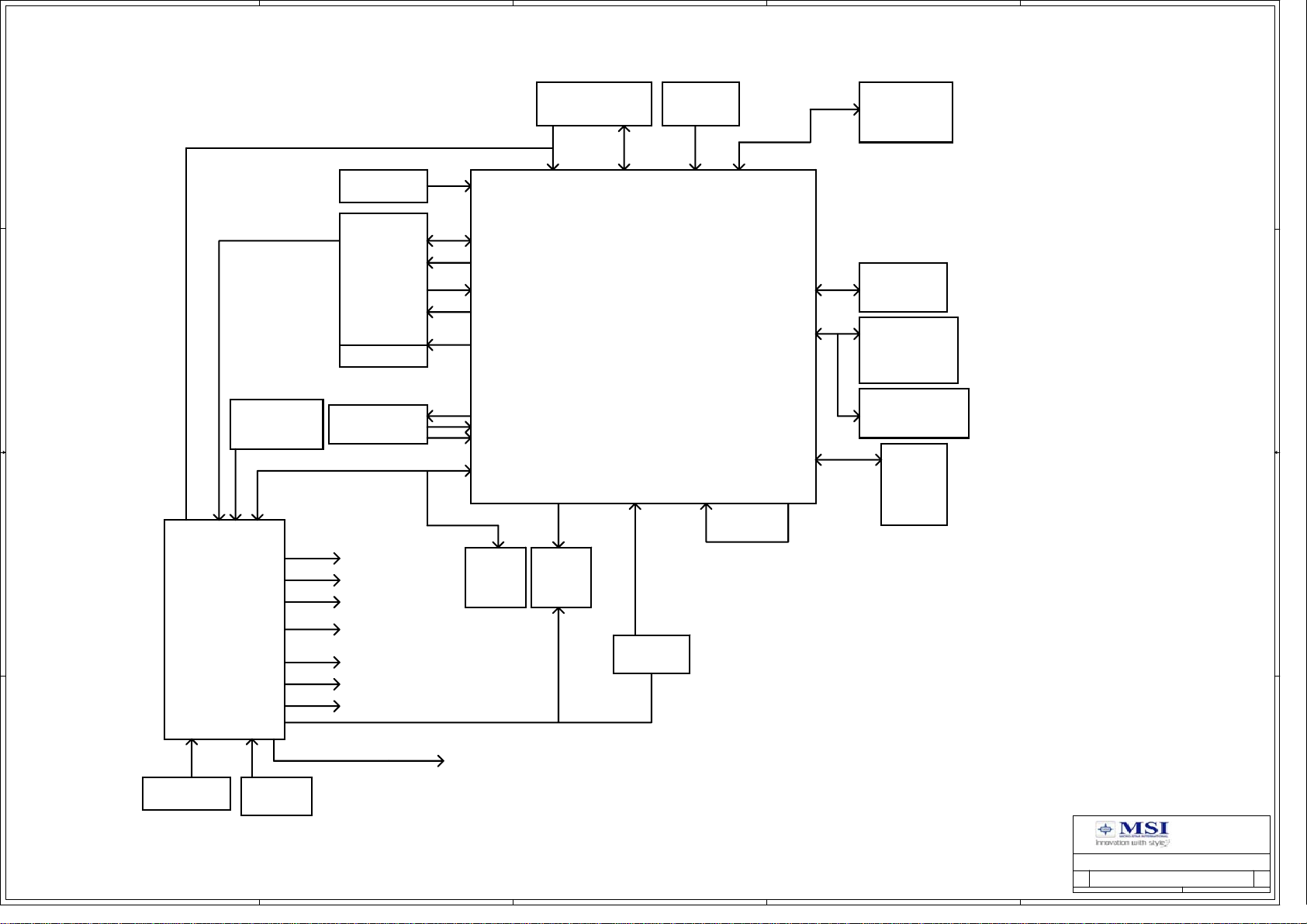

BLOCK DIAGRAM

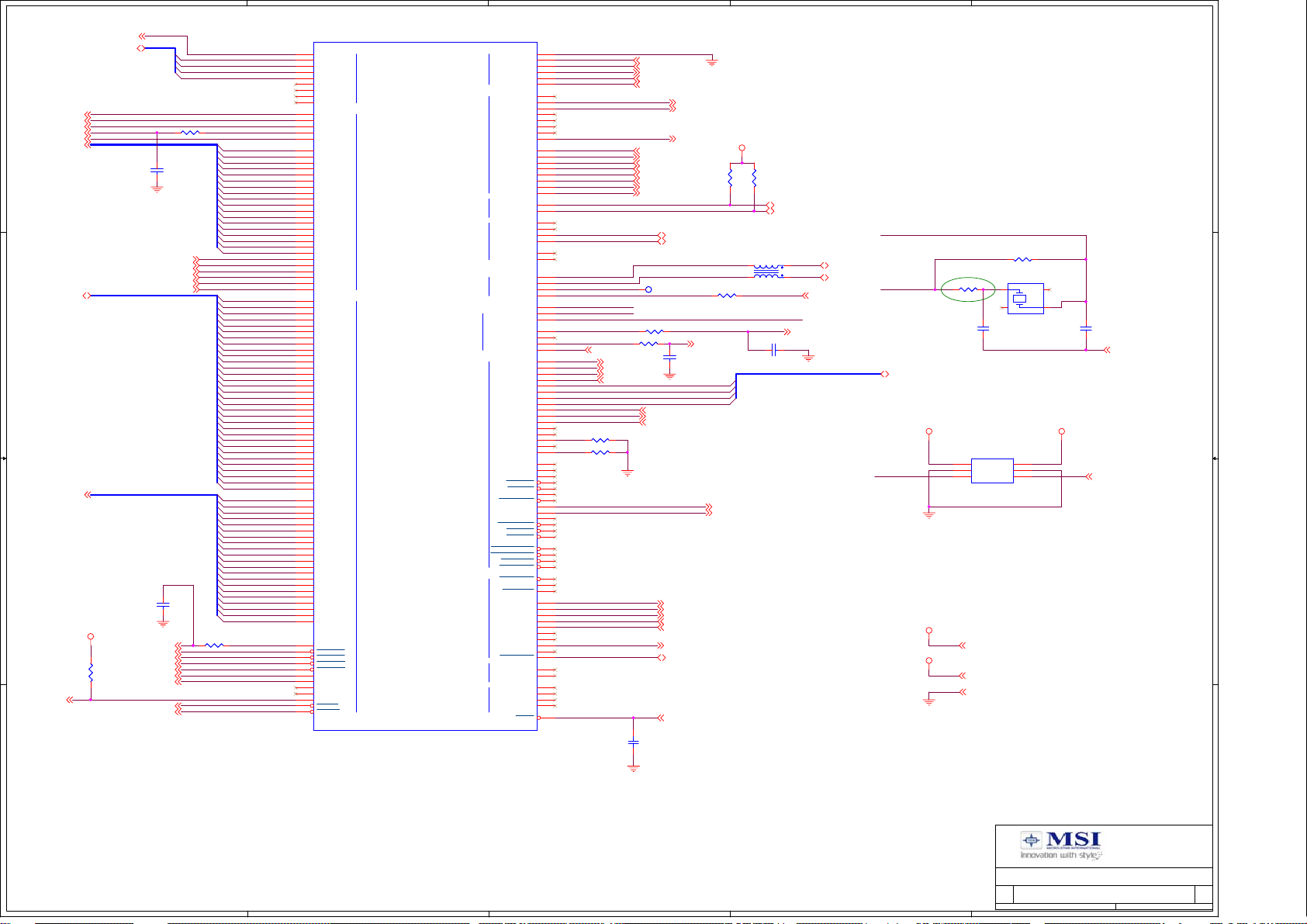

AP10_1 PROCESSOR

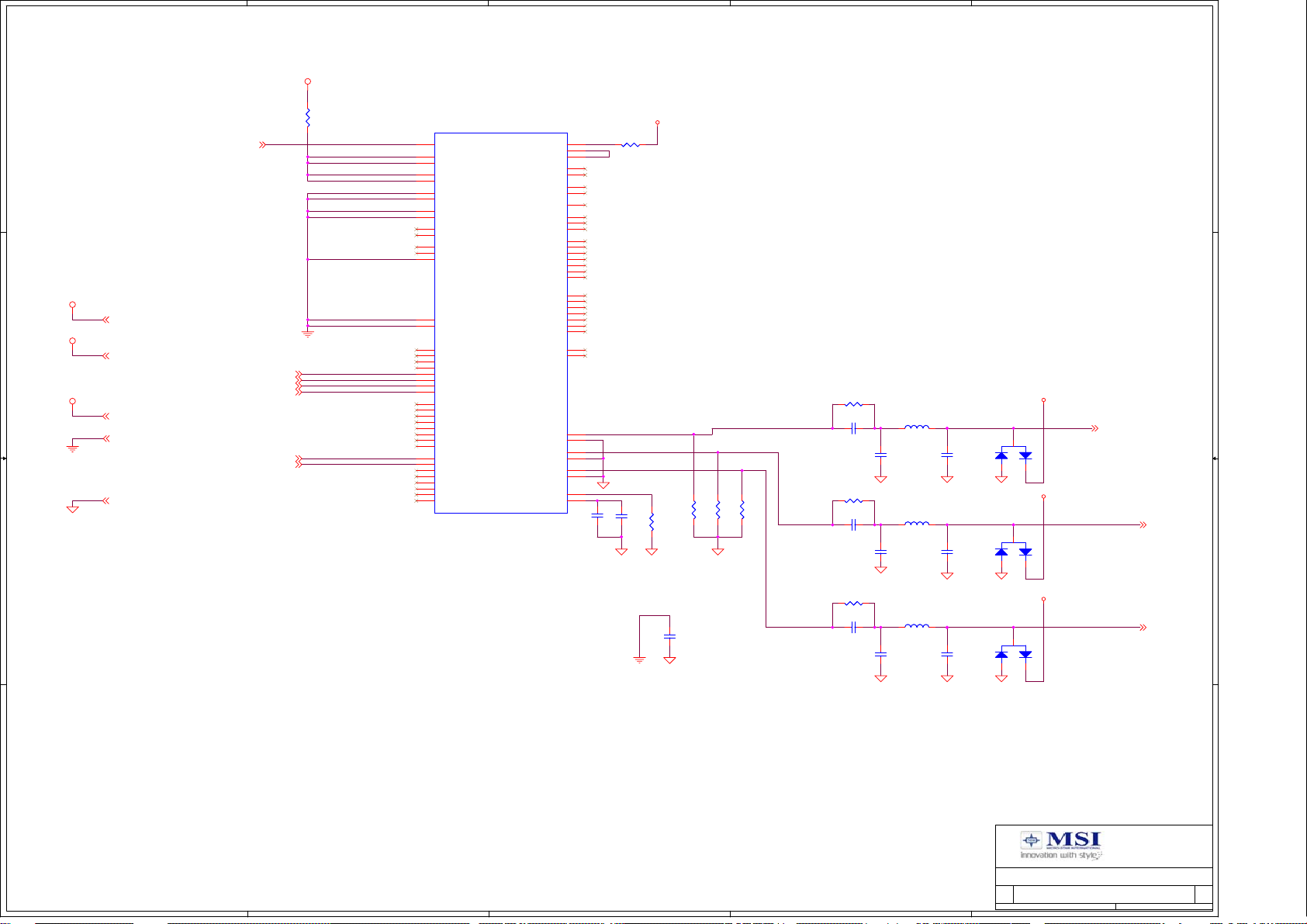

AP10_2 WiFi & Video & GPIO

AP10_3 POWER

AP10_4 AUDIO

FM tuner

Memory (SDRAM/Harp/EEPROM)

LCD and switch

Docking

AS3517

Micro-SD and JTAG

BOOTSTRAP

Page-3 BMM3_CMD / MM3_CMD change pin

Add SM3_CS2#, SM3_CS3#

Page-4 WLAN_AFE termination, 9.6MHz Osc. R28-33R,

C11-0.1uF

Page-5 R43 connect to VCC_3V3

Page-6 U1.E18~E20, B20~B21 floating

VDL,VDR connect to VCC_3V0

Add R69~R71

D1,D2,L13 connect to AGND_HP

R58,R59 change to 15 Ohm

Page-7 Add U20 and Y4 to provide 32k to FM chip

Page-8 Delete U6 NAND and add these signal to Harp CN

Page-9 Delete U19 chip antenna

Page-10 Add R203~R206 and Q9 to LED control

Page-12 Modify LDO5 for BT power, HC_LDO not used

Use Vsys on PMU_ONKEY power source

Page-14 Bootstrap resistor modified

Page-3 Add U3 for 32k level shift

MM3 bus re-connect to test point

Page-8 Harp interface re-connect to bus switch

Page-13 Add U8 and U9 for HSM3 bus switch

Page-13 Remove bus switch and add resistor to select

harp or u-SD

JTAG modify to 8-pin

Page-3 Add ADP_5V_SENSE to GPIO

Add to DOCK_3V_EN GPIO

Add BMM3 port to micro-SD

Add I2S bus

Page-7 Delete R75, R76

Page-11 Add R188 and R189 to provide VDD_5V sense

to CPU

Add 3.3V LDO out to docking pin-19

Page-12 Add Q4 and Q5 to control backlight power

Add D15 to limit backlight power under 15V

Change L14 to 22uH

Add U6 LDO for docking 3.3V output

Add sub-battery for backup power

Add Q7 and D19 for VDD_5V / USB5V power switch

Add I2S bus

Add TP1 and TP2 for HPOUT

Remove R185 for reset double pull high

Page-13 BMM3 bus connect to micro-SD

5

4

REV 0A-0314 : 3/14/2007 release

REV 0A-0316 : 3/16/2007 release

REV 0A-0319 : 3/19/2007 release

REV 0A-0320 : 3/20/2007 release

REV 0A-0321 : 3/21/2007 release

Page-3 Delete TP7, TP61 and R10

Page-6 Delete de-pop circuit, add D6 change C107 to 10uF/0805

REV 0A-0323 : 3/23/2007 release

Page-3 Add RTCK from PM3_PWM0 to JTAG

Page-12 Add USB IF circuit

Add R19, R20, R192

REV 0A-0326 : 3/26/2007 release

Page-9 Delete J8

Page-13 Add R185

REV 0A-0327 : 3/27/2007 release

Page-8 SDRAM Resistor pack pin / signal swap

REV 0A-0328 : 3/28/2007 release

Page-3 R6 not stuff, R12 33R->0R

Change RTCK to FM_RESET#

Page-4 R25 1.15K-->205K

Page-6 U1.D19 connect to U1.E18

Add C139 for EMI, add C117

Page-7 R78 change to 200R

Page-8 R84, R87 pull high to VCC_HARP

Page-9 Add C140 for EMI

Page-11 Add R140 and J5.9 / J5.10 connect to VDD_5V

Page-13 Change R185 to connect J6.5 and J6.8

Page-14 Delete R307~R309, add R332

REV 0A-0329 : 3/29/2007 release

Page-4 R25 205K-->2.05K

Page-11 Fix J5.7 short to DGND

Page-12 Delete R96~R98, Q4, Q5

REV 0A-0330 : 3/30/2007 release

Page-9 Add con5 for 50 Ohm impedance control measurement

REV 0B-0517 : 5/17/2007 release

Page-3 Delete NAND and UART interface

Delete some GPIO for power control (BT,DOCKING)

Page-8 Delete SDRAM bus resistor pack

Modify HARP connector to 20-pin

Page-9 Modify LCD J4 connector to B-B and pin-assignment

Modify SW1 Power/hold switch and SW12 menu key

J7 pin-assignment swap

Page-10 Add R141 and R142 pull high for

docking signal

Page-11 Delete 1 LDO instead of PVDD1 for docking 3.3V

Delete sub-battery

Page-3 Add CLK_SUS_OUT for WLAN_PLL

Page-4 Delete 9.6MHz osc. and use CLK_SUS_OUT

Page-13 Use HSM3_MUX port for Micro-SD

Page-3 Change C230 to 1uF/0603

Page-9 Add U8 chip antenna and R75 for BT power

Page-12 Change reset to Powergood pin

Add D30, change sub-batt out to RTC only

Change VCC_2V7 to VCC_VB3_TBD

Page-4 Delete TP15~TP18,TP21 and TP22

Page-5 Floating U1.E11, E13, B3

Page-9 Add R75 to reserve VCC_3V3_FIX to BT

Page-5 Floating U1.E11, E13, B3

Page-12 Add D5 for main batt to RTC power in

Add R76 for VCC_3V3_FIX

Add R15, R16 for CVDD3 1.2V 3.3V select

Delete VREF and AGND's cap.

Page-3 Delete R4 and R7

Page-6 Add FM_ANT to HP_JACK_GND

Page-9 Change R75 to VCC_3V3 power rail

Page-12 Add TP1 to VPRG1

3

2

REV 0B-0606 : 6/6/2007 release

Page-6 Update J2 librbry and footprint

Delete some resistorsport and TP.

Page-8 Adjust J11 pin direction for Harp6 new define

Add R,C filter for Harp clock

Page-9 Modify J4 pin direction for LCM B-B CN

Page-11 Modify U19 to SC70 package

Update J12 footprint to JAM part

REV 0B-0607-C : 6/7/2007 release

Page-3 Add C193, C194 for LCD_PCLK and WLAN

CLK for EMI issue.

Page-9 Update J7 footprint from 25 to 23 pins

REV 0B-0608-A : 6/8/2007 release

Page-3 Change MM3_CD#, DOCK_I2C_OE and

VIDEO_SENSE to AT3_HD5~7.

Change jog-wheel key to LCD_DB18~23

Page-4 LED1~4 change to GP3_PR4~7

Change PMU_ONKEY and hold to GP3_PT0~1

Delete R180,R61,R49,C235,C239,C236

No stuff C88, C240, C95

Page-6 Connect MICDET to AGND_A

Add TP57 for MHPCOM

Page-9 Jt footprint modify

REV 0B-0612-B : 6/12/2007 release

Page-3 Change FM_RESET# to U1.W9

Page-5 Remove C24, 27, 29, 34, 40, 26, 44, 37,

38

Page-8 Modify Harp B-B connector pin-definition

REV 0B-0613-A : 6/13/2007 release

Page-5 Remove R39, R40, C35, C41

Page-8 Modify Harp B-B connector pin-22 to floating

Page-11 Add R4 33 Ohm to Reset#

REV 0B-0614-B : 6/14/2007 release

Page-3 Add 3-wire bus to I2S GPIO-N

Add R333/R334 to GPIO-G for Mode configuration

Page-4 Add C249 for EMI

Page-5 Change C49 to VCC_3V3

Page-6 Add C250, C251 for EMI

Add R70 for AGND_A to DGND

Page-7 Change FM I2C to 3-wire interface

Page-8 Update harp pin-assignment

Add C161, C162 for EMI

Page-10 Add PAD1~PAD5 for EMI

Page-11 Add C235,236,239,241,242,252,253,254 for EMI

Add R192, R195 connect DGND and PGND

1

REV 0B-0615-A : 6/15/2007 release

Page-3 Change FM_RESET# to U1.W9

Page-5 Remove L3, L5, C18, C28, C30

Change C47, C52 to 0.01uF

Page-12 R161 change to VCC_3V3 and value change

to 100k

REV 0B-0615-A : 6/15/2007 release

Page-2 Add Mictor Connector releated signals.

Page-14 Add Mictor Connector releated signals page.

Page-13 R292, R315 pull down, Delete SW10, R311 use 0 ohm

REV 0B-0530 : 5/30/2007 release

Page-3 Add LED1~4 and LCD BL control to KSO

port. Add LED5-6-7 / LED8-9-10 to KSI port

Page-8 Modify HARP connector to 40-pin

Page-9 Modify SW1 and SW11 circuit

Page-11 Add Q4, Q5 to control LCD BL

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc> 0B

C

<Doc> 0B

C

<Doc> 0B

C

Date: Sheet

Date: Sheet

Date: Sheet

INDEX

INDEX

INDEX

1

philchen@msi.com.tw

philchen@msi.com.tw

philchen@msi.com.tw

886-2-232345599 ext 8481

886-2-232345599 ext 8481

886-2-232345599 ext 8481

Drawn by Phil Chen

Drawn by Phil Chen

Drawn by Phil Chen

MS-5611

MS-5611

MS-5611

of

of

of

114Tuesday, July 17, 2007

114Tuesday, July 17, 2007

114Tuesday, July 17, 2007

5

4

3

2

1

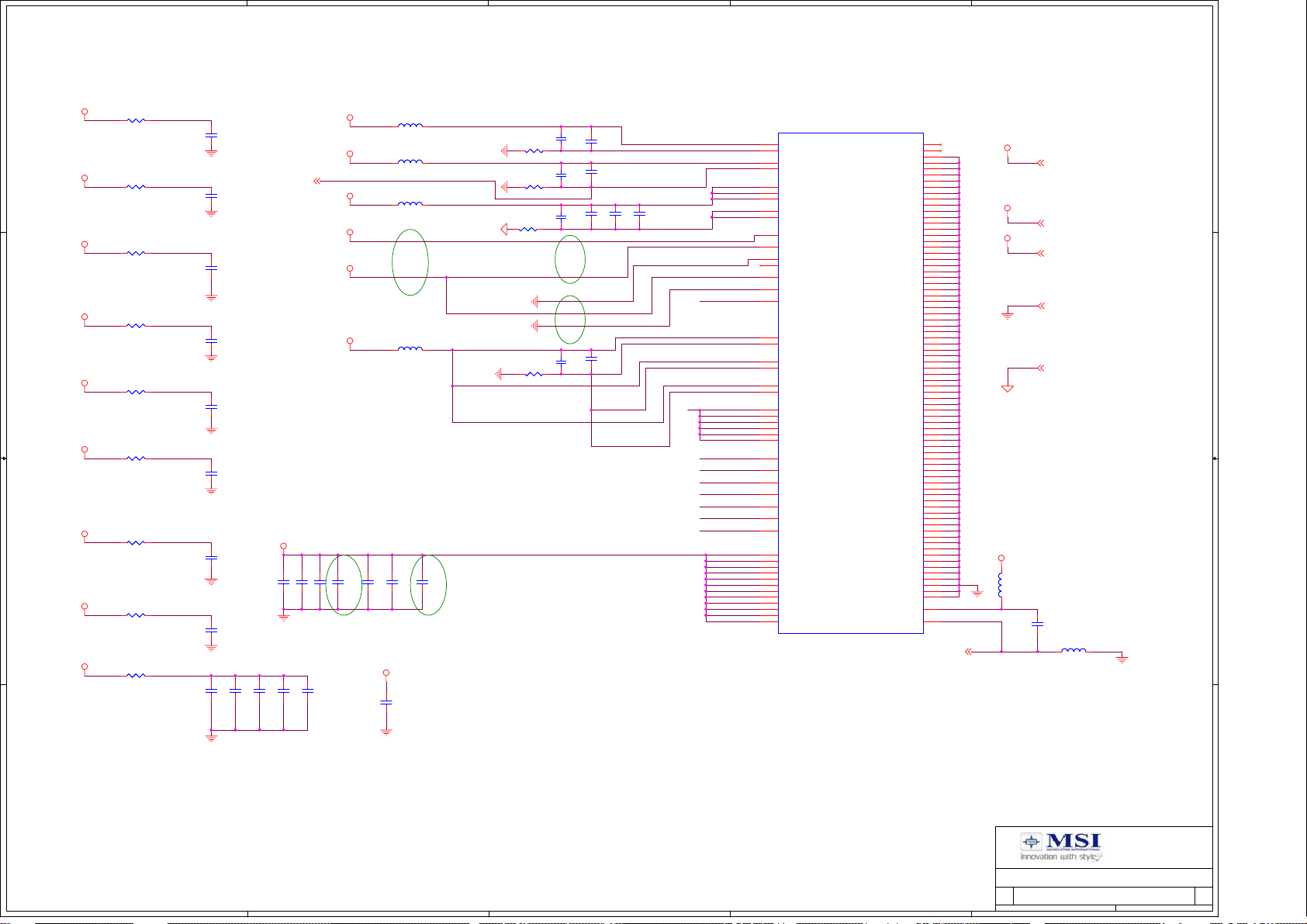

GoForce6100 SYSTEM BLOCK DIAGRAM

DEBUG

D D

12MHz

CRYSTAL

XTAL

PORT

RESET DBG

Micro-SD

CONNECTOR

HSM3_MUX

HARP

HSM3

DOCKING

CONNECTOR

USB2.0

Video Out

LINE-IN

ANT.

5V

C C

Line-OUT

HEADPHONE

DP,DM,VBUS

VIDEO OUT

LINE-IN

LINE-OUT

MHPOUT R/L

GoForce6100

LCD_DB[0..23]

GPIOs

GP3_PT

QVGA+ 2.4"

TFT LCD

Menu BUTTON

and

PWR/Slide

switch

PWR / Slide

switch

DIFFERENTIAL

MIC

MMICBIAS2

MMICIN2

MMICIN3_0

SDRAM

I2C

3-wire

I2C

VBUS

PWGD

B B

AS3517

DC/DC

POWER SUPPLY,

&

LI-ION BATTERY

CHARGER

1.2V

1.8V

3.0V

3.0V

3.0V

3.0V

3.3V

AP10 CORE,PLLs

AP10,SDRAM

64Kb

EEPROM

Audio AMP

LCD

FM

AP10 audio codec

I/O, AP10, Peripherals, BT

CLK_32K_IN

Si4702

FM

module

74AVC1T45

32k clock

WLAN_AFE_PLL

TFT BL

CLK_SUS_OUT

Power rail

VCC_1V2

VCC_1V8

VCC_3V3

VCC_LDO3

VCC_3V0

VCC_3V0LCD

VCC_3V3_FIX

BVDD

USB_VBUS

VDD_5V

LED+/-

Jog-wheel with

5 buttons

10-LED

1.8V

MOBILE

SDRAM

16MBX32

GND plane

PGND

DGND

AGND_A

AGND_HP

AGND_V

A A

32.768 KHz

CRYSTAL

5

Battery

philchen@msi.com.tw

philchen@msi.com.tw

philchen@msi.com.tw

886-2-232345599 ext 8481

886-2-232345599 ext 8481

886-2-232345599 ext 8481

Drawn by Phil Chen

Drawn by Phil Chen

Drawn by Phil Chen

MS-5611

MS-5611

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A2

A2

A2

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

Block diagram

Block diagram

Block diagram

PAGE02 : BLOCK DIAGRAM

PAGE02 : BLOCK DIAGRAM

PAGE02 : BLOCK DIAGRAM

1

MS-5611

214Tuesday, July 17, 2007

214Tuesday, July 17, 2007

214Tuesday, July 17, 2007

0B

0B

0B

of

of

of

5

U1-1

AA15

AB16

AA16

AA18

AA17

AC17

AC16

AB18

AC19

AA19

AB19

AC18

AB17

AA20

AA7

AA8

AC7

AC8

AA9

Y16

Y17

W19

W16

Y18

U19

R20

Y19

Y20

V19

T20

V20

U20

W20

T19

W6

Y6

W7

Y8

G4

K3

L2

E4

F4

L4

M1

H4

M4

N1

N3

N4

N2

P4

P2

P1

P3

R3

U3

R1

R4

T5

T1

T4

R2

U5

U1

V5

U4

T3

V4

W4

E3

F1

D3

E2

G2

D4

H2

G1

G3

H3

H1

J4

J3

E5

J1

F2

E6

K1

E7

D6

L3

K2

E1

D1

F3

J2

M3

K4

M2

L1

D2

C3

B1

U1-1

AP10

AP10

DTV3_XCLK

DTV3_PD0

DTV3_PD1

DTV3_PD2

DTV3_PD3

DTV3_PD4

DTV3_PD5

DTV3_PD6

DTV3_PD7

LCD3_AA0

LCD3_CS2

LCD3_RD

LCD3_RST

LCD3_RW

LCD3_DB0

LCD3_DB1

LCD3_DB2

LCD3_DB3

LCD3_DB4

LCD3_DB5

LCD3_DB6

LCD3_DB7

LCD3_DB8

LCD3_DB9

LCD3_DB10

LCD3_DB11

LCD3_DB12

LCD3_DB13

LCD3_DB14

LCD3_DB15

LCD3_DB16

LCD3_DB17

LCD3_DB18

LCD3_DB19

LCD3_DB20

LCD3_DB21

LCD3_DB22

LCD3_DB23

XM2_MD00

XM2_MD01

XM2_MD02

XM2_MD03

XM2_MD04

XM2_MD05

XM2_MD06

XM2_MD07

XM2_MD08

XM2_MD09

XM2_MD10

XM2_MD11

XM2_MD12

XM2_MD13

XM2_MD14

XM2_MD15

XM2_MD16

XM2_MD17

XM2_MD18

XM2_MD19

XM2_MD20

XM2_MD21

XM2_MD22

XM2_MD23

XM2_MD24

XM2_MD25

XM2_MD26

XM2_MD27

XM2_MD28

XM2_MD29

XM2_MD30

XM2_MD31

XM2_MA00

XM2_MA01

XM2_MA02

XM2_MA03

XM2_MA04

XM2_MA05

XM2_MA06

XM2_MA07

XM2_MA08

XM2_MA09

XM2_MA10

XM2_MA11

XM2_MA12

XM2_MA13

XM2_MA14

XM2_MA15

XM2_MA16

XM2_MA17

XM2_MA18

XM2_MA19

XM2_MA20

XM2_CKE

XM2_CS_A

XM2_CS_B

XM2_CS_C

XM2_CS_D

XM2_DQM_H

XM2_DQM_L

XM2_LDQS

XM2_UDQS

XM2_MIO_RDY

XM2_RE

XM2_WE

HSM3_MUX_CLK12

HSM3_MUX_D[0..3]12

Mux HSMMC

LCD3_XRESET9

D D

LCD3_DE9

LCD3_HSYNC9

LCD3_PCLK9

LCD3_VSYNC9

LCD3_DB[0..17]9

TFT LCD 18-BIT RGB I/F

XM2_MD[0..31]8,14

SDRAM DATA BUS

C C

XM2_MA[0..20]13

SDRAM ADDRESS BUS

B B

XM2_MIO.RDY14

SDRAM CONTROL

VCC_1V8

1 2

LCD3_DB[0..17]

XM2_MD[0..31]

XM2_MA[0..20]

R14

R14

10K

10K

12

C193

C193

X_10pF

X_10pF

UP9

DOWN9

MENU9

FORWARD9

ENTER9

REVERSE9

12

10pF

10pF

SDR_CKE8,14

XM2_CS.A#14

XM2_CS.B#14

XM2_CS_C#8,14

XM2_CS.D#14

XM2_DQM18

XM2_DQM08

XM2_DQM38

XM2_DQM28,14

1 2

C189

C189

HSM3_MUX_CLK

HSM3_MUX_D0

HSM3_MUX_D1

HSM3_MUX_D2

HSM3_MUX_D3

R133 R133

R29110R291

1 2

10

LCD3_XRESET

LCD3_DE

LCD3_HSYNC

LCD3_PCLKR

LCD3_VSYNC

LCD3_DB0

LCD3_DB1

LCD3_DB2

LCD3_DB3

LCD3_DB4

LCD3_DB5

LCD3_DB6

LCD3_DB7

LCD3_DB8

LCD3_DB9

LCD3_DB10

LCD3_DB11

LCD3_DB12

LCD3_DB13

LCD3_DB14

LCD3_DB15

LCD3_DB16

LCD3_DB17

UP

DOWN

MENU

FORWARD

ENTER

REVERSE

XM2_MD0

XM2_MD1

XM2_MD2

XM2_MD3

XM2_MD4

XM2_MD5

XM2_MD6

XM2_MD7

XM2_MD8

XM2_MD9

XM2_MD10

XM2_MD11

XM2_MD12

XM2_MD13

XM2_MD14

XM2_MD15

XM2_MD16

XM2_MD17

XM2_MD18

XM2_MD19

XM2_MD20

XM2_MD21

XM2_MD22

XM2_MD23

XM2_MD24

XM2_MD25

XM2_MD26

XM2_MD27

XM2_MD28

XM2_MD29

XM2_MD30

XM2_MD31

XM2_MA0

XM2_MA1

XM2_MA2

XM2_MA3

XM2_MA4

XM2_MA5

XM2_MA6

XM2_MA7

XM2_MA8

XM2_MA9

XM2_MA10

XM2_MA11

XM2_MA12

XM2_MA13

XM2_MA14

XM2_MA15

XM2_MA16

XM2_MA17

XM2_MA18

XM2_MA19

XM2_MA20

XM2_CKE

XM2_CS.A#

XM2_CS.B#

XM2_CS_C#

XM2_CS.D#

XM2_DQM1

XM2_DQM0

XM2_MIO_RDY

XM2_DQM3

XM2_DQM2

LCD INTERFACE

LCD INTERFACE

4

K19

CNF3_TST

DBG3_TRST

JTAG &

CONFIG

JTAG &

CONFIG

GPIOI2CI2SUSB

GPIOI2CI2SUSB

XTAL_12M_OUT

CLK3_SYS_OUT

CLK3_SYS_OUT_N

CLK3_SUS_OUT

CLOCKS

CLOCKS

CLK3_DEV_OUT

AT3_HDMARQ

AT3_HDMACK

AT3_S_HDMACK

AT3_S_HDMARQ

ATAPI/EDID INTERFACE

ATAPI/EDID INTERFACE

PWMUART D LCD

PWMUART D LCD

DBG3_TMS

DBG3_TDO

DBG3_TDI

DBG3_TCK

BM3_KSO_7

BM3_KSO_6

BM3_KSO_5

BM3_KSO_4

BM3_KSO_3

BM3_KSO_2

BM3_KSO_1

BM3_KSO_0

BM3_KSI_7

BM3_KSI_6

BM3_KSI_5

BM3_KSI_4

BM3_KSI_3

BM3_KSI_2

BM3_KSI_1

BM3_KSI_0

RM3_SDA

RM3_SCL

I2S_SCLK

I2S_DOUT

I2S_DIN

I2S_LRCK

SPDIF_IN

SPDIF_OUT

USB_BP

USB_BN

XTAL_12M_IN

CLK_32K_IN

AT3_HD15

AT3_HD14

AT3_HD13

AT3_HD12

AT3_HD11

AT3_HD10

AT3_HD09

AT3_HD08

AT3_HD07

AT3_HD06

AT3_HD05

AT3_HD04

AT3_HD03

AT3_HD02

AT3_HD01

AT3_HD00

AT3_HA2

AT3_HA1

AT3_HA0

AT3_HIOW

AT3_HIOR

AT3_HIORDY

AT3_HRESET

AT3_HIRQ0

AT3_HIRQ1

AT3_HCS0

AT3_HCS1

AT3_S_HIOR

AT3_S_HIOW

D_LCD3_RST

D_LCD3_RW

D_LCD3_RD

D_LCD3_DB7

D_LCD3_DB6

D_LCD3_DB5

D_LCD3_DB4

D_LCD3_DB3

D_LCD3_DB2

D_LCD3_DB1

D_LCD3_DB0

D_LCD3_AA0

D_LCD3_CS2

PM3_PWM1

PM3_PWM0

IR3_TXD

IR3_RXD

UA3_TXD

UA3_RXD

DTV

DTV

SDRAM, SRAM, FLASH ROM

MEMORY INTERFACE

SDRAM, SRAM, FLASH ROM

MEMORY INTERFACE

PP6110A-TFBGA441

PP6110A-TFBGA441

VBUS

REXT

RESET

DBG3_TRST

H22

DBG3_TMS

K21

DBG3_TDO

L20

DBG3_TDI

P21

DBG3_TCK

L22

Y9

W9

HSM3_MUX_CMD

Y7

Y22

AB21

Y21

W21

AC20

USB_VBUS_SENSE

U23

R22

T22

N21

J19

PMU_IRQ

T21

U22

V21

I2C_DATA

H20

I2C_CLK

J20

K23

J21

L23

J23

J22

K22

USB_BP

AA23

USB_BN

AB23

AA22

USB_RREF GND_USB_IO

W23

XTAL_12M_IN

P23

XTAL_12M_OUT

P22

CLK_32K_IN

C1

CLK_SYS_OUT

L5

M5

AC9

M19

AB6

AC5

AB5

AC2

AB2

AC1

AA3

AB1

AB3

W1

AA4

V3

AA2

AA1

W2

Y1

T2

Y5

Y2

AC6

Y4

W3

AB4

V2

AC3

Y3

AC4

V1

U2

AC21

AC22

AB20

AC23

Y11

AB10

AC12

Y13

AC10

AA11

AA10

Y12

Y10

AB9

AB11

AA12

AC11

W17

W12

V22

R21

N19

P20

M23

CLK_DEV.OUT_M 14

HSM3_D3

HSM3_D2

HSM3_D1

HSM3_D0

VIDEO_SENSE

DOCK_I2C_OE

MM3_CD#

R333

R333

1 2

R334

R334

1 2

RESET#

3

DBG3_TRST 12

DBG3_TMS 12

DBG3_TDO 12

DBG3_TDI 12

DBG3_TCK 12

FM_RESET# 7

HSM3_MUX_CMD 12

R9 33R9 33

R120R12

1 2

LCD3_XCS 9

LCD3_SCL 9

LCD3_SDOUT 9

LCD3_SDI 9

X_100K, 5%

X_100K, 5%

X_100K, 5%

X_100K, 5%

BL_ON 11

USB_VBUS_SENSE 10

VBUS_ON 11

PHASE_1 9

PHASE_2 9

ADP_5V_SENSE 10

PMU_IRQ# 11

LED5-6-7 9

LED8-9-10 9

3WIRE_CLK 7

3WIRE_DATA 7

TP74TP74

1 2

0

12

C194

C194

X_10pF

X_10pF

LCD SPI I/F

VIDEO_SENSE 10

DOCK_I2C_OE 10

MM3_CD# 12

R2

10KR210K

R8

1 2

6.04K, 1%R86.04K, 1%

CLK_SUS_OUT 4

1 2

VCC_3V3

3

4

Reserved for Sandisk different mode setting

HSM3_CLK

HSM3_CMD

12

C230

C230

X_1U/16V/0603

X_1U/16V/0603

SD_PWR_OFF# 12

HARP_PWR_OFF# 8

DOCKING_IRQ 10

DOCKING_DETECT 10

RESET# 11,12,14

PDN 9

I2C_WP 8

FM3_SEN# 7

HSM3_CLK 8

HSM3_CMD 8

JTAG

Primary SDIO1 I/F(MM3)

R3

10KR310K

1 2

I2C_DATA 8,10,11

I2C_CLK 8,10,11

T1

2

1

90 OHMST190 OHMS

C190

C190

1 2

X_10pF

X_10pF

GND_USB_IO 5

SDR_CLK 8,14

HSM3_D[0..3]

For the Harp

HSMMC control

FM

2

USB_DP 10

USB_DN 10

XTAL_12M_IN

XTAL_12M_OUT

HSM3_D[0..3] 8

HSMMC data

CLK_32K_IN

R5

VCCB

12

10MR510M

Y1

1

4

DIR

B

12.00MHZY112.00MHZ

A2

B2

C2

2

3

33PFC233PF

R1033R10

33

1 2

12

C1

33PFC133PF

VCC_1V8 VCC_3V3

U3

U3

A1

VCCA

B1

GND

C1

A

SN74AVC1T45YZP

SN74AVC1T45YZP

VCC_3V3

VCC_3V3 4,5,8,9,10,11,12,14

VCC_1V8

VCC_1V8 5,8,11,13

DGND 4,5,6,8,9,10,11,12,13,14

12

C2

1

XTAL_GND 5

CLK_32K 7,11

A A

PRELIMINARY SCHEMATICS ONLY - NOT TESTED AND NOT

QUALIFIED FOR MANUFACTURING

philchen@msi.com.tw

philchen@msi.com.tw

philchen@msi.com.tw

886-2-232345599 ext 8481

886-2-232345599 ext 8481

886-2-232345599 ext 8481

Drawn by Phil Chen

Drawn by Phil Chen

Drawn by Phil Chen

MS-5611

MS-5611

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

AP10_1: PROCESSOR

AP10_1: PROCESSOR

AP10_1: PROCESSOR

PAGE03 : AP10_1: PROCESSOR 0B

PAGE03 : AP10_1: PROCESSOR 0B

PAGE03 : AP10_1: PROCESSOR 0B

MS-5611

314Tuesday, July 17, 2007

314Tuesday, July 17, 2007

314Tuesday, July 17, 2007

of

of

1

of

5

VCC_1V2

4

3

2

1

R3291KR329

D D

CLK_SUS_OUT3

VCC_1V2

VCC_1V2 5,11

C C

B B

VCC_3V3

VCC_3V3 3,5,8,9,10,11,12,14

VCC_1V8

VCC_1V8 3,5,8,11,13

DGND 3,5,6,8,9,10,11,12,13,14

PMU_ONKEY11

AGND_V 5,10,11

AGND_V

1K

WLAN_AFE_PLLIN

WLAN_AFE_VINPI

WLAN_AFE_VINNI

WLAN_AFE_VINPQ

WLAN_AFE_VINNQ

LED19

LED29

LED39

LED49

HOLD9

U1-2

U1-2

AP10

AP10

C13

WLAN_AFE_PLLIN

A2

WLAN_AFE_VINPI

A3

WLAN_AFE_VINNI

B4

WLAN_AFE_VINPQ

A4

WLAN_AFE_VINNQ

D8

WLAN_AFE_VAINP_0

D7

WLAN_AFE_VAINN_0

C8

WLAN_AFE_VAINP_1

C7

WLAN_AFE_VAINN_1

C5

WLAN_AFE_VREFP

C4

WLAN_AFE_VREFN

B5

WLAN_AFE_VBG

A1

WLAN_AFE_VCM

A9

WLAN_AFE_IBEXT

C9

BT_RX_ACTIVE

E9

BT_TX_ACTIVE

C18

GP3_PR0

B15

GP3_PR1

E17

GP3_PR2

C16

GP3_PR3

D17

GP3_PR4

D18

GP3_PR5

E16

GP3_PR6

A15

GP3_PR7

C17

GP3_PS0

A14

GP3_PS1

C15

GP3_PS2

D16

GP3_PS3

D15

GP3_PS4

B14

GP3_PS5

C14

GP3_PS6

B13

GP3_PS7

N22

GP3_PT0

K20

GP3_PT1

V23

GP3_PT2

U21

GP3_PT3

AB8

GP3_PT4

AA5

GP3_PT5

AA6

GP3_PT6

AB7

GP3_PT7

WLAN_LDO_CTRL_EN

WLAN_LDO_EN

WLAN_LDO_PWR_OK

WLAN_AFE_VOUTPI

WLAN_AFE_VOUTNI

WLAN_AFE_VOUTPQ

WLAN_AFE_VOUTNQ

WLAN_AFE_VOUT

WLAN_RFSPI_CLK

WLAN_RFSPI_CSB

WLAN_RFSPI_WDATA

WLAN_RF_SLEEP

WLAN_RX_ON

WLAN_HP_FILTER_ENABLE

WLAN_TX_ON

WLAN_TX_PA_ON_G

WLAN_ANT_SEL

WLAN_ANT_SEL_B

WLAN_ALP_GAIN_3

WLAN_ALP_GAIN_4

WLAN_ALP_GAIN_5

WLAN_ALP_GAIN_6

WLAN_ALP_GAIN_7

WLAN_ALP_GAIN_8

WLAN_ALP_GAIN_9

WLAN_RX_ACTIVE

WLAN_TX_ACTIVE

VDAC_IOUTP0

VDAC_IOUTN0

VDAC_IOUTP1

VDAC_IOUTN1

VDAC_IOUTP2

VDAC_IOUTN2

VDAC_IREF

VDAC_VDREF

B8

A10

B12

A7

A6

B7

C6

A8

D10

D9

C11

E8

D11

B10

E10

B11

D14

A13

C12

A12

D12

E14

D13

E15

A11

B9

C10

AC15

AA14

AC13

AB14

AC14

AA13

AB12

AB13

12

VCC_3V3

R290R29

1 2

0

VDAC0

VDAC1

VDAC2

AGND_V

C8

0.1UFC80.1UF

12

C9

R25

R25

1UF/6.3VC91UF/6.3V

1 2

AGND_V AGND_V AGND_V

EMI

2.05K, 1%

2.05K, 1%

AGND_V

C249

C249

X_0.1UF

X_0.1UF

1 2

R24

R24

75, 1%

75, 1%

R181 0R181 0

1 2

L23

1 2

C88 X_22PFC88 X_22PF

AGND_V AGND_V AGND_V

R88 0R88 0

R23

R23

R182

R182

75, 1%

75, 1%

75, 1%

75, 1%

1 2

1 2

1 2

1 2

C240 X_22PFC240 X_22PF

AGND_V

R50 0R50 0

1 2

1 2

C95 X_22PFC95 X_22PF

AGND_V AGND_V AGND_V

L23

1 2

2.7UH

2.7UH

LQM21NN2R7K10 COMPOSITE

12

C233

C233

560PF

560PF

12

C237

C237

560PF

560PF

LQM21NN2R7K10

12

C231

C231

560PF

560PF

1 2

LQM21NN2R7K10

1 2

12

L24

L24

2.7UH

2.7UH

12

AGND_V AGND_V

L22

L22

2.7UH

2.7UH

12

C234

C234

560PF

560PF

C238

C238

560PF

560PF

C232

C232

560PF

560PF

D17

D17

BAT54S

BAT54S

D18

D18

BAT54S

BAT54S

D16

D16

BAT54S

BAT54S

VCC_3V3

Y_OUT

C_OUT

CVBS_OUT 10

Y_OUT 10

C_OUT 10

3

1

2

VCC_3V3

3

1

2

VCC_3V3

3

1

2

A A

5

4

3

PRELIMINARY SCHEMATICS ONLY - NOT TESTED AND NOT

QUALIFIED FOR MANUFACTURING

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

2

Date: Sheet of

AP10_2: WiFi & Video

AP10_2: WiFi & Video

AP10_2: WiFi & Video

PAGE04 : AP10_2: WiFi & Video 0B

PAGE04 : AP10_2: WiFi & Video 0B

PAGE04 : AP10_2: WiFi & Video 0B

1

philchen@msi.com.tw

philchen@msi.com.tw

philchen@msi.com.tw

886-2-232345599 ext 8481

886-2-232345599 ext 8481

886-2-232345599 ext 8481

Drawn by Phil Chen

Drawn by Phil Chen

Drawn by Phil Chen

MS-5611

MS-5611

MS-5611

414Tuesday, July 17, 2007

414Tuesday, July 17, 2007

414Tuesday, July 17, 2007

of

of

5

4

3

2

1

VCC_3V3

D D

VCC_3V3

VCC_3V3

VCC_3V3

C C

VCC_3V3

VCC_3V3

VCC_3V3

B B

VCC_3V3

VCC_1V8

R300R30

1 2

0

R320R32

1 2

0

R350R35

1 2

0

R360R36

1 2

0

R380R38

1 2

0

R410R41

1 2

0

R420R42

1 2

0

R430R43

1 2

0

R440R44

1 2

0

VDD_IO

VDD_IO_DBG

VDD_IO_I2S

VDD_IO_DTV

VDD_IO_AT

VDD_IO_DLCD

VDD_IO_WLAN

VDD_IO_MEM

12

C14

C14

0.1UF

0.1UF

12

C19

C19

0.1UF

0.1UF

12

C25

C25

0.1UF

0.1UF

12

C31

C31

0.1UF

0.1UF

12

C36

C36

0.1UF

0.1UF

12

C42

C42

0.1UF

0.1UF

12

C43

C43

0.1UF

0.1UF

12

C68

C68

0.1UF

0.1UF

12

C69

C69

0.1UF

0.1UF

GND_USB_IO3

VCC_1V2

12

C45

C45

0.1UF

0.1UF

12

12

12

C70

C70

C71

C71

C72

0.1UF

0.1UF

C72

0.1UF

0.1UF

0.1UF

0.1UF

VCC_1V2

L10L1

1 2

0

VCC_3V3

L40L4

1 2

0

VCC_3V3

L20L2

1 2

0

VCC_3V3

VCC_1V2

VCC_1V2

L60L6

1 2

0

12

12

12

C48

C48

0.1UF

0.1UF

C50

C50

0.1UF

0.1UF

VCC_3V3

12

C52

C52

C51

C51

0.01UF

0.01UF

0.1UF

0.1UF

1 2

12

C49

C49

0.1UF

0.1UF

C46

C46

0.1UF

0.1UF

12

C73

C73

0.1UF

0.1UF

C47

C47

0.01UF

0.01UF

1 2

R34 0R34 0

1 2

R31 0R31 0

1 2

R33 0R33 0

1 2

R37 0R37 0

1 2

12

12

12

12

C15

C15

1UF/6.3V

1UF/6.3V

C16

C16

1UF/6.3V

1UF/6.3V

C20

C20

1UF/6.3V

1UF/6.3V

C32

C32

1UF/6.3V

1UF/6.3V

12

C13

C13

0.1UF

0.1UF

12

C17

C17

0.1UF

0.1UF

12

12

C22

C22

C21

C21

0.1UF

0.1UF

0.1UF

0.1UF

12

C33

C33

0.1UF

0.1UF

12

C23

C23

0.1UF

0.1UF

VDD_USB

GND_USB

VCC_3VA

GND_USB_IO

VDAC_AVDD

GND_VDAC_GNDA

WLAN_AFE_AVDD33

WLAN_AFE_AVDD

WLAN_AFE_AVDD

VCC_1V2PA

GND_PA

VCC_1V2PC

GND_PC

VCC_1V2PP

GND_PP

VDD_IO_WLAN

VDD_IO_MEM

VDD_IO_ATVDD_IO_LCD

VDD_IO_DBG

VDD_IO_DLCD

VDD_IO_DTV

VDD_IO_I2S

VDD_IO_LCD

VDD_IO

U1-3

U1-3

AP10

AP10

W22

USB_VDDP

Y23

USB_VSSP

AB22

USB_VDDA

AA21

USB_VSSA

AB15

VDAC_AVDD1

W15

VDAC_AVDD2

Y14

VDAC_AVDD3

Y15

VDAC_AGND2

W14

VDAC_AGND1

A5

WLAN_AFE_AVDD33

B2

WLAN_AFE_AVDD

C2

WLAN_AFE_AGND2

B3

WLAN_AFE_AGND1

D5

WLAN_AFE_VDREF

B6

WLAN_AFE_AGNDREF

E12

VDD_IO_WLAN

M20

PLLA_VDD

L21

PLLA_VSS

M21

PLLC_VDD

N20

PLLC_VSS

M22

PLLP_VDD

N23

PLLP_VSS

R5

VDD_IO_MEM1

F5

VDD_IO_MEM2

G5

VDD_IO_MEM3

H5

VDD_IO_MEM4

J5

VDD_IO_MEM5

P5

VDD_IO_MEM6

W5

VDD_IO_AT

P19

VDD_IO_DBG

W10

VDD_IO_DLCD

W8

VDD_IO_DTV

H19

VDD_IO_I2S

W18

VDD_IO_LCD

R19

VDD_IO

H11

VDD_CORE1

H12

VDD_CORE2

H13

VDD_CORE3

L8

VDD_CORE4

L16

VDD_CORE5

M8

VDD_CORE6

M16

VDD_CORE7

N8

VDD_CORE8

N16

VDD_CORE9

T11

VDD_CORE10

T12

VDD_CORE11

T13

VDD_CORE12

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

GND19

GND20

GND21

GND22

GND23

GND24

GND25

GND26

GND27

GND28

GND29

GND30

GND31

GND32

GND33

GND34

GND35

GND36

GND37

GND38

GND39

GND40

GND41

GND42

GND43

GND44

GND45

GND46

GND47

GND48

GND49

GND50

GND51

GND52

GND53

GND54

GND55

GND56

GND57

GND58

GND59

GND60

GND61

GND62

GND63

GND64

GND65

GND66

GND67

GND68

GND69

GND70

GND71

GND72

GND73

GND74

GND75

GND76

XTAL_12M_VDD

XTAL_12M_VSS

XTAL12M_VDD

VCC_3V3

VCC_1V8

VCC_1V2

AGND_V

VCC_1V2

1 2

VCC_3V3 3,4,8,9,10,11,12,14

VCC_1V8 3,8,11,13

VCC_1V2 4,11

DGND 3,4,6,8,9,10,11,12,13,14

AGND_V 4,10,11

L90L9

0

12

C67

C67

0.1UF

0.1UF

1 2

L100L10

0

E11

E13

H8

H9

H16

H15

H14

H10

J8

J9

J10

J11

J12

J13

J14

J15

J16

K5

K8

K9

K10

K11

K12

K13

K14

K15

K16

L9

L10

L11

L12

L13

L14

L15

L19

M9

M10

M11

M12

M13

M14

M15

N5

N9

N10

N11

N12

N13

N14

N15

R8

R9

R10

R11

R12

R13

R14

R15

R16

T8

T9

T10

T14

T15

T16

P16

P15

P14

P13

P12

P11

P10

P9

P8

W11

W13

T23

R23

XTAL_GND3

A A

philchen@msi.com.tw

philchen@msi.com.tw

philchen@msi.com.tw

886-2-232345599 ext 8481

886-2-232345599 ext 8481

886-2-232345599 ext 8481

Drawn by Phil Chen

Drawn by Phil Chen

Drawn by Phil Chen

MS-5611

MS-5611

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

AP10_3: POWER

AP10_3: POWER

AP10_3: POWER

PAGE05 : AP10_3: POWER 0B

PAGE05 : AP10_3: POWER 0B

PAGE05 : AP10_3: POWER 0B

MS-5611

of

of

of

514Tuesday, July 17, 2007

514Tuesday, July 17, 2007

1

514Tuesday, July 17, 2007

Loading...

Loading...