MOTOROLA MC10101FNR2 Datasheet

SEMICONDUCTOR TECHNICAL DATA

3–1

REV 5

Motorola, Inc. 1996

3/93

The MC10101 is a quad 2–input OR/NOR gate with one input from

each gate common to pin 12.

PD= 25 mW typ/gate (No Load)

tpd= 2.0 ns typ

tr, tf= 2.0 ns typ (20%–80%)

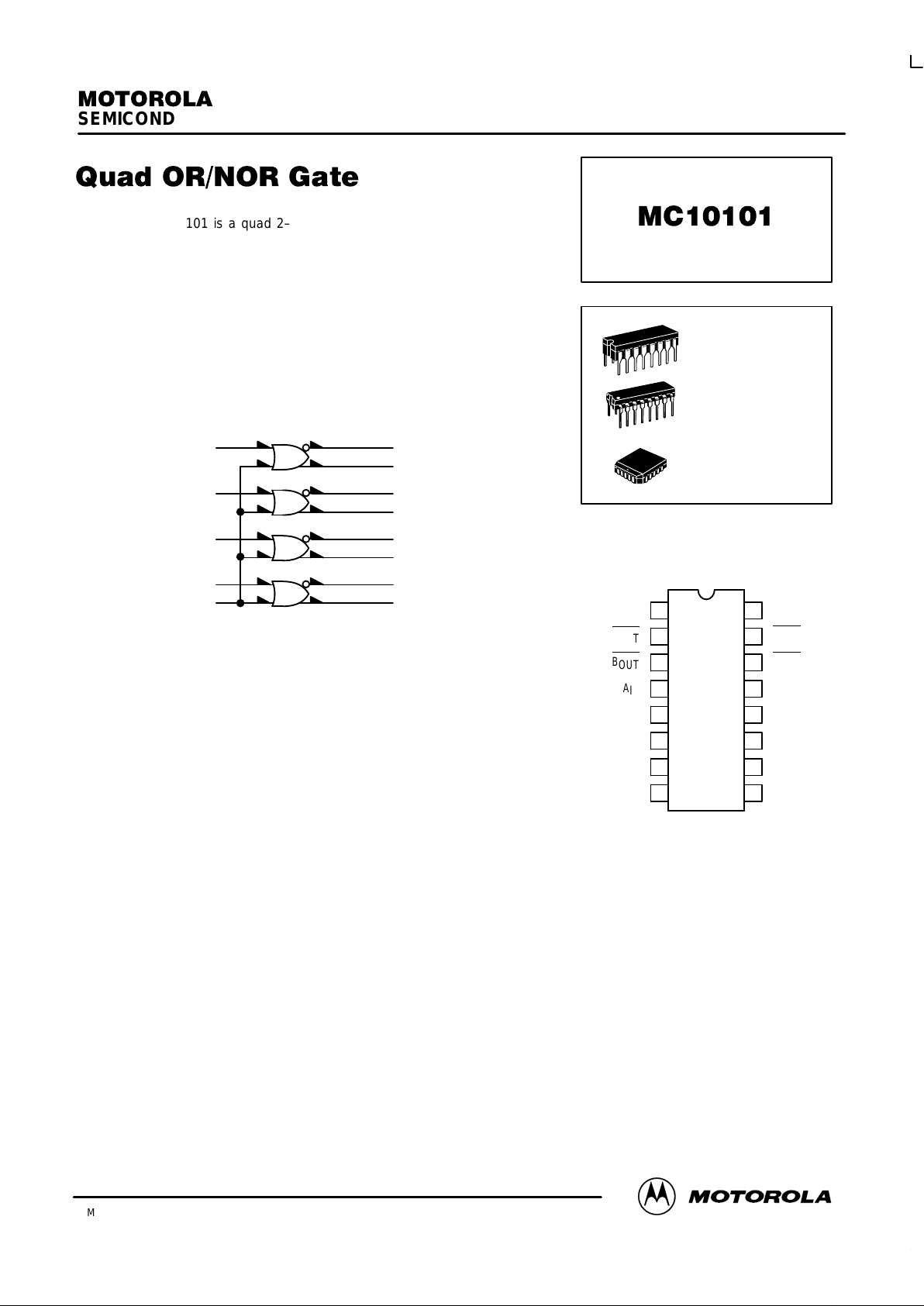

LOGIC DIAGRAM

V

CC1

= PIN 1

V

CC2

= PIN 16

VEE= PIN 8

12

9

13

10

7

4

15

11

14

6

3

5

2

DIP

PIN ASSIGNMENT

V

CC1

A

OUT

B

OUT

A

IN

A

OUT

B

OUT

B

IN

V

EE

V

CC2

D

OUT

C

OUT

D

IN

COMMON

INPUT

C

OUT

C

IN

D

OUT

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

L SUFFIX

CERAMIC PACKAGE

CASE 620–10

P SUFFIX

PLASTIC PACKAGE

CASE 648–08

FN SUFFIX

PLCC

CASE 775–02

Pin assignment is for Dual–in–Line Package.

For PLCC pin assignment, see the Pin Conversion

T ables on page 6–36 of the Motorola MECL Data

Book (DL122/D).

MC10101

MOTOROLA MECL Data

DL122 — Rev 6

3–2

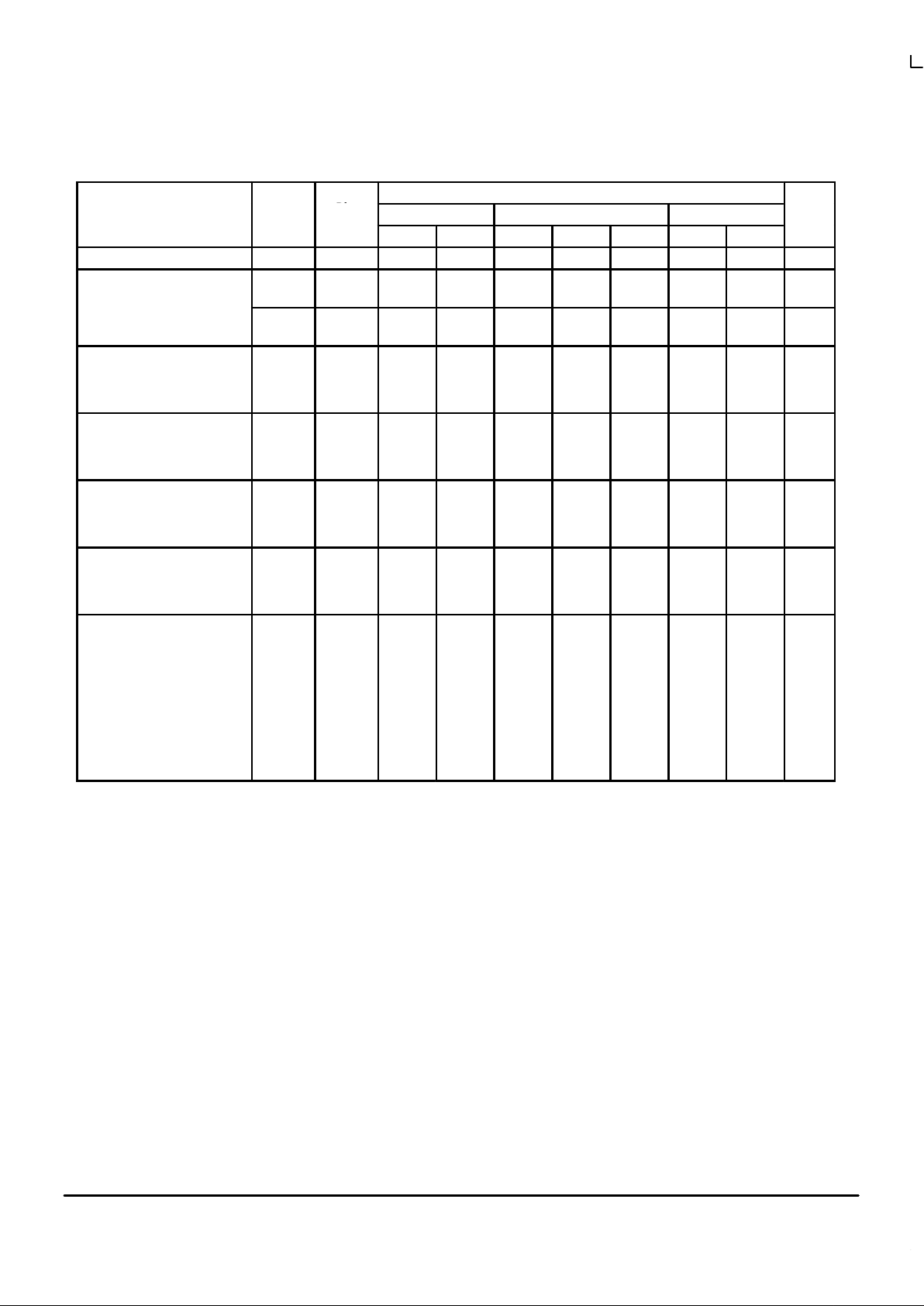

ELECTRICAL CHARACTERISTICS

Test Limits

Pin

Under

–30°C +25°C +85°C

Characteristic Symbol

Under

Test

Min Max Min Typ Max Min Max

Unit

Power Supply Drain Current I

E

8 29 20 26 29 mAdc

Input Current I

inH

4

12

425

850

265

535

265

535

µAdc

I

inL

4

12

0.5

0.5

0.5

0.5

0.3

0.3

µAdc

Output Voltage Logic 1 V

OH

5

5

2

2

–1.060

–1.060

–1.060

–1.060

–0.890

–0.890

–0.890

–0.890

–0.960

–0.960

–0.960

–0.960

–0.810

–0.810

–0.810

–0.810

–0.890

–0.890

–0.890

–0.890

–0.700

–0.700

–0.700

–0.700

Vdc

Output Voltage Logic 0 V

OL

5

5

2

2

–1.890

–1.890

–1.890

–1.890

–1.675

–1.675

–1.675

–1.675

–1.850

–1.850

–1.850

–1.850

–1.650

–1.650

–1.650

–1.650

–1.825

–1.825

–1.825

–1.825

–1.615

–1.615

–1.615

–1.615

Vdc

Threshold Voltage Logic 1 V

OHA

5

5

2

2

–1.080

–1.080

–1.080

–1.080

–0.980

–0.980

–0.980

–0.980

–0.910

–0.910

–0.910

–0.910

Vdc

Threshold Voltage Logic 0 V

OLA

5

5

2

2

–1.655

–1.655

–1.655

–1.655

–1.630

–1.630

–1.630

–1.630

–1.595

–1.595

–1.595

–1.595

Vdc

Switching Times (50Ω Load) ns

Propagation Delay t

4+2–

t

4–2+

t

4+5+

t

4–5–

2

2

5

5

1.0

1.0

1.0

1.0

3.1

3.1

3.1

3.1

1.0

1.0

1.0

1.0

2.0

2.0

2.0

2.0

2.9

2.9

2.9

2.9

1.0

1.0

1.0

1.0

3.3

3.3

3.3

3.3

Rise Time (20 to 80%) t

2+

t

5+

2

5

1.1

1.1

3.6

3.6

1.1

1.1

2.0

2.0

3.3

3.3

1.1

1.1

3.7

3.7

Fall Time (20 to 80%) t

2–

t

5–

2

5

1.1

1.1

3.6

3.6

1.1

1.1

2.0

2.0

3.3

3.3

1.1

1.1

3.7

3.7

Loading...

Loading...