Page 1

Intel®Desktop Board

D810E2CB

Technical Product Specification

January 2001

Order Number A44673-001

The Intel®Desktop Board D810E2CB may contain design defects or errors knowna serratathat may cause the product to deviate from published specifications. Current characterized

errata are documented in the Intel Desktop Board D810E2CB Specification Update.

Page 2

Revision History

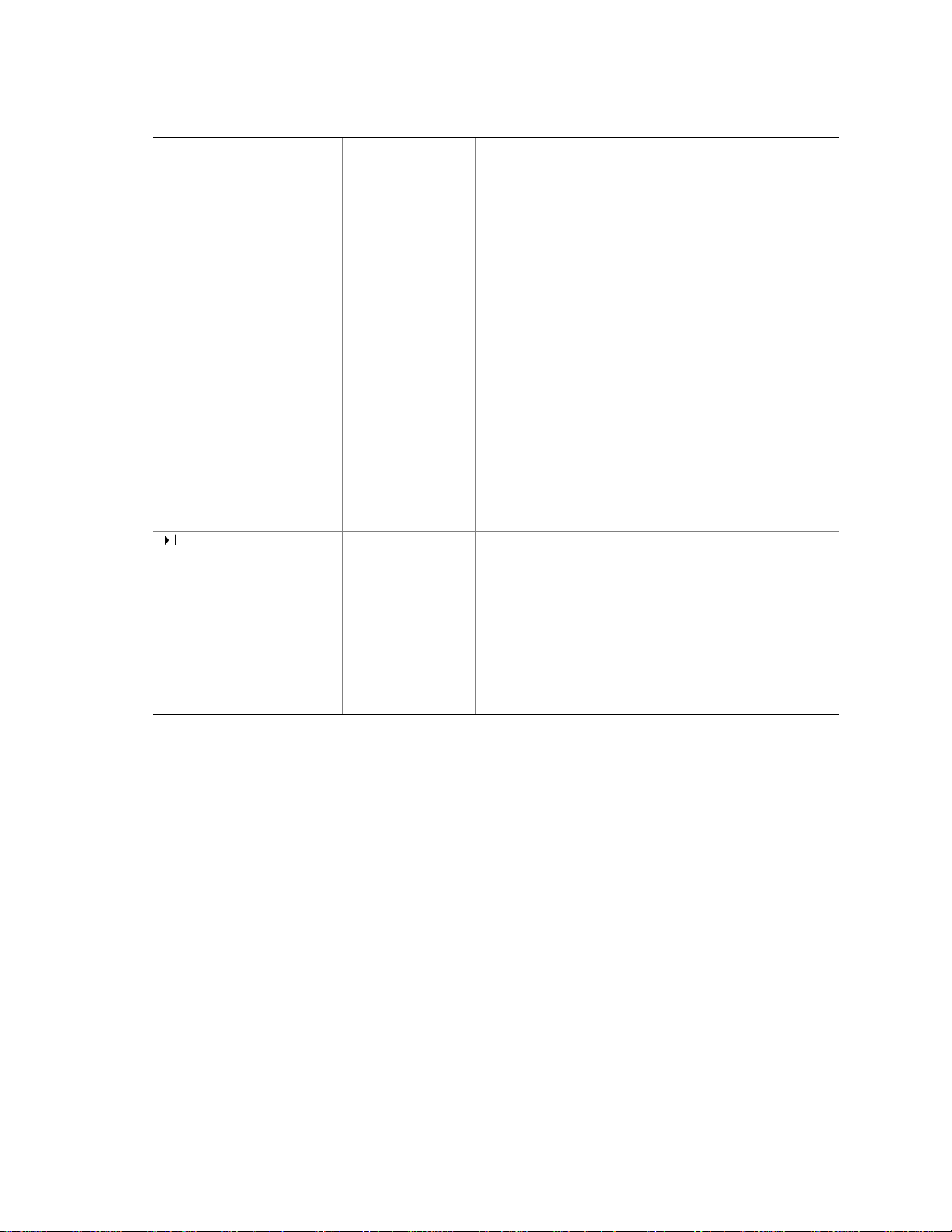

Revision Revision History Date

001 First release of the Intel®Desktop Board D810E2CB Technical Product

Specification.

This product specification applies to only standard D810E2CB boards with BIOS identifier

CB81010A.86A.

®

Changes to this specification will be published in the Intel

Desktop Board D810E2CB Specification

Update before being incorporated into a revision of this documen t.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL®PRODUCTS. EXCEPT AS

PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY

W HATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE

OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR

PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL

PROPERTY RIGHT.

January 2001

Intel Corporation mayhave patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that

relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any

license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property

rights.

Intel products are not intended for use in medical, lifesaving, or life sustaining applications or for anyother application in which

the failure of the Intel product could create a situation where personal injury or death may occur.

Intel may make changes to specifications and product descriptions at any time, without notice.

The D810E2CB board may contain design defects or errors known as errata that may causethe product to deviate from

published specifications. Current characterized errata are availableon request.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 5937

Denver,CO 80217-9808

or call in North America1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777,

Germany44-0-1793-421-333, other Countries 708-296-9333.

†

Third-party brands and names are the property of their respective owners.

Copyright 2001, Intel Corporation. All rights reserved.

Page 3

Preface

This Technical Product Specification (TPS) specifies the board layout, components, connectors,

power and environmental requirements, and theBIOS for the D810E2CB desktop board. It

describes the standard product and available manufacturing options.

Intended Audience

The TPS is intended to provide detailed, technical information about the D810E2CB board and its

components to the vendors, system integrators, and other engineers and technicians who need this

level of information. It is specifically not intended for general audiences.

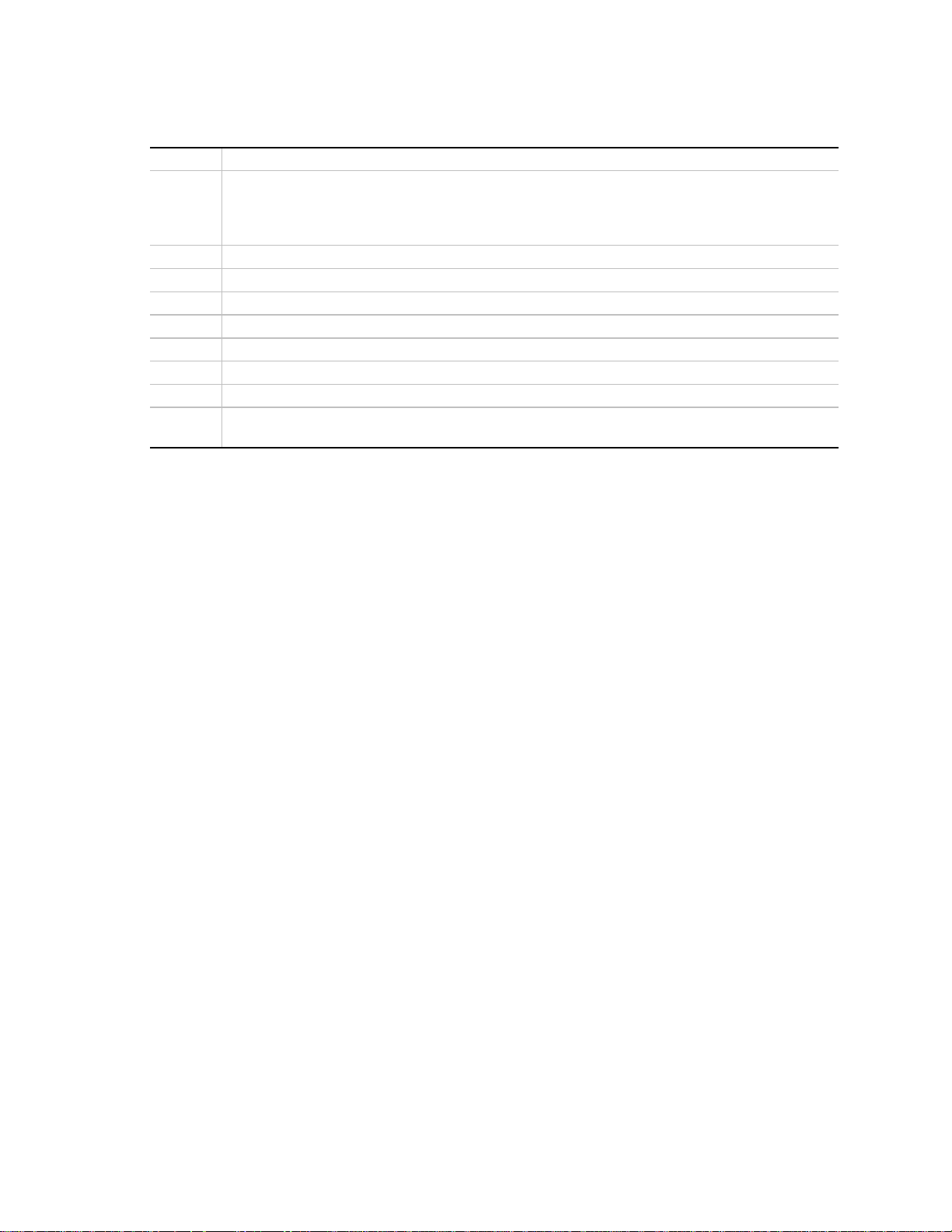

What This Document Contains

Chapter Description

1 A description of the hardware used on this board

2 A map of theresources of the board

3 The features supported by the BIOS Setup program

4 The contents of the BIOS Setup program’s menus and submenus

5 A description of the BIOS error messages, beep codes, and POST codes

Typographical Conventions

This section contains information about the conventions used in this specification. Not all of these

symbols and abbreviations appear in all specifications of this type.

Notes, Cautions, and Warnings

NOTE

✏

Notes call attention to important information.

CAUTION

Cautions are included to help you avoid damaging hardware or losing data.

WARNING

Warnings indicate conditions which, if not observed, can cause personal injury.

iii

Page 4

Intel Desktop Board D810E2CB Technical Product Specification

Other Common Notation

# Used after a signal name to identify an active-low signal (such as USBP0#)

(NxnX) When used in the description of a component, N indicates component type, xn are the relative

coordinates of its location on the D810E2CB board, and X is the instance of the particular part

at that general location. For example, J5J1 is a connector, located at 5J. It is the first

connector in the 5J area.

KB Kilobyte (1024 bytes)

Kbit Kilobit (1024 bits)

MB Megabyte (1,048,576 bytes)

Mbit Megabit (1,048,576 bits)

GB Gigabyte (1,073,741,824 bytes)

xxh An address or data value ending with a lowercase h indicates a hexadecimal value.

x.xV Volts. Voltages are DC unless otherwise specified.

†

This symbol is used to indicate third-party brands and names that are the property of their

respective owners.

iv

Page 5

Contents

1 Product Description

1.1 Overview....................................................................................................................12

1.1.1 Feature Summary........................................................................................12

1.1.2 Manufacturing Options ................................................................................13

1.1.3 D810E2CB Board Layout............................................................................14

1.1.4 Block Diagram .............................................................................................15

1.2 Online Support...........................................................................................................16

1.3 Design Specifications.................................................................................................16

1.4 Processor................................................................................................................... 19

1.5 System Memory.........................................................................................................20

1.6 Intel

1.7 I/O Controller..............................................................................................................25

1.8 Graphics Subsystem..................................................................................................27

1.9 Audio Subsystem.......................................................................................................28

1.10 Hardware Management Subsystem...........................................................................29

1.11 LAN Subsystem (Optional).........................................................................................30

1.12 Power Management Features.................................................................................... 31

®

810E Chipset....................................................................................................21

1.6.1 Direct AGP...................................................................................................22

1.6.2 USB.............................................................................................................22

1.6.3 IDE Support.................................................................................................23

1.6.4 Real-Time Clock, CMOS SRAM, and Battery..............................................24

1.6.5 SST 49LF004A 4 Mbit Firmware Hub (FWH)...............................................24

1.7.1 Serial Port....................................................................................................25

1.7.2 Parallel Port.................................................................................................25

1.7.3 Diskette Drive Controller ..............................................................................26

1.7.4 Keyboard and Mouse Interface....................................................................26

1.9.1 CS4201 Analog Codec................................................................................28

1.9.2 Audio Connectors........................................................................................28

1.10.1 Hardware Monitor Component (Optional)....................................................29

1.10.2 Fan Control and Monitoring .........................................................................29

®

1.11.1 Intel

1.11.2 RJ-45 LAN Connector with Integrated LEDs ...............................................30

1.12.1 ACPI............................................................................................................31

1.12.2 APM.............................................................................................................33

1.12.3 Hardware Support .......................................................................................34

82562ET Platf orm LAN Connect Device............................................30

2 Technical Reference

2.1 Introduction................................................................................................................39

2.2 Memory Map..............................................................................................................39

2.3 I/O Map...................................................................................................................... 40

2.4 DMA Channels...........................................................................................................42

2.5 PCI Configuration Space Map....................................................................................42

2.6 Interrupts....................................................................................................................43

2.7 PCI Interrupt Routing Map .........................................................................................44

v

Page 6

Intel Desktop Board D810E2CB Technical Product Specification

2.8 Connectors ................................................................................................................45

2.8.1 Back Panel Connectors...............................................................................46

2.8.2 Internal I/O Connectors................................................................................50

2.8.3 External I/O Connectors ..............................................................................58

2.9 Jumper Block.............................................................................................................61

2.10 Mechanical Considerations........................................................................................63

2.10.1 FlexATX Form Factor ..................................................................................63

2.10.2 I/O Shield.....................................................................................................64

2.11 Electrical Considerations............................................................................................65

2.11.1 Power Consumption ....................................................................................65

2.11.2 Power Supply Considerations......................................................................66

2.11.3 Standby Current Requirements...................................................................66

2.11.4 Fan Power Requirements............................................................................66

2.12 Thermal Considerations.............................................................................................67

2.13 Reliability....................................................................................................................68

2.14 Environmental............................................................................................................69

2.15 Regulatory Compliance..............................................................................................70

2.15.1 Safety Regulations......................................................................................70

2.15.2 EMC Regulations.........................................................................................70

2.15.3 Product Certification Markings (Board Level)...............................................71

3 Overview of BIOS Features

3.1 Introduction................................................................................................................73

3.2 BIOS Flash Memory Organization..............................................................................73

3.3 Resource Configuration.............................................................................................74

3.3.1 PCI Autoconfiguration..................................................................................74

3.3.2 PCI IDE Support ..........................................................................................74

3.4 System Management BIOS (SMBIOS).......................................................................75

3.5 USB Legacy Support .................................................................................................75

3.6 BIOS Updates............................................................................................................76

3.6.1 Language Support.......................................................................................76

3.6.2 Custom Splash Screen................................................................................76

3.7 Recovering BIOS Data...............................................................................................77

3.8 Boot Options..............................................................................................................78

3.8.1 CD-ROMand Network Boot......................................................................... 78

3.8.2 Booting Without Attached Devices..............................................................78

®

3.9 Fast Booting Systems with Intel

Rapid BIOS Boot...................................................78

3.9.1 Peripheral Selection and Configuration.......................................................78

3.9.2 Intel Rapid BIOS Boot..................................................................................79

3.9.3 Operating System........................................................................................79

3.10 BIOS Security Features .............................................................................................80

4 BIOS Setup Program

4.1 Introduction................................................................................................................81

4.2 Maintenance Menu ....................................................................................................82

4.2.1 Extended Conf iguration Submenu...............................................................83

4.3 Main Menu.................................................................................................................84

4.4 Advanced Menu.........................................................................................................85

vi

Page 7

4.4.1 PCI Configuration Submenu........................................................................86

4.4.2 Boot Conf iguration Submenu ......................................................................87

4.4.3 Peripheral Configuration Submenu..............................................................88

4.4.4 IDE Configuration Submenu........................................................................90

4.4.5 Diskette Configuration Submenu.................................................................93

4.4.6 Event Log Configuration Submenu..............................................................94

4.4.7 Video Configuration Submenu.....................................................................95

4.5 Security Menu............................................................................................................96

4.6 Power Menu...............................................................................................................97

4.7 Boot Menu .................................................................................................................98

4.8 Exit Menu.................................................................................................................100

5 Error Messages and Beep Codes

5.1 BIOS Error Messages..............................................................................................101

5.2 Port 80h POST Codes.............................................................................................103

5.3 Bus Initialization Checkpoints ..................................................................................107

5.4 Speaker ...................................................................................................................108

5.5 BIOS Beep Codes....................................................................................................109

Contents

Figures

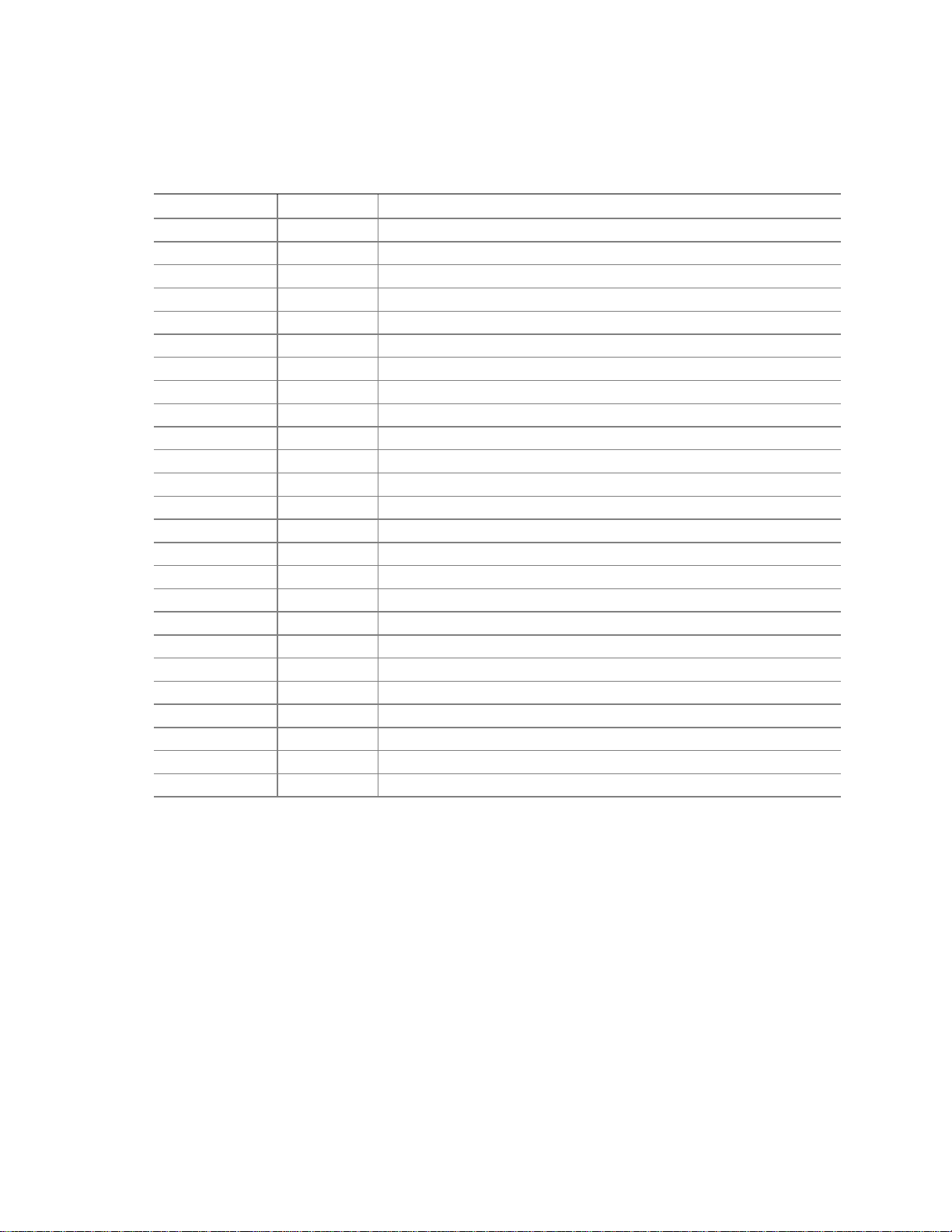

1. D810E2CB Board Components.................................................................................14

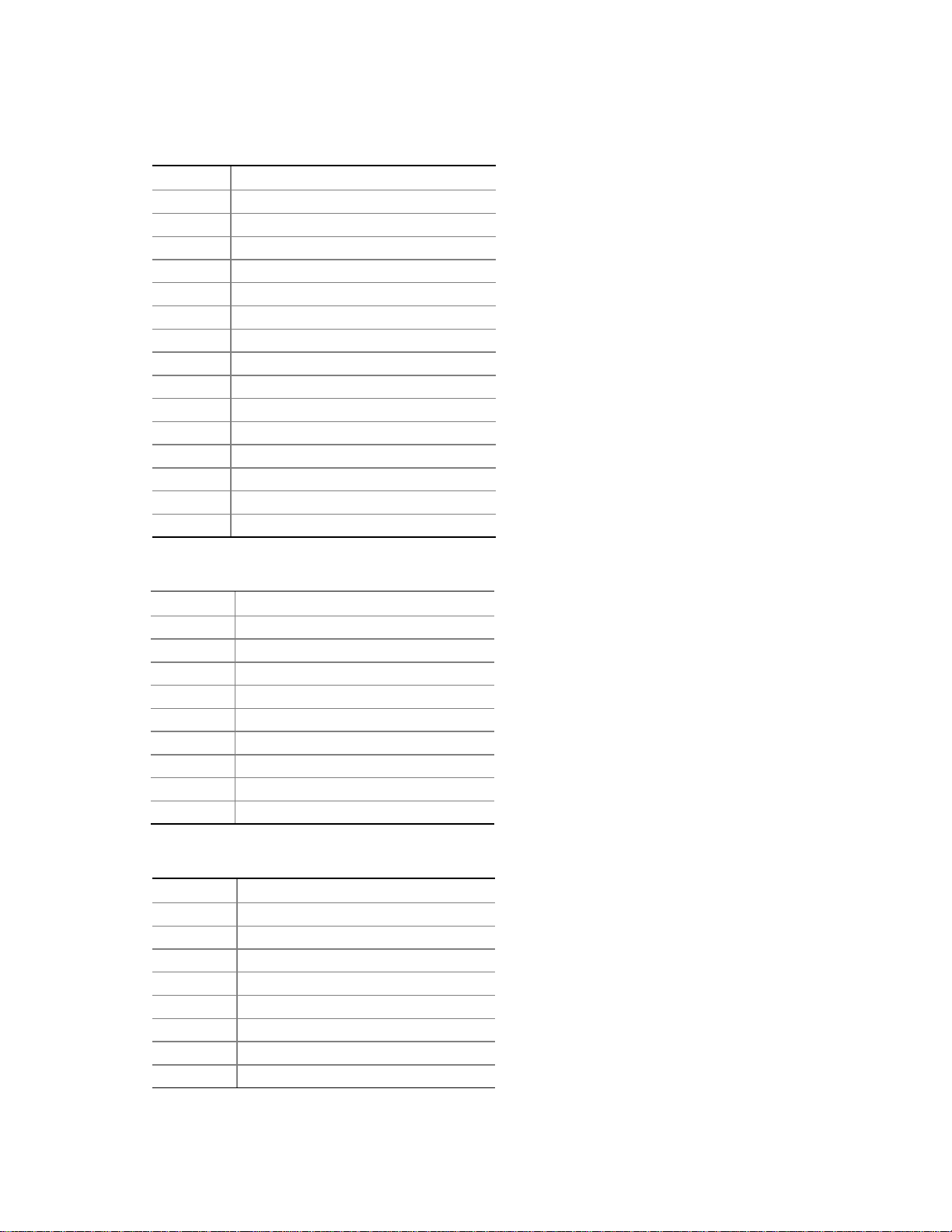

2. Block Diagram............................................................................................................15

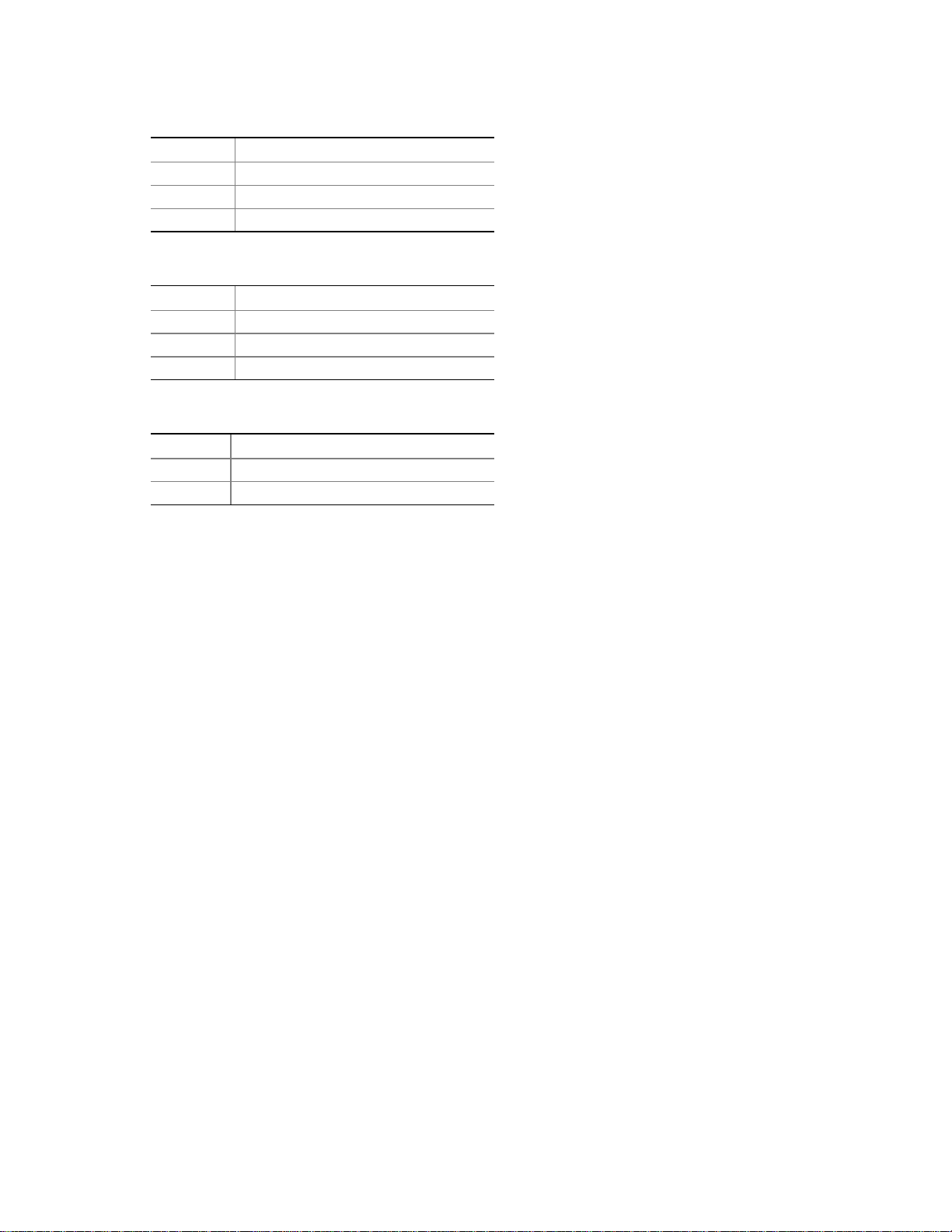

3. Intel 810E Chipset Block Diagram .............................................................................21

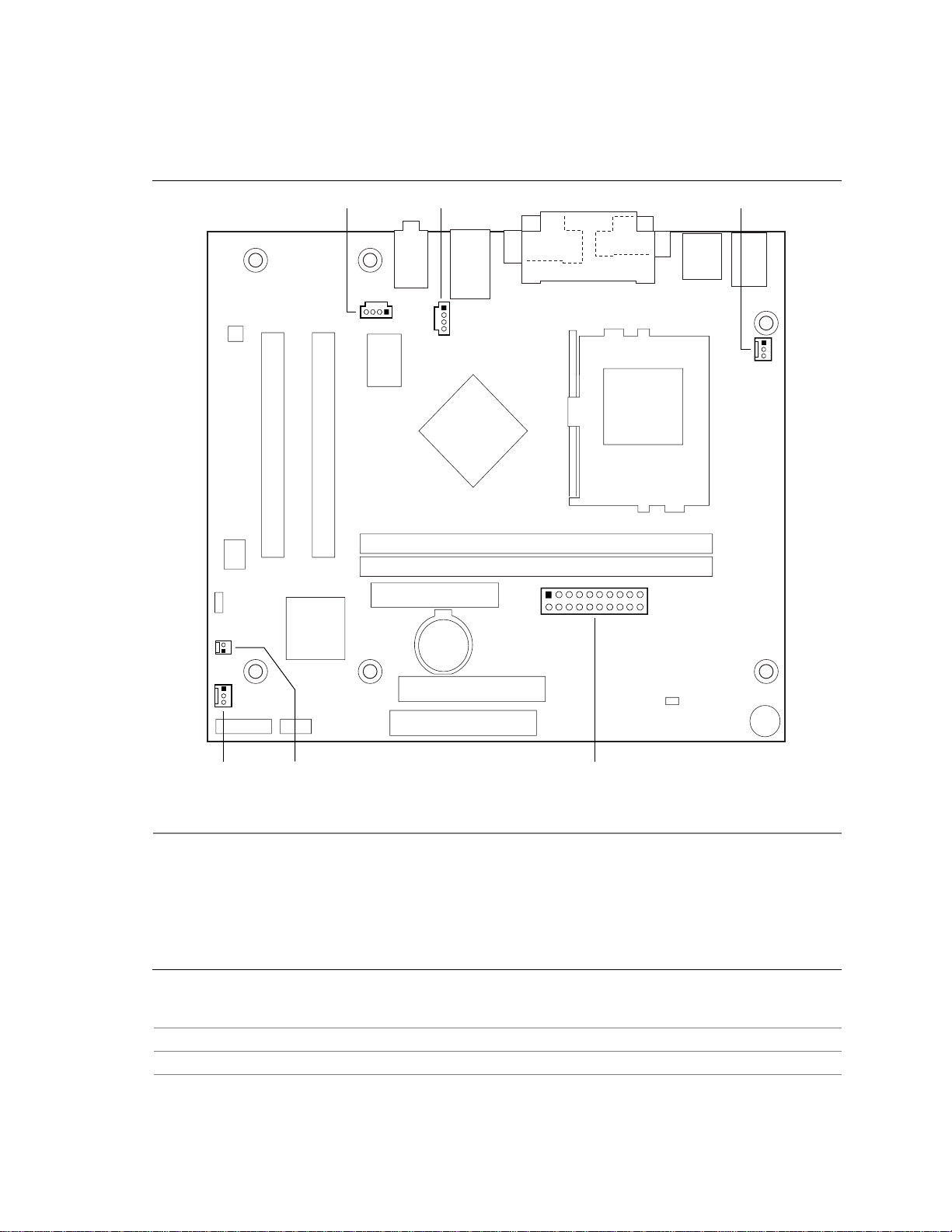

4. Block Diagram of Audio Subsystem with CS4201 Codec..........................................28

5. Back Panel Connectors .............................................................................................46

6. Audio, Power, and Hardware Control Connectors .....................................................51

7. Add-in Board and Peripheral Interface Connectors ...................................................54

8. External I/O Connectors.............................................................................................58

9. Location of the BIOS Setup Jumper Block.................................................................61

10. Board Dimensions......................................................................................................63

11. I/O Shield Dimensions................................................................................................64

12. High Temperature Zones...........................................................................................67

Tables

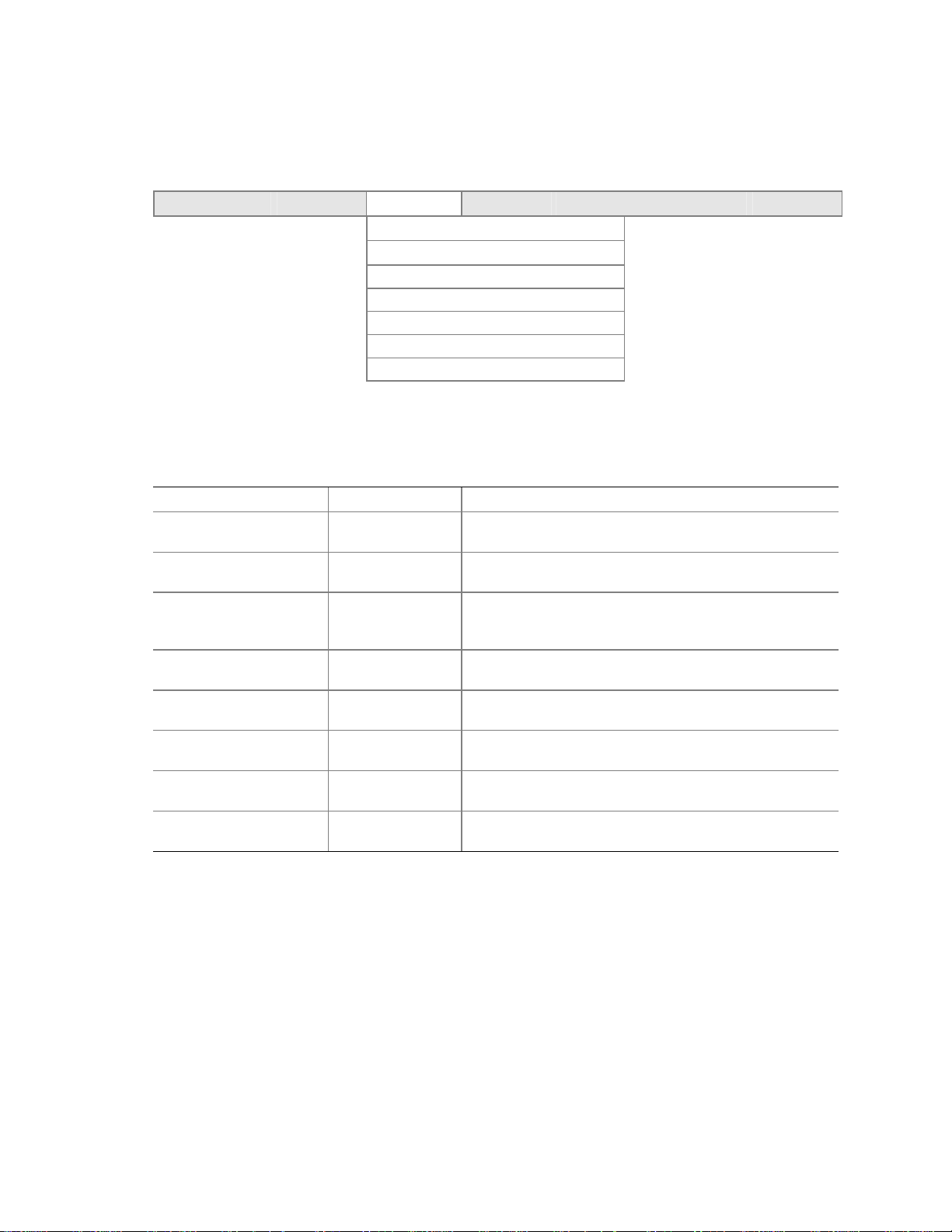

1. Feature Summary......................................................................................................12

2. Manufacturing Options...............................................................................................13

3. Specifications.............................................................................................................16

4. Supported Processors ...............................................................................................19

5. System Memory Configuration...................................................................................20

6. Supported Graphics Refresh Rates...........................................................................27

7. LAN Connector LED States .......................................................................................30

8. Effects of Pressing the Power Switch........................................................................31

9. Power States and Targeted System Power...............................................................32

10. ACPI Wake-up Devices and Events ..........................................................................33

11. APM Wake-up Devices and Events...........................................................................34

12. Fan Connector Descriptions.......................................................................................35

13. Wake on Ring Support for Modems...........................................................................36

vii

Page 8

Intel Desktop Board D810E2CB Technical Product Specification

14. System Memory Map .................................................................................................39

15. I/O Map...................................................................................................................... 40

16. DMA Channels...........................................................................................................42

17. PCI Configuration Space Map....................................................................................42

18. Interrupts....................................................................................................................43

19. PCI Interrupt Routing Map .........................................................................................44

20. PS/2 Mouse/Keyboard...............................................................................................47

21. USB Ports 0 and 1.....................................................................................................47

22. Parallel Port ...............................................................................................................47

23. VGA Port.................................................................................................................... 48

24. Serial Port A...............................................................................................................48

25. LAN (Optional)...........................................................................................................48

26. Audio Line In..............................................................................................................49

27. Audio Line Out...........................................................................................................49

28. Mic In Connector........................................................................................................49

29. ATAPI CD-ROM Connector (J1C1)............................................................................52

30. Telephony Connector (J2D1).....................................................................................52

31. Processor Fan Connector (J2J1)...............................................................................52

32. Power Connector (J6F1)............................................................................................53

33. Chassis Intrusion Connector (J6A2)...........................................................................53

34. Chassis Fan Connector (J7A1)..................................................................................53

35. PCI Bus Connectors (J3A2 and J3B1).......................................................................55

36. PCI IDE Connectors (J8D1, Primary and J7E1, Secondary)...................................... 56

37. Diskette Drive Connector (J6D1)................................................................................57

38. Front Panel Connector (J8A1) ...................................................................................59

39. States for a One Color Power LED............................................................................59

40. States for a Two Color Power LED ............................................................................59

41. Front Panel USB Connector (J8B1)...........................................................................60

42. BIOS Setup Configuration Jumper Settings (J4A1)...................................................62

43. Power Usage .............................................................................................................65

44. Fan DC Power Requirements....................................................................................66

45. Thermal Considerations for Components ..................................................................68

46. Environmental Specifications.....................................................................................69

47. Safety Regulations.....................................................................................................70

48. EMC Regulations.......................................................................................................70

49. Supervisor and User Password Functions.................................................................80

50. BIOS Setup Program Menu Functions.......................................................................81

51. BIOS Setup Program Function Keys..........................................................................82

52. Maintenance Menu ....................................................................................................82

53. Extended Configuration Submenu.............................................................................83

54. Main Menu.................................................................................................................84

55. Advanced Menu.........................................................................................................85

56. PCI Configuration Submenu ......................................................................................86

57. Boot Configuration Submenu.....................................................................................87

58. Peripheral Configuration Submenu............................................................................88

59. IDE Configuration Submenu ......................................................................................90

60. Primary/Secondary IDE Master/Slave Submenus......................................................91

61. Diskette Configuration Submenu...............................................................................93

viii

Page 9

Contents

62. Event Log Configuration Submenu............................................................................94

63. Video Configuration Submenu...................................................................................95

64. Security Menu............................................................................................................96

65. Power Menu............................................................................................................... 97

66. Boot Menu .................................................................................................................98

67. Exit Menu.................................................................................................................100

68. BIOS Error Messages..............................................................................................101

69. Uncompressed INIT Code Checkpoints...................................................................103

70. Boot Block Recovery Code Check Points................................................................103

71. Runtime Code Uncompressed in F000 Shadow RAM .............................................104

72. Bus Initialization Checkpoints ..................................................................................107

73. Upper Nibble High Byte Functions...........................................................................107

74. Lower Nibble High Byte Functions...........................................................................108

75. Beep Codes.............................................................................................................109

ix

Page 10

Intel Desktop Board D810E2CB Technical Product Specification

x

Page 11

1 Product Description

What This Chapter Contains

1.1 Overview....................................................................................................................12

1.2 Online Support...........................................................................................................16

1.3 Design Specifications.................................................................................................16

1.4 Processor................................................................................................................... 19

1.5 System Memory.........................................................................................................20

1.6 Intel

1.7 I/O Controller..............................................................................................................25

1.8 Graphics Subsystem..................................................................................................27

1.9 Audio Subsystem.......................................................................................................28

1.10 Hardware Management Subsystem...........................................................................29

1.11 LAN Subsystem (Optional).........................................................................................30

1.12 Power Management Features.................................................................................... 31

®

810E Chipset....................................................................................................21

11

Page 12

Intel Desktop Board D810E2CB Technical Product Specification

1.1 Overview

1.1.1 Feature Summary

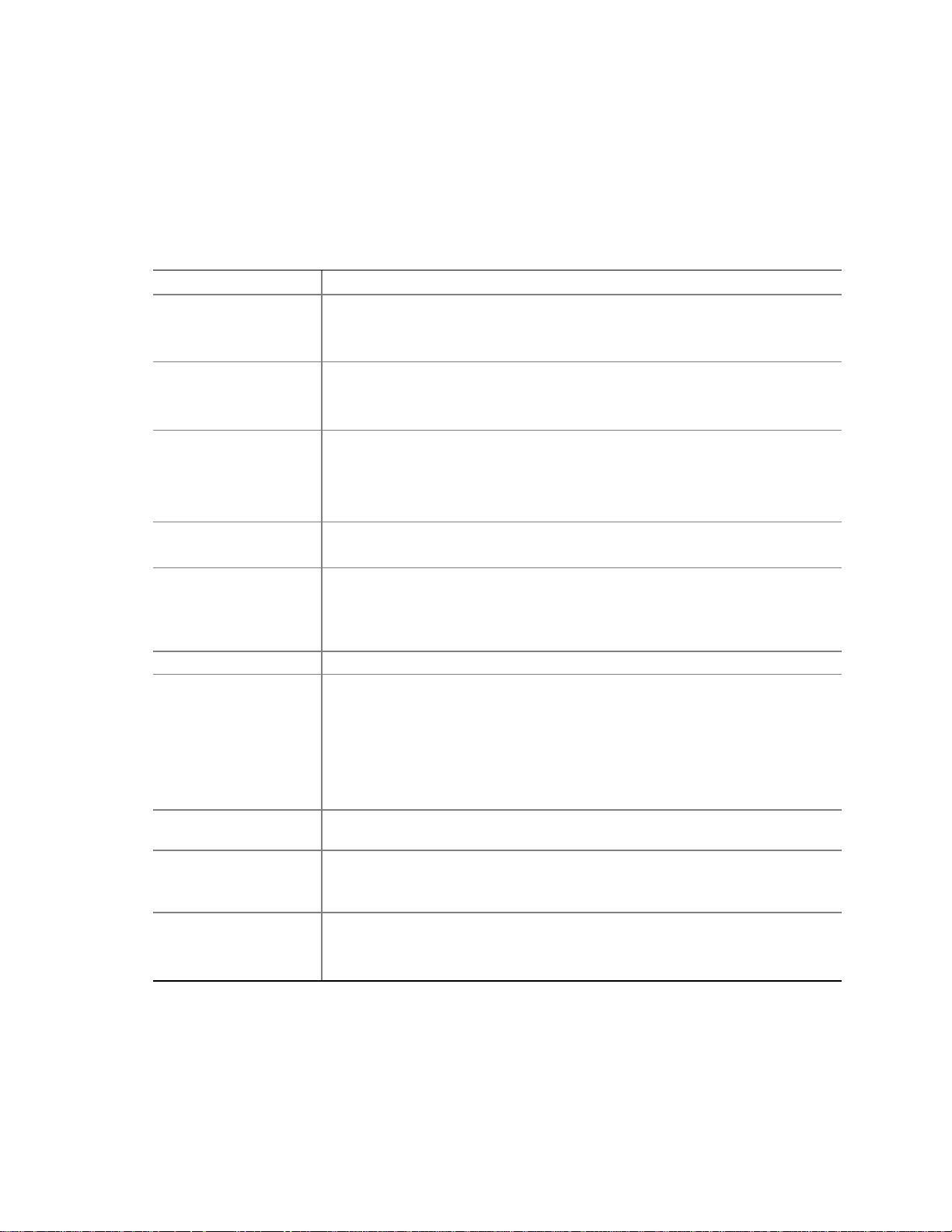

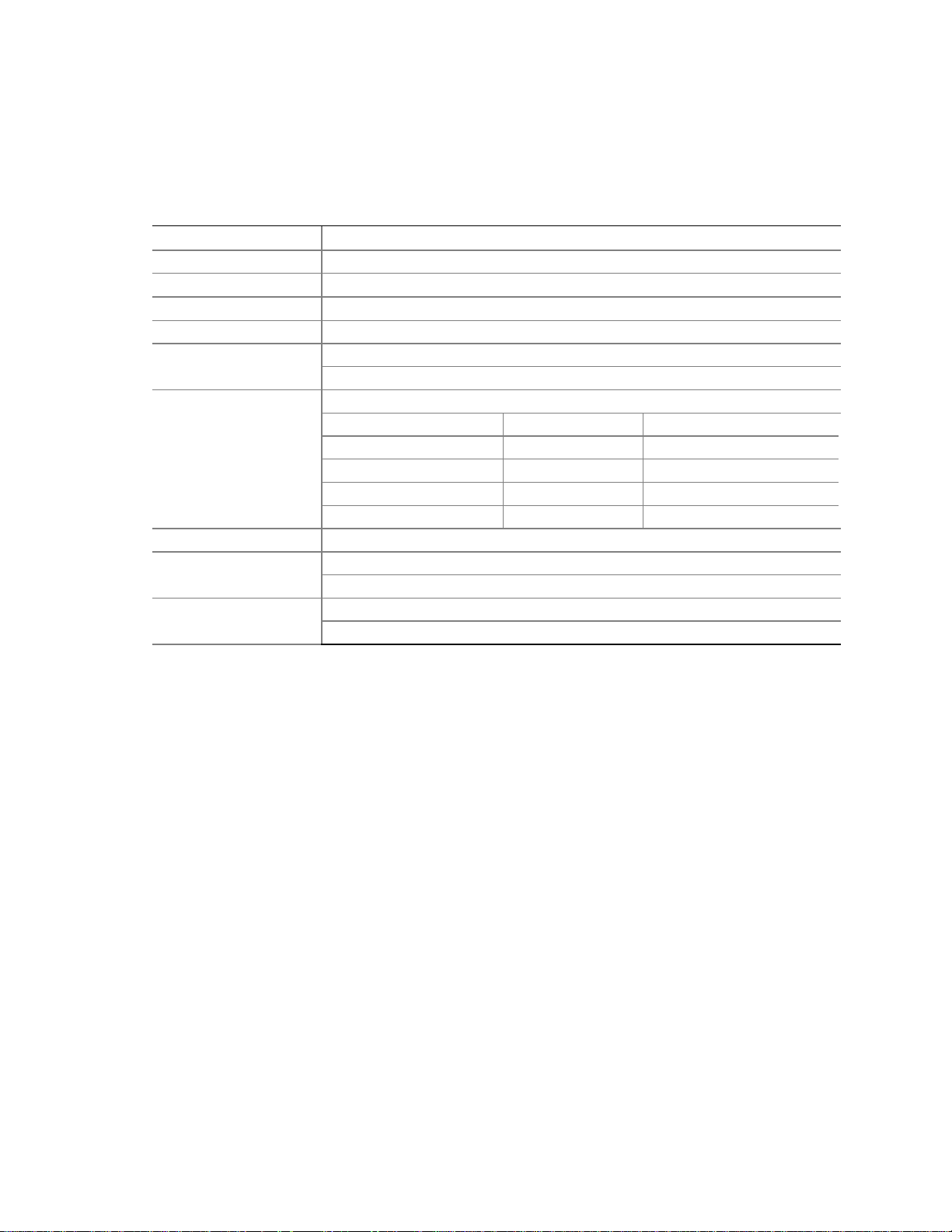

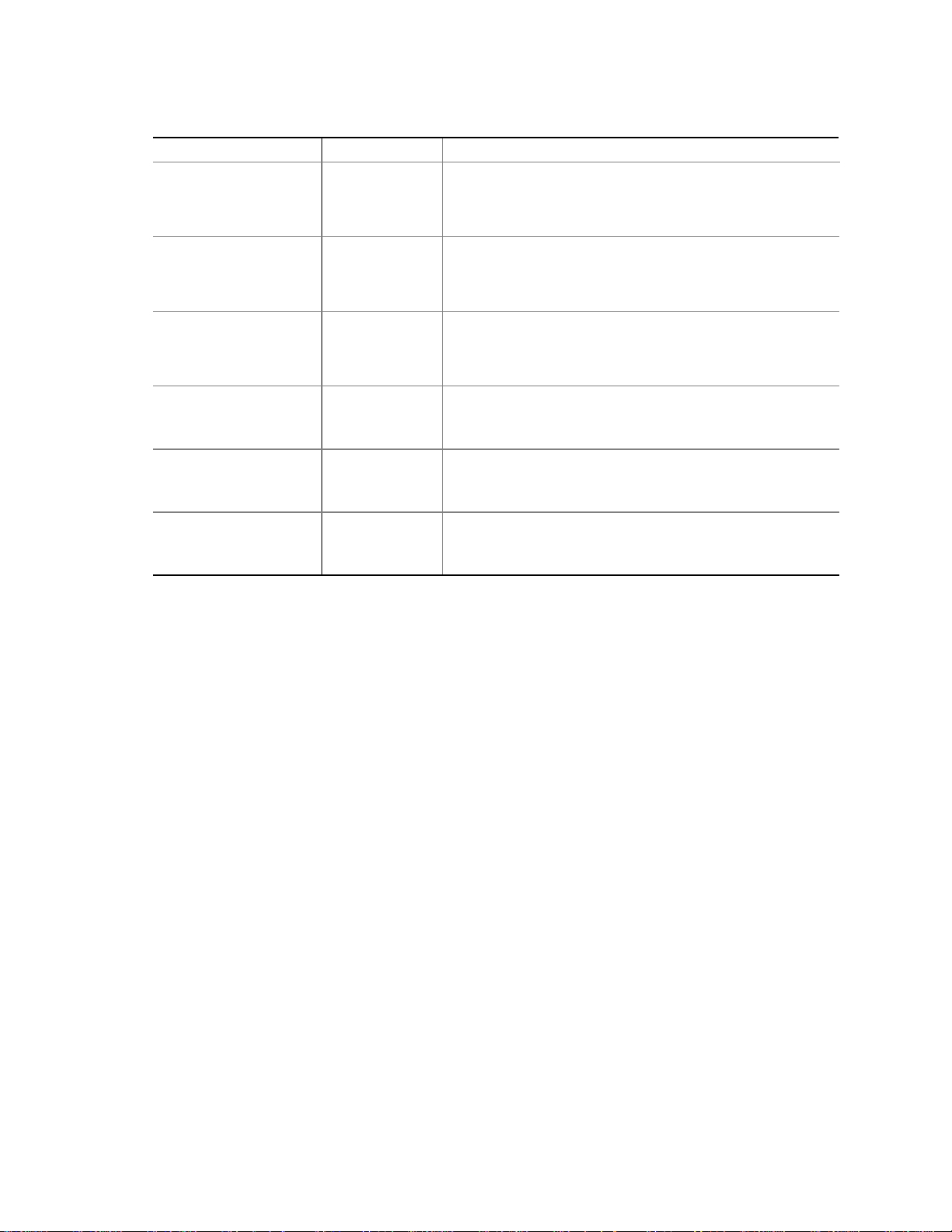

Table 1 summarizes the D810E2CB board’s major features.

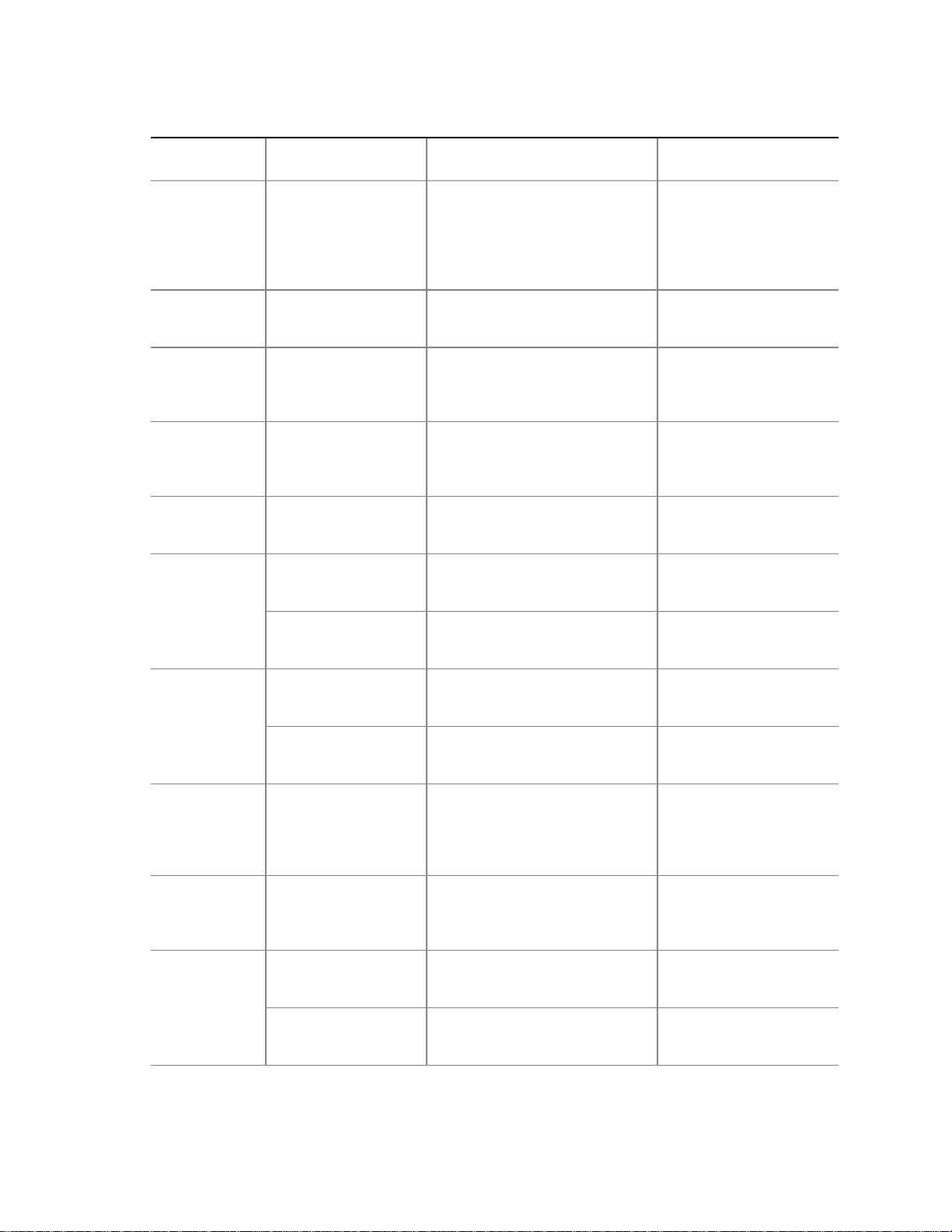

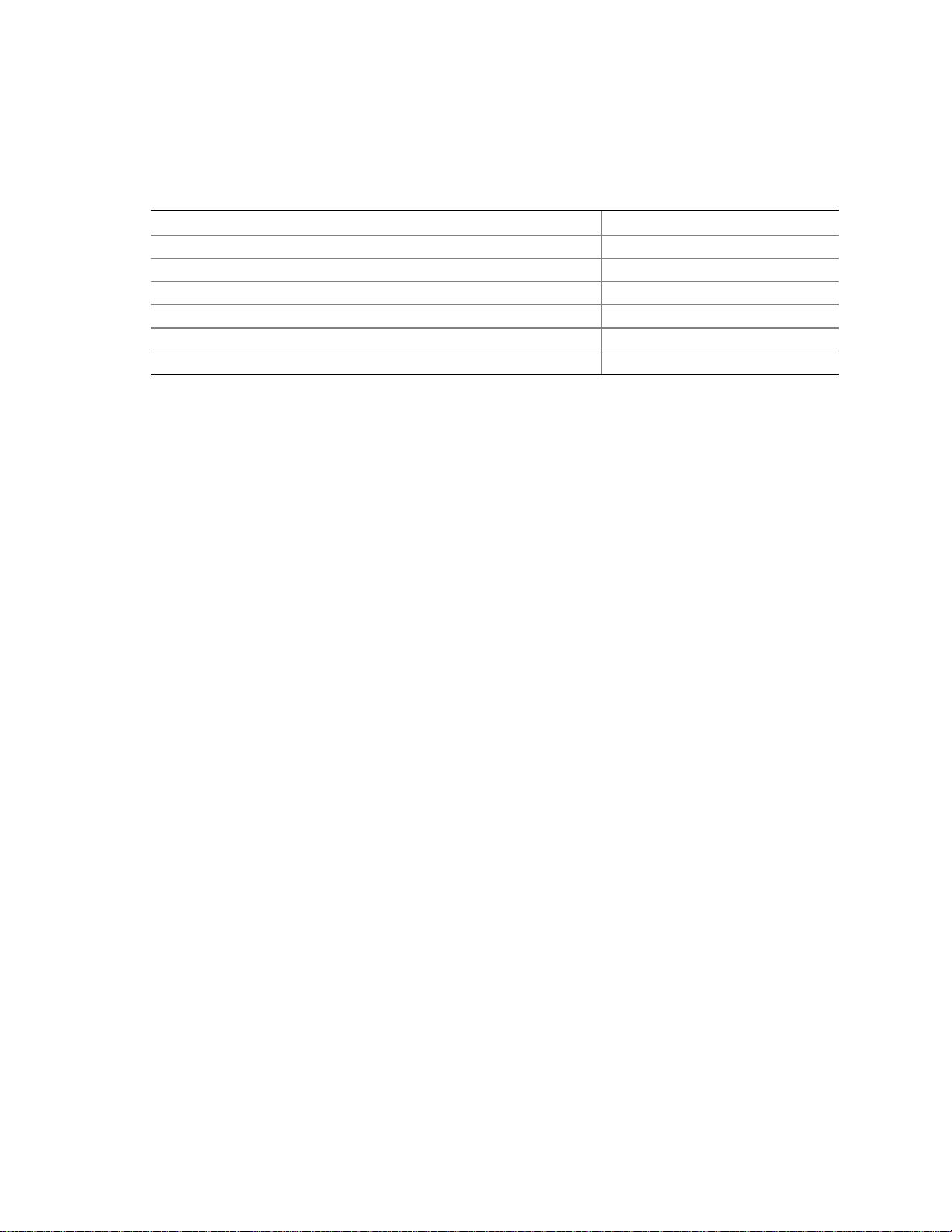

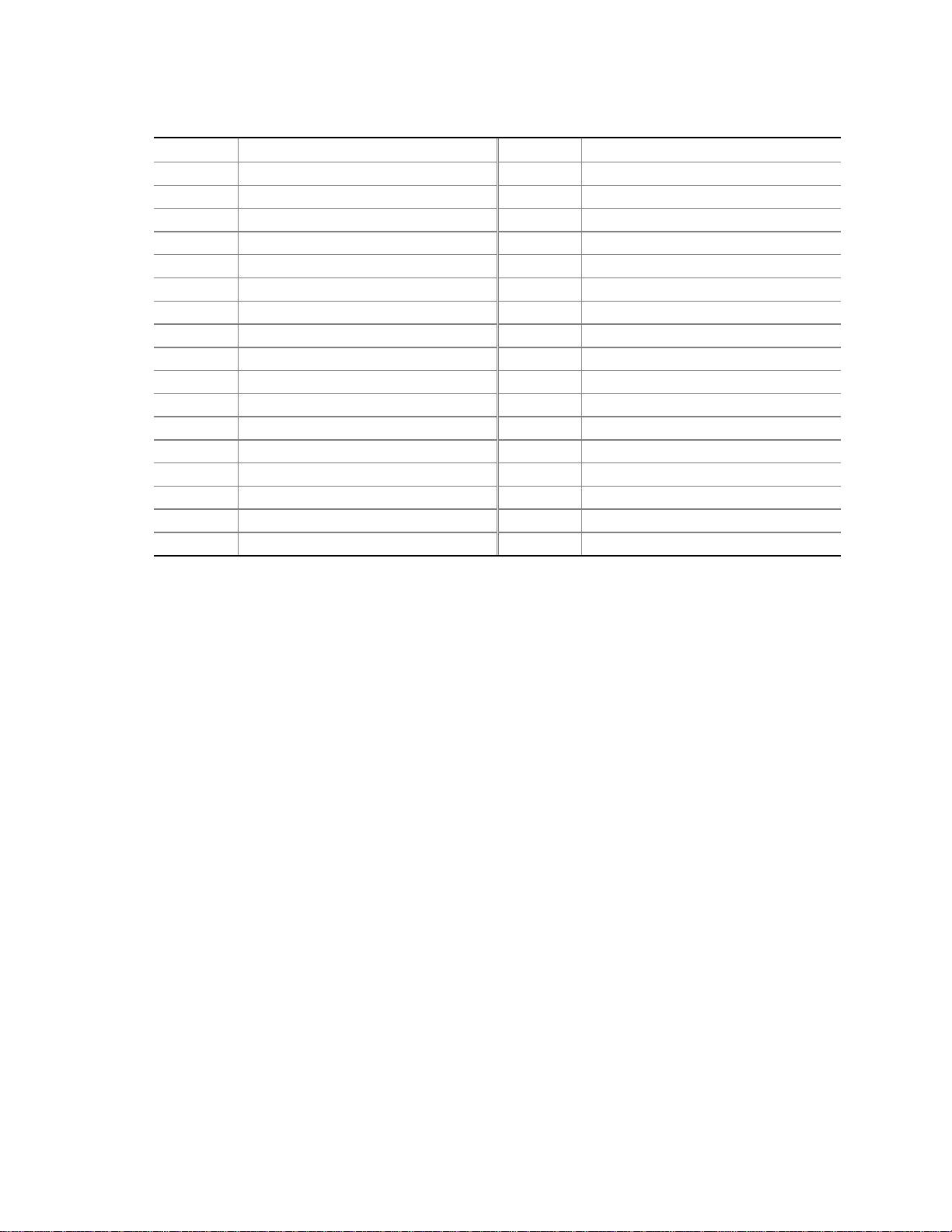

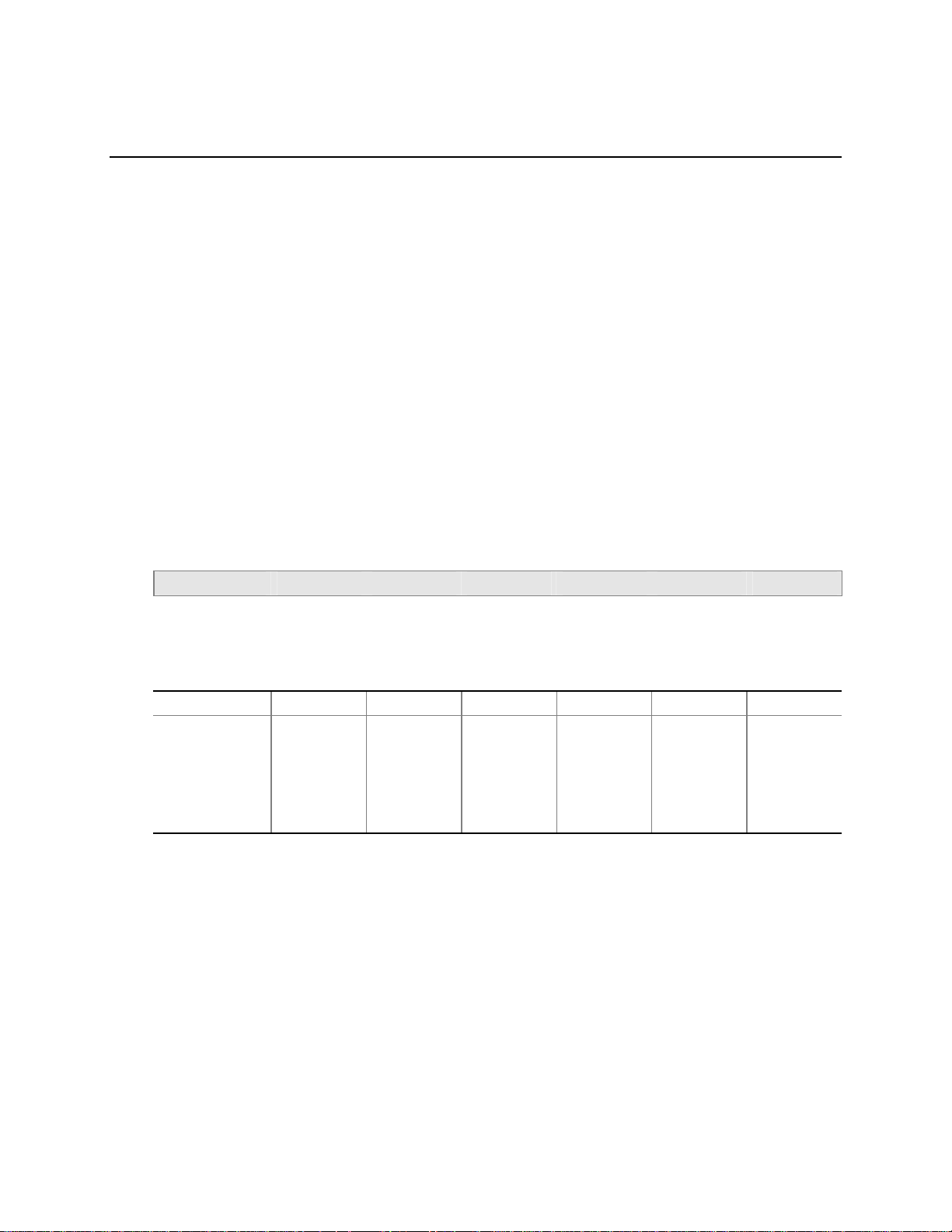

Table 1. Feature Summary

Form Factor

Processor

Memory

Chipset

Direct AGP Video

Audio

I/O Control

Peripheral Interfaces

Expansion

Capabilities

BIOS

Instantly Available PC

FlexATX (9.00 inches by 7.50 inches)

Support for either an:

®

• Intel

• Intel

• Two 168-pin dual inline memory module (DIMM) sockets

• Supports up to 512 MB of 100 MHz non-ECC synchronous DRAM (SDRAM)

• Support for serial presence detect (SPD) and non-SPD DIMMs

Intel

• Intel

• Intel

• SST 49LF004A 4 Mbit Firmware Hub (FWH)

• Intel 82810E GMCH

• VGA port connector on back panel

Audio Codec ’97 (AC’97) compatible audio subsystem, consisting of the

following:

• Intel 82801BA ICH2 (AC link output)

• CS4201 analog codec

LPC47M102 Low Pin Count (LPC) I/O controller

• Four universal serial bus (USB) ports (two back panel, two front panel)

• Two IDE interfaces with Ultra DMA, ATA-66/100 support

• One diskettedrive interface

• One serial port

• One parallel port

• PS/2

Two PCI-bus add-in card connectors

• Intel/AMI BIOS stored in an SST 49LF004A 4 Mbit firmware hub (FWH)

• Support for Advanced Configuration and Power Interface (ACPI), Advanced

• Support for

• Suspend-to-RAM support

• Wake from USB ports

Pentium®III processor with 256 KB L2 cache (in an FCPGA package)

®

Celeron™processor with 128 KB L2 cache (in a PGA package)

®

810E chipset, consisting of:

®

82810E Graphics/Memory Controller Hub (GMCH)

®

82801BA I/O Controller Hub (ICH2)

†

keyboard and mouse ports

Power Management (APM), Plug and Play, and SMBIOS

PCI Local Bus Specifi cation

, Revision 2.2

NOTE

✏

The D810E2CB board is designed to support only USB-aware operating systems.

12

Page 13

Product Description

For information about Refer to

The board’s compliance level with ACPI, APM, Plug and Play, and SMBIOS Table 3, page 16

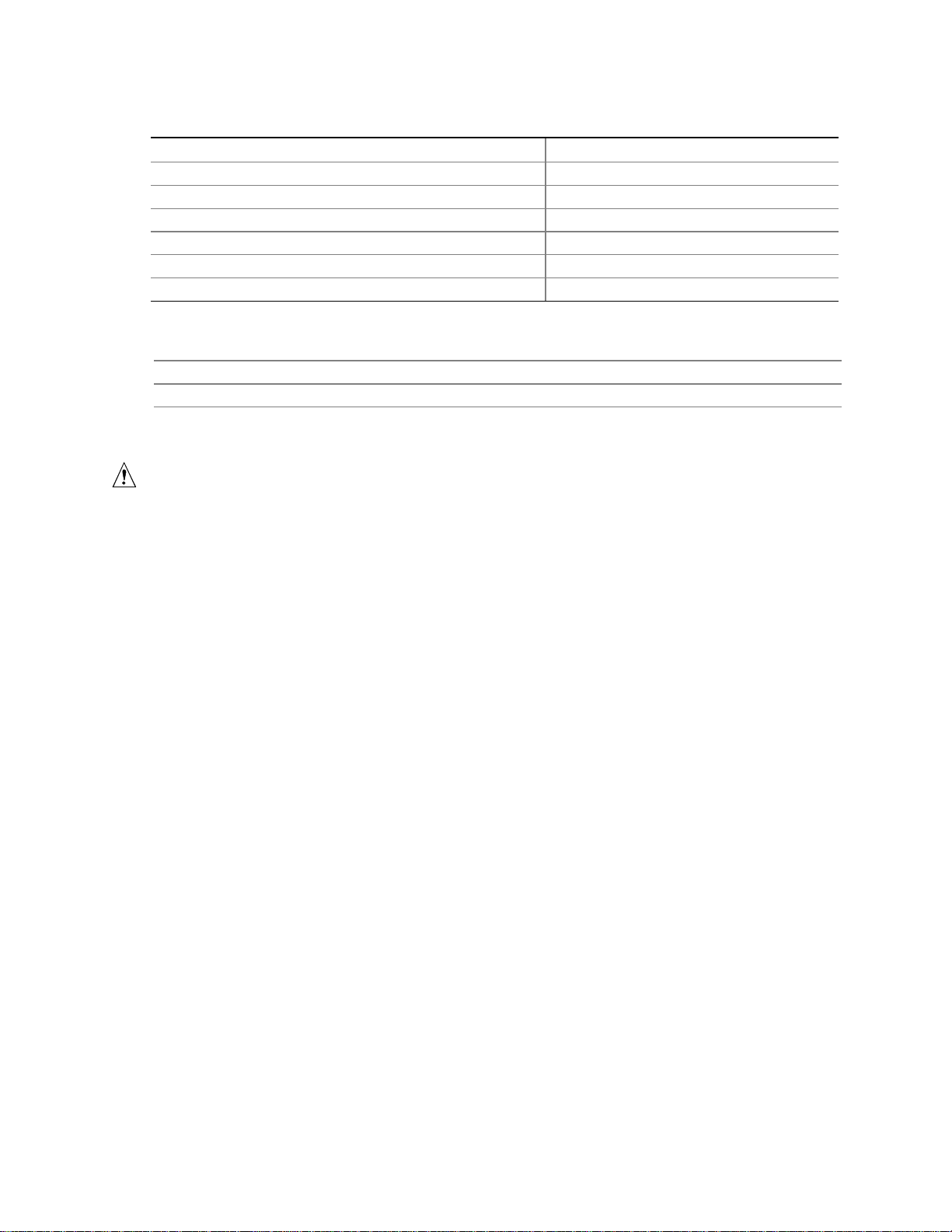

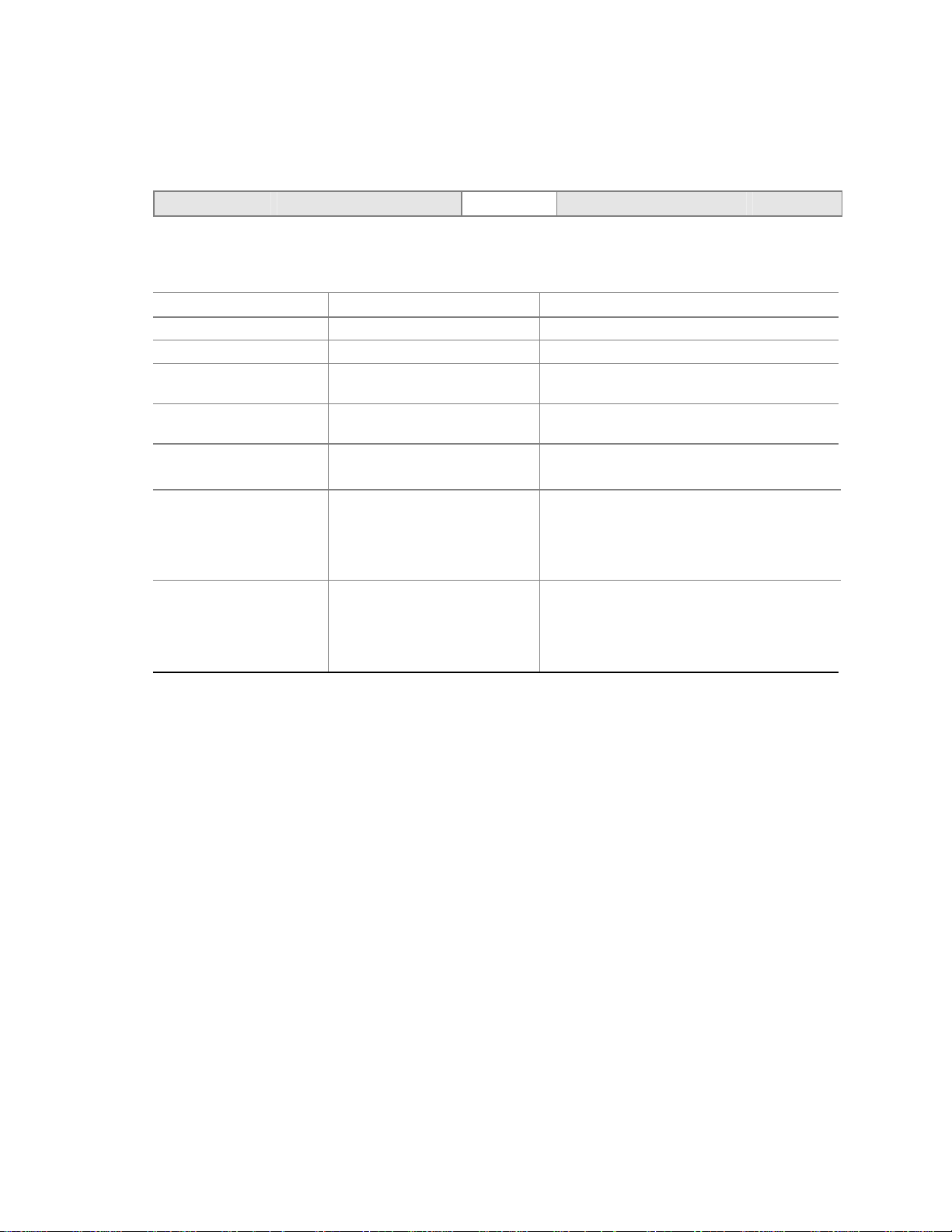

1.1.2 Manufacturing Options

Table 2 describes the D810E2CB board’s manufacturing options. Not every manufacturing option

is available in all marketing channels. Please contact your Intel representative to determine which

manufacturing options are available to you.

Table 2. Manufacturing Options

LAN Intel®82562ET 10/100 Mbit/sec Platform LAN Connect (PLC) device

Hardware monitor

component

Hardware monitor component features include:

• Voltage sense to detect out of range power supply voltages

• Thermal sense to detect out of range thermal values

13

Page 14

Intel Desktop Board D810E2CB Technical Product Specification

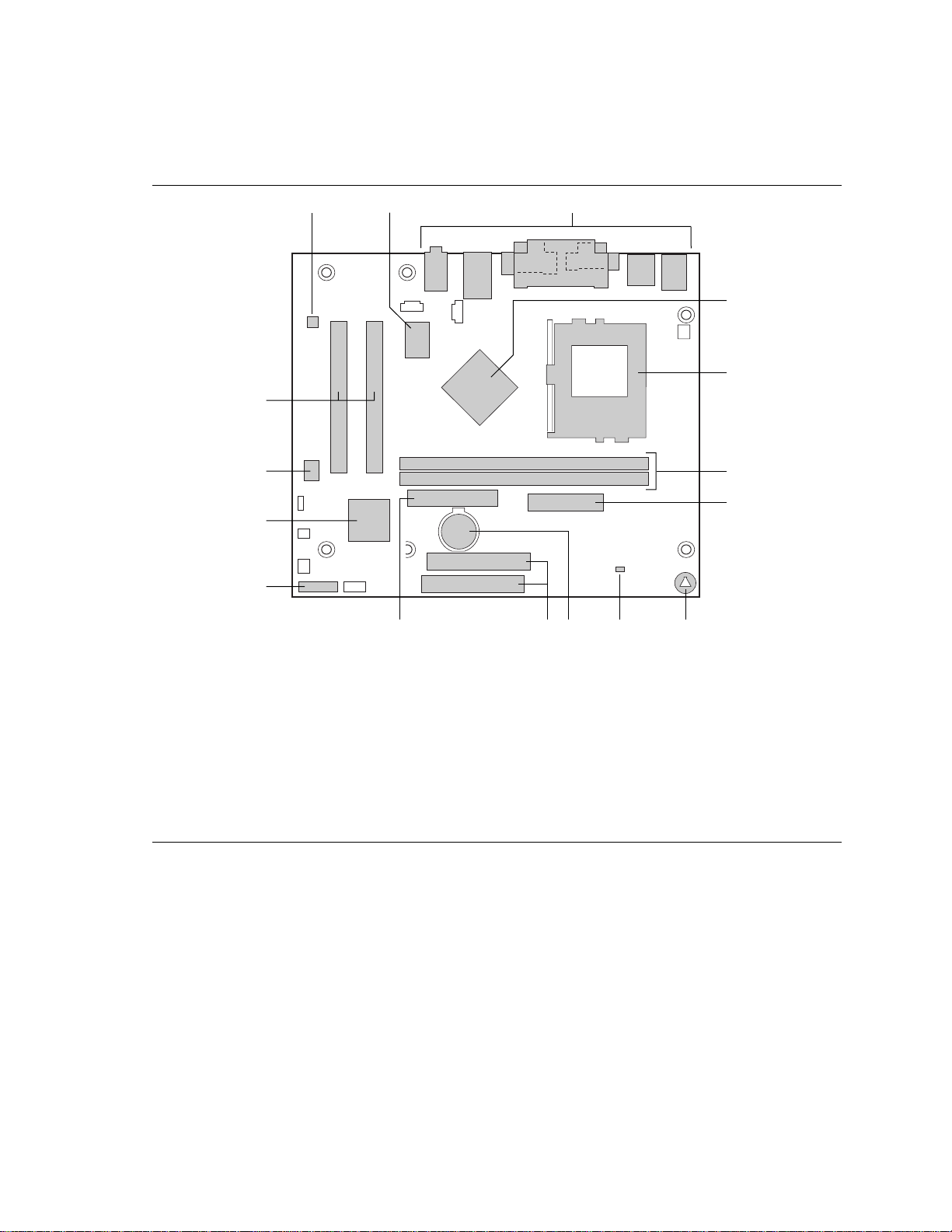

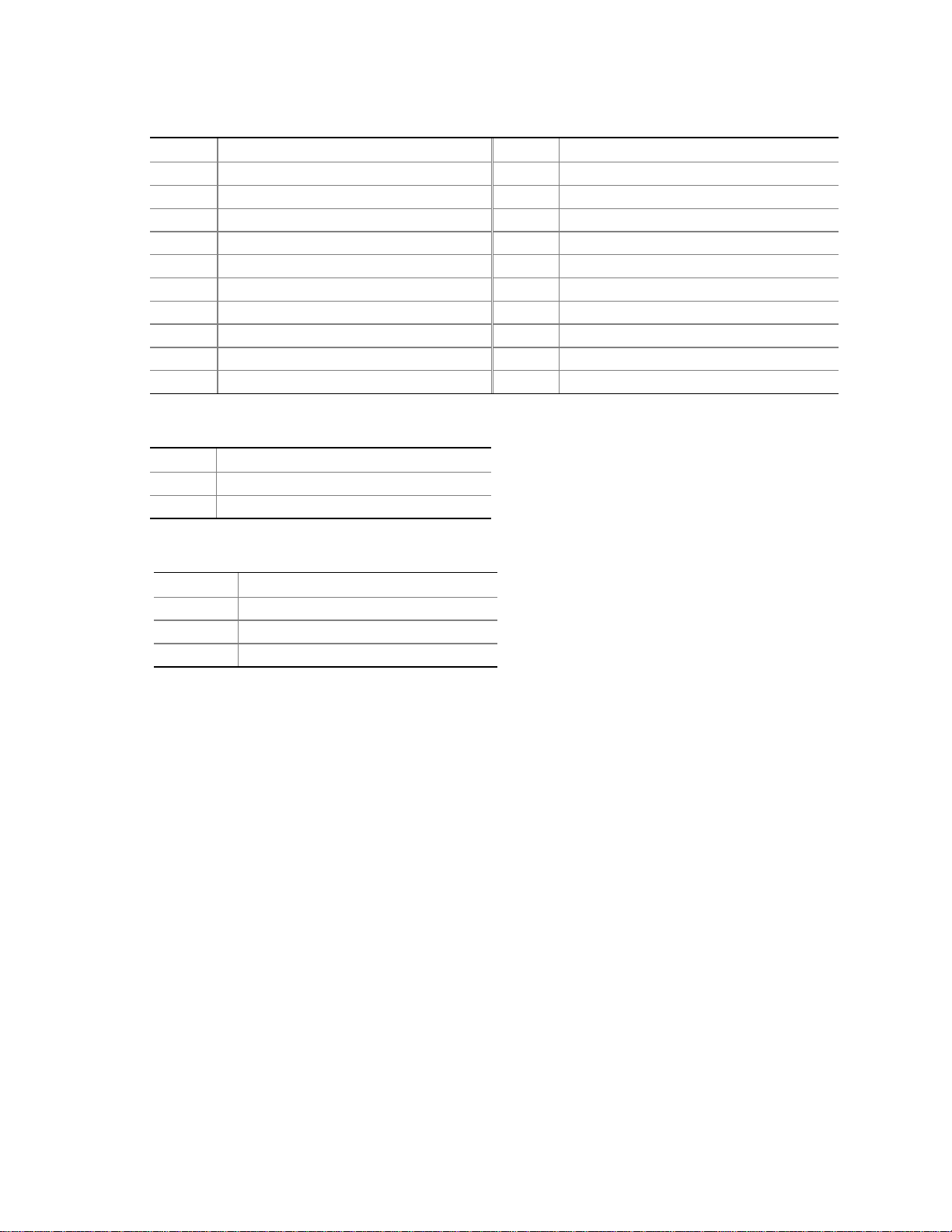

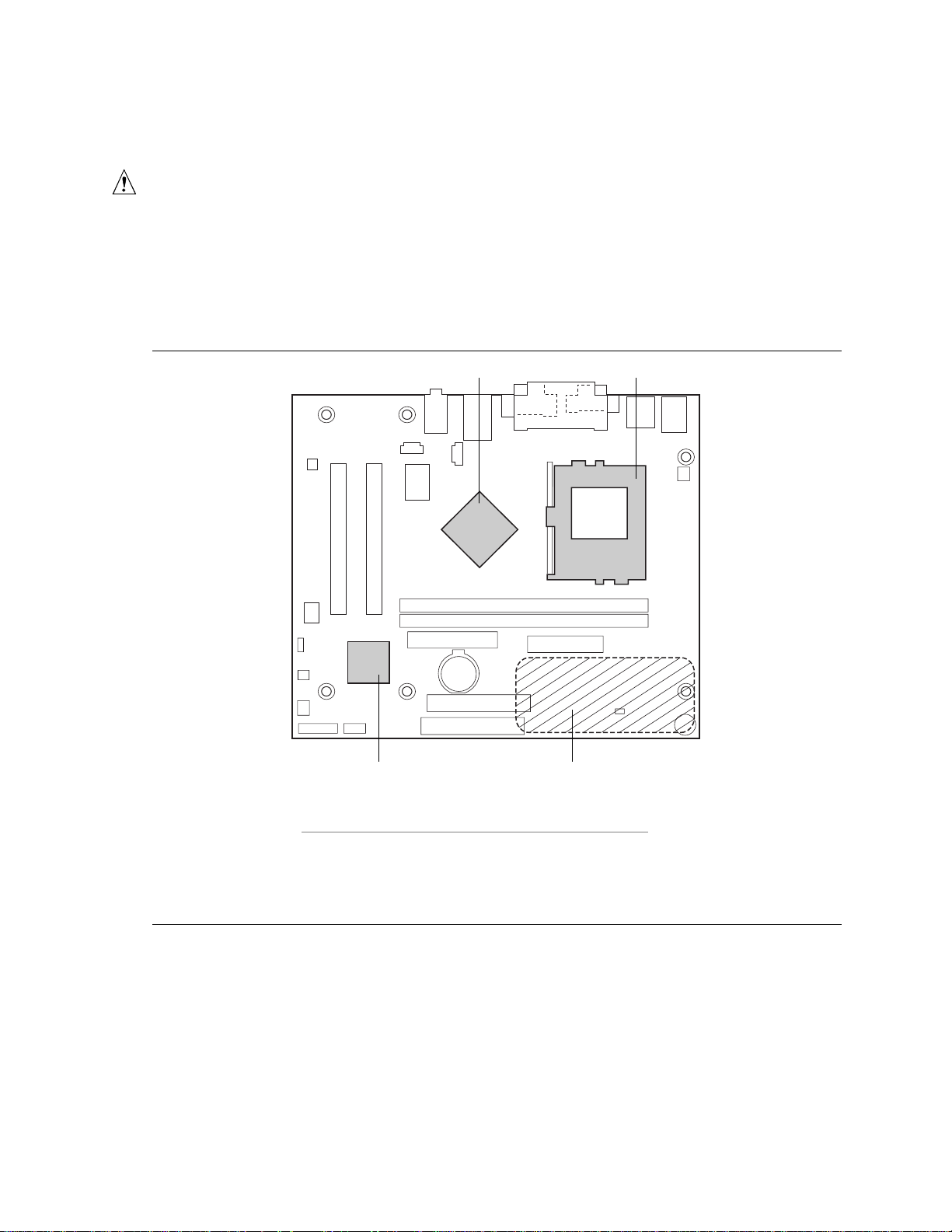

1.1.3 D810E2CB Board Layout

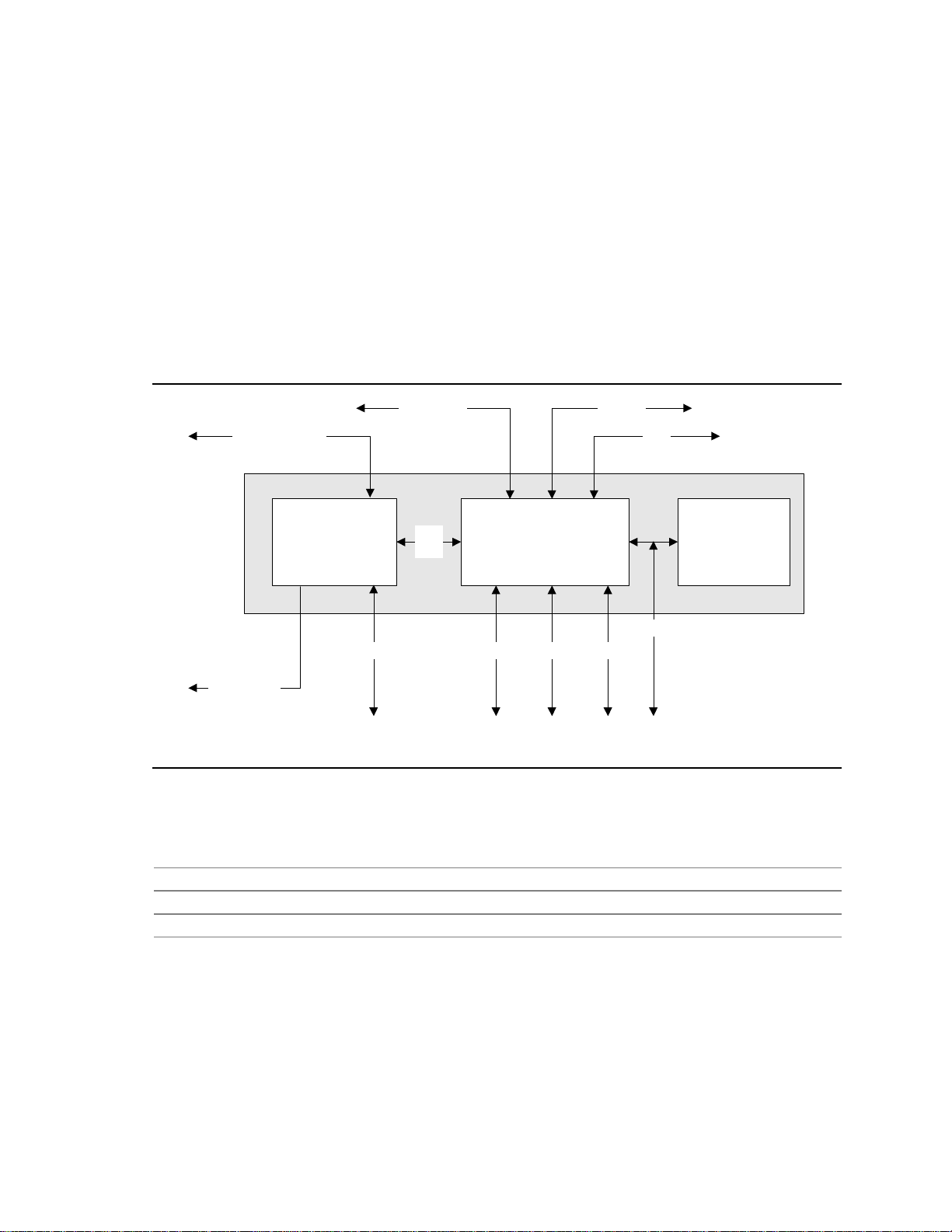

Figure 1 shows the location of the major components on the D810E2CB board.

M

A B

C

D

E

P

O

F

G

N

L

K J HI

OM11019

A CS4201 Audio Codec I Hardwaremonitor

B SMSC LPC47M102 I/O Controller J Battery

C Back panel connectors K IDE connectors

D Intel 82810E GMCH (Graphics/Memory Controller Hub) L Diskette drive connector

E Processor socket M Front panel connector

F DIMM sockets N Intel 82801BA ICH2 (I/O Controller Hub)

G Power connector O SST 49LF004A 4M Mbit Firmware Hub

H Speaker P PCI bus add-in card connectors

Figure 1. D810E2CB Board Components

14

Page 15

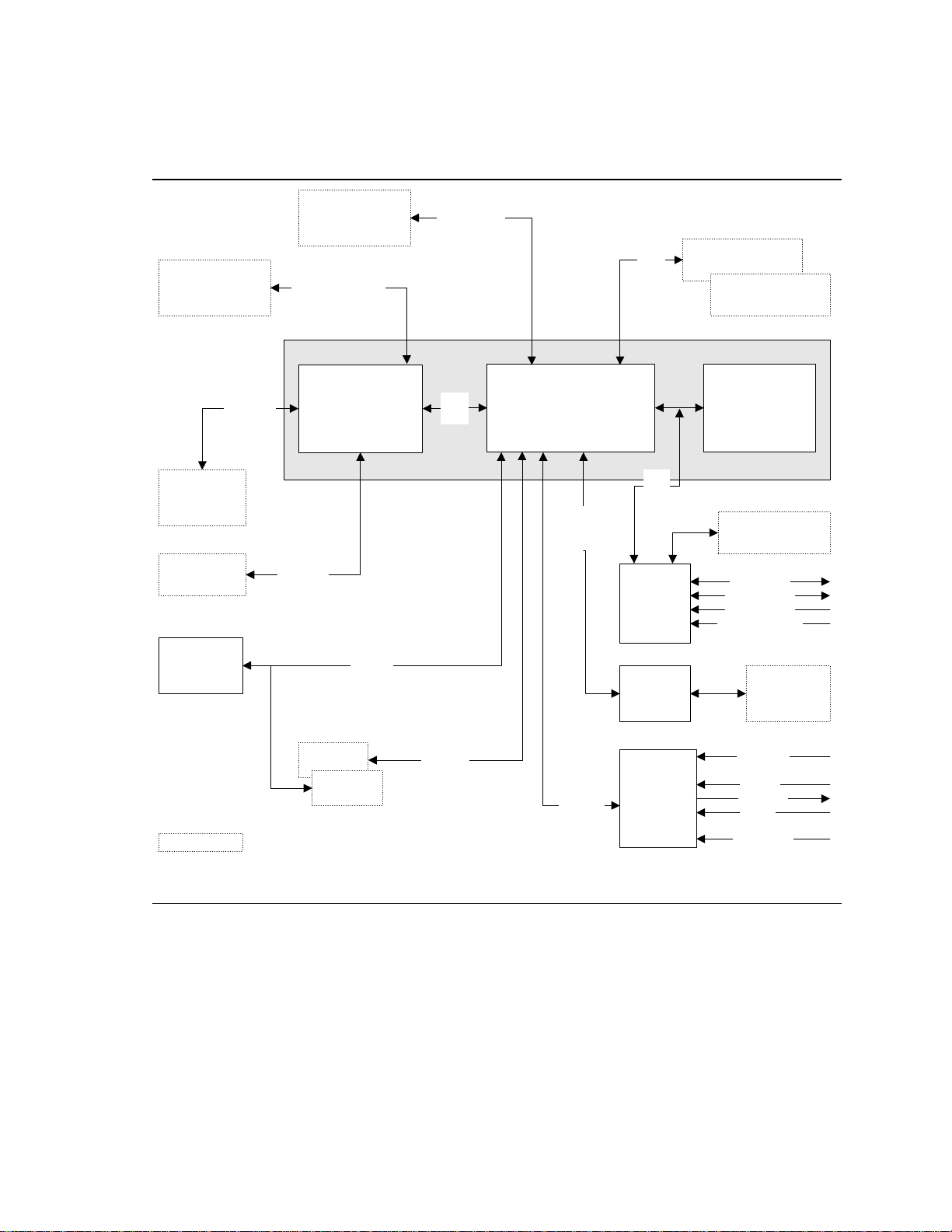

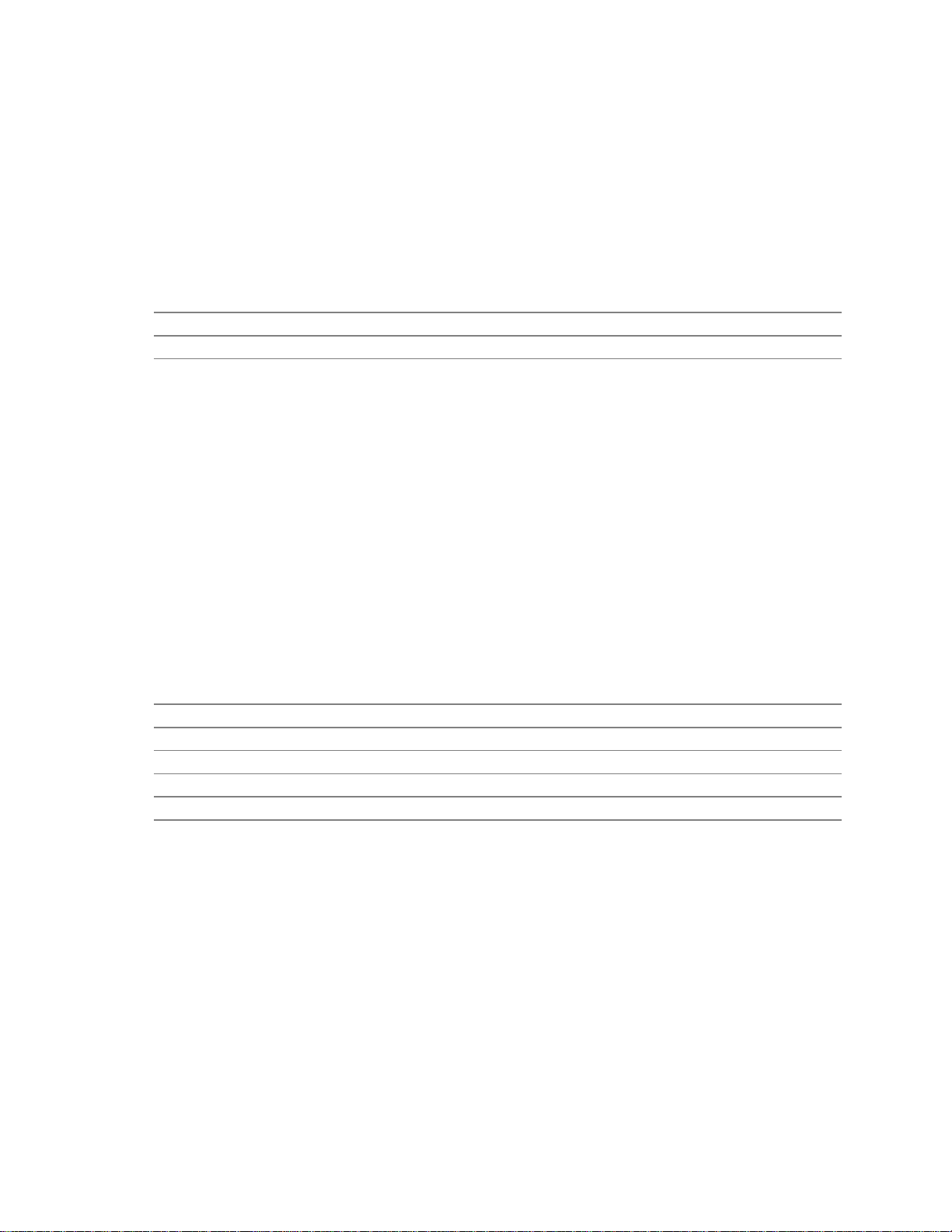

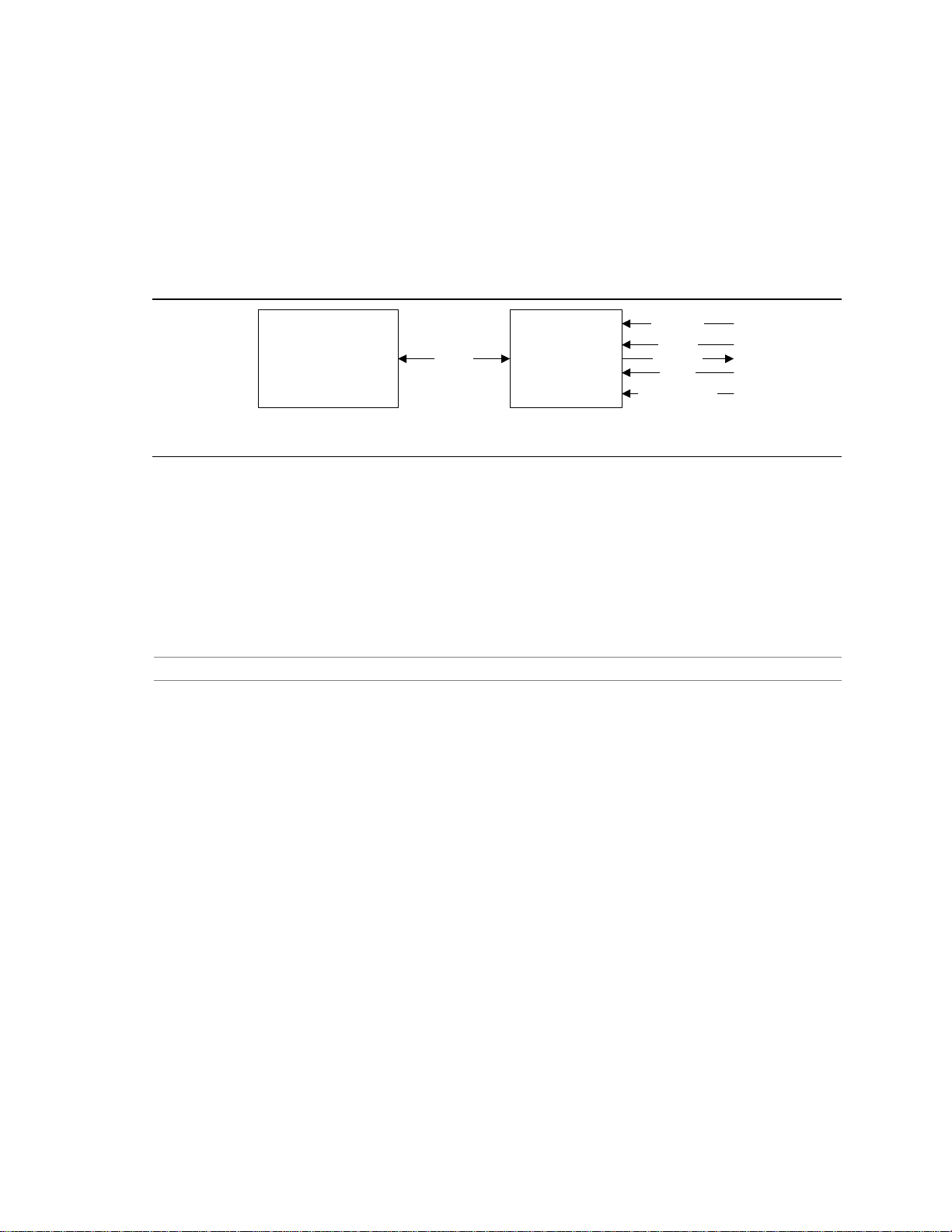

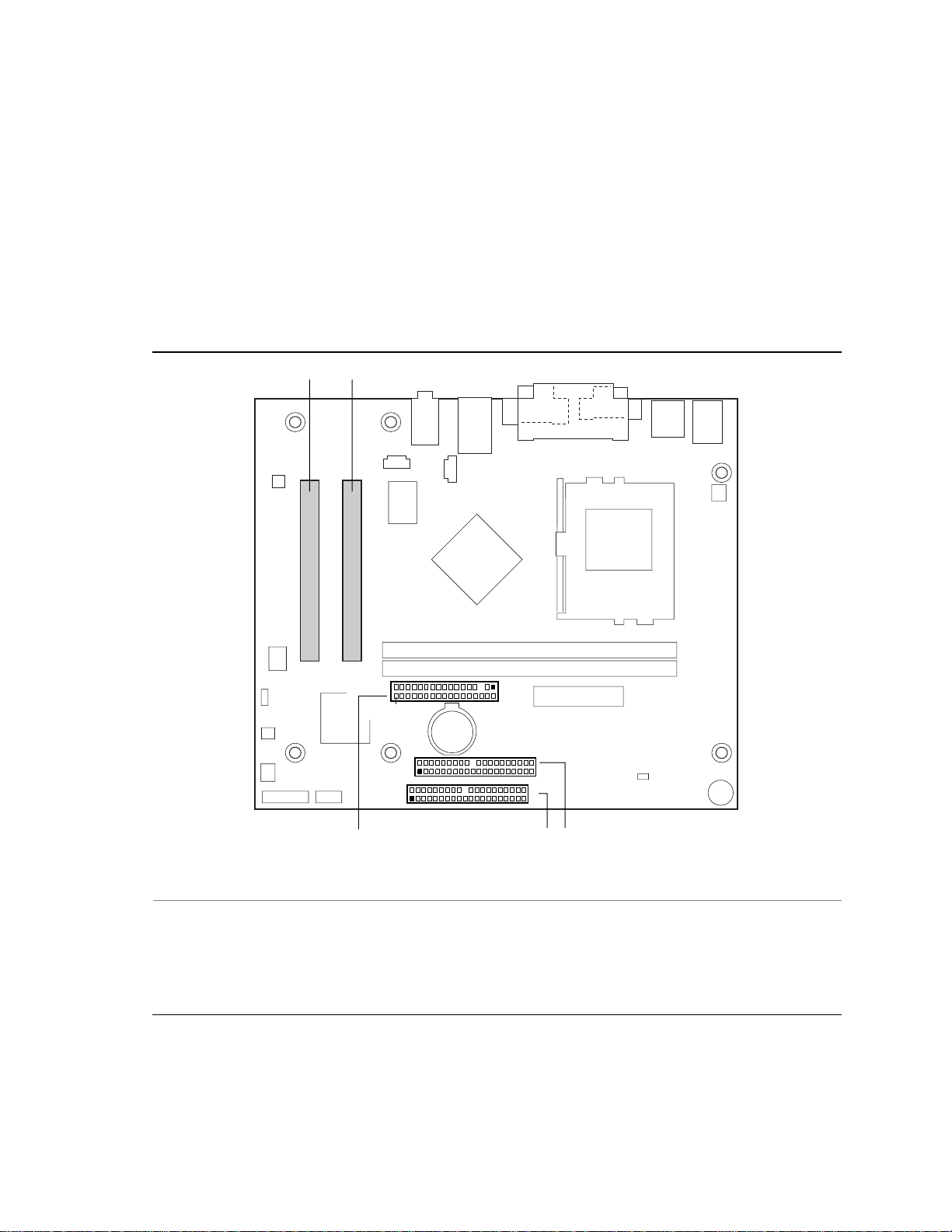

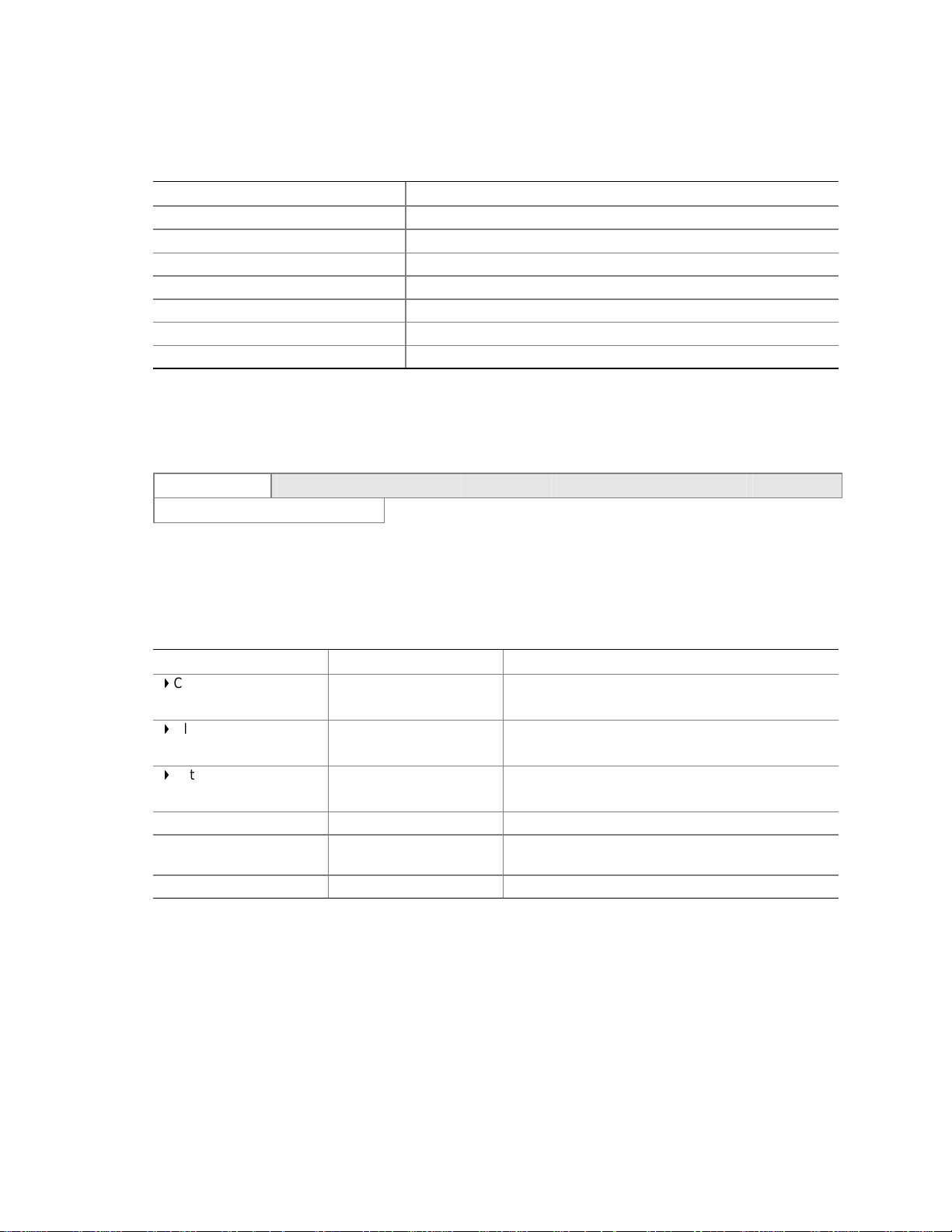

1.1.4 Block Diagram

Figure 2 is a block diagram of the major functional areas of the D810E2CB board.

Product Description

Processor

Socket

DIMM Banks

0and1

VGA Port

Hardware

Monitor

100 MHz

SDRAM

Bus

Primary/

SecondaryIDE

66/100/133 MHz

SystemBus

82810E

Graphics Memory

Controller Hub

(GMCH)

Display

Interface

SMBus

ATA-66/100

810E Chipset

AHA

Bus

82801BA

I/O Controlle rHub

(ICH2)

CSMA/CD

Unit

Interface

USB

LPC

Bus

LPC I/O

Controller

Physical

Laye r

Interface

USB Ports 0 and1

USB Ports 2 and3

SST 49LF004A

Firmw are Hub

(FWH)

DisketteDrive

Connector

Serial Port

Parallel Port

PS/2 Mouse

PS/2 Keyboard

LAN

Connector

(optional)

PCISlot1

PCISlot2

= connector or socket

PCI Bus

AC Link

Figure 2. Block Diagram

CS4201

Audio

Code c

CD-ROM

Line In

Line Out

Mic In

Telephony

OM11130

15

Page 16

Intel Desktop Board D810E2CB Technical Product Specification

1.2 Online Support

To find information about… Visit this World Wide Web site:

Intel’s D810E2CB board under “Product Info” or

“Customer Support”

Processor data shee ts http://www.intel.com/design/litcentr

Proper date access in systems with Intel

motherboards

ICH2 addressing http://developer.intel.com/design/chipsets/datashts

Custom splash screens http://intel.com/design/motherbd/gen_indx.htm

Audio softwareand utilities http://www.intel.com/design/motherbd

LAN software and drivers http://www.intel.com/design/motherbd

®

http://www.intel.com/design/motherbd

http://support.intel.com/support/motherboards/deskto

p

http://support.intel.com/support/year2000

1.3 Design Specifications

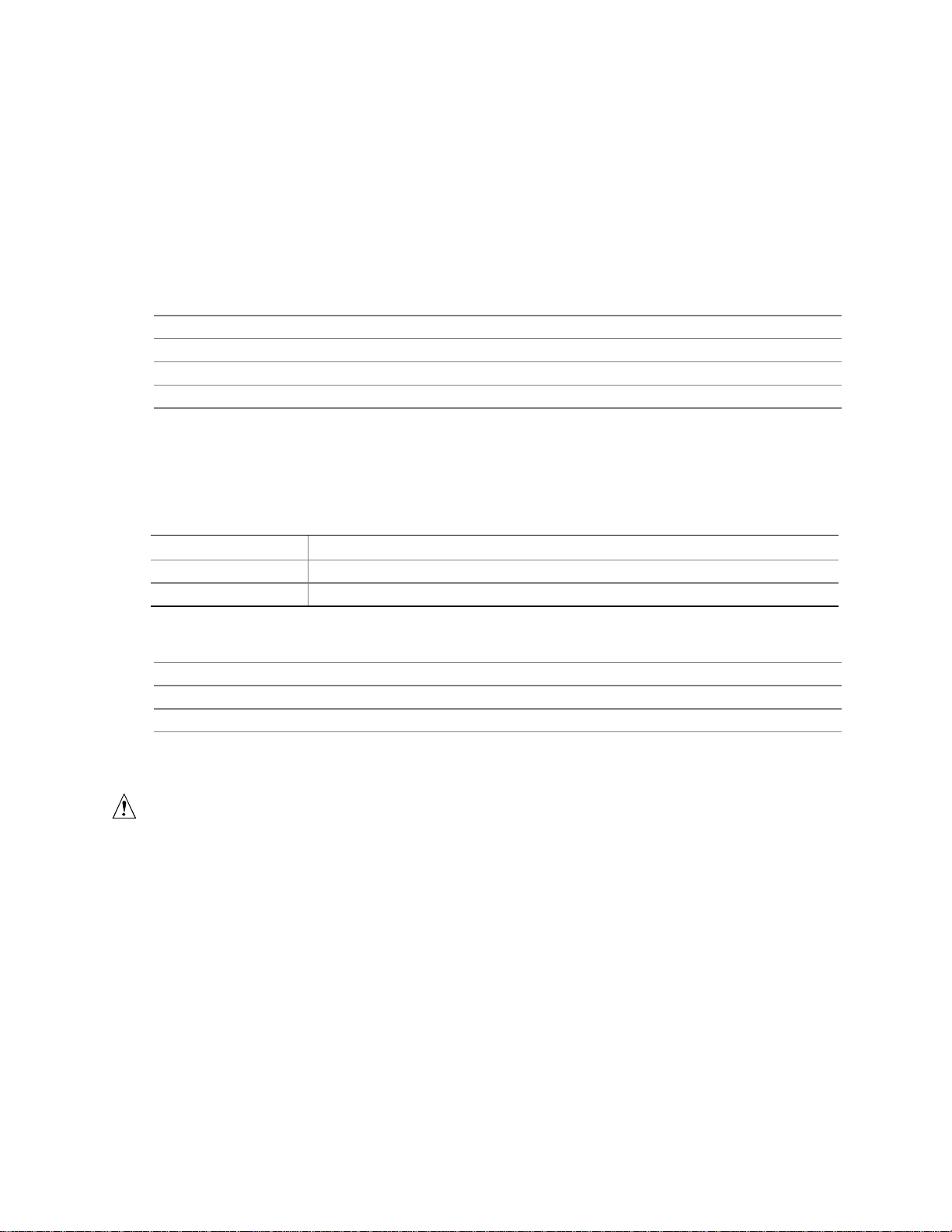

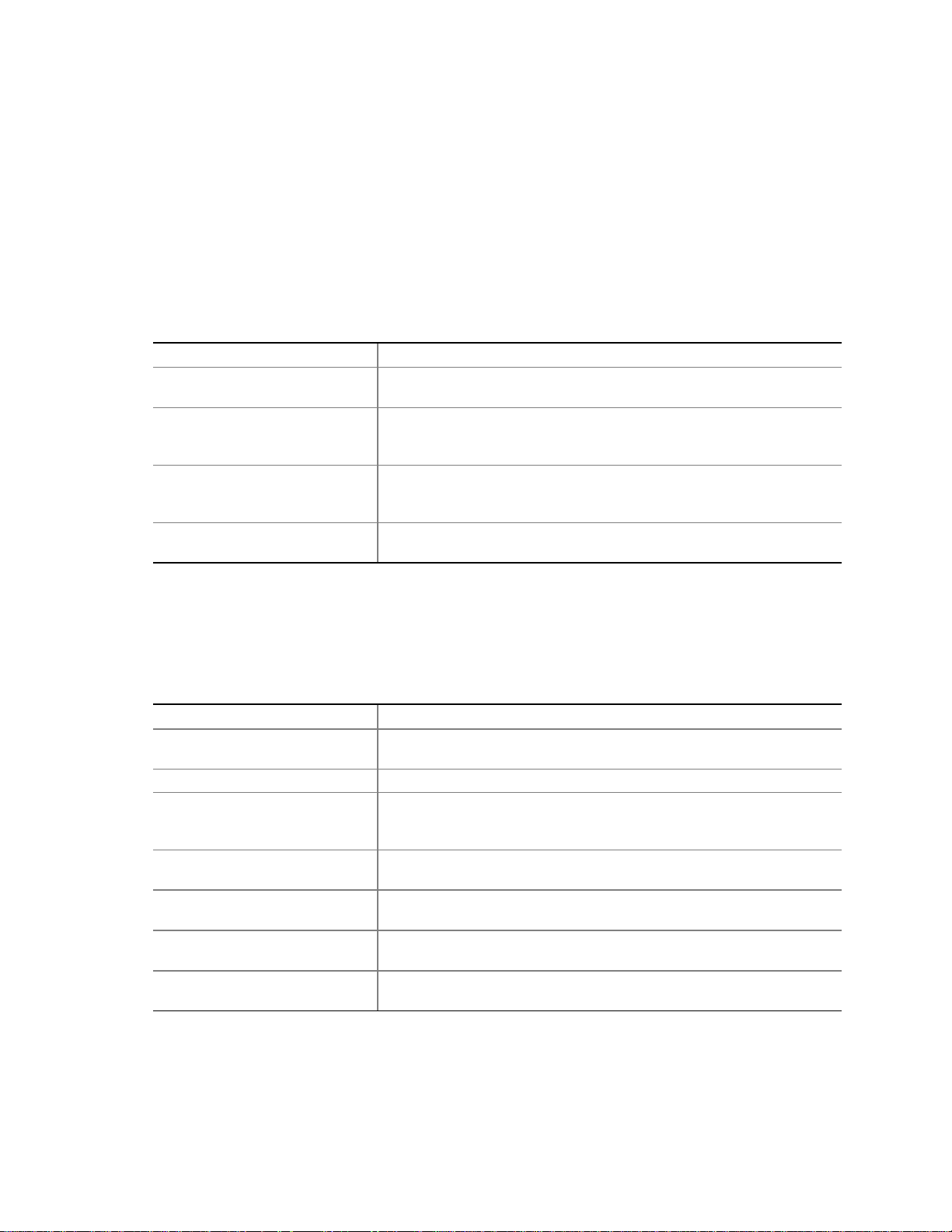

Table 3 lists the specifications applicable to the D810E2CB board.

Table 3. Specifications

Reference

Name

AC ‘97

ACPI

AGP

AMI BIOS

APM

ATA-3

Specification

Title

Audio Codec ‘97

Advanced Configuration

and Power Interface

Specification

Accelerated Graphics Port

Interface Specification

(2X only)

American Megatrends

BIOS Specification

Advanced Power

Management Specification

Information Technology AT Attachment-3 Interface,

X3T10/2008D

Version, Revision Date,

and Ownership

Version 2.1,

May 1998,

Intel Corporation.

Version 1.0b,

July 1, 1998,

Intel Corporation,

Microsoft Corporation,

and Toshiba Corporation.

Version 2.0,

May 4, 1998,

Intel Corporation.

AMIBIOS99,

1999

American Megatrends, Inc.

Version 1.2,

February 1996,

Intel Corporation

and Microsoft Corporation.

Version 6,

October 1998,

ASC X3T10.

This specification is

available from:

ftp://download.intel.com/

pc-supp/platform/ac97

http://www.teleport.com/~acpi/

the Accelerated Graphics

Implementers Forum at:

http://www.agpforum.org/

http://www.amibios.com, or

http://www.ami.com/download

/

amibios99.pdf

http://www.microsoft.com/hwd

ev/busbios/amp_12.htm

ATA Anonymous FTP Site:

ftp://www.dt.wdc.com/ata/

ata-3/

continued

16

Page 17

Table 3. Specifications (continued)

Product Description

Reference

Name

ATAPI

Specification

Title

Information

Technology AT

Attachment with

Packet Interface

Extensions

T13/1153D

ATX

El Torito

ATX Specification

Bootable CD-ROM

format specification

FlexATX FlexATX Addendum to

the microATX

Specification,

Version 1.0

LPC

Low Pin Count

Interface Specification

MicroATX

microATX

Motherboard Interface

Specification

SFX Power Supply

Design Guide

PCI

PCI Local Bus

Specification

PCI Bus Power

Management Interface

Specification

Plug and Play

Plug and Play BIOS

Specification

SDRAM

DIMMs

(64- and 72bit)

PC SDRAM

Unbuffered DIMM

Specification

PC SDRAM DIMM

Specification

PC Serial Presence

Detect (SPD)

Specification

Version, Revision Date and

Ownership

Version 18,

August 19, 1998,

Contact: T13 Chair, Seagate

Technology.

Version 2.01,

February 1997,

Intel Corporation.

Version 1.0,

January 25, 1995,

Phoenix Technologies Ltd.

and IBM Corporation.

Version 1.0

March 1999,

Intel Corporation.

Version 1.0,

September 29, 1997,

Intel Corporation.

Version 1.0, December 1997,

Intel Corporation.

Version 1.0, December 1997,

Intel Corporation.

Version 2.2,

December 18, 1998,

PCI Special Interest Group.

Version 1.1,

December 18, 1998,

PCI Special Interest Group.

Version 1.0a,

May 5, 1994,

Compaq Computer Corp.,

Phoenix Technologies Ltd., and

Intel Corporation.

Version 1.0,

February 1998,

Intel Corporation.

Version 1.5,

November 1997,

Intel Corporation.

Version 1.2A,

December 1997,

Intel Corporation.

This specification is

available from:

T13 Anonymous FTP

Site:

ftp://fission.dt.wdc.com/

x3t13/project/

d1153r18.pdf

http://developer.intel.com/

design/motherbd/atx.htm

the Phoenix Web site at:

http://www.ptltd.com/

techs/specs.html

http://www.teleport.com/

~ffsupprt/spec/

FlexATXaddn1_01.pdf

http://www.intel.com/

design/chipsets/industry/

lpc.htm

http://www.teleport.com/

~ffsupprt/spec/

http://www.teleport.com/

~ffsupprt/spec/microatx /

sfx11_ps.pdf

http://www.pcisig.com/

http://www.pcisig.com/

ftp://download.intel.com/

ial/wfm/bio10a.pdf

http://www.intel.com/

technology/memory/

http://www.intel.com/

technology/memory/

http://www.intel.com/

technology/memory/

continued

17

Page 18

Intel Desktop Board D810E2CB Technical Product Specification

Table 3. Specifications (continued)

Reference

Name

SMBIOS

UHCI

USB

WfM

Specification

Title

System Management

BIOS

Universal Host Controller

Interface Design Guide

Universal Serial Bus

Specification

Wired for Management

Baseline

Version, Revision Date and

Ownership

Version 2.3.1,

August 12, 1998,

Award Software International Inc.,

Dell Computer Corporation,

Hewlett-Packard Company,

Intel Corporation,

International Business Machines

Corporation,

Phoenix Technologies Limited,

American Megatrends Inc.,

SystemSoft Corporation, and

Compaq Computer Corporation.

Version 1.1,

March 1996,

Intel Corporation.

Version 1.1,

September 23, 1998,

Compaq Computer Corporation,

Intel Corporation,

Microsoft Corporation, and

NEC.

Version 2.0,

December 18, 1998,

Intel Corporation.

This specification is

available from:

http://developer.intel.com/

ial/wfm/wfm20/design/

smbios/index.htm

http://www.usb.org/

developers

http://www.usb.org/

developers

http://developer.intel.com/

ial/WfM/wfmspecs.htm

18

Page 19

Product Description

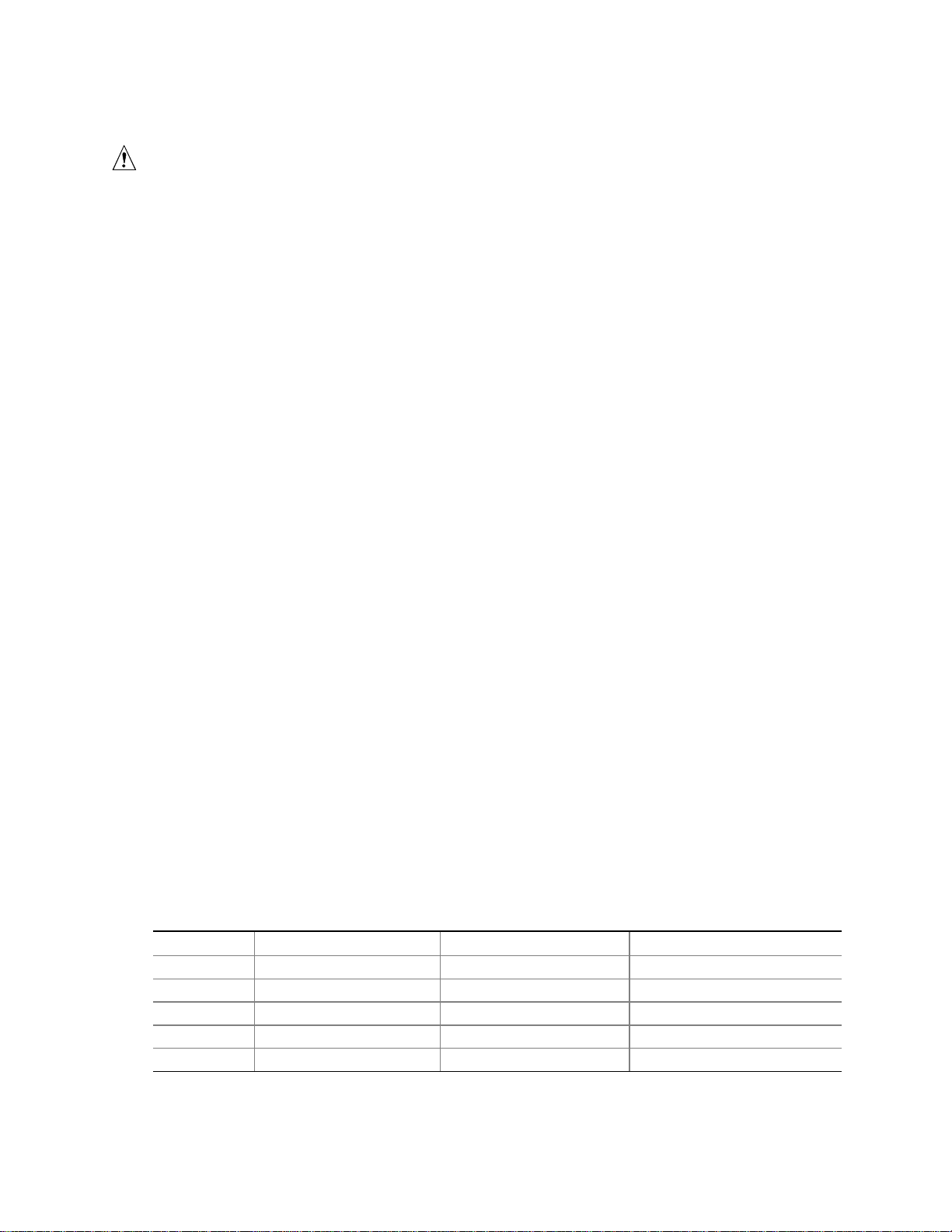

1.4 Processor

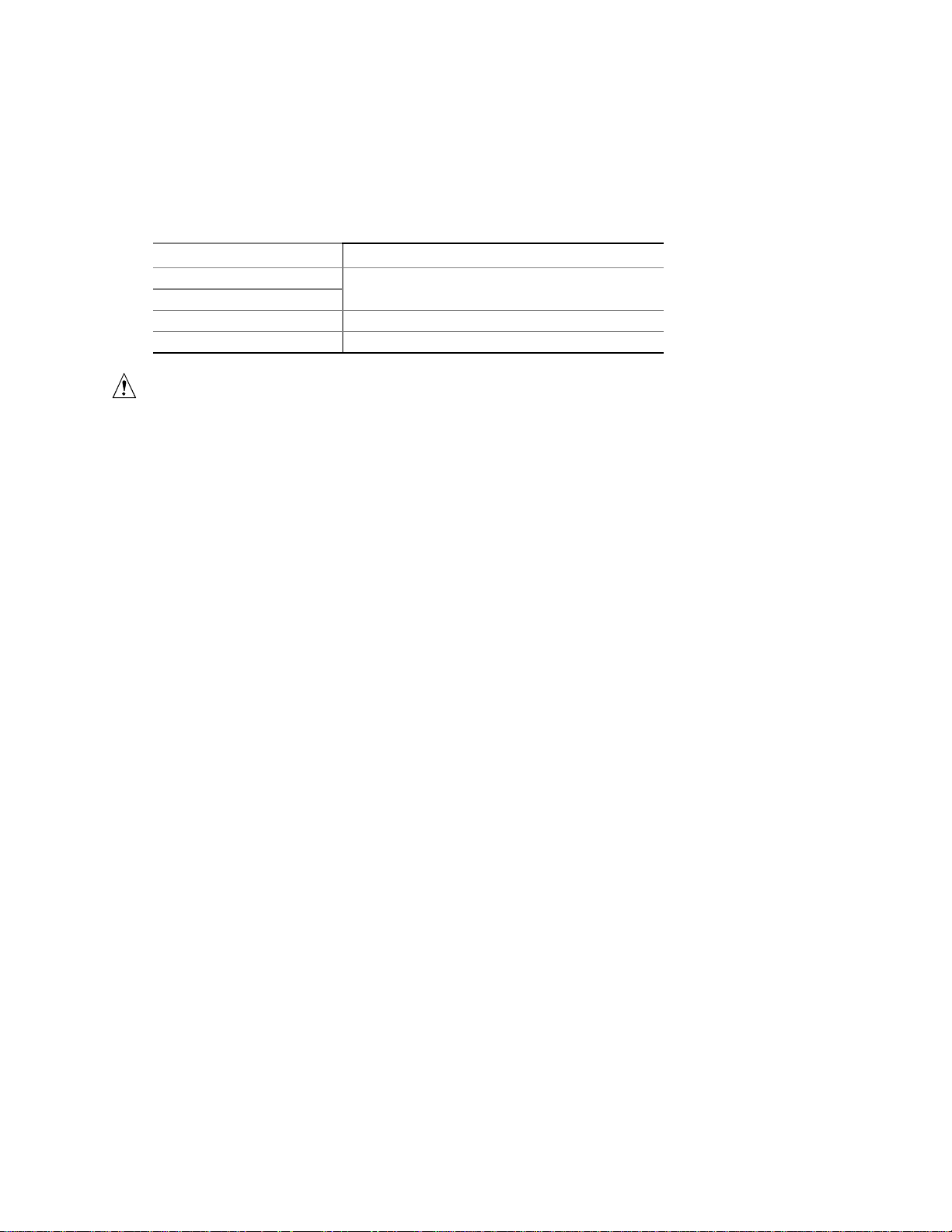

CAUTION

The D810E2CB board supports processors that draw a maximum of 22 A. Using a processor that

draws more than 22 A can damage the processor, the board, and the power supply. See the

processor’s data sheet for current usage requirements.

CAUTION

Before installing or removing the processor, make sure that AC power has been removed by

unplugging the power cord from the computer. Failure to do so could damage the processor and

the board.

The D810E2CB board supports either an Intel PentiumIII processor (FCPGA package), or an Intel

Celeron processor (PGA package) as shown in Table 4. The system bus frequency is automatically

selected.

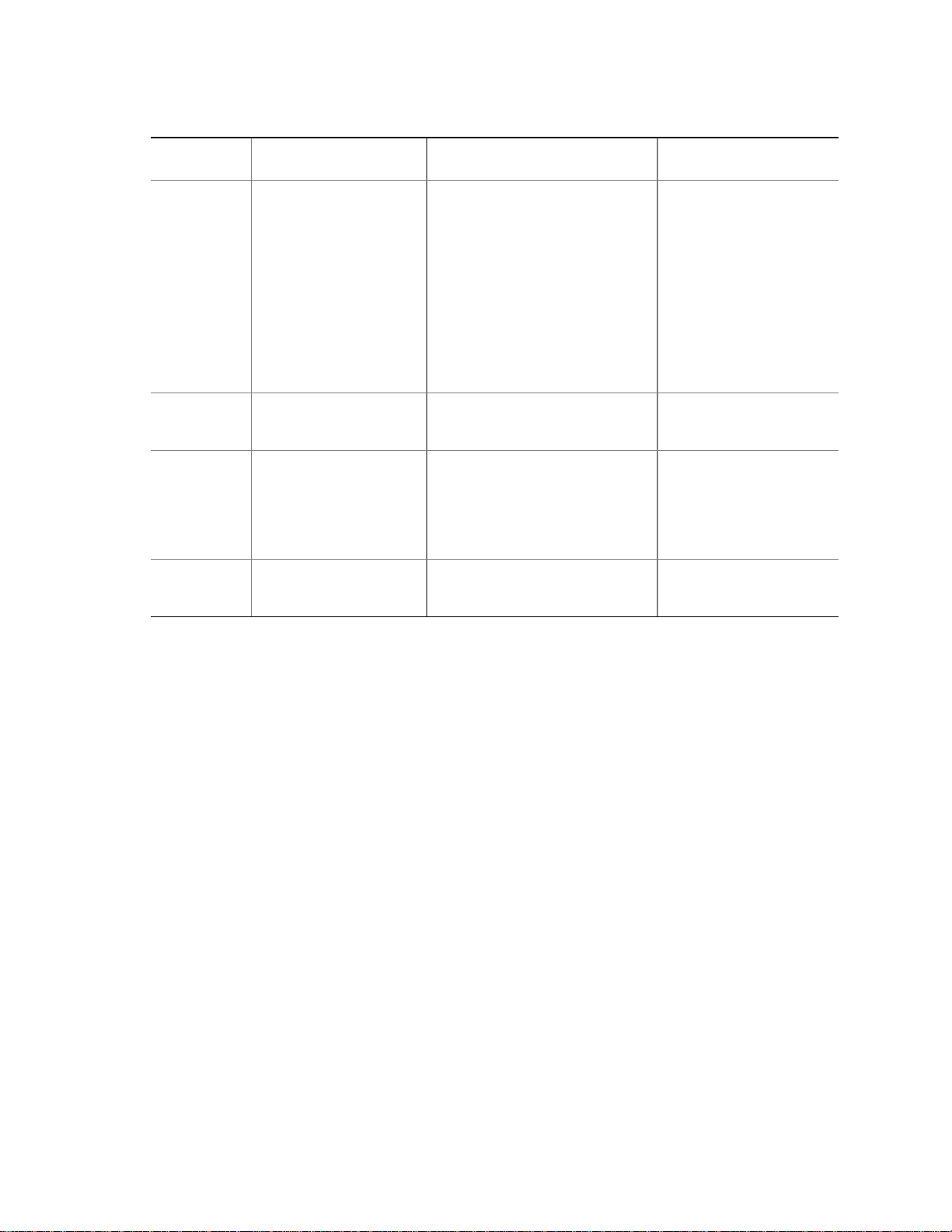

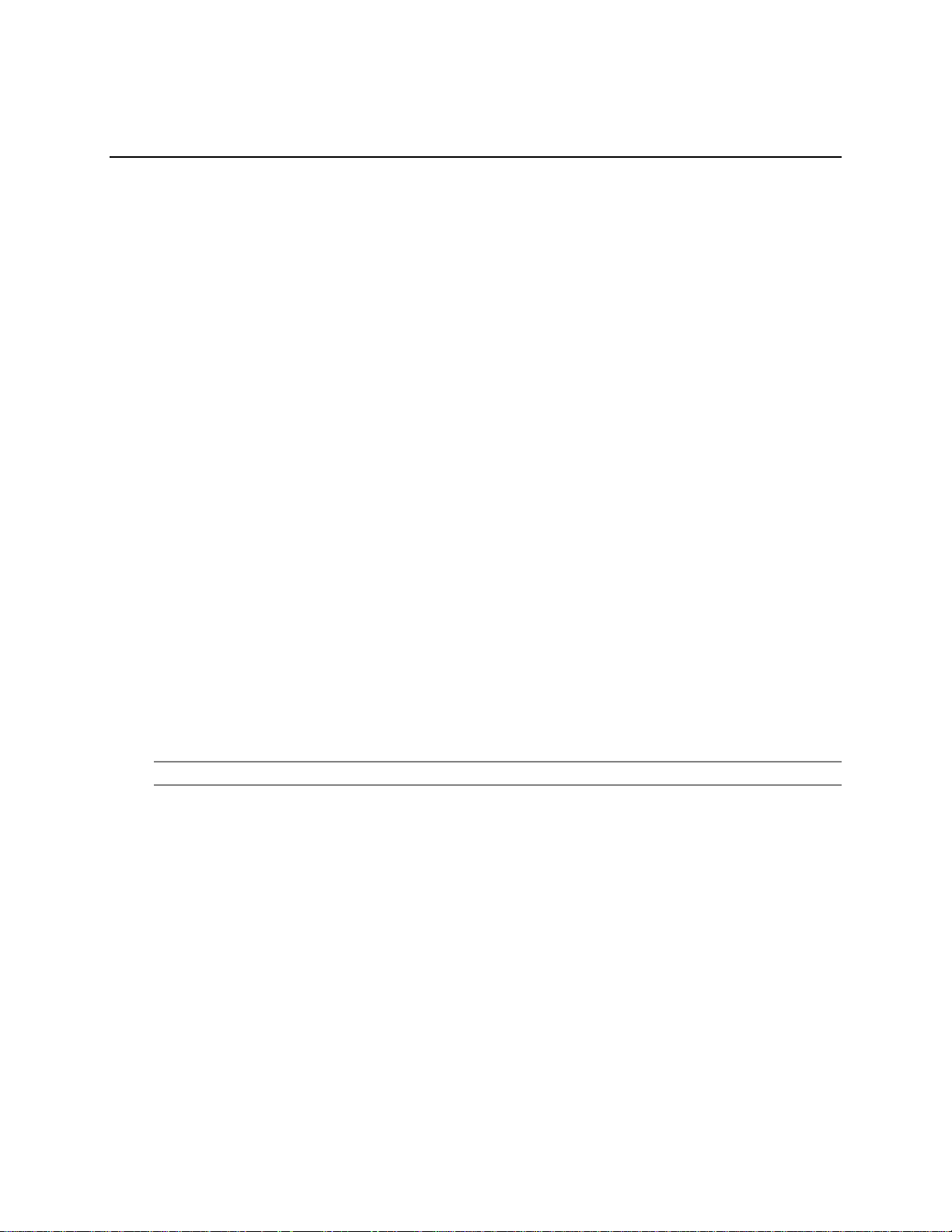

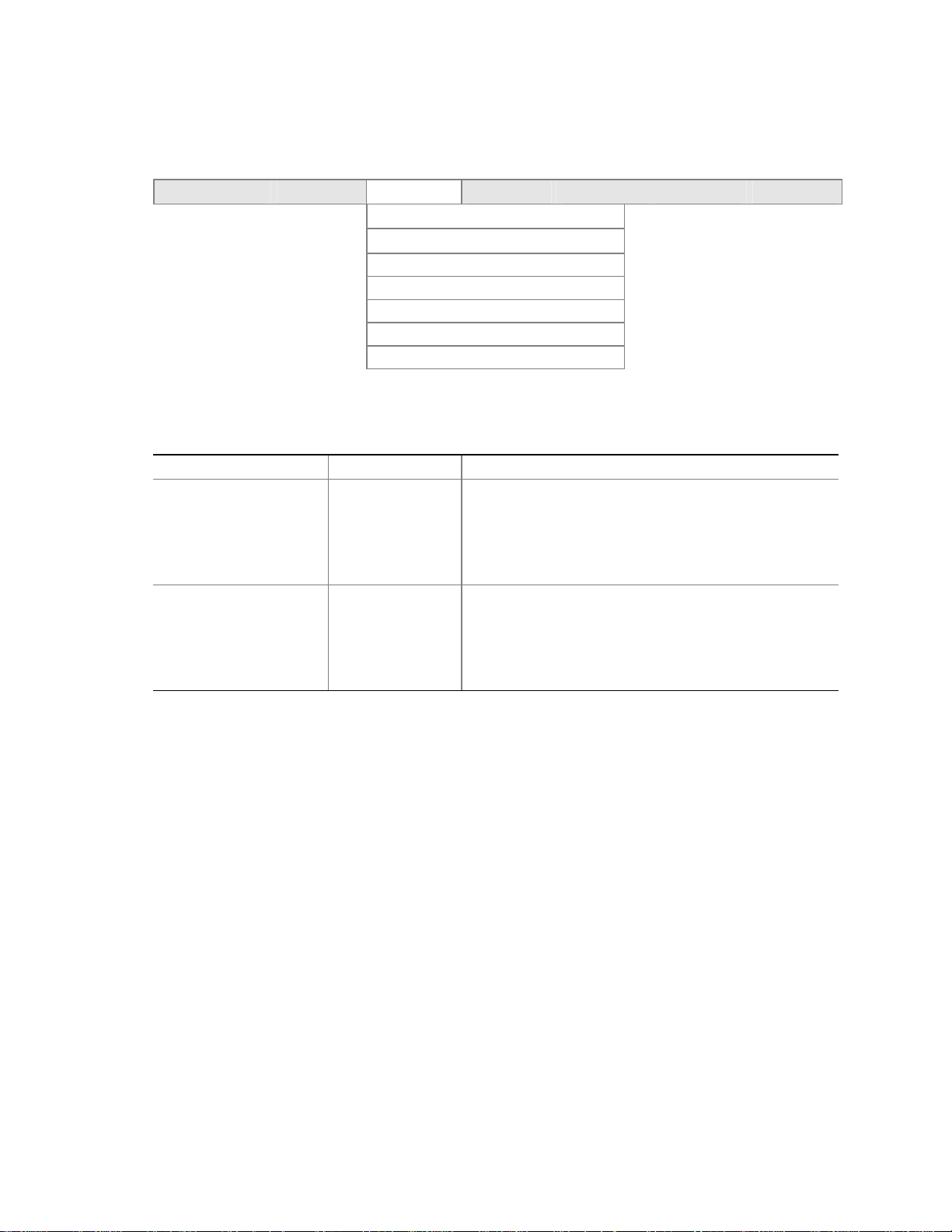

Table 4. Supported Processors

Processor Type Processor Designation System Bus Frequency L2 Cache Size

Pentium III processors 500E, 550E, 600E, 650, 700,

750, 800, and 850 MHz

533B, 600EB, 667, 733,

800EB, 866, and 933 MHz

1.0B GHz 133 MHz 256 KB

Celeron processors 800 MHz 100 MHz 128 KB

400, 433, 466, 500, 533,

533A, 566A, 600, 633, 667,

700, 733, and 766 MHz

100 MHz 256 KB

133 MHz 256 KB

66 MHz 128 KB

All supported onboard memory can be cached, up to the cachability limit of the processor.

For information about Refer to

Processor support for the D810E2CB board http://support.intel.com/support/motherboards/deskto

p

Processor data shee ts http://www.intel.com/design/litcentr

19

Page 20

Intel Desktop Board D810E2CB Technical Product Specification

1.5 System Memory

NOTE

✏

To be compliant with applicable Intel®SDRAM memory specifications, the D810E2CB board

should be populated with DIMMs that support the Serial Presence Detect (SPD) data structure. If

your memory modules do not support SPD, the BIOS will attempt to configure the memory

controller for normal operation; however, the DIMMs may not function at their optimum speed.

CAUTION

Before installing or removing memory, make sure that AC power has been removed by unplugging

the power cord from the computer. Failure to do so could damage the memory and the board.

CAUTION

Because the main system memory is also used as video memory, the board r equires 100 MHz

SDRAM DIMMs even though the processor’s system bus speed is 66 MHz. It is highly

recommended that SPD DIMMs be used, since this allows the BIOS to read the SPD data and

program the chipset to accurately configure memory settings for optimum performance. If nonSPD memory is installed, the BIOS will attempt to correctly configure the memory settings, but

performance and reliability may be impacted.

The D810E2CB board has two DIMM sockets. The minimum memory size is 64 MB and the

maximum memory size is 512 MB. The BIOS automatically detects memory type, size, and speed.

Memory can be installed in one or both sockets. Memory size can vary between sockets.

The D810E2CB board supports the following memory features:

• 3.3 V, 168-pin DIMMs with gold-plated contacts

• 100 MHz SDRAM

• Serial Presence Detect (SPD) or non-SPD memory (BIOS recovery requires SPD DIMMs)

• Non-ECC (64-bit) memory

• Unbuffered single- or double-sided DIMMs

The board is designed to support DIMMs in the configurations listed in Table 5 below.

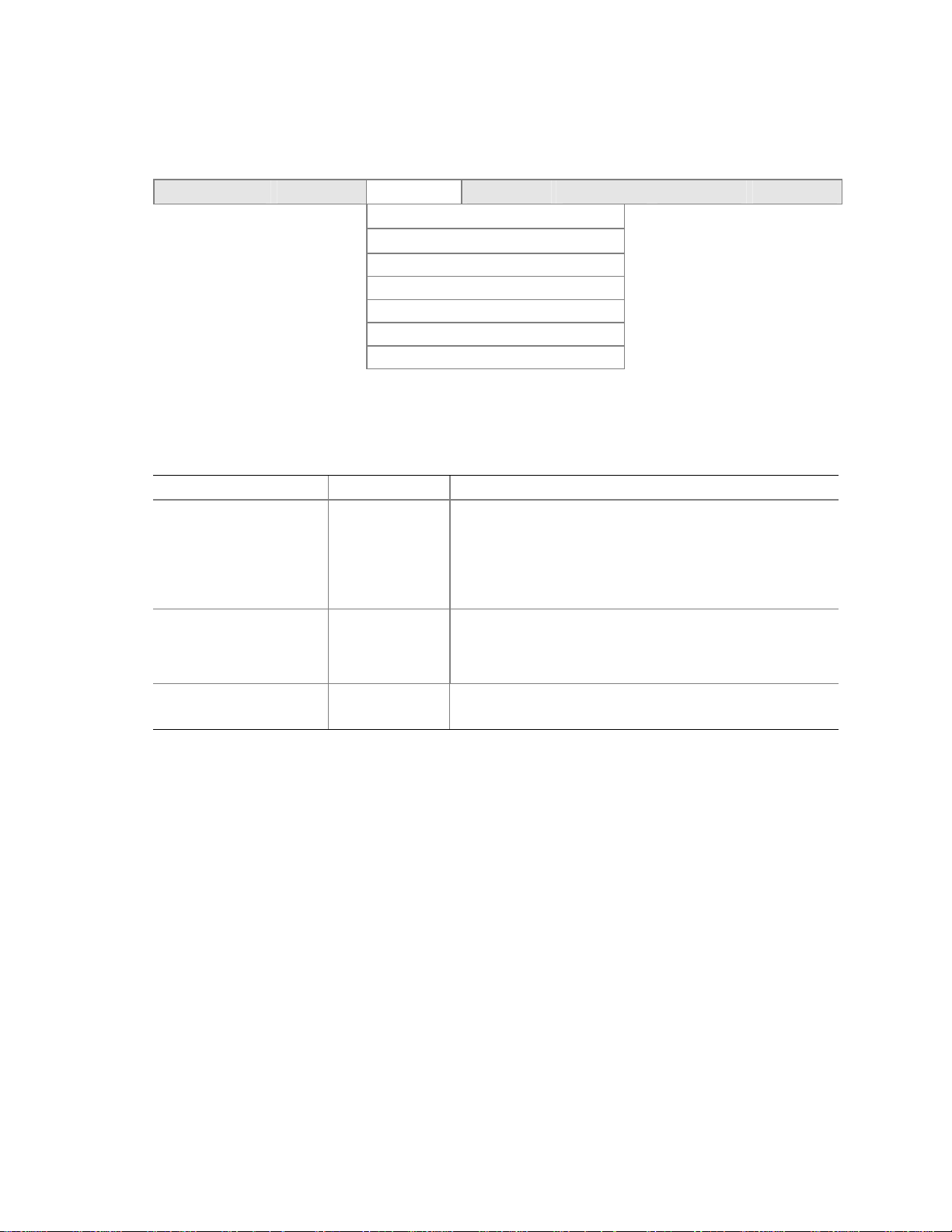

Table 5. System Memory Configuration

DIMM Size Non-ECC Configuration

16 MB 2 Mbit x 64

32 MB 4 Mbit x 64

64 MB 8 Mbit x 64

128 MB 16 Mbit x 64

256 MB 32 Mbit x 64

20

For information about Refer to

PC Serial Presence Detect Specification

The

Obtaining copies of PC SDRAM specifications http://www.intel.com/design/pcisets/memory

Table 3, page 16

Page 21

Product Description

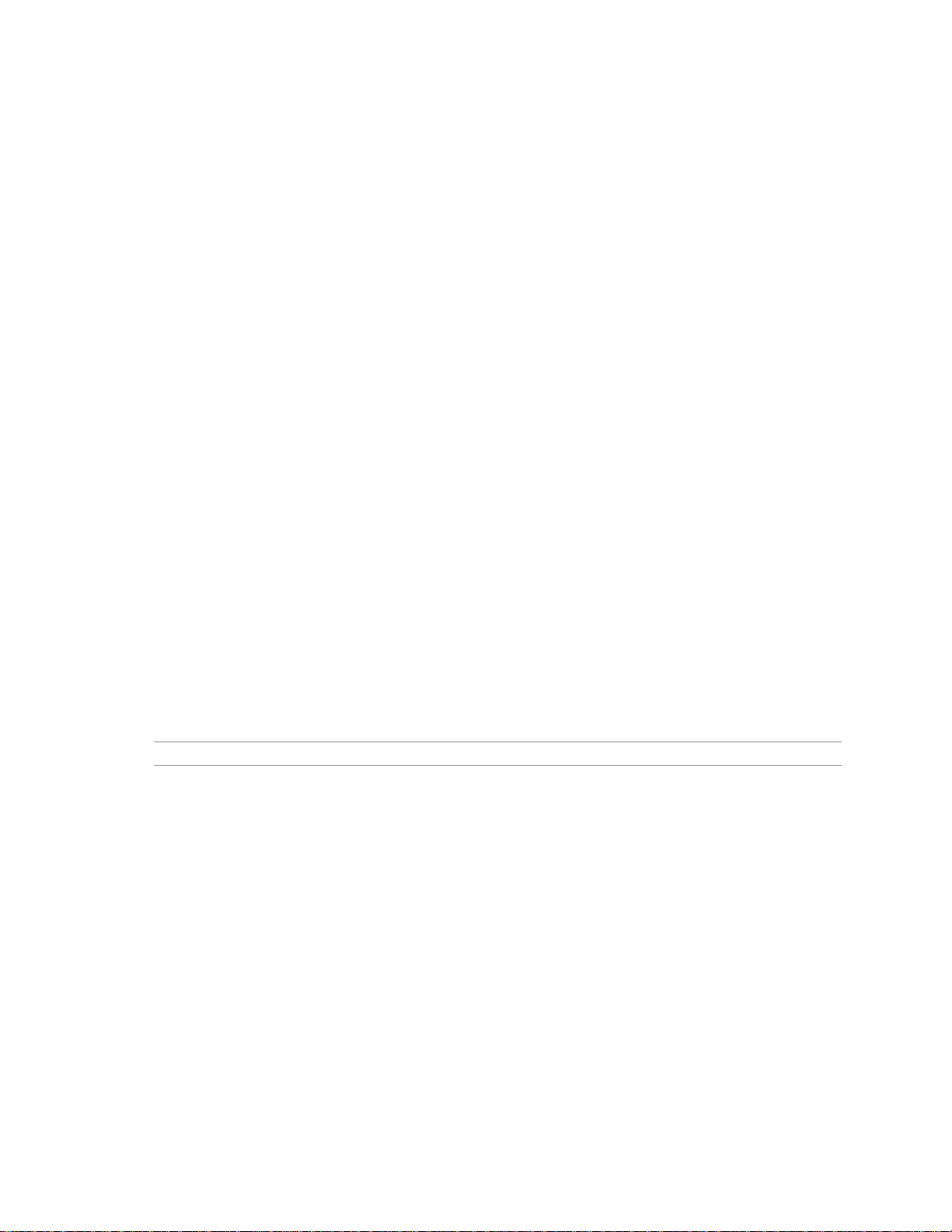

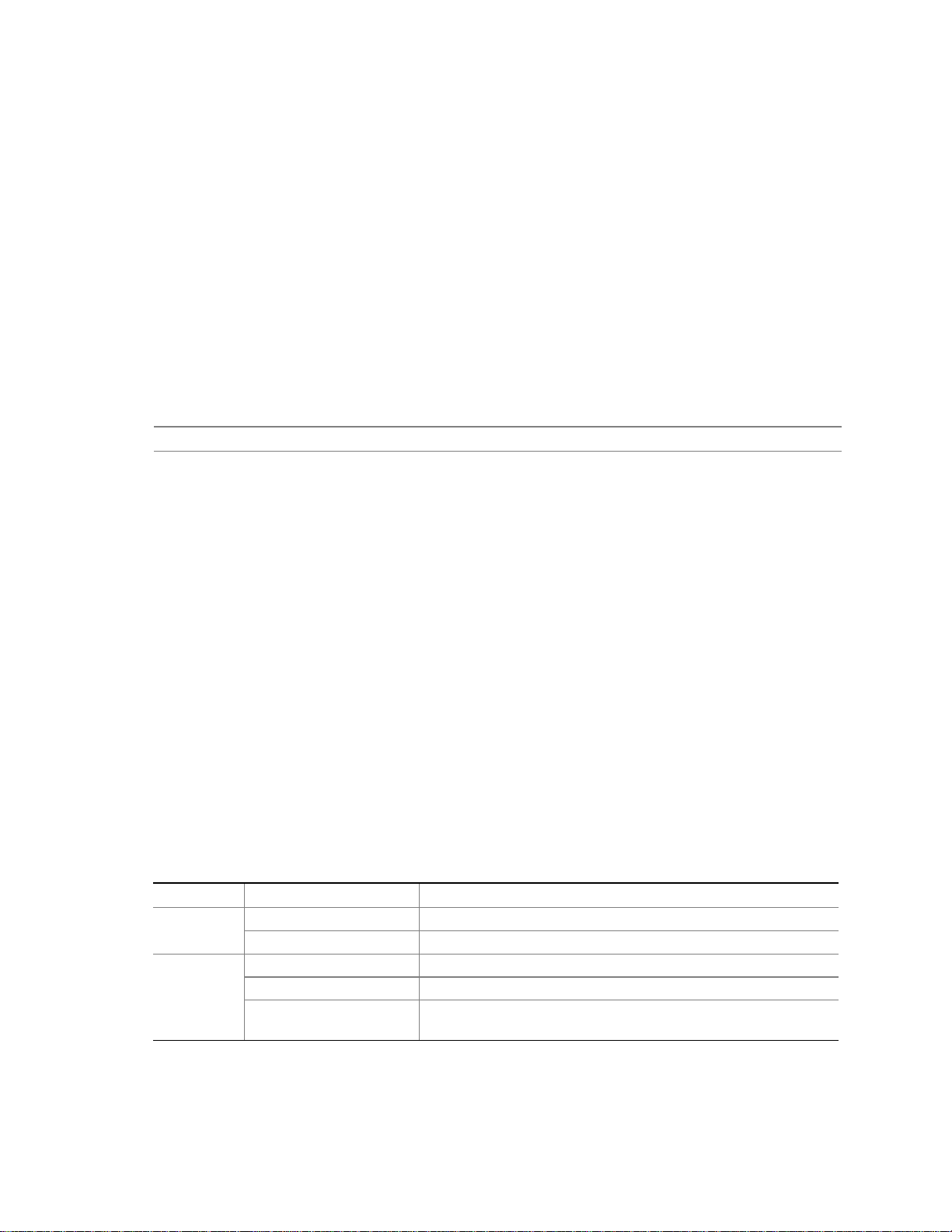

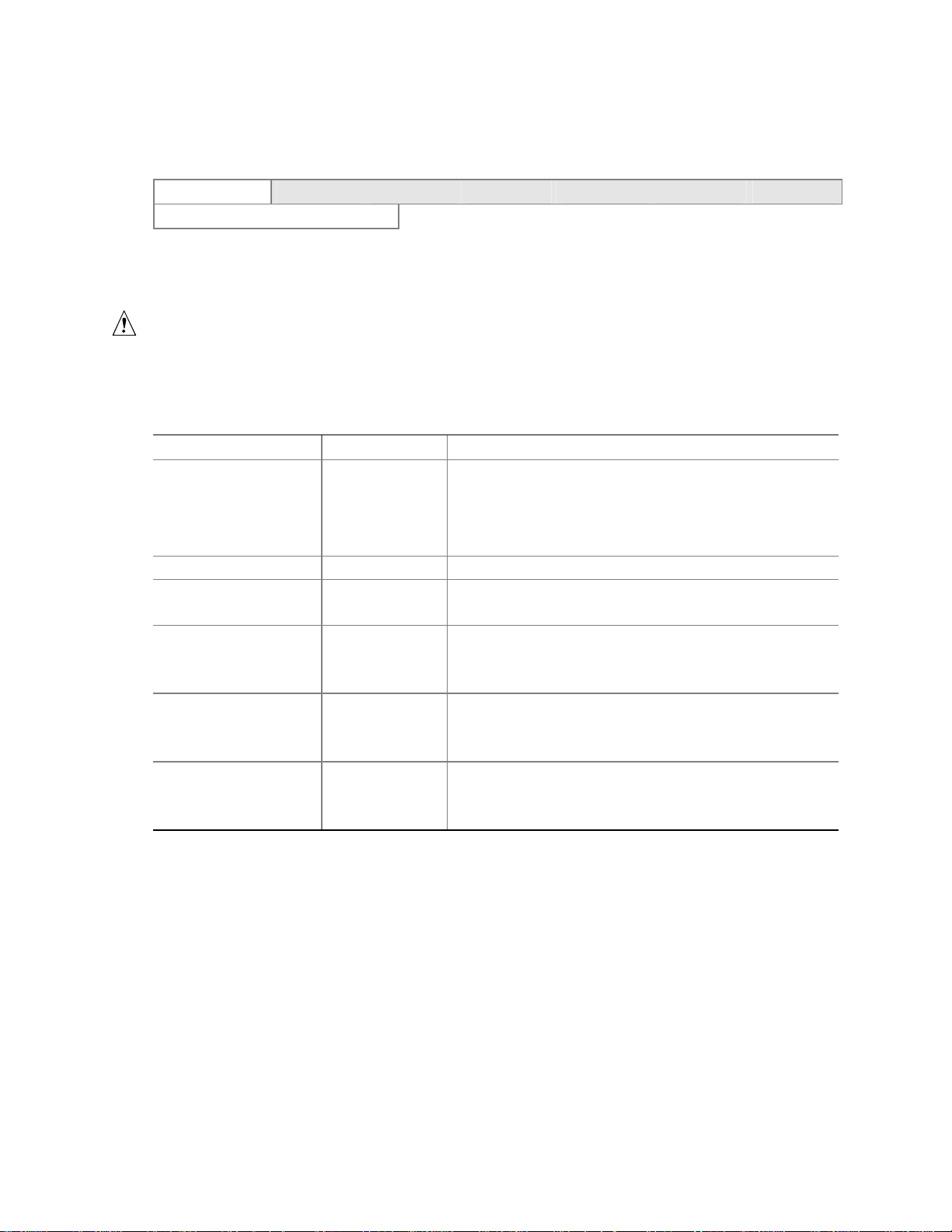

1.6 Intel®810E Chipset

The Intel 810E chipset consists of the following devices:

• 82810E Graphics Memory Controller Hub (GMCH) with Accelerated Hub Architecture (AHA)

bus

• 82801BA I/O Controller Hub (ICH2) with AHA bus

• SST 49LF004A Firmware Hub (FWH)

The GMCH is a centralized controller for the system bus, the memory bus, the AGP bus, and the

Accelerated Hub Architecture interface. The ICH2 is a centralized controller for the board’s I/O

paths. The FWH provides the nonvolatile storage of the BIOS. The component combination

provides the chipset interfaces as shown in Figure 3.

ATA-66/100

66/100/133 MHz

SystemBus

Network

USB

810E Chipset

100 MHz

SDRAM Bus

82810E

Graphics Memory

Controller Hub

(GMCH)

DisplayInterface

AHA

Bus

82801BA

I/O Controller Hub

(ICH2)

LPC Bus

AC LinkPCI BusSMBus

Figure 3. Intel 810E Chipset Block Diagram

For information about Refer to

The Intel 810E chipset http://www.developer.intel.com

The resources used by the chipset Chapter 2

The chipset’s compliance with ACPI and AC ‘97 Table 3, page 16

SST 49LF004A

FirmwareHub

(FWH)

OM11129

21

Page 22

Intel Desktop Board D810E2CB Technical Product Specification

1.6.1 Direct AGP

Direct (integrated) AGP is a high-performance bus (independent of the PCI bus) for graphicsintensive applications, such as 3D applications. AGP overcomes certain limitations of the PCI bus

related to handling large amount of graphics data with the following features:

• Pipelined memory read and write operations that hide memory access latency

• Demultiplexing of address and data on the bus for nearly 100 percent bus efficiency

For information about Refer to

The location of the VGA port connector Figure 5, page 46

Obtainingthe

Accelerated Graphics Port Interface Specification

Table 3, page 16

1.6.2 USB

The ICH2 contains two separate USB controllers supporting four USB ports. One USB peripheral

can be connected to each port. For more than four USB devices, an external hub can be connected to

any of the ports. Two of the USB ports are implemented with stacked back panel connectors. The

other two are accessible via the front panel USB connector at location J8B1. The D810E2CB board

fully supports Universal Hub Controller Interface (UHCI) and uses UHCI-compatible software

drivers.

NOTE

✏

Computer systems that have an unshielded cable attached to a USB port may not meet FCC

Class B requirements, even if no device is attached to the cable. Use shielded cable that meets the

requirements for full-speed devices.

For information about Refer to

The location of the USB connectors on the back panel Figure 5, page 46

The signal names of the USB connectors on the back panel Table 21, page 47

The location of the USB connectors on the front panel Figure 8, page 58

The signal names of the USB connectors on the front panel Table 41, page 60

The USB and UHCI specifications Table 3, page 16

22

Page 23

Product Description

1.6.3 IDE Support

The ICH2’s IDE controller has two independent bus-mastering IDE interfaces that can be

independently enabled. The IDE interfaces support the following modes:

• Programmed I/O (PIO): processor controls data transfer.

• 8237-style DMA: DMA offloads the processor, supporting transfer rat es of up to 16 MB/sec.

• Ultra DMA: DMA protocol on IDE bus supportinghost and target throttling a nd transfer rates

of up to 33 MB/sec.

• Ultra ATA-66: DMA protocolon IDE bus supporting host and target throttling and transfer

rates of up to 66 MB/sec. ATA-66 protocol is similar to Ultra DMA and is device driver

compatible.

• Ultra ATA-100: DMA protocolon IDE bus allows host and target throttling. The ICH2 Ultra

ATA-100 logic can achieve read transfer rates up to 100 MB/sec and write transfer rates up to

88 MB/sec.

✏ NOTE

ATA-100 and ATA-66 use faster timings and require a specialized cable to reduce reflections,

noise, and inductive coupling.

The IDE interfaces also support ATAPI devices (such as CD-ROM drives) and ATA devices using

the transfer modes listed in Section 4.4.4.1 on page 91.

The BIOS supports logical block addressing (LBA) and extended cylinder head sector (ECHS)

translation modes. The drive reports the transfer rate and translation mode to the BIOS.

The D810E2CB board supports laser servo (LS-120) diskette technology through its IDE interfaces.

An LS-120 drive can be configured as a boot device by setting the BIOS Setup program’s Boot

menu to one of the following:

• ARMD-FDD (ATAPI removable media device – floppy disk drive)

• ARMD-HDD (ATAPI removable media device – hard disk drive)

For information about Refer to

The location of the IDE connectors Figure 7, page 54

The signal names of the IDE connectors Table 36, page 56

BIOS Setup program’s Boot menu Table 66, page 98

23

Page 24

Intel Desktop Board D810E2CB Technical Product Specification

1.6.4 Real-Time Clock, CMOS SRAM, and Battery

The real-time clock is compatiblewith DS1287 and MC146818 components. The clockprovides a

time-of-day clock and a multicentury calendar with alarm features and century rollover. The realtimeclock supports 256 bytes of battery-backed CMOS SRAM in two banks that are reservedfor

BIOS use.

A coin-cell battery powers the real-time clock and CMOS memory. When the computer is not

plugged into a wall socket, the battery has an estimated life of three years. When the computer is

plugged in, the 3.3 V standby current from the power supply extends the life of the battery. The

clock is accurate to ± 13 minutes/year at 25 ºC with 3. 3 VSB applied.

The time, date, and CMOS values can be specified in the BIOS Setup program. The CMOS values

can be returned to their defaults by using the BIOS Setup program.

NOTE

✏

If the battery and AC power fail, the last saved defaults, custom or standard, will be loaded into

CMOS SRAM at power on.

NOTE

✏

The recommended method of accessing the date in systems with Intel®desktop boards is indirectly

from the Real-Time Clock (RTC) via the BIOS. The BIOS on Intel desktop boards contains a

century checking and maintenance feature. This feature checks the two least significant digits of

the year stored in the RTC during each BIOS request (INT 1Ah) to read the date and, if less than

80 (i.e., 1980 is the first year supported by the PC), updates the century byte to 20. This feature

enables operating systems and applications using the BIOS date/time services to reliably

manipulate the year as a four-digit value.

For information about Refer to

Proper date access in systems with Intel desktop boards http://support.intel.com/support/year2000/

1.6.5 SST 49LF004A 4 Mbit Firmware Hub (FWH)

The FWH provides the following:

• System BIOS program

• System security and manageability logic that enables protection for storing and updating of

platform information

24

Page 25

1.7 I/O Controller

The SMSC LPC47M102 I/O controller provides the following features:

• 3.3 V operation

• One serial port

• One parallel port with Extended Capabilities Port (ECP) and Enhanced Parallel Port

(EPP) support

• Serial IRQ interface compatiblewith serialized IRQ support for PCI systems

• PS/2-style mouse and keyboard interfaces

• Interface for one 1.2 MB or 1.44 MB diskette drive

• Intelligent power management, including a programm able wake up event interface

• PCI power management support

The BIOS Setup program provides configuration options for the I/O controller.

For information about Refer to

SMSC LPC47M102 I/O controller http://www.smsc.com

Product Description

1.7.1 Serial Port

The D810E2CB board has one serial port connector on the back panel. The serial port’s

NS16C550-compatible UART supports data transfers at speeds up to 115.2 kbits/sec with BIOS

support. The serial port can be assigned as COM1 (3F8h), COM2 (2F8h), COM3 (3E8h), or

COM4 (2E8h).

For information about Refer to

The location of the serial port connector Figure 5, page 46

The signal names of the serial port connector Table 24, page 48

1.7.2 Parallel Port

The connector for the multimode bidirectional parallel port is a 25-pin D-Sub connector located on

the back panel. In the BIOS Setup program, the parallel port can be configured for the following:

• Output only (PC AT

• Bi-directional (PS/2 compatible)

• EPP

• ECP

For information about Refer to

The location of the parallel port connector Figure 5, page 46

The signal names of the parallel port connector Table 22, page 47

†

-compatible mode)

25

Page 26

Intel Desktop Board D810E2CB Technical Product Specification

1.7.3 Diskette Drive Controller

The I/O controller supports one diskettedrive that is compatible with the 82077 diskette drive

controller and supports both PC-AT and PS/2 modes.

For information about Refer to

The location of the diskette drive connector Figure 7, page 54

The signal names of the diskette drive connector Table 37, page 57

The supported diskette drive capacities and sizes Table 61, page 93

1.7.4 Keyboard and Mouse Interface

PS/2 keyboard and mouse connectors are located on the back panel. The +5 V lines to these

†

connectors are protected with a PolySwitch

connection after an overcurrent condition is removed.

NOTE

✏

The keyboard is supported in the bottom PS/2 connector and the mouse is supported in the top

PS/2 connector. Power to the computer should be turned off before a keyboard or mouse is

connected or disconnected.

circuit that, like a self-healing fuse, reestablishes the

The keyboard controller contains the AMI keyboard and mouse controller code, provides the

keyboard and mousecontrol functions, and supports password protectionfor power-on/reset. A

power-on/reset password can be specified in the BIOS Setup program.

For information about Refer to

The location of the keyboard and mouse connectors Figure 5, page 46

The signal names of the keyboard and mouse connectors Table 20, page 47

26

Page 27

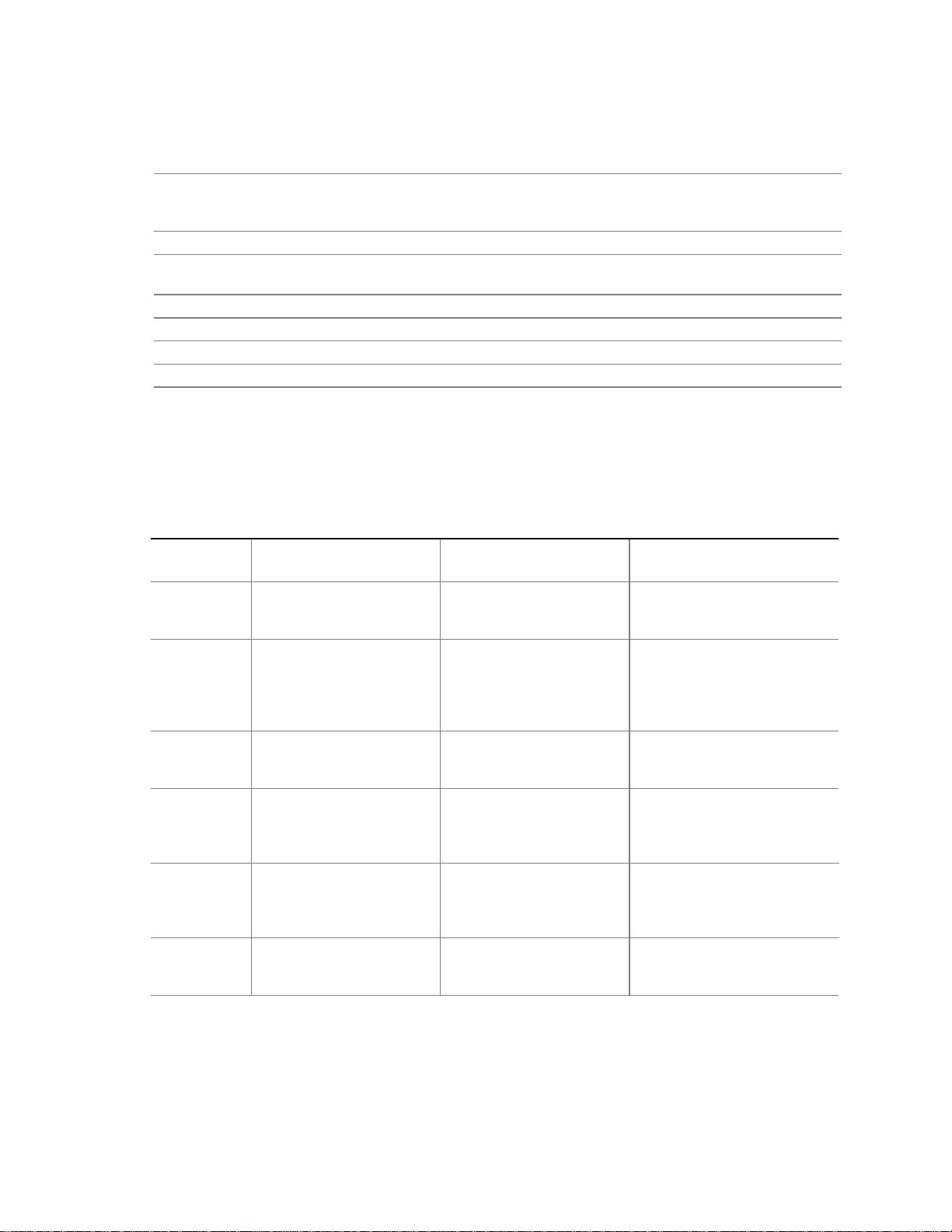

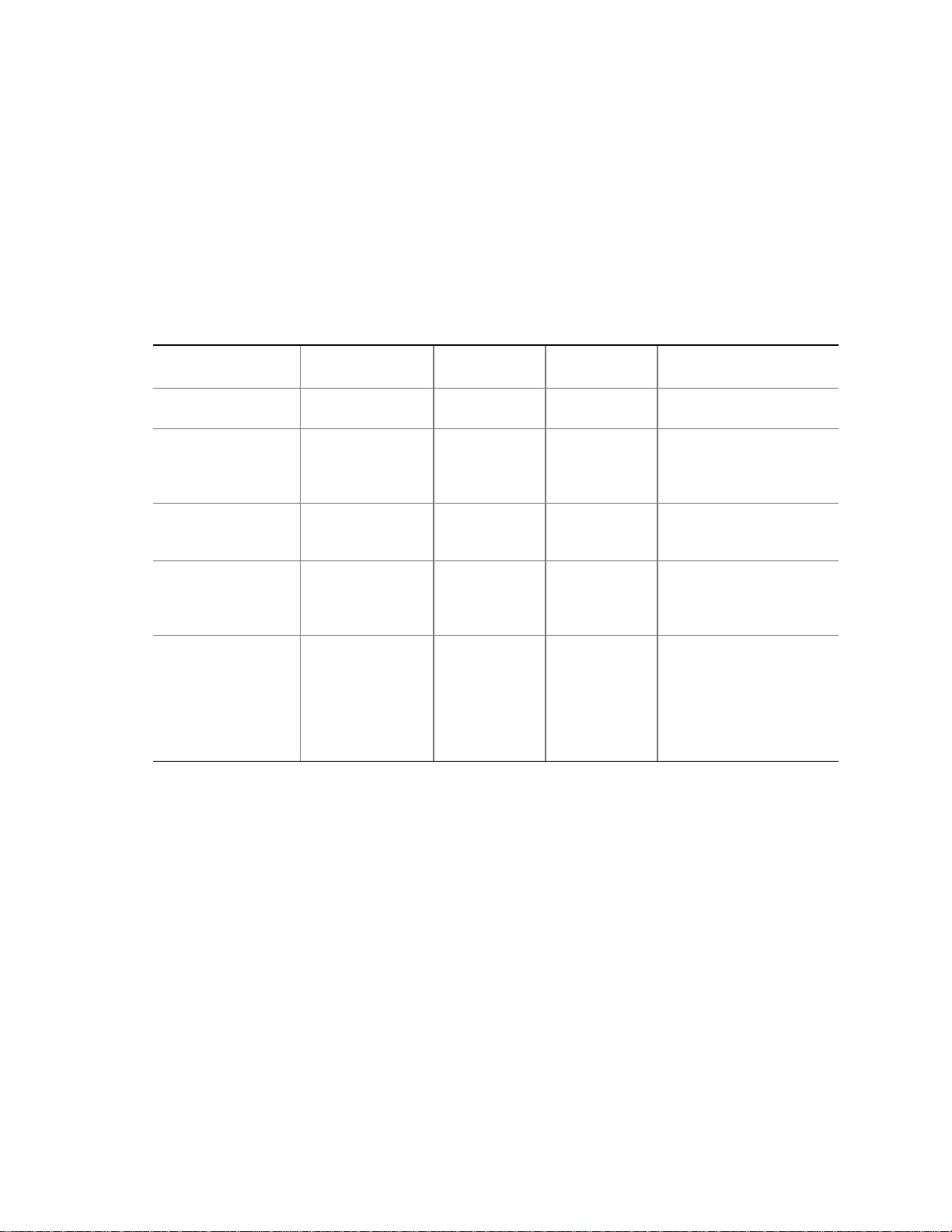

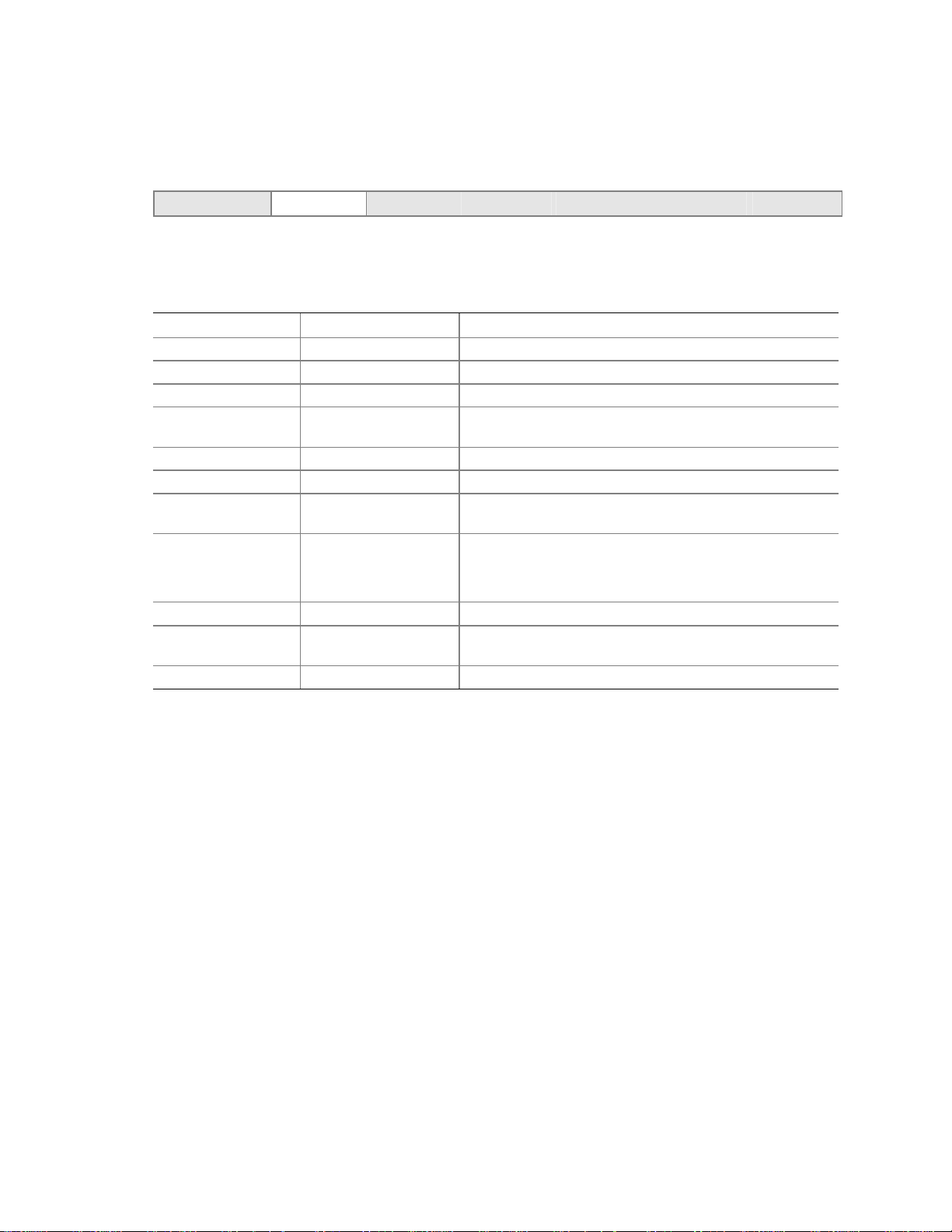

1.8 Graphics Subsystem

The Intel 82810E GMCH graphics memory controller hub component provides the following

graphics support features:

• Integrated 2-D and 3-D graphics engines

• Integrated hardware motion compression engine

• Integrated230 MHz DAC

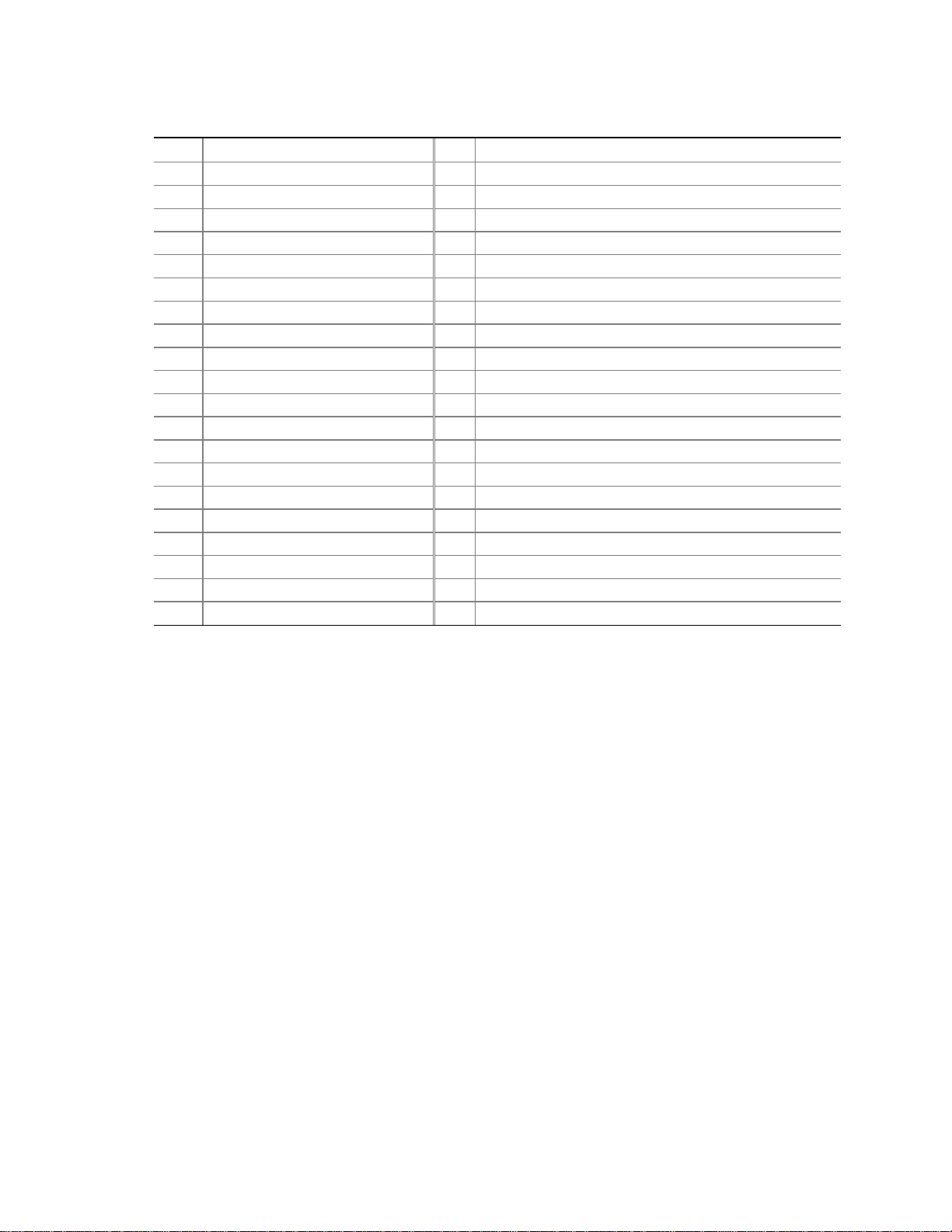

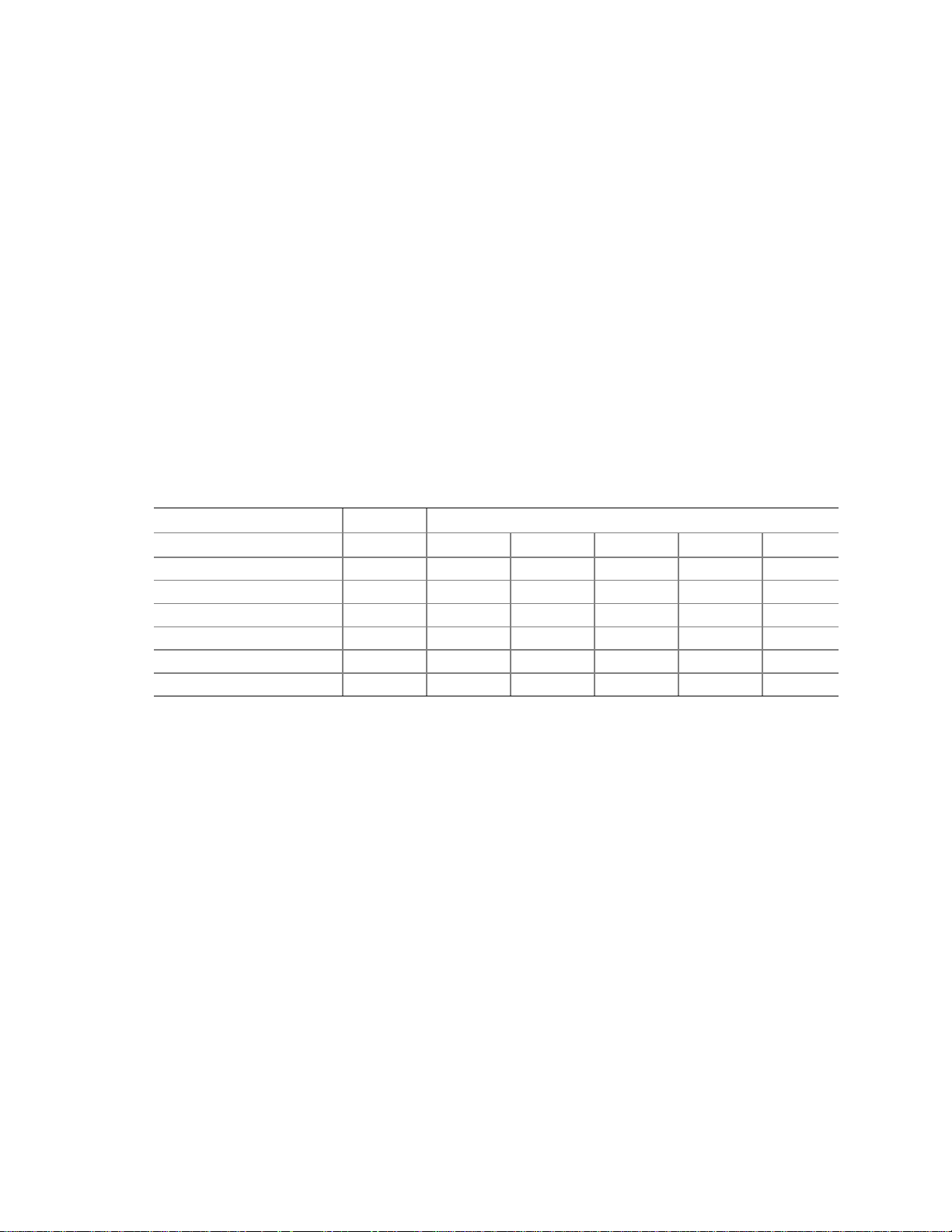

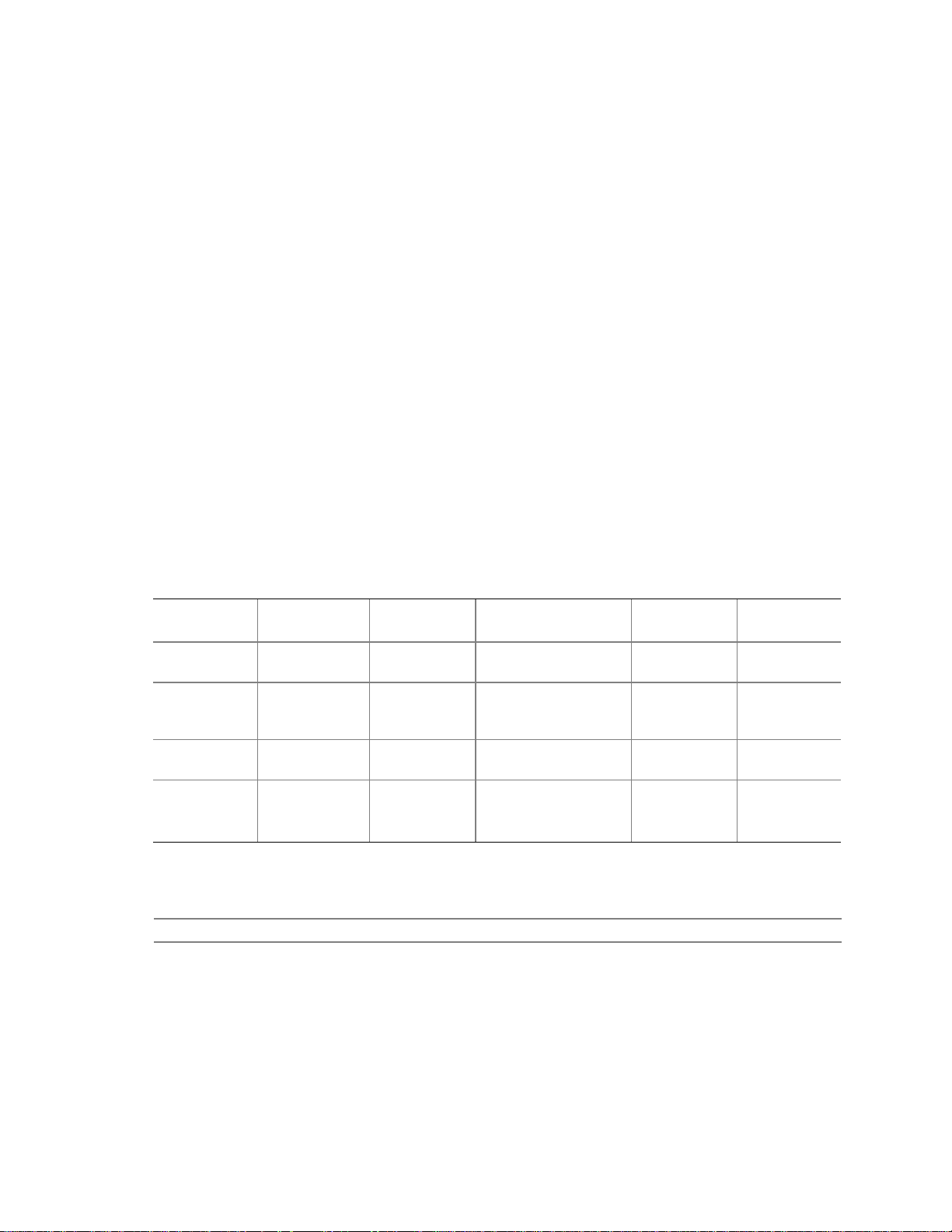

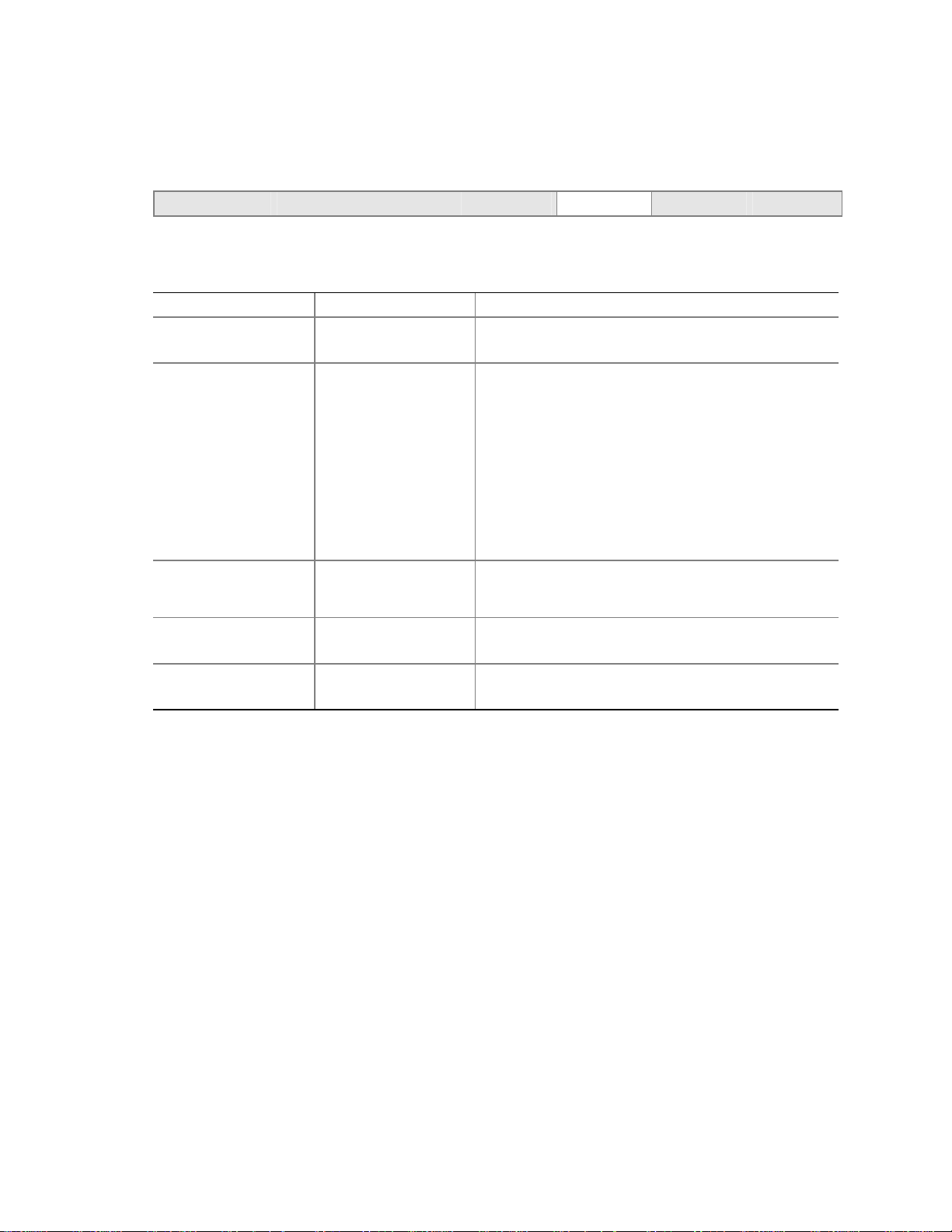

Table 6 lists the refresh r ates supported by the graphics subsystem.

Table 6. Supported Graphics Refresh Rates

Resolution Available Refresh Rates (Hz)

640 x 200 x 16 colors 70

640 x 350 x 16 colors 70

640 x 400 x 256 colors 60, 70, 75, 85

640 x 400 x 64 K colors 60, 70, 75, 85

640 x 400 x 16 M colors 70

640 x 480 x 16 colors 60, 72, 75, 85

640 x 480 x 256 colors 60, 70, 72, 75, 85

640 x 480 x 32 K colors 60, 75, 85

640 x 480 x 64 K colors 60, 70, 72, 75, 85

640 x 480 x 16 M colors 60, 70, 72, 75, 85

800 x 600 x 256 colors 60, 75, 85

800 x 600 x 32 K colors 60, 70, 72, 75, 85

800 x 600 x 64 K colors 60, 70, 72, 75, 85

800 x 600 x 16 M colors 60, 70, 72, 75, 85

1024 x 768 x 256 colors 60, 70, 75, 85

1024 x 768 x 32 K colors 60, 75, 85

1024 x 768 x 64 K colors 60, 70, 72, 75, 85

1024 x 768 x 16 M colors 60, 70, 72, 75, 85

1056 x 800 x 16 colors 70

1280 x 1024 x 256 colors 60, 70, 72, 75, 85

1280 x 1024 x 32 K colors 60, 75, 85

1280 x 1024 x 64 K colors 60, 70, 72, 75

1280 x 1024 x 16 M colors 60, 70, 72, 75, 85

Product Description

For information about Refer to

Obtaining graphics software and utilities http://support.intel.com/support/motherboards/desktop

27

Page 28

Intel Desktop Board D810E2CB Technical Product Specification

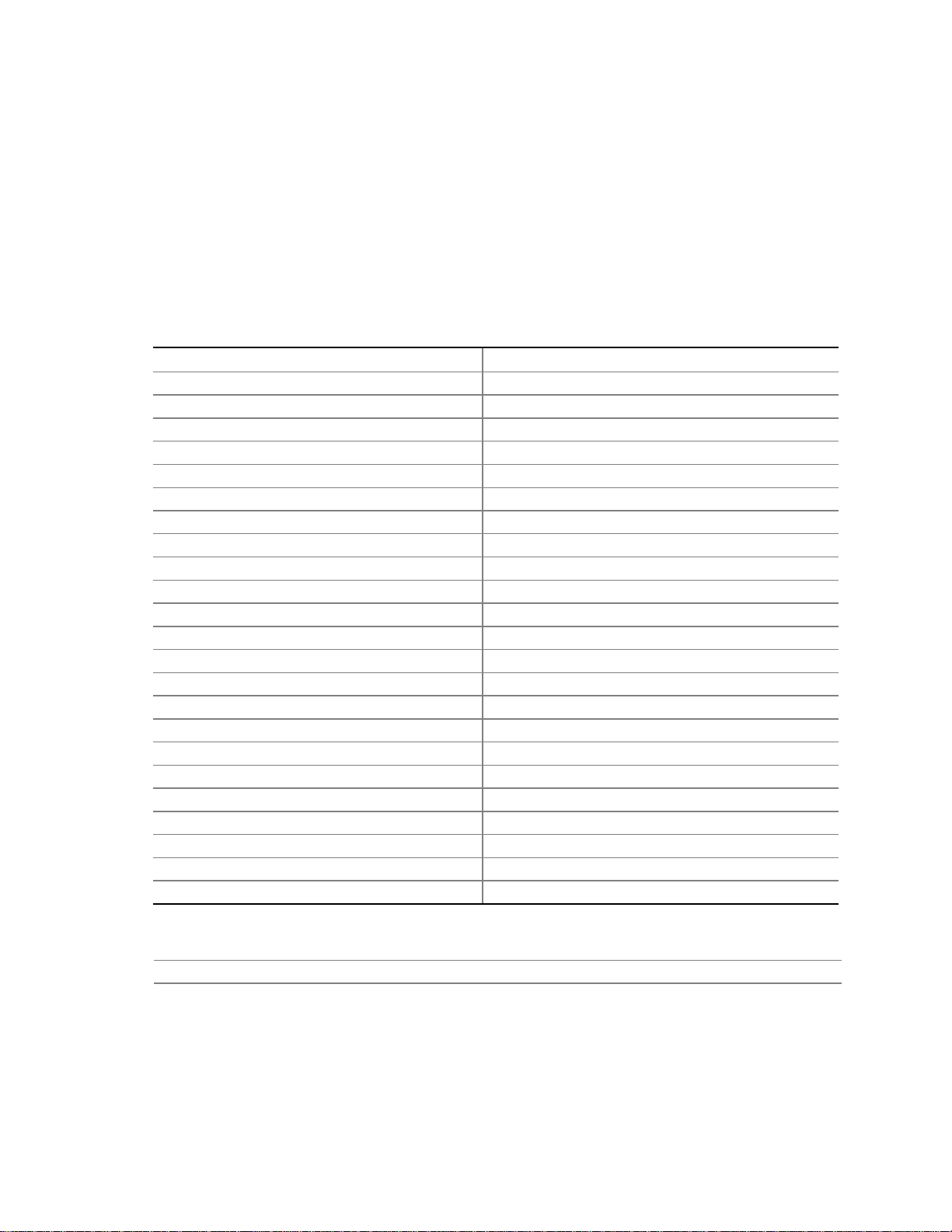

1.9 Audio Subsystem

The D810E2CB board includes an Audio Codec ’97 (AC ’97) compatible audio subsystem

consisting of these devices:

• Intel 82801BA ICH2 (AC link output)

• CS4201 analog codec

Figure 4 is a block diagram of the audio subsystem.

CD-ROM

82801BA

I/O ControllerHub

(ICH2)

Figure 4. Block Diagram of Audio Subsystem with CS4201 Codec

AC '97

Link

CS4201

Analog Codec

Line In

Line Out

MicIn

Modem Audio

OM11128

Features of the audio subsystem include:

• Independent channels for PCM in, PCM out, and Mic in

• 16-bit stereo I/O up to 48 kHz

• Multiple sample rates

For information about Refer to

Obtaining audio software and utilities Section1.2, page 16

1.9.1 CS4201 Analog Codec

The CS4201 is a fully AC ’97 compliant codec. T he codec's features include:

• 16-bit stereo full-duplex operation

• High quality CD-ROM input with ground sense

• Stereo line level output

• Power management support

• Full duplex variable sampling rate (7 kHz to 48 kHz) with 1 Hz resolution

†

• Phat

Stereo 3-D stereo enhancement

1.9.2 Audio Connectors

The audio connectors include the following:

• ATAPI CD-ROM (connects an internal ATAPI CD-ROM drive to the audio mixer)

• Telephony

• Line out (back panel)

• Line in (back panel)

• Mic in

28

Page 29

Product Description

For information about Refer to

The location of the ATAPI CD-ROM and telephony connectors Figure 6, page 51

The signal names of the ATAPI CD-ROM connector Table 29, page 52

The signal names of the telephony connector Table 30, page 52

The back panel audio connectors Section 2.8.1, page 46

1.10 Hardware Management Subsystem

The hardware manageme nt features enable the board to be compatible with the Wired for

Management (WfM) specification. The board has several hardware management features, including

the following:

• Fan control and monitoring

• Thermal and voltage monitoring

For information about Refer to

The WfM specification Table 3, page 16

1.10.1 Hardware Monitor Component (Optional)

The hardware monitor component provides low-cost instrumentation capabilities. The features of the

component include:

• Internal ambient temperaturesensing

• Remote thermal diode sensing for direct monitoring of processor temperature

• Power supply monitoring (+12 V, +5 V, +3.3 V, +2.5 V, 3.3 VSB, Vccp) to detect levels above

or below acceptable values

• SMBus interface

The hardware monitor component enables the board to be compatible with the Wired for

Management (WfM) specification.

For information about Refer to

The board’s compatibility with the WfM specification Table3, page 16

1.10.2 Fan Control and Monitoring

The SMSC LPC47M102 I/O controller provides two fan sense inputs and two fan control outputs.

Monitoring and control can be impleme nted using third-party software.

For information about Refer to

The functions of the fan connectors Section 1.12.3.2, page 35

The locations of the fan connectors Figure 6, page 51

The signal names of the fan connectors Section 2.8.2.1, page 51

29

Page 30

Intel Desktop Board D810E2CB Technical Product Specification

1.11 LAN Subsystem (Optional)

The Network Interface Controller subsystemconsists of the ICH2 (with integrated LAN Media

Access Controller) and a physical layer interface device. Features of the LAN subsystem include:

• PCI Bus Master interface

• CSMA/CD Protocol Engine

• Serial CSMA/CD unit interface that supports the 82562ET (10/100 Mbit/sec Ethernet) physical

layer interface device

• PCI Power Management

Supports APM

Supports ACPI technology

†

Supports Wake up from suspend state (Wake on LAN

For information about Refer to

Obtaining LAN software and drivers Section 1.2, page 16

1.11.1 Intel®82562ET Platform LAN Connect Device

technology)

The Intel 82562ET component provides a n interface to the back panel RJ-45 connector with

integrated LEDs. This physical interface may alternately be provided via the CNR connector.

The Intel 82562ET provides the following functions:

• Basic 10/100 Ethernet LAN connectivity

• Supports RJ-45 connector with status indicator LEDs on the back panel

• Full device driver compatibility

• Advanced Power Management and ACPI support

• Programmable transit threshold

• Configuration EEPROM that contains the MAC address

• Remote monitoring (alerting)

1.11.2 RJ-45 LAN Connector with Integrated LEDs

Two LEDs are built into the RJ-45 LAN connector. Table 7 describes the LED states when the

board is powered up and the LAN subsystem is operating.

Table 7. LAN Connector LED States

LED Color LED State Condition

Off 10 Mbit/sec data rate is selected.Green

On 100 Mbit/sec data rate is selected.

Yellow

Off LAN link is not established.

On (steady state) LAN link is established.

On (brighter and pulsing) The computer is communicating with another computer on

the LAN.

30

Page 31

1.12 Power Management Features

Power management is implemented at several levels, including:

• Advanced Configuration and Power Interface (ACPI)

• Advanced Power Management (APM)

• Hardware support:

Power connector

Fan connectors

Wake on LAN technology

†

Instantly Available

Wake on Ring

Resume on Ring

Wake from USB

PME# wakeup support

1.12.1 ACPI

technology

Product Description

If the board is used with an ACPI-aware operating system, the BIOS can provide ACPI support.

ACPI gives the operating system direct control over the power management and Plug and Play

functions of a computer. The use of ACPI with this board requires the support of a n operating

system that provides full ACPI functionality. ACPI features include:

• Plug and Play (including bus and device enumeration)

• Power management control of individual devices, video displays, and hard disk drives

• Methods for achieving less than 30-watt system operation in the Power On Suspend sleeping

state, and less than 5-watt system operationin the Suspend to RAM sleepingstate

• A Soft-off feature that enables the operating system to power off the computer

• Support for multiple wake up events (see Table 10 on page 33)

• Support for a front panel power and sleep mode switch.

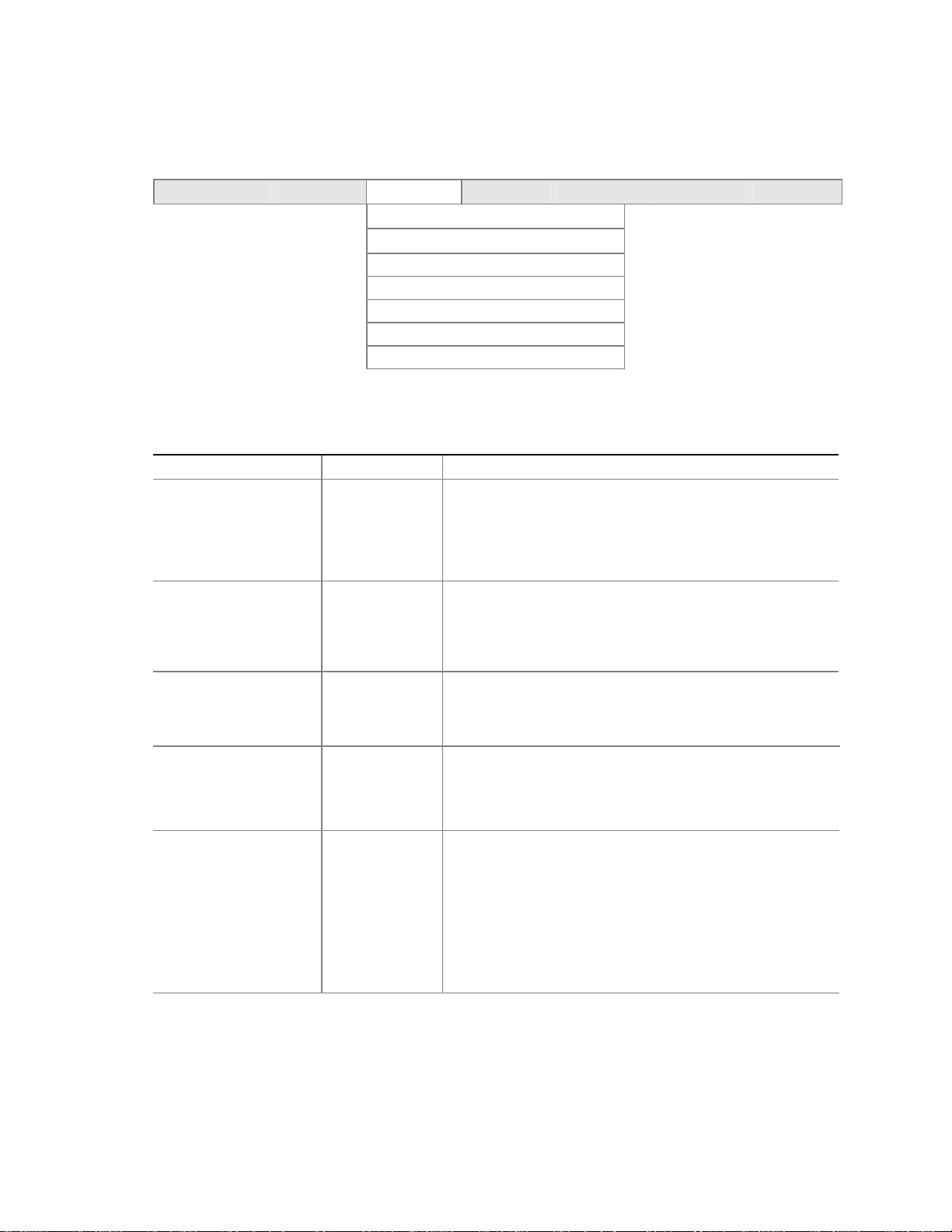

Table 8 lists the system states based on how long the power switch is pressed, depending on how

ACPI is configured with an ACPI-aware operating system.

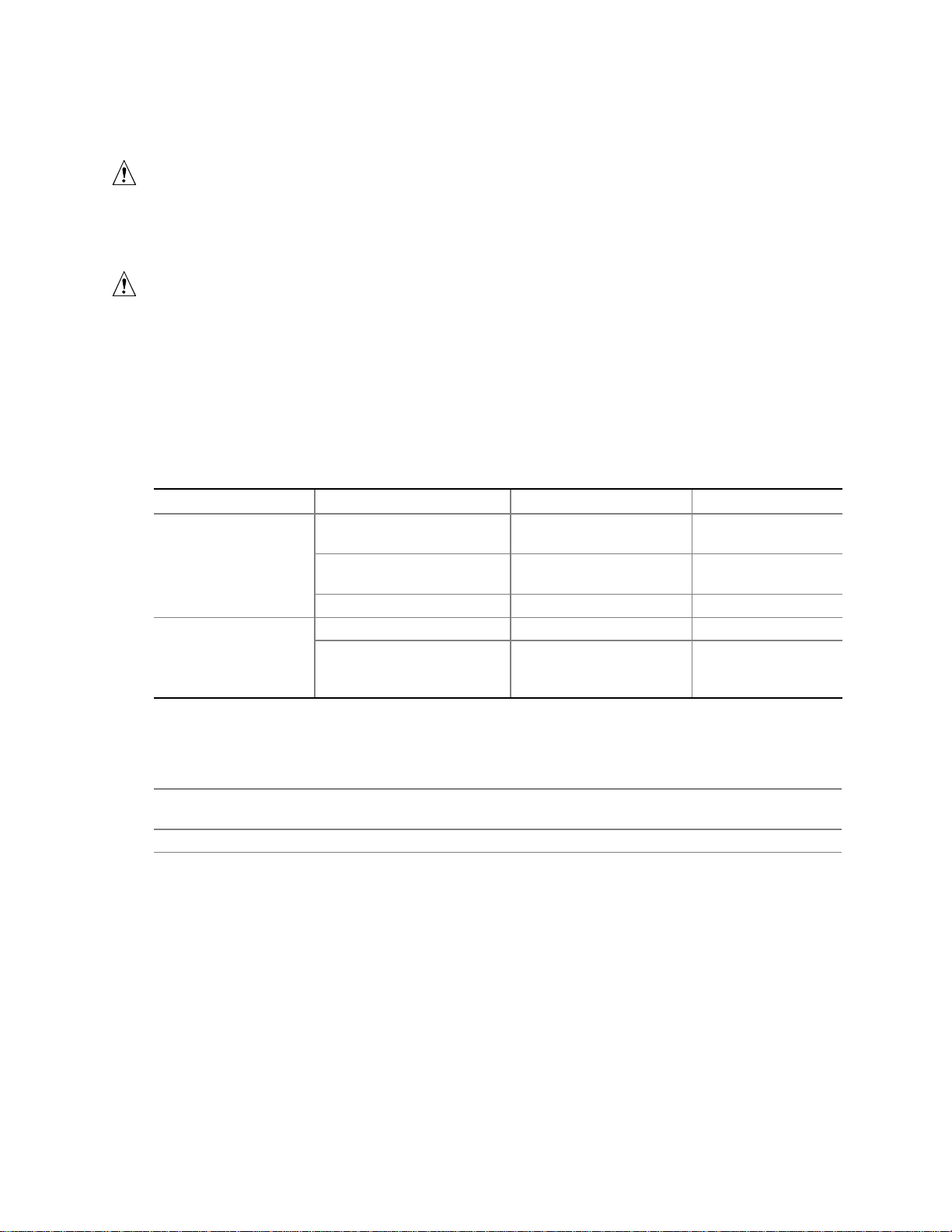

Table 8. Effects of Pressing the Power Switch

…and the power switch is

If the system is in this state…

Off (ACPI G2/S5 state) Less than four seconds Power on

On (ACPI G0 state) Less than four seconds Soft off/Suspend

On (ACPI G0 state) More than four seconds Fail safe power off

Sleep (ACPI G1 state) Less than four seconds Wake up

Sleep (ACPI G1 state) More than four seconds Power off

pressed for …the system enters this state

For information about Refer to

The board’s compliance level with ACPI Table 3, page 16

31

Page 32

Intel Desktop Board D810E2CB Technical Product Specification

1.12.1.1 System States and Power States

Under ACPI, the operating system directs all system and device power state transitions. The

operating system puts devices in and out of low-power states based on user preferences and

knowledge of how devices are being used by applications. Devices that are not being used can be

turned off. The operating system uses information from applications and user settings to put the

system as a whole into a low-power state.

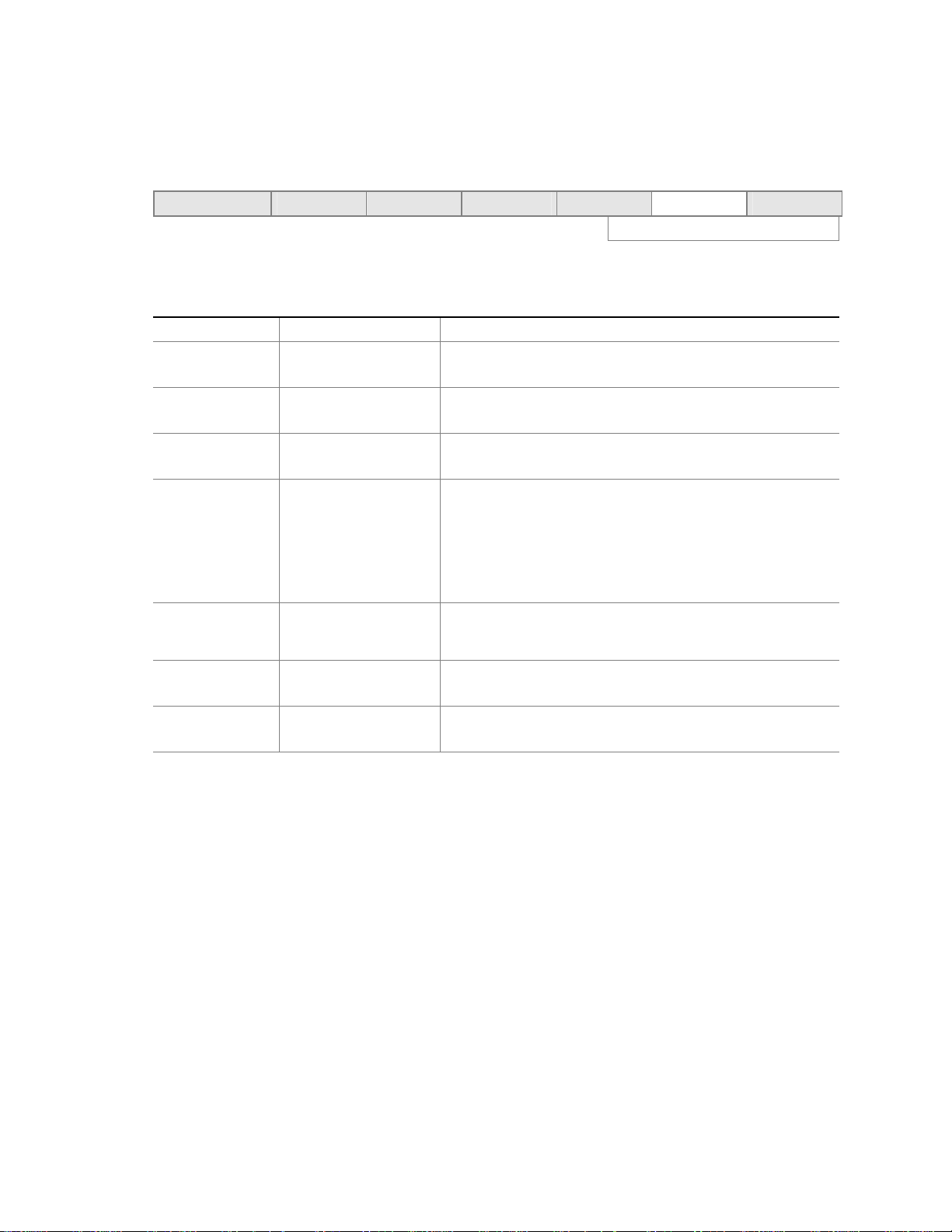

Table 9 lists the power sta t es supported by the board along with the associated system power targets.

See the ACPI specification for a complete description of the various system and power states.

Table 9. Power States and Targeted System Power

Global States Sleeping States CPU States Device States Targeted System

Power*

G0 - working state S0 - working C0 - working D0 - working

state

G1 - sleeping state S1 - CPU stopped C1 - stop grant D1, D2, D3 -

device

specification

specific.

G1 - sleeping state S3 - Suspend-to-

RAM. Context

saved to RAM.

G2/S5 S5 - Soft off.

Context not

saved. Cold boot

is required.

G3 - mechanical off.

(AC power is

disconnected from

the computer.)

* Totalsystempower is dependent on the system configuration, including peripherals poweredby the system chassis’ power

supply.

** Dependent on the standbypower consumption of wake-up devices used in the system.

No power to the

system.

No power D3 - no power

except for

wake up logic.

No power D3 - no power

except for

wake up logic.

No power D3 - no power

for wakeup

logic, except

when provided

by battery or

external

source.

Full power > 30 W

5W<power<30W

Power < 5 W **

Power < 5 W **

No power to the system

so that service can be

performed.

32

Page 33

Product Description

1.12.1.2 Wake-up Devices and Events

Table 10 lists the devices or specific events that can wake the computer from specific states.

Table 10. A CPI Wake-up Devices and Events

These devices/events can wake-up the computer… …from this state

Power switch S1, S3, S5

RTC alarm S1, S3, S5

LAN S1, S3

PME# S1, S3

USB S1, S3

PS/2 S1, S3

1.12.1.3 Plug and Play

In addition to power management, ACPI provides controls and information so that the operating

system can facilitate Plug and Play device enumeration and configuration. ACPI is used only to

enumerate and configure devices that do not have other hardware standards for enumeration and

configuration. PCI devices on a desktop board, for example, are not enumerated by ACPI.

1.12.2 APM

APM makes it possible for the computer to enter an energy saving standby mode. The standby mode

can be initiated in the following ways:

• Time-out period specified in the BIOS Setup program

• Suspend/Resume switch connected to the front panel sleep connector

• From the operating system, such as the Suspend menu item in Windows 98 SE

In standby mode, the board can reduce power consumption by spinning down hard drives, and

†

reducing power to or turning off VESA

be enabled or disabled in the BIOS Setup program.

While in standby mode, the system retains the ability to respond to external interrupts and service

requests, such as incoming faxes or network messages. Any keyboard or mouse activity brings the

system out of standby mode and immediately restores power to the monitor.

The BIOS enables APM by default, but the operating system must support an APM driver for the

power-management features to work. For example, Windows 98 SE supports the powermanagement features upon detecting that APM is enabled in the BIOS.

Table 11 lists the devices or specific events that can wake the computer from specific states.

DPMS-compliant monitors. Power-manageme nt mode can

33

Page 34

Intel Desktop Board D810E2CB Technical Product Specification

Table 11. A PM Wake-up Devices and Events

These devices/events can wake up the computer… …from this state

Power switch Soft-off

RTC alarm* Soft-off, suspend

LAN Soft-off, suspend

PME# Soft-off, suspend

USB Suspend

PS/2 Suspend

* Unattended WakeMode – display will be video BIOS string only

For information about Refer to

Enabling or disabling power management in the BIOS Setup program Section 4.6, page 97

The board’s compliance level with APM Table 3, page 16

1.12.3 Hardware Support

CAUTION

If Wake on LAN and Instantly Available technology features are used, the power supply must be

capable of providing adequate +5 V standby current. Failure to provide adequate standby current

can damage the power supply. The total amount of standby current required depends on the wake

devices supported and manufacturing options. Refer to Section 2.11.2 on page 66 for additional

information.

The board provides several hardware features that support power management, including:

• Power connector

• Fan connectors

• Wake on LAN technology

• Instantly Available technology

• Wake on Ring

• Resume on Ring

• Wake from USB

• PME# wakeup support

Wake on LAN technology and Instantly Available technology require power from the +5 V standby

line. The sections discussing these features describe the incremental standby power requirements for

each.

Wake on Ring and Resume on Ring enable telephony devices to access the computer when it is in a

power-managed state. The method used depends on the type of telephony device (external or

internal) and the ACPI or APM state beingused.

NOTE

✏

The use of Wake on Ring, Resume on Ring, and Wake from USB technologies from an ACPI state

require the support of an operating system that provides full ACPI functionality.

34

Page 35

Product Description

1.12.3.1 Power Connector

When used with an ATX-compliant power supply that supports remotepower on/off, the D810E2CB

board can turn off the system power through software control.

With soft-off enabled, if power to the computer is interrupted by a power outage or a disconnected

power cord, when power resumes, the computer returns to the power state it was in before power

was interrupted (on or off).

For information about Refer to

The location of the power connector Figure 6, page 51

The signal names of the power connector Table 32, page 53

The ATX specification Table 3, page 16

The MicroATX specification and the SFX Power Supply Design Guide Table 3, page 16

1.12.3.2 Fan Connectors

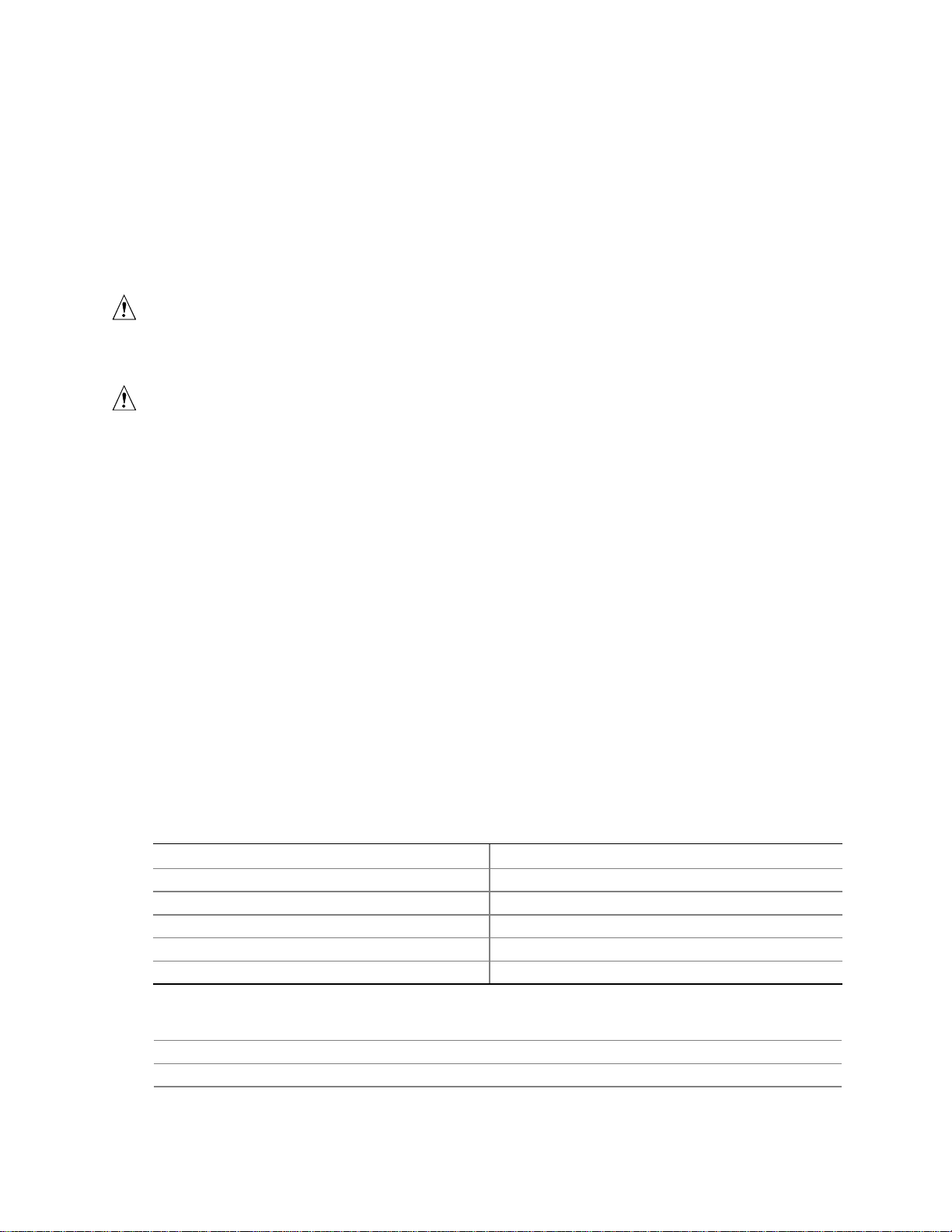

Table 12 describes the functions of the fan connectors.

Table 12. Fan Connector Descriptions

Connector Function

Processor fan (fan 1) Provides +12 V DC for a processor fan or active fan heatsink.

Chassis fan (fan 2) Provides +12 V DC for a system or chassis fan.

For information about Refer to

The location of the fan connectors Figure 6, page 51

The signal names of the processor fan connector Table 31, page 52

The signal names of the chassis fan connector Table 34, page 53

1.12.3.3 Wake on LAN T echnology

CAUTION

For Wake on LAN technology, the 5-V standby line for the power supply must be capable of

providing adequate +5 V standby current. Failure to provide adequate standby current when

implementing Wake on LAN technology can damage the power supply. Refer to Section 2.11.2 on

page 66 for additional information.

Wake on LAN technology enables remote wakeup of the computer through a network. The LAN

subsystem monitors network traffic at the Media Independent Interface. Upon detecting a Magic

†

Packet

D810E2CB board supports Wake on LAN technology through the PCI bus PME# signal.

frame, the LAN subsystem asserts a wakeup signal that powers up the computer. The

35

Page 36

Intel Desktop Board D810E2CB Technical Product Specification

1.12.3.4 Instantly Available T echnology

CAUTION

For Instantly Available technology, the 5-V standby line for the power supply must be capable of

providing adequate +5 V standby current. Failure to provide adequate standby current when

using this feature can damage the power supply. Refer to Section 2.11.2 on page 66 for additional

information.

Instantly Available technology enables the board to enter the ACPI S3 (Suspend-to-RAM) sleepstate. While in the S3 sleep-state, the computer will appear to be off. The power supply appears to

be off, the fans are off, and the front panel power LED will be yellow (unless a single color LED is

installed, in which case, it will be off.) When signaled by a wake-up device or event, the system

quickly returns to its last known wake state. Table 10 on page 33 lists the devices and events that

can wake the computer from the S3 state.

The D810E2CB board supports the PCI Bus Power Management Interface Specification.For

information on the versions of this specification, see Section 1.3. Add-in boards that also support

this specification can participate in power management and can be used to wake the computer.

The use of Instantly Available technology requires operating system support and PCI 2.2 compliant

add-in cards and drivers.

1.12.3.5 Wake on Ring

NOTE

✏

Wake on Ring requires the use of a modem (external USB, or modem connected to serial port A)

that supports the Wake on Ring feature.

The operation of Wake on Ring can be summarized as follows:

• Powers up the computer from the ACPI S5 state or from APM soft-off mode

• Requires two calls to access the computer:

First call restores the computer from an ACPI S5 state or powers up the computer from

APM soft-off mode.

Second call enables access (when the appropriate software is loaded).

• Detects incoming calls for external USB modems. The USB bus is monitored for the

RING_DETECT signal.

Table 13 outlines wake on ring support for modems.

Table 13. Wake on Ring Support for Modems

State USB Modem Serial Port Modem PCI Bus Modem (via PME#)

S1 Refer to Section 1.12.3.6 Refer to Section 1.12.3.6 Supported

S3 Supported Supported Supported

S5 Not supported Supported Not supported

Soft-off Not supported Supported Supported

Suspend Refer to Section 1.12.3.6 Refer to Section 1.12.3.6 Supported

36

Page 37

Product Description

1.12.3.6 Resume on Ring

The operation of Resume on Ring can be summarized as follows:

• Resumes operation from the ACPI S1 state or APM suspend mode

• Requires only one call to access the computer

• Detects incoming call similarly for external and internal modems

1.12.3.7 Wake from USB

USB bus activity wakes the computer from an ACPI S1 or S3 state or APM suspend mode.

NOTE

✏

Wake from USB requires the use of a USB peripheral that supports Wake from USB. Wake from

USB is not supported in APM soft-off mode.

1.12.3.8 PME# Wakeup Support

When the PME# signal on the PCI bus is asserted, the computer wakes from an ACPI S1 or S3

state.

37

Page 38

Intel Desktop Board D810E2CB Technical Product Specification

38

Page 39

2 Technical Reference

What This Chapter Contains

2.1 Introduction................................................................................................................39

2.2 Memory Map..............................................................................................................39

2.3 I/O Map...................................................................................................................... 40