ICST AV9342F-T, ICS9342F-T Datasheet

Integrated

Circuit

Systems, Inc.

ICS9342

Third party brands and names are the property of their respective owners.

9342 Rev E 9/06/00

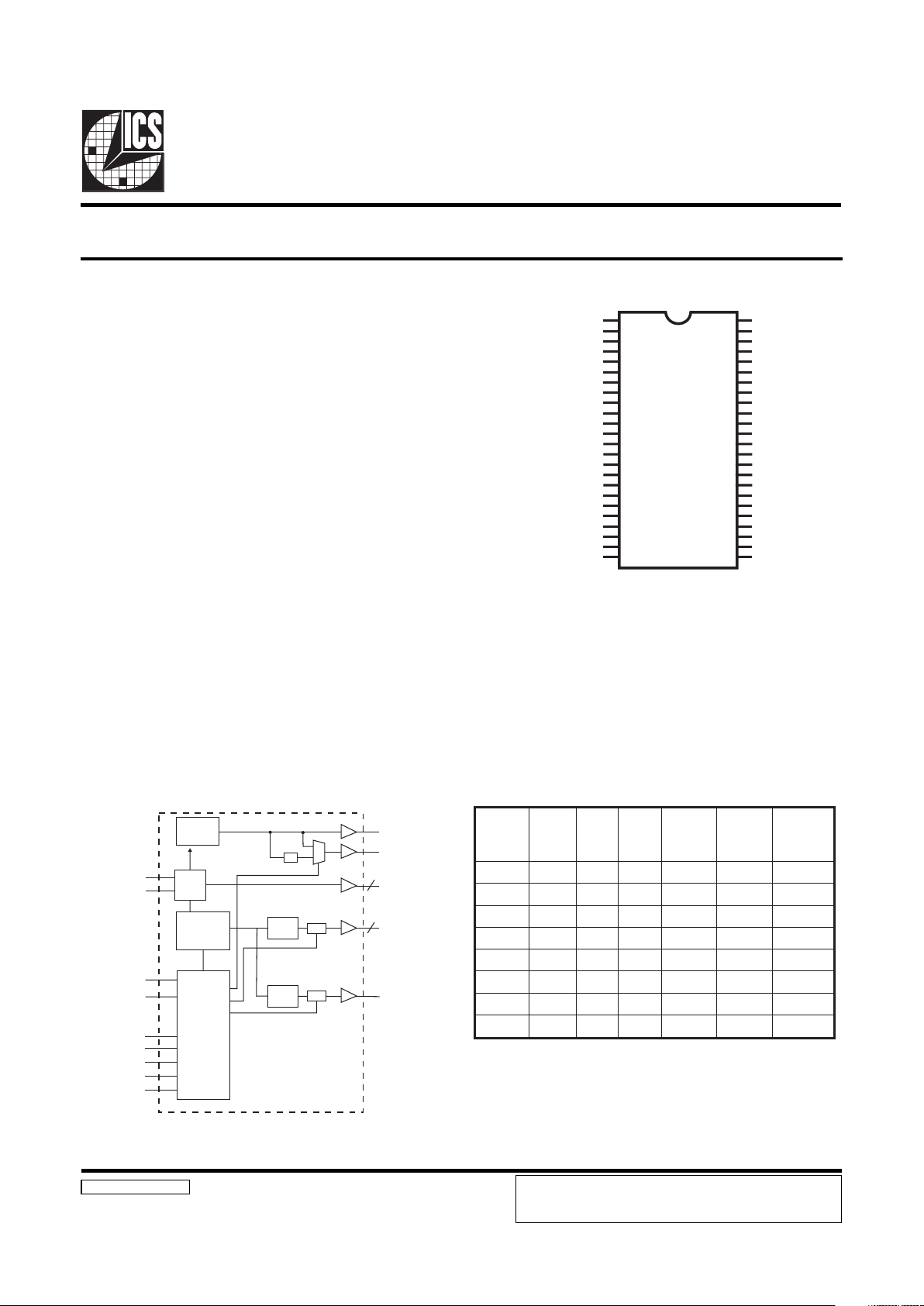

Pin Configuration

48-Pin 300mil SSOP

Recommended Application:

Power PC System Clock

Output Features:

• 12- CPUs @ 3.3V, up to 146MHz

• 1- PCIREF @ 3.3V, up to 73MHz

• 1 - OUT 3.3V, 64MHz

• 1 - OUT/2 3.3V, OUT/2MHz

• 2 - REF @ 3.3V, 14.318MHz

Features:

• Up to 146MHz frequency support

• Support power management: CPU, PCI stop and power

down mode.

• Spread spectrum for EMI control (0 to -0.5%, ± 0.25%).

• Uses external 14.318MHz crystal

• FS pins for frequency select

• Support for industrial temperature range (-40C° to 85C°)

Key Specifications:

• CPU Output Skew: <200ps

• CPU - PCI Output Skew: <500ps

• CPU Output Jitter: <150ps

• PCI Output Jitter: <500ps

133MHz Clock Generator and Integrated Buffer for PowerPC™

VDDREF

REF1

REF0

GNDREF

X1

X2

*PD#

*CPU-STOP#

VDD

GND

*PCI_STOP#

*SS_EN#

VDDPCI

PCIREF

GNDPCI

*FS0

*FS1

*FS2

VDDFP

GNDFP

*TEST#/OUT

*BOOST#/OUT_DIV2

*PDFP#

VDDA

OUTSEL1*

VDDCPU

GNDCPU

CPU0

CPU1

CPU2

VDDCPU

GNDCPU

CPU3

CPU4

CPU5

VDDCPU

GNDCPU

CPU6

CPU7

CPU8

VDDCPU

GNDCPU

CPU9

CPU10

CPU11

VDDCPU

GNDCPU

OUTSEL0*

ICS9342

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

* Internal pull-up resistor of 120K to VDD

on indicated inputs.

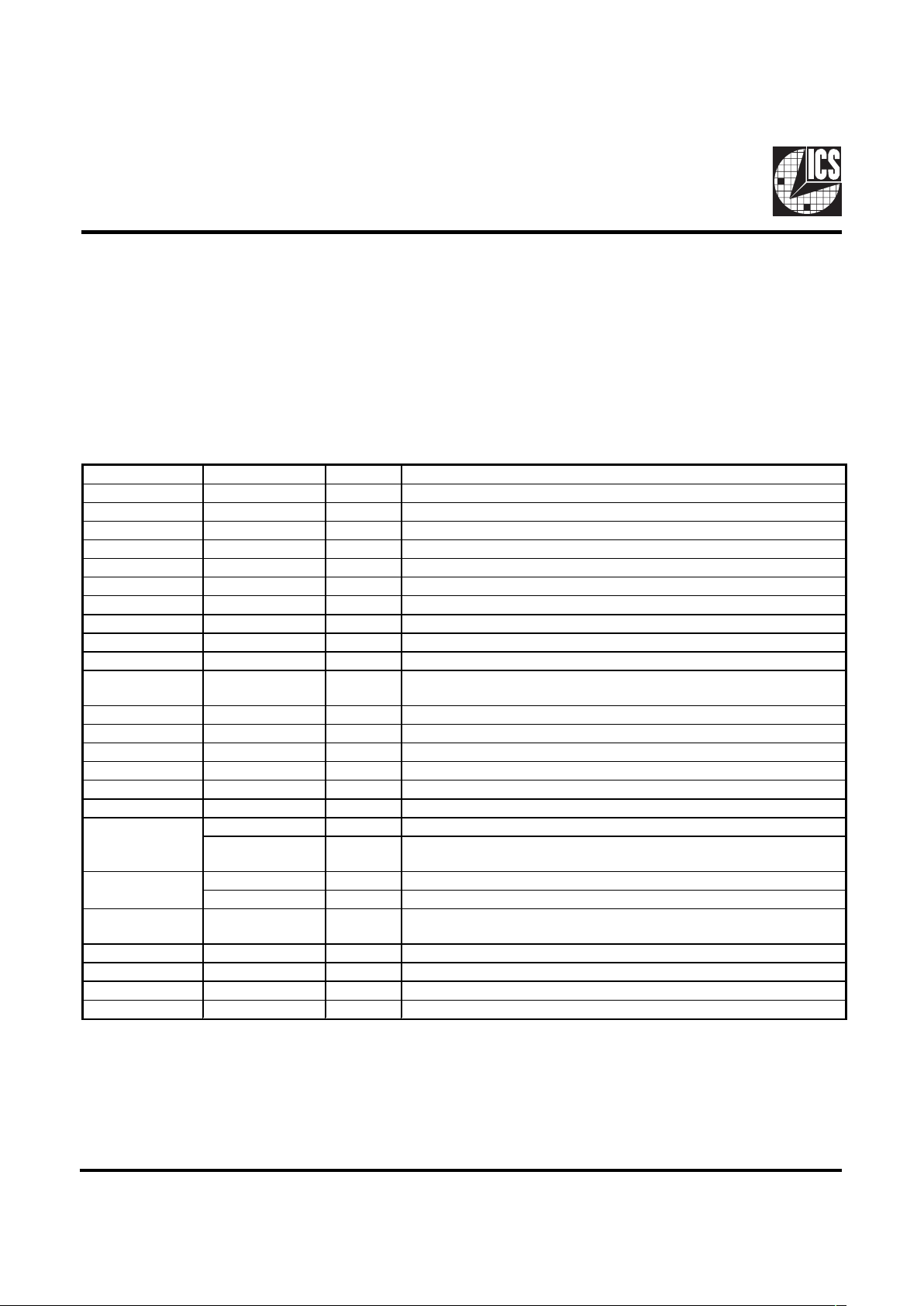

Functionality

Block Diagram

SS_EN#

OUTSEL (1:0)

PLL2

PLL1

Spread

Spectrum

OUT

OUT/DIV2

CPUCLK (11:0)

12

2

PCIREF

X1

X2

XTAL

OSC

CPU

DIVDER

PCI

DIVDER

Stop

Stop

FS (2:0)

PD#

PDFP#

TEST#

BOOST#

Control

Logic

Config.

Reg.

/ 2

REF (1:0)

TSET2SF1SF0SF

UPC

zHM

ICP

zHM

FER

zHM

1111 33.33133.33813.41

1110 00.00133.33813.41

1101 33.3833.33813.41

1100 66.6633.33813.41

1011 33.33166.66813.41

1010 00.00166.66813.41

1001 33.3866.66813.41

1000 66.6666.66813.41

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS93 42

Third party brands and names are the property of their respective owners.

Pin Configuration

General Description

The ICS9342 generates all clocks required for high speed PowerPC RISC microprocessor systems. With a zero delay buffer

chip such as the ICS9112-17 multiple PCI clock outputs can be generated in phase with PCIREF.

Spread Spectrum may be enabled by driving the SS_EN# pin low. Spread spectrum typically reduces system EMI by 8dB to

10dB. This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS9342

employs a proprietary closed loop design, which tightly controls the percentage of spreading over process and temperature

variations.

PIN NUMBER PIN NAME TYPE DESCRIPTION

1 VDDREF PWR Ref(1:0), XTAL power supply, nominal 3.3V

2,3 REF[1:0] OU T 14.318 MHz reference clocks

4 GNDREF PWR Ground pin for the REF outputs

5 X1 IN Crystal input,nominally 14.318M H z.

6 X2 OUT Crystal output, nominally 14.318MHz.

7 PD # IN Pow ers down chip, active low .

8 CPU_STOP# IN Stops all CPUCLKs [11:0] at logic 0 level, when input low

9 VDD PWR 3.3V power for the digital core.

10 GND PWR Ground pin for the digital core.

11 PCI_STO P# IN Drives P CIREF to logic 0 level, when input low

12 SS_EN# IN

Spread spectrum is turned on by driving this input low and turned off by

drivin

g

it high.

13 VDDPCI PWR Power supply for PCIREF, nominal 3.3V.

14 PCIREF OU T Reference clock for PCI Zero Delay Buffer.

15 GNDPCI PWR Ground pin for PCIREF.

18, 17, 16 FS (2:0) IN Frequency select pins.

19 VDDFP PWR 3.3V power for the Fixed PLL core.

20 GNDFP PER Ground pin for the Fixed PLL core.

OUT OUT 3.3V OUT reference clock.

TEST# IN

Logic input to select over clocking or under clocking frequencies.

(latched in

p

ut)

OUT_DIV2 OUT 3.3V 1/2 frequency OUT reference clock.

BOOST# IN Logic input to select normal or test mode frequencies. (latched input)

23 PDFP# IN

Powers down Fixed PLL. When driven to low, OUT and OUT_DIV2 clocks

will be sto

pp

ed

24 VDDA PWR 3.3V power for the PLL core

48, 25 OUTSEL(1:0) IN Frequency select pins for OUT and OUT_DIV2 clocks.

26, 31, 36, 41, 46 GNDCPU PWR Ground pin for CPU clocks.

27, 32, 37, 42, 47 VDDCPU PWR 3.3V power supply for CPU clocks.

21

22

3

ICS93 42

Third party brands and names are the property of their respective owners.

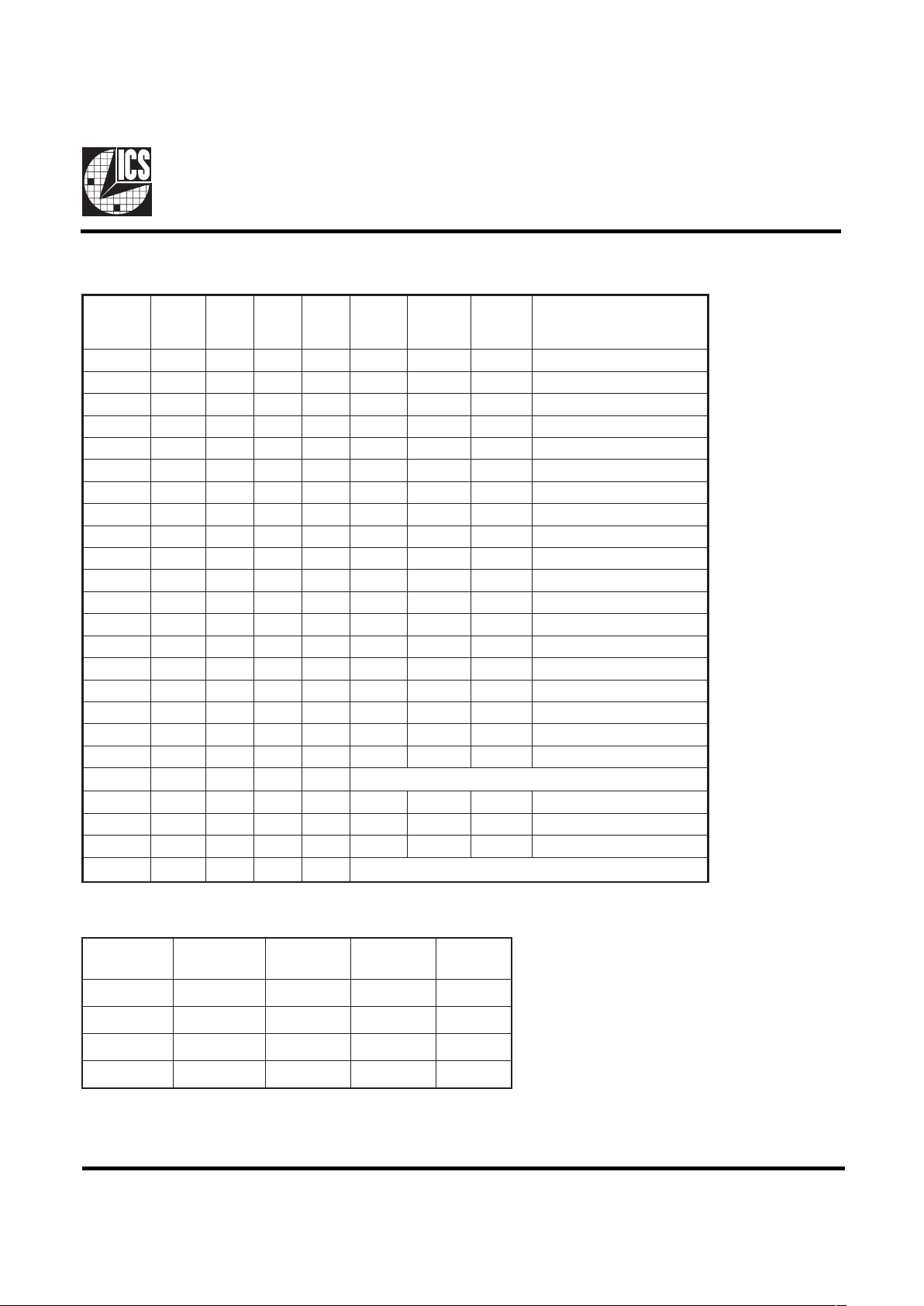

Frequency Selection

1LES_TUO0LES_TUO

TUO

)zHM(

2VID_TUO

)zHM(

FER

)zHM(

118442813.41

100402813.41

014623813.41

0084#84813.41

#TSOOB#TSET2SF1SF0SF

UPC

zHM

ICP

zHM

FER

zHM

EULAV/EPYTSS

delbaneSSfI

X 1 111 33.33133.33813.41daerpSnwoD%5.0-ot0

X1110 00.00133.33813.41daerpSnwoD%5.0-ot0

X1101 33.3833.33813.41daerpSnwoD%5.0-ot0

X1100 66.6633.33813.41daerpSnwoD%5.0-ot0

X1011 33.33166.66813.41daerpSnwoD%5.0-ot0

X1010 00.00166.66813.41daerpSnwoD%5.0-ot0

X1001 33.3866.66813.41daerpSnwoD%5.-ot0

X 1 000 66.6666.66813.41daerpSnwoD%5.0-ot0

1 0 111 26.6416.63813.41daerpSretneC%52.0+

10110 99.9016.63813.41daerpSretneC%52.0+

10101 85.196.63813.41daerpSretneC%52.0+

10100 13.376.63813.41daerpSretneC%52.0+

10011 26.6413.37813.41daerpSretneC%52.0+

10010 99.9013.37813.41daerpSretneC%52.0+

10001 85.193.37813.41daerpSretneC%52.0+

1 0 000 13.373.37813.41daerpSretneC%52.0+

0 0 111 89.91100.03813.41daerpSretneC%52.0+

00110 00.0900.03813.41daerpSretneC%52.0+

00101 39.4700.03813.41daerpSretneC%52.0+

00100 8/feR=ICP,4/feR=UPC,edoMtseT

00011 89.91100.06813.41daerpSretneC%52.0+

00010 00.0900.06813.41daerpSretneC%52.0+

00001 39.4700.06813.41daerpSretneC%52.0+

0 0 000 stuptuolla,etatsirT

Loading...

Loading...