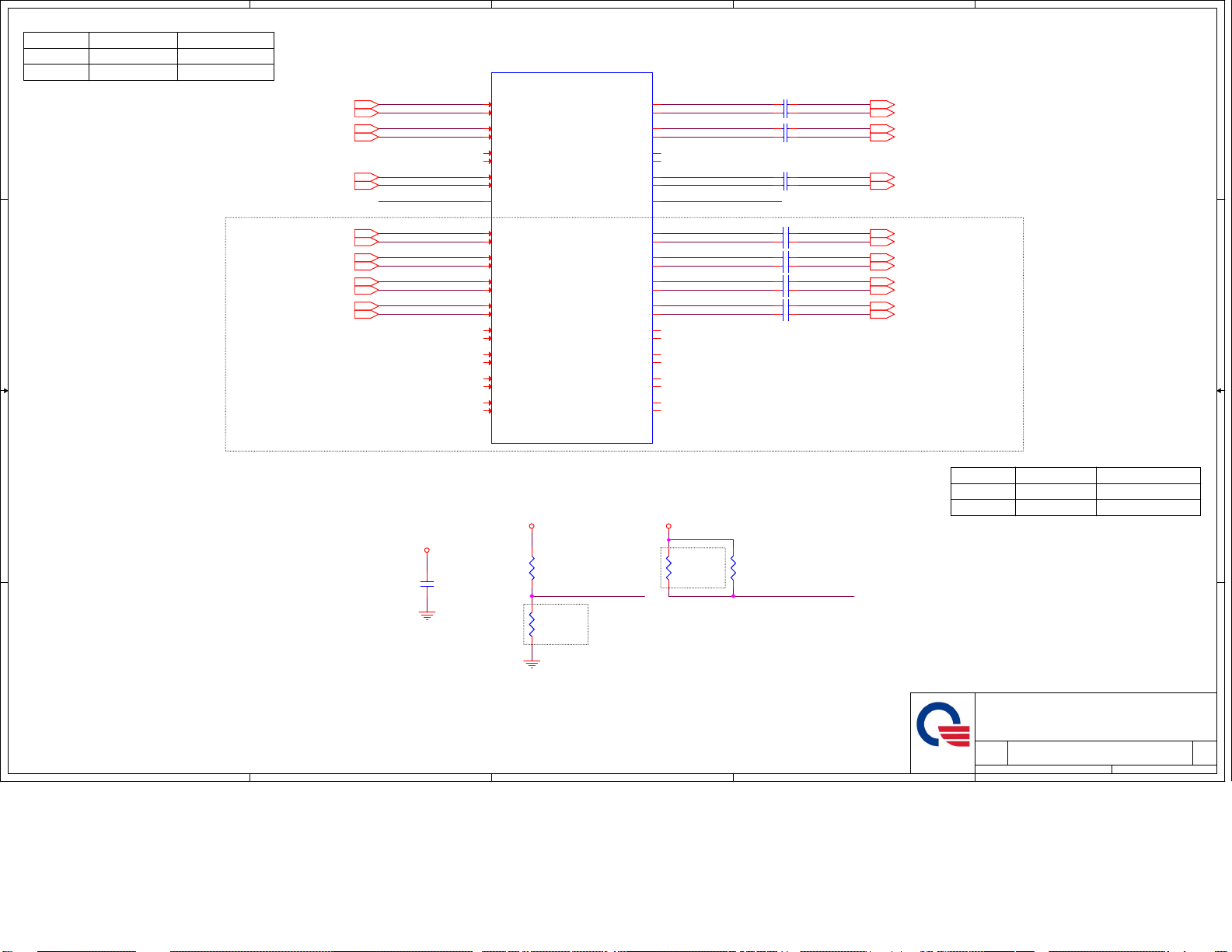

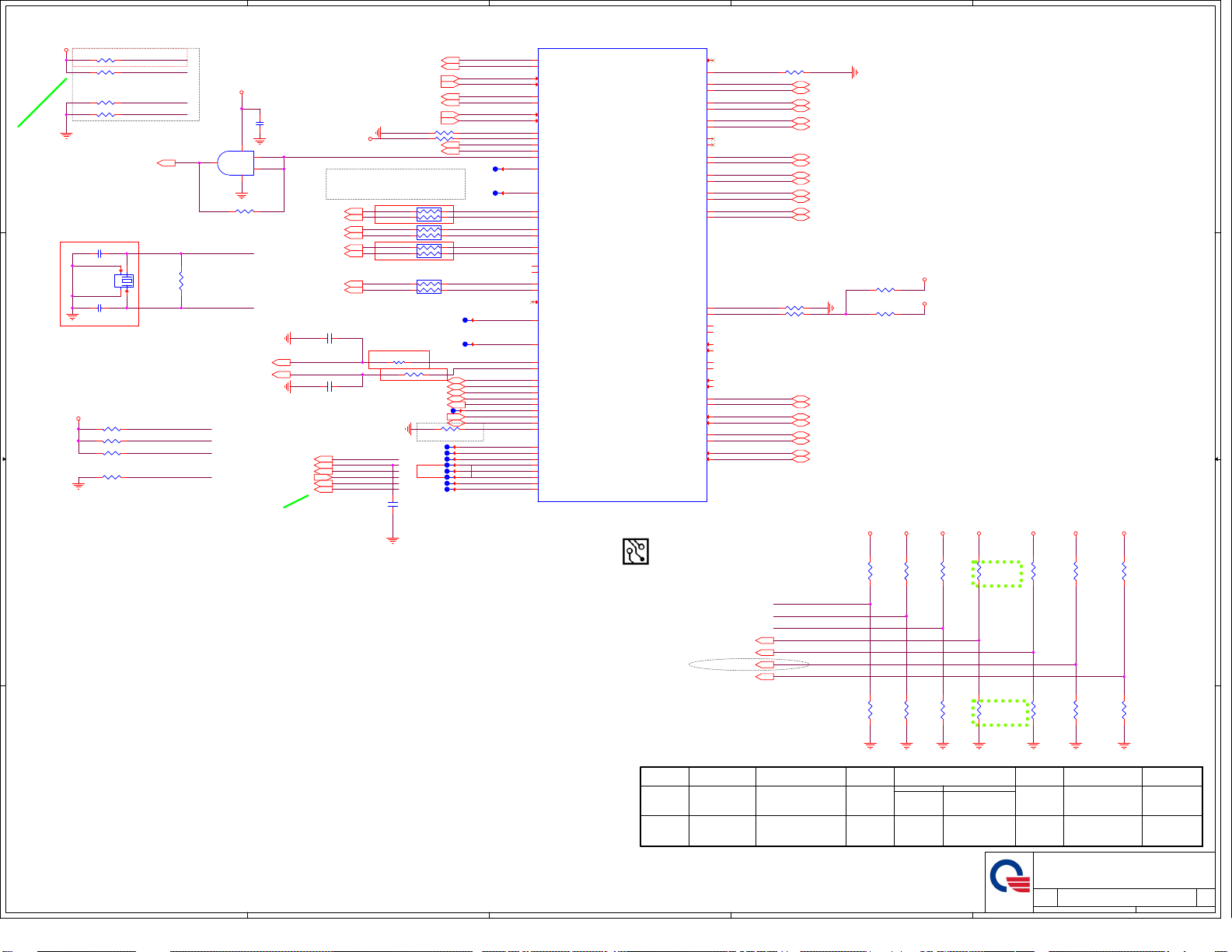

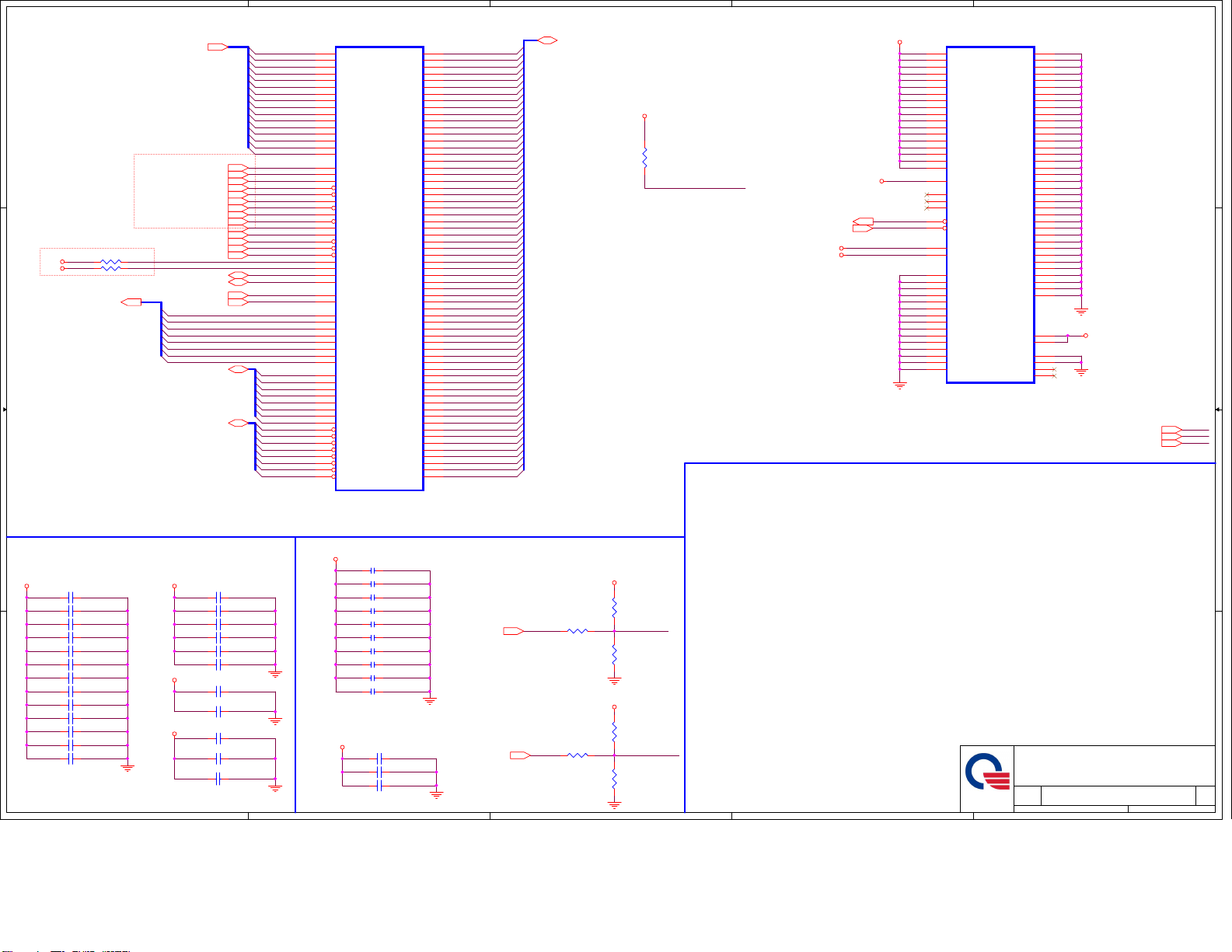

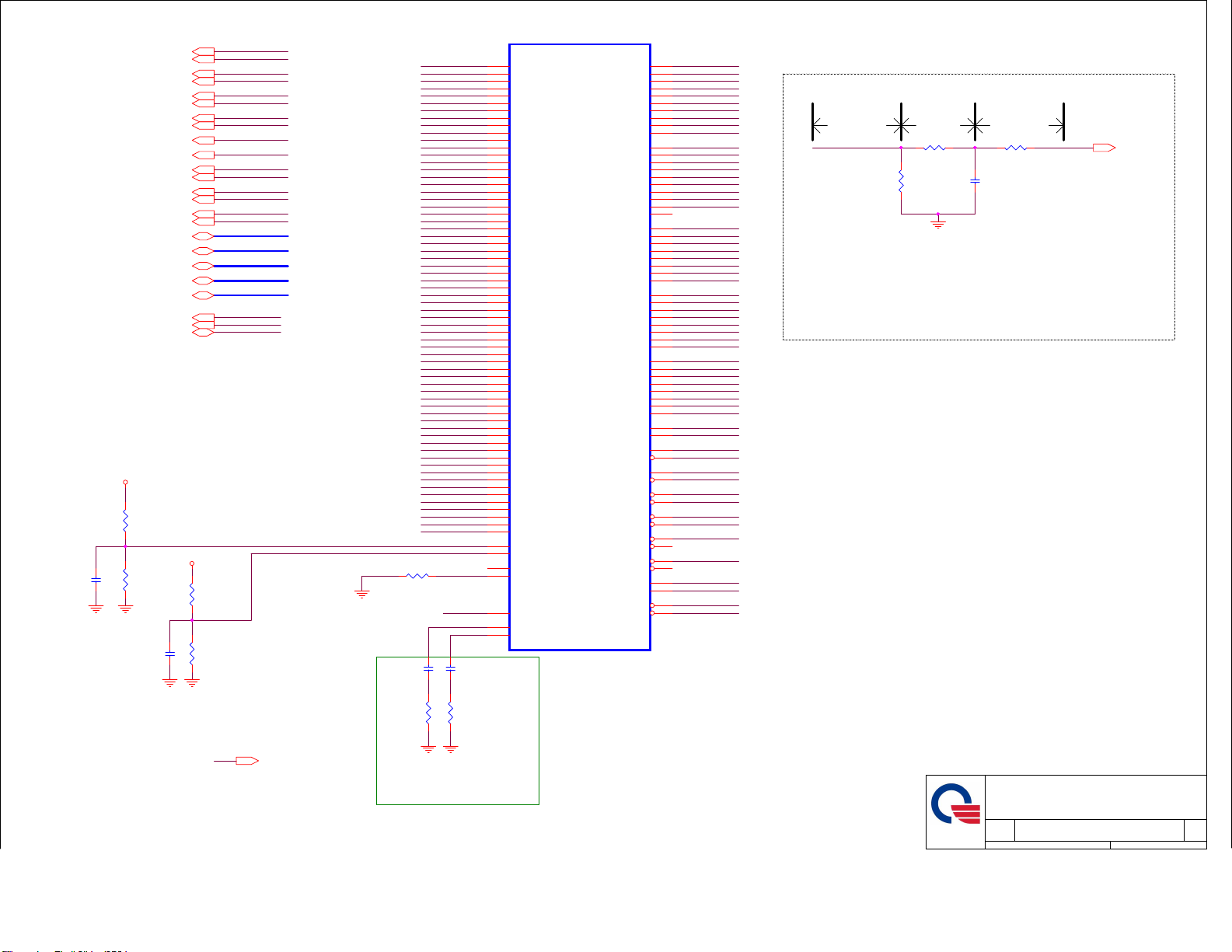

HP Probook 455 G3 Schematics

5

4

3

2

1

400 series Palazzo / X73A (UMA/DIS) Schematics

01

D D

DDR3L 1600MHz

16GB

PAGE 10

DDR3L 1600MHz

16GB

PAGE 09

Single Channel-B

DDR3L 1600

DDI0 x2

CARRIZO (L)

DDI1

DIS only

x2

For Carrizo L

gDDR3

1GB/2GB

gDDR3

1GB/2GB

gDDR3

1GB/2GB

gDDR3

1GB/2GB

4 pcs of x16 PAGE 16

C C

64bit

iGP

Processor : Daul Core

Power : 15 (Watt)

DDI2

x4

x4

Graphics Controller

AMD Meso Pro 64-bit gDDR3

M/B down dGPU S3 Package 18W TDP

PAGE 11~15

SATA - ODD

SATA1 3GB/s

PAGE 37

SATA0 6GB/sPrimary HDD

2.5" / 7, 9.5mm

PAGE 37

B B

InfineonTPM

48MHz

32.768KHz

PAGE 26SLB9670 TT1.2

LPC Interface

Keyboard

PAGE 32

Battery PAGE 57

FAN

A A

Function Conn.

PAGE 35 HD Audio

KBC

Nuvoton

NPCE586HA0MX

Embedded Controller

PAGE 39, 40

128TQFP

SPI Interface

System BIOS

SPI ROM 8MB

PAGE 41

PAGE 25

5

4

iFCH

USB2.0 Interface

PCIE Gen 1 x 1 Lane

PAGE 2~8

HD and FHD

eDP

PAGE 19

DP to VGA Controller

DP Switch IC

Realtek RTD2168

DP x2

PAGE 20

PS8339A PAGE 21

HDMI

HDMI CONN

PAGE 22

USB2.0 Interface USB 2.0 standard port

USB 2.0 standard ports

USB3.0 Interface

USB 3.0 standard port

CN18 (Upper Left)

USB 3.0 standard port

CN19 (Lower Left)

PAGE 29NGFF

WLAN Combo

USB3.0 Re-driver IC

PTN36001 PAGE 27

Camera

Port2

PAGE 19

Fingerprint

VFS495

Port 4

PAGE 17

10/100/1000 NIC

Realtek RTL8111HSH

PAGE 24

Card Reader controller

RTS5237-GR

PAGE 34

RJ45

MicroSD Socket

Digital MIC

PAGE 24

PAGE 34

PAGE 19

on Daugther Board

on Forced Pad Board

Conexant

CX7501

Speaker

PAGE 23

Combo Jack

PAGE 23

3

PAGE 24

2

CRT CONN

PAGE 20

PAGE 24

PAGE 24

PAGE 27

PAGE 27

PCB 6L STACK UP(1.2mm)

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1(High)

LAYER 4 : IN2(Low)

LAYER 5 : SVCC

LAYER 6 : BOT

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

NB5

NB5

NB5

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1 62Friday, July 24, 2015

1 62Friday, July 24, 2015

1 62Friday, July 24, 2015

1A

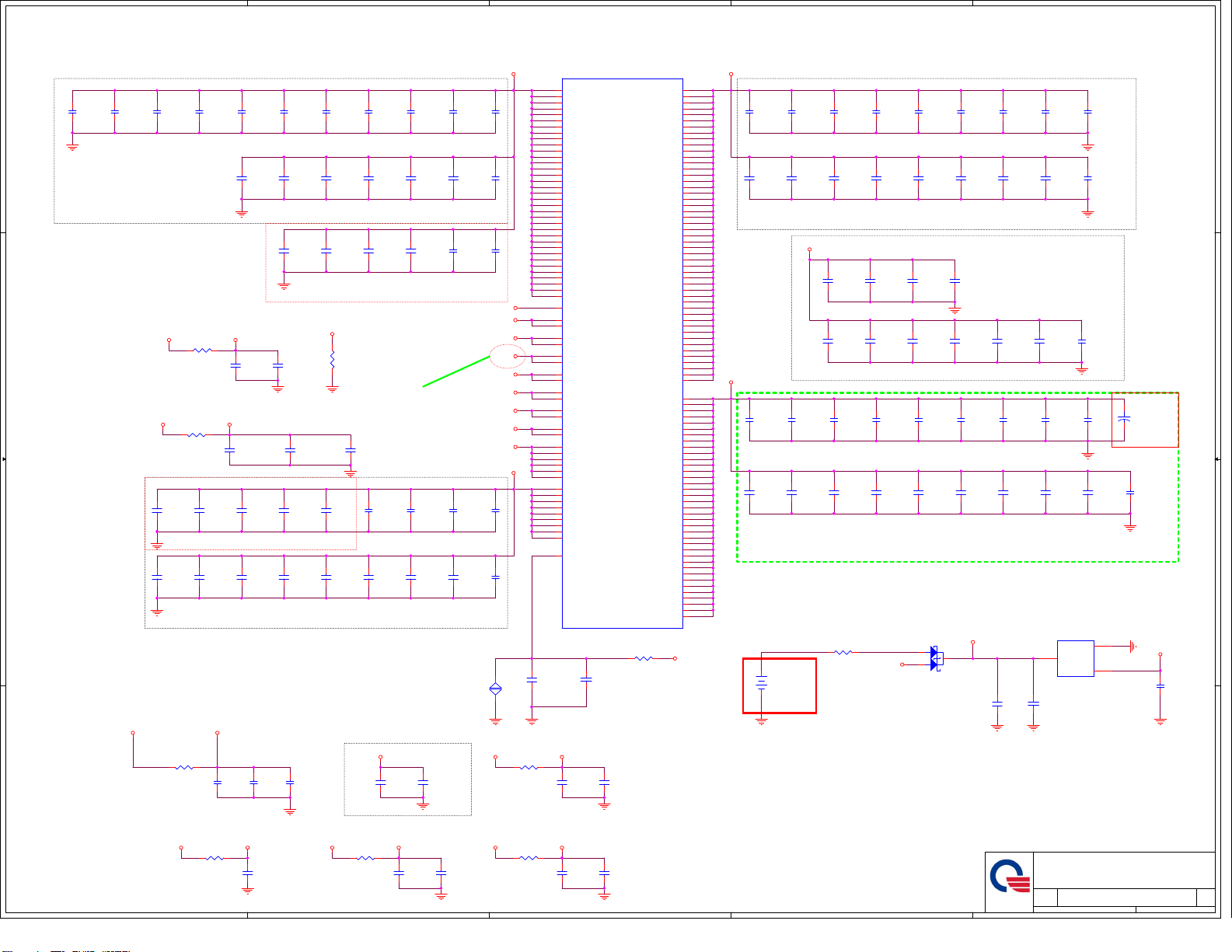

5

4

3

2

1

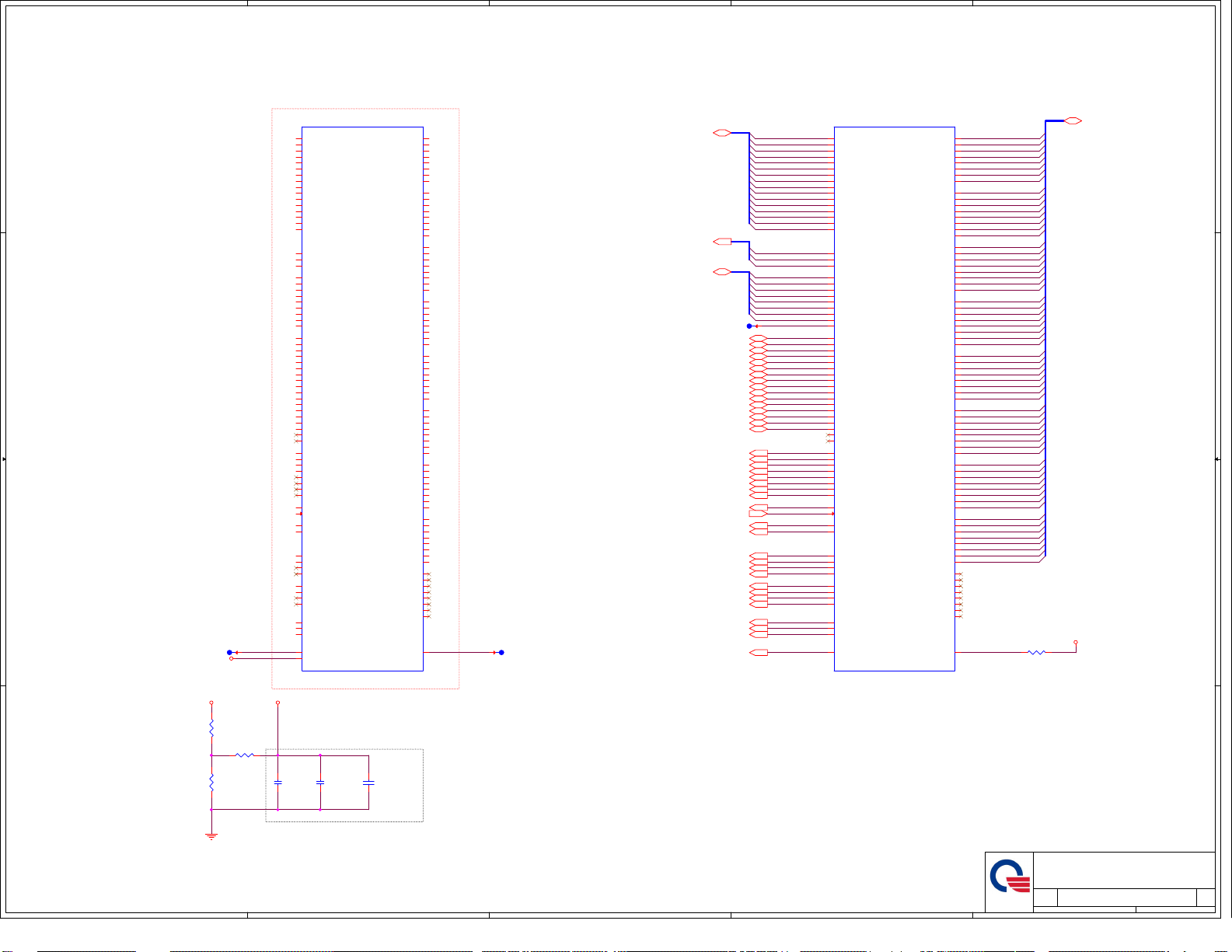

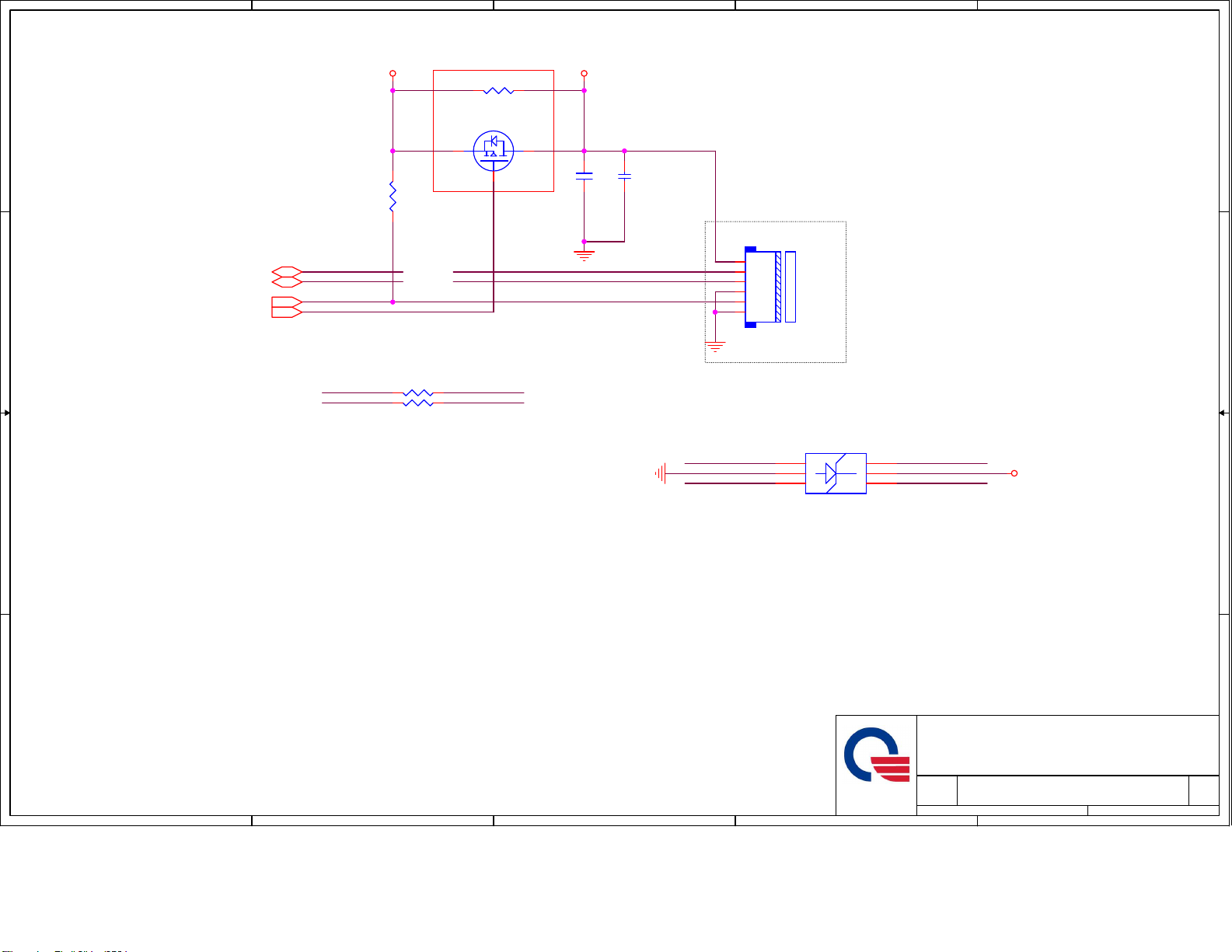

QBCON TOPBSQ

Carrizo

Carrizo DB phase use AJ1802CUT00

D D

AJ1802CUT01

AJ1802CUT02

U24B

U10

PCIE_RXP0_LAN[24]

PCIE_RXN0_LAN[24]

PCIE_RXP1_WLAN[29]

PCIE_RXN1_WLAN[29]

PCIE_RXP3_CARD[34]

PCIE_RXN3_CARD[34]

U9

T6

T5

T9

T8

P7

P6

U7

P_GPP_RXP[0]

P_GPP_RXN[0]

P_GPP_RXP[1]

P_GPP_RXN[1]

P_GPP_RXP[2]

P_GPP_RXN[2]

P_GPP_RXP[3]

P_GPP_RXN[3]

P_ZVDDP

PCIE

P_GPP_TXP[0]

P_GPP_TXN[0]

P_GPP_TXP[1]

P_GPP_TXN[1]

P_GPP_TXP[2]

P_GPP_TXN[2]

P_GPP_TXP[3]

P_GPP_TXN[3]

P_ZVSS/P_RX_ZVDDP

R1

PCIE_TXP0_LAN_C

R2

PCIE_TXN0_LAN_C

R4

PCIE_TXP1_WLAN_C

R3

PCIE_TXN1_WLAN_C

N1

N2

N4

PCIE_TXP3_C

N3

PCIE_TXN3_C

U6

P_ZVSS_P_RX_ZVDD_095P_ZVDDP_P_TX_ZVDD_095

C445 0.1U/16V/X7R_4

C444 0.1U/16V/X7R_4

C447 0.1U/16V/X7R_4

C446 0.1U/16V/X7R_4

C443 0.1U/16V/X7R_4

C449 0.1U/16V/X7R_4

PCIE_TXP0_LAN [24]

PCIE_TXN0_LAN [24]

PCIE_TXP1_WLAN [29]

PCIE_TXN1_WLAN [29]

PCIE_TXP3_CARD [34]

PCIE_TXN3_CARD [34]

CZ support GFX 0~7 & Gen3

02

CZ-L only support GFX 0~3 & Gen2

P10

L10

P9

N6

N5

N9

N8

L7

L6

L9

K6

K5

K9

K8

J7

J6

P_GFX_RXP[0]

P_GFX_RXN[0]

P_GFX_RXP[1]

P_GFX_RXN[1]

P_GFX_RXP[2]

P_GFX_RXN[2]

P_GFX_RXP[3]

P_GFX_RXN[3]

P_GFX_RXP[4]

P_GFX_RXN[4]

P_GFX_RXP[5]

P_GFX_RXN[5]

P_GFX_RXP[6]

P_GFX_RXN[6]

P_GFX_RXP[7]

P_GFX_RXN[7]

PEG_RXP0[11]

PEG_RXN0[11]

PEG_RXP1[11]

PEG_RXN1[11]

PEG_RXP2[11]

C C

PEG_RXN2[11]

PEG_RXP3[11]

PEG_RXN3[11]

ALF@1028:

HP request to add 4Lanes

For DIS GPU

FP4 REV 1.0

*FP4

B B

+0.95V +0.95V

+0.95V

R81

C434

0.1U/16V/X7R_4

*CZL@1K/F_4

P_ZVSS_P_RX_ZVDD_095 P_ZVDDP_P_TX_ZVDD_095

P_GFX_TXP[0]

P_GFX_TXN[0]

P_GFX_TXP[1]

P_GFX_TXN[1]

P_GFX_TXP[2]

P_GFX_TXN[2]

P_GFX_TXP[3]

P_GFX_TXN[3]

P_GFX_TXP[4]

P_GFX_TXN[4]

P_GFX_TXP[5]

P_GFX_TXN[5]

P_GFX_TXP[6]

P_GFX_TXN[6]

P_GFX_TXP[7]

P_GFX_TXN[7]

M2

M1

L1

L2

L4

L3

J1

J2

J4

J3

H2

H1

G1

G2

G4

G3

GFX_TX0P_C

GFX_TX0N_C

GFX_TX1P_C

GFX_TX1N_C

GFX_TX2P_C

GFX_TX2N_C

GFX_TX3P_C

GFX_TX3N_C

R91

CZ@196/F_4

C450 DIS@0.22U/10V_4

C453 DIS@0.22U/10V_4

C458 DIS@0.22U/10V_4

C461 DIS@0.22U/10V_4

C454 DIS@0.22U/10V_4

C457 DIS@0.22U/10V_4

C456 DIS@0.22U/10V_4

C460 DIS@0.22U/10V_4

R84

*CZL@1.69K/F_4

PEG_TXP0 [11]

PEG_TXN0 [11]

PEG_TXP1 [11]

PEG_TXN1 [11]

PEG_TXP2 [11]

PEG_TXN2 [11]

PEG_TXP3 [11]

PEG_TXN3 [11]

Platform

Carrizo CH4222K9B04

Gen 3

Gen 1/Gen 2

P/NType

CH4103K1B08Carrizo-L

R78

CZ@196/F_4

A A

5

4

CZ: R91 & R78

Z-L: R81 & R84

C

3

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

NB5

NB5

2

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

Carrizo 1/7 (PCIE)

Carrizo 1/7 (PCIE)

Carrizo 1/7 (PCIE)

Friday, July 24, 2015 2 62

Friday, July 24, 2015 2 62

Friday, July 24, 2015 2 62

1

1A

1A

1A

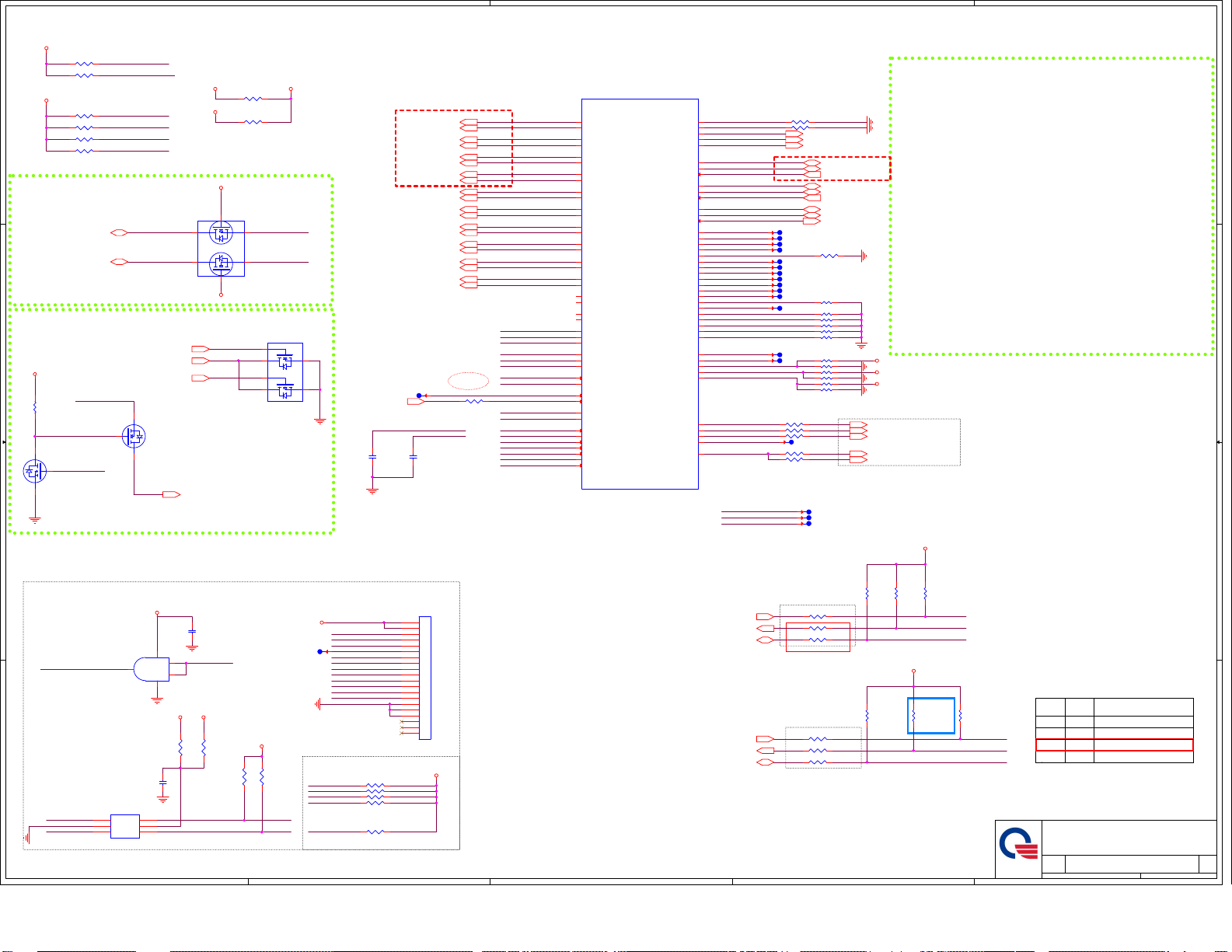

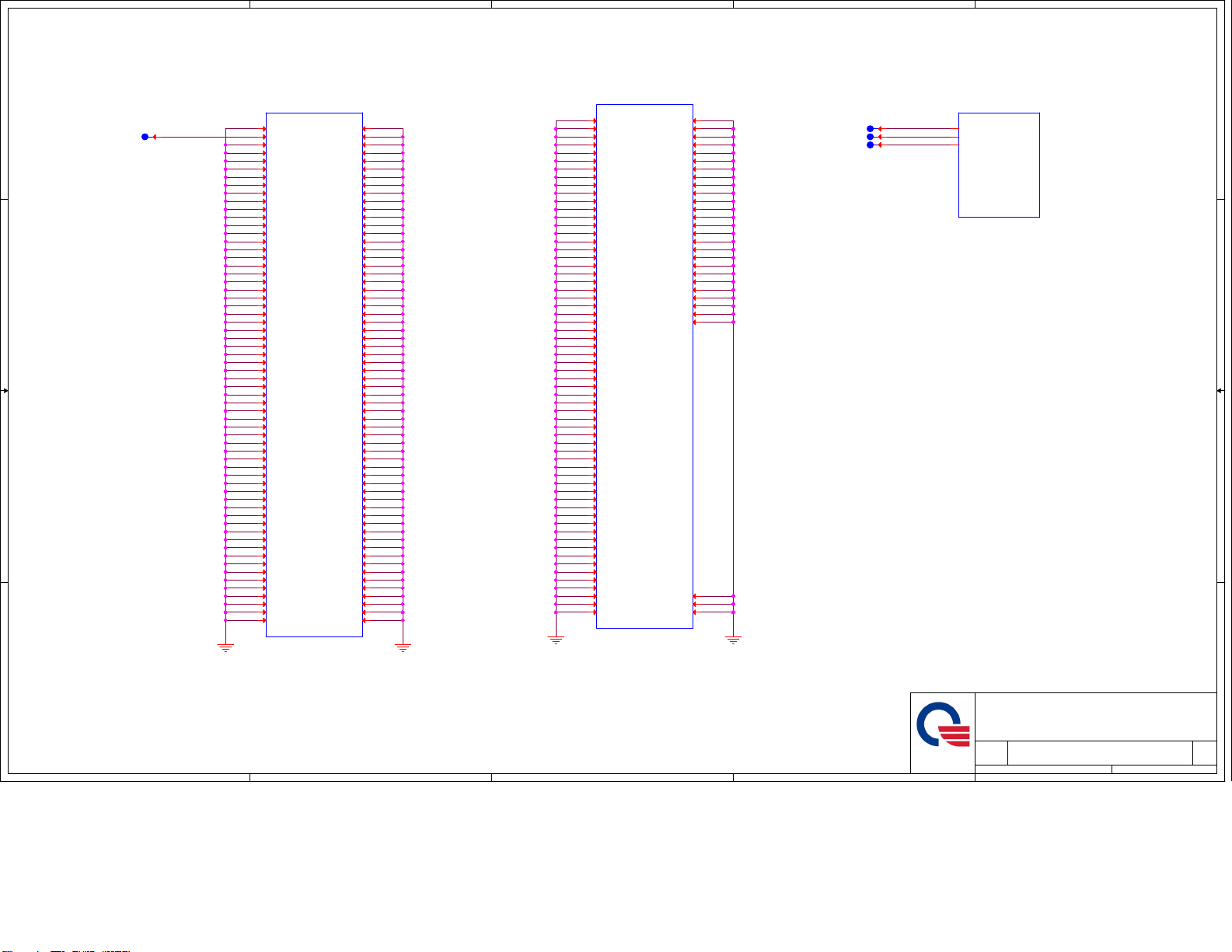

5

4

3

2

1

03

Ronny@1013:

2 So-Dimm per Channel (B)

D D

C C

B B

TP68

M_VREF

+1.35VSUS

R680

1K/F_4

M_VREF

AE28

MA_ADD[0]

Y27

MA_ADD[1]

Y29

MA_ADD[2]

Y26

MA_ADD[3]

W28

MA_ADD[4]

W29

MA_ADD[5]

W26

MA_ADD[6]

U29

MA_ADD[7]

W25

MA_ADD[8]

U26

MA_ADD[9]

AG29

MA_ADD[10]

U27

MA_ADD[11]

T28

MA_ADD[12]

AK26

MA_ADD[13]

T26

MA_ADD[14]/MA_BG[1]

T25

MA_ADD[15]/MA_ACT_L

AG26

MA_BANK[0]

AG27

MA_BANK[1]

T29

MA_BANK[2]/MA_BG[0]

E19

MA_DM[0]

D21

MA_DM[1]

K21

MA_DM[2]

F29

MA_DM[3]

AP28

MA_DM[4]

AV26

MA_DM[5]

AR22

MA_DM[6]

BC22

MA_DM[7]

K29

MA_DM[8]

H19

MA_DQS_H[0]

G19

MA_DQS_L[0]

B22

MA_DQS_H[1]

A22

MA_DQS_L[1]

F23

MA_DQS_H[2]

E23

MA_DQS_L[2]

G27

MA_DQS_H[3]

F27

MA_DQS_L[3]

AP25

MA_DQS_H[4]

AP26

MA_DQS_L[4]

AW27

MA_DQS_H[5]

AV27

MA_DQS_L[5]

AV22

MA_DQS_H[6]

AU22

MA_DQS_L[6]

BA21

MA_DQS_H[7]

AY21

MA_DQS_L[7]

L27

MA_DQS_H[8]

L26

MA_DQS_L[8]

AE25

MA_CLK_H[0]

AE26

MA_CLK_L[0]

AD26

MA_CLK_H[1]

AD27

MA_CLK_L[1]

AB28

MA_CLK_H[2]

AB29

MA_CLK_L[2]

AB25

MA_CLK_H[3]

AB26

MA_CLK_L[3]

N29

MA_RESET_L

AE29

MA_EVENT_L

P27

MA_CKE0

P29

MA_CKE1

AK27

MA0_ODT[0]

AL26

MA0_ODT[1]

AH25

MA1_ODT[0]

AL25

MA1_ODT[1]

AH26

MA0_CS_L[0]

AL29

MA0_CS_L[1]

AH29

MA1_CS_L[0]

AL28

MA1_CS_L[1]

AG24

MA_RAS_L/MA_RAS_L_ADD[16]

AK29

MA_CAS_L/MA_CAS_L_ADD[15]

AH28

MA_WE_L/MA_WE_L_ADD[14]

B19

MA_VREFDQ

T32

M_VREF

1013@RNY: Also need to check AMD whether it can float ot not?

1102@RNY: AMD recommend reserve test point at VREFDQ/ZVDDIO_MEM_S

U24A

MEMORY A

FP4 REV 1.0

H17

MA_DATA[0]

J17

MA_DATA[1]

F20

MA_DATA[2]

H20

MA_DATA[3]

E17

MA_DATA[4]

F17

MA_DATA[5]

K18

MA_DATA[6]

E20

MA_DATA[7]

A21

MA_DATA[8]

C21

MA_DATA[9]

C23

MA_DATA[10]

D23

MA_DATA[11]

B20

MA_DATA[12]

B21

MA_DATA[13]

B23

MA_DATA[14]

A23

MA_DATA[15]

G22

MA_DATA[16]

H22

MA_DATA[17]

E25

MA_DATA[18]

G25

MA_DATA[19]

J20

MA_DATA[20]

E22

MA_DATA[21]

H23

MA_DATA[22]

J23

MA_DATA[23]

F26

MA_DATA[24]

E27

MA_DATA[25]

J26

MA_DATA[26]

J27

MA_DATA[27]

H25

MA_DATA[28]

E26

MA_DATA[29]

G28

MA_DATA[30]

G29

MA_DATA[31]

AN26

MA_DATA[32]

AP29

MA_DATA[33]

AR26

MA_DATA[34]

AP24

MA_DATA[35]

AN29

MA_DATA[36]

AN27

MA_DATA[37]

AR29

MA_DATA[38]

AR27

MA_DATA[39]

AU26

MA_DATA[40]

AV29

MA_DATA[41]

AU25

MA_DATA[42]

AW25

MA_DATA[43]

AU29

MA_DATA[44]

AU28

MA_DATA[45]

AW26

MA_DATA[46]

AT25

MA_DATA[47]

AV23

MA_DATA[48]

AW23

MA_DATA[49]

AV20

MA_DATA[50]

AW20

MA_DATA[51]

AR23

MA_DATA[52]

AT23

MA_DATA[53]

AR20

MA_DATA[54]

AT20

MA_DATA[55]

BB23

MA_DATA[56]

BB22

MA_DATA[57]

BB20

MA_DATA[58]

AY19

MA_DATA[59]

BA23

MA_DATA[60]

BC23

MA_DATA[61]

BC21

MA_DATA[62]

BB21

MA_DATA[63]

K26

MA_CHECK[0]

K28

MA_CHECK[1]

N26

MA_CHECK[2]

N28

MA_CHECK[3]

J29

MA_CHECK[4]

K25

MA_CHECK[5]

L29

MA_CHECK[6]

N25

MA_CHECK[7]

AD29

MA_ZVDDIO_MEM_S

*FP4

TP21

M_B_A[15:0][9,10]

M_B_BS#[2..0][9,10]

M_B_DM[7..0][9,10]

CR-L only channel B

U24I

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_BS#0

M_B_BS#1

M_B_BS#2

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

TP75

M_B_DQSP0[9,10]

M_B_DQSN0[9,10]

M_B_DQSP1[9,10]

M_B_DQSN1[9,10]

M_B_DQSP2[9,10]

M_B_DQSN2[9,10]

M_B_DQSP3[9,10]

M_B_DQSN3[9,10]

M_B_DQSP4[9,10]

M_B_DQSN4[9,10]

M_B_DQSP5[9,10]

M_B_DQSN5[9,10]

M_B_DQSP6[9,10]

M_B_DQSN6[9,10]

M_B_DQSP7[9,10]

M_B_DQSN7[9,10]

M_B_CLKP0[9]

M_B_CLKN0[9]

M_B_CLKP1[9]

M_B_CLKN1[9]

M_B_CLKP2[10]

M_B_CLKN2[10]

M_B_CLKP3[10]

M_B_CLKN3[10]

M_B_RST#[9,10]

M_B_EVENT#[9,10]

M_B_CKE0[9,10]

M_B_CKE1[9,10]

M_B_ODT0[9]

M_B_ODT1[9]

M_B1_ODT0[10]

M_B1_ODT1[10]

M_B_CS#0[9]

M_B_CS#1[9]

M_B1_CS#0[10]

M_B1_CS#1[10]

M_B_RAS#[9,10]

M_B_CAS#[9,10]

M_B_WE#[9,10]

M_B_DM8

M_B_VREFDQ[9,10]

AG31

MB_ADD[0]

AC30

MB_ADD[1]

AC31

MB_ADD[2]

AB32

MB_ADD[3]

AA32

MB_ADD[4]

AA33

MB_ADD[5]

AA31

MB_ADD[6]

Y33

MB_ADD[7]

AA30

MB_ADD[8]

W32

MB_ADD[9]

AG32

MB_ADD[10]

Y32

MB_ADD[11]

W33

MB_ADD[12]

AL31

MB_ADD[13]

W30

MB_ADD[14]/MB_BG[1]

V32

MB_ADD[15]/MB_ACT_L

AH32

MB_BANK[0]

AG33

MB_BANK[1]

W31

MB_BANK[2]/MB_BG[0]

D25

MB_DM[0]

D29

MB_DM[1]

E33

MB_DM[2]

J33

MB_DM[3]

AR30

MB_DM[4]

AW30

MB_DM[5]

BC30

MB_DM[6]

BC26

MB_DM[7]

N33

MB_DM[8]

B26

MB_DQS_H[0]

A26

MB_DQS_L[0]

B30

MB_DQS_H[1]

A30

MB_DQS_L[1]

F32

MB_DQS_H[2]

E32

MB_DQS_L[2]

K32

MB_DQS_H[3]

J32

MB_DQS_L[3]

AR32

MB_DQS_H[4]

AR33

MB_DQS_L[4]

AW32

MB_DQS_H[5]

AW33

MB_DQS_L[5]

BA29

MB_DQS_H[6]

AY29

MB_DQS_L[6]

BA25

MB_DQS_H[7]

AY25

MB_DQS_L[7]

P32

MB_DQS_H[8]

N32

MB_DQS_L[8]

AE33

MB_CLK_H[0]

AE32

MB_CLK_L[0]

AE30

MB_CLK_H[1]

AE31

MB_CLK_L[1]

AD32

MB_CLK_H[2]

AD33

MB_CLK_L[2]

AC33

MB_CLK_H[3]

AC32

MB_CLK_L[3]

T33

MB_RESET_L

AG30

MB_EVENT_L

U32

MB_CKE0

U33

MB_CKE1

AL30

MB0_ODT[0]

AM32

MB0_ODT[1]

AJ32

MB1_ODT[0]

AM33

MB1_ODT[1]

AJ33

MB0_CS_L[0]

AL32

MB0_CS_L[1]

AJ30

MB1_CS_L[0]

AL33

MB1_CS_L[1]

AH33

MB_RAS_L/MB_RAS_L_ADD[16]

AK32

MB_CAS_L/MB_CAS_L_ADD[15]

AJ31

MB_WE_L/MB_WE_L_ADD[14]

A19

MB_VREFDQ

MEMORY B

FP4 REV 1.0

A25

C25

C27

D27

B24

B25

B27

A27

A29

C29

B32

D32

B28

B29

A31

C31

E30

E31

G33

G32

C33

D33

G30

G31

J30

J31

L33

L32

H32

H33

L30

L31

AN31

AP32

AT32

AU32

AN33

AN32

AR31

AT33

AU30

AV32

BA33

AY32

AU33

AU31

AW31

AY33

BC31

BB30

BB28

AY27

BB32

BA31

BC29

BB29

BB27

BB26

BB24

AY23

BA27

BC27

BC25

BB25

N30

N31

R33

R32

M32

M33

R30

R31

AF32

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_ZVDDIO

R670 39.2/F_4

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

MB_CHECK[0]

MB_CHECK[1]

MB_CHECK[2]

MB_CHECK[3]

MB_CHECK[4]

MB_CHECK[5]

MB_CHECK[6]

MB_CHECK[7]

MB_ZVDDIO_MEM_S

*FP4

M_B_DQ[0..63] [9,10]

+1.35VSUS

R678 *0_4/S

R679

A A

1K/F_4

C587

1000P/50V_4

C586

0.1U/16V/X7R_4

1 2

C585

0.47U/10V_4

Place within 1000mil of the APU

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Carrizo 2/7 (MEM)

Carrizo 2/7 (MEM)

NB5

NB5

5

4

3

2

NB5

Carrizo 2/7 (MEM)

Date: Sheet of

Friday, July 24, 2015 3 62

Date: Sheet of

Friday, July 24, 2015 3 62

Date: Sheet of

Friday, July 24, 2015 3 62

1

1A

1A

1A

5

4

3

2

1

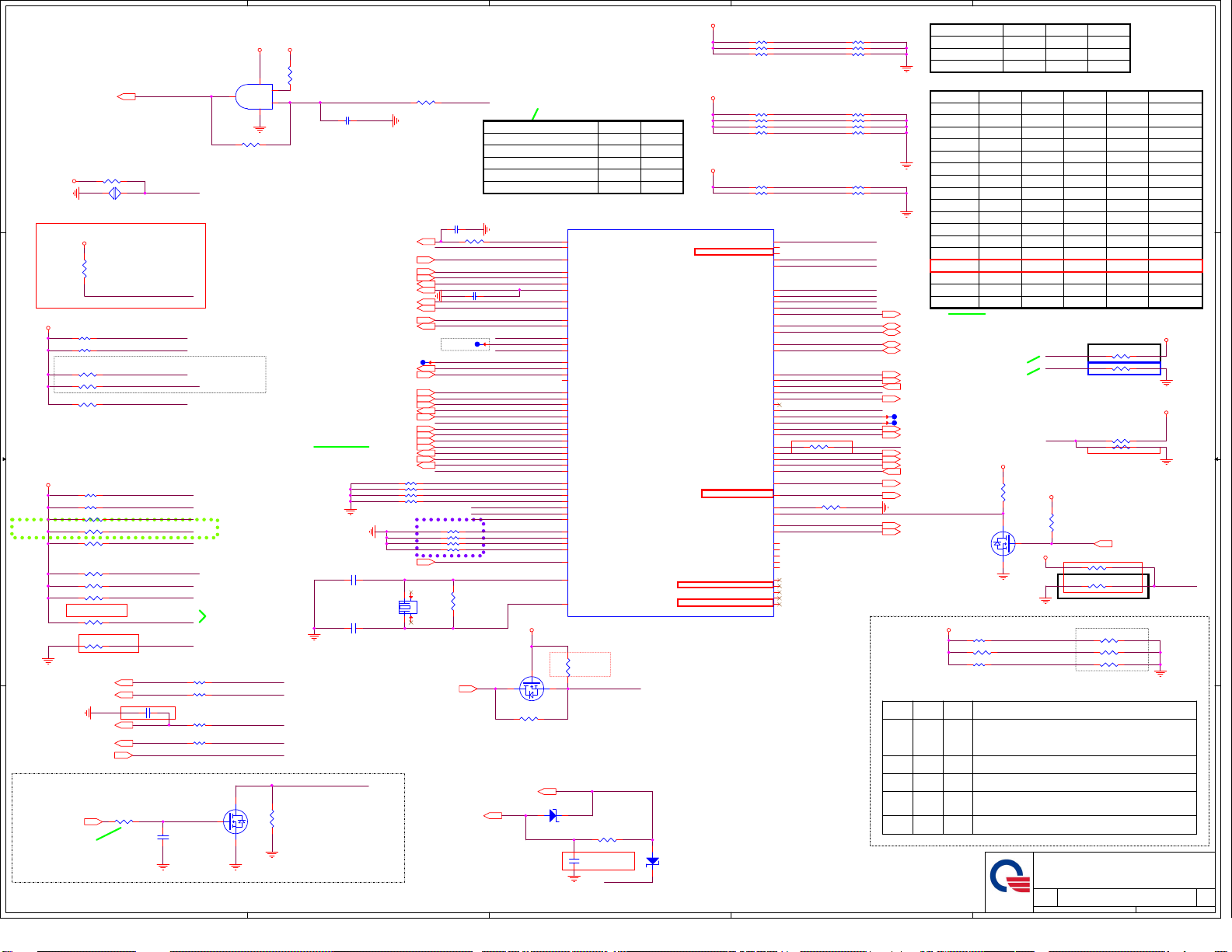

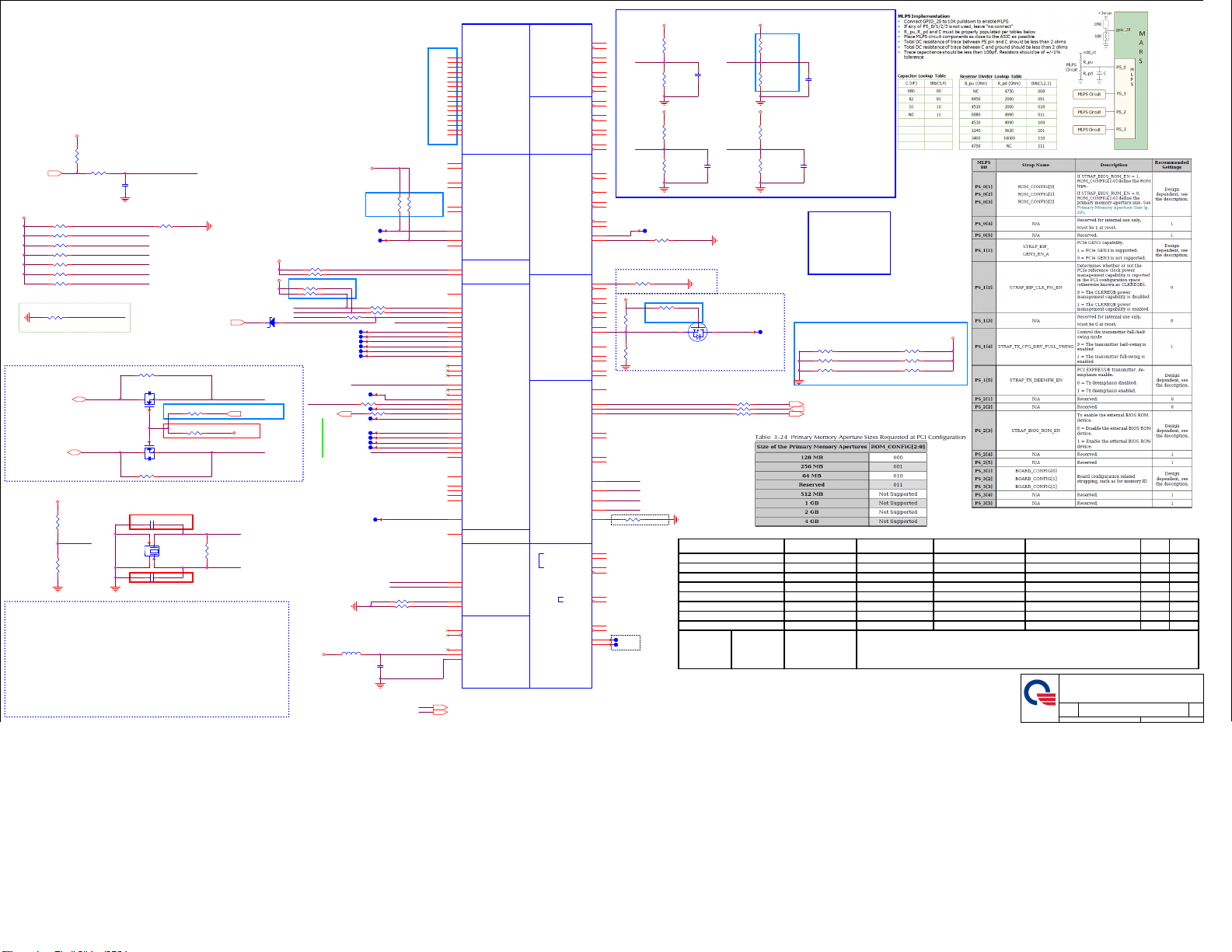

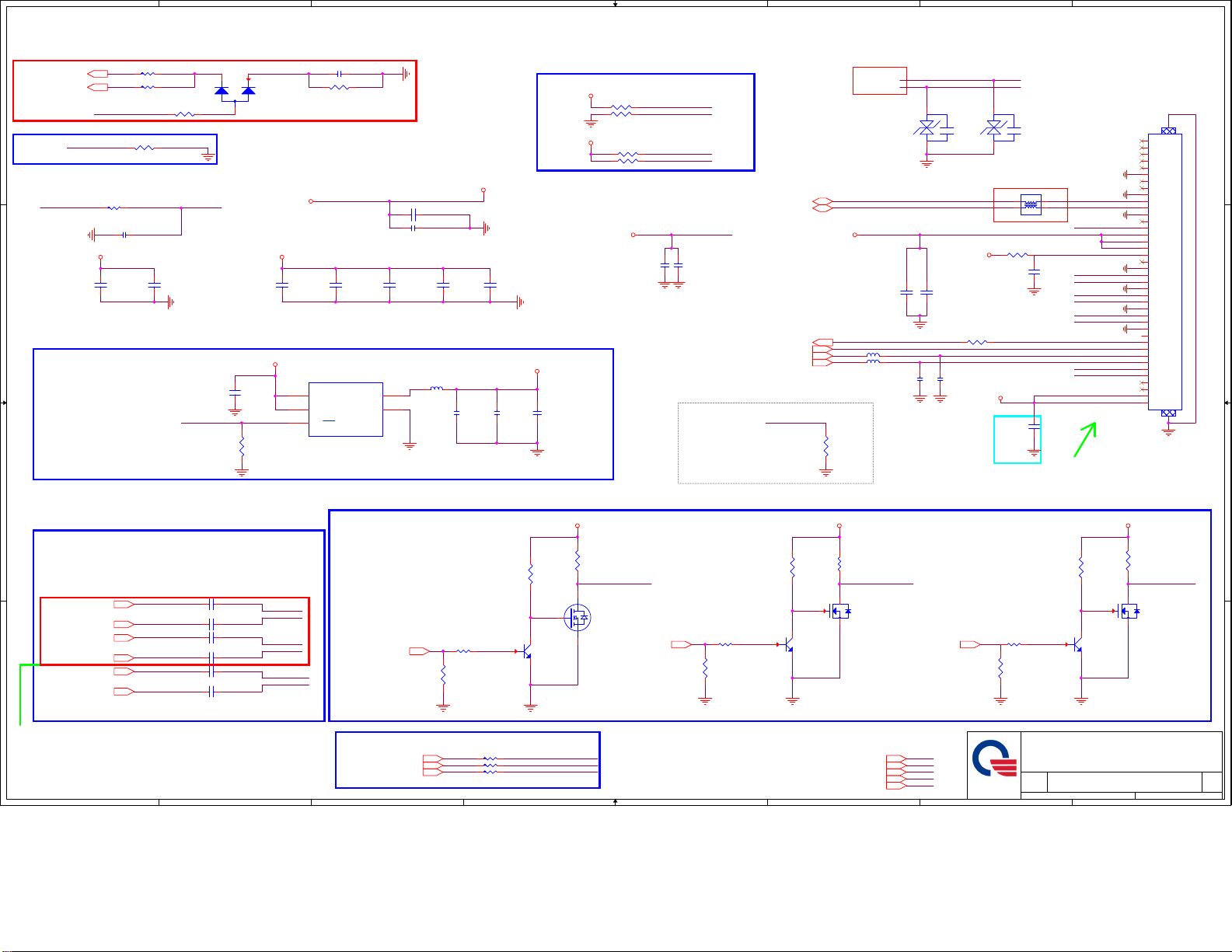

Boot Voltage

1.1V

1.0V

0.8V

04

1A

1A

1A

+1.8V

APU_PROCHOT#

1

2

74LVC2G07GW

APU_RST#

APU_PW ROK

APU_PROCHOT#

APU_ALERT#

APU_SIC

APU_SID

KBC_SMDATA

1

2

3

U12

TC7SH08FU

4

C327

0.1U/16V/X7R_4

U11

A1

Y1

GND

VCC

A23Y2

5

KBC_SMCLK

KBC_PROCHOT[39]

APU_PROCHOT#[43,4 8,50]

OCP_PW M_OUT[40]

PJA138K

Q49

+3V

3 5

6

5

4

+3V CZ18V_CZL 30V

+1.8V

+1.8V

5

6

2

+1.8V

KBC_PROCHOT

APU_PROCHOT#

FAN_FULL_ SPEED# [35,36]

C331

0.1U/16V/X7R_4

2

APU_RST#

1

+3V

+1.8V

R295

R290

0_4

*0_4

1K/F_4

APU_PW ROK_BUF

R2

R169 *CZL@0_4

R1

R176 CZ@0_4

Z: R1

C

CZ

-L: R2

LS

43

APU_SIC

1

APU_SID

Q26

DMN5L06DW K/50V_0.302A

Q53

5

2

6

2N7002DW

+1.8V

R284

R288

1K/F_4

1016: Alfred

S

wap the DDI Port frm DDI2 to DDI1.

CZ only

HDMI

DP Switch or

DP to VGA Chip

eDP

INT

43

1

+1.8V

TP35

APU_TEST18

APU_TEST19

APU_RST_L_BUF

CPU_LDT_RST_HTPA#

APU_DBREQ#

APU_DBRDY

APU_TCK

APU_TMS

APU_TDI

APU_TRST#

APU_TDO

APU_PW ROK_BUF

Thermal Sensor

ALF@1025:

CZ & CZ-L for LS

TP25

APU_PG[48,50]

C251

*150P/50 V_4

HDT CONN

88511-20 01-20p-l

C294

*150P/50 V_4

J1

Close to HDT & No remove.

APU_TDI

R409 1K/F_4

APU_TCK

R407 1K/F_4

APU_TMS

R410 1K/F_4

APU_TRST#

R408 1K/F_4

APU_DBREQ#

R400 1K/F_4

4

DDI1_TX0_P[21]

DDI1_TX0_N[21]

DDI1_TX1_P[21]

DDI1_TX1_N[21]

DDI1_TX2_P[21]

DDI1_TX2_N[21]

DDI1_TX3_P[21]

DDI1_TX3_N[21]

INT_eDP_TXP0[19]

INT_eDP_TXN0[19]

INT_eDP_TXP1[19]

INT_eDP_TXN1[19]

APU_RST#

APU_PW ROK

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

+1.8V

IN_D2[21]

IN_D2#[21]

IN_D1[21]

IN_D1#[21]

IN_D0[21]

IN_D0#[21]

IN_CLK[21]

IN_CLK#[21]

R255 *0_4/S

DISPLAY/SVI2/JTAG/TEST

B6

DP2_TXP[0]

A6

DP2_TXN[0]

D7

DP2_TXP[1]

C7

DP2_TXN[1]

A7

DP2_TXP[2]

B7

DP2_TXN[2]

D9

DP2_TXP[3]

C9

DP2_TXN[3]

A2

DP1_TXP[0]

A3

DP1_TXN[0]

B4

DP1_TXP[1]

A4

DP1_TXN[1]

D5

DP1_TXP[2]

C5

DP1_TXN[2]

A5

DP1_TXP[3]

B5

DP1_TXN[3]

E2

DP0_TXP[0]

E1

DP0_TXN[0]

E3

DP0_TXP[1]

E4

DP0_TXN[1]

D1

DP0_TXP[2]

D2

DP0_TXN[2]

C1

DP0_TXP[3]

B1

DP0_TXN[3]

SVT

SVC

SVD

GFX_SVT_R

GFX_SVC_ R

GFX_SVD_ R

APU_SIC

APU_SID

APU_RST#

APU_PW ROK

APU_PROCHOT#

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

C15

SVT0

D17

SVC0

D19

SVD0

B15

SVT1

B16

SVC1

A18

SVD1

B18

SIC

C17

SID

D15

RESET_L

C19

PWROK

A15

PROCHOT_L

B17

ALERT_L

H15

TDI

H14

TDO

D13

TCK

G15

TMS

J14

TRST_L

C13

DBRDY

A11

DBREQ_L

IO Thermal Protect

ALF@1031:

Del NTC Circuit

3

FP4 REV 1.0

CZ: Ra+LS / 1.8V interface (level-shifter)

CZ-L: Rb / 3.3V interface

U24C

A9

DP_ZVSS

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP2_AUXP

DP2_AUXN

DP2_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP0_AUXP

DP0_AUXN

DP0_HPD

TEMPIN0

TEMPIN1

TEMPIN2

TEMPINRETURN

TEST28_H

TEST28_L

DP_STEREOSYNC/TEST36

RSVD_1

TEST410

TEST411

TEST4

TEST5

TEST6

TEST9

TEST10

TEST14

TEST15

TEST16

TEST17

TEST11

TEST18

TEST19

TEST31

TEST37

DP_ZVSS

B9

DP_AUX_ZVSS

G5

APU_LVDS _BLON

G6

APU_DISP_ON

F11

APU_DPST_P WM

H9

G9

E9

F7

E7

F5

F8

INT_eDP_AUXP

E8

INT_eDP_AUXN

G8

K24

CORETYPE

E15

APU_TEMPIN0

E14

APU_TEMPIN1

E12

APU_TEMPIN2

F14

APU_TEMPRETURN

AK24

APU_TEST410

AL24

APU_TEST411

P24

APU_THERMDA

N24

APU_THERMDC

AN24

APU_TEST6

AB8

APU_TEST9

Y9

APU_TEST10

B10

APU_TEST14

D11

APU_TEST15

A10

APU_TEST16

C11

APU_TEST17

B11

APU_TEST11

A14

APU_TEST18

B14

APU_TEST19

A13

APU_TEST28_ H

B13

APU_TEST28_ L

P26

APU_TEST31

E11

DP_STEREOS YNC

A17

APU_TEST37

R458 2K/F_ 4

R451 150/F_4

APU_LVDS _BLON [19]

APU_DISP_ON [19]

APU_DPST_P WM [19]

TP34

TP17

TP16

TP64

R508 *0_4/S

TP22

TP23

TP20

TP19

TP31

R446 *1K/F_4

TP15

TP24

R452 *1K/F_4

R493 *1K/F_4

R482 *1K/F_4

R279 1K/F_4

R243 1K/F_4

TP66

R700 *1K/F_4

TP65

R693 *1K/F_4

R159 1K/F_4

R158 *1K/F_4

R531 *1K/F_4

R530 *1K/F_4

CZ only

IN_DDC_SCL [21]

IN_DDC_SDA [21]

IN_HPD [21]

INT_DDI1_AUX P [21]

INT_DDI1_AUX N [21]

DDI1_HPD_CON [21]

INT_eDP_AUXP [19 ]

INT_eDP_AUXN [19]

EDP_HPD [19]

TP14

+1.8V

CZ18V_CZL 30V

+1.8V

RNY@1122

Move LS to LCD side and follow CRB

DP_STEREOSYNC: HDMI enable pin.

TP46

TP12

TP62

DIFFERENTIAL ROUTING

GFX_FB_H [50]

APU_VDDNB _FB_H [48]

APU_VDD_FB_H [48 ]

GFX_FB_L [50]

APU_VDD_VDDNB_FB_L [48]

R566

*1K/F_4

R545

*CZ@1K/F_4

2

+1.8V

R576

R513

*1K/F_4

*1K/F_4

SVT

SVC

SVD

+1.8V

12/9: confirm AMD PAE Scoop no need setting

VFIX MODE

R536

R518

*CZ@1K/F_4

*CZ@1K/F_4

GFX_SVT_R

GFX_SVC_ R

GFX_SVD_ R

NB5

NB5

NB5

VID Override table (VDD)

SVDSVC

0

0

0

110 0.9V

11

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Carrizo 3/7 (DIS/MISC)

Carrizo 3/7 (DIS/MISC)

Carrizo 3/7 (DIS/MISC)

Date: Sheet of

Friday, July 24, 2 015 4 62

Date: Sheet of

Friday, July 24, 2 015 4 62

Date: Sheet of

Friday, July 24, 2 015 4 62

1

H11

VDDCR_GFX_SENSE

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

*FP4

VDDCR_GFX_ SENSE

J12

VDDCR_NB_S ENSE

G12

VDDCR_CPU_SENSE

AY18

VDDP_SENSE

VDDP_SENSE

H12

VSS_SENSE

VSS_SENSE

APU Serial VID

ALF@1030:

Needs confirm with AMD

APU_SVT[48]

APU_SVC[48]

APU_SVD[48]

GFX Serial VID

ALF@1030:

Needs confirm with AMD

GFX_SVT[50]

GFX_SVC[50]

GFX_SVD[50]

R494 CZ@0_4

R481 *0_4/S

R471 *0_4/S

TP27

R487 CZ@0_4

R478 *0_4/S

CZ: R494, R487 Stuff

CZ-L: R494, R487 No Stuff

VDDCR_CPU_SENSE

VDDCR_NB_S ENSE

VDDCR_GFX_ SENSE

Place near APU within 500mil

R507 *0_4/S

R575 36/F_4

R565 36/F_4

PV, 0414, change SVID R to 0 ohm

PV, 0420, change SVID R to 36 ohm

Place near APU within 500mil

R512 CZ@0_4

R535 CZ@0_4

R544 CZ@0_4

R198 301/F_4

R242 301/F_4

CZ18V_CZL 30V

D D

C C

B B

A A

R181 1K/F_4

R523 1K/F_4

R549 1K/F_4

R548 1K/F_4

CZ: LS, CZ18V_CZL30V=1.8V

CZ-L: LS, CZ18V_CZL30V=3.3V

KBC_SMCLK[12,20,36,39]

KBC_SMDATA[12,20,36,39]

APU_PROCHOT# Signal Level:

CZ: +1.8V

CZ-L: +3.3V

+1.8V

R710

2.2K_4

3

2

KBC_PROCHOT

2N7002K

Q54

1

HDT+ Connector for Debug only

Can remove on MP

CPU_LDT_RST_HTPA#

APU_RST# APU_RST_L_BUF

APU_PW ROK

5

+3V_DEEP_SUS+3V_DEEP_SUS

U21

*MC74VHC1G08DFT2G

PCIE_RST#_R1[11,24,26,29,34]

D D

+3V_DEEP_SUS

R404 *1K/F_4

1 2

G2

*SOLDERJUMPER-2

PCIE_RST#_R1

SYS_RST# internal 10K pull up

SYS_RST#

4

R418 *0_4/S

R422

*4.7K/F_4

35

1

2

PV, 0415, reserve NMI_SMI_DBG# PU resistor

+3V_DEEP_SUS

R736

10K/F_4

NMI_SMI_DBG#

+3V

R540 2.2K_4

+3V_DEEP_SUS

R539 2.2K_4

R167 10K/F_4

R301 10K/F_4

R229 10K/F_4

R403 2.2K_4

R405 2.2K_4

R406 10K/F_4

R417 10K/F_4

R166 *10K/F_4

C C

PCIE_WAKE# PU & LAN use 0 ohm to open.

B B

A A

R92 10K/F_4

R448 *10K/F_4

R415 10K/F_4

R231 10K/F_4

R350 *100K/F_4

ACZ_SDOUT_AUDIO[23]

ACZ_SYNC_AUDIO[23]

BIT_CLK_AUDIO[23]

ACZ_RST#_AUDIO[23]

ALF@1030:

For dGPU VGA REQ

DGPU_PWROK[5,11]

From dGPU PG Ready

(As default)

to DDR3 SMBUS

FCH_3S_SMCLK

FCH_3S_SMDATA

CLKREQG#

PCIE_CLKREQ_CARD#

FPR_OFF

to TP SMBUS

SMB_NIC_SMCLK

SMB_NIC_SMDATA

PWR_BTN_OUT#

NIC_SMBUS_ALERT#

DGPU_PWROK

APU_VRM_GFX_PWRGD

WLAN_WAKE#

LOW_BAT#

PV, 0420, delete CR_PWREN# pull-up resistor

CR_RST#

For EMI

VGA_EN

To Azalia

C90 1K/F_4

SI, 0117, fine tune GPU sequence

ACZ_SDIN0[23]

Pure UMA can remove

R160 *DIS@0_4/S

C143

DIS@0.47U/6.3V_4

5

Only CZ Stuff

ALF@1119:

Reserved the CLKREQG# for dGPU

PV, 0420, change NMI_SMI_DBG#

from AGPIO86 to AGPIO17, and delete CR_PWREN#

for GPIO145~148

CZ pop those resistor

CZ-L can NC them

ALF@1109:

HP request to add the

Card Reader weak feature

Q21

2

ACZ_SDOUT_R

ACZ_SYNC_R

ACZ_BCLK_R

ACZ_RST#_R

ACZ_SDIN0

3

1

CLKREQG#

R162

*DIS@10K_4

R129 33_4

R134 33_4

PV, 0414, pull-down 1K for AZ timing issue

R122 BLM15BB470SN1D(47,300MA)

R138 33_4

DIS@2N7002K

4

PCIE_RST#_R PCIE_RST#

R107 33_4

C78 150P/50V_4

LPC_RST#[29,38,39]

RSMRST#[42]

PWR_BTN_OUT#[40]

SYS_PWRGD[42]

SYS_RST#[6]

NIC_SMBUS_ALERT#[24]

SLP_S3#_3R[40,42,52]

SLP_S5#_3R[24,27,29,40,42]

S0A3_GPIO[39,42,52]

S5_MUX_CTRL[47]

TP67

FPR_OFF[17]

RUNSCI_EC#[36,39]

ADP_PRES_OUT[12,39,52]

ZERO_ODD_DA#[37]

ZERO_ODD_DP#[37]

TPM_INT#[26]

LOW_BAT#[39]

PCIE_CLKREQ_WLAN#[29]

KBL_DET#[32]

PCIE_CLKREQ_CARD#[34]

CLKREQG#[12]

SPI_TPM_CS#_CZL[26]

NMI_SMI_DBG#[38,39]

CR_RST#[34]

R121 *10K/F_4

R132 *10K/F_4

R143 10K/F_4

R144 10K/F_4

RTC_CLK[6,40]

C448 18P/50V_4

C455 18P/50V_4

23

4 1

PCIE_CLKREQ_LAN#_D[24]

4

C479150P/50V_4

R495 33_4

C459 *100P/50V_4

TP45

LOW_BAT#

PCIE_CLKREQ_LAN#

PCIE_CLKREQ_WLAN#

PCIE_CLKREQ_CARD#

CLKREQG#

SPI_TPM_CS#_CZL

NMI_SMI_DBG#

CR_RST#

VBIOS_ID2

ACZ_BCLK_R

ACZ_SDIN0

ACZ_SDIN1

ACZ_SDIN2

ACZ_RST#_R

ACZ_SYNC_R

ACZ_SDOUT_R

R484 10K/F_4

R479 10K/F_4

R477 10K/F_4

R476 10K/F_4

32K_X1

R412

Y3

20M_4

32.768KHZ

32K_X2

ALF@1030:

For dGPU Power Enable Sequence & GPIOs

VGA_EN[53,56]

SI, 0117, fine tune GPU sequence

3

ALF@1110:

HP confirmed the 00 for DIS, 11 for UMA,

need to set in BOM

VBIOS_ID

Discrete VRAM Group #1

Discrete VRAM Group #2

Discrete VRAM Group #3

UMA

LPC_RST#_R

PCIE_RST#

PWR_BTN_OUT#

SYS_RST#

NIC_SMBUS_ALERT#

S0A3_GPIO

APU_TEST0

APU_TEST1

APU_TEST2

EC_RCIN#

FPR_OFF

RUNSCI_EC#

GPIO145

GPIO146

GPIO147

GPIO148

+3V

BC19

BC15

BC17

BB12

AY15

BB13

BB17

BB18

BB16

BB10

AN7

AE4

AE1

BC9

AF2

AG2

AK7

AH5

AE8

AH8

AH6

AK8

AE3

AD7

AG3

AD5

AL8

AN8

AE2

AH9

AG1

AH2

AL9

AU6

AR8

AP6

AR5

AU9

AT9

AR7

BB9

BB7

BC7

AG7

AT1

AT2

VBIOS_ID1 VBIOS_ID2

LPC_RST_L

PCIE_RST_L/EGPIO26

S5

RSMRST_L

PWR_BTN_L/AGPIO0

PWR_GOOD

SYS_RESET_L/AGPIO1

S5

WAKE_L/AGPIO2

S5

SLP_S3_L

SLP_S5_L

S0A3_GPIO/AGPIO10

S5

S5_MUX_CTRL/EGPIO42

S5

TEST0

TEST1/TMS

TEST2

ESPI_RESET_L/KBRST_L/AGPIO129

GA20IN/AGPIO126

S0

LPC_PME_L/AGPIO22

S5

LPC_SMI_L/AGPIO86

S0

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

IR_TX0/USB_OC5_L/AGPIO13

IR_TX1/USB_OC6_L/AGPIO14

IR_RX1/AGPIO15

IR_LED_L/LLB_L/AGPIO12

CLK_REQ0_L/SATA_IS0_L/ SATA_ZP0_L/AGPIO92

CLK_REQ1_L/AGPIO115

CLK_REQ2_L/AGPIO116

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

CLK_REQG_L/OSCIN/EGPIO132

USB_OC0_L/TRST_L/AGPIO16

USB_OC1_L/TDI/AGPIO17

USB_OC2_L/TCK/AGPIO18

USB_OC3_L/TDO/AGPIO24

AZ_BITCLK/I2S_BCLK_MIC

AZ_SDIN0/I2S_DATA_MIC[0]

AZ_SDIN1/I2S_LR_PLAYBACK

AZ_SDIN2/I2S_DATA_PLAYBACK

AZ_RST_L/I2S_LR_MIC

AZ_SYNC/I2S_BCLK_PLAYBACK

AZ_SDOUT/I2S_DATA_MIC1

I2C0_SCL/EGPIO145

S0

I2C0_SDA/EGPIO146

S0

I2C1_SCL/EGPIO147

S0

I2C1_SDA/EGPIO148

S0

RTCCLK

X32K_X1

X32K_X2

1029@RNY: Add PU for LAN CLKREQ#

Q44

*2N7002K

3

R524 *0_4/S

DGPU_PWR_EN[55]

VGA_EN

2

R519

10K/F_4

1

PCIE_CLKREQ_LAN#

ALF@1031:

Following AMD Leading to add LS

D17

2 1

DIS@RB751V40

DGPU_PWR_EN

R454 DIS@4.7K_4

C470

DIS@0.47U/6.3V_4

SLP_S3#_3R

3

AGPIO24AGPIO6

0

0

1

1 1

ACPI/SD/AZ/GPIO/RTC/I2C/UART/MISC

X

X

S5

X

S5

X

Power Domain

CZ CZ-L

S0

S0

S0

S5

X

S5

S5

S5

S5

S5

S5

S5

S5

S5

S5

S5

S0

S0

S0

S0

S0

S0

S0

S0

S5

S5

S5

S5

S5

S5

S5

S5

X

S0

S0

S0

21

0

1

0

U24D

S0

S0

FP4 REV 1.0

*FP4

D16

DIS@RB751V40

+3V

+3V

Default

+3V_DEEP_SUS

S0

S0

X

S0

S0

S5

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S5

S5

S5

S5

S5

S5

S5

S5

S5

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S5

S0

S0

S0

S0

S0

S0

S0

S0

S0

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

S0

X

UART1_RXD/BT_I2S_SDI/EGPIO141

S5

S0

S0

X

UART1_TXD/BT_I2S_SDO/EGPIO143

S0

X

UART1_INTR/BT_I2S_LRCLK/AGPIO144

S5

S0

R442 *10K/F_4

R439 10K/F_4

R112 *10K/F_4

R436 10K/F_4

R428 10K/F_4

R474 *10K/F_4

R450 *10K/F_4

R76 *10K/F_4

R98 *10K/F_4

SD0_WP/EGPIO101

SD0_PWR_CTRL/AGPIO102

SD0_CD/AGPIO25

SD0_CLK/EGPIO95

SD0_CMD/EGPIO96

SD0_DATA0/EGPIO97

S0

SD0_DATA1/EGPIO98

S0

SD0_DATA2/EGPIO99

S0S5S0

SD0_DATA3/EGPIO100

S0S5S0

SD0_LED/EGPIO93

S0

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

S5

S5

S5

S5

S5

S5

AGPIO6/LDT_RST_L

S5

AGPIO7/LDT_PWROK

S5

S5

S5

VDDGFX_PD/AGPIO39

X

X

S0

S0

AGPIO66/SHUTDOWN_L

AGPIO68/SGPIO_CLK

AGPIO69/SGPIO_LOAD

AGPIO71/SGPIO_DATAOUT

AGPIO72/SGPIO_DATAIN

SPKR/AGPIO91

S0

BLINK/USB_OC7_L/AGPIO1 1

S0

GENINT1_L/AGPIO89

S0

GENINT2_L/AGPIO90

S0

FANIN0/AGPIO84

S0

FANOUT0/AGPIO85

S0

UART0_CTS_L/EGPIO135

X

UART0_RXD/EGPIO136

X

UART0_RTS_L/EGPIO137

X

UART0_TXD/EGPIO138

X

UART0_INTR/AGPIO139

X

UART1_RTS_L/EGPIO142

PLT_ID1

PLT_ID2

PLT_ID3

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

VBIOS_ID1

VBIOS_ID2

ALF@1110:

HP confirmed Okay!!

BB2

BB5

BC2

BB4

AY5

BC3

BA3

BC5

BA5

BB6

BA15

AY17

AG5

AG4

AL5

AGPIO3

AL6

AGPIO4

AJ1

AGPIO5

AJ3

AH1

AJ4

AGPIO8

AK5

AGPIO9

AD8

AG8

AGPIO40

AW15

AGPIO64

AU15

AGPIO65

AT15

R440 *0_4/S

AU12

AT14

AR14

BC13

BA17

AN5

BB14

BA19

BC18

BB19

AY9

AW8

AV5

AV8

AW9

AV11

AU7

AT11

AR11

AP9

2

R441 10K/F_4

R438 *10K/F_4

R111 10K/F_4

R433 *10K/F_4

R426 *10K/F_4

R456 10K/F_4

R449 10K/F_4

R82 10K/F_4

R105 10K/F_4

PLT_ID3

PLT_ID1

PLT_ID2

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

FCH_3S_SMCLK

FCH_3S_SMDATA

SMB_NIC_SMCLK

SMB_NIC_SMDATA

LANLINK#

VBIOS_ID1

WOL_EN

WLAN_WAKE#

VDDGFX_PD

APU_VRM_GFX_PWRGD

DGPU_PWR_EN

FPR_LOCK#

HDD_HALTLED

AGPIO11

R510 *150/F_4

ACCEL_INTH

2

1

Palazzo 15"

RD_ID1 BRD_ID2 BRD_ID3 BRD_ID4

BOARD REVISION

ODD_PWR [37]

FCH_3S_SMCLK [9,10,20,28]

FCH_3S_SMDATA [9,10,20,28]

SMB_NIC_SMCLK [34]

SMB_NIC_SMDATA [34]

RNY@1108: Changed LANLINK# to PU

AGPIO3 [6]

LANLINK# [24]

FCH_WAKE#_EC [39]

WOL_EN [52]

TP13

TP5

WLAN_OFF [29]

WLAN_TRANSMIT_OFF# [29]

SI, 0117, fine tune GPU sequence

DPTMDS_SEL [21]

FPR_LOCK# [17]

HDD_HALTLED [34]

DGPU_PWROK [5,11]

SPKR [23]

AGPIO11 [6]

GENINT1: HVB function

Vss:enabke; NC: disable

BT_OFF [29]

DGPU_HOLD_RST# [11]

+3V_DEEP_SUS

B

EG

PIO97 EGPIO98 EGPIO99 EGPIO100

DB0

DB1

DB2

SI1

SIB

SI2

PV1

MV1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 10 1

1 1 0 0

ALF@1105:

Changed the "ODD_PWR" to EGPIO93

ALF@1107:

Changed WOL_EN and PD

+3V

3

1

R424 *2.2K_4

R475 *1K/F_4

R416 *2.2K_4

PLT_ID1 PLT_ID2 PLT_ID3

0 01

+3V

R147

10K/F_4

2

+3V

2N7002K

Q19

APU_TEST0

APU_TEST1

APU_TEST2

EGPIO101EGPIO96EGPIO95

111 0

111 0

1111

+3V_DEEP_SUS

LANLINK#

R435 10K/F_4

WOL_EN

R411 10K/F_4

Only CZ Stuff if no used

DGPU_HOLD_RST#

R550 *10K/F_4

R727 *10K/F_4

SI, 0201, reserved for

fine tune GPU sequence

PV, 0414, change ACCEL_INTH GPIO pin

and Pull-up power rail

R164

*10K/F_4

R726 10K/F_4

R447 *100K/F_4

Only CZ-L Stuff if no used

SI, 0201, fine tune GPU sequence

ACCEL_INTH# [28]

R425 15K/F_4

R473 15K/F_4

R420 15K/F_4

Follow AMD checklist 53537_1_03 suggestion to stuff R118/R120/R122

TEST2 TEST1 TEST0 Description

0

0 0

0

0

0

1

1

TMS

1 TMS

FCH TAP accessible from APU when TAPEN is asserted

FCH JTAG pins are overloaded for multiple

functions, in this configuration the FCH JTAG are

used as non-JTAG pins

1

Reserved

X

Reserved

FCH JTAG multi-function pins are configured as

0

JTAG pins, in this configuration the FCH TAP

can be accessed from FCH JTAG pins

Use on ATE only

Yuba JTAG enabled

1

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Carrizo 4/7 (GPIO/AZ/UARTH)

Carrizo 4/7 (GPIO/AZ/UARTH)

NB5

NB5

NB5

Carrizo 4/7 (GPIO/AZ/UARTH)

Friday, July 24, 2015 5 62

Date: Sheet of

Friday, July 24, 2015 5 62

Date: Sheet of

Friday, July 24, 2015 5 62

Date: Sheet

1

05

Default

+3V

DGPU_PWR_EN

of

1A

1A

1A

5

4

3

2

1

Only CZ Stuff if no used

1029@RNY: DEVSLP0 is used, PU no need

+3V

R179 *10K/F_4

R182 10K/F_4

R489 *10K/F_4

D D

ALF@1109:

HP request to add Card Reader weak feature

R455 10K/F_4

SI, 0203, change cap to fine tune XTAL

C74

4.7P/50V_4

C67

4.7P/50V_4

C C

+3V

R480

R514 10K/F_4

R597 10K/F_4

R488 *150/F_4

DEVSLP0

CAMERA_ON

SPI_TPM_CS#

EGPIO119

Y1

48MHZ +-10PPM

*MC74VHC1G08DFT2G

R83

1M/F_4

LED_3S_SATA#[34]

1

2

4

3

PV, 0414, change CLK_R3S_DEBUG R to 56ohm for CZ

4.7K_4

PCI_3S_CLKRUN#

SB_SATA_LED#

PCI_3S_SERIRQ

PCI_3S_CLKRUN#

+3V

U23

4

2

1

3 5

R522 *0_4/S

48M_X1

48M_X2

CLK_R3S_KBC[29,39]

CLK_R3S_DEBUG[38]

1029@RNY: follow Leading NC

PV, 0415, follow AMD DG to PD LPC_PD_L, no used

ALF@1103:

HP request to add SPI_WP to SPI

C492

*0.1U/16V/X7R_4

CLK_PCIE_LANP[24]

CLK_PCIE_LANN[24]

CLK_PCIE_CARDP[34]

CLK_PCIE_CARDN[34]

SPI_CS0#[41]

SPI_CLK[41]

SPI_SO[41]

SPI_SI[41]

SPI_TPM_CS#[26]

SPI_WP[41]

SATA_TXP0[37]

HDD

ODD

+0.95V

PV, 0414, change AGPIO90 to CAMERA_ON

Integrated Clock Mode:

Leave unconnected.

CLK_GFX_P[11]

CLK_GFX_N[11]

CLK_WLAN_P[29]

CLK_WLAN_N[29]

PV, 0414, change RP1 to 33ohm, RP2 to 47ohm for CZ

C485 *10P/50V_4

C473 *10P/50V_4

SPI_CS0#

SPI_CLK

SPI_SO

SPI_SI

SPI_TPM_CS#

SPI_WP

SATA_TXN0[37]

SATA_RXN0[37]

SATA_RXP0[37]

SATA_TXP1[37]

SATA_TXN1[37]

SATA_RXN1[37]

SATA_RXP1[37]

R427 1K/F_4

R434 1K/F_4

DEVSLP0[37]

CAMERA_ON[19]

2

RP1

4

33_4P2R_4

2

RP4

4

0_4P2R_4

2

RP2

4

47_4P2R_4

2

RP3

4

0_4P2R_4

SI, 0203, EMI solution

R496 BLM15BB470SN1D(47,300MA)

R486 56_4

LAD0[29,38,39]

LAD1[29,38,39]

LAD2[29,38,39]

LAD3[29,38,39]

LFRAME#[29,38,39]

TP39

PCI_3S_SERIRQ[38,39]

PCI_3S_CLKRUN#[39]

R156

TP41

TP1

TP40

TP36

TP42

TP53

TP44

TP60

C467

PV, 0421, TP42 change to 2075 for layout

*15P/50V_4

1

3

1

3

1

3

1

3

TP4

TP3

TP37

TP38

CLK_GFX_P_R

CLK_GFX_N_R

CLK_PCIE_LANP_R

CLK_PCIE_LANN_R

CLK_PCIE_WLAN_R

CLK_PCIE_WLAN#_R

CLK_PCIE_CARDP_R

CLK_PCIE_CARDN_R

PCI_3S_SERIRQ

10K/F_4

SATA_CALRN

SATA_CALRP

DEVSLP0

CAMERA_ON

SB_SATA_LED#

48M_X1

48M_X2

LPC_CLK0

LPC_CLK1

LFRAME#

LDRQ#0

LPC_PD#

SPI_CLK

SPI_CS0#

EGPIO119

SPI_SI

SPI_SO

SPI_WP

SPI_HOLD#

SPI_TPM_CS#

AU3

SATA_TX0P

AU4

SATA_TX0N

AV1

SATA_RX0N

AV2

SATA_RX0P

AY2

SATA_TX1P

AY1

SATA_TX1N

AW4

SATA_RX1N

AW3

SATA_RX1P

AW1

SATA_ZVSS

AW2

SATA_ZVDDP

AT17

DEVSLP[0]/EGPIO67

AT12

DEVSLP[1]/EGPIO70

BB15

SATA_ACT_L/AGPIO13 0

AU2

SATA_X1

AU1

SATA_X2

U4

GFX_CLKP

U3

GFX_CLKN

U1

GPP_CLK0P

U2

GPP_CLK0N

W4

GPP_CLK1P

W3

GPP_CLK1N

W1

GPP_CLK2P

W2

GPP_CLK2N

Y2

GPP_CLK3P

Y1

GPP_CLK3N

BC10

X25M_48M_OSC

T2

X48M_X1

T1

X48M_X2

AW14

LPCCLK0/EGPIO74

AY13

LPCCLK1/EGPIO75

BB11

LAD0

BA11

LAD1

AY11

LAD2

BA13

LAD3

AV14

LFRAME_L

BA1

ESPI_ALERT_L/LDRQ0 _L

BC14

SERIRQ/AGPIO87

BC11

LPC_CLKRUN_L/AGPIO88

AE9

LPC_PD_L/AGPIO21

BC6

SPI_CLK/ESPI_CLK/EG PIO117

BB8

SPI_CS1_L/EGPIO11 8

AW7

SPI_CS2_L/ESPI_CS _L/EGPIO119

BA9

SPI_DI/ESPI_DATA /EGPIO120

AY7

SPI_DO/EGPIO121

AW11

SPI_WP_L/EGPIO1 22

BA7

SPI_HOLD_L/EGPIO133

AW12

SPI_TPM_CS_L/AGPIO76

U24E

CLK/SATA/USB/SPI/LPC

FP4 REV 1.0

*FP4

USBCLK/25M_48M_OSC

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

USB_SS_3TXP

USB_SS_3TXN

USB_SS_3RXP

USB_SS_3RXN

AP8

AP5

USB_ZVSS

AR2

AR1

AR3

AR4

AN2

AN1

AN3

AN4

AM1

AM2

AL2

AL1

AL3

AL4

AK2

AJ2

R137 11.8K/F_4

USBP0+ [19]

USBP0- [19]

USBP1+ [24]

USBP1- [24]

USBP2+ [24]

USBP2- [24]

USBP4+ [29]

USBP4- [29]

USBP5+ [17]

USBP5- [17]

USBP6+ [27]

USBP6- [27]

USBP7+ [27]

USBP7- [27]

Camera USB

DB right side USB2.0 port

DB right side USB2.0 port

ALF@1029:

Del the USB2.0 for Touch Screen

WLAN Min-Card

Finger Printer

le

ft side USB Combo 3.0/2.0.

left side USB Combo 3.0/2.0.

CZ: Maximum 8 devices (Ex: 8 USB2.0 –OR-- 4 USB2.0 + 4 USB3.0 external, etc…)

CZ-L: Maximum 8 devices (Ex: 8 USB2.0 –OR-- 6 USB2.0 + 2 USB3.0 external, etc…)

+0.95V_DEEP_SUS

Support S3~S5 wake up

+0.95V

No support S3~S5 wake up

+3V_DEEP_SUS +3V_DEEP_SUS +3V_DEEP_SUS+3V_DEEP_SUS+3V +3V +3V

AD2

AD1

AA3

AA4

W9

W8

AA2

AA1

W5

W6

AC1

AC2

Y6

Y7

AC4

AC3

AB5

AB6

USBSS_CALRN

USBSS_CALRP

R931K/F_4

R941K/F_4

USB30_TX2+ [27]

USB30_TX2- [27]

USB30_RX2+ [27]

USB30_RX2- [27]

USB30_TX3+ [27]

USB30_TX3- [27]

USB30_RX3+ [27]

USB30_RX3- [27]

R73 *0_4/S

R74 *0_4

Left side USB Combo 3.0/2.0.

Left side USB Combo 3.0/2.0.

06

STRAPS PINS

AGPIO11

1

R401

10K/F_4

R421

*2K/F_4

normal reset mode

short reset modeLDT_RST#/LDT_PWRGD

SYS_RST#

DEFAULT

1A

1A

1A

R504

B B

1024@Ronny: AGPIO11 STRAP?

A A

5

4

OVERLAP COMMON PADS WHERE

POSSIBLE FOR DUAL-OP RESISTORS.

AGPIO3[5]

RTC_CLK[5,40]

AGPIO11[5]

SYS_RST#[5]

REQUIRED STRAPS

LPC_CLK0 BLINK

BOOT FAIL TIMER

PULL

ENABLED

HIGH

BOOT FAIL TIMER

PULL

DISABLED

LOW

3

DEFAULT

LPC_CLK0

LPC_CLK1

LFRAME#

CZ: pop R445

CZ-L:pop R457

LPC_CLK1

Use 48Mhz crystal clock

and generate both internal

and external clocks

DEFAULT

Use 100Mhz PCIE clock as

reference clock and generate

internal clocks only

Follow FAE comment: R659 change to 2K, R401 to 10k, R142 is NC

LFRAME#

SPI ROM

DEFAULT

LPC ROM

2

*10K/F_4

R506

2K/F_4

R491

10K/F_4

R485

*2K/F_4

AGPIO3

Int Pull-Up

CZ-L CZ

1.8V SPI ROM

3.3V SPI ROM

DEFAULT

R445

R174

CZ@10K/F_4

10K/F_4

R168

R457

*2K/F_4

*CZL@2K/F_4

RTC_CLK

Int Pull-Up Int Pull-Up Int Pull-Up

NB5

NB5

NB5

Coin battery is

on board.

Coin battery is

not on board.

Enhanced reset logic

(for quicker S5 resume)

DEFAULT DEFAULT DEFAULT

Default to

traditional reset logic

R142

R672

*10K/F_4

10K/F_4

R141

R659

*2K/F_4

*2K/F_4

LDT_RST#/LDT_PWRGD

output to APU

output to Pads

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Carrizo 5/7 (SATA/USB/SPI)

Carrizo 5/7 (SATA/USB/SPI)

Carrizo 5/7 (SATA/USB/SPI)

Date: Sheet of

Friday, July 24, 2015 6 62

Date: Sheet of

Friday, July 24, 2015 6 62

Date: Sheet of

Friday, July 24, 2015 6 62

5

4

3

2

1

07

U8

W7

W12

W15

W18

W21

Y8

Y10

Y13

Y16

Y19

Y22

AB7

AB9

AB12

AB15

AB18

AB21

AD6

AD10

AD13

AD16

AD19

AD22

AE7

AE12

AK9

AG10

AK10

AG13

AK13

AG16

AK16

AG19

AK19

AG22

AK22

AH7

AE18

AE21

AH21

AG6

AH12

AN6

AH15

AH18

AL7

AK6

AE15

L8

L13

L16

L19

L22

N7

N12

N15

N18

N21

P8

P13

P16

P19

P22

T7

F12

F15

G11

G14

J8

J9

J11

K7

K12

K13

K15

K16

T12

T15

T18

T21

U13

U16

U19

U22

K19

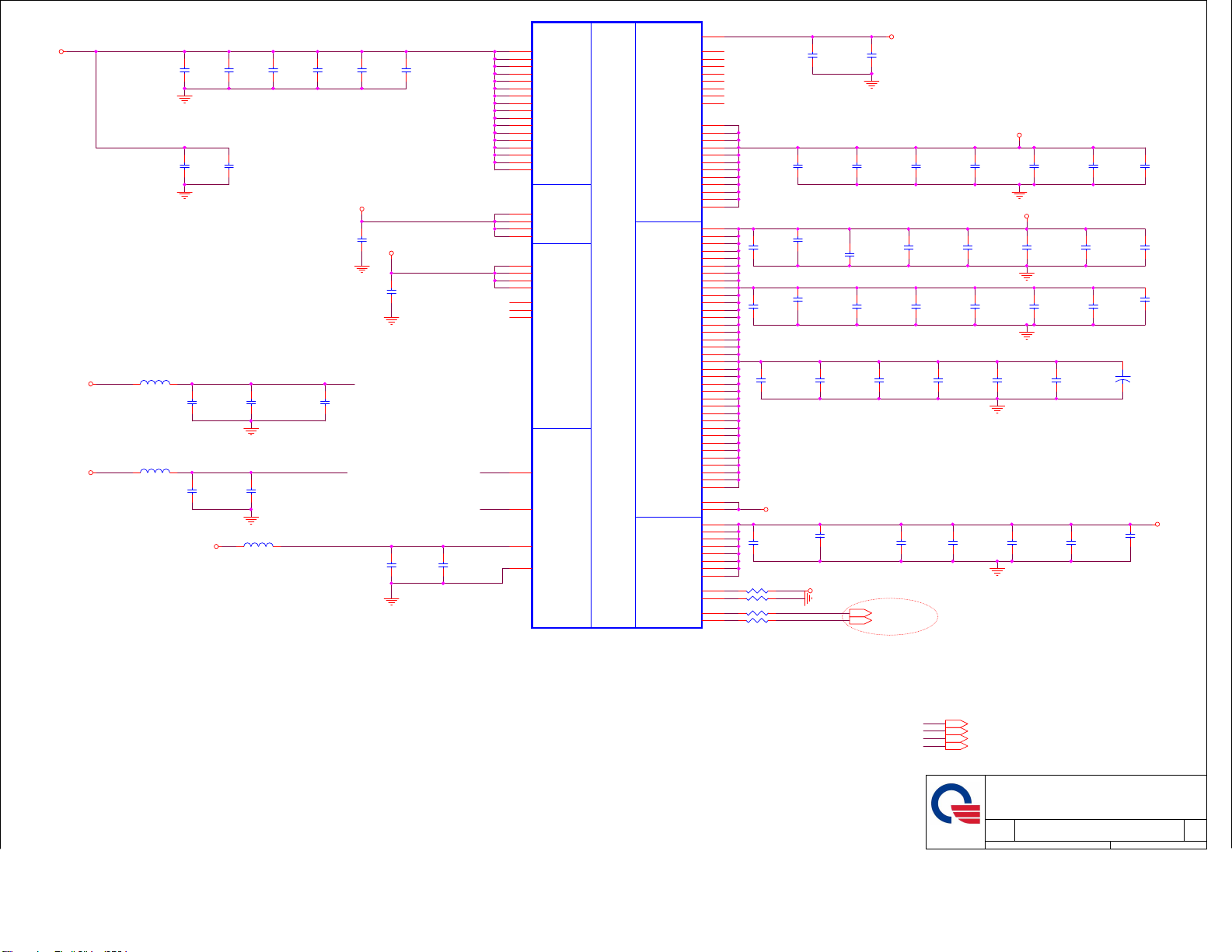

+1.5V_RTC

+VCC_CORE

C132

22U/6.3V_6

C168

0.22U/10V_4

C199

22U/6.3VS_6

C150

0.22U/10V_4

C159

22U/6.3V_6

C121

0.22U/10V_4

C171

22U/6.3V_6

C120

0.22U/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

+0.95V

+APU_VDDGFX

C163

CZ@22U/6.3V_6

C125

CZ@0.22U/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

C441

C452

10U/6.3VS_6

10U/6.3VS_6

C437

C178

0.22U/10V_4

0.22U/10V_4

C226

C170

C152

CZ@22U/6.3V_6

CZ@22U/6.3V_6

CZ@22U/6.3V_6

C182

CZ@0.22U/10V_4

C141

C192

CZ@0.22U/10V_4

CZ@0.22U/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

CZ: All +APU_VDDGFX_RUN cap Stuff.

CZ-L: All +APU_VDDGFX_RUN cap No Stuff.

+VCCRTC_2

+3VPCU

12

CN13

BAT_CONN

DFHS02FS027

BAT-23_2-4_2

+BAT

R208 470/F_4

C439

10U/6.3V_6

C73

0.22U/10V_4

D25

BAT54CW

C203

22U/6.3VS_6

C149

0.22U/10V_4

C116

CZ@22U/6.3V_6

C209

CZ@0.22U/10V_4

C144

22U/6.3V_6

C157

0.22U/10V_4

C440

10U/6.3V_6

C438

0.22U/10V_4

C128

CZ@22U/6.3V_6

C180

CZ@0.22U/10V_4

+3VRTC

C320

0.1U/16V/X7R_4

C167

22U/6.3VS_6

C135

0.22U/10V_4

C442

0.22U/10V_4

C151

CZ@22U/6.3V_6

C118

CZ@0.22U/10V_4

20MIL

+3VRTC

C318

1U/10V_4

12

C193

22U/6.3VS_6

C136

0.22U/10V_4

C75

0.22U/10V_4

C131

CZ@22U/6.3V_6

C164

CZ@0.22U/10V_4

U10

3

VIN

IC AP2138N-1.5TRG1

C200

22U/6.3VS_6

C142

180P/50V_4

C179

180P/50V_4

SI, 0210, reserved 3528 cap

C198

CZ@22U/6.3V_6

C139

CZ@0.22U/10V_4

2

GND

1

VOUT

12

+

C621

*330U_2.5V_3528

C123

CZ@180P/50V_4

+1.5V_RTC

C325

10U/6.3V_6

+1.35VSUS

3A

P25

VDDIO_MEM_S3_1

P28

VDDIO_MEM_S3_2

T24

VDDIO_MEM_S3_3

T27

VDDIO_MEM_S3_4

C339

22U/6.3VS_6

C297

22U/6.3VS_6

C300

22U/6.3VS_6

C290

22U/6.3VS_6

C283

0.22U/10V_4

C211

D D

22U/6.3VS_6

C296

22U/6.3VS_6

C345

0.22U/10V_4

C289

22U/6.3VS_6

C286

0.22U/10V_4

C197

22U/6.3VS_6

C326

0.22U/10V_4

C288

*22U/6.3VS_6

C207

0.22U/10V_4

C298

*22U/6.3VS_6

C324

0.22U/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

C205

C204

C346

0.22U/10V_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

ACROSS VDDNB AND VSS SPLIT

C122

0.22U/10V_4

+VDDP_GFX

R402

CZ: always pop

C C

CZ-L PX: Stuff

UMA: No Stuff

+0.95V +VDDP_GFX

R402 0_6

C436

10U/6.3VS_6

C206

0.22U/10V_4

0.22U/10V_4

R155

R155

only pop on

*0_4

CZ-L UMA SKU.

ALF@1031:

Changed Power Naming

+VDDCR_FCH_S5 +VDDCR_FCH_S5_R

+VDDCR_FCH_S5

R175

CZ: Stuff

CZ-L: No Stuff

R175 CZ@0_4

C148

0.22U/10V_4

C426

0.22U/10V_4

C188

CZ@10U/6.3VS_6

C433

0.22U/10V_4

C187

CZ@10U/6.3VS_6

C435

0.22U/10V_4

C429

0.22U/10V_4

C174

CZ@0.22U/10V_4

C201

22U/6.3V_6

0.22U/10V_4

C140

22U/6.3V_6

C208

180P/50V_4

+APU_VDDIO_AZ

+VDDP_GFX

+APU_VDD_33

+APU_VDD_18_S5

+APU_VDD_33_S5

+VDDP_S5

+VDDCR_FCH_S5_R

C137

22U/6.3V_6

+1.8V

+0.95V

+VDDNB_CORE

ACROSS VDDNB AND VSS SPLIT

B B

C173

0.22U/10V_4

C432

0.22U/10V_4

C183

0.22U/10V_4

C156

0.22U/10V_4

C154

0.22U/10V_4

C427

0.22U/10V_4

C430

0.22U/10V_4

C166

0.22U/10V_4

C299

*22U/6.3VS_6

C321

180P/50V_4

C323

180P/50V_4

C117

22U/6.3V_6

C431

180P/50V_4

AB24

AB27

AB30

AB33

AD25

AD28

AD30

AE24

AE27

AF30

AF33

AG25

AG28

AH24

AH27

AH30

AK25

AK28

AK30

AK33

AL27

AM30

AR19

AP19

AP21

AP16

AP18

AP10

AP15

AR15

AN12

AP12

AP13

AR12

AW19

AU17

AU19

AV17

AV19

AW17

AL12

AL13

AL15

AL18

AL21

AN13

AN16

AN19

AN22

AR17

U25

U28

V30

V33

W24

W27

Y25

Y28

Y30

AE6

AE5

AR9

VDDIO_MEM_S3_5

VDDIO_MEM_S3_6

VDDIO_MEM_S3_7

VDDIO_MEM_S3_8

VDDIO_MEM_S3_9

VDDIO_MEM_S3_10

VDDIO_MEM_S3_11

VDDIO_MEM_S3_12

VDDIO_MEM_S3_13

VDDIO_MEM_S3_14

VDDIO_MEM_S3_15

VDDIO_MEM_S3_16

VDDIO_MEM_S3_17

VDDIO_MEM_S3_18

VDDIO_MEM_S3_19

VDDIO_MEM_S3_20

VDDIO_MEM_S3_21

VDDIO_MEM_S3_22

VDDIO_MEM_S3_23

VDDIO_MEM_S3_24

VDDIO_MEM_S3_25

VDDIO_MEM_S3_26

VDDIO_MEM_S3_27

VDDIO_MEM_S3_28

VDDIO_MEM_S3_29

VDDIO_MEM_S3_30

VDDIO_MEM_S3_31

VDDIO_MEM_S3_32

VDDIO_MEM_S3_33

VDDIO_MEM_S3_34

VDDIO_MEM_S3_35

0.2A

VDDIO_AUDIO

1.5A

VDDP_GFX_2

VDDP_GFX_1

0.2A

VDD_33_1

VDD_33_2

1.5A

VDD_18_1

VDD_18_2

0.5A

VDD_18_S5_1

VDD_18_S5_2

0.2A

VDD_33_S5_1

VDD_33_S5_2

0.8A

VDDP_S5_1

VDDP_S5_2

0.2A

VDDCR_FCH_S5_1

VDDCR_FCH_S5_2

7A

VDDP_6

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

12A

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDBT_RTC_G

BOTTOM SIDE DECOUPLING UNDER APU

20MIL

VDDBT_RTC

12

G1

*SHORT_ PAD1

+1.5V

+APU_VDDIO_AZ

ALF@1031:

Changed Power Naming

1029@RNY: follow DG

+1.8V

+1.8V_DEEP_SUS +APU_VDD_18_S5

R209 *0_4/S

1.5V For HDA Only

A A

C202

1U/10V_4

C248

1U/10V_4

C242

1U/10V_4

C238

10U/6.3VS_6

C230

0.22U/10V_4

C322

0.22U/10V_4

R152 *0_4/S

C126

10U/6.3VS_6

12

C224

1U/10V_4

U24F

POWER

FP4 REV 1.0

*FP4

R287 1K/F_4

C113

0.22U/10V_4

22~39A

VDDCR_CPU_1

VDDCR_CPU_2

VDDCR_CPU_3

VDDCR_CPU_4

VDDCR_CPU_5

VDDCR_CPU_6

VDDCR_CPU_7

VDDCR_CPU_8

VDDCR_CPU_9

VDDCR_CPU_10

VDDCR_CPU_11

VDDCR_CPU_12

VDDCR_CPU_13

VDDCR_CPU_14

VDDCR_CPU_15

VDDCR_CPU_16

VDDCR_CPU_17

VDDCR_CPU_18

VDDCR_CPU_19

VDDCR_CPU_20

VDDCR_CPU_21

VDDCR_CPU_22

VDDCR_CPU_23

VDDCR_CPU_24

VDDCR_CPU_25

VDDCR_CPU_26

VDDCR_CPU_42

VDDCR_CPU_31

VDDCR_CPU_43

VDDCR_CPU_32

VDDCR_CPU_44

VDDCR_CPU_33

VDDCR_CPU_45

VDDCR_CPU_34

VDDCR_CPU_46

VDDCR_CPU_35

VDDCR_CPU_47

VDDCR_CPU_36

VDDCR_CPU_28

VDDCR_CPU_29

VDDCR_CPU_40

VDDCR_CPU_30

VDDCR_CPU_37

VDDCR_CPU_49

VDDCR_CPU_38

VDDCR_CPU_39

VDDCR_CPU_48

VDDCR_CPU_41

VDDCR_CPU_27

22~30A

VDDCR_GFX_14

VDDCR_GFX_15

VDDCR_GFX_16

VDDCR_GFX_17

VDDCR_GFX_18

VDDCR_GFX_19

VDDCR_GFX_20

VDDCR_GFX_21

VDDCR_GFX_22

VDDCR_GFX_23

VDDCR_GFX_24

VDDCR_GFX_25

VDDCR_GFX_26

VDDCR_GFX_27

VDDCR_GFX_28

VDDCR_GFX_29

VDDCR_GFX_1

VDDCR_GFX_2

VDDCR_GFX_3

VDDCR_GFX_4

VDDCR_GFX_5

VDDCR_GFX_6

VDDCR_GFX_7

VDDCR_GFX_8

VDDCR_GFX_9

VDDCR_GFX_10

VDDCR_GFX_11

VDDCR_GFX_12

VDDCR_GFX_30

VDDCR_GFX_31

VDDCR_GFX_32

VDDCR_GFX_33

VDDCR_GFX_34

VDDCR_GFX_35

VDDCR_GFX_36

VDDCR_GFX_37

VDDCR_GFX_13

400 series 1002

400 series 1002

400 series 1002400 series 1002

+3V +APU_VDD_33

R188 *0_4/S

C219

10U/6.3VS_6

5

+3V_DEEP_SUS +APU_VDD_33_S5 +0.95V_DEEP_SUS +VDDP_S5

R187 *0_4/S

4

C223

10U/6.3VS_6

C222

0.22U/10V_4

R154 *0_6/S

C114

10U/6.3VS_6

C119

0.22U/10V_4

3

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Carrizo 6/7 (POWER)

Carrizo 6/7 (POWER)

NB5

NB5

2

NB5

Carrizo 6/7 (POWER)

Date: Sheet of

Friday, July 24, 2015 7 62

Date: Sheet of

Friday, July 24, 2015 7 62

Date: Sheet of

Friday, July 24, 2015 7 62

1

1A

1A

1A

5

4

3

2

1

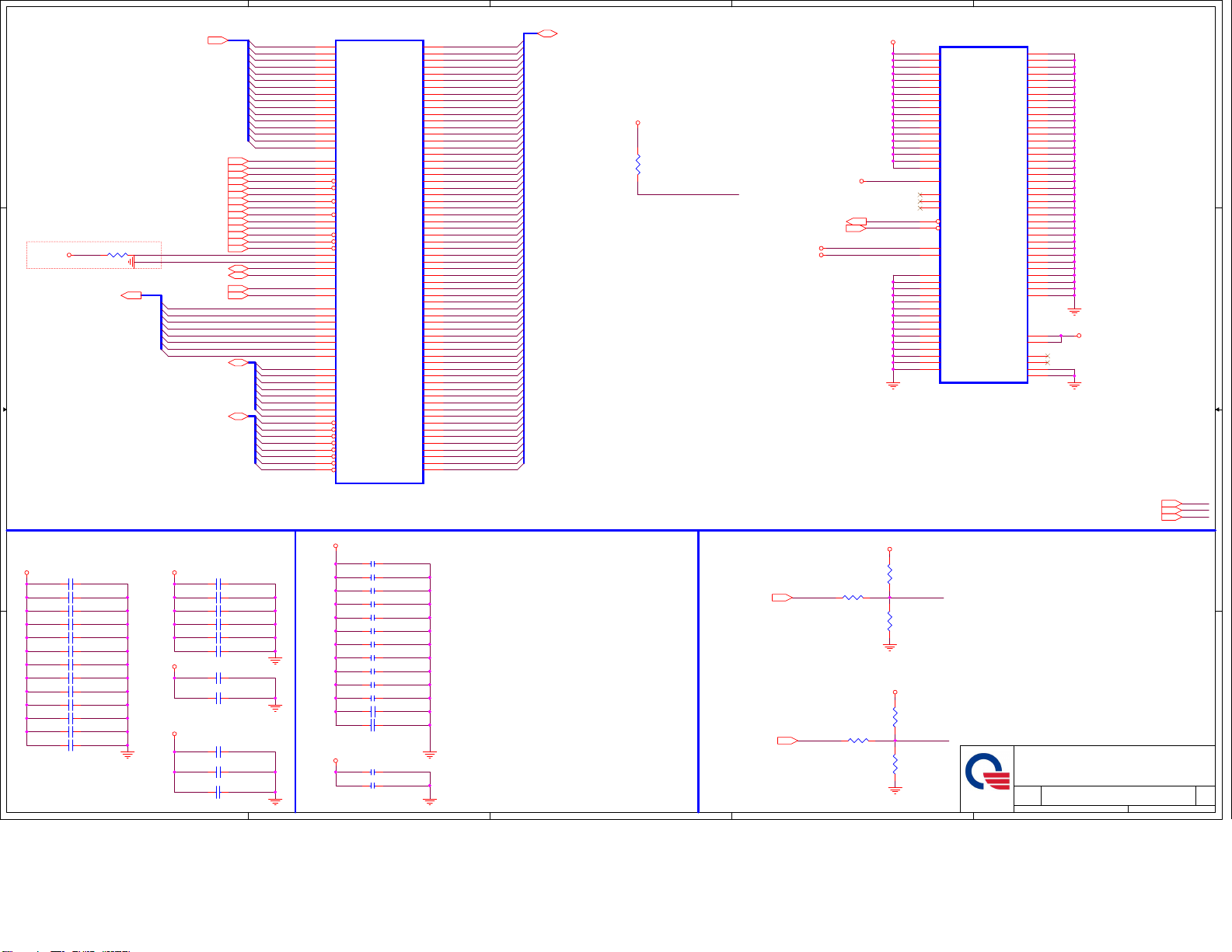

08

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

U24G

GND

FP4 REV 1.0

*FP4

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

L28

M4

M30

N10

N13

N16

N19

N22

N27

P1

P2

P4

P5

P12

P15

P18

P21

P30

P33

T4

T10

T13

T16

T19

T22

T30

U5

U12

U15

U18

U21

U24

V1

V2

V4

W10

W13

W16

W19

W22

Y4

Y5

Y12

Y15

Y18

Y21

Y24

AB1

AB2

AB4

AB10

AB13

AB16

AB19

AB22

AD4

AD9

AD12

AD15

AD18

AD21

AD24

AE10

AE13

AE16

AE19

AE22

AF1

AF4

AG9

AG12

AG15

AG18

AG21

AH4

AH10

AH13

AH16

AH19

AH22

AK1

AK4

AK12

AK15

AK18

AL16

AL19

AL22

AM4

AN9

AN10

AN15

AN18

AN21

AN25

AN28

AP1

AP2

AP4

AP7

AP22

AP27

AP30

AP33

AR6

AR25

AR28

AT4

AT19

AT22

AT30

AU5

AU8

AU11

AU14

AU20

AU23

AU27

AV4

AV7

AV9

AV12

AV15

AV25

D D

A8

ORIENT_APU#

TP55

C C

B B

A12

A16

A20

A24

A28

A32

B12

B33

D10

D12

D14

D16

D18

D20

D22

D24

D26

D28

D30

F19

F22

F25

F30

F33

G17

G20

G23

G26

H30

J15

J19

J22

J25

J28

K10

K22

K27

K30

K33

L12

L15

L18

L21

L25

B2

B8

C3

D4

D6

D8

F1

F2

F4

F9

G7

H4

J5

K1

K2

K4

L5

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

U24H

GND

FP4 REV 1.0

*FP4

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_215

VSS_214

AV30

AV33

AW22

AY4

AY6

AY8

AY10

AY12

AY14

AY16

AY20

AY22

AY24

AY26

AY28

AY30

BB1

BB33

BC4

BC8

BC12

BC16

BC20

BC24

BC28

BC32

L24

AL10

AK21

TP32

TP33

TP77

APU_U30

APU_U31

APU_AN30

U30

U31

AN30

RSVD_2

RSVD_3

RSVD_4

U24J

FP4 REV 1.0

*FP4

A A

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Carrzio 7/7 (GND)

Carrzio 7/7 (GND)

NB5

NB5

5

4

3

2

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

Carrzio 7/7 (GND)

Friday, July 24, 2015 8 62

Friday, July 24, 2015 8 62

Friday, July 24, 2015 8 62

1

1A

1A

1A

5

4

3

2

1

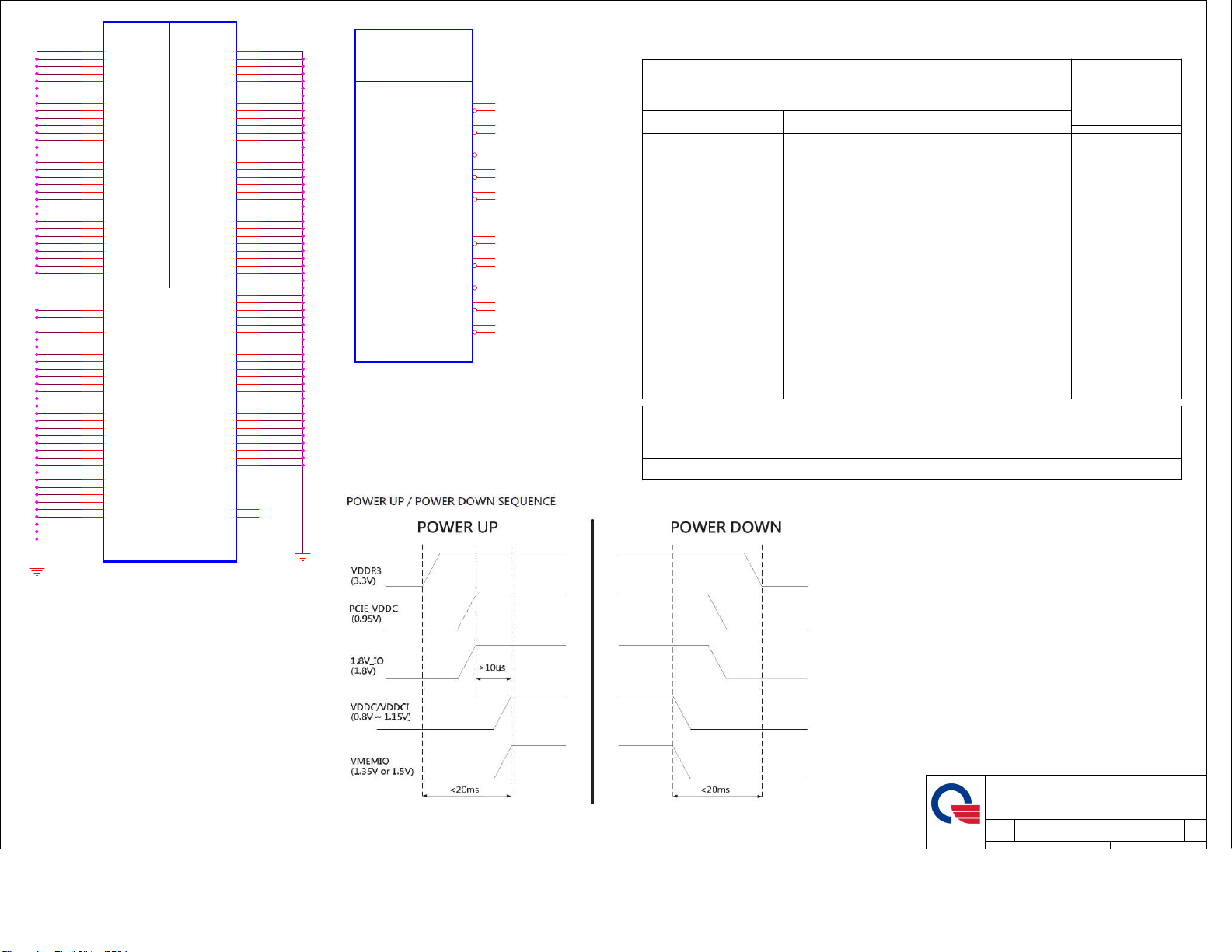

M_B_A[15:0][3,10]

D D

M_B_BS#0[3,10]

M_B_BS#1[3,10]

M_B_BS#2[3,10]

M_B_CS#0[3]

M_B_CS#1[3]

M_B_CLKP0[3]

M_B_CLKN0[3]

M_B_CLKP1[3]

FCH_3S_SMCLK[5,10,20,28]

FCH_3S_SMDATA[5,10,20,28]

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQSP[7:0][3,10]

M_B_DQSN[7:0][3,10]

M_B_CLKN1[3]

M_B_CKE0[3,10]

M_B_CKE1[3,10]

M_B_CAS#[3,10]

M_B_RAS#[3,10]

M_B_WE#[3,10]

M_B_ODT0[3]

M_B_ODT1[3]

Ronny@1013:

2 So-Dimm per 1 Channel

R309 4.7K_4

+3V

M_B_DM[7..0][3,10]

C C

B B

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

DIMM0_SA0

DIMM0_SA1

FCH_3S_SMCLK

FCH_3S_SMDATA

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

Place these Caps near So-Dimm0.

+1.35VSUS +0.65V_DDR_VTT

C349 1U/6.3V_4

C351 1U/6.3V_4

C347 1U/6.3V_4

C362 1U/6.3V_4

C395 10U/6.3VS_6

C344 10U/6.3VS_6

C364 10U/6.3VS_6

C352 10U/6.3VS_6

C379 10U/6.3VS_6

C350 10U/6.3VS_6

A A

C363 *10U/6.3VS_6

C361 10U/6.3VS_6

C372 10U/6.3VS_6

+VREF_DQ0

+VREF_CA0

5

C380 1U/6.3V_4

C342 1U/6.3V_4

C381 1U/6.3V_4

C360 1U/6.3V_4

C377 10U/6.3VS_6

C340 *10U/6.3VS_6

C354 0.1U/16V/X7R_4

C353 1000P/50V_4

C356 0.1U/16V/X7R_4

C368 1000P/50V_4

C355 *0.047U/10V_4

JDIM1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3-DIMM1_H=4.0_RVS

ddr-ddrrk-20401-tp4b-204p-smt

DGMK0000158

SOCKET DDR3 SODIMM(204P,H4.0,RVS)QBCON

+1.35VSUS

EC6 180P/50V_4

EC16 180P/50V_4

EC9 180P/50V_4

EC26 220P/50V_4

EC12 220P/50V_4

EC20 220P/50V_4

EC23 220P/50V_4

EC22 220P/50V_4

EC24 220P/50V_4

EC15 220P/50V_4

EC17 220P/50V_4

EC8 0.1U/16V/X7R_4

EC11 2200P/50V_4

+0.65V_DDR_VTT

EC13 *120P/50V_4

EC7 *120P/50V_4

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

(204P)

PC2100 DDR3 SDRAM SO-DIMM

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

4

5

M_B_DQ5

7

M_B_DQ4

15

M_B_DQ3

17

M_B_DQ2

4

M_B_DQ0

6

M_B_DQ1

16

M_B_DQ6

18

M_B_DQ7

21

M_B_DQ9

23

M_B_DQ13

33

M_B_DQ14

35

M_B_DQ10

22

M_B_DQ8

24

M_B_DQ12

34

M_B_DQ11

36

M_B_DQ15

39

M_B_DQ20

41

M_B_DQ21

51

M_B_DQ18

53

M_B_DQ22

40

M_B_DQ17

42

M_B_DQ16

50

M_B_DQ19

52

M_B_DQ23

57

M_B_DQ25

59

M_B_DQ29

67

M_B_DQ27

69

M_B_DQ26

56

M_B_DQ28

58

M_B_DQ24

68

M_B_DQ31

70

M_B_DQ30

129

M_B_DQ36

131

M_B_DQ37

141

M_B_DQ35

143

M_B_DQ34

130

M_B_DQ33

132

M_B_DQ32

140

M_B_DQ39

142

M_B_DQ38

147

M_B_DQ44

149

M_B_DQ40

157

M_B_DQ42

159

M_B_DQ43

146

M_B_DQ45

148

M_B_DQ41

158

M_B_DQ46

160

M_B_DQ47

163

M_B_DQ49

165

M_B_DQ48

175

M_B_DQ54

177

M_B_DQ55

164

M_B_DQ52

166

M_B_DQ53

174

M_B_DQ50

176

M_B_DQ51

181

M_B_DQ61

183

M_B_DQ56

191

M_B_DQ63

193

M_B_DQ62

180

M_B_DQ57

182

M_B_DQ60

192

M_B_DQ58

194

M_B_DQ59

M_B_DQ[63:0] [3,10]

3

+1.35VSUS

R329

1K/F_4

M_B_EVENT#

M_B_EVENT#[3,10]

M_B_RST#[3,10]

+VREF_DQ0

+VREF_CA0

DDR_VTTREF[10,45]

M_B_VREFDQ[3,10]

R312 *0_6

3mA

R308 *0_6

3mA

2.48A

+3V

+VREF_DQ0

+VREF_CA0

2

+1.35VSUS

M_B_EVENT#

+1.35VSUS

R311

1K/F_4

R310

1K/F_4

+1.35VSUS

JDIM1B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

31

32

37

38

43

1014: Ronny

follow DG use voltage divider

+VREF_CA0

53537_105 change:

Type 1: and Type 2: from 1K/2 voltage

R306

1K/F_4

+VREF_DQ0

R307

1K/F_4

PC2100 DDR3 SDRAM SO-DIMM

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

DDR3-DIMM1_H=4.0_RVS

ddr-ddrrk-20401-tp4b-204p-smt

DGMK0000158

SOCKET DDR3 SODIMM(204P,H4.0,RVS)QBCON

NB5

NB5

NB5

44

VSS16

48

VSS17

49

VSS18

54

VSS19

55

VSS20

60

VSS21

61

VSS22

65

VSS23

66

VSS24

71

VSS25

72

VSS26

127

VSS27

128

VSS28

133

VSS29

134

VSS30

138

VSS31

139

VSS32

144

VSS33

145

VSS34

150

VSS35

151

VSS36

155

VSS37

156

VSS38

161

VSS39

162

VSS40

167

VSS41

168

VSS42

172

VSS43

173

VSS44

178

VSS45

179

VSS46

184

VSS47

185

VSS48

189

VSS49

190

VSS50

195

VSS51

196

VSS52

(204P)

203

VTT1

204

VTT2

205

GND

206

GND

207

GND

208

GND

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Size Document Number Rev