5

D D

4

3

2

1

C C

Wistron Confidential

MV1

2010/1/21 REV :MV-01

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Cover

Cover

Cover

PATEK

PATEK

PATEK

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

150Thursday, January 21, 2010

150Thursday, January 21, 2010

150Thursday, January 21, 2010

1

of

of

of

-1

-1

-1

5

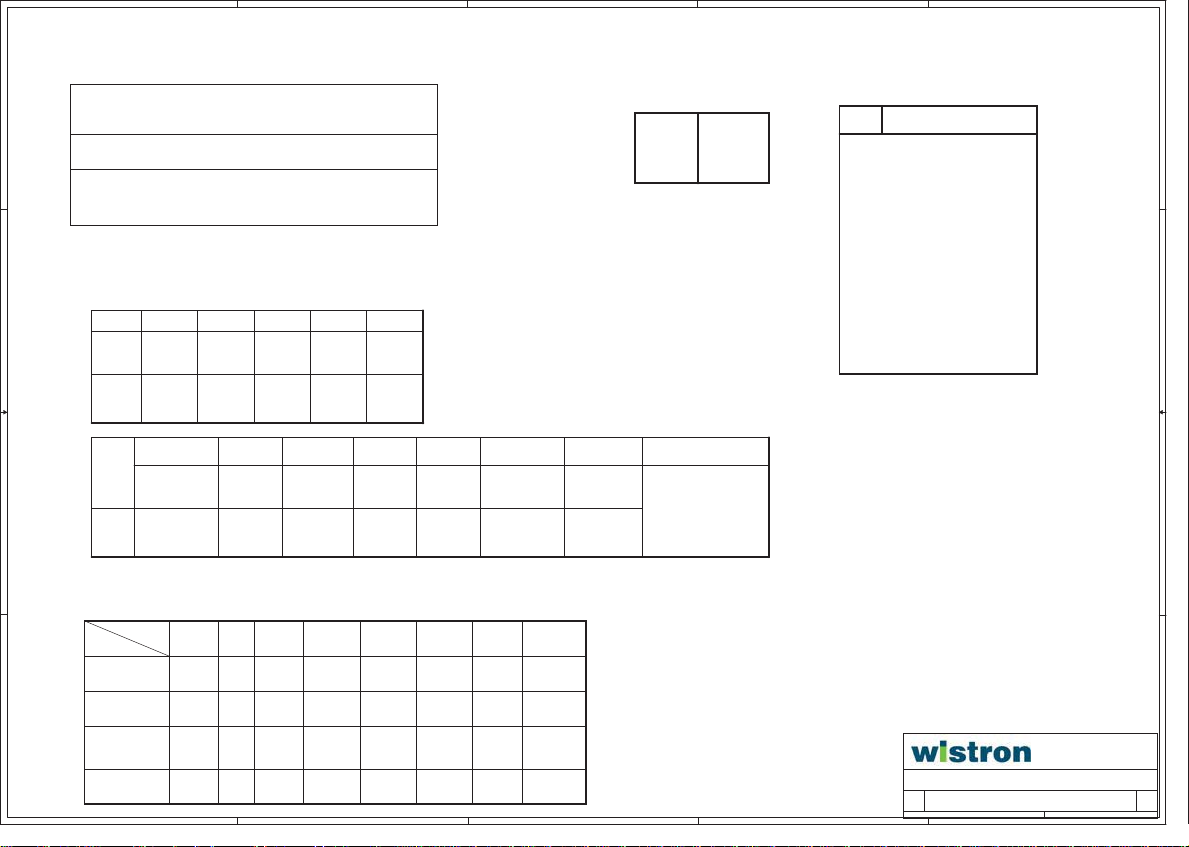

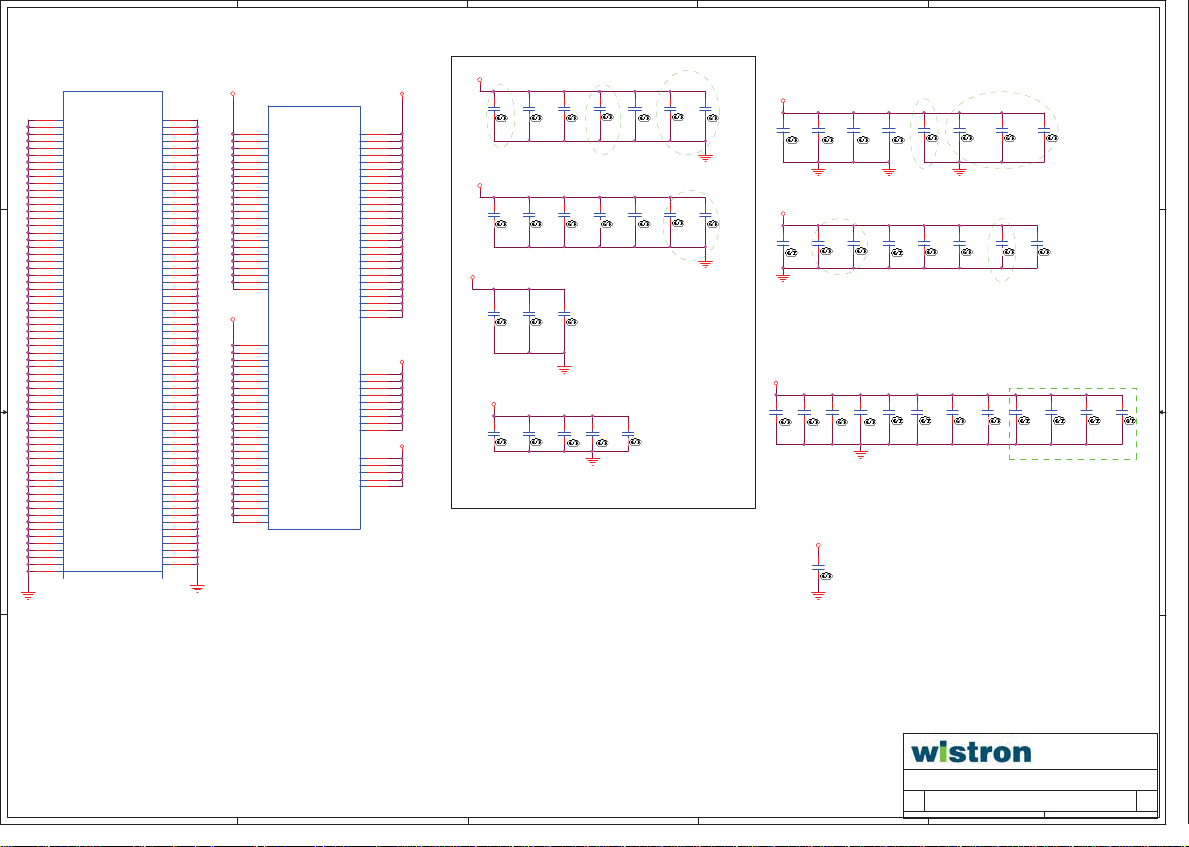

Patek UMA Block Diagram

30

Pre-AMP

35

DDRIII

800/1066/1333

DDRIII

800/1066/1333

D D

RJ45

CONN

C C

B B

RJ11

CONN

30

INTERNAL

D-MIC

MIC IN TLV2462

HEADPHONE

A A

2CH SPEAKER

5

Slot 0

Slot 1

REALTEK

RTL8151

10/100/1000

Mini-Card

WLAN

Express Card

34

Thermal Sensor

G781

Accelerometer

ST HP302DL

MODEM

MDC V1.5

HP Vulcan

AUDIO CODEC

IDT 92HD80

8

9

29

28

27

24

28

32

33

4

DDRIII Channel A

DDRIII Channel B

PCIE

PCIE

PCIE+USB 2.0

SMBUS

HD Audio

4

AMD CPU

Champlain

S1G4 package

HT3.0

16X16

4,5,6,7

North Bridge

AMD RS8800M/RX881

LVDS, CRT I/FCPU I/F

INTEGRATED GRAHPICS

10,11,12,13

A-Link

4x1

South Bridge

AMD SB820M

14 USB 2.0/1.1 ports

ETHERNET (10/100/1000Mb)

High Definition Audio

6 SATA ports

4 PCIe GPP

ACPI 1.1

LPC I/F

PCI/PCI BRIDGE

16,17,18,19,20

USB 2.0

RealTek

RTS5138

SD/MMC

MS/MS Pro/xD

Mini-Card

WWAN

26

SIM Card

26

3

Clock Generator

ICS9LRS3197

R.G.B

LVDS

HDMI

21

CRT

1600X1200@75

LCD

WXGA+

HDMI

14

15

23

Fringer printer

USB 2.0

CAMERA

BLUETOOTH

USB x 3

SATAII

SATAII+USB2.0

LPC Bus

SPI

USB 2.0

SMSC KBC1098

50

50

3

SPI

Flash ROM

2 MB

2

VFS451

23

15

25

25

KBC

31

Touch

Int.

PAD

22 32

KB

32

2

1

SYSTEM DC/DC

INPUTS

DCBATOUT

SYSTEM DC/DC

INPUTS

SYSTEM DC/DC

INPUTS

+3VS

SYSTEM DC/DC

INPUTS

+1.5VS

SYSTEM DC/DC

INPUTS

+5VALW

MAXIM CHARGER

INPUTS

DCBATOUT

HDD

27

ODD

27

e-SATA

25

LPC debug

22

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Date: Sheet

Date: Sheet

Date: Sheet

A3

A3

A3

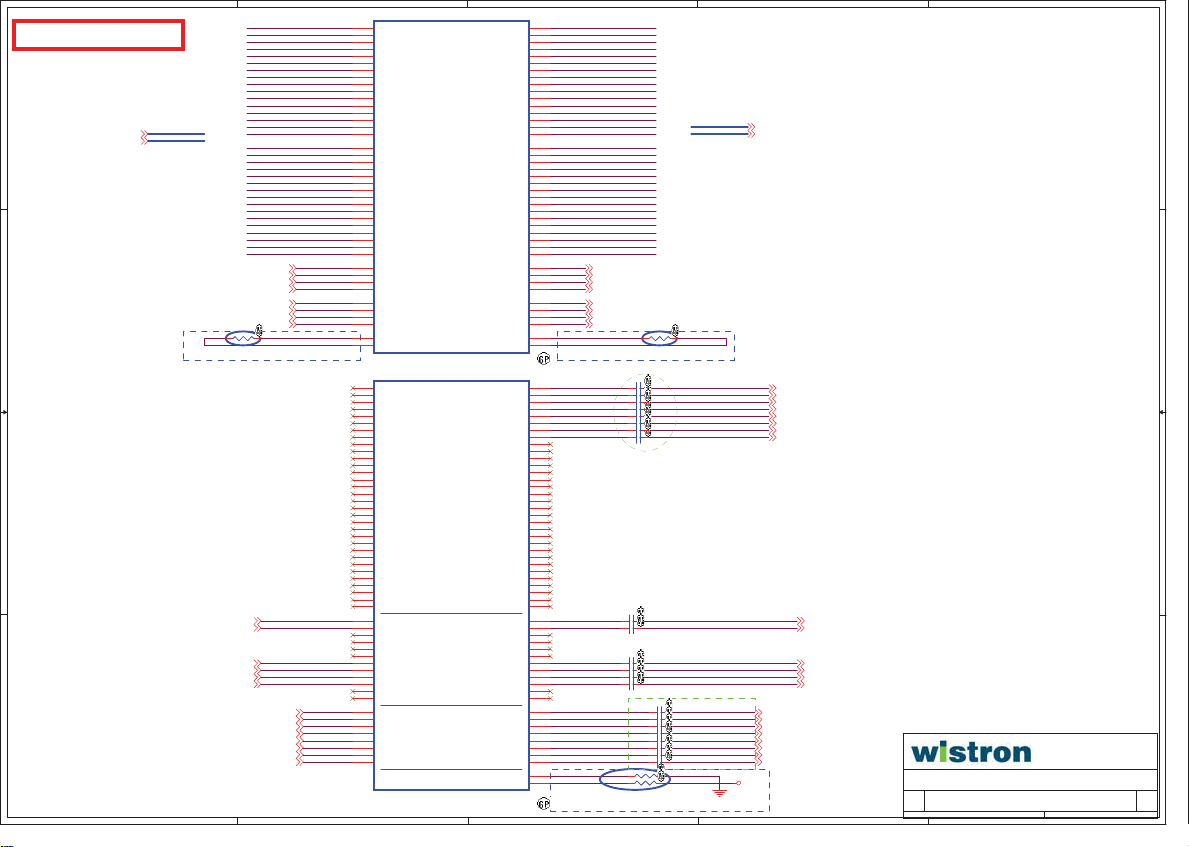

Block Diagram

Block Diagram

Block Diagram

ISL6265/RT8209B

INPUTS

DCBATOUT

+5VALW

PCB 6 LAYER

L1:

L2:

L3:

L4:

L5:

L6:

PATEK

PATEK

PATEK

1

RT8205A

OUTPUTS

+5VALW

+3VALW

RT8209B

OUTPUTS

+1.1VALW+5VALW

G972

OUTPUTS

+1.8VS

G9091/RT9205

OUTPUTS

+2.5VS_LDO_CPU+3VS

+1.05VS

RT8207

OUTPUTS

+1.5V

+0.75V

BQ24740

OUTPUTS

BT+

18V 3.0A

5V 100mA

CPU DC/DC

OUTPUTS

+VCC_CORE

+VDDNB

+NB_VDDC

Signal 1

GND

Signal 2

Signal 3

VCC

Signal 4

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

250Tuesday, February 09, 2010

250Tuesday, February 09, 2010

250Tuesday, February 09, 2010

of

of

of

+VL

+3VL

39

41

38

37

40

43

36

46

-1

-1

-1

5

4

3

2

1

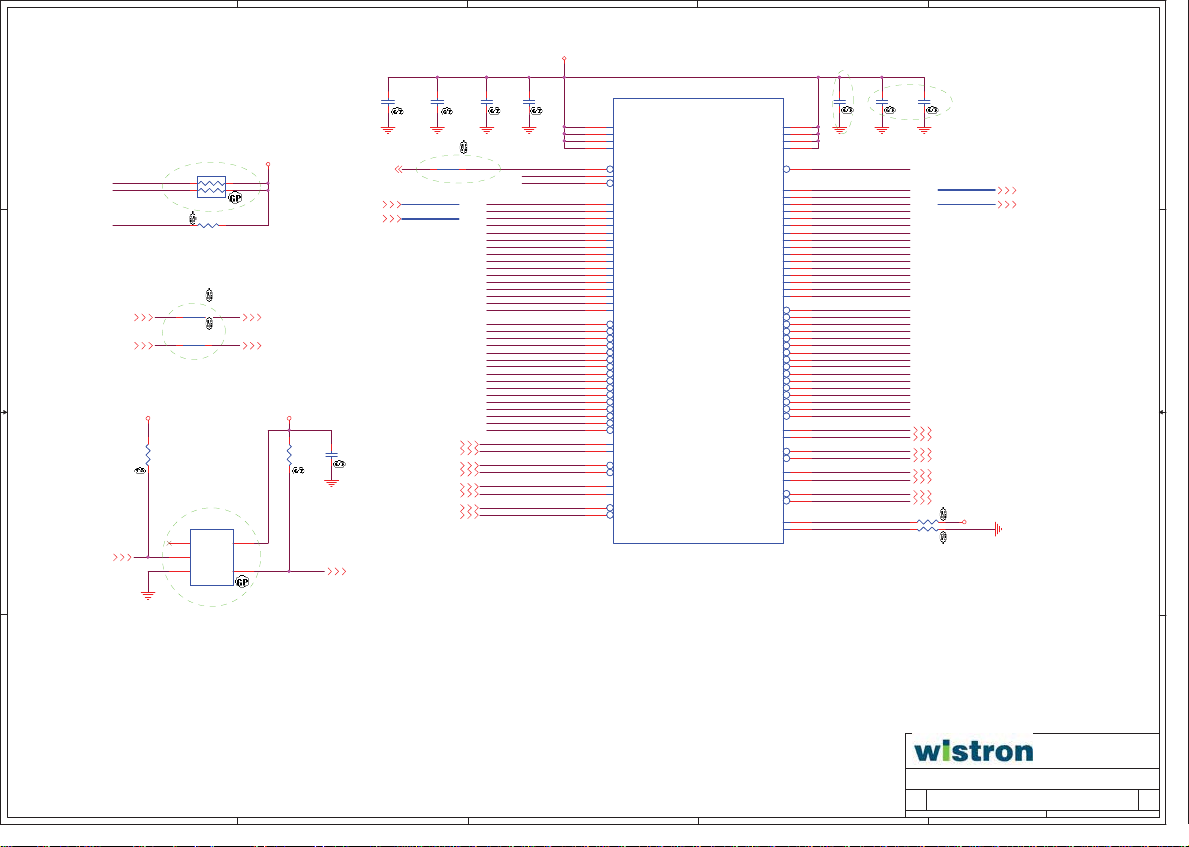

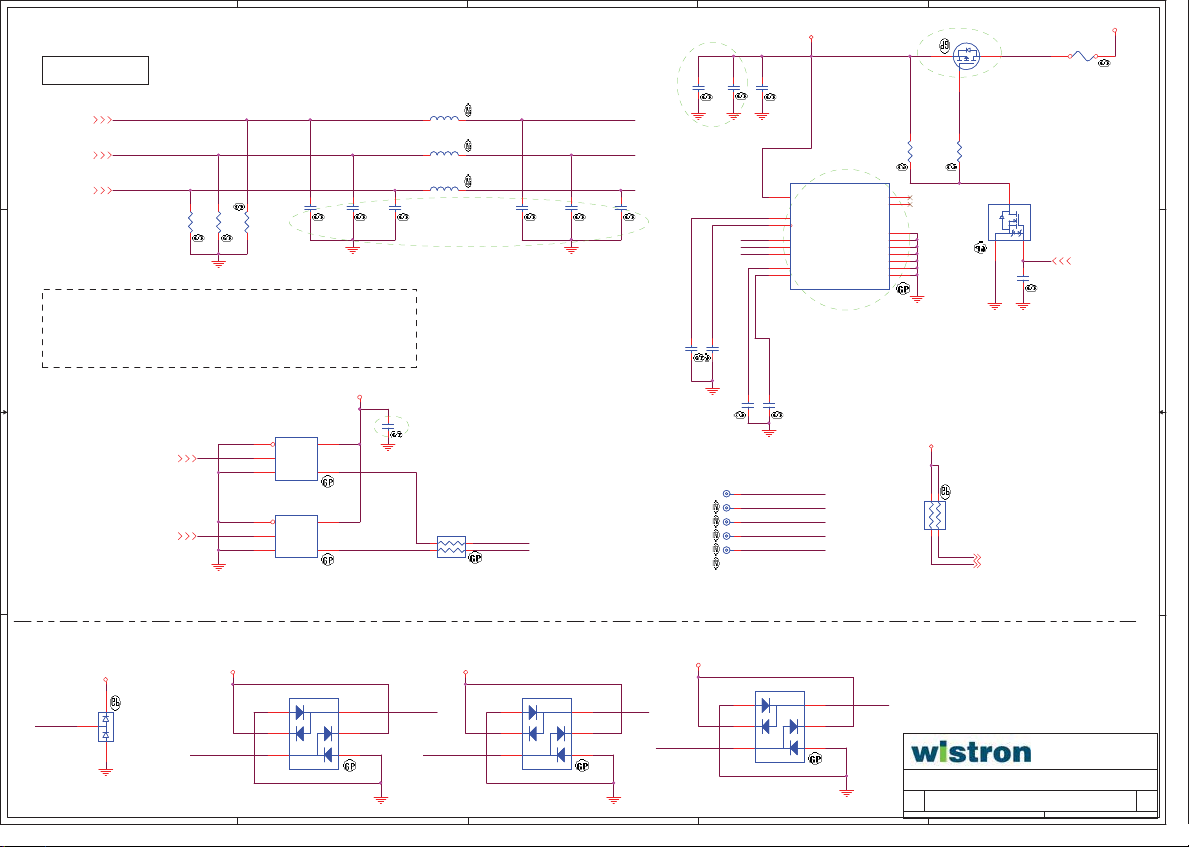

RS880M strapping

STRAP_DEBUG_BUS_GPIO_ENABLEb

D D

Enables the Test Debug Bus using GPIO.(PIN: RS880M--> VSYNC)

0 : Enable 1 : Disable

RS880: Enables Side port memory ( RS880 use HSYNC)

0 : Enable 1 : Disable

SUS_STAT#

Selects Loading of STRAPS From EEPROM

1 : Bypass the loading of EEPROM straps and use Hardware Default Values

*

0 : I2C Master can load strap values from EEPROM if connected,

or use default values if not connected

*

*

PCIE routing

Page 10

LANE 0

LANE 3

LANE 4

LAN

NEW CARD

WLAN

SB820M strapping

C C

Note: SB820 has 15K internal PU FOR PCI_AD[27:23]

USE PCI

PULL

PLL

HIGH

BYPASS

PULL

PCI PLL

LOW

PCI_AD25 PCI_AD23

PCI_AD26PCI_AD27

USE FC

Disable ILA

PLL

AUTORUN

Enable ILA

BYPASS FC

AUTORUN

PLL

PCI_AD24

USE DEFAULT

PCIE STRAPS

USE EEPROM

PCIE STRAPS

Disable PCI

MEM BOOT

(DEFAULT)(DEFAULT)(DEFAULT)(DEFAULT)(DEFAULT)

Enable PCI

MEM BOOT

USB table

Pair Device

USB-FSD1 FPR

USB-9 Bluetooth

USB-8 WLAN

USB-7 WWAN

USB-6 USB Card Reader

USB-5 Right Side

USB-4 USB Camera

USB-3 Right Side

USB-2 Left Side (e-SATA combo)

USB-1 New Card

USB-0 Left Side (S/W Debug port)

Page 19

AZ_SDOUT#

PULL

HIGH

LOW POWER

MODE

B B

PULL

LOW

PERFORMANCE

MODE

DEFAULT

PCI_CLK1

Allow

PCIE GEN2

Force

PCIE GEN1

DEFAULT

PCI_CLK2

WatchDOG

(NB_PWRGD)

ENABLED

WatchDog

(NB_PWRGD)

DISABLED

DEFAULT

USE

DEBUG

STRAPS

IGNORE

DEBUG

STRAPS

DEFAULT

PCI_CLK4PCI_CLK3

non_Fusion

CLOCK mode

DEFAULT

Fusion

CLOCK mode

LPC_CLK_KBC

(LPCCLK0)

ENABLE EC

DISABLE EC

DEFAULT

LPC_CLK_DB

(LPCCLK1)

CLKGEN

ENABLED

(Use Internal)

CLKGEN

DISABLED

(Use External)

DEFAULT

SB_GPO200 , SB_GPO199

ROM TYPE:

H, H = Reserved

H, L = SPI ROM

L, H = LPC ROM

L, L = FWH ROM

DEFAULT

SMBUS Control Table

SOURCE

AB1A_DATA

AB1A_CLK

SB_SMB_CLK1

A A

SB_SMB_DAT1

SB_SMB_CLK0

SB_SMB_DAT0

CPU_SIC_SB700

CPU_SID_SB700

SMSC1098

V XXXXX

SB820M

X

SB820M

X VVVV

CPU

XXXXXX

5

CLK GEN SODIMM G-SENSOR

SENSOR

XXXX

4

THERMAL

BATT

SMSC1098

X

X

SB-TSI

X

X

X

V

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

3

2

Date: Sheet

PATEK

PATEK

PATEK

NOTES

NOTES

NOTES

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

350Thursday, January 21, 2010

350Thursday, January 21, 2010

350Thursday, January 21, 2010

1

-1

-1

-1

of

of

of

5

4

3

2

1

HT

+1.1VS

C1

C1

C2

1222

C2

1

1

2

2

SCD22U25V3KX-GP

SCD22U25V3KX-GP

R3

R3

1 2

0R0402-PAD-1-GP

0R0402-PAD-1-GP

1

1

2

D D

1222

LDT_PWRO K CPU_LDT_STOP#

LDT_RST#_CPU

LDT_REQ#

1

2 3

S1G3 & S1G4 not suppor t LDT_REQ#

RN141

RN141

SRN300J-3-GP

SRN300J-3-GP

300R2J-4-GP

300R2J-4-GP

DY

DY

+1.5VS

4

NB0CADOUT[15..0]10

R5

R5

12

NB0CADOUTJ [15..0]10

2

SCD22U25V3KX-GP

SCD22U25V3KX-GP

HDT_RST#6

1222

C C

B B

CPU_LDT_RST#16

CPU_PWRGD16

R2

300R2J-4-GPR2300R2J-4-GP

CPU_LDT_STOP#16

R6

R6

1 2

0R0402-PAD-1-GP

0R0402-PAD-1-GP

R7

R7

1 2

0R0402-PAD-1-GP

0R0402-PAD-1-GP

+1.5VS +1.8VS

12

LDT_RST#_CPU 11

LDT_PWRO K 37

1222

U155

U155

1

5

NC#1

VCC

2

A

4

GND3Y

74LVC1G07GW-G P

74LVC1G07GW-G P

12

R2283

R2283

12

2K2R2F-GP

2K2R2F-GP

C994

C994

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

LDT_STP#_CPU 11

NB0HTTCLKOUT110

NB0HTTCLKOUT010

NB0HTTCLKOUTJ110

NB0HTTCLKOUTJ010

NB0HTTCTLOUT110

NB0HTTCTLOUT010

NB0HTTCTLOUTJ110

NB0HTTCTLOUTJ010

C4

C3

12

12

SC180P50V2JN-1GPC4SC180P50V2JN-1GP

SC180P50V2JN-1GPC3SC180P50V2JN-1GP

LDT_RST#_CPU

LDT_PWRO K

NB0CADOUT15

NB0CADOUT14

NB0CADOUT13

NB0CADOUT11

NB0CADOUT10 CPUCADOUT8

NB0CADOUT9

NB0CADOUT8

NB0CADOUT7

NB0CADOUT6

NB0CADOUT5

NB0CADOUT4

NB0CADOUT3

NB0CADOUT2

NB0CADOUT1

NB0CADOUT0

NB0CADOUTJ15

NB0CADOUTJ14

NB0CADOUTJ13

NB0CADOUTJ12

NB0CADOUTJ11

NB0CADOUTJ10

NB0CADOUTJ9

NB0CADOUTJ8

NB0CADOUTJ7

NB0CADOUTJ6

NB0CADOUTJ5

NB0CADOUTJ4

NB0CADOUTJ3

NB0CADOUTJ2

NB0CADOUTJ1

NB0CADOUTJ0

NB0HTTCLKOUT1

NB0HTTCLKOUT0

NB0HTTCLKOUTJ1

NB0HTTCLKOUTJ0

1

NB0HTTCTLOUT1

NB0HTTCTLOUT0

NB0HTTCTLOUTJ1

NB0HTTCTLOUTJ0

CPU VLDT MAX 1.5A

CPU1A

CPU1A

D1

V_HT_A1

D2

V_HT_A2

D3

V_HT_A3

D4

V_HT_A4

RESET*

B7

PWROK

A7

LDTSTOP*

F10

N5

HT_RXD_P15

M3

HT_RXD_P14

L5

HT_RXD_P13

K3

HT_RXD_P12

H3

HT_RXD_P11

G5

HT_RXD_P10

F3

HT_RXD_P9

E5

HT_RXD_P8

N3

HT_RXD_P7

L1

HT_RXD_P6

L3

HT_RXD_P5

J1

HT_RXD_P4

G1

HT_RXD_P3

G3

HT_RXD_P2

E1

HT_RXD_P1

E3

HT_RXD_P0

P5

HT_RXD_N15

M4

HT_RXD_N14

M5

HT_RXD_N13

K4

HT_RXD_N12

H4

HT_RXD_N11

H5

HT_RXD_N10

F4

HT_RXD_N9

F5

HT_RXD_N8

N2

HT_RXD_N7

M1

HT_RXD_N6

L2

HT_RXD_N5

K1

HT_RXD_N4

H1

HT_RXD_N3

G2

HT_RXD_N2

F1

HT_RXD_N1

E2

HT_RXD_N0

J5

HT_RXCLK_P1

J3

HT_RXCLK_P0

K5

HT_RXCLK_N1

J2

HT_RXCLK_N0

P3

HT_RXCTL_P1

N1

HT_RXCTL_P0

P4

HT_RXCTL_N1

P1

HT_RXCTL_N0

SEC 1 OF 6

SEC 1 OF 6

LDT

LDT

V_HT_B1

V_HT_B2

V_HT_B3

V_HT_B4

LDTREQ*

HT_TXD_P15

HT_TXD_P14

HT_TXD_P13

HT_TXD_P12

HT_TXD_P11

HT_TXD_P10

HT_TXD_P9

HT_TXD_P8

HT_TXD_P7

HT_TXD_P6

HT_TXD_P5

HT_TXD_P4

HT_TXD_P3

HT_TXD_P2

HT_TXD_P1

HT_TXD_P0

HT_TXD_N15

HT_TXD_N14

HT_TXD_N13

HT_TXD_N12

HT_TXD_N11

HT_TXD_N10

HT_TXD_N9

HT_TXD_N8

HT_TXD_N7

HT_TXD_N6

HT_TXD_N5

HT_TXD_N4

HT_TXD_N3

HT_TXD_N2

HT_TXD_N1

HT_TXD_N0

HT_TXCLK_P1

HT_TXCLK_P0

HT_TXCLK_N1

HT_TXCLK_N0

HT_TXCTL_P1

HT_TXCTL_P0

HT_TXCTL_N1

HT_TXCTL_N0

HTREF1

HTREF0

LAYOUT: PLACE CLOSE TO CPU

C7

C7

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

LDT_REQ#

CPUCADOUT15

CPUCADOUT14

CPUCADOUT13

CPUCADOUT12

CPUCADOUT11

CPUCADOUT10NB0CADOUT12

CPUCADOUT9

CPUCADOUT7

CPUCADOUT6

CPUCADOUT5

CPUCADOUT4

CPUCADOUT3

CPUCADOUT2

CPUCADOUT1

CPUCADOUT0

CPUCADOUTJ15

CPUCADOUTJ14

CPUCADOUTJ13

CPUCADOUTJ12

CPUCADOUTJ11

CPUCADOUTJ10

CPUCADOUTJ9

CPUCADOUTJ8

CPUCADOUTJ7

CPUCADOUTJ6

CPUCADOUTJ5

CPUCADOUTJ4

CPUCADOUTJ3

CPUCADOUTJ2

CPUCADOUTJ1

CPUCADOUTJ0

CPUHTTCLKOUT1

CPUHTTCLKOUT0

CPUHTTCLKOUTJ1

CPUHTTCLKOUTJ0

CPUHTTCTLOUT1

CPUHTTCTLOUT0

CPUHTTCTLOUTJ1

CPUHTTCTLOUTJ0

ALONG HT POWER SHAPE

12

12

C5

SC10U6D3V5KX-1GPC5SC10U6D3V5KX-1GP

R10 44D2R2F-GPR10 44D2R2F-GP

1 2

1 2

R11

R11

44D2R2F-GP

44D2R2F-GP

PLACE WITHIN 1"

5MIL TRACE

10MIL SPACE

1028

C6

SC10U6D3V5KX-1GPC6SC10U6D3V5KX-1GP

CPUHTTCLKOUT1 10

CPUHTTCLKOUT0 10

CPUHTTCLKOUTJ1 10

CPUHTTCLKOUTJ0 10

CPUHTTCTLOUT1 10

CPUHTTCTLOUT0 10

CPUHTTCTLOUTJ1 10

CPUHTTCTLOUTJ0 10

+1.1VS

CPUCADOUT[15..0] 10

CPUCADOUTJ[15..0] 10

1207

12

DY

DY

AE2

AE3

AE4

AE5

C6

T4

V5

V4

Y5

AB5

AB4

AD5

AD4

T1

U2

V1

W2

AA2

AB1

AC2

AD1

T3

U5

V3

W5

AA5

AB3

AC5

AD3

R1

U3

U1

W3

AA3

AA1

AC3

AC1

Y4

Y1

Y3

W1

T5

R2

R5

R3

L0_REF1

P6

L0_REF0

R6

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

A3

A3

A3

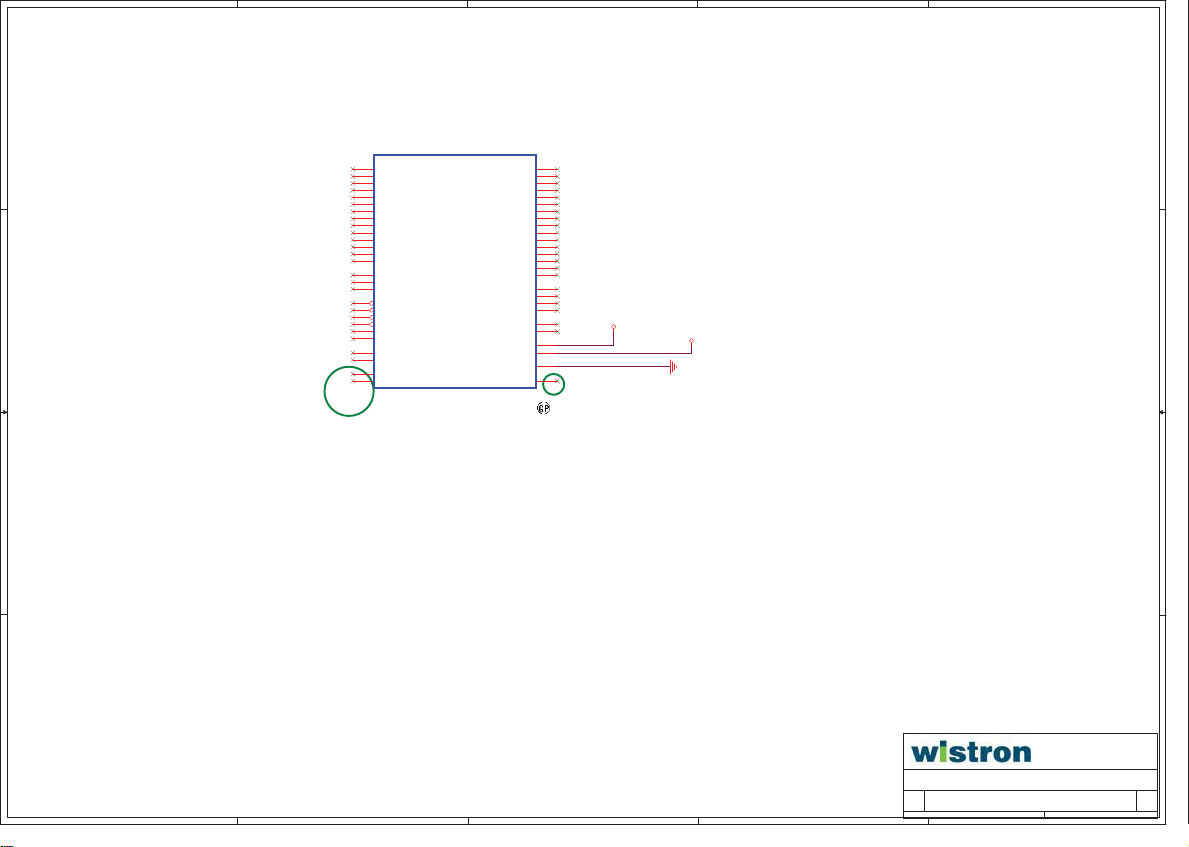

CPU(1/4) HT

CPU(1/4) HT

CPU(1/4) HT

PATEK

PATEK

PATEK

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

450Monday, March 15, 2010

450Monday, March 15, 2010

450Monday, March 15, 2010

1

of

of

of

-1

-1

-1

5

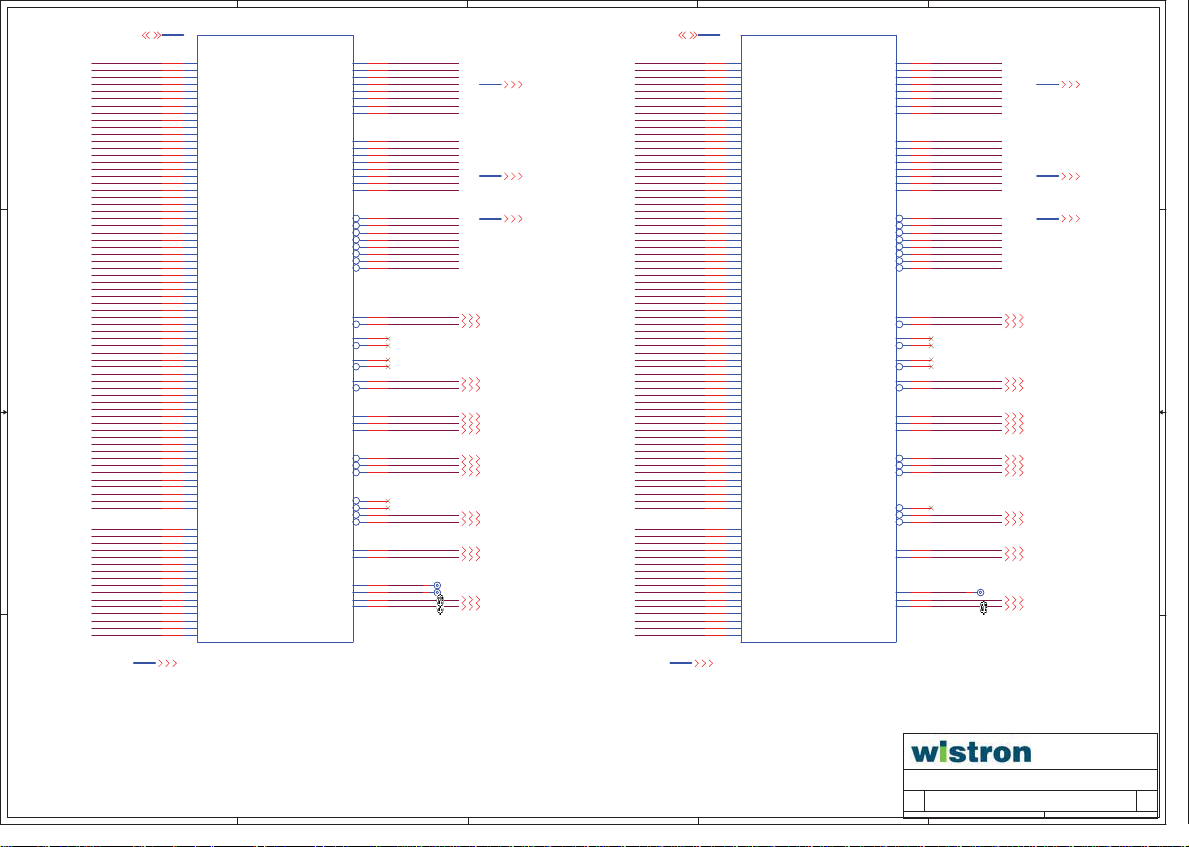

M_A_DQ[63..0]8

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

D D

C C

B B

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

AA12

AB12

AA14

AB14

AD13

AB13

AD15

AB15

AB17

AD17

AD19

AD21

AB21

AB18

AA18

AA20

AA22

AA21

AB22

AB24

CPU1C

CPU1C

SEC 3 OF 6

SEC 3 OF 6

MEMORY_A

MEMORY_A

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

W11

MA_DATA59

Y12

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

Y17

MA_DATA52

Y14

MA_DATA51

W14

MA_DATA50

W16

MA_DATA49

MA_DATA48

Y18

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

Y20

MA_DATA40

MA_DATA39

Y22

MA_DATA38

W21

MA_DATA37

W22

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

Y24

MA_DATA32

H22

MA_DATA31

H20

MA_DATA30

E22

MA_DATA29

E21

MA_DATA28

J19

MA_DATA27

H24

MA_DATA26

F22

MA_DATA25

F20

MA_DATA24

C23

MA_DATA23

B22

MA_DATA22

F18

MA_DATA21

E18

MA_DATA20

E20

MA_DATA19

D22

MA_DATA18

C19

MA_DATA17

G18

MA_DATA16

G17

MA_DATA15

C17

MA_DATA14

F14

MA_DATA13

E14

MA_DATA12

H17

MA_DATA11

E17

MA_DATA10

E15

MA_DATA9

H15

MA_DATA8

E13

MA_DATA7

C13

MA_DATA6

H12

MA_DATA5

H11

MA_DATA4

G14

MA_DATA3

H14

MA_DATA2

F12

MA_DATA1

G12

MA_DATA0

K19

MA_ADD15

K24

MA_ADD14

V24

MA_ADD13

K20

MA_ADD12

L22

MA_ADD11

R21

MA_ADD10

K22

MA_ADD9

L19

MA_ADD8

L21

MA_ADD7

M24

MA_ADD6

L20

MA_ADD5

M22

MA_ADD4

M19

MA_ADD3

N22

MA_ADD2

M20

MA_ADD1

N21

MA_ADD0

CLK5

CLK1

CLK7

CLK4

M_A_A[15..0] 8

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_P7

MA_DQS_P6

MA_DQS_P5

MA_DQS_P4

MA_DQS_P3

MA_DQS_P2

MA_DQS_P1

MA_DQS_P0

MA_DQS_N7

MA_DQS_N6

MA_DQS_N5

MA_DQS_N4

MA_DQS_N3

MA_DQS_N2

MA_DQS_N1

MA_DQS_N0

MA_CLK5_P

MA_CLK5_N

MA_CLK1_P

MA_CLK1_N

MA_CLK7_P

MA_CLK7_N

MA_CLK4_P

MA_CLK4_N

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS*

MA_CAS*

MA_WE*

MA1_CS1*

MA1_CS0*

MA0_CS1*

MA0_CS0*

MA_CKE1

MA_CKE0

MA1_ODT1

MA1_ODT0

MA0_ODT1

MA0_ODT0

4

M_A_DM7

Y13

M_A_DM6

AB16

M_A_DM5

Y19

M_A_DM4

AC24

M_A_DM3

F24

M_A_DM2

E19

M_A_DM1

C15

M_A_DM0

E12

M_A_DQS7

W12

M_A_DQS6

Y15

M_A_DQS5

AB19

M_A_DQS4

AD23

M_A_DQS3

G22

M_A_DQS2

C22

M_A_DQS1

G16

M_A_DQS0

G13

M_A_DQS#7

W13

M_A_DQS#6

W15

M_A_DQS#5

AB20

M_A_DQS#4

AC23

M_A_DQS#3

G21

M_A_DQS#2

C21

M_A_DQS#1

G15

M_A_DQS#0

H13

M_A_CLK_DDR1

N19

N20

E16

F16

Y16

AA16

P19

P20

J21

R23

R20

R19

T22

T24

V20

U20

U19

T20

J20

J22

V19

U21

V22

T19

M_A_CLK_DDR1#

M_A_CLK_DDR2

M_A_CLK_DDR2#

MA1_ODT1

MA1_ODT0

M_A_ODT1

M_A_ODT0

M_A_BS#2

M_A_BS#1

M_A_BS#0

M_A_RAS#

M_A_CAS#

M_A_WE#

M_A_CS1#

M_A_CS0#

M_A_CKE1

M_A_CKE0

1

1

M_A_CLK_DDR1 8

M_A_CLK_DDR1# 8

M_A_CLK_DDR2 8

M_A_CLK_DDR2# 8

M_A_BS#2 8

M_A_BS#1 8

M_A_BS#0 8

M_A_RAS# 8

M_A_CAS# 8

M_A_WE# 8 M_B_WE# 8

M_A_CS1# 8

M_A_CS0# 8

M_A_CKE1 8

M_A_CKE0 8

TP1 TPAD14-GPTP1 TPAD14-GP

TP2 TPAD14-GPTP2 TPAD14-GP

M_A_ODT1 8

M_A_ODT0 8

M_A_DM[7..0] 8

M_A_DQS[7..0] 8

M_A_DQS#[7..0] 8

3

M_B_DQ[63..0]8

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

Y11

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

G24

MB_DATA31

G23

MB_DATA30

D26

MB_DATA29

C26

MB_DATA28

G26

MB_DATA27

G25

MB_DATA26

E24

MB_DATA25

E23

MB_DATA24

C24

MB_DATA23

B24

MB_DATA22

C20

MB_DATA21

B20

MB_DATA20

C25

MB_DATA19

D24

MB_DATA18

A21

MB_DATA17

D20

MB_DATA16

D18

MB_DATA15

C18

MB_DATA14

D14

MB_DATA13

C14

MB_DATA12

A20

MB_DATA11

A19

MB_DATA10

A16

MB_DATA9

A15

MB_DATA8

A13

MB_DATA7

D12

MB_DATA6

E11

MB_DATA5

G11

MB_DATA4

B14

MB_DATA3

A14

MB_DATA2

A11

MB_DATA1

C11

MB_DATA0

J24

MB_ADD15

J23

MB_ADD14

W24

MB_ADD13

L25

MB_ADD12

L26

MB_ADD11

T26

MB_ADD10

K26

MB_ADD9

M26

MB_ADD8

L24

MB_ADD7

N25

MB_ADD6

L23

MB_ADD5

N26

MB_ADD4

N23

MB_ADD3

P26

MB_ADD2

N24

MB_ADD1

P24

MB_ADD0

CPU1D

CPU1D

2

SEC 4 OF 6

SEC 4 OF 6

MEMORY_B

MEMORY_B

CLK7

CLK4

1

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_P7

MB_DQS_P6

MB_DQS_P5

MB_DQS_P4

MB_DQS_P3

MB_DQS_P2

MB_DQS_P1

MB_DQS_P0

MB_DQS_N7

MB_DQS_N6

MB_DQS_N5

MB_DQS_N4

MB_DQS_N3

MB_DQS_N2

MB_DQS_N1

MB_DQS_N0

MB_CLK5_P

CLK5

MB_CLK5_N

MB_CLK1_P

CLK1

MB_CLK1_N

MB_CLK7_P

MB_CLK7_N

MB_CLK4_P

MB_CLK4_N

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS*

MB_CAS*

MB_WE*

MB1_CS0*

MB0_CS1*

MB0_CS0*

MB_CKE1

MB_CKE0

MB1_ODT0

MB0_ODT1

MB0_ODT0

AD12

AC16

AE22

AB26

E25

A22

B16

A12

AF12

AE16

AF21

AC25

F26

A24

D16

C12

AE12

AD16

AF22

AC26

E26

A23

C16

B12

P22

R22

A17

A18

AF18

AF17

R26

R25

J26

U26

R24

U25

U24

U23

U22

W25

V26

H26

J25

Y26

W23

W26

M_B_DM7

M_B_DM6

M_B_DM5

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

M_B_DQS7

M_B_DQS6M_B_DQ51

M_B_DQS5

M_B_DQS4

M_B_DQS3

M_B_DQS2

M_B_DQS1

M_B_DQS0

M_B_DQS#7

M_B_DQS#6

M_B_DQS#5

M_B_DQS#4

M_B_DQS#3

M_B_DQS#2

M_B_DQS#1

M_B_DQS#0

M_B_CLK_DDR1

M_B_CLK_DDR1#

M_B_CLK_DDR2

M_B_CLK_DDR2#

MB1_ODT0

M_B_ODT1

M_B_ODT0

M_B_BS#2

M_B_BS#1

M_B_BS#0

M_B_RAS#

M_B_CAS#

M_B_WE#

M_B_CS1#

M_B_CS0#

M_B_CKE1

M_B_CKE0

1

TP3 TPAD14-GPTP3 TPAD14-GP

M_B_CLK_DDR1 8

M_B_CLK_DDR1# 8

M_B_CLK_DDR2 8

M_B_CLK_DDR2# 8

M_B_BS#2 8

M_B_BS#1 8

M_B_BS#0 8

M_B_RAS# 8

M_B_CAS# 8

M_B_CS1# 8

M_B_CS0# 8

M_B_CKE1 8

M_B_CKE0 8

M_B_ODT1 8

M_B_ODT0 8

M_B_DM[7..0] 8

M_B_DQS[7..0] 8

M_B_DQS#[7..0] 8

M_B_A[15..0] 8

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

CPU(2/4) DDR III

CPU(2/4) DDR III

CPU(2/4) DDR III

PATEK

PATEK

PATEK

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

550Monday, March 15, 2010

550Monday, March 15, 2010

550Monday, March 15, 2010

1

of

of

of

-1

-1

-1

5

169R2F-GP

169R2F-GP

+1.1VS

R58

R58

10KR2J-3-GP

10KR2J-3-GP

1207

R21

R21

R32

R32

300R2J-4-GP

300R2J-4-GP

LDT_RST#_HDT

+3VALW

12

DY

DY

CH3904GP-GP-U

CH3904GP-GP-U

+2.5VS_VDDA+2.5VS_LDO_CPU

12

C9

ROUTE AS DIFF PAIR

SC4D7U25V5KX-GPC9SC4D7U25V5KX-GP

CPU_VDD1_RU N_FB_H37

CPU_VDD1_RU N_FB_L37

CPU_VDD0_RU N_FB_H37

CPU_VDD0_RU N_FB_L37

R18

R18

R19

R19

CLKCPU_IN

12

CLKCPU#_IN

1224

+1.5V

1 2

DY

DY

+1.5V

4

RN105

RN105

SRN1KJ-7-GP

SRN1KJ-7-GP

1

2 3

CPU_ALERT#_U

CBE

Q18

Q18

1012

SC3300P50V2KX-1GP

SC3300P50V2KX-1GP

CPU_ALERT#_L

L18

L18

1 2

PBY160808T-600Y-N-GP

PBY160808T-600Y-N-GP

12

C8

C8

SC180P50V2JN-1GP

SC180P50V2JN-1GP

D D

CPU_VDDNB_RUN_FB_H37

CPU_VDDNB_RUN_FB_L37

CPU_CLK16,21

C C

CPU_CLK#16,21

LAYOUT: PLACE 169 OHM NO MORE THAN 500 MILS FROM CPU

HDT Connectors

+1.5V

12

R33

R33

300R2J-4-GP

300R2J-4-GP

DBREQJ

DBRDY

TCK

TMS

B B

TDI

TRST_L

TDO

A A

1 2

1 2

12

DY

DY

C18

C18

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

HDT1

HDT1

1

3

5

7

9

11

13

15

17

19

21

23

SMC-CONN26A-FP

SMC-CONN26A-FP

20.F0357.025

20.F0357.025

DY

DY

THERM_SCI#19,24

5

C13

C13

SC3900P50V2KX-2GP

SC3900P50V2KX-2GP

C14

C14

SC3900P50V2KX-2GP

SC3900P50V2KX-2GP

2

4

6

8

10

12

14

16

18

20

22

24

26

12

C10

C10

1 2

0R0402-PAD

0R0402-PAD

1 2

0R0402-PAD

0R0402-PAD

1222

4

TP121TPAD14-GP TP121T PAD 14-G P

TP122TPAD14-GP TP122T PAD 14-G P

TP123TPAD14-GP TP123T PAD 14-G P

TP124TPAD14-GP TP124T PAD 14-G P

1 2

1 2

TP5TPAD14-GP TP5TPAD14-GP

TP6TPAD14-GP TP6TPAD14-GP

TP7TPAD14-GP TP7TPAD14-GP

TP8TPAD14-GP TP8TPAD14-GP

0R0402-PAD-1-GP

0R0402-PAD-1-GP

TP9TPAD14-GP TP9TPAD14-GP

TP10TPAD14-GP TP10TPAD 14-GP

TP11TPAD14-GP TP11TPAD 14-GP

M_A_RST#8

M_B_RST#8

4

1

1

C11

C11

SCD22U25V3KX-GP

SCD22U25V3KX-GP

2

2

CPU_NB_FB_1

CPU_NB_FB_0

DBRDY

TMS

1

TCK

1

TRST_L

1

TDI

1

R26510R2F-L-GP R26510R2F-L-GP

R28510R2F-L-GP R28510R2F-L-GP

1

1

1

1

1 2

R34

R34

1

1

1

TP4TPAD14-GP TP4TPAD14-GP

CPU_TEST8

CPU_TEST7

CPU_TEST6

TP56

1

CPU_TEST25

CPU_TEST25#

CPU_TEST19

CPU_TEST18

CPU_TEST12

CPU_TEST17

CPU_TEST16

CPU_TEST15

CPU_TEST14

CPU_TEST10

CPU_TEST9

NC

NC

3

+1.5V

0930

RN104

RN104

SRN1KJ-7-GP

THERMTRIP*

PROCHOT*

ALERT*

MEMHOT*

THERMDC

THERMDA

VTT_SENSE

M_VREF

M_ZN

DBREQ*

TEST29

TEST29*

TEST28

TEST28*

TEST27

TEST24

TEST23

TEST22

TEST21

TEST20

SID

SIC

SVD

SVC

M_P

TDO

SRN1KJ-7-GP

AF6

AC7

AE6

AA8

W7

W8

AF5

AF4

A4

A6

Y10

W17

AE10

AF10

E10

AE9

C9

C8

J7

H8

AF8

AE7

AD7

AE8

AB8

AF7

CPU_MEMHOT#_L

CPU_VDDR_SENSE

MEMZN

MEMZP

TP_FBCLKOUT

TP_FBCLKOUT#

CPU_TEST27

CPU_TEST24

CPU_TEST23

CPU_TEST22

CPU_TEST21

CPU_TEST20

CPU1B

CPU1B

SEC 2 OF 6

SEC 2 OF 6

MISC

MISC

VDDA

F8

VDDA

F9

VDD1_FB

Y6

VDD1_FB*

AB6

VDD0_FB

F6

VDD0_FB*

E6

VDDNB_FB

H6

VDDNB_FB*

G6

VDDIO_FB

W9

VDDIO_FB*

Y9

CLKIN

A9

CLKIN*

A8

DBRDY

G10

TMS

AA9

TCK

AC9

TRST*

AD9

TDI

AF9

TEST25

E9

TEST25*

E8

TEST19

G9

TEST18

H10

TEST12

AC8

TEST17

D7

TEST16

E7

TEST15

F7

TEST14

C7

TEST10

K8

TEST9

C2

TEST8

C4

TEST7

C3

TEST6

AA6

NC

W18

NC

M11

RSVD

B3

RSVD

H19

RSVD

H18

RSVD

D5

RSVD

AA7

RSVD

H16

RSVD

B18

RSVD

B5

RSVD

C5

RSVD

A5

RSVD

C1

RSVD

A3

+1.5V

+1.5V

12

4

R55

R55

DY

DY

1

2 3

1KR2J-1-GP

1KR2J-1-GP

1

R24

R24

12

39D2R2F-L-GP

39D2R2F-L-GP

R27

R27

39D2R2F-L-GP

39D2R2F-L-GP

12

DBREQJ

TDO

1 2

R35 80D6R2F-L-GPR35 80D6R2F-L-GP

DY

DY

4

1

TP14 TPAD14-GPTP14 TPAD14-GP

1

1 2

1222

RN142

CPU_TEST18

CPU_TEST19

CPU_TEST22

CPU_TEST24

CPU_TEST27

CPU_TEST12

CPU_TEST21

CPU_TEST20

RN142

1

2

3

4 5

SRN1KJ-4-GP

SRN1KJ-4-GP

RN143

RN143

1

2

3

4 5

SRN1KJ-4-GP

SRN1KJ-4-GP

3

8

7

6

8

+1.5V

7

6

RN107

RN107

SRN1KJ-7-GP

SRN1KJ-7-GP

2 3

CPU_SID

CPU_SIC

TP125 TPAD 14- GPTP125 TPAD14-GP

R39

R39

2

300R2J-4-GP

300R2J-4-GP

CPU_THERMDC

CPU_THERMDA

CPU_SVD 37

CPU_SVC 37

12

C17

C17

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

1KR2J-1-GP

1KR2J-1-GP

2

R2315

R2315

R2316

R2316

12

12

1KR2J-1-GP

1KR2J-1-GP

CPU_PROCHOT#_CPU

CPU_ALERT#_L

CPU_MEMHOT#_L 8

R45 0R0402-PAD-1-GPR45 0R0402-PAD-1-GP

1 2

1 2

R43 0R0402-PAD-1-GPR43 0R0402-PAD-1-GP

+1.5V

1224

HDT_RST#4

1

+1.5V

4

RN61

RN61

SRN10KJ-5-GP

SRN10KJ-5-GP

1

2 3

THERMTRIP#

1

1

TP15 TPAD14-GPTP15 TPAD14-GP

TP16 TPAD14-GPTP16 TPAD14-GP

CPU_SID_SB700 19

CPU_SIC_SB700 19

PROCHOT#_CPU_B

CBE

Q21

Q21

CH3904GP-GP-U

CH3904GP-GP-U

1012

THERMTRIP#_B

Q19

Q19

CH3904GP-GP-U

CH3904GP-GP-U

CBE

1222

VREF_DDR_CLAW

12

C12

C12

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

R25 1KR2F-3-GPR25 1KR2F-3-GP

1 2

R23 1KR2F-3-GPR23 1KR2F-3-GP

1 2

12

12

C15

C15

C16

C16

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

/$<287/RFDWHFORVHWR&38

M_VREF

SHORTER THAN 6 INCHES

15MIL TRACE, 20 MIL SPACE

1111

+1.5VS

12

R38

R38

+3VS

DY

DY

1012

CH3904GP-GP-U

CH3904GP-GP-U

DY

DY

1 2

R56 0R2J-2-GP

R56 0R2J-2-GP

DY

DY

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

A3

A3

A3

CPU(3/4) CONTROL

CPU(3/4) CONTROL

CPU(3/4) CONTROL

Q18_B

CBE

Q2

Q2

PATEK

PATEK

PATEK

12

4K7R2J-2-GP

4K7R2J-2-GP

DY

DY

1

CPU_THERMTRIP# 19,24

CPU_PROCHOT# 24

CPU_PROCHOT#_CPU 16,48

+1.5V

R46

R46

4K7R2J-2-GP

4K7R2J-2-GP

LDT_RST#_HDT

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

650Monday, March 15, 2010

650Monday, March 15, 2010

650Monday, March 15, 2010

of

of

of

-1

-1

-1

5

CPU1F

CPU1F

SEC 6 OF 6

SEC 6 OF 6

GROUND

D D

AA4

AA11

AA13

AA15

AA17

AA19

AB2

AB7

AB9

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

C C

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

F11

F13

F15

F17

F19

B B

F21

F23

F25

H21

H23

GROUND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B4

VSS

B6

VSS

B8

VSS

B9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D6

VSS

D8

VSS

D9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E4

VSS

F2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H7

VSS

H9

VSS

VSS

VSS

J4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

+VCC_CORE +1.5V

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M17

N4

N6

N8

N10

+VCC_CORE

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

AC6

CPU1E

CPU1E

N9

VDD0

N7

VDD0

N11

VDD0

M8

VDD0

M6

VDD0

M2

VDD0

M10

VDD0

L9

VDD0

L7

VDD0

L4

VDD0

L15

VDD0

L13

VDD0

L11

VDD0

VDD0

K6

K14

VDD0

K12

VDD0

K10

VDD0

J9

VDD0

J15

VDD0

J13

VDD0

J11

VDD0

H2

VDD0

G4

VDD0

Y2

VDD1

W4

VDD1

V8

VDD1

V6

VDD1

V14

VDD1

V12

VDD1

V10

VDD1

U9

VDD1

U7

VDD1

U15

VDD1

U13

VDD1

U11

VDD1

T8

VDD1

T6

VDD1

T2

VDD1

T14

VDD1

T12

VDD1

T10

VDD1

R9

VDD1

R7

VDD1

R4

VDD1

R11

VDD1

P8

VDD1

P10

VDD1

AD2

VDD1

AC4

VDD1

SEC 5 OF 6

SEC 5 OF 6

POWER

POWER

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

4

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

+1.5V@9AVCORE 36A

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

VDDR 1.5A

+1.05VS

A10

AA10

AB10

AC10

AD10

B10

C10

D10

W10

+VDDNB

V16

T16

P16

M16

K16

VDDNB CORE

0.9V 4A

3

LAYOUT: PLACE UNDER CPU ON BACK

+VCC_CORE

22uF x 4, 0.22uF x 1, 0.01uF x 1, 180pF x1

12

C19

C19

RF

RF

+VCC_CORE

22uF x 4, 0.22uF x 1, 0.01uF x 1, 180pF x1

12

C34

C34

+VDDNB

22uF x 3

12

C49

C49

DY

DY

+1.5V

22u x 2 0.22u X 2 180pF x1

12

C60

C60

DY

DY

12

12

C21

C21

C20

C20

DY

DY

DY

DY

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C35

C35

C36

C36

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C50

C50

C51

C51

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C62

C62

12

1

1

C61

C61

2

2

DY

DY

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C23

C23

12

1

1

C22

C22

RF

RF

2

2

12231223

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC68P50V2JN-1GP

SC68P50V2JN-1GP

C38

C38

12

1

1

C37

C37

2

2

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C68

C68

C66

C66

12

1

1

2

2

DY

DY

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

2

1

CPU MEMORY VTT

1028

C24

C24

C25

C25

12

12

DY

DY

DY

DY

SC180P50V2JN-1GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

DY

DY

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SC180P50V2JN-1GP

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

1028

C39

C39

C40

C40

12

12

DY

DY

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

LAYOUT: PLACE CLOSE T O CP U so cket

+1.05VS

+1.05VS

DY

DY

C27

C27

C26

C26

1

1

1

1

2

2

2

2

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

1n x 4

12

12

C42

C42

C41

C41

1028

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1028

C29

C29

C28

C28

1

1

2

2

DY

DY

12

C43

C43

12

1

1

C30

C30

2

2

DY

DY

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

C45

C45

12

12

C44

C44

DY

DY

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1207

4.7u x 40.22u X 4

12

C31

C31

DY

DY

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

180p x 4

C46

C46

12

DY

DY

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

1028

12

12

C33

C33

C32

C32

DY

DY

DY

DY

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

DY

DY

C48

C48

C47

C47

12

12

DY

DY

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

CPU VDDIO

LAYOUT: PLACE CLOSE TO CPU BETWEEN CPU AND M EMORY

+1.5V

C53

C53

C54

C54

C52

C52

1

1

1

1

1

1

2

2

2

2

2

2

DY

DY

DY

DY

DY

DY

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD22U25V3KX-GP

+1.5V

C73

C73

12

0.1u X 1

C55

C55

C56

C56

12

1

1

2

2

DY

DY

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

SCD22U25V3KX-GP

C58

C58

C57

C57

12

12

SC180P50V2JN-1GP

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

SC180P50V2JN-1GP

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

4.7u x 40.22u X 4 180p x 20.01u X 1

C59

C59

12

12

12

C63

C63

DY

DY

DY

DY

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

1207

12

12

C67

C65

C65

C67

C64

C64

DY

DY

DY

DY

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

SC4D7U25V5KX-GP

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

A3

A3

A3

CPU(4/4) POWER

CPU(4/4) POWER

CPU(4/4) POWER

PATEK

PATEK

PATEK

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

750Thursday, January 21, 2010

750Thursday, January 21, 2010

750Thursday, January 21, 2010

1

of

of

of

-1

-1

-1

5

DIMM1

M_B_A[15..0]5

D D

C C

B B

A A

M_B_BS#25

M_B_BS#05

M_B_BS#15 M_A_BS#25

M_B_DQ[63..0]5

M_B_DQS#[7..0]5

M_B_DQS[7..0]5

M_B_ODT05

M_B_ODT15

DDR_VREF_S3

DDR_VREF_DQ_S3

C84

C84

12

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

12

5

M_B_RST#6

C85

C85

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

MEM_VTT

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

DIMM1

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/BA2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_DQ

30

RESET#

203

VTT1

204

VTT2

DDR3-204P-21-GP

DDR3-204P-21-GP

62.10017.J71

62.10017.J71

+ PP

EVENT#

VDDSPD

NC#/TEST

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

NP1

NP1

NP2

NP2

110

RAS#

113

WE#

115

CAS#

114

CS0#

121

CS1#

73

CKE0

74

CKE1

101

CK0

103

CK0#

102

CK1

104

CK1#

M_B_DM0

11

DM0

M_B_DM1

28

DM1

M_B_DM2

46

DM2

M_B_DM3

63

DM3

M_B_DM4

136

DM4

M_B_DM5

153

DM5

M_B_DM6

170

DM6

M_B_DM7

187

DM7

200

SDA

202

SCL

198

199

DIMM2_SA0

197

SA0

201

SA1

77

NC#1

122

NC#2

DIMM_TEST1

125

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

105

106

111

112

117

118

123

124

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

44

VSS

48

VSS

49

VSS

54

VSS

55

VSS

60

VSS

61

VSS

65

VSS

66

VSS

71

VSS

72

VSS

127

VSS

128

VSS

133

VSS

134

VSS

138

VSS

139

VSS

144

VSS

145

VSS

150

VSS

151

VSS

155

VSS

156

VSS

161

VSS

162

VSS

167

VSS

168

VSS

172

VSS

173

VSS

178

VSS

179

VSS

184

VSS

185

VSS

189

VSS

190

VSS

195

VSS

196

VSS

205

VSS

206

VSS

M_B_EVENT#

M_B_RAS# 5

M_B_WE# 5

M_B_CAS# 5

M_B_CS0# 5

M_B_CS1# 5

M_B_CKE0 5

M_B_CKE1 5

M_B_CLK_DDR1 5

M_B_CLK_DDR1# 5

M_B_CLK_DDR2 5

M_B_CLK_DDR2# 5

SB_SMB_DAT0 19,21,24,28

SB_SMB_CLK0 19,21,24,28

1 2

4K7R2J-2-GP

4K7R2J-2-GP

TP12 TPAD14-GPTP12 TPAD14-GP

1

+1.5V

4

M_B_DM[7..0] 5

R108

R108

CPU_MEMHOT#_L6

+0.75V

1214

4

3

DIMM2

M_A_A[15 ..0]5

M_A_BS#05

M_A_BS#15

M_A_DQ[63..0]5

12

1222

R61

R61

1 2

0R0603-PAD-1-GP

0R0603-PAD-1-GP

+3VS

C79

C79

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

Check if SB need

Memhot event

1 2

DY

DY

R60 0R2J-2-GP

R60 0R2J-2-GP

1 2

R107 0R2J-2-GP

R107 0R2J-2-GP

MEM_VTT

DY

DY

M_A_EVENT#

M_B_EVENT#

DDR_VREF_S3

DDR_VREF_DQ_S3

C86

C86

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

M_A_DQS#0

M_A_ODT05

M_A_ODT15

C87

C87

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_RST#6

MEM_VTT

M_A_DQS#[7..0]5

M_A_DQS[7..0]5

12

12

+3VS

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

DIMM2

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/BA2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_DQ

30

RESET#

203

VTT1

204

VTT2

DDR3-204P-20-GP

DDR3-204P-20-GP

62.10017.J61

62.10017.J61

EVENT#

VDDSPD

NC#/TEST

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

NP1

NP2

RAS#

WE#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0

CK0#

CK1

CK1#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

SDA

SCL

SA0

SA1

NC#1

NC#2

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

+ PP

1224 1224

+1.5V

12

12

12

EC175

EC175

EC174

EC174

EC170

EC170

RF

RF

RF

RF

1223

RF

RF

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SC68P50V2JN-1GP

SC68P50V2JN-1GP

12

EC177

EC177

RF

RF

SC68P50V2JN-1GP

SC68P50V2JN-1GP

1223 1223

12

12

EC178

EC178

EC182

EC182

RF

RF

RF

RF

SC68P50V2JN-1GP

SC68P50V2JN-1GP

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

12

EC179

EC179

RF

RF

DY

DY

SC18P50V2JN-1-GP

SC18P50V2JN-1-GP

SC18P50V2JN-1-GP

SC18P50V2JN-1-GP

12

EC180

EC180

12

EC183

EC183

RF

RF

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

3

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

2

NP1

NP2

110

113

115

114

121

73

74

101

103

102

104

M_A_DM0

11

M_A_DM1

28

M_A_DM2

46

M_A_DM3

63

M_A_DM4

136

M_A_DM5

153

M_A_DM6

170

M_A_DM7

187

200

202

198

199

197

201

77

122

DIMM_TEST2

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

SB_SMB_DAT0

SB_SMB_CLK0

M_A_EVENT#

TP13 TPAD14-GPTP13 TPAD14-GP

1

+1.5V

2

M_A_RAS# 5

M_A_WE# 5

M_A_CAS# 5

M_A_CS0# 5

M_A_CS1# 5

M_A_CKE0 5

M_A_CKE1 5

M_A_CLK_DDR1 5

M_A_CLK_DDR1# 5

M_A_CLK_DDR2 5

M_A_CLK_DDR2# 5

M_A_DM[7..0] 5

+3VS

12

C80

C80

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

DDR_VREF_CA

+1.5V

R113

R113

1KR2F-3-GP

1KR2F-3-GP

1 2

R112

R112

1 2

1KR2F-3-GP

1KR2F-3-GP

Change to signle R

/$<287/RFDWHFORVHWR',00

090803-1

DDR_VREF_DQ

+1.5V

R114

R114

1KR2F-3-GP

1KR2F-3-GP

1 2

R115

R115

1 2

1KR2F-3-GP

1KR2F-3-GP

Change to signle R

/$<287/RFDWHFORVHWR',00

C81

C81

C117

C117

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

12

12

A2

A2

A2

DDR_VREF_S3

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

C82

C82

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

DDR_VREF_DQ_S3

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

C118

C118

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

DDR3-SOCKET

DDR3-SOCKET

DDR3-SOCKET

1

12

12

PATEK

PATEK

PATEK

1

C83

C83

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

C116

C116

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

Wistron Incorporate d

Wistron Incorporate d

Wistron Incorporate d

21F, 88, Hsin T ai Wu Rd

21F, 88, Hsin T ai Wu Rd

21F, 88, Hsin T ai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

850Monday, March 15, 2010

850Monday, March 15, 2010

850Monday, March 15, 2010

of

of

of

-1

-1

-1

5

4

3

2

1

MEM_VTT

12

C88

C88

D D

SCD1U16V2ZY-2GP

DE-COUPLING FOR CHANNEL A SODIMM

1223 1223

+1.5V

12

DY

DY

C C

12

12

DY

DY

C91

C91

C90

C90

RF

RF

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SC68P50V2JN-1GP

SC68P50V2JN-1GP

1223 1223

12

12

DY

DY

C94

C94

C92

C92

C93

C93

RF

RF

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DE-COUPLING FOR CHANNEL A SODIMM (ONE CAP PER POWER PIN)

+1.5V

0114

12

DY

DY

TC1

TC1

ST330U2VDM-5-GP

ST330U2VDM-5-GP

B B

SCD1U16V2ZY-2GP

1223 1028

12

12

RF

RF

SC18P50V2JN-1-GP

SC18P50V2JN-1-GP

12

12

DY

DY

C97

C97

C95

C95

C96

C96

RF

RF

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C98

C98

SC18P50V2JN-1-GP

SC18P50V2JN-1-GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

12

C101

C101

C100

C100

C99

C99

RF

RF

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SC18P50V2JN-1-GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SC18P50V2JN-1-GP

+1.5V

12

DY

DY

C102

C102

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DE-COUPLING FOR CHANNEL B SODIMM (ONE CAP PER POWER PIN)

MEM_VTT

12

C114

C114

SC4D7U6D3V3KX-G P

SC4D7U6D3V3KX-G P

DE-COUPLING FOR CHANNEL B SODIMM

12

12

RF

RF

C103

C103

C104

C104

RF

RF

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SC68P50V2JN-1GP

SC68P50V2JN-1GP

MEM_VTT

12

C89

C89

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

1223

12

12

12

DY

DY

C219

C219

C115

C115

RF

RF

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C232

C232

C108

C108

RF

RF

RF

RF

SC68P50V2JN-1GP

SC68P50V2JN-1GP

SC68P50V2JN-1GP

SC68P50V2JN-1GP

SC18P50V2JN-1-GP

SC18P50V2JN-1-GP

MEM_VTT

12

C109

C109

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C233

C233

SC4D7U6D3V3KX-G P

SC4D7U6D3V3KX-G P

12

12

C110

C110

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

12

C113

C111

C111

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C113

C112

C112

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

DDR3-RESISTOR/CAP

DDR3-RESISTOR/CAP

DDR3-RESISTOR/CAP

A3

A3

A3

PATEK

PATEK

PATEK

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

950Thursday, January 21, 2010

950Thursday, January 21, 2010

950Thursday, January 21, 2010

1

of

of

of

-1

-1

-1

5

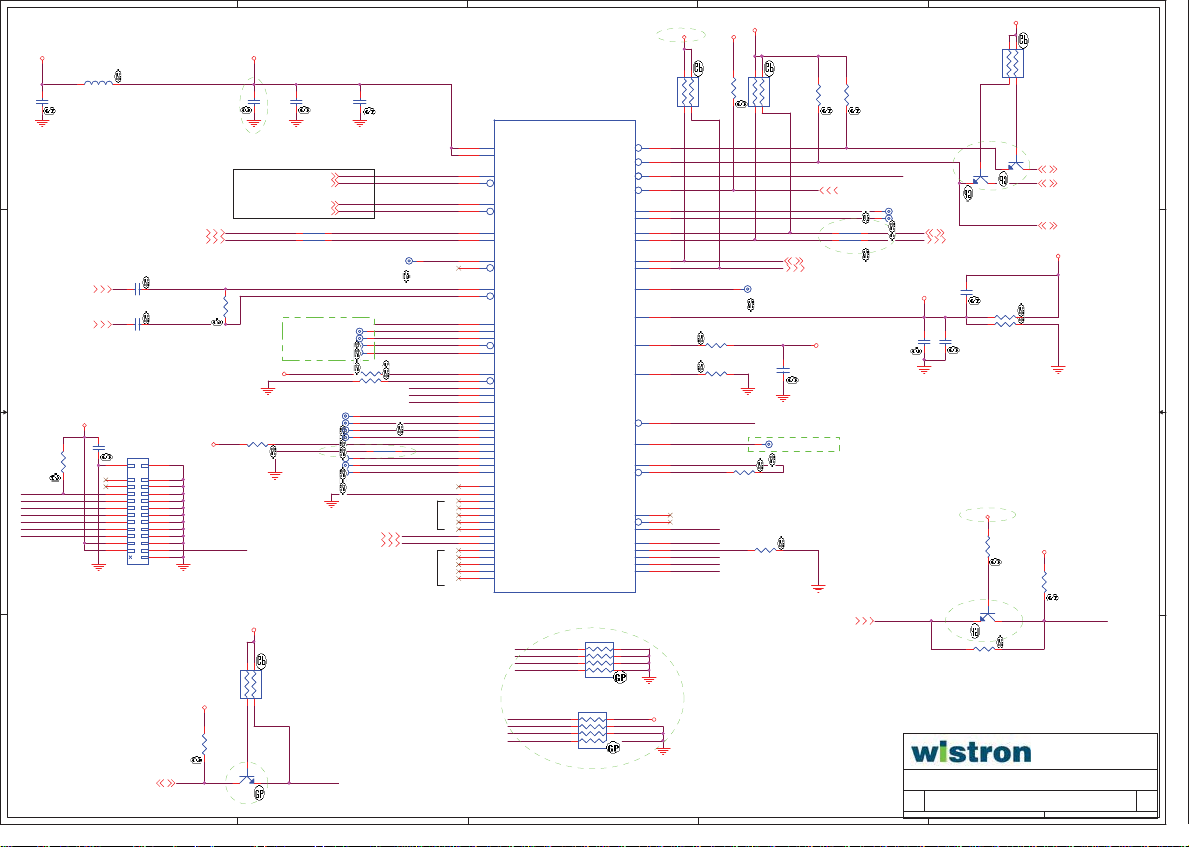

CPUCADOUT0

CPUCADOUTJ0

SSID = N.B

D D

CPUCADOUT[15..0]4

CPUCADOU TJ[15..0]4

C C

B B

NEW CARD

A A

A-LINK

5

CPUCADOUT1

CPUCADOUTJ1

CPUCADOUT2

CPUCADOUTJ2

CPUCADOUT3

CPUCADOUTJ3

CPUCADOUT4

CPUCADOUTJ4

CPUCADOUT5

CPUCADOUTJ5

CPUCADOUT6

CPUCADOUTJ6

CPUCADOUT7

CPUCADOUTJ7

CPUCADOUT8

CPUCADOUTJ8

CPUCADOUT9

CPUCADOUTJ9

CPUCADOUT10

CPUCADOUTJ10

CPUCADOUT11

CPUCADOUTJ11

CPUCADOUT12

CPUCADOUTJ12

CPUCADOUT13

CPUCADOUTJ13

CPUCADOUT14

CPUCADOUTJ14

CPUCADOUT15

CPUCADOUTJ15

CPUHTTCLKOUT04

CPUHTTCLKOUTJ04

CPUHTTCLKOUT14

CPUHTTCLKOUTJ14

CPUHTTCTLOUT04

CPUHTTCTLOUTJ04

CPUHTTCTLOUT14

CPUHTTCTLOUTJ14

R62

R62

1 2

301R2F-GP

301R2F-GP

Place < 100mils from pin C23 and A24

PCIE_RXP029

PCIE_RXN029

PCIE_RXP327

PCIE_RXN327

PCIE_RXP428

PCIE_RXN428

ALINK_NBRX_SBTX_P016

ALINK_NBRX_SBTX_N016

ALINK_NBRX_SBTX_P116

ALINK_NBRX_SBTX_N116

ALINK_NBRX_SBTX_P216

ALINK_NBRX_SBTX_N216

ALINK_NBRX_SBTX_P316

ALINK_NBRX_SBTX_N316

4

U1001A

U1001A

Y25

HT_RXCAD0P

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

AC24

AC25

AB25

AB24

AA24

AA25

Y22

Y23

W21

W20

V21

V20

U20

U21

U19

U18

T22

T23

AB23

AA22

M22

M23

R21

R20

HT_RXCALP HT_TXCALP

C23

HT_RXCALN

A24

D4

C4

A3

B3

C2

C1

E5

F5

G5

G6

H5

H6

J6

J5

J7

J8

L5

L6

M8

L8

P7

M7

P5

M5

R8

P8

R6

R5

P4

P3

T4

T3

AE3

AD4

AE2

AD3

AD1

AD2

V5

W6

U5

U6

U8

U7

AA8

Y8

AA7

Y7

AA5

AA6

W5

Y5

4

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS880M-GP

RS880M-GP

U1001B

U1001B

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

GPP_RX4P

GPP_RX4N

GPP_RX5P

GPP_RX5N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

RS880M-GP

RS880M-GP

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

PART 2 OF 6

PART 2 OF 6

PCIE I/F GFX

PCIE I/F GFX

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

PCE_CALRP

PCE_CALRN

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

F21

G21

G20

H21

J20

J21

J18

K17

L19

J19

M19

L18

M21

P21

P18

M18

H24

H25

L21

L20

M24

M25

P19

R18

B24

HT_TXCALN

B25

Place < 100mils from pin B25 and B24

HDMI_TXD2_R

A5

HDMI_TXD2#_R

B5

HDMI_TXD1_R

A4

HDMI_TXD1#_R

B4

HDMI_TXD0_R

C3

HDMI_TXD0#_R

B2

HDMI_TXC_R

D1

HDMI_TXC#_R

D2

E2

E1

F4

F3

F1

F2

H4

H3

H1

H2

J2

J1

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

PCIE_TXP0_NB

AC1

PCIE_TXN0_NB

AC2

AB4

AB3

AA2

AA1

PCIE_TXP3_NB

Y1

PCIE_TXN3_NB

Y2

PCIE_TXP4_NB

Y4

PCIE_TXN4_NB

Y3

V1

V2

ALINK_NBTX_SBRX_P0

AD7

ALINK_NBTX_SBRX_N0

AE7

ALINK_NBTX_SBRX_P1

AE6

ALINK_NBTX_SBRX_N1

AD6

ALINK_NBTX_SBRX_P2

AB6

ALINK_NBTX_SBRX_N2

AC6

ALINK_NBTX_SBRX_P3

AD5

ALINK_NBTX_SBRX_N3

AE5

PCE_PCAL

AC8

PCE_NCAL

AB8

Place < 100mils fr om pin AC8 and AB8

3

NB0CADOUT0

NB0CADOUTJ0

NB0CADOUT1

NB0CADOUTJ1

NB0CADOUT2

NB0CADOUTJ2

NB0CADOUT3

NB0CADOUTJ3

NB0CADOUT4

NB0CADOUTJ4

NB0CADOUT5

NB0CADOUTJ5

NB0CADOUT6

NB0CADOUTJ6

NB0CADOUT7

NB0CADOUTJ7

NB0CADOUT8

NB0CADOUTJ8

NB0CADOUT9

NB0CADOUTJ9

NB0CADOUT10

NB0CADOUTJ10

NB0CADOUT11

NB0CADOUTJ11

NB0CADOUT12

NB0CADOUTJ12

NB0CADOUT13

NB0CADOUTJ13

NB0CADOUT14