A

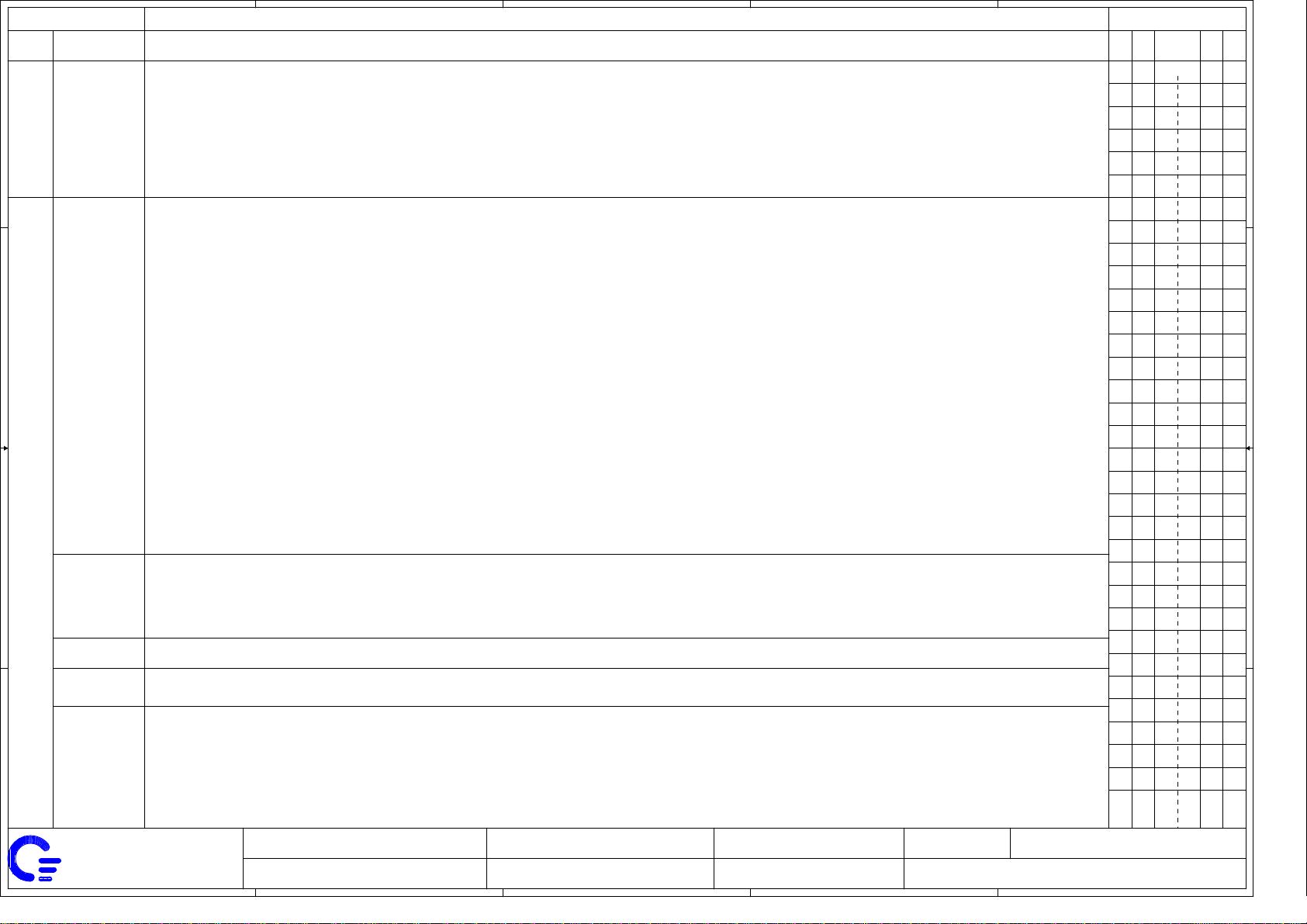

MODEL:

REV DATE

4 4

2001/05/29

3B

RT2

CHANGE LIST

C2 Test (PCB P/N: DA0RT2MBAD1)

31. To Decrease volume of PC Beep,

Page25: Change R319 to 22K, R312 to 680

Page26: Change R288 to 22K, R303 to 680

32. Page47: For machenism interference, change C509, C510 to no-loading; C511,C512 to 270U.

33. Page14: For USB signals quality, change C415, C366, C391, C386, C429, C421 to no-loading.

34.Page15: Add 2'nd source for eeprom of Lan

35.Page8: Pull-up & pull-down already built in GMCH, so change R242, R38-40, R46-49, R52, R53, R60, R62-67, R72, R73 to no-loading.

36. Page42: Change spring to FDRT1010019(5mm): PAD100, PAD102, PAD106-108, 110-112.

Ramp ( PCB P/N: DA0RT2MBAE0 )

2001/06/20

3C

3 3

2 2

2001/06/22

2001/06/28

2001/07/04

2001/07/10

1 1

1.Page12: For ICH3 (B0 stepping, QB62), change R547 to 18.2_1%.

2.Page42: Hole1, Hole2 are NPTH, so change pin1 to NC.

3.Page34: To awake EC, change D32.2 to <SUSB#> from <SUSA#>.

4.Page17: Add discharge circuits for CD_VCC: Q116, R676.

5.Page44: Change PC69, PC71 footprint to TC1206.

6.Page22: Change Q48 to 2N7002.

7.Page14: Change R20 to 0805 for USB GND.

8.Page46: To avoid interference with Lan cable, move PFL2 to TOP side.

9. For EMI,

Page27: Change C858, C860 to 180P.

Page42: Load PAD107, PAD29, PAD37. Change PAD110 to no-loading. Change PAD37 to FDSS2002019.

10.Page15: For lan, change R385 to 124_1%. Reserve C967,C757. Add 2'nd source for U59:ATP119(this config can pass the lan test in intel

lab). Change C968,C969 to 1000P_2KV_1206(footprint is compatible with 1808 size).

11. Change U47(ATI M6-P) P/N to AJAFA120T03 for TOP.

12.Page16: Change CON18(HDD conn) to DFHS44FR096.

13.Page12: Change RTC cap: C797, C796 to 15P.

14.Page36: To avoid mechanism interference, change CON15(stick conn) to 5.5mm(ACS).

15.Page30: To avoid conflict with wireless card, change R318.2 (USB_DISCONN) to CON24.4; R622.2 (USB_RESET) to CON24.6

16.Page22: Change C483 from 10U/25V_4532 to 10U/25V_1210.

17. For ESD,

Page42: Change Hole1 to <GND_DC1> and connected gnd by R678, R680. Change Hole2, PAD100 to <GND_DC2> and connected gnd by R677, R679.

Page41: Change CON5.243,244 to NC from GND.

18. Change PCB to DA0RT2MBAE0, Rev E.

19.Page47: Change D5 footprint to DSMA.

20.Page8: Because of external graphic, pull down <DREF_CLK>: delete C963, change R666 to 10K.

21.Page26: Change R165 to 0603; add R681, but reserved.

22.Page41: U5,U6,U7 cghange foot print to APIC16861-RT2.

23.Page42: Change PAD37 to FDSS2002019 to avoid interference.

24.Page8: Reserve R666.

25.Page45: Deeper sleep voltage change to 0.85V, so reserve R12,R170,R219; change R220, R169, R13 to loading.

26. Add jumper wire(AWG26) to connect PQ43 pin3 and L124 pin2 on PCB top side, to avoid VGA core power <+1.8V_VGA> drop down.

B

C

D

E

RT2 MB

Page From To

1

1A

2

1A

3

1A 2A

4

1A

5

1A

6

1A

7

1A

8

1A

9

1A

10

1A

11

1A

12

1A

13

1A

14

1A

15

1A

16

1A

17

1A

18

1A

19

1A

20

1A

21

1A

22

1A

23

1A

24

1A

25

1A

26

1A

27

1A

28

1A

29

1A

30

1A

31

1A

32

1A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

From ToPage

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

2A

2A

2A

2A

2A

2A

2A

2A

PROJECT : RT2.0

Quanta Computer Inc.

A

MB Assy' P/N: 31RT2MBAB5 Cover Sheet: 6 ofRev: 3CProject : RT2 MB

Project Manager : Jacky Lee Approved by : Jacky LeeProject Leader : T.S. Wan

B

C

Document No.: 204

Drawing by : Allan Yu

D

6

E

A

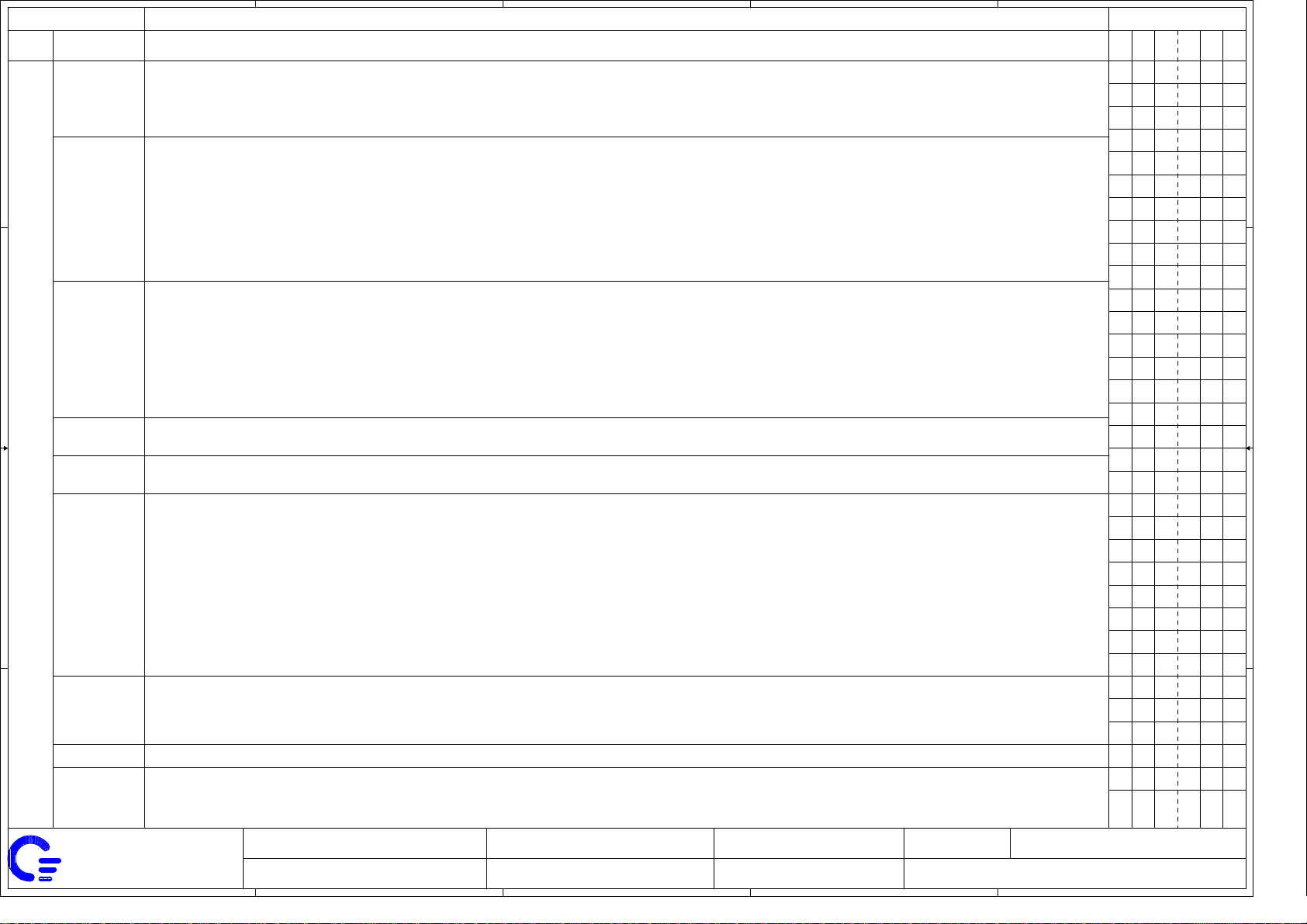

MODEL:

REV DATE

4 4

3 3

2 2

1 1

3B

2001/04/25

2001/05/07

2001/05/09

2001/05/10

2001/05/15

2001/05/17

2001/05/18

2001/05/19

2001/05/24

PROJECT : RT2.0

Quanta Computer Inc.

RT2

CHANGE LIST

C2 Test (PCB P/N: DA0RT2MBAD1)

6. Page12: Move R600, C874, R609 close to ICH3.

7. Page28: To avoid floating, add pull-up R669 at <PCICSPK>.

8. Page47: For machenism interference, exchange the parts loaded on C510-512 with C81-83.

9. Page44: Change PQ47 from <1.8V_S5> to <+1.8V>.

10. Page46: Reserved PAD101.

11. Page47: Delete R299. Change PU9.18 to GND. Delete <S0>, <S1>, R80, R81, R70, R68, R69, R77.

12. Page46: Add PC101 470P, PC102 1000P for EMI.

13. Page15: For LAN performance,

(1) Delete L101-L104, short directly.

(2) Delete <GND_LAN>, R407.

(3) C745, C730 change to GND.

(4) Change R376 to 0805.

(5) Add LAN termination plane <GND_LAN_TERM >. Add C967-C969 1000P.

(6) Change U59 to Pulse H0022.

14. Page44: Delete PR71, PR75 short directly. Change PC82 to 1U_0805.

15. To avoid ICH3 SM bus leakage,

Page37: Change U21 to FST 3253.

Page12: Change R454, R445 to <3V_S5> from <+3V>.

Page3: Add Q114, Q115, R671, R672, R673.

16. Page44: Delete PFL3, short directly. Delete PD27 and PD24. Change PR72 to 240K, PC95 to 220P, PR80 to 20K_1%, PR74 to 200K.

17. Page42: Delete PAD103, 104, 105.

18. Page15: For LAN, add R674, R675 0_0805.

19. Page28: Add C970, C971 0.1u_0402 at L100.

20. Page15: Change R397 to BK2125HM121. Change CON23.15 to GND.

21. Page42: Delete PAD13, PAD32, PAD38.

22. Page23: Change the trace width or CRT RGB to 4 mil from 10 mil to approach the recommended impedance 75 ohm.

23. Page15: Add C972, C973 by intel recommendation for LAN.

24. For EMI

Page18: Add C974, L134.

Page24: Add C975, C976.

Page46: Change PL6, PL10 to FBMJ3216HS800-T.

Page47: Add L135 FBMJ3216HS800-T.

Page23: Delete TV_GND, change to GND. Delete R144.

25. To reduce Audio noise,

Page41: Change CON5.182 to AUDGND from GND.

Page26: Change Q62, Q60, C610, C64 to AUDGND.

Page30: Delete C65.

Page22: Delete C399-C403, C53, C464.

Page26,27: Change footprint of CON20,CON19,CON22. Delete R525, R550, R521, R523, R158, R568.

Page25: Delete R314, R313.

26. To Add regulator for VGA PLL power,

Page24: Delete C149, C121, C79. Add U89, C988, C985, C986, C989, C987, C978, C984, C982.

27. To fix VAUXPCIC leakage under Suspend to Disk,

Page12: Add U87(NC7SZ32), C977, <SUSCLK_ICH>.

28. Page42: For ICT test tool, change HOLE4,20,15,21,16 to NPTH.

29. Page23: Move C8 from TOP to BOT.

30. BOM changes: Page42: PAD109 no loading; Page18: Y1 change part to BG627000106; Page3: Update U24 to rev E; Page23:

Change CON12 to Yellow, and C803,C804,C808,C809,C811,C812 to 82P, and L34-36 to 1.8UH; Page27: Change CON19 to Blue,

CON20 to Pink; Page36: Change CON15 to vendor ACES; Page38: Change CON28 to vendor ACES; Page15: Change U59 from H0022

to H0029 (it's same as the former but lower cost for asia market). Page6: Change U17 to new ver, QC32.

Project Manager : Jacky Lee Approved by : Jacky LeeProject Leader : T.S. Wan

A

B

C

D

E

RT2 MB

Page From To

1

1A

2

1A

3

1A 2A

4

1A

5

1A

6

1A

7

1A

8

1A

9

1A

10

1A

11

1A

12

1A

13

1A

14

1A

15

1A

16

1A

17

1A

18

1A

19

1A

20

1A

21

1A

22

1A

23

1A

24

1A

25

1A

26

1A

27

1A

28

1A

29

1A

30

1A

31

1A

32

1A

MB Assy' P/N: 31RT2MBAB5 Cover Sheet: 5 ofRev: 3CProject : RT2 MB

Document No.: 204

Drawing by : Allan Yu

B

C

D

E

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

From ToPage

1A

1A

2A

1A

1A

2A

1A

1A

2A

1A

1A

1A

1A

1A

2A

1A

2A

1A

1A

2A

1A

2A

1A

1A

1A

1A

2A

6

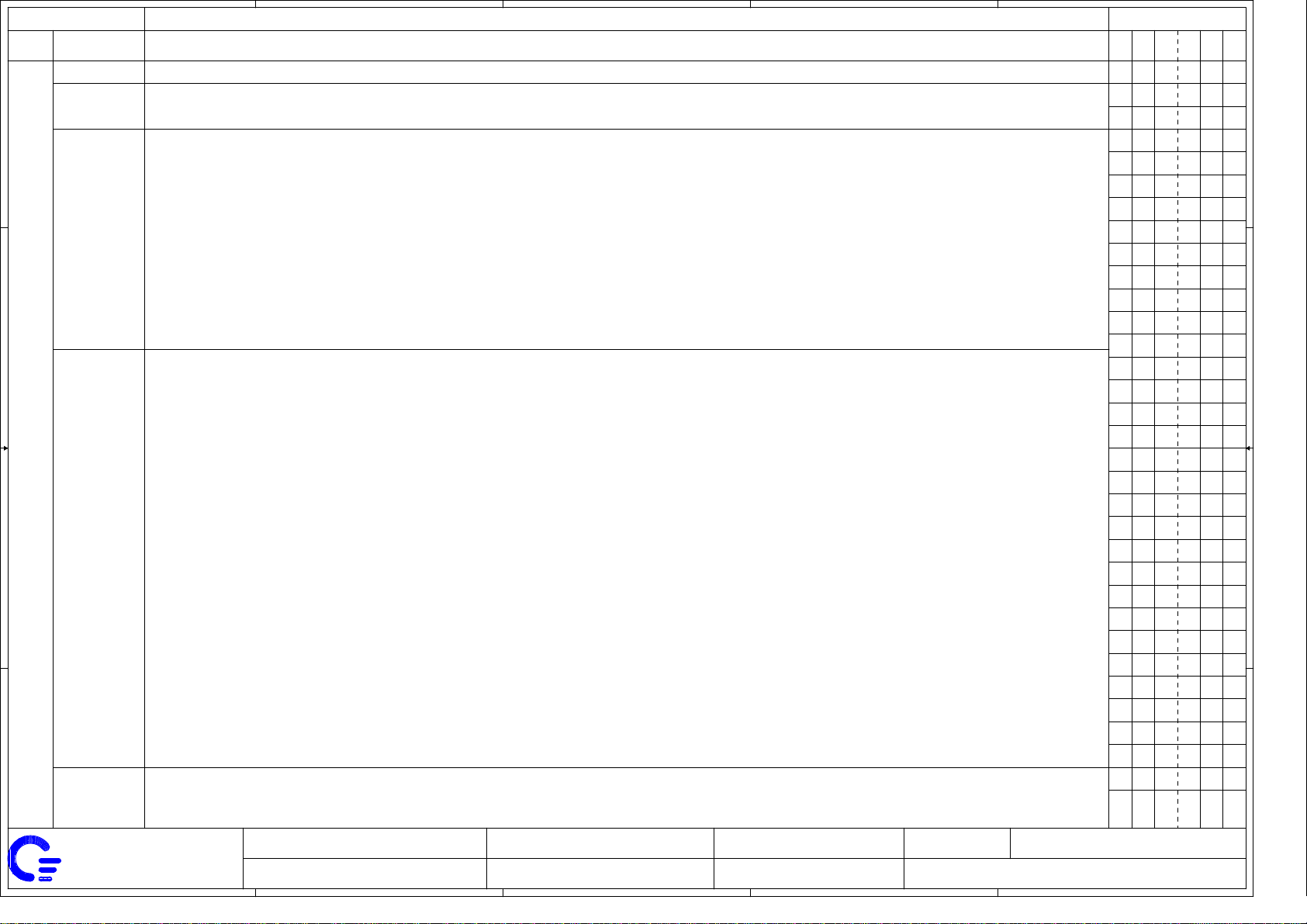

MODEL:

REV DATE

A

RT2

CHANGE LIST

B

C

D

E

RT2 MB

Page From To

From ToPage

48. Page35: For interference, change U58 to NC7SZ58.

2001/04/02

4 4

3A

2001/04/03

3 3

2001/04/09

2 2

2001/04/16

49. Page38: Change R614 to 680 ohm; CON28.1,R614 to be powered by +5V.

50. Page18: For ATI P6 D3 cold, add R659 to interconnect <PCIRST#> and P6. Change R518,Q80,U68,C841 to no-loading.

51. Page47: To interconnect pwrgood of MAX1718 and <HPWG> to EC, add D46, R660.

52. Page18: Change the gate of Q33,Q41 from <5VSUS> to <+5V>.

53. Page47: Change R299 to no-loading.

54. Page16: For<- HDDRESET>, change U83 to NAND(TC7SH00FU), add DTC144EU,10K to isolate different powers.

55. For ATI P6 D3 cold, delete <2.5VSUS>,

Page44: Delete <2.5VSUS>, PQ48,PR77, change PQ46 to no load and nets. Add R661,R662(no load). Change the control of U16.11 to <MAINON>

but option to <SUSON> by R662.

Page24: Delete L131,<2.5VSUS>.

56. Page24: Add regulators for DAC powers of CRT & TVout. Add U85,U86,C949-958. Delete L21,L93,C133,C515.

57. Page24, 44 ATI P6 power source options about D3 cold and D3 hot:

Power source option

for ATI P6 power states selection

ATI P6 power

states

Control

signals

Location

Q110

R661

L133

L130

R662

PQ46

L22

U68 Q80

R518 C841

58. To decrease volume of pc beep,

Page26: Change R288 to 6.8K.

Page25: Change R319 to 6.8K.

59. Page47: To fine tune CPU core voltage (VTT), change R89 to 1.82K_1%.

60. Page15: To improve Lan performance, change R385 to 110_1% from 100_1%, C757 to 1000P_2KV from 68P_2KV.

D3 cold

MAINON

Components options

Load

R659

L129

No load

D3 hot

SUSON

No load

Load

C2 Test (PCB P/N: DA0RT2MBAD1)

1. To fix wrong pins' definitions of ZV port buffer,

Page29: swap net names between U56.3 and U56.9; U56.17 and U56.11.

Page18: Change net name of U47.AA3 to <ZV_PCLK>.

Page25: Change net name of U43.50 to <ZV_SCLK>.

2001/04/23

3B

1 1

2001/04/24

PROJECT : RT2.0

Quanta Computer Inc.

2. For EMI,

Page3: Add R668, R664 0 ohm to connect GND planes.

Page6: Add R665, C960, but reserved.

Page7: Add C961, C962, C965, C966.

Page8: Add R666, C963, but reserved.

Page12: Add R667, C964, but reserved. Change R475 to 22 ohm from 68; C817 to 5P from 15P.

3. Page44: Change PC96 to 10U/10V/TAN.

4. Page15: Change C757 to 1000P_X7R_4520_3KV for LAN.

5. Page29: Change C723 to 0603 from 0402.

Page30: Change C733 to 0603 to 0402.

MB Assy' P/N: 31RT2MBAB5 Cover Sheet: 4 ofRev: 3CProject : RT2 MB

Project Manager : Jacky Lee Approved by : Jacky LeeProject Leader : T.S. Wan

A

B

C

Document No.: 204

Drawing by : Allan Yu

D

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

E

1A

1A

1A 2A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

1A

1A

2A

1A

1A

2A

1A

1A

2A

1A

1A

1A

1A

1A

2A

1A

2A

1A

1A

2A

1A

2A

1A

1A

1A

1A

2A

6

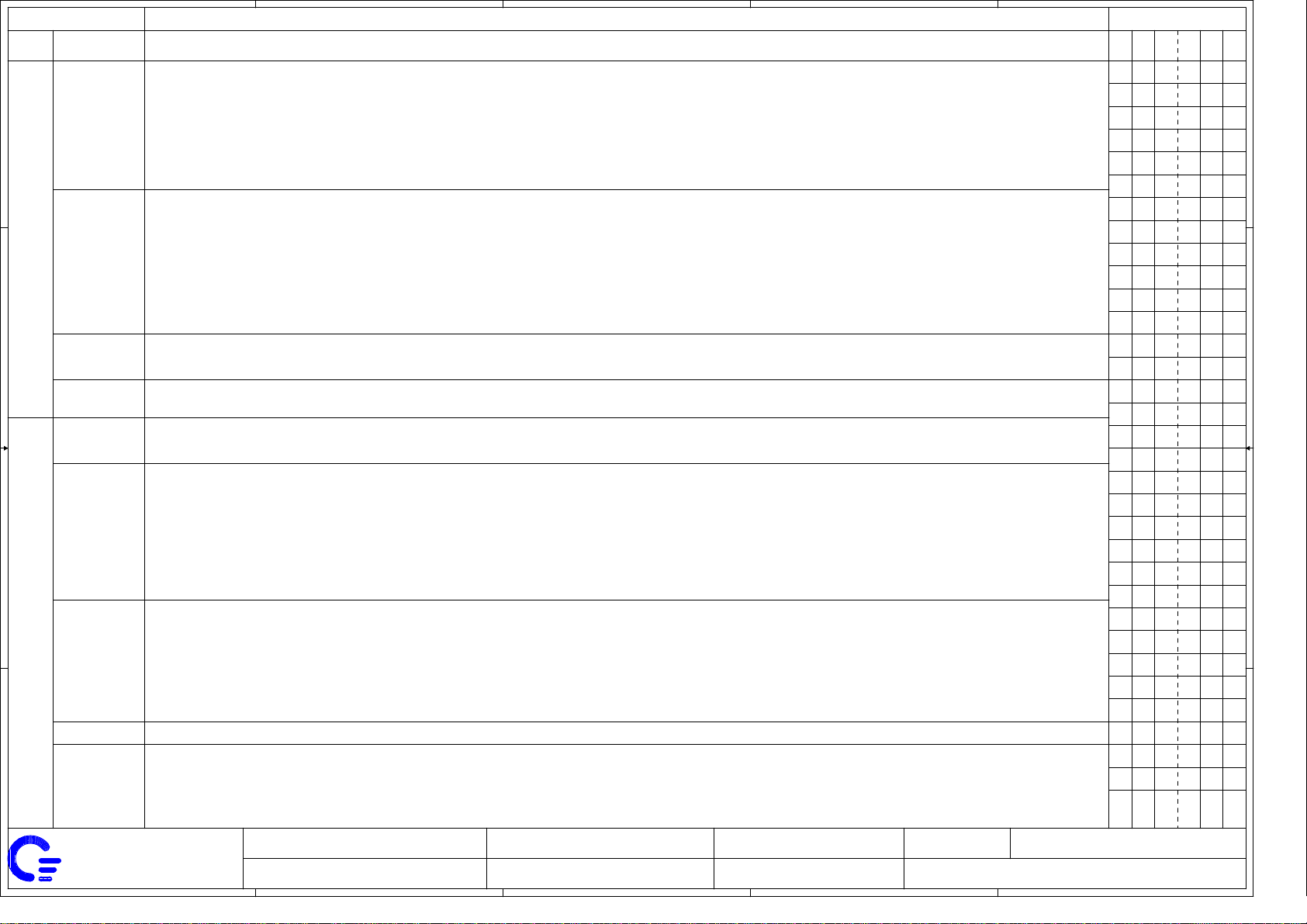

MODEL:

REV DATE

A

RT2

CHANGE LIST

B

C

D

E

RT2 MB

Page From To

From ToPage

2001/03/15

4 4

3 3

2 2

1 1

2001/03/16

3A

2001/03/22

2001/03/28

2001/03/29

15. Page47: Delete R644.

16. Page44: Change PQ48 to SI4800DY for larger current rating.

17. Page16: Change Q102, Q103 to DTC144EU to fix the problem that high level driven by 3.3V is lower than <HDD_VCC>.

18. Page44: Change PU16 pin20, 21 to 5VPCU.

19. Page47: Change D3 to EC31QS03L.

20. For Intel recommended on GMCH QS stepping,

Page6: Modify C430 and change value to 0.01U

Page3: Add R649 240K at U24.24.

21. Change part 1U_0805 to 1U_0603: C59-62, C521, C463, C545, C462, C533, C564, C559, C625, C624.

22. Page11: Add R658 pull-up for <RC> but reserved.

23. Page7: Change <SM_CLK> layout for Intel design change.

24. Page39: Change U30 power to <+5VA>, add C941 to reduce noise of <BEEP>.

25. For audio noise,

Page26: Change the power to <+5VA> and gnd to <AUDGND> for U12, Q47, C64, R54,R225, R256.

Page41: CON5 pin1,2,61,62,183,65 to <AUDGND> from <GND>.

Page27: Delete R292, R204, R269 and short the nets directly.

Page26: Delete R232.

26. Page41: Change R27 to <AUDGND> from <GND>, CON5 pin243, 244 to <GND> from <CHASIS_DOCK_1>(chasis gnd).

27. To prevent <HDD_VCC> and <CD_VCC> from power down during <PCIRST#> acting in warm-boot,

Page12: Delete the GPIO41, GPIO42 at U67(ICH3) pin G21, D23. Add <HDDVCC_EN> at pin W4(GPIO27), <CDVCC_EN> at pin Y3(GPIO28).

Page16: Add <HDDVCC_EN>, R653, R654(reserved), and <HDDVCC_ON> from EC. Change Q106 to 2N7002E.

Page17: Add <CDVCC_EN>, R655, R656(reserved), and <CDVCC_ON> from EC.

Page35: Add <HDDVCC_ON>,<CDVCC_ON> at U82 pin2, 5, controlled by EC (reserved).

28. Page12: Add R652 pull-low <PWROK>.

29. For RTC leakage, implement the design changes from Intel(WW08),

Page12: Add R652 pull-low <PWROK>. Add U84, C948, R651.

The rest changes have been done.

30. Page12: Move the RTC short pad G2 near CON29 under ninipci door.

31. Page16: For <-HDRESET>, Add U83, C942; delete Q102,103105, R630, R632.

32. Page16: Add C943. Change R629 to 1M.

33. Page17: Change R143 to 1M.

34. Page11: Add R657 10K at <APICD1>. Change R510 to 10K.

35. Page12 Change R547 to 22.6_1% for uab bias.

36. Page 24: For ATI P6 D3 cold, Change L131,L129,L22 to no-loading; L132,L130,L133 to loading.

37. For EC to control RF ON or OFF,

Page38: Add Q112, <RF_ON_OFF>.

Page35: Add <RF_ON_OFF> at U78.19.

38. Page36: For FAN driving current, change R458 to 1K; D41to loading; C895 to 4700P for <FANSIG>.

39. To prevent interference from wireless card,

Page30: Change C590,711,748 to 1U_0603.

Page25: Change C552 to 1U_0603.

Page28: Change C684 to 1U_0603.

40. Page46: To save power, change PR49,50,12,13 from 100K to 1M.

41. Page42: Add EMI Spring: PAD100-109.

42. Page5: Add C944-C947 for VTT.

43. For interference, move Q56,R380 away from CON29.

44. Page34: For interference, change C844 to 1U-0603.

45. Page33: Add IRGND plane under the ir module.

46. Page36: Move R458, Q73 to top side.

47. For impedance control, Change USB diffrrencial pairs to 7.5/7.5 mil (width/space).

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

1A

1A

1A 2A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

2A

2A

2A

2A

2A

2A

2A

2A

PROJECT : RT2.0

Quanta Computer Inc.

A

MB Assy' P/N: 31RT2MBAB5

Project Manager : Jacky Lee Drawing by : Allan Yu

B

Project Leader : T.S. Wan

C

Document No.: 204Project : RT2 MB Cover Sheet: 3 of

D

Rev: 3C 6

Approved by : Jacky Lee

E

MODEL:

REV DATE

A

RT2 MB 16M

CHANGE LIST

B

C

D

E

RT2 MB 16M

Page From To

From ToPage

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

1A

1A

1A 2A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

B Test (PCB P/N: DA0RT2MBAB5)

40. Page46: For power on squence, change PC36, PC38 to 1000P.

4 4

3 3

2A

2001/02/26

2001/02/27

2001/03/02

2001/03/06

41. Page4: Change R108 to 0603 size.

42. Page24,44: Change C149, C167, C171, C793 foot print to TC1206

43. Page38: Change R362 to 10K.

44. Page43: Change R516, R520 to no-loading for ITP.

45. Page25, 12, 15: ChangeY3 to Epson SG-710ECK, Y6 to MC-306, add 2nd source BG625000508.

46. Page12: Add L122 on <VCCRTC> for EMI.

47. Page46: Change R300 to 0603 size.

48. Page3: For EMI, add C900-C905(10P, reserved) and place near the destinations.

49. Page5: Add bypass cap 0.1U_0402 on VTT (C906-C926) and VCCT(C927-C936).

50. Page24: Modify power circuit for <VGA_PLL1.8>,<VGA_PNLPLL1.8>.

51. Page3: For EMI, modify GND of CLK generator. Add <CLK_GND>, R642, R643.

52. Page30, 35: Change the control of <-RF_ON_LED>, R633 from miniPCI to EC.

53. Page23, 38: To save power, change power plane from <5VPCU> to <+5V> on U39.8, R176, R3; from <3VSUS> to <3.3VAUX> on R369, R362.

54. Page47: Change Q6, Q12 to IRF7811A; Q5, Q10, Q11 to FDS7764A because of better characteristics.

55. Page20: Change L23 to no-loading, L24 to loading for Hyundai DDR. And change part to FCM2012V131DC10 for larger current rating.

56. Page36: Change R628 from 180K to 100K for part available.

57. Page12: For RTC leakage, change R455 to 22K at U67.Y6 ( INTRUDER# ).

C1 Test (PCB P/N: DA0RT2MBAC3)

2001/03/07

2001/03/08

2 2

3A

2001/03/12

2001/03/13

2001/03/15

1 1

1. Page22: Change R210 from 22_1206 to 22R_0805.

2. Modify 3V power circuits to simplify 3V resources and components. Delete <3V_ALWAYS> in entire schematics because it doesn't need

ALWAYS 3V.

Page49: Change PU15.28 from <VL> to <RVCC_ON>, change <3V_ALWAYS> to <3V_S5>.Change parts of PL4, PR63. Delete PC36, PC47. NC PD19.

3. Page21: Change memory I/O power of VGA chip, VDDR1, from <VDD_SDRAM> to <VDDQ_2.5V>. Because it must be same as VDDQ of VGA SDRAM(U23,

U60). Change VDDRH(U47.C5) to <VDDQ_2.5V> thru L123.

4. Page44, 46: Change net name from <MAINON_0> to <-MAIN_ON>, from <SUSON_0> to <-SUS_ON>.

5. Page47: Add L127, R644 but reserved for second source.

6. Page13: Change R432 from 0805 to 0603.

7. Page46: Delete fuse L33, L44. Change PL6 to FBM3216HS480NT(6 Amp) and add PL10 the same part.

8. Page 44: Modify 1.8 and 2.5 voltage circuits to switching power circuits for efficiency, change the source of <+1.5V> to be from

<+1.8V>.

9. As the changes of item 8, modify the VGA power circuits,

Page24: Delete regulators circuits: PU1, R98, R99 for <+1.8_VGA>; Q21, Q72, PU11, C285, C787-788, R447 for <VDDQ_2.5V>; U20, C173, C146,

R337-338 for <VGA_MEMPLL1.8>, and the relative discharging circuits. Then power them thru beads.

10. Page25, 35: Change <-M3_RST_EN> to <M3_RST_EN> for high-active.

11. Page47: Add discharge circuits for <VCCT>: R647, Q109; <VTT>: R645-646, Q107-108.

12. Page6: Change R324 footprint from 0603 to 0805.

13. Page17: Change Q78 from SI4800DY to SI3456 for small size.

14. For VGA D3-cold,

Page44: Add <+2.5V> power, PQ48, Q110, R648.

Page24: Add <2.5_VGA>, L131(reserved), L132 for option of power.

Page20: Change L24 to be powered with <2.5_VGA>.

Page24: Add <1.8_VGA>, L129(reserved), L130 for option of power.

Page24: Add L133( reserve L22 ) for option of power between <3VSUS> and <+3V>.

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

2A

2A

2A

2A

2A

2A

2A

2A

PROJECT : RT2.0

Quanta Computer Inc.

A

Project : RT2 MB 16M MB Assy' P/N: 31RT2MB0019

Project Manager : Jacky Lee Project Leader : T.S. Wan

B

C

Document No.: 204

Drawing by : Allan Yu

D

Rev: 3C

Cover Sheet: 2 of 6

Approved by : Jacky Lee

E

MODEL:

A

B

C

D

E

RT2 MB 16M RT2 MB 16M

CHANGE LISTREV DATE

Page From To

Page From To

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

1A

1A

1A 2A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

2000/01/04

1A

4 4

2001/01/12

2A

3 3

2 2

2001/02/26

1 1

A Test

First Release (PCB P/N: DA0RT2MBA7)

B Test (PCB P/N: DA0RT2MBAB5)

1. Change R103, R107, R61, R92, R97, R122, R123, R75, R379, R581, R582 from 22_1206 to 22_0805.

2. Page24: Modify footprint (UMAX8) of U19,U42.

3. For NS87570 strap pin,

Page34: Change R584 from 10K to no-loading, R585 from no-loading to 10K.

4. For Super I/O (PC87393) strap pin,

Page 31 Delete R463 at <TXD1>.

5. Page 5: Change R439 from 0805 to 0603.

6. The NMOS turn-on voltage (Q84, Q18) for 3V_S5, 3.3VAUX is not high enough,

Page44: Add Q98, Q97, R613, R612, <3V_S5_EN>, <3VAUX_EN>.

7. The voltage level of VGA_PLL1.8 and VGA_PNLPLL1.8 is not correct

Page24: Change R283, R51 to 44.2K_1%.

8. Spring arm ground contact

Page30, 10, 51: CON27.125.126; CON24.125.126; CON25.147.148; CON26.125.126.

9. Page15: Change U57(LAN PHY) to 82562EP(Kinnereth-M).

10. Simplify RI# circuits:

Page38: Delete U53, U54, C694, C695, R372, R373. Short D21.2, D22.2, D23.2, Q64.2.

11. Page 3: Exhange clock generator U24 66MHz output pin 22 & 23 for power down mode sequence.

12. Page 12: Delete USB pull low 1.5K: R559-R564, R541-R546.

13. Modify <DISPON> circuits :

Page22: Delete U35,U11, add D39, D40.

14.To prevent interference,

Page34, 51: change C789, C878, C810, C843 to 1U_0603_X5R.

15. To eliminate ground noise,

Page47: Change PU9.15 from inverter ground to system ground(GND).

16. Page15: Add one 4-pin lan pass through connector(CON29) for docking.

17. Page15: Add bypass cap C885-C889 for U56 (86562EP).

18. Page47: Delete SW2, add R618, change R272 from 0 to 15K_1%.

19. Page14: Change pin assignment of USB connector(CON6) and del U10. Change C422, C423 from 4.7Uf to 100uF

20. Page 16: Add reset and power control circuit for HDD.

21. Page 20: Pin 28 of U60 changes net name from VMCS1# to VMCS0#

22. Page 25: Add L120, L121for 49.152MHz oscillator for EMI.

23. Page 26: To increase the volume gain. Change R330 from 20K to 33K and R331 from 2.49K to 0.

24. Page 30: Add BlueTooth USB signals to 1st mini PCI connector.

25. Page 34: MY11 pin name is duplicated on BP4, pin5 and CON10, pin15. Change the net name to MY1_1.

26. Page 34,35: Add additional GPI and GPO for 87570.

27. Page 36: Add new fan drive circuit.

28. Page 36: Modify power LED control circuit for single color support, but reserved <-PWRLED1>.

29. Page 38: Add wireless LAN enable/disable circuit and add CON28 for antenna support.

30. Page 30: Route the AC-link signals to 1st mini PCI connector.

31. Page 14: Add two power control signals to USB ports and <USBOC0#>,<USBOC1#>.

32. Page 5: VID pullup resistor changes from 10K to 1K.

33. Page7, 9: New pin definition were added for GMCH-A3 silicon.

34. Page 7: Del R345 and make the length equals to 150+-50 mil.

35. Page 22: Modify <DIPON> circfuits, it controled by VGA(<-BLON>), ICH3(<DISP_ON>); simplify LCDVCC control circuits(<DIGON>).

36. Page46: Add spring ( PAD101 ) under power jack( PJ1 ).

37. For EMI,

Page25: Add L120, L121.

Page6: Add R639, C899(reserved), <CLK66_GBIN_1>.

38. Page6: R300 change to 0603 size.

39. Page25: Change R313 to noloading to disable modem auto detect by ES1988.

33

1A

34

1A

2A

35

1A

36

1A

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A 2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

2A

PROJECT : RT2.0

Quanta Computer Inc.

A

Project : RT2 MB 16M MB Assy' P/N: 31RT2MB0019

Project Manager : Jacky Lee Project Leader : T.S. Wan

B

C

Document No.: 204

Drawing by : Allan Yu

D

Rev: 3C

Approved by :

Cover Sheet: 1 of

E

6

5

4

3

2

1

0711 modify

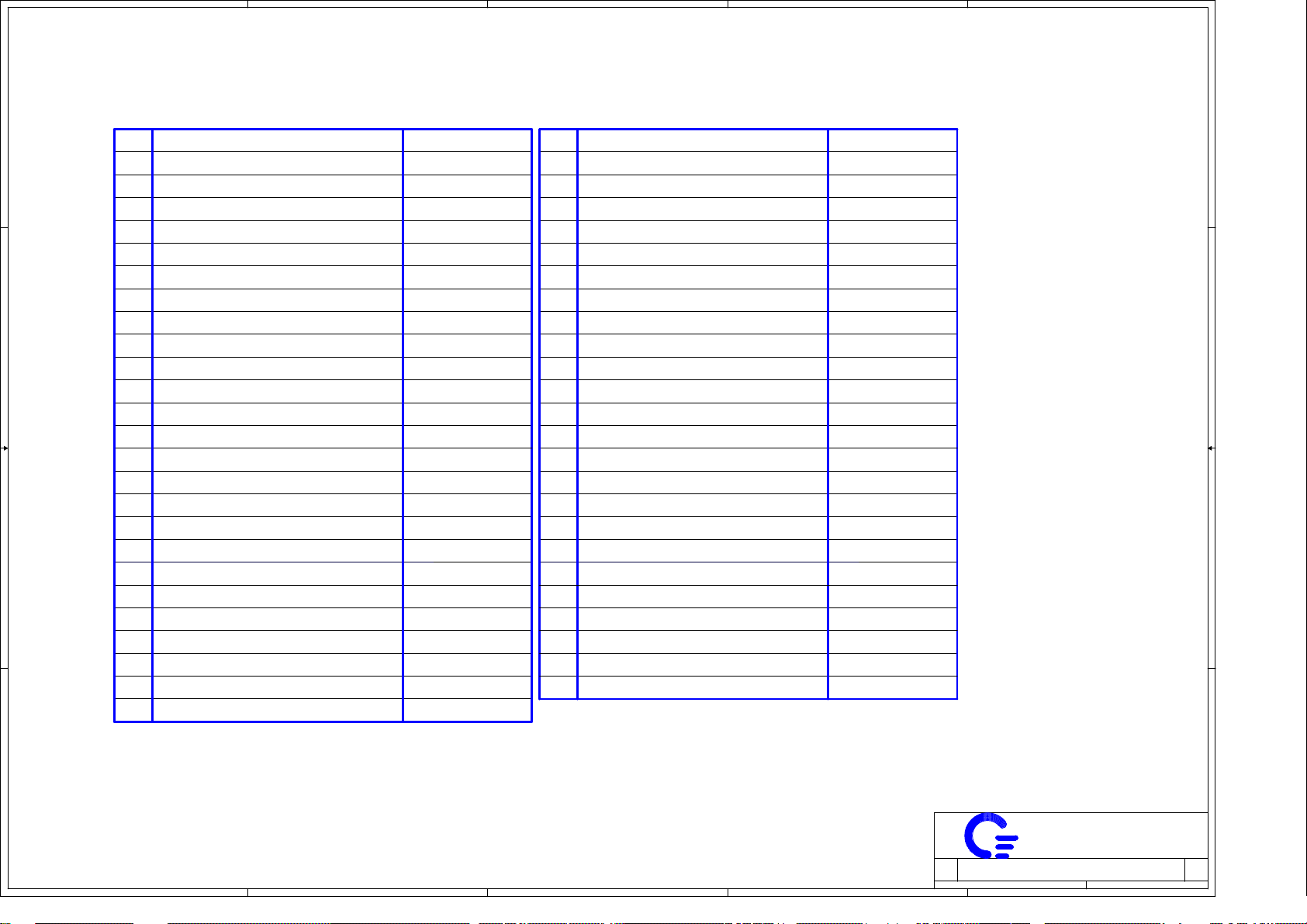

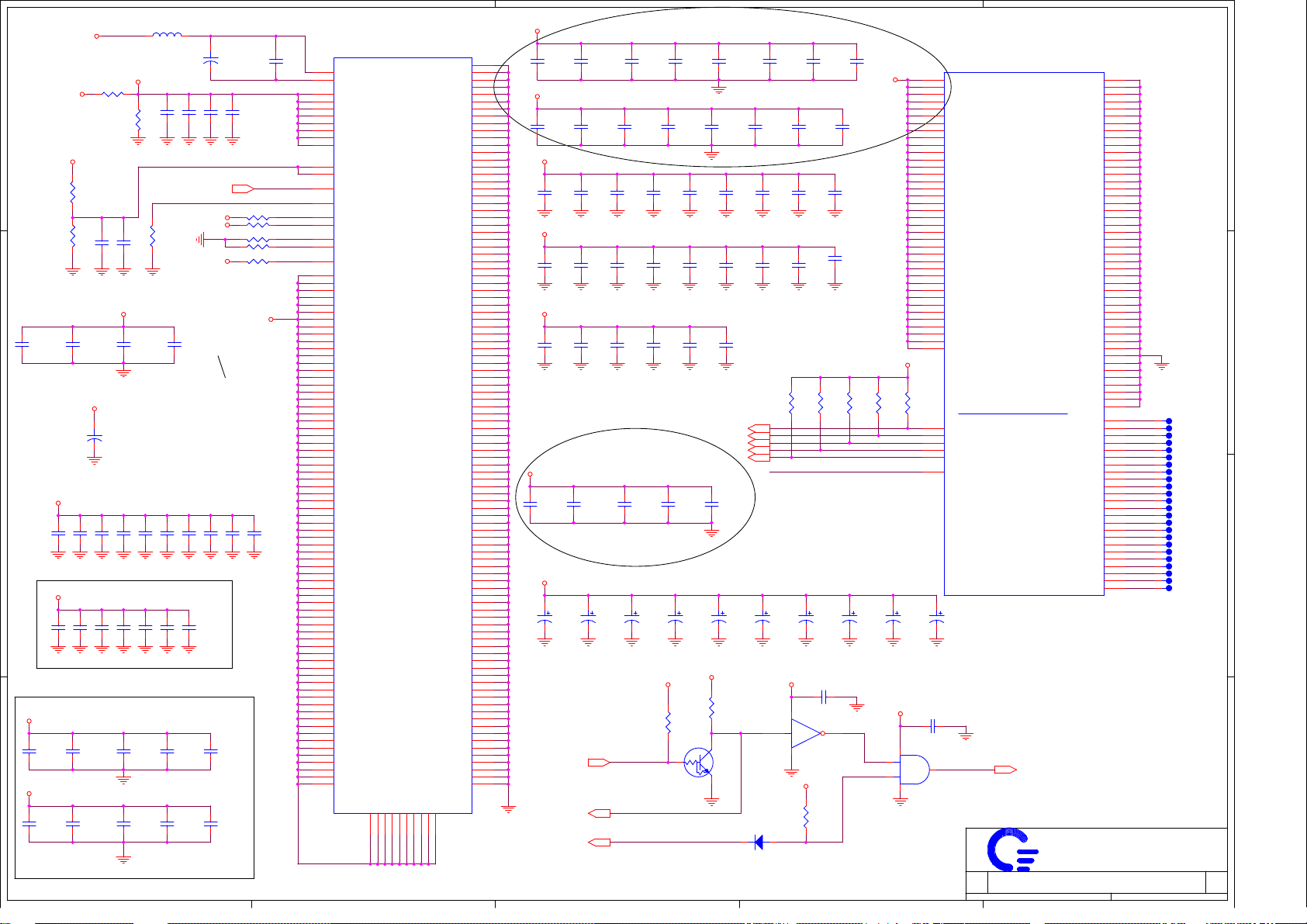

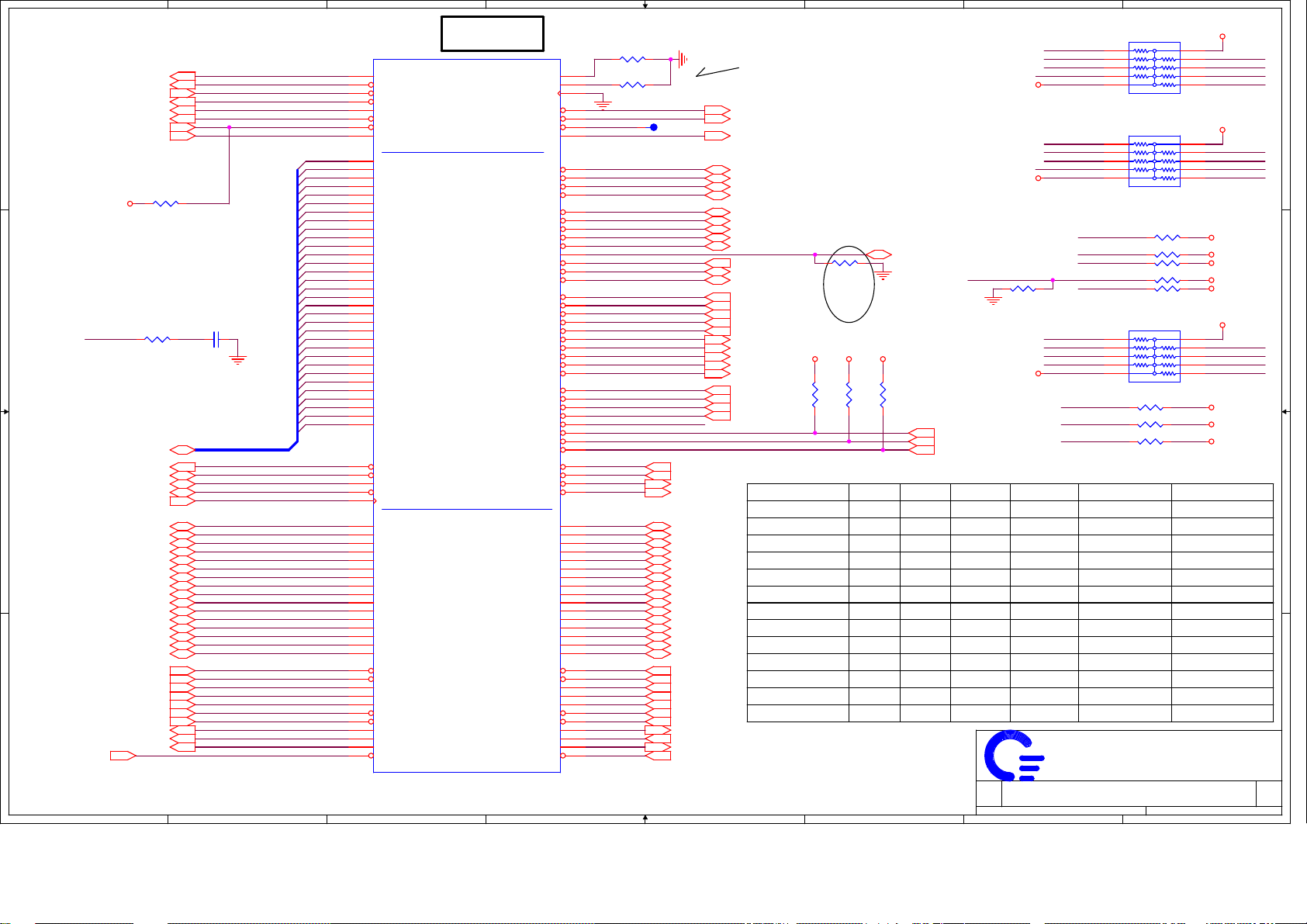

RT2 MB: PCB Rev E , Schematics Rev 3C

Schematics Page Index

D D

C C

B B

Pg#

Schematic Block Diagram

1

2

PAGE INDEX

3

Clock Generator

TUALATIN CPU(HOST BUS)-1

4

5

TUALATIN CPU(POWER/NC)-2

GMCH-M(HOST)-1

6

7

GMCH-M(DRAM)-2

8

GMCH-M(AGP)-3

9

GMCH-M(VCC,GND)-4

SDRAM,SODIMMX2

10

11

ICH3-M (CPU,PCI,IDE)-1

12

ICH3-M (USB,HUB,LPC)-2

13

ICH3-M (POWER&GND)-3

USBx2

14

15

LAN interface

Primary IDE (HDD interface)

16

17

Secondary IDE/FDD interface

18

ATI P6 (HOST,VIDEO O/P)-1

19

ATI P6 (VRAM)-2

20

Video DDR SDRAM

21

ATI M6 (PWR/GND)-3

LCD interface

22

S Video/Composite,CRT

23

VGA power

24

25

ESS1988

26

AMP/line out

Description

DNI LIST

Pg#

line in/mic in/CD audio in

27

TI1420 CARDBUS CONTROLLER

28

CARDBUS interface

29

MINI PCI-1 interface

30

super I/O (PC87393F)

31

LPT/FDD interface

32

COM/IR interface

33

PC87570F

34

35

570 I/O & RF/B CONN

570 access BUS/PS2/FAN/touch PAD

36

37

ICH SMBus

38

RING INDICATOR

39

1K Hz BEEP

40

upper,volume interface

FULL DOCK

41

hole PAD and EMI PAD

42

43 ITP interface

44

system special power

45

VID selector

46

power JACK/BATTERY CONN.

47 CPU power-VCCT/VTT

4850CHARGER & DISCHARGER

POWER CIRCUIT(MAX1632)

49

BATTERY SELECTOR

MINI PCI second interface51

Description

DNI LIST

11

10-LAYERS

STACKUP

Layer 1

Layer 2

Layer 3

Layer 4

Layer 5

Layer 6

Layer 7

Layer 8

Layer 9

Layer 10

TOP

GND

IN1

IN4

GND1

IN5

IN2

IN3

VCC

BOT

Modified on C1 test

A A

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

FRONT-PAGE

PROJECT : RT2.0

Quanta Computer Inc.

1 57Tuesday, September 11, 2001

1

1A

5

4

3

2

1

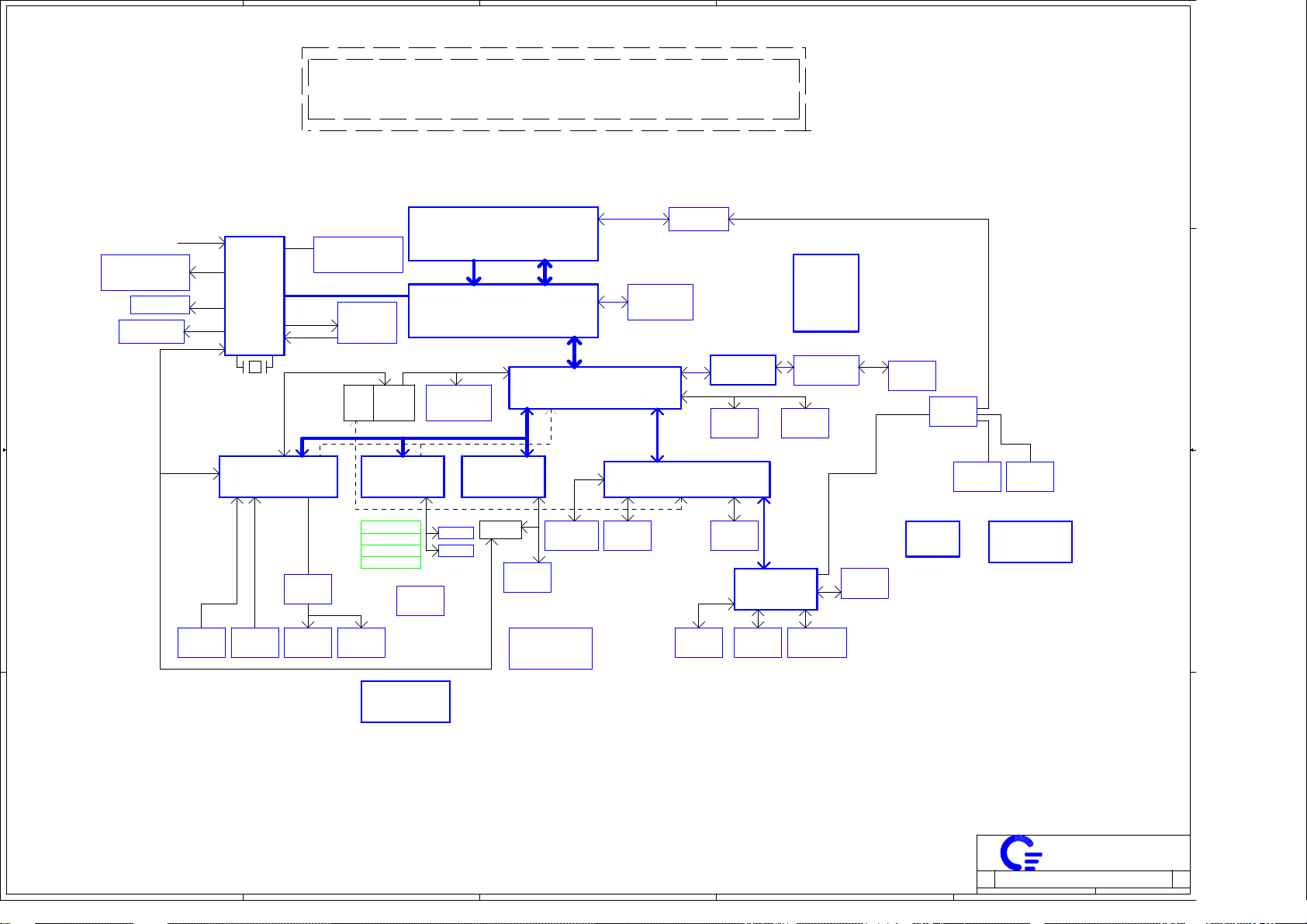

RT2.0

D D

SO_DIMM*2

Page 10

LPC

PC87393F

Page 31

MAX1617

Page 4

IC9250-38

OR

FS6234-01

Clock Genrator

Page 3

PHY_82562EM H0009 LAN

Page 15

Page 15

USB1USB0

Page 14 Page 14

XBUS

PC87570F

Page 34

PS2 K/B TOUCH PADLINE_OUTLINE_IN MIC SPK_INT

Page 36

Page 34

BIOS

Page 34

connector

Page 15

CHARGE

GATE

Page 48

BAT2

Page 46 Page 46

BAT1

DC/DC

Page 47 Page 49

CLK66_AGP

LCD PANEL

XGA,SXGA+,UXGA TFT

(13.1/14.1/15.0")

C C

CRT port

S_VIDEO

TV OUT

Page 22

Page 23

Page 23

ZV_VIDEO

SHFCLK

LCD DATA

R,G,B

Y,C,COMP

ATI P6

VGA CONTROLLER

Page 18~21

27MHZ

Video-RAM Module

SDR: 8M/16MB

DDR: 16M/32MB

GAD[0--31], AGP control signal

MK1707

PVCLKI

PMCLKI

SHFCLK

spread spectrum

control

(Optional)

FDD

ZV_AUDIO

B B

PCI_AUDIO

ES1988

Page 25

AMP

Page 26

PCI_MODEM

802.11_LAN

BLUE_TOOTH

ACLINK_MODEM

Page 26Page 27Page 27

CPU: Tualatin

Page 20

Page 18

CD_AUDIO

SEC/IDE

Page 17Page 17 Page 16

MINI_PCI

first

Coppermine T

GMCH-M

PRY/IDE

PCI_BUS

Page 30 Page 28

ANTANA1

ANTANA2

MODEM

JACK

PSB

PCMCIA

TI1420

ZV_PORT

PCMCIA

SOCKET

HD#(0..63)HA#(3..31)

ICH3-M

AC_LINK

LPT/FDD COM1 IR

Page 29

DOCKING

Page 41

CPU thermal diode in

Page 04~05

Page 06~09

HUB

Page 11~13

Page 33 Page 33Page 32

MINI_PCI

second

Page 51

A A

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

PROJECT : RT2.0

Quanta Computer Inc.

BLOCK DIAGRAM

1

2 57Tuesday, September 11, 2001

1A

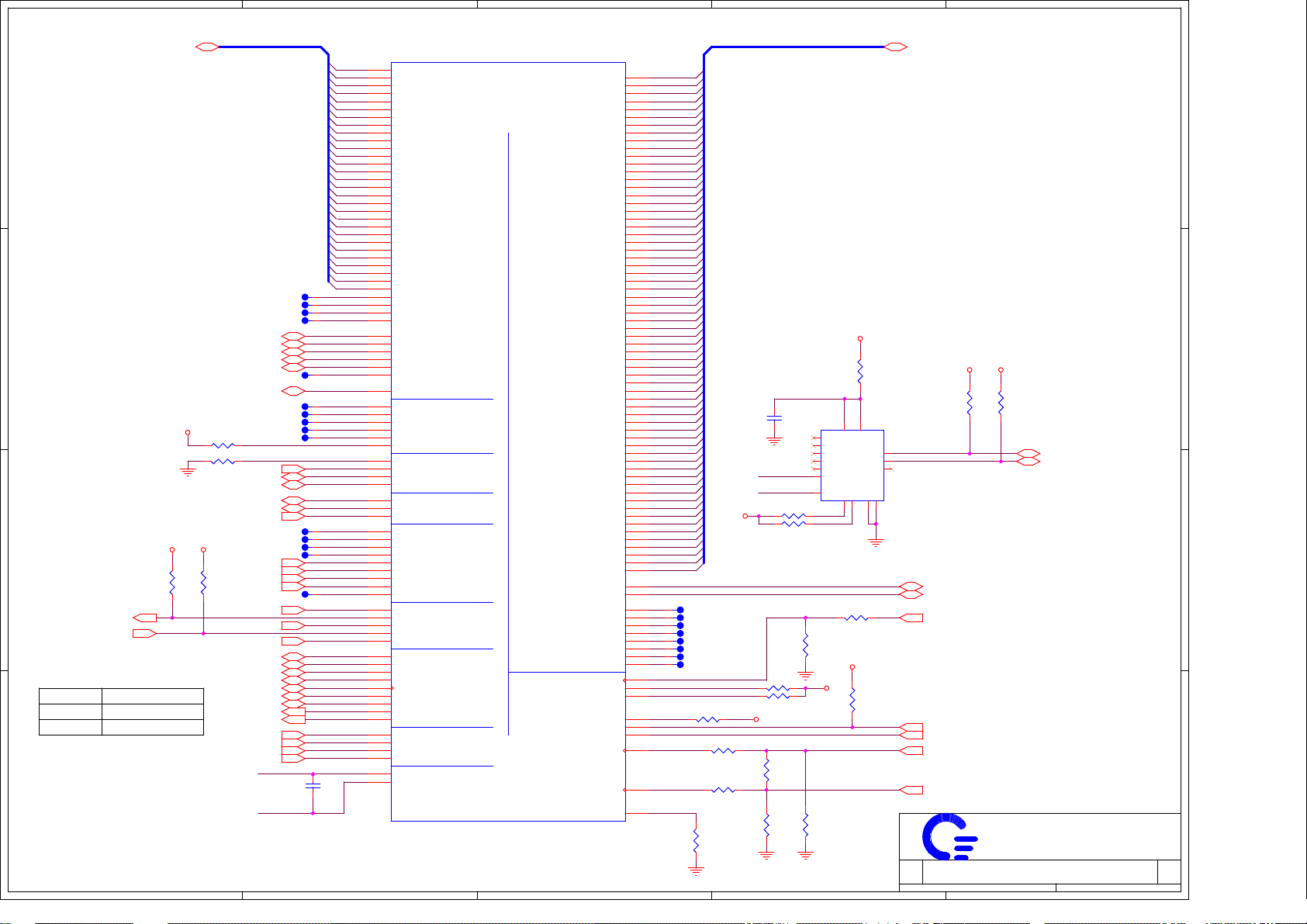

1

2

3

4

5

6

7

8

1 133MHZ

STSEM BUS FREQUENCYBSEL[1:0]

1

100MHZ10

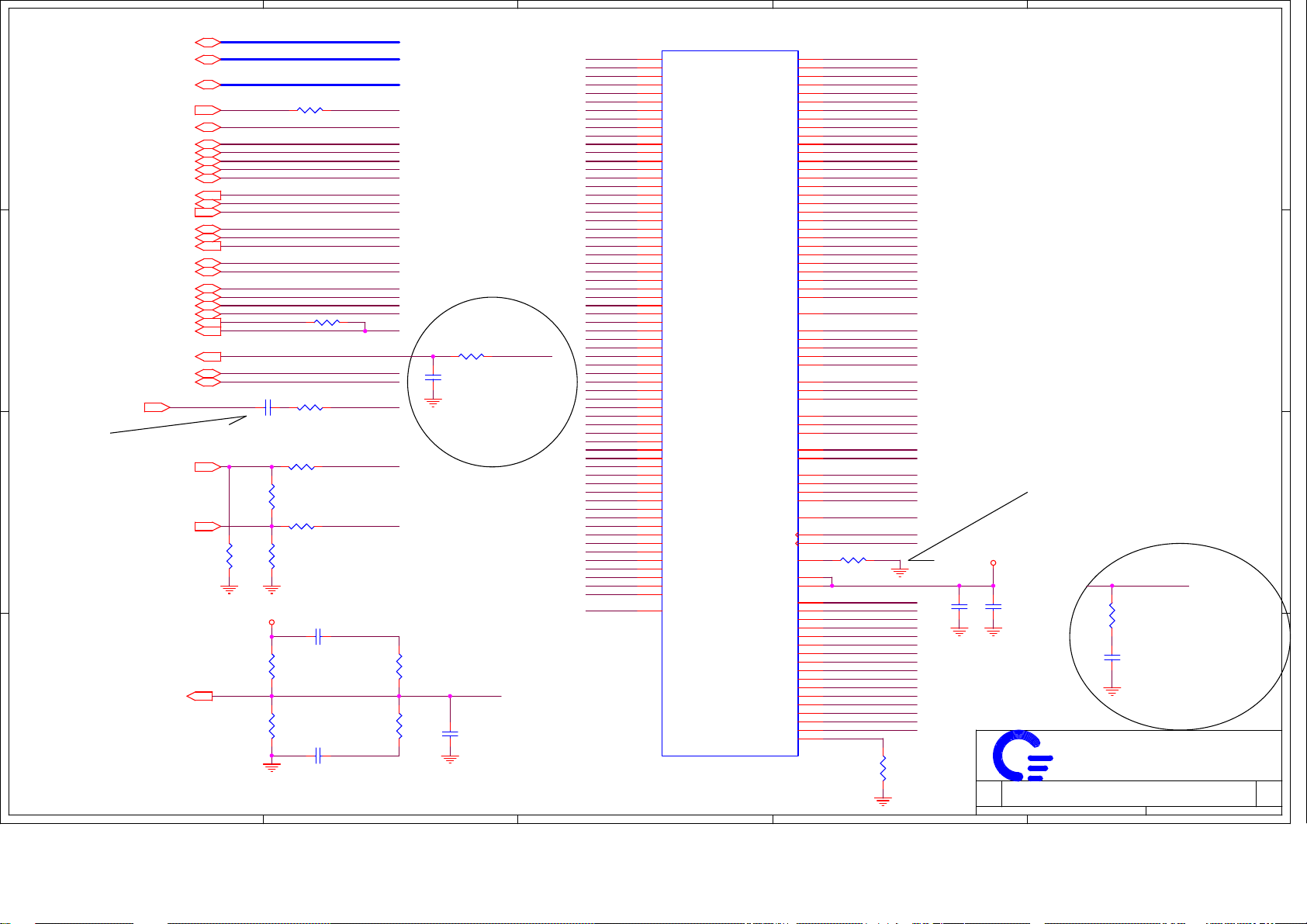

Ramp_0704: Update

A A

+3V

C237

10P

R399

R400

330

R402 *0

SUSA#[12,18,25]

PCI_STP#[12]

CPU_STP#[12]

VTT_PWRGD#[5]

B B

BSEL0[4]

+3V

+3V

+3V

C C

+3V

+3V

C23910U/25V_1206

C241

0.1u_0402

C275

0.1u_0402

C959

0.1u_0402

C2_0423: Add

Q114

2N7002E

R673 100K

3

Q115

2N7002E

3

2

2

ICH_SMCLK[12,37]

D D

ICH_SMDATA[12,37]

12V

1

330

BK2125HM471

L25

BK2125HM471

L28

BK2125HM471

C242

0.1u_0402

BK2125HM471

C88110U/25V_1206

BK2125HM471

1

1

R124

10K

CK_VDD_REF

C250

1000P

L105

L118

L29

10U/25V_1206

+3V

+3V

2

R671

10K

CK_SMCLK

R672

10K

CK_SMDATA

12

C236

10P

12

CK_SMCLK

CK_SMDATA

C256

0.1u_0402

CK_VDD_3

C268

1000P

CK_VDD_CPU

1000P

C252

CK_VDD_48MHZ

C264

0.1u_0402

CK_VDDA

C277

12

R116

2M

C246

0.1u_0402

C269

0.1u_0402

0.1u_0402

C254

R411 221_1%

R120 10K

C274

0.1u_0402

12

CLK_XIN

Y2

14.318MHz

CLK_XOUT

BSEL2

BSEL1

BSEL0

C244

0.1u_0402

C263

0.1u_0402

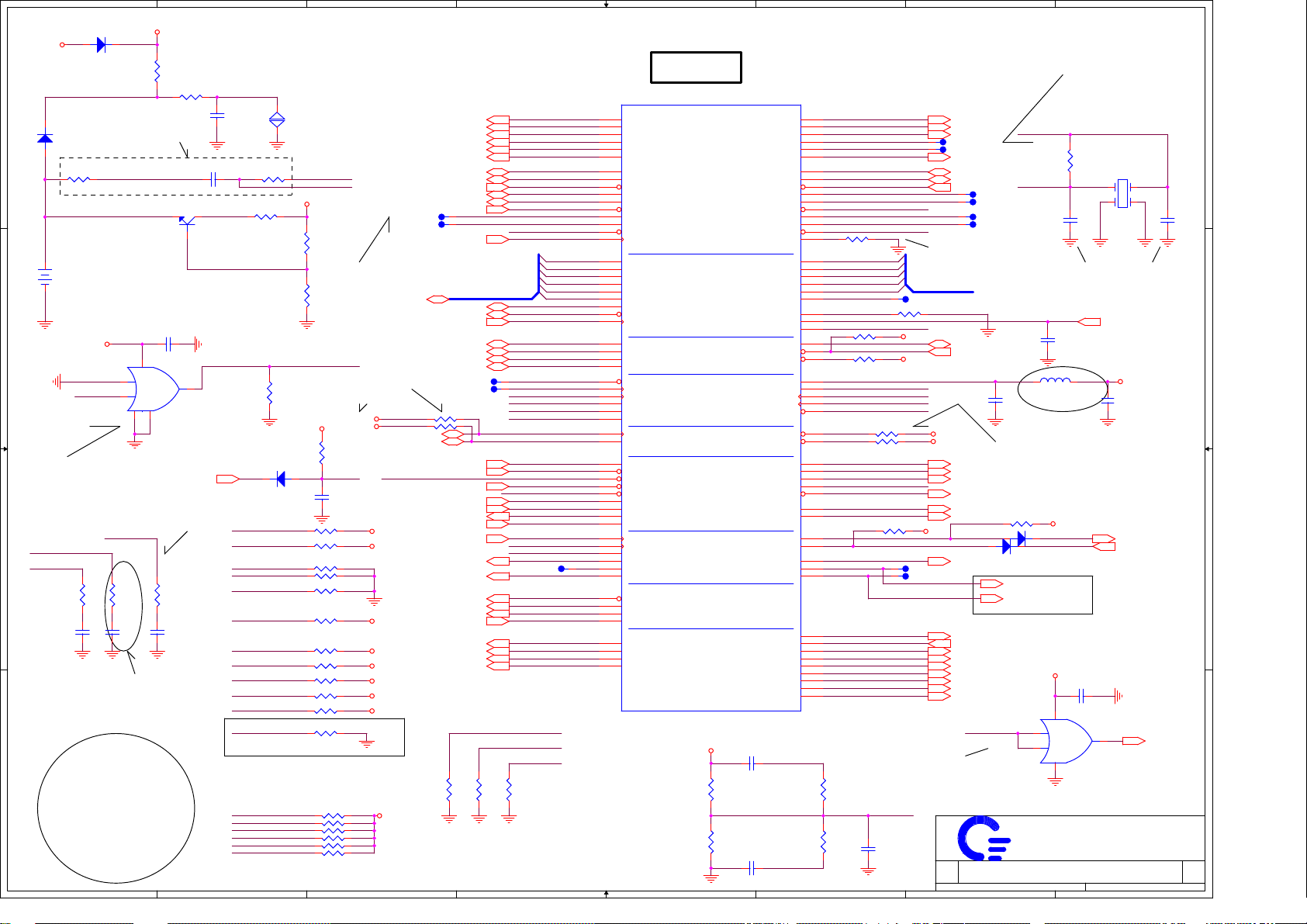

Clock Generator

U24

2

XTAL_IN

3

XTAL_OUT

25

PWR_DWN#

34

PCI_STP#

53

CPU_STP#

28

PWRGD#

30

SCLK

29

SDATA

40

SEL2

55

SEL1

54

SEL0

1

VDD_REF

8

VDD_PCI_1

14

VDD_PCI_2

19

VDD_3V66_1

32

VDD_3V66_2

46

VDD_CPU_1

50

37

42

43

26

27

VDD_CPU_2

VDD_48MHZ

IREF

MULT0

VDD_CORE

GND_CORE

0.1u_0402

C247

CLK_GND

FOR GMCH A3

ICS: ICS9250EG-38 *** Used in C2 test, P/N:AL009250K17

Cypress: W320-03X

3

CK-TITAN

GND_REF

GND_PCI_2

GND_3V66_1

GND_3V66_2

GND_PCI_1

4

1511203147

9

66B2/3V66_4

66B1/3V66_3

66B0/3V66_2

GND_48MHZ

GND_IREF

36

41

CLK_GND

REF

CPU0

CPU#0

CPU1

CPU#1

CPU2

CPU#2

3V66_0

3V66_1/VCH

66IN/3V66_5

PCI_F2

PCI_F1

PCI_F0

PCI6

PCI5

PCI4

PCI3

PCI2

PCI1

PCI0

48M_USB

48M_DOT

GND_CPU

4

56

52

51

49

48

45

44

33

35

24

23

22

21

7

6

5

18

17

16

13

12

10

39

38

CK-TITAN-A

CLK66_GBOUT

14M_S

T201 *PAD

T200 *PAD

CLK66_GBOUT

CLK66_ICHHUB_S

CLK66_GBIN_S

CLK66_AGP_S

PCLK_ICH_S

PCLK_CPUAPIC_S

T198 *PAD

PCLK_SIO_S

PCLK_PCIC_S

PCLK_AUD_S

PCLK_MINI2_S

PCLK_MINI_S

PCLK_DK_S

T199

CLK48_USB_S

CLK48_DREF_S

R128

33

12

C267

5P

R395 33

R391 33

*PAD

CLK_GND

CLK_GND

R434 33

R431 33

R417 33

R398 33

R118 33

R121 33

R413 33

R410 33

R409 33

R119 33

R401 33

R414 33

R426 22

0_0805

R668

0_0805

R664

0_0805

R642

0_0805

R643

5

C749

C744

*10P

*10P

C768

C778

*10P

*10P

C2_0423: Add

Add

Place near destination

C902

C903

C904

*10P

*10P

C782

C780

C762

*10P

*10P

*10P

PROJECT : RT2.0

Quanta Computer Inc.

CLOCK GENERATOR

C253

*10P

R649 240K

C755

*10P

6

C767

*10P

C900

*10P

C257

*10P

C901

*10P

*10P

0322: Add for QS stepping.

C750

C243

C756

*10P

C775

*10P

*10P

*10P

Size Document Number Rev

Custom

Date: Sheet of

7

C905

*10P

14M_SIO [31]

14M_ICH [12]

HCLK_CPU [4]

HCLK_CPU# [4]

HCLK_GMCH [6]

HCLK_GMCH# [6]

HCLK_ITP [43]

HCLK_ITP# [43]

CLK66_GBOUT [6]

CLK66_ICHHUB [12]BSEL1[4]

CLK66_GBIN [6]

CLK66_AGP [18]

PCLK_ICH [11]

PCLK_CPUAPIC [4]

PCLK_SIO [31]

PCLK_PCIC [28]

PCLK_AUD [25]

PCLK_MINI2 [51]

PCLK_MINI [30]

PCLK_DK [41]

CLK48_USB [12]

CLK48_DREF [8]

3 57Tuesday, September 11, 2001

8

2B

A

B

C

D

E

1617VCC

16

13

5

1

3

4

10K

R85

137_1%

R418

61.9_1%

HD#[0..63]

NC1

NC2

NC3

NC4

NC5

DXP

DXN

VCCT

+1.5V

D

+3V

15

STBY#

ALERT#

ADD1

ADD0

678910

R94

26.7_1%

HD#[0..63] [6]

R438

200_0805

2

SMBC

SMBD

R108

56.2_1%

U63

MAX1617A

VCC

14

12

11

GND1

GND2

DBSY# [6]

DRDY# [6]

PCLK_CPUAPIC [3]

CPURST# [6]

CPUINIT# [11]

HCLK_CPU [3]

HCLK_CPU# [3]

Size Document Number Rev

Custom

Date: Sheet of

+3V+3V

R436

R437

10K

10K

KBSMCLK [36]

KBSMDAT[36]

PROJECT : RT2.0

Quanta Computer Inc.

TUALATIN CPU(HOST BUS)-1

E

1A

4 57Tuesday, September 11, 2001

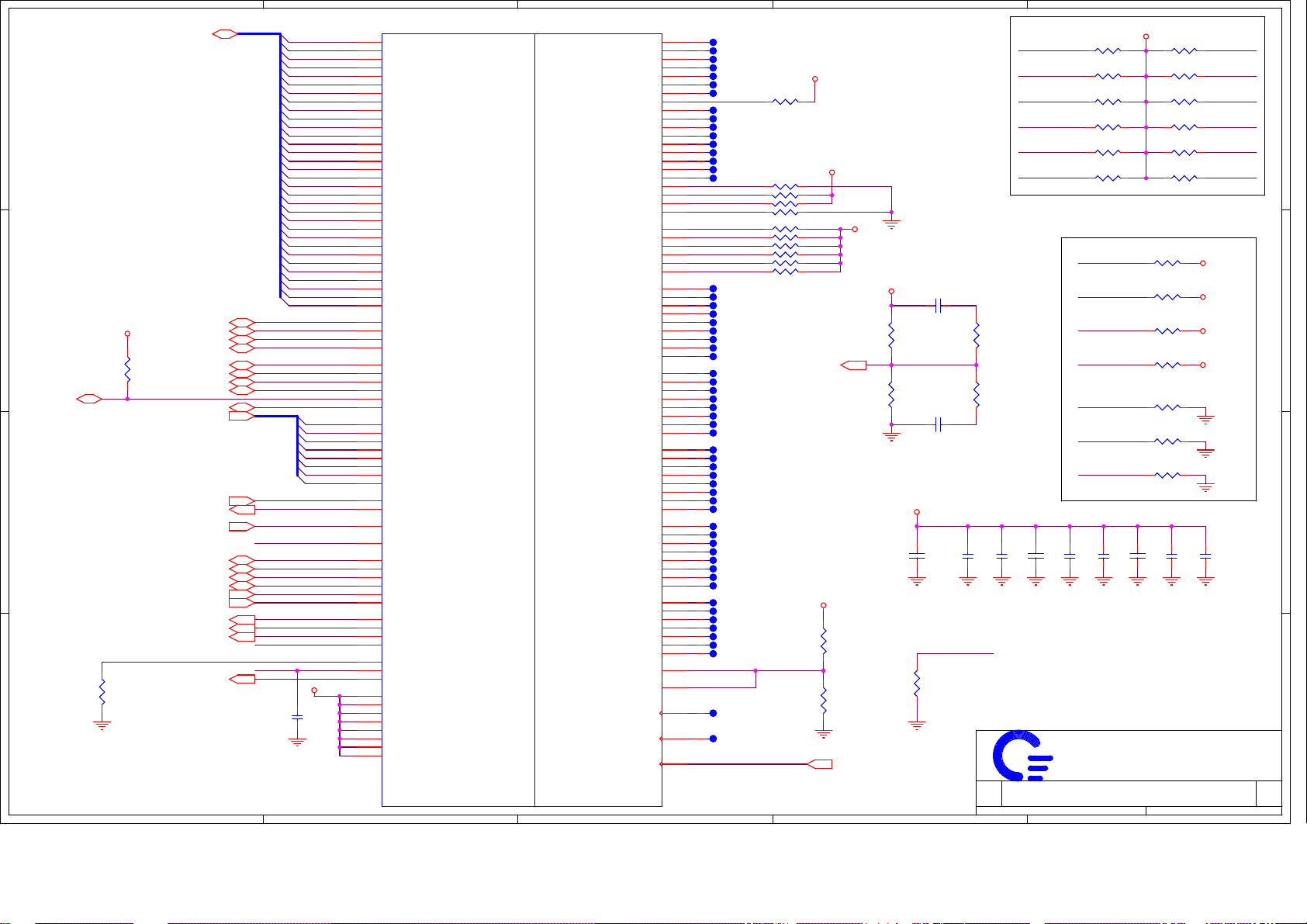

+1.5V

R433 1.5K

R115 10

+1.8V+1.5V

R131

1.5K

HA#[3..31]

ITP_TRST#[43]

ITP_PREQ#[43]

ITP_PRDY#[43]

H_DPSLP#[11,47]

HREQ#0[6]

HREQ#1[6]

HREQ#2[6]

HREQ#3[6]

HREQ#4[6]

HLOCK#[6]

DEFER#[6]

HTRDY#[6]

IGNNE#[11]

ITP_TDO[43]

ITP_TDI[43]

ITP_TMS[43]

ITP_TCK[43]

STPCLK#[11]

T171

T172

T174

T176

T186

ADS#[6]

T191

T189

T188

T173

T163

BPRI#[6]

BNR#[6]

HIT#[6]

HITM#[6]

T166

T168

T165

T167

RS#0[6]

RS#1[6]

RS#2[6]

T181

A20M#[11]

SMI#[11]

BSEL0[3]

BSEL1[3]

INTR[11]

NMI[11]

THERMDA

THERMDC

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

C255

2200P

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

IERR#

BREQ#0

FERR#

ITP_TDO

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_PREQ#

ITP_PRDY#

U22A

K1

A3#

J1

A4#

G2

A5#

K3

A6#

J2

A7#

H3

A8#

G1

A9#

A3

A10#

J3

A11#

H1

A12#

D3

A13#

F3

A14#

G3

A15#

C2

A16#

B5

A17#

B11

A18#

C6

A19#

B9

A20#

B7

A21#

C8

A22#

A8

A23#

A10

A24#

B3

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

RP#

ADS#

AERR#

AP0#

AP1#

BERR#

BINIT#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BP2#

BP3#

BPM0#

BPM1#

TRDY#

RS0#

RS1#

RS2#

RSP#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TDO

TDI

TMS

TRST#

TCK

PREQ#

PRDY#

BSEL0

BSEL1

INTR/LINT0

NMI/LINT1

STPCLK#

DPSLP#

THERMDA

THERMDC

REQUEST

PHASE

SIGNALS

A13

A9

C3

C12

C10

A6

A15

A14

B13

A12

R1

L3

T1

U1

L1

T4

AA3

W2

AB3

P3

C14

AF23

AF4

A7

R2

L2

V3

AA2

U2

T3

AF22

AE20

AD22

AD21

W1

Y3

V1

U3

M5

AC3

AF6

AD9

AB4

AD3

AD11

AD7

AF7

AF15

AD10

AF19

AE22

AE12

AF10

AD15

AE14

AE4

AF8

AF13

AF14

B

TUALATIN

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

TUALATIN_3

1 OF 3

DATA

PHASE

SIGNALS

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBSY#

DRDY#

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

PICCLK

PICD1

PICD0

FLUSH#

RESET#

INIT#

BCLK

BCLK#

EDGECTRLP

C

A16

B17

A17

D23

B19

C20

C16

A20

A22

A19

A23

A24

C18

D24

B24

A18

E23

B21

B23

E26

C24

F24

D25

E24

B25

G24

H24

F26

L24

H25

C26

K24

G26

K25

J24

K26

F25

N26

J26

M24

U26

P25

L26

R24

R26

M25

V25

T24

M26

P24

AA26

T26

U24

Y25

W26

V26

AB25

T25

Y24

W24

Y26

AB24

AA24

V24

W3

Y1

AE24

AD25

AE25

AC24

AF24

AD26

AC26

AD24

AF20

AD17

AD19

AF5

B15

AE6

AC1

AD1

AF16

FLUSH#

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

T160

T155

T156

T158

T161

T154

T153

T159

R425 150

HCLK_CPU_R

HCLK_CPU#_R

EDGCTRLP

PICD1

PICD0

R95

110_1%

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

*PAD

R403

33

R404

33

+3V

C785

0.1u

THERMDA

THERMDC

R435 10K

R457

PCLK_CPUAPIC_1

R86 150

R93 150

+1.5V

R419

475_1%

R420

61.9_1%

HA#[3..31][6]

4 4

3 3

2 2

PWRGD_CPU[12]

1 133MHZ

1

1 1

R127

1.5K

FERR#[11]

STSEM BUS FREQUENCYBSEL[1:0]

100MHZ1 0

A

A

VAGTL_VCCA

C278

+

47u/6.3V_7343

VAGTL_VSSA

C226

C270

C225

0.1u_0402

0.1u_0402

0.1u_0402

CPUPERF#[12]

R117 1K

VCCT

R424 1K

VCCT

R129 1K

R132 1K

VCCT

C947

0.1u_0402

C1_0328: Add

C203

C593

1u_0805

C931

0.1u_0402

C936

0.1u_0402

C202

1u_0805

C233

1u_0805

C594

*1u

C930

0.1u_0402

C935

0.1u_0402

R134

14_1%

1u_0805

C784

0.1u_0402

N3

N2

A4

A21

N1

AF9

AF21

AA1

AB26

H26

AD5

AF12

L5

AE16

E2

AF11

M1

Y4

AD16

D6

D8

D10

D12

D14

D16

W21

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

D18

D20

D22

E11

E13

E15

E17

E19

E21

F10

F12

F14

F16

F18

F20

F22

G21

H22

K22

L21

M22

N21

P22

R21

T22

U21

V22

Y22

AA5

AA7

AA9

E5

E7

E9

F6

F8

G5

H6

J5

J21

K6

M6

N5

P6

R5

T6

U5

V6

W5

Y6

VTT

C786

VAGTLREF

R101

1K_1%

C759

C758

0.1u_0402

0.1u_0402

VTT

C946

0.1u_0402

C136

150u/6.3V_7343

C218

C726

1u_0805

1u_0805

C765

C766

*1u

*1u

1 2

L26

4.7uH

C174

0.1u_0402

R100

2K_1%

CMOSREF

RTTIMPEDP

R439

56.2_1%

C710

C273

1u_0805

1u_0805

C595

*1u

*1u

VCCT

VCCT

4 4

+1.5V

R406

1K_1%

R405

2K_1%

VCCT

VCCT

C272

1u_0805

C763

*1u

C945

0.1u_0402

VCCT

+

C271

1u_0805

C764

*1u

C944

3 3

0.1u_0402

2 2

assembly if breaket not sssembly.

VCCT

C927

C928

0.1u_0402

0.1u_0402

VCCT

1 1

C933

C932

0.1u_0402

0.1u_0402

C929

0.1u_0402

C934

0.1u_0402

Add

A

U22B

VCCA

VSSA

PLL ANALOG VOLTAGE

VREF0

VREF1

VREF2

VREF3

VREF4

VREF5

VREF6

VREF7

CMOSREF1

CMOSREF2

GHI#

RTTIMPEDP

TESTHI1

TESTHI2

TESTLO1

TESTLO2

NCTRL

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

B

TUALATIN

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

TUALATIN_3

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

AB22

AC5

AC7

AC9

AC11

AC13

B

C

VTT

C907

A25

VSS01

B2

VSS02

B4

VSS03

B6

VSS04

B8

VSS05

B10

VSS06

B12

VSS07

B14

VSS08

B16

VSS09

B18

VSS10

B20

VSS11

B22

VSS12

B26

VSS13

C23

VSS14

C25

VSS15

D2

VSS16

D4

VSS17

D7

VSS18

D9

VSS19

D11

VSS20

D13

VSS21

D15

VSS22

D17

VSS23

D19

VSS24

D21

VSS25

E8

VSS26

E10

VSS27

E12

VSS28

E14

VSS29

E16

VSS30

E18

VSS31

E20

VSS32

E22

VSS33

E25

VSS34

F2

VSS35

F4

VSS36

F5

VSS37

F7

VSS38

F9

VSS39

F11

VSS40

F13

VSS41

F15

VSS42

F17

VSS43

F19

VSS44

F21

VSS45

F23

VSS46

G6

VSS47

G22

VSS48

G25

VSS49

H2

VSS50

H4

VSS51

H21

VSS52

H23

VSS53

J6

VSS54

J22

VSS55

J25

VSS56

K2

VSS57

K4

VSS58

K5

VSS59

K21

VSS60

K23

VSS61

L6

VSS62

L22

VSS63

L25

VSS64

M2

VSS65

M3

VSS66

M4

VSS67

M21

VSS68

M23

VSS69

N6

VSS70

N22

VSS71

N25

VSS72

P2

VSS73

P21

VSS74

P23

VSS75

R4

VSS76

R6

VSS77

R22

VSS78

R25

VSS79

T2

VSS80

T5

VSS81

T21

VSS82

T23

VSS83

U4

VSS84

U6

VSS85

U22

VSS86

U25

VSS87

V2

VSS88

V5

VSS89

V21

VSS90

V23

VSS91

W4

VSS92

W6

VSS93

W22

VSS94

W25

VSS95

Y2

VSS96

Y5

VSS97

Y21

VSS98

Y23

VSS99

AA6

VSS100

VCC77

VCC78

VCC79

VCC80

AC15

AC17

AC19

AC21

C906

VTT

C914

VTT

VTT

VTT

C656

0.47u_X7R

VTT

C922

0.1u_0402

VTT

12

VTT_PWRGD#[3]

0.1u_0402

0.1u_0402

C686

0.47u_X7R

C706

0.47u_X7R

0.47u_X7R

C649

10u/10V_1206

VTT_PWRGD[47]

VRON[34]

0.1u_0402

C915

0.1u_0402

C680

0.47u_X7R

C705

0.47u_X7R

C655

C923

0.1u_0402

12

C675

0.47u_X7R

C704

0.47u_X7R

C654

0.47u_X7R

Add

C687

10u/10V_1206

VTT_PWRGD

VTT_PWRGD#

C

C908

C909

0.1u_0402

0.1u_0402

C918

C917

C916

0.1u_0402

C668

0.47u_X7R

C703

0.47u_X7R

0.47u_X7R

C653

C924

0.1u_0402

12

C662

10u/10V_1206

VCCT +3V

Q15

DTC144EU

0.1u_0402

C707

0.47u_X7R

C925

0.1u_0402

12

C678

10u/10V_1206

R84

1K

2

C688

0.47u_X7R

C702

0.47u_X7R

CPU_VID0[45]

CPU_VID1[45]

CPU_VID2[45]

CPU_VID3[45]

CPU_VID4[45]

+3V

1 3

0.1u_0402

C926

0.1u_0402

12

R76

10K

C910

0.1u_0402

C681

0.47u_X7R

C701

0.47u_X7R

C657

0.47u_X7R

C692

10u/10V_1206

D17

1SS355

C911

0.1u_0402

C919

0.1u_0402

C676

0.47u_X7R

C660

0.47u_X7R

12

C669

10u/10V_1206

2

21

C920

0.1u_0402

C670

0.47u_X7R

C659

0.47u_X7R

R130

1K

VTT_PWRGD

12

C719

10u/10V_1206

C89 0.1u_0402

5

U16

7SH04

3

+3V

R274

10K

C912

0.1u_0402

R423

1K

4

D

C921

0.1u_0402

C708

0.47u_X7R

C658

0.47u_X7R

R422

1K

12

C720

10u/10V_1206

D

C913

0.1u_0402

VCCT

+3V

R133

R421

1K

1K

12

C650

10u/10V_1206

+3V

C99 0.1u_0402

5

1

2

3

E

Add

U22C

A26

VCCT1

C5

VCCT2

C7

VCCT3

C9

VCCT4

C11

VCCT5

C13

VCCT6

C15

VCCT7

TUALATIN

VCCT8

VCCT9

VCCT10

VCCT11

VCCT12

VCCT13

VCCT14

VCCT15

VCCT16

VCCT17

VCCT18

VCCT19

VCCT20

VCCT21

VCCT22

VCCT23

VCCT24

VCCT25

VCCT26

VCCT27

VCCT28

VCCT29

VCCT30

VCCT31

VCCT32

VCCT33

VCCT34

VCCT35

VCCT36

VCCT37

VCCT38

VID0

VID1

VID2

VID3

VID4

VTTPWRGD

C677

10u/10V_1206

3 OF 3

POWER, GROUND AND NC

VID

TUALATIN_3

ON_BOARD_CORE_ON [47]

Size Document Number Rev

Custom

Date: Sheet of

Quanta Computer Inc.

TUALATIN CPU(POWER/NC)-2

W23

AA23

AC4

AC23

AD6

AD8

AD12

AD14

AD18

AD20

AE18

C17

C19

C21

G23

N23

R23

U23

AA4

AE3

AF1

AF2

AB1

AC2

AE2

AF3

D5

E4

E6

G4

J4

J23

L4

L23

V4

R3

E3

12

4

U18

TC7SH08FU

AA8

VSS101

AA10

VSS102

AA12

VSS103

AA14

VSS104

AA16

VSS105

AA18

VSS106

AA20

VSS107

AA22

VSS108

AA25

VSS109

AB2

VSS110

AB5

VSS111

AB7

VSS112

AB9

VSS113

AB11

VSS114

AB13

VSS115

AB15

VSS116

AB17

VSS117

AB19

VSS118

AB21

VSS119

AB23

VSS120

AC6

VSS121

AC8

VSS122

AC10

VSS123

AC12

VSS124

AC14

VSS125

AC16

VSS126

AC18

VSS127

AC20

VSS128

AC22

VSS129

AC25

VSS130

AD2

VSS131

AE1

VSS132

AE5

VSS133

AE7

VSS134

AE9

VSS135

AE11

VSS136

AE13

VSS137

AE15

VSS138

AE17

VSS139

AE19

VSS140

AE21

VSS141

AE23

VSS142

AE26

VSS143

AF25

VSS144

AF26

VSS145

H5

VSS146

A2

NC1

A5

NC2

A11

NC3

B1

NC4

C1

NC5

C4

NC6

C22

NC7

D1

NC8

D26

NC9

E1

NC10

F1

NC11

N4

NC12

N24

NC13

P1

NC14

P4

NC15

P5

NC16

P26

NC17

AD4

NC18

AD13

NC19

AD23

NC20

AE8

NC21

AE10

NC22

AF17

NC23

AF18

NC24

PROJECT : RT2.0

E

T190*PAD

T180*PAD

T177*PAD

T192*PAD

T193*PAD

T183*PAD

T164*PAD

T194*PAD

T151*PAD

T195*PAD

T196*PAD

T184*PAD

T157*PAD

T197*PAD

T185*PAD

T182*PAD

T152*PAD

T187*PAD

T175*PAD

T162*PAD

T179*PAD

T178*PAD

T170*PAD

T169*PAD

5 57Tuesday, September 11, 2001

3A

A

HL[0..10][12]

HD#[0..63][4]

HA#[3..31][4]

ITP_CPURST#[43]

CLK66_GBIN[3]

PCIRST#[11,16,18,25,28,30,31,41,51]

ADS#[4]

HREQ#0[4]

HREQ#1[4]

HREQ#2[4]

HREQ#3[4]

HREQ#4[4]

BPRI#[4]

BNR#[4]

HLOCK#[4]

HIT#[4]

HITM#[4]

DEFER#[4]

DBSY#[4]

DRDY#[4]

HTRDY#[4]

RS#0[4]

RS#1[4]

RS#2[4]

CPURST#[4]

HLSTRB[12]

HLSTRB#[12]

CLK66_GBOUT

4 4

3 3

CLK66_GBOUT[3]

0322: Change

HCLK_GMCH[3]

2 2

1 1

HCLK_GMCH#[3]

VHUBREF[12]

A

HL[0..10]

HD#[0..63]

HA#[3..31]

R231 0

ADS#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

BPRI#

BNR#

HLOCK#

HIT#

HITM#

DEFER#

DBSY#

DRDY#

HTRDY#

RS#0

RS#1

RS#2

CPURST#

HLSTRB

HLSTRB#

R25

475_1%

R19

61.9_1%

HUBREF = 0.5 * VCC1_8

Place divider in the middle of

the bus

CLK66_GBIN

C430

0.01u

R28

61.9_1%

+1.8V

R298

301_1%

R307

301_1%

R270 0

R201

49.9_1%

R18

33

R24

33

C582

*470P

C588

0.1u_0402

CLK66_GBOUT_S

HCLK_GMCH_R

HCLK_GMCH#_R

HUBREF_CV

HUBREF_CG

PCIRST#_1

B

B

R315

*56.2_1%

R321

0

R639

C899

*10P

0

VHUBREF

C568

0.01u

CLK66_GBIN_1

EMI

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

PCIRST#_1

AA3

AD3

AB4

AB5

AA4

AA1

AA6

AB1

AC4

AA2

AB3

AD2

AD1

AC2

AB6

AC6

AC1

AF3

AD4

AD6

AC3

AH3

AE5

AE3

AG2

AF4

AF2

AJ3

AE4

AG1

AE1

AG4

AH4

AG3

AF1

AB24

C

W6

W5

W4

W3

W1

C

U4

P1

U2

U6

R1

N3

V4

P3

R3

U1

V6

T3

P2

V3

R2

T1

U3

Y4

V1

Y1

Y6

V2

Y3

Y2

GMCH3-M

U17A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

RESET#

GMCH-M

HOST BUS INTERFACE (Processor

System Bus)

GTL_RCOMP

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

BPRI#

BNR#

HLOCK#

HIT#

HITM#

DEFER#

DBSY#

DRDY#

HTRDY#

RS0#

RS1#

RS2#

CPURST#

HTCLK

HTCLK#

GTL_REFA

GTL_REFB

GBOUT

GBIN

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HLREF

HLSTRB

HLSTRB#

HL_RCOMP

H2

E3

G3

N4

M6

F1

F2

J3

F3

P6

G1

N5

H1

P4

T4

M2

J2

L2

R4

K1

L3

L1

J1

N1

T5

H3

M3

M1

K3

C1

K6

M4

K5

K4

L6

L4

E1

J6

D3

D1

J4

G5

F4

G4

H6

H4

G6

R6

AJ4

AH5

C2

J7

AA7

AD24

AG26

G26

H28

H29

H27

F29

F27

E29

E28

G25

G27

H26

H24

G29

F28

J23

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

ADS#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

BPRI#

BNR#

HLOCK#

HIT#

HITM#

DEFER#

DBSY#

DRDY#

HTRDY#

RS#0

RS#1

RS#2

CPURST#

HCLK_GMCH_R

HCLK_GMCH#_R

R324

80.6_1%_0805

CLK66_GBOUT_S

CLK66_GBIN_1

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

VHUBREF

HLSTRB

HLSTRB#

HL_RCOMP

D

R300

54.9_1%

D

E

B2_0313: Change to 0805

VAGTLREF

CLK66_GBIN_1

C561

C460

0.1u_0402

0.1u_0402

Size Document Number Rev

B

Date: Sheet of

Quanta Computer Inc.

GMCH-M (HOST)-1

R665

C2_0423: Add,

*22

reserved

12

C960

Close to GMCH

*5P

PROJECT : RT2.0

E

2B

6 57Tuesday, September 11, 2001

A

B

C

D

E

GMCH-M

CS0#

CS1#

CS2#

CS3#

4 4

3 3

2 2

CLK_SDRAM0[10]

CLK_SDRAM1[10]

CLK_SDRAM2[10]

CLK_SDRAM3[10]

MD[0..63][10]

MA[0..12][10]

CS0#[10]

CS1#[10]

CS2#[10]

CS3#[10]

DQM0[10]

DQM1[10]

DQM2[10]

DQM3[10]

DQM4[10]

DQM5[10]

DQM6[10]

DQM7[10]

BMWEA#[10]

SRASA#[10]

SCASA#[10]

BS0[10]

BS1[10]

CKE0[10]

CKE1[10]

CKE2[10]

CKE3[10]

C965

*10P

MD[0..63]

MA[0..12]

C961

*10P

RP1

8P4R_10

RP2

8P4R_10

RP3

8P4R_10

R346 10

R347 10

R348 10

C962

C966

*10P

*10P

MA0

7 8

MA1

5

MA2

3

MA3

1

MA4

7 8

MA5

5

MA6

3

MA7

1

MA8

7 8

MA9

5

MA10

3

MA11

1

MA12

R349 10

R326 10

R350 10

R332 10

R351

10

SM_MA0

SM_MA1

6

SM_MA2

4

SM_MA3

2

SM_MA4

SM_MA5

6

SM_MA6

4

SM_MA7

2

SM_MA8

SM_MA9

6

SM_MA10

4

SM_MA11

2

SM_MA12

CS0#

CS1#

CS2#

CS3#

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

BMWEA#_1

SRASA#_1

SCASA#_1

BS0

BS1

CKE0

CKE1

CKE2

CKE3

CLK_SDRAM0_S

CLK_SDRAM1_S

CLK_SDRAM2_S

CLK_SDRAM3_S

3VSUS

R353

249_1%

R354

49.9_1%

C2_0423,24:

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

BMWEA#_1

SRASA#_1

SCASA#_1

BS0

BS1

CKE0

CKE1

CKE2

CKE3

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

CLK_SDRAM0_S

CLK_SDRAM1_S

CLK_SDRAM2_S

CLK_SDRAM3_S

T137*PAD

T140*PAD

T139*PAD

T144*PAD

R352 27.4_1%

SM_REF

C622

0.1u_0402

E17

F16

D16

D15

F18

D18

D13

D12

E18

F17

F14

F13

A21

C20

D19

B16

C16

A13

C9

C13

A9

A20

B20

B19

C19

A18

A19

C17

C18

B17

A17

A16

C15

C14

A15

B2

B14

A3

F20

E20

F12

E11

F6

E5

F24

GMCH3-M

U17B

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_DQM0

SM_DQM1

SM_DQM2

SM_DQM3

SM_DQM4

SM_DQM5

SM_DQM6

SM_DQM7

SM_WE#

SM_RAS#

SM_CAS#

SM_BA0

SM_BA1

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

SM_CLK0

SM_CLK1

SM_CLK2

SM_CLK3

NC

NC

NC

NC

SM_RCOMP

SM_REFA

SM_REFB

A3

DRAM INTERFACE

SM_MD0

SM_MD1

SM_MD2

SM_MD3

SM_MD4

SM_MD5

SM_MD6

SM_MD7

SM_MD8

SM_MD9

SM_MD10

SM_MD11

SM_MD12

SM_MD13

SM_MD14

SM_MD15

SM_MD16

SM_MD17

SM_MD18

SM_MD19

SM_MD20

SM_MD21

SM_MD22

SM_MD23

SM_MD24

SM_MD25

SM_MD26

SM_MD27

SM_MD28

SM_MD29

SM_MD30

SM_MD31

SM_MD32

SM_MD33

SM_MD34

SM_MD35

SM_MD36

SM_MD37

SM_MD38

SM_MD39

SM_MD40

SM_MD41

SM_MD42

SM_MD43

SM_MD44

SM_MD45

SM_MD46

SM_MD47

SM_MD48

SM_MD49

SM_MD50

SM_MD51

SM_MD52

SM_MD53

SM_MD54

SM_MD55

SM_MD56

SM_MD57

SM_MD58

SM_MD59

SM_MD60

SM_MD61

SM_MD62

SM_MD63

SM_RCLK

SM_OCLK

D29

C29

D27

C27

A27

B26

E24

C25

E23

B25

C23

F22

B23

C22

E21

B22

C12

D10

C11

A10

C10

C8

A7

E9

C7

E8

A5

F8

C5

D6

B4

C4

E27

C28

B28

E26

C26

D25

A26

D24

F23

A25

G22

D22

A23

F21

D21

A22

F11

A11

B11

F10

B10

B8

D9

B7

F9

A6

C6

D7

B5

E6

A4

D4

C24

A24

SM_CLK

Add,

butreserved

1 1

Close to GMCH

UPDATE VER0.7A BY INTEL

LAYOUT 2'' AND 6'' FOR EACH LINE

A

B

C

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

12

C615

*22P

D

CHECK LAYOUT GUIDE

DEL R345(56.2_1%)

Length: 150 +- 50 MIL

Size Document Number Rev

B

Date: Sheet of

PROJECT : RT2.0

Quanta Computer Inc.

GMCH-M (DRAM)-2

7 57Tuesday, September 11, 2001

E

2A

A

GAD[0..31][18]

4 4

3 3

GPAR[18]

2 2

1 1

R275

4.7K

+1.5V

R289

54.9_1%

A

GCBE0#[18]

GCBE1#[18]

GCBE2#[18]

GCBE3#[18]

GFRAME#[18]

GIRDY#[18]

GTRDY#[18]

GDEVSEL#[18]

GSTOP#[18]

SBA[0..7][18]

GREQ#[18]

GGNT#[18]

RBF#[18]

AD_STBA[18]

AD_STBA#[18]

AD_STBB[18]

AD_STBB#[18]

SB_STB[18]

SB_STB#[18]

ST0[18]

ST1[18]

ST2[18]

AGP_BUSY#[12,18]

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

PIPE#

WBF#

GMCH_GRCOMP

VAGPREF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

+1.5V

C131

0.1u_0402

GMCH3-M

B

U17C

J29

G_AD0/DVOB_HS

J28

G_AD1/DVOB_VS

K26

G_AD2/DVOB_D1

K25

G_AD3/DVOB_D0

L26

G_AD4/DVOB_D3

J27

G_AD5/DVOB_D2

K29

G_AD6/DVOB_D5

K27

G_AD7/DVOB_D4

M29

G_AD8/DVOB_D6

M28

G_AD9/DVOB_D9

L24

G_AD10/DVOB_D8

M27

G_AD11/DVOB_D11

N29

G_AD12/DVOB_D10

M25

G_AD13/DVOBC_CLKINT

N26

G_AD14/DVOB_FLD/STL

N27

G_AD15

R25

G_AD16/DVOC_VSYNC

R24

G_AD17/DVOC_HSYNC

T29

G_AD18/DVOC_BLANK#

T27

G_AD19/DVOC_D0

T26

G_AD20/DVOC_D1

U27

G_AD21/DVOC_D2

V27

G_AD22/DVOC_D3

V28

G_AD23/DVOC_D4

U26

G_AD24/DVOC_D7

V29

G_AD25/DVOC_D6

W29

G_AD26/DVOC_D9

V25

G_AD27/DVOC_D8

W26

G_AD28/DVOC_D11

W25

G_AD29/DVOC_D10

W27

G_AD30/DVOBC_INTR#/DPMS_CLK

Y29

G_AD31/DVOC_FLD/STL

L27

G_CBE0#/DVOB_D7

P29

G_CBE1#/DVOB_BLANK#

R27

G_CBE2#/ZV_VS

T25

G_CBE3#/DVOC_D5

R29

G_FRAME#/M_DDC2_DATA

P26

G_IRDY#/M_I2C_CLK

P27

G_TRDY#/M_DDC2_CLK

R28

G_DEVSEL#/M_I2C_DATA

P28

G_PAR/DVO_DETECT

N25

G_STOP#

AA29

SBA0/ZV_D8

AA24

SBA1/ZV_D7

AA25

SBA2/ZV_D6

Y24

SBA3/ZV_D5

Y27

SBA4/ZV_D2

Y26

SBA5/ZV_D1

W24

SBA6/ZV_D0

Y28

SBA7/ZV_HREF

AC27

G_REQ#/ZV_CLK

AD29

G_GNT#/ZV_D15

AB25

RBF#/ZV_D11

AB26

PIPE#/ZV_D10

L29

AD_STB0/DVOB_CLK

L28

AD_STB0#/DVOB_CLK#

U29

AD_STB1/DVOC_CLK

U28

AD_STB1#/DVOC_CLK#

AA27

SB_STB/ZV_D4

AA28

SB_STB#/ZV_D3

AC28

ST0/ZV_D14

AC29

ST1/ZV_D13

AB27

ST2/ZV_D12

AB29

WBF#/ZV_D9

K24

AGP_RCOMP/DVOBC_RCOMP

J25

AGPREF

AC24

AGP_BUSY#

L23

VCCAGP_1

U24

VCCAGP_2

J26

VCCAGP_3

M26

VCCAGP_4

R26

VCCAGP_5

V26

VCCAGP_6

AA26

VCCAGP_7

AA23

VCCAGP_8

B

GMCH-M

AGP INTERFACE

VIDEO INTERFACE

DVOA_CLK#

DVOA_CLK

DVOA_D0

DVOA_D1

DVOA_D2

DVOA_D3

DVOA_D4

DVOA_D5

DVOA_D6

DVOA_D7

DVOA_D8

DVOA_D9

DVOA_D10

DVOA_D11

DVOA_HSYNC

DVOA_VSYNC

DVOA_BLANK#

DVOA_RCOMP

DVOA_INTR#

DVOA_CLKINT

DVOA_FLD/STL

DDC1_CLK

DDC1_DATA

I2C_CLK

I2C_DATA

DDC2_CLK

DDC2_DATA

RED

GREEN

BLUE

VSYNC

HSYNC

REFSET

RED#

GREEN#

BLUE#

DQ_A0

DQ_A1

DQ_A2

DQ_A3

DQ_A4

DQ_A5

DQ_A6

DQ_A7

DQ_B0

DQ_B1

DQ_B2

DQ_B3

DQ_B4

DQ_B5

DQ_B6

DQ_B7

RQ0

RQ1

RQ2

RQ3

RQ4

RQ5

RQ6

RQ7

CTM

CTM#

CFM

CFM#

CMD

SCK

RAM_REFA

RAM_REFB

GM_GCLK

GM_RCLK

DREF_CLK

C

SIO

C

AG24

AJ24

AJ22

AH22

AG22

AJ23

AH23

AG23

AE23

AE24

AJ25

AH25

AG25

AJ26

AF22

AF23

AD21

AC22

AE21

AD20