Page 1

FILE NO.

SERVICE MANUAL

PH-DTA300M

(DE)

Audio System

R

CONTENTS

Laser Beam Safety Precaution ........................................1

IC Block............................................................................1,2,8

Tuner Adjustment.............................................................2

Wiring Connection............................................................3

Exploded View (Cabinet & Chassis) ................................4

Parts List ..........................................................................5

Block Diagram..................................................................11

Schematic Diagram (MAIN) .............................................12

Schematic Diagram (CD MAIN) .......................................14

Wiring Diagram (MAIN and TACT SW A,B) ..................... 16

Wiring Diagram (CD)........................................................18

Wiring Diagram (Power, Ant, Key, Led 1, 2, Phone and

Motor)...................................................19

Wiring Diagram (Display) .................................................20

REMOTECONTROLLERRB-DTA300M

PRODUCT CODE No.

129 668 07

REFERENCE No.

SM5810433

Page 2

LASER BEAM SAFETY PRECAUTION

• Pickup that emits a laser beam is used on this CD section.

CAUTION :

USE OF CONTROLS OR ADJUSTMENTS OR

PERFORMANCE OF PROCEDURES OTHER

THAN THOSE SPECIFIED HEREIN MAY RESULT

IN HAZARDOUS RADIATION EXPOSURE.

LASER OUTPUT................ 0.6 mW Max. (CW)

WAVE LENGTH ................. 790 nm

IC BLOCK DIAGRAM & DESCRIPTION

IC803 TA2092N (Power Driver)

CAUTION – INVISIBLE LASER RADIATION WHEN OPEN AND

INTERLOCKS DEFEATED. AVOID EXPOSURE TO BEAM.

ADVARSEL – USYNLIG LASER STRÅLING VED ÅBNING, NÅR

SIKKERHEDSAFBRYDERE ER UDE AF FUNKTION, UNDGÅ UDS ÆTTELSE

FOR STRÅLING.

VARNING – OSYNLIG LASER STRÅLNING NÄR DENNA DEL ÄR ÖPPNAD

OCH SPÄRR ÄR URKOPPLAD. STRÅLEN ÄR FARLIG.

VORSICHT – UNSICHTBARE LASERSTRAHLUNG TRITT AUS, WENN

DECKEL GEÖFFNET UND WENN SICHERHEITSVERRIEGELUNG

ÜBERBRÜCKT IST. NICHT, DEM STRAHL AUSSETZEN.

VARO – AVATTAESSA JA SUOJALUKITUS OHITETTAESSA OLET ALTTIINA

NÄKYMÄTTÖMÄLLE LASERSÄTEILYLLE. ÄLÄ KATSO SÄTEESEEN.

TERMINAL

NO.

1

2

3

4

5

6

7

SYMBOL

PW GND

OUT(-)1

CC1

PV

OUT(+)1

V

IN1

V

RI

V

CI

PW GND

CC4

PV

IN4

V

CC1

SV

SGND

IN3

V

CC3

PV

PW GND

24 23 22 21 20 19 18 17 16 15 14 13

123456789101112

VR1V

C1

IN2

V

TERMINAL

NO.

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

CC2

PV

SYMBOL

V

IN2

OUT(+)2

PV

OUT(-)2

PW GND

PW GND

OUT(-)3

PV

OUT(+)3

V

IN3

S GND

S V

V

IN4

OUT(+)4

PV

OUT(-)4

PW GND

PW GND

CC2

CC3

CC

CC4

PW GND

2413121

CC1

PV

IN1

V

- 1 -

FUNCTION

Input for CH2

Non-inverted output for CH2

Supply terminal of output stage for CH2

Inverted output for CH2

Power GND

Power GND

Inverted output for CH3

Supply terminal of output stage for CH3

Non-inverted output for CH3

Input for CH3

Supply terminal of small signal GND

Small signal GND

Input for CH4

Non-inverted output for CH4

Supply terminal of output stage for CH4

Inverted output for CH4

Power GND

Page 3

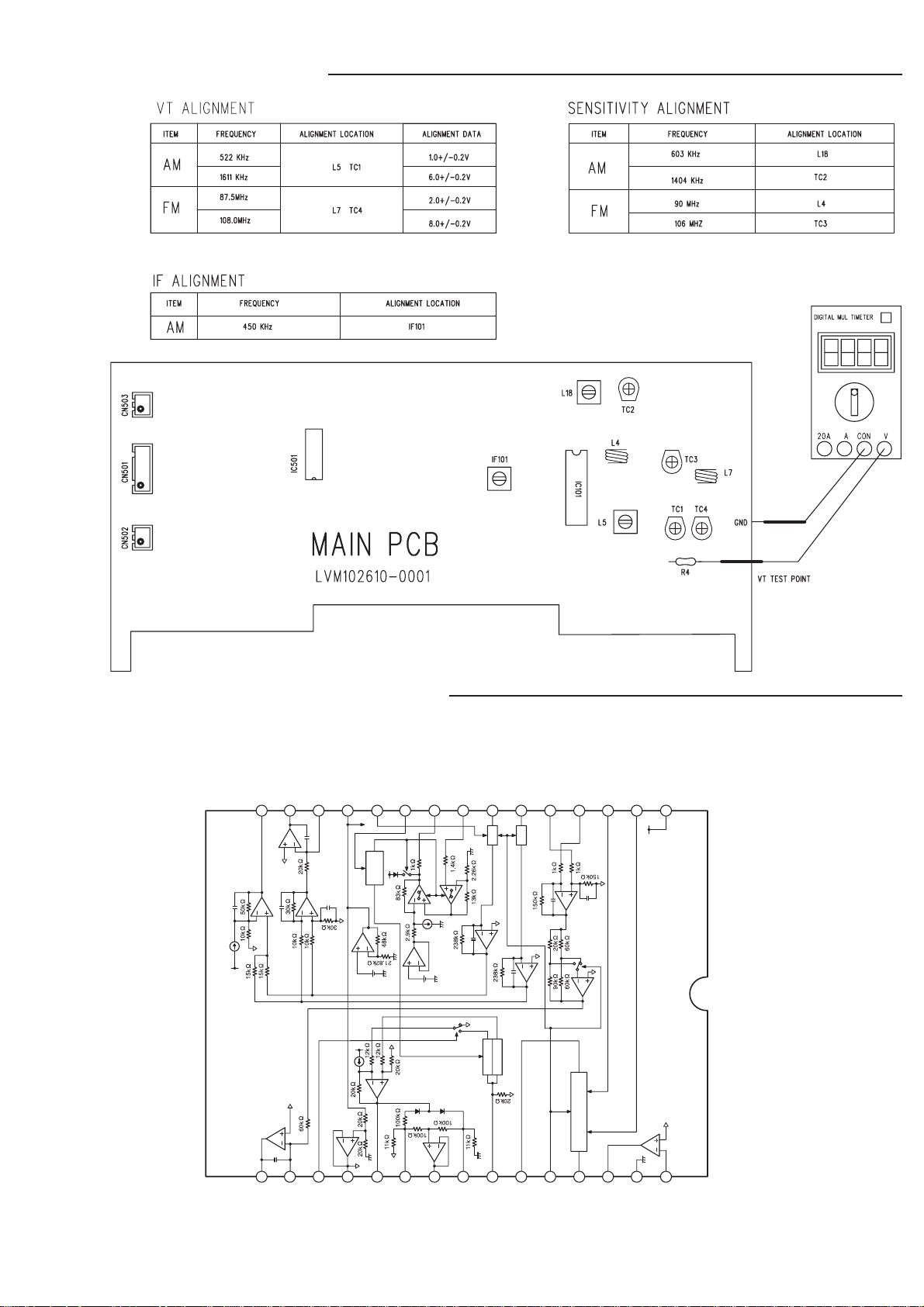

TUNER ADJUSTMENTS

16

17

18

FEO

FEN

SEB

19VRO

20RFRP

21BTC

22RFCT

23PKC

24RFRPIN

25RFGO

26GVSW

27AGCIN

28RFO

29GND

30RFN2

15

14

13

SBAD

TEO

TEN

12 2VRO

11 TEB

10 SEL

9 LDO

8 MDI

7 TNI

6 TPI

5 FPI

4 FNI

3 GMAD

2 RFGC

1 Vcc

AGC Amp.

BOTTOM

PEAK

3 STATE

DET.

I-I

I-I

10pF

15pF

40pF

15pF

3pF

10pF

3pF

36pF

40pF

SW1

SW3

SW2

IC BLOCK DIAGRAM & DESCRIPTION

IC801 TA2153FN (RF AMP)

- 2 -

Page 4

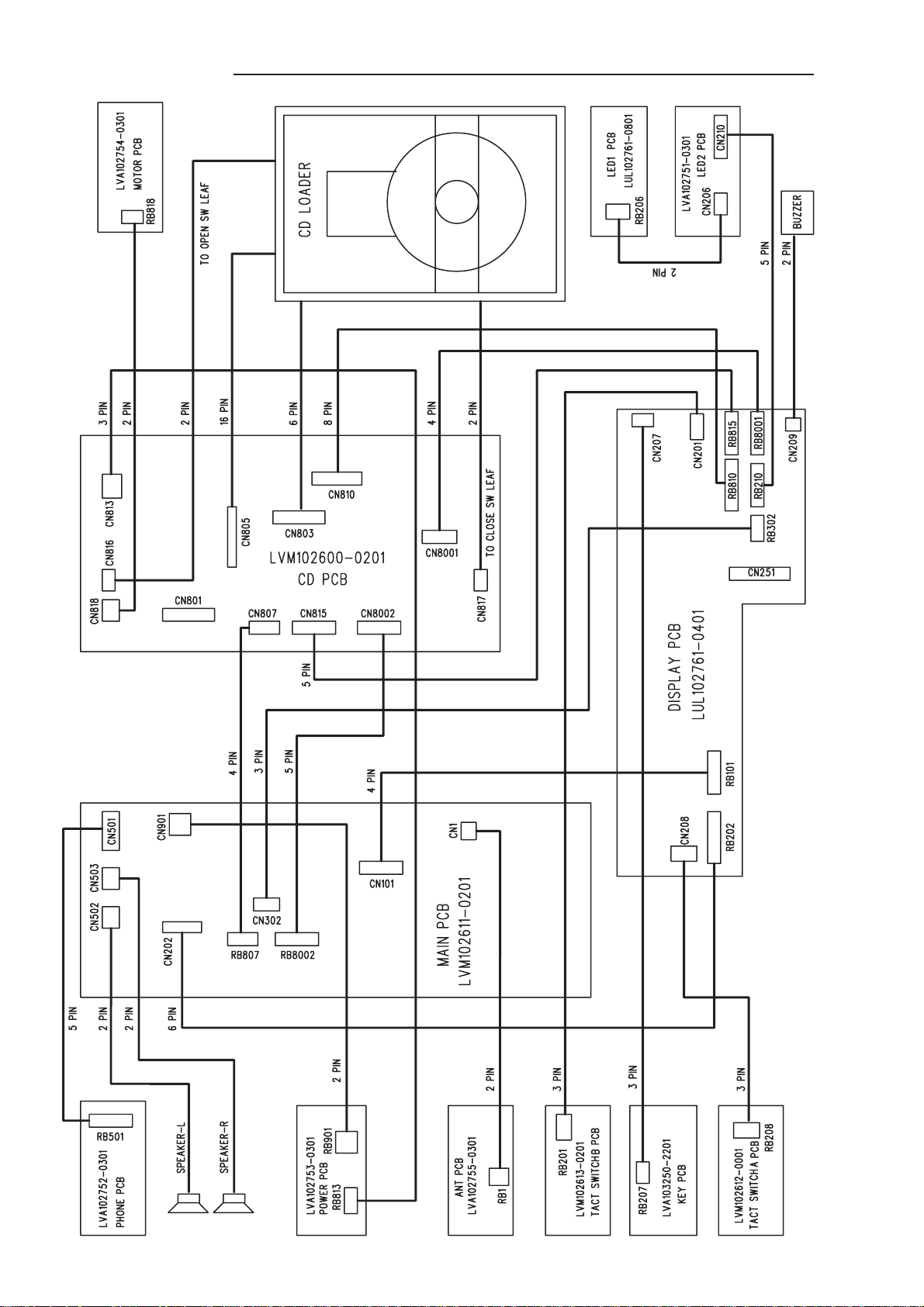

WIRING CONNECTION

- 3 -

Page 5

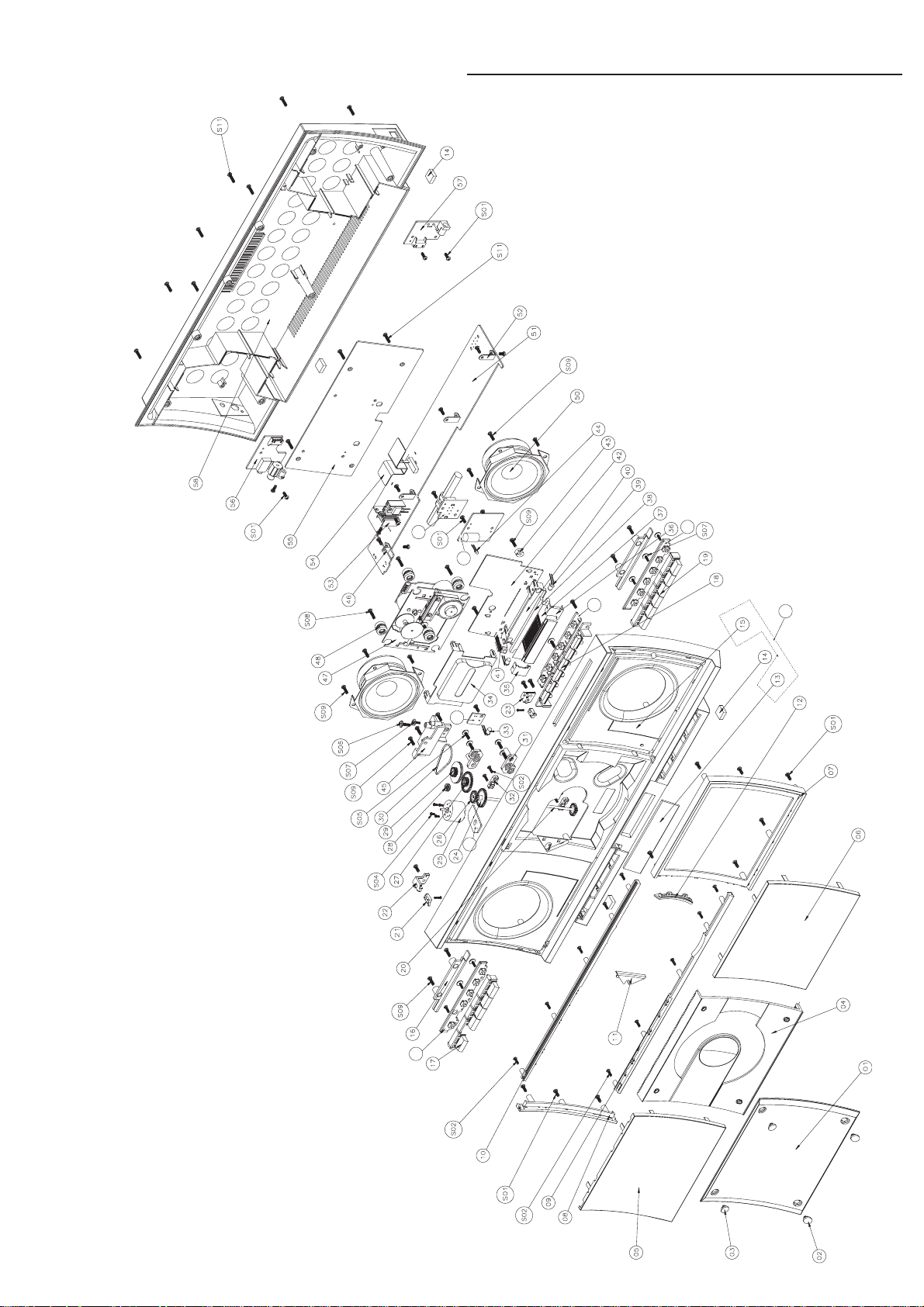

EXPLODED VIEW( CABINET & C HASSIS)

59

61

62

65

63

64

60

66

- 4 -

Page 6

PARTS LIST

PRODUCT SAFETY NOTICE

EACH PRECAUTION IN THIS MANUAL SHOULD BE FOLLOWED DURING SERVICING. COMPONENTS IDENTIFIED WITH

!!

!

THE IEC SYMBOL

CAN OF SPECIAL SIGNIFICANCE. WHEN REPLACING A COMPONENT IDENTIFIED , USE ONLY THE REPLACEMENT

PARTS DESIGNATED , OR PA RT S WITH THE SAM E RATING S O F RE SIST ANCE , WATT AG E OR VO LTAGE THA T AR E

DESIGNATED IN THE PARTS LIST IN THIS MANUAL. LEAKAGE-CURRENT OR RESISTANCE MEASUREMENTS MUST

BE MADE TO DETER MINE THAT EXPOSED PARTS A RE ACCEPTA BLY INSULA TED FROM TH E SUPPLY C IRCUIT

BEFORE RETURNING THE PRODUCT TO THE CUSTOMER.

CAUTION : Regular type resistors and capacitors are not listed. To know those values, refer to the schematic diagram.

IN THE PA RTS LIST AND THE SCHEMATIC DIAGRAM DESIGNATE COMPONENTS IN WHICH SAFETY

Regular type resistors are less than 1/4W carbon type and 0 ohm chip resistors.

Regular type capacitors are less than 50V and less than 1000µF of Ceramic type and Electrolytic type.

PACKING & ACCESSORIES

REF.NO. PART NO. DESCRIPTION

645 063 7636 CARTON CASE

645 063 7643 CARTON OUTER

645 063 7698 INSTRUCTION MANUAL

645 063 7704 QUICK GUIDE

645 063 3553 POLYFOAM

645 063 3560 POLYFOAM

645 060 7011 POLYBAG,AC CORD

645 063 3607 POLYBAG,I/B

645 063 3607 POLYBAG,TRANSFORMER

645 063 3614 POLYBAG,UNIT

!!

!

645 063 2273 AC ADAPTOR

645 063 7650 REMOTE CONTROL,

645 063 3546 FM ANT,AWG24UL 1007

REM-DTA300M FISHER

CABINET & CHASSIS

REF.NO. PART NO. DESCRIPTION

1 645 063 7742 CD WINDOW,FISHER

2 645 063 6301 CD-WIN -SUPPORT-BTM,CAP PIN

3 645 063 6295 CD-WIN-SUPPORT-TOP,CAP PIN

4 645 063 6196 CD DOOR

5 645 063 6318 SPEAKER GRILL LEFT

6 645 063 6325 SPEAKER GRILL RIGHT

7 645 063 6226 GRILL BASE RIGHT

8 645 063 6219 GRILL BASE LEFT

9 645 063 7735 GUIDE-GROOVE BTM

10 645 063 7728 GUIDE-GROOVE TOP

11 645 063 3201 CD SIGN-LENS-LEFT

12 645 063 3195 CD SIGN-LENS-RIGHT

13 645 063 6271 DISPLAY WINDOW

14 645 063 3300 RUBBER FOOT SILICON

15 645 063 6202 CABINET FRONT

16 645 063 3072 FUN-KNOB HOLDER

17 645 063 6240 POWER KNOB

18 645 063 6233 VOLUME KNOB

19 645 063 6257 CD FUNCTION KNOB,PLAY

20 645 063 3478 SHAFT STAINLESS STEE

22 645 063 3058 SW HOLDER L

23 645 063 3102 SW HOLDER R

24 645 063 2976 END GEAR

25 645 063 2860 MOTOR DC 3.5V

26 645 063 2969 DOOR GEAR

27 645 063 2990 MIDDLE GEAR

28 645 063 3218 PULLEY MOTOR

29 645 063 3003 PULLEY GEAR

30 645 063 3324 BELT

31 645 063 3126 CD BOSS HOLDER

32 645 063 3041 SHAFT HOLDER

33 645 063 2501 LED 5,CLASSIC

34 645 063 7711 CD DECK COVER

35 645 063 3065 LED HOLDER LEFT

36 645 063 3119 LED HOLDER RIGHT

37 645 063 2648 LCD FILTER PVC

38 645 063 3171 LCD LENS

39 645 063 2501 LED ,CLASSIC

40 645 063 3027 LCD HOLDER

REF.NO. PART NO. DESCRIPTION

41 645 063 3638 SPONGE

43 645 063 3096 SCREW WASHER

44 645 063 2495 LED

45 645 063 3263 MOTOR BASE

46 645 063 3355 PCB BKT-2

47 645 063 2365 CD DECK MECHANISM

48 645 060 6540 CD FOOT BUSHING

52 645 063 3348 PCB BKT-1

53 645 063 2242 HEAT SINK,FOR IC901,IC903

54 645 063 3591 HEAT SINK,FOR IC501

58 645 063 6288 REAR CAB

66 645 063 6134 ASSY CABINET FRONT

FIXING PARTS

REF.NO. PART NO. DESCRIPTION

S01 645 063 3430 SCR 3X10,GRILL L TO FRT

S02 645 063 3423 SCR 2.5X10,GUIDE TO FRT

S04 645 063 3454 SCR 2X4,MTR TO MTR BASE

S05 645 063 3508 SCR 3X10,CD BOSS TO FRT

S06 645 063 3430 SCR 3X10,KNOB HOLD. TO FRT

S07 645 060 6779 SCR 3X8,MTR PCB BKT TO FRT

S08 645 063 3416 SCR 2.5X18,CD DECK TO FRT

S09 645 063 3430 SCR 3X10,

SPEAKER DRIVER TO FRT

S11 645 063 3447 SCR 3X12,CD PCB TO FRT

ELECTRICAL-PARTS

REF.NO. PART NO. DESCRIPTION

21 645 063 3485 MICRO SWITCH

50 645 063 3331 SPEAKER

645 063 2525 BEAD FERRITE

645 063 3256 BUZZER

645 063 2624 5P J WIRE AWG22 2468,TO CN501

645 063 3782 2P J WIRE AWG20 2468,SP-L WIRE

645 063 3775 2P J WIRE AWG20 2468,

CN503 TO SPEAKER -R

645 063 2563 2P J WIRE AWG26,OPEN SW LEAF

645 063 2556 2P J WIRE,CLOSE SW LEAF

645 063 2532 FFC CABLE 16P,

CD DECK TO CD BD CN805

645 063 3652 6P J WIRE AWG30 157,

CN803 TO CD LOADER

DISPLAY P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

42 614 327 8597 ASSY,PWB,DISPLAY(Only initial)

B8001 645 063 2433 4P CONNECTOR,RB8001

C0212 403 135 5108 ELECT 4700U M 10V

CN201 645 060 5062 3P CONNECTOR,

TO TACT SW RB201

CN207 645 060 5062 3P CONNECTOR,TO KEY BD RB207

CN208 645 060 5062 3P CONNECTOR

CN209 645 060 5055 2P CONNECTOR

CN251 645 060 5086 8P CONNECTOR

D0201 645 060 4775 DIODE 1N4148

D0202 645 060 4775 DIODE 1N4148

- 5 -

Page 7

PARTS LIST

REF.NO. PART NO. DESCRIPTION

D0203 645 060 4775 DIODE 1N4148

DP201 645 063 2846 LCD DISPLAY,DTE102465A1P

IC201 645 048 8238 IC 5V43-1 J15,M-CU TMP87EP26

IC205 645 063 2921 IC FS8339,MUSIC IC

L0201 645 060 4805 CHOKE COIL 10UH

L0202 645 060 4805 CHOKE COIL 10UH

L0203 645 060 4812 CHOKE COIL 100UH

L0210 645 063 2723 COIL 8MH

LD201 645 063 2501 LED ,CLASSIC

LD202 645 063 2501 LED ,POP

Q0201 645 063 2457 TR 2SC1623

Q0208 645 063 2457 TR 2SC1623

Q0209 645 063 2457 TR 2SC1623

Q0211 645 063 2488 TR 2SA733,TR 2SA812

Q0212 645 063 2457 TR 2SC1623

RB101 645 063 2433 4P CONNECTOR

RB202 645 060 5079 6P CONNECTOR

RB210 645 063 2440 5P CONNECTOR

RB302 645 060 5062 3P CONNECTOR

RB810 645 060 5086 8P CONNECTOR

RB815 645 063 2440 5P CONNECTOR

SN201 645 060 5475 IRT SENSOR,REMOTE SENSOR

XL201 645 063 3287 CRYSTAL 7.3728MHZ

XL202 645 063 3270 CRYSTAL 32.768KHZ

ZD202 645 063 2297 ZENER DIODE 3.3V

645 063 2648 LCD FILTER PVC

645 063 3027 LCD HOLDER

645 063 3065 LED HOLDER

645 063 3119 LED HOLDER R

645 063 3171 LCD LENS

645 063 3621 SPONGE

MAIN P.C.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

51 614 327 8559 ASSY,PWB,MAIN(Only initial)

B8002 645 063 3706 5P J WIRE 2547&2468,RB8002

C0119 403 058 2406 POLYESTER 0.015U J 50V

C0120 403 058 2406 POLYESTER 0.015U J 50V

C0422 403 125 5507 ELECT 1000U M 16V

C0509 403 125 5507 ELECT 1000U M 16V

C0511 403 058 4608 POLYESTER 0.15U J 50V

C0512 403 058 4608 POLYESTER 0.15U J 50V

C0513 403 125 5507 ELECT 1000U M 16V

C0514 403 125 5507 ELECT 1000U M 16V

C0905 403 135 5702 ELECT 4700U M 25V

C0926 403 125 5507 ELECT 1000U M 16V

CF101 645 060 5338 CERAMIC FILTER 450KH

CF103 645 060 5345 CERAMIC FILTER 10.7M

CF104 645 060 5369 CERAMIC FILTER 10.7M

CF152 645 060 5352 CERAMIC FILTER 10.7M

CN001 645 063 2464 2P CONNECTOR,TO ANT BD.RB01

CN101 645 063 3676 4P J WIRE AWG30 1571,

TO CTL BD RB101

CN202 645 063 2631 6P J WIRE AWG26,

TO CTL BD RB202

CN302 645 063 3539 3P J WIRE UL2547,

TO CTL BD RB302

CN501 645 060 5178 5P CONNECTOR,

TO PHONE BD RB501

CN502 645 063 2464 2P CONNECTOR,TO SPEAKER L

CN503 645 063 2464 2P CONNECTOR,TP SPEAKER R

CN901 645 063 2471 2P CONNECTOR,

TO PWR BD RB901

D0001 645 060 4775 DIODE 1N4148

D0002 645 060 4775 DIODE 1N4148

D0003 645 060 4775 DIODE 1N4148

D0004 645 060 4775 DIODE 1N4148

D0503 645 060 4775 DIODE 1N4148

D0901 645 060 5383 RECTIFIER 1N5401

D0902 645 063 2228 DIODE 1N4007

D0903 645 063 2228 DIODE 1N4007

D0906 645 063 2228 DIODE 1N4007

D0907 645 063 2235 DIODE 1N5392

REF.NO. PART NO. DESCRIPTION

D0908 645 063 2228 DIODE 1N4007

IC101 645 060 5390 IC TA2104BN,DIGITAL TUNING SYS

IC151 645 060 5017 IC TC9257F

IC401 645 048 8269 IC TDA7440D,VOL TONE CTL

IC501 645 063 2686 IC TA8227P

IC901 645 063 2679 IC 7808,REGULATOR

IC902 645 060 5437 IC AN7806

IC903 645 060 5437 IC AN7806

IF101 645 060 5543 AM IFT

L0001 645 060 5567 SPR COIL

L0002 645 060 5567 SPR COIL

L0004 645 060 5567 SPR COIL

L0005 645 063 2716 OSC COIL 108UH

L0007 645 063 2709 SPEAKER COIL

L0018 645 060 5611 AM ANT OSC,COIL:R2523-0A10

L0101 645 060 4812 CHOKE COIL 100UH

L0901 645 060 4812 CHOKE COIL 100UH

Q0001 645 060 4799 TR 2SK192A-Y

Q0102 645 060 4829 TR 2SC945P

Q0103 645 060 4829 TR 2SC945P

Q0104 645 060 4829 TR 2SC945P

Q0105 645 060 4829 TR 2SC945P

Q0106 645 060 4829 TR 2SC945P

Q0107 645 060 4829 TR 2SC945P

Q0108 645 060 4850 TR 2SA733Q P

Q0152 645 060 4829 TR 2SC945P

Q0155 645 060 4829 TR 2SC945P

Q0156 645 060 4829 TR 2SC945P

Q0157 645 060 4836 TR 2SC1675L

Q0501 645 063 2266 TR 2SC2878A

Q0502 645 063 2266 TR 2SC2878A

Q0902 645 060 4829 TR 2SC945P

Q0903 645 063 2693 TR 2SB772P Q

Q0904 645 060 4829 TR 2SC945P

Q0905 645 060 5468 TR 2SD882P

Q0906 645 063 2693 TR 2SB772P Q

SS01 645 060 6779 SCR 3X8,IC901,

IC903 TO HEAT SINK

SS02 645 063 3461 SCR 3X6,MAIN PCB TO PCB BKT

TC001 645 060 7059 TRIMMER 20PF

TC002 645 060 7059 TRIMMER 20PF

TC003 645 060 7042 TRIMMER 10PF

TC004 645 060 7042 TRIMMER 10PF

VD001 645 060 5499 DIODE 1SV101,FM TUNING DIODE

VD002 645 060 5505 DIODE 1SV149B,AM TUNING DIODE

VD004 645 060 5505 DIODE 1SV149B,AM TUNING DIODE

VD005 645 060 5499 DIODE 1SV101,FM TUNING DIODE

XL151 645 060 6533 CRYSTAL 7.2MHZ

ZD101 645 060 4881 ZENER DIODE 3.9V

ZD401 645 060 4928 ZENER DIODE 9.1V

645 063 2242 HEAT SINK,FOR IC901,IC903

645 063 3591 HEAT SINK,FOR IC501

645 063 3348 PCB BKT-1

645 063 3355 PCB BKT-2

645 060 6687 SLEEVING SILICON TUB

645 063 3393 SLEEVING

645 063 3799 TEST PIN 1MM,FOR GND TOP

CD P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

55 614 327 8580 ASSY,PWB,CD(Only initial)

C0812 403 061 7306 POLYESTER 4700P J 50V

C0818 403 059 9800 POLYESTER 2700P J 50V

CN803 645 060 5079 6P CONNECTOR,TO CD LOADER

CN805 645 063 2372 16P CONNECTOR,TO CD LOADER

CN807 645 063 2433 4P CONNECTOR,

TO MAIN BD RB807

CN810 645 063 3669 8P J WIRE AWG30 1571,

TO CTL BD RB810

CN815 645 063 3683 5P J WIRE AWG30 1571,

TO CTL BD RB815

CN816 645 060 5055 2P CONNECTOR,

TO OPEN SW LEAF

- 6 -

Page 8

PARTS LIST

REF.NO. PART NO. DESCRIPTION

CN817 645 060 5055 2P CONNECTOR,

TO CLOSE SW LEAF

CN818 645 063 2464 2P CONNECTOR,TO MTR BD RB818

D8001 645 063 2662 IC TL431,VOLT. REGULATOR

D8002 645 063 2662 IC TL431,VOLT. REGULATOR

D8005 645 060 4775 DIODE 1N4148

D8006 645 060 4775 DIODE 1N4148

I8001 645 063 2402 IC TC94A02F-005,

IC8001 CMOS DIGITAL IC

I8002 645 063 2426 IC TC74HC14AFN,IC8002

I8003 645 063 2419 IC UT621024SC-70LL,IC8003

I8004 645 063 2389 IC REG1117,IC8004

IC801 645 063 2396 IC TA2153FN,

RF AMP DIGIT.SERV CD

IC802 645 060 5031 IC TC9462F,

DIGITAL SERVO SINGLE

IC803 645 063 2655 IC TA2092N,PWR DRIVE

IC804 645 060 5413 IC TA7291S

L0801 645 060 4812 CHOKE COIL 100UH

L0802 645 060 4812 CHOKE COIL 100UH

L0805 645 060 4805 CHOKE COIL 10UH

L0806 645 063 2518 BEAD FERRITE 100MHZ

L0807 645 063 2518 BEAD FERRITE 100MHZ

L0808 645 060 4812 CHOKE COIL 100UH

L8001 645 063 2259 INDUCTOR 47UH

L8002 645 063 2259 INDUCTOR 47UH

L8003 645 063 2259 INDUCTOR 47UH

L8004 645 063 2259 INDUCTOR 47UH

L8006 645 063 2259 INDUCTOR 47UH

N8001 645 063 3676 4P J WIRE AWG30 1571,CN8001

N8002 645 063 2440 5P CONNECTOR,CN8002

Q0801 645 060 4867 TR 2SA952

Q0804 645 060 4843 TR 2SC2001L

Q0805 645 063 2457 TR 2SC1623

Q0806 645 063 2457 TR 2SC1623

Q8001 645 060 4829 TR 2SC945P

Q8002 645 060 4829 TR 2SC945P

Q8003 645 060 4829 TR 2SC945P

Q8005 645 060 4829 TR 2SC945P

TP801 645 063 3799 TEST PIN 1MM,FEO

TP802 645 063 3799 TEST PIN 1MM,RFO

TP803 645 063 3799 TEST PIN 1MM,TEO

TP804 645 063 3799 TEST PIN 1MM,VRO

XL801 645 060 6519 CRYSTAL 16.9344MHZ

ZD801 645 060 4898 ZENER DIODE 4.6V

ZD802 645 060 4898 ZENER DIODE 4.6V

645 063 3584 HEAT SINK,FOR CD PCB IC803

PHONE P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

56 614 327 8627 ASSY,PWB,PHONE(Only initial)

C0528 403 059 7509 POLYESTER 0.22U J 50V

JK501 645 063 2747 PHONE JACK

JK502 645 063 2761 RCA JACK,RJ-1081-01-0300A

RB501 645 060 5178 5P CONNECTOR,

TO MAIN BD CN501

POWER P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

57 614 327 8634 ASSY,PWB,POWER(Only initial)

JK901 645 063 2754 POWER JACK,DJ-0702-020

RB901 645 063 3768 2P J WIRE AWG18 UL10,

TO MAIN BD CN901

TACT SW A P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

59 614 327 8566 ASSY,PWB,TACT SW A(Only initial)

RB208 645 063 2594 3P J WIRE AWG26

TA007 645 060 4874 SW TACT,PRESET

TA008 645 060 4874 SW TACT,MEMORY

TA009 645 060 4874 SW TACT,TIMER

TA010 645 060 4874 SW TACT,SLEEP

TA017 645 060 4874 SW TACT,POWER

TACT SW B P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

60 614 327 8573 ASSY,PWB,TACT SW B(Only initial)

RB201 645 063 2587 3P J WIRE AWG26 UL24

TA011 645 060 4874 SW TACT,OPEN / CLOSE

TA012 645 060 4874 SW TACT,BACK / TUNETA013 645 060 4874 SW TACT,FWD / TUNE+

TA014 645 060 4874 SW TACT,STOP

TA015 645 060 4874 SW TACT,PLAY / PAUSE

TA016 645 060 4874 SW TACT,BAND

MOTOR P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

61 614 327 8641 ASSY,PWB,MOTOR(Only initial)

M0801 645 063 2860 MOTOR DC 3.5V

RB818 645 063 2549 2P J WIRE AWG26,TO CD BD CN818

LED 1 P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

62 614 327 8603 ASSY,PWB,LED 1(Only initial)

LD203 645 063 2501 LED 5

RB206 645 063 2570 2P J WIRE,LED BD CN206

LED 2 P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

63 614 327 8610 ASSY,PWB,LED 2(Only initial)

CN206 645 060 5055 2P CONNECTOR,

TO LED 1 BD RB206

CN210 645 063 3690 5P J WIRE AWG30 1571,

TO CTL BD RB210

D0205 645 060 4775 DIODE 1N4148

D0206 645 060 4775 DIODE 1N4148

D0208 645 060 4775 DIODE 1N4148

D0209 645 060 4775 DIODE 1N4148

D0210 645 060 4775 DIODE 1N4148

D0211 645 060 4775 DIODE 1N4148

D0212 645 060 4775 DIODE 1N4148

L0206 645 060 4812 CHOKE COIL 100UH

LD204 645 063 2495 LED

Q0203 645 060 4829 TR 2SC945P

Q0204 645 060 4850 TR 2SA733Q P

Q0205 645 060 4829 TR 2SC945P

Q0206 645 060 4829 TR 2SC945P

Q0207 645 060 4829 TR 2SC945P

Q0210 645 060 4829 TR 2SC945P

645 063 2853 LED HOLDER,FOR LD204

ANT P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

64 614 327 8658 ASSY,PWB,ANT COIL(Only initial)

L0003 645 063 3294 ROD ANT

RB001 645 063 3522 2P J WIRE AWG28 1533,

TO MAIN BD CN01

KEY P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

65 614 327 8665 ASSY,PWB,KEY(Only initial)

RB207 645 063 2600 3P J WIRE AWG26,

TO CTL BD CN207

TA001 645 060 4874 SW TACT,VOLTA002 645 060 4874 SW TACT,VOL+

TA003 645 060 4874 SW TACT,BASS

TA004 645 060 4874 SW TACT,SOUND

TA005 645 060 4874 SW TACT,FUNCTION

TA006 645 060 4874 SW TACT,SNOOZE

- 7 -

Page 9

IC BLOCK DIAGRAM & DESCRIPTION

IC101 TA2104B (Tuner) IC501 TA8227P (Power Amp.)

FM

RF OUT

24 21 20 19 18 17 16 15 14 132223

FMRF

RF

Vcc

AM

RF IN

FM

AM

OSC

OSC

AM

OSC

FM

OSC

BUFF

BUFF

AM

MIX

FM

MIX

OSC

OUT

LEVEL

DET

ST

IF

LED

SW

ST

IF

BUFF

1/8

FMIFAMIF

DEV

REQ

OUT

IF

REQ

AF

BUFF

AM

DETFMDET

AGC

LPF1AF IN LPF2

AF

VCO

DECODE

DIVIDE

ST/MO

FM/AM

MJTE

145678910111232

RF

FM

AM

MIX

GND

RF IN

LOW

CUT

OUT

Vcc AM

IF INFMIF IN

IC151 TC9257F (Tuner PLL)

XT 16 DO2/OT-41

XT 15 DO12

PERIOD 14 I/O-5/IF

CLOCK 13 I/O-6/IF

DATA 12 GND5

OT-1 116

OT-2 10 AM

OT-3 9 V

FM

L

AMP

FM

AM

XT

XT

DAT A

CLOCK

PERIOD

IN

IN

(Note) Mark terminals are not existence in TC9256P, TC9256F.

Terminal name of TC9256P, TC9256F is shown in parentheses.

Others are common terminals.

1/ 2

H

OSC

CIRCUIT

HFFM

AGC QUAD R-OUT L-OUT

GND

TC9256P, TC9256F

3

4

7

8

Top View

DIP-16PIN / SOP-16PIN

2 MODULUS

PRESCALER

MODE LFFM

REFERENCE COUNTER

1ms

OSC

8

ADDRESS

DECODER

OUTPUT PORT

OT-1 OT-3

OT-2 OT-4

TEST

4

FM

IN1

IN2

IN

IN

DD

PERIOD 18 I/O-7/SC

CLOCK 17 I/O-8/IF

I/O-5/CLK I/O-6

PSC

4bit SWALLOW

COUNTER

12bit PROGRAMMABLE COUNTER

4

12

15

24bit REGISTER

24bit SHIFT REGISTER

24 22

10

24bit REGISTER

4

20bit BINARY COUNTER

UNIVERSAL COUNTER CONTROL

OT-4

XT

1ms

- 8 -

TC9257P, TC9257F

XT 20 DO21

XT 19 DO12

3

4

DATA 16 I/O-9/IF

5

OT-1 15 GND6

7

OT-2 14 FM

OT-3 13 AM

8

OT-4 V

Top View

DIP-20PIN / SOP-20PIN

DD

POWER ON

RESET

RESET

PHASE

MAX

4

UNLOCK

5

GATE

IN

IN

DD

129

1110

GNDV

TRI-ST ATE

BUFFER

TRI-ST ATE

BUFFER

COMP ARATOR

OT-4

5

IN

IN1

IN2

I/O PORT

AMP

AMP

DO1

DO2

(DO2 / OT-4)

I / O-5 / CLK

I / O-6

IN2

I / O-9 / IF

(I / O-6 / IF

I / O-8 / IF

IN1

(I / O-5 / IF

I / O-7 / SC

IN2

)

IN1

)

IN

Page 10

IC BLOCK DIAGRAM & DESCRIPTION

IC804 TA7291S (Bridge Driver)

IC401 TDA7440D (VOLUME TONE CTL)IC8002 TC74HC14AFN (Gate)

PIN FUNCTION

Vcc

7 / 2 / 1 1 4 / 8 / 5

5 / 9 / 7 6 / 1 / 9 1 / 5 / 1

Vref

REG

PROTECTOR

CIRCUIT

(TSD)

IN2 GNDIN1

8 / 6 / 15

2 / 7 / 4

10 / 3 / 13

TA7291P / TA7291S / TA7291F

VS

OUT1

OUT2

P

7

8

4

1

5

6

2

10

PIN No.

S

2

6

8

5

9

1

7

3

F

11

15

5

1

7

9

4

13

SYMBOL

Vcc

Vs

Vref

GND

IN1

IN2

OUT1

OUT2

FUNCTIONAL DESCRIPTION

Supply voltage terminal for Logic

Supply voltage tarminal for Motor driver

Supply voltage terminal for control

GND terminal

Input terminal

Input terminal

Output terminal

Output terminal

- 9 -

Page 11

X-Pointer

register

1

2

3

4

5

6

7

13

12

11

10

9

8

17

18

19

20

21

22

23

24

25

26

27

28

29

30

/RESET

MiMD

AD0

AD1

MiDio

/MiCK

AD2

LRCKiA

BCKiA

SDi0

AD4

AD3

SDo

VDD

Lo

VRAL

VDAL

VDAR

VRAR

STANDBY

Ro

CKS

VSSL

Bus

Switch

Microcom. I/F

XRAM

YRAM

CROM

register

A1

MX MY

MZ AX AY

round & limit

MAC

ALU

round & limit

X0 X1 X2

Y0 Y1 Y1

40bit

Address Calc.

2sets

X-Bus

Y-Bus

I-Bus

ERAM

2k word

A0

A2

A3

Y-Pointer

register

C-Pointer

register

Audio I/F

Instruction

Decoder

Program

Control

Flag

VSS

VSSR

TESTP

4k word

4kword

*3

4k word

256word

PROM

PRAM

4k*2+2k

=10kword

DAC

14

AD5

15

/CE

16

/oE

31

AD12

32

AD11

48

47

46

45

44

43

42

36

37

38

39

40

41

35

34

33

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

io2

io3

io4

VDD

io5

io6

io7

VSSP

PDo

VCoi

VDDP

CKO

VDDX

Xi

Xo

VSSX

VCO

Timing

Generator

General

Input Port

DIT

General

Output Port

SRAM I/F

DAC

Prog.

Start

VDDT

Interrupt

Control

Timer

AD15

AD10

AD9

VDDT

AD8

AD7

AD6

REQ

VSS

AD13

AD14

/WR

AD16

io0

io1

VSS

IC BLOCK DIAGRAM & DESCRIPTION

IC8001 TC94A02-005 (MP3 DECODER)

PIN FUNCTION

PIN

NO.

Sy

mbol I/O

1/RESET

2MiMD

3AD0

4AD1

I

I

I

I

5MiDio I/O

6/MiCK

7AD2

8 VDDT

9

S

Do

I

I

%

O

10 AD3 O

11 AD4 O

12 SDi0 I

13 BCKiA I

14 LRCKiA I

15 AD5 I

16 CE I

17 OE I

18 VDD -19 STANBY I

20 VSS -21 VSSL -22 VRAL -23 LO

O

24 VDAL -25 VDAR -26 RO O

27 VRAR -28 VSSR -29

TESTP

30 CKS I

31 AD12 O

32 AD11 O

33 AD10 O

34 AD9 O

35 VDDT -36 AD8 O

37 AD7 O

I

DESCRIPTION OF PIN FUNCT I ON Remark

Reset signal input terminal(H:Op eration,L:R eset) Reset(MC

Mode select input for MCU interface (H:I

2

C L:T SB)ì! î

Address output-0 for external SRAM AD0(SRAM

Address output-1 for external SRAM AD1(SRAM

Data input and output for MCU i nterface" I2C# SDA$SDA(MCU)

2

Clock input for MCU interface" I

C# SCL$ SCL( MCU)

Address output-2 for external SRAM AD2(SRAM

Digital power supply for interface (3.3V) VDDT (3.3V)

Data output for audio interface

SDO

Address output-3 for external SRAM AD3(SRAM)

Address output-4 for external SRAM AD4(SRAM)

Data input-0 for audio interface SDi(CDP)

Bit clock input-A for audio interface BCK(CDP )

LR clock input-A for audio interface LRCK (CDP)

Address output-5 for external SRAM AD5(SRAM)

Chip enable signal output for external SRAM CE(SRAM)

Enable signal output for external SRAM OE(SRAM)

Digital p ower supply(2.5V ) VDD(2 .5V)

Stand-by terminal& (H:ST B, L:Operation) STABY(MCU)

Digital GND GND

DAC L ch An alo g GND GND

DAC V ref for L ch VR

DAC Lch analog signal output LO(am

DAC power supply f or L ch(2.5V ) V DA(2.5V)

DAC power supply f or Rch(2.5V) V DA(2.5V)

DAC Rch analog signal output RO(amp)

DAC V ref for Rch VR

DAC Rc h Analog GND GND

Test input (H:Test& L: Normal) ìLî

VCO clo ck selection input(! :VC O& L: X I clock) ìH î

Address output-12 for external SRAM AD12(SRAM)

Address output-11 for external SRAM AD11(SRAM)

Address output-10 for external SRAM AD10(SRAM)

Address output-9 for external SRAM AD9(SRAM)

Digital power supply for interface(3.3V) VDDT (3.3V)

Address output-8 for external SRAM AD8(SRAM)

Address output-7 for external SRAM AD7(SRAM)

U)

p)

38 A D6 O

39 REQ O

40 VSS -41 AD13 O

)

42 AD14 O

43 WR I

)

44 AD16 O

45 AD15 -46 io0 I/O

)

47 io1 I/O

48 VSS -49 io2 I/O

50 io3 I/O

51 Io4 I/O

52 VDD -53 io5 I/O

54 io6 I/O

55 io7 I/O

56 VSSP -57 Pdo O

58 V coi I

59 VDDP -60 C ko O

61 VDDX -62 Xi I

63 X o O

64 VSSX --

- 10 -

Address output-6 for external SRAM AD6(SRAM

Request pin for interrupt host

Digital GND

REQ(MCU)

GND

Address output-13 for external SRAM AD13(SRAM

Address output-14 for external SRAM AD14(SRAM

Write signal output for external SRAM WR(SRA

M)

Address output-16 for external SRAM AD16(SRAM

Address output-15 for external SRAM AD15(SRAM)

Data I/O-0 for external SRAM Io0(SRAM)

Data I/O-1 for external SRAM Io1(SRAM

Digital GND

)

GND

Data I/O-2 for external SRAM Io2(SRAM)

Date I/O-3 for external SRAM Io3(SRAM)

Data I/O-4 for external SRAM Io4(SRAM

Digital power supply(2.5V) VDD(2 .5V

)

)

Data I/O-5 for external SRAM Io5(SRAM)

Data I/O-6 for external SRAM Io6(SRAM)

Data I/O-7 for external SRAM Io7(SRAM

)

GND f or VCO circ uit GND

Phase detector output Pd

o

Controlled voltage input for VCO circuit Vcoi

Power supply for VCO circu it VDDP (2.5

V)

16.934Mhz clock output pin Cko (CD)

Power supply for cry stal oscillator" 2.5V) VDDX(2 .5V

Crystal oscillato r input Xi(16.934M Hz)

Crystal oscillato r output

Xo

GND f or cr ystal oscillator GND

)

)

)

)

)

Page 12

BLOCK DIAGRAM

- 11 -

Page 13

SCHEMATI C DIAGRAM (MA IN)

This is a basic schematic diagram.

PRODUCT SAFETY NOTICE

!!

EACH PRECAUTION IN THIS MANUAL SHOULD BE FOLLOWED DURING SERVICING. COMPONENTS IDENTIFIED WITH THE IEC SYMBOL

IN WHICH SAFETY AND PERFORMANCE CAN BE OF SPECIAL SIGNIFICANCE. WHEN REPLACING A COMPONENT IDENTIFIED BY

OF RESISTANCE, WATTAGE OR VOLTAGE THAT ARE DESIGNATED IN THE PARTS LIST IN THIS MANUAL. LEAKAGE-CURRENT OR RESISTANCE MEASUREMENTS MUST BE MADE TO DETERMINE THAT EXPOSED PARTS ARE ACCEPTABLY

INSULATED FROM THE SUPPLY CIRCUIT BEFORE RETURNING THE PRODUCT TO THE CUSTOMER.

!

!!

!

AND MARK IN THE PARTS LIST AND THE SCHEMATIC DIAGRAM DESIGNATED COMPONENTS

AND , USE ONLY THE REPLACEMENT PARTS DESIGNATED, OR PARTS WITH THE SAME RATINGS

- 13 -- 12 -

Page 14

SCHEMATIC DIAGRAM (CD MAIN)

This is a basic schematic diagram.

- 15 -- 14 -

Page 15

WIRING DIAGRAM (MAIN and TACT SW A,B)

MAIN A side

TACT SW A A side

TACT SW A B side

MAIN B side

TACT SW B A side

TACT SW B B side

- 17 -- 16 -

Page 16

WIRING DIAGRAM (CD MAIN) WIRING DIAGRAM (POWER, ANT, KEY, LED 1, LED 2, PHONE and MOTOR)

POWER

ANT

LED 1 A side

LED 1 B side

KEY A side

KEY B side

LED 2

A side

B side

PHONE

MOTOR

- 19 -- 18 -

Page 17

WIRING DIAGRAM (DISPLAY)

A side

B side

- 20 -

Page 18

Jun / '03 BB Printed in Japan

R

SANYO Electric Co., Ltd.

Osaka, Japan

Loading...

Loading...