Page 1

SERVICE MANUAL

For U.S.A., Canada

& Europe model

Ver. 1

MODEL

S-101

DVD HOME THEATER SYSTEM

HOME THEATER SYSTEM (S-101) consists of DVD SURROUND RECEIVER (ADV-S101)

and SUB WOOFER (DSW-S101) and SPEAKER SYSTEM (SC-S101)

注 意

サービスをおこなう前に、このサービスマニュアルを

必ずお読みください。本機は、火災、感電、けがなど

に対する安全性を確保するために、さまざまな配慮を

おこなっており、また法的には「電気用品安全法」に

もとづき、所定の許可を得て製造されております。

従ってサービスをおこなう際は、これらの安全性が維

持されるよう、このサービスマニュアルに記載されて

いる注意事項を必ずお守りください。

●

For purposes of improvement, specifications and

design are subject to change without notice.

●

Please use this service manual with referring to the

operating instructions without fail.

●

Some illustrations using in this service manual are

slightly different from the actual set.

Denon Brand Company, D&M Holdings Inc.

●

●

●

●

TOKYO, JAPAN

本機の仕様は性能改良のため、予告なく変更すること

があります。

補修用性能部品の保有期間は、製造打切後8年です。

修理の際は、必ず取扱説明書を参照の上、作業を行っ

てください。

本文中に使用しているイラストは、説明の都合上現物

と多少異なる場合があります。

X0244 V.01 DE/CDM 0507

Page 2

S-101

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, make sure you make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 0.5 milliamps, or if the resistance from chassis to either side of the

power cord is less than 460 kohms, the unit is defective.

LASER RADIATION

Do not stare into beam or view directly with optical instruments, class 3A laser product.

注 意

注意事項をお守りください!

サービスのとき特に注意を必要とする個所について

は、キャビネット、部品、シャーシなどにラベルや

捺印で、注意事項を表示しています。これらの注意

書きおよび取扱説明書などの注意事項を必ずお守り

ください。

感電に注意!

(1)このセットは、交流電圧が印加されていますの

で、通電時に内部金属部に触れると感電するこ

とがあります。従って通電サービス時には、絶

縁トランスの使用や手袋の着用、部品交換に

は、電源プラグを抜くなどして、感電にご注意

ください。

(2)内部には、高電圧の部分がありますので、通電

時の取扱には、十分ご注意ください。

指定部品の使用!

セットの部品は難燃性や耐電圧など安全上の特性を

持ったものとなっています。従って交換部品は、使

用されていたものと同じ特性の部品を使用してくだ

さい。特に配線図、部品表に

安全上重要な部品は必ず指定のものをご使用くださ

い。

サービス、点検時には次のことにご注意願います。

印で指定されている

(絶縁チェックの方法)

電源コンセントから電源プラグを抜き、アンテナ

や、プラグなどを外し、電源スイッチを入れま

す。500V絶縁抵抗計を用いて、電源プラグのそれ

ぞれの端子と、外部露出金属部〔アンテナ端子、

ヘッドホン端子、マイク端子、入力端子など〕と

の間で、絶縁抵抗値が1MΩ以上であること、この

値以下のときは、セットの点検修理が必要です。

安全上重要な部品について

注 意

注 意

安全上重要な部品について

部品の取付けや配線の引きまわしは、元どおりに!

安全上、テープやチューブなどの絶縁材料を使用し

たり、プリント基板から浮かして取付けた部品があ

ります。また内部配線は引きまわしやクランパーに

よって発熱部品や高圧部品に接近しないように配慮

されていますので、これらは必ず元どおりにしてく

ださい。

サービス後は安全点検を!

サービスのために取り外したねじ、部品、配線など

が元どおりになっているか、またサービスした個所

の周辺を劣化させてしまったところがないかなどを

点検し、外部金属端子部と、電源プラグの刃の間の

絶縁チェックをおこなうなど、安全性が確保されて

いることを確認してください。

本機に使用している多くの電気部品、および機構部品

は安全上、特別な特性を持っています。この特性はほ

とんどの場合、外観では判別つきにくく、また、もと

の部品より高い定格(定格電力、耐圧)を持ったもの

を使用しても安全性が維持されるとは、限りません。

安全上の特性を持った部品は、このサービスマニュア

ルの配線図、部品表につぎのように表示していますの

で、必ず指定されている部品番号のものを使用願いま

す。

(1) 配線図…

(2) 部品表… マークで表示しています。

マークで表示しています。

指定された部品と異なるものを使用し

た場合には、感電、火災などの危険を

生じる恐れがあります。

2

Page 3

S-101

RDISASSEMBLY

(Follow the procedure below in reverse order when

reassembling.)

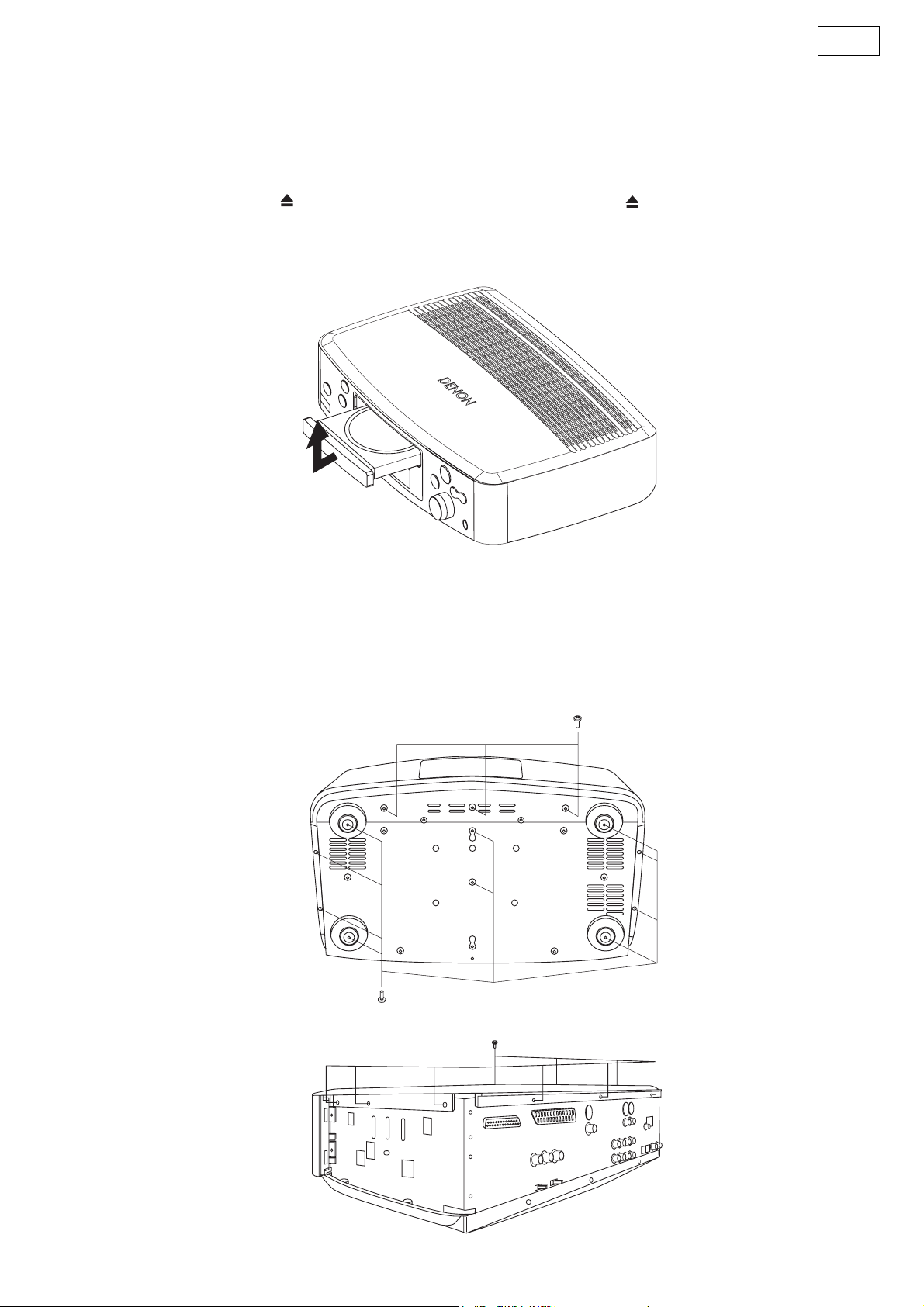

1. Loader Panel

(1) Switch on, and press [ (OPEN/CLOSE)] button

to open the Disc tray.

(2) Detach the Loader Panel by lifting.

各部のはずしかた

(組み立てるときは、逆の順序でおこなってください。)

1. ローダーパネルのはずしかた

(1) 電源を入れ「 (OPEN/CLOSE)」ボタンを押して、

ディスクトレイを開きます。

(2) ローダーパネルを持ち上げてはずします。

2. Side Panel, Bottom Cover

(1) Remove 13 bottom screws.

(2) Remove 7 rear screws, then detach Side Panel and

Bottom Cover.

2. サイドパネル、ボトムカバーのはずしかた

(1) 底面よりネジを 13 本はずします。

(2) 裏面よりネジを 7 本はずし、サイドパネル、ボトムカ

バーをそれぞれ矢印の方向へはずします。

3

Page 4

S-101

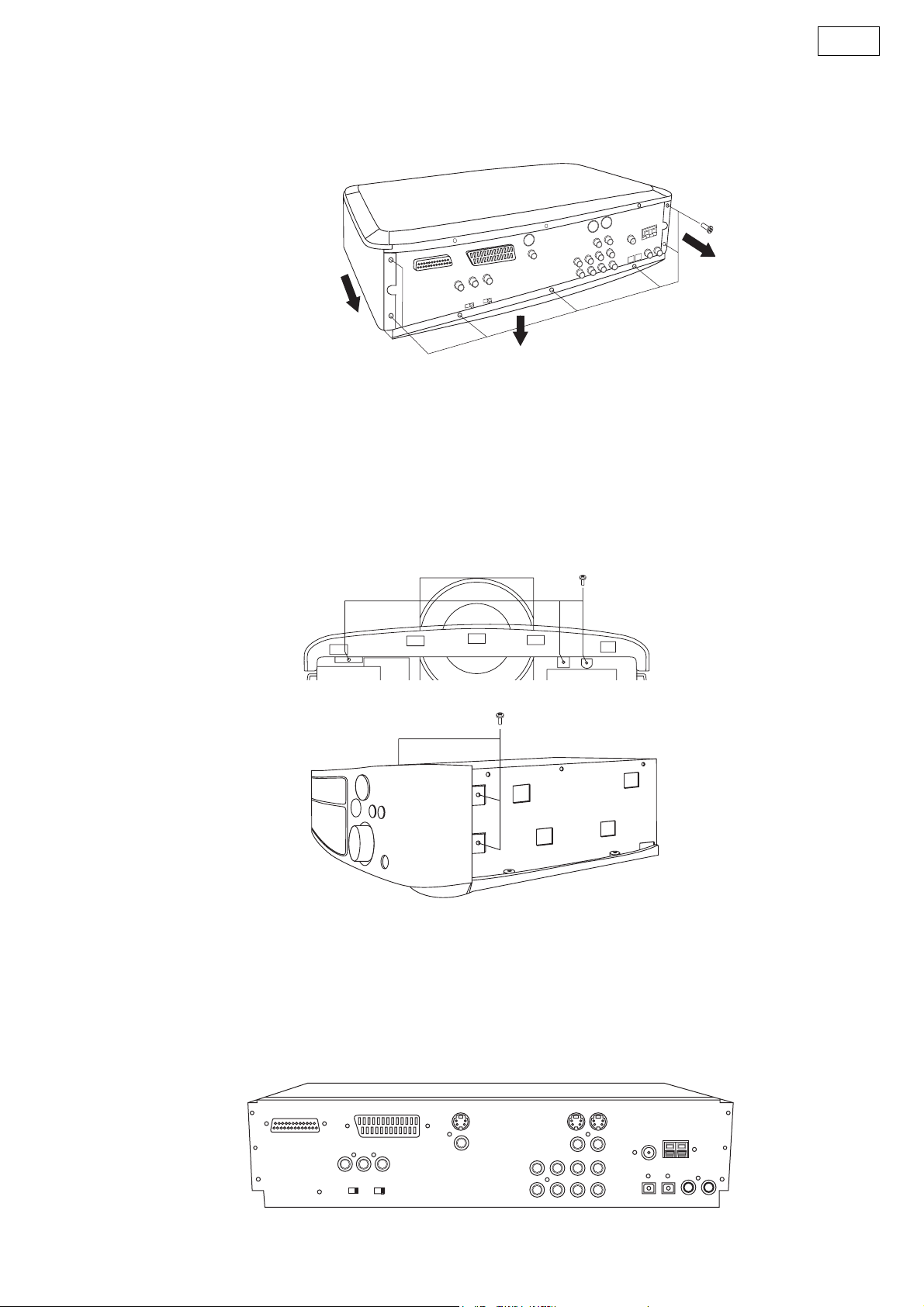

3. Top Cover

(1) Remove 9 top screws, then detach Top Cover.

4. Front Panel Ass’y

(1) Remove 3 Front panel screws, then detach P.W.B.

and chassis.

(2) Remove 4 Front panel side screws, then detach the

Front Panel Ass’y.

3. トップカバーのはずしかた

(1) トップカバーを止めている上部のネジ 9 本をはず

し、トップカバーを矢印の方向へはずします。

4. フロントパネルのはずしかた

(1) フロントパネルからの基板とシャーシを止めてい

るネジを 3 本はずします。

(2) フロントパネル側面を止めているネジ 4 本(左右各 2

本)をはずし、フロントパネルを矢印の方向へはずし

ます。

5. Front Panel Ass’y

(1) Remove earch terminal screws, Back Panel screws

and Chassis screws, then detch the Back Panel.

5. バックパネルのはずしかた

(1) 各端子を止めているネジおよびバックパネルと

シャーシを止めているネジをはずし、バックパネ

ルをはずします。

4

Page 5

S-101

Special operating procedures

1. Initialization

※ This initializes the data for the function, volume,

DVD mechanism (RL-874), etc.

(1) Check that the AC cord is disconnected from the

power outlet. (AC OFF)

(2) While pressing the FUNCTION and OPEN/CLOSE

( ) buttons on the main unit, plug the AC cord into

the power outlet. (AC ON)

(3) Check that the entire display and all the LEDs light,

then release the FUNCTION and OPEN/CLOSE

() buttons.

(4) After about 3 seconds, "INITIALIZE" appears on the

display.

(5) After initialization is complete (when "INITIALIZE"

turns off), the function is set to "DVD" and the volume level is set to -∞ ("-dB" is displayed).

2. System check mode

※ Use this to display the version information, etc.

(1) In the standby mode, while pressing the STOP ( )

and A.FWD ( ) buttons on the main unit, press

the ON/STANDBY button.

(2) Press the STATUS button on the remote control

unit (RC-1007) to display the following information,

in this order: Time (TIME) → System microprocessor version (SYS Ver) → Date of system microprocessor version updating (SYS Date) → DSP version (DSP Ver) → Date of DSP version updating

(DSP Date)→ Date of drive microprocessor version

updating (Dr Date) → ESS version (Ess Ver) →

Date of ESS version updating (Ess Date) →Region

number (Region No.)

(3) To cancel, unplug the AC cord. (AC OFF)

NOTE 1: The DVD mechanism driver version and

ESS version are not displayed unless the

function is once set to DVD.

特殊操作方法

1. 初期化

※ ファンクション、VOL 及び DVD メカ (RL-874) 等の

データを初期化します。

(1) ACコードがコンセントより外れていることを確認

します。(ACOFF)

(2) 本体の FUNCTION ボタンと OPEN/CLOSE( ) ボタ

ンを押しながら、AC コードをコンセントに接続

(ACON) します。

(3) ディスプレイと LED の全点灯を確認したら、本体

の FUNCTION ボタンと OPEN/CLOSE( ) ボタンを

離します。

(4) 約 3 秒後、ディスプレイに "INITIALIZE" が表示され

ます。

(5) 初期化完了 ("INITIALIZE" 消灯 ) 後、FUNCTION は

"DVD"、VOL位置は -∞ (表示は "---dB")となります。

2. システムチェックモード

※ バージョン表示等をおこないます。

(1) STANDBY 時、本体の STOP( )ボタンと A.FWD

( )ボタンを押しながら、ON/STANDBY ボタ

ンを押します。

(2) リモコン(RC-1007)の STATUS ボタンを押すこと

により

時間(TIME)→システムマイコンのバージョン(SYS

Ver) →システムマイコンのバージョンアップ日

(SYSDate)→DSP のバージョン (DSPVer) → DSP

のバージョンアップ日(DSPDate)→ドライブマイ

コンのバージョンアップ日 (DrDate) →ESS のバー

ジョン (EssVer) → Ess のバージョンアップ日 (Ess

Date) →地域番号 (RegionNo.)

の順に表示されます。

(3) 解除するにはAC コードを抜きます。(ACOFF)

( 注 1) DVD メカのドライブバージョン表示、ESS

のバージョン表示については、1 度ファン

クッションを DVD にしないと表示されま

せん。

5

Page 6

S-101

ADJUSTMENT

1. SETTING

(1) Connect the oscilloscope to the Y-signal, PB-signal and

C

B-signal, PR-signal and CR-signal of ZONE2 COMPO-

NENT OUT terminal and each terminate at 75 Ohms.

※ Use the 75 Ohms resistance must be 1%

(2) DVD test disc : DVDT-S01

(3) S OUT of DVD player is connected to AUX1 S IN.

2. Before Adjustment

2.1. Setting the Oscilloscope as below.

(1) PB/CB, PR/CR

(a) TIME/DIV : 10μs

(b) VOLT/DIV : 100mV

(Use the probe : x10 )

(2) Y

(a) TIME/DIV : 10μs

(b) VOLT/DIV : 200mV

(Use the probe : x10 )

Power on. Power Supply

USA & Canada : 120V

Europe : 230V

Japan : 100V

China & Korea : 220V

調整

1. セッティング手順

(1) セットの ZONE2COMPONENTOUT の端子(Y,PB/CB,

PR/CR)をそれぞれオシロスコープ(終端抵抗:75Ω)

に接続します。

※ 75Ω 抵抗は 1%品を使用する事。

(2) DVD テストディスク:DVDT-S01 を用意します。

(3) DVD プレーヤーの SOUT を AUX1SIN に接続します。

2. 調整のまえに

2.1. オシロスコープを下記に設定

(1) PB/CB,PR/CR

(a) TIME/DIV : 10μs

(b) VOLT/DIV : 100mV

(プローブ x10 使用)

(2) Y

(a) TIME/DIV : 10μs

(b) VOLT/DIV : 200mV

(プローブ x10 使用)

電源電圧 : 100V

2.2. Setup the DVD player and confirmation of the

stators

(1) Set to "INTERLACED" mode at the COMPONENT OUT.

(2) Confirm the DVD player’s out put level is equal as the

item 2.4. in following.

2.3. Preparation

(1) Push the FUNCTION knob to select "AUX1" input.

(2) Push [OPEN/CLOSE] button of DVD player, then open

the Disc Tray.

Set DVD test disc (DVDT-S01) on the Disc Tray, and

then push [CLOSE] button.

(3) DVD player FL display appear "STOP", push [PLAY] but-

ton to playback DVD.

(4) Push the [DISPLAY] button of remote control of DVD

player unit and then appear the ON-Screen Display (GUI)

on the monitor TV.

(5) Push the [+10] and [2] button, select Title 12 of DVD.

(6) Push the [ENTER] button, playback Title 12.

(color bar 75%)

2.2. DVD プレーヤの設定と確認

(1) COMPONENTOUTの設定を"インターレース "にします。

(2) DVD プレーヤーの出力が以下 2.4. に合っていることを

確認します。

2.3. 準備手順

(1) FUNCTION ノブを押し、入力を "AUX1" に切り替えます。

(2) DVD プレーヤーの「OPEN/CLOSE」ボタンを押しトレイ

を開き、トレイ上に DVD テストディスク(DVDT-S01)

をセット後、「CLOSE」ボタンを押します。

(3) DVD プレーヤーの表示管上に "STOP" が表示されてか

ら、「PLAY」ボタンを押し、ディスクを再生します。

(4) DVD プレーヤーのリモコンの「DISPLAY」ボタンを押

しグラフィカル・ユーザー・インターフェイス (GUI) 画

面を出します。

(5) 番号ボタンの「 +10 」 , 「 2 」ボタンを押し、Title12 を選択

します。

(6) 「ENTER」ボタンを押し、Title12 を再生します。

(75%カラーバー信号)。

6

Page 7

S-101

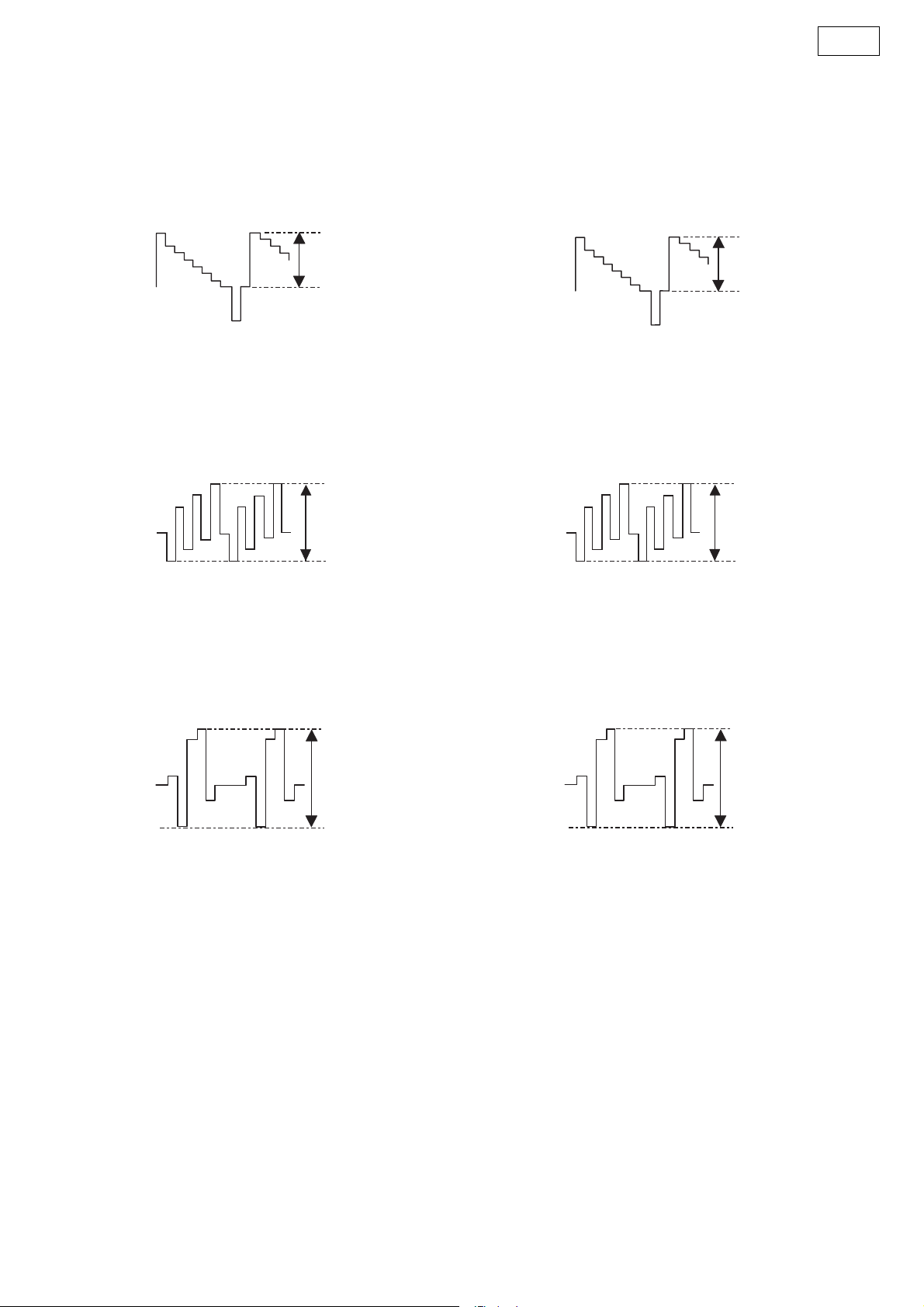

2.4. Procedure

(1) Adjust the signal of COMPONENT OUT by the wave of

oscilloscope.

(a) Target, Y-signal

Point : 1U-3695-3 VR601

Adjustment Value : 714 ± 35mV

Waveform

Y

Y-signal COMPONENT OUT

(b) Target, P

Point : 1U-3695-3 VR602

Adjustment Value : *525 ± 25mV

Waveform

B/CB-signal

PB

2.4. 手順

(1) COMPONENTOUTの信号レベルをオシロスコープ上の

波高値で調整します。

(a) Y 信号レベル

調整個所 : 1U-3695-3VR601

調整値 : 714 ± 35mV

波形

Y

COMPONENTOUT の Y 信号レベル

B/CB 信号レベル

(b) P

調整個所 : 1U-3695-3VR602

調整値 : 525 ± 25mV

波形

PB/CB

PB/CB-signal COMPONENT OUT

(c) Target, PR/CR-signal

Point : 1U-3695-3 VR603

Adjustment Value : *525 ± 25mV

Waveform

PR/CR

PR/CR-signal COMPONENT OUT

* : 486 ± 10mV for U.S.A. & Canada model

COMPONENTOUT の PB/CB 信号レベル

(c) PR/CR 信号レベル

調整個所 : 1U-3695-3VR603

調整値 : 525 ± 25mV

波形

PR/CR

COMPONENTOUT の PR/CR 信号レベル

7

Page 8

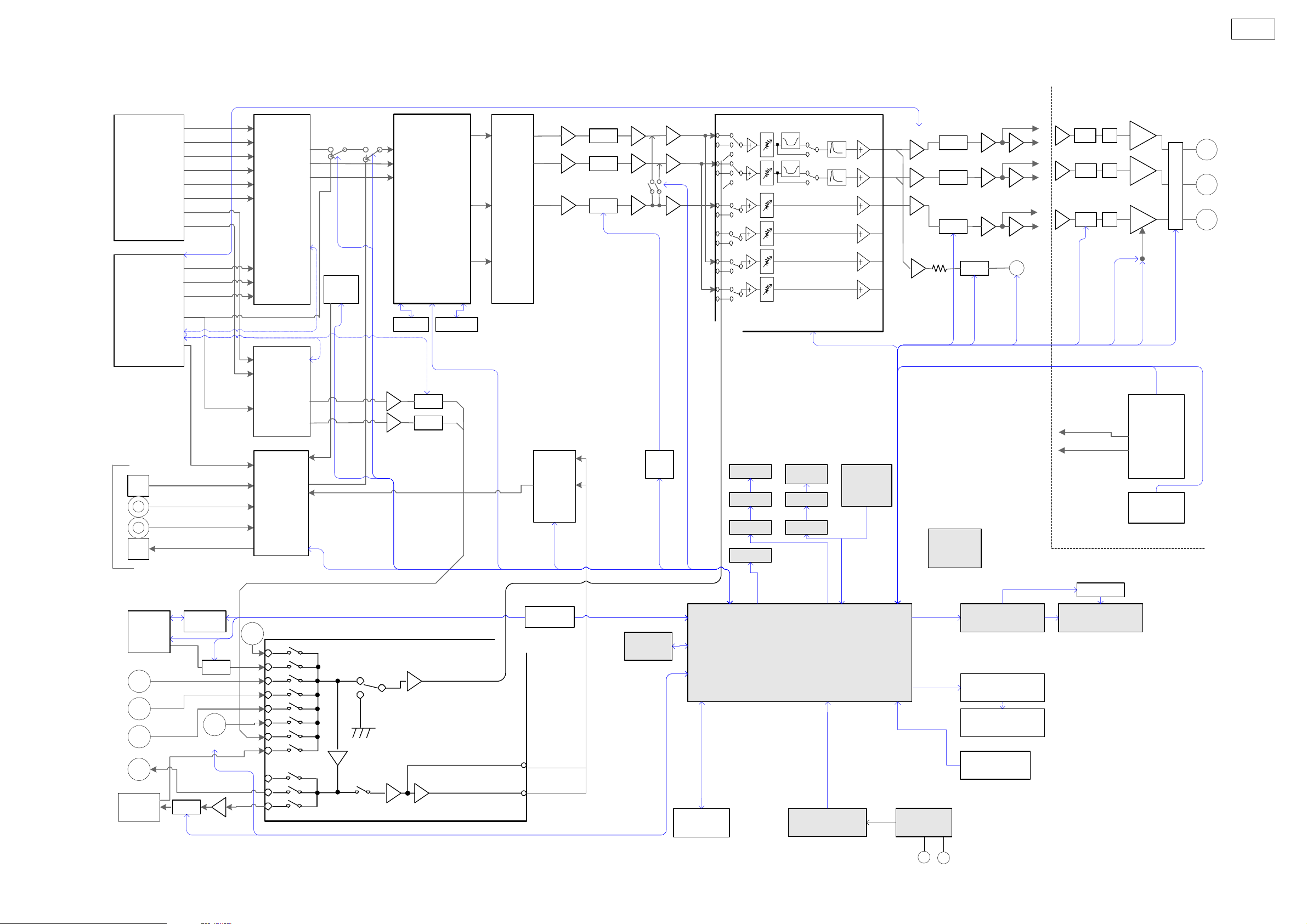

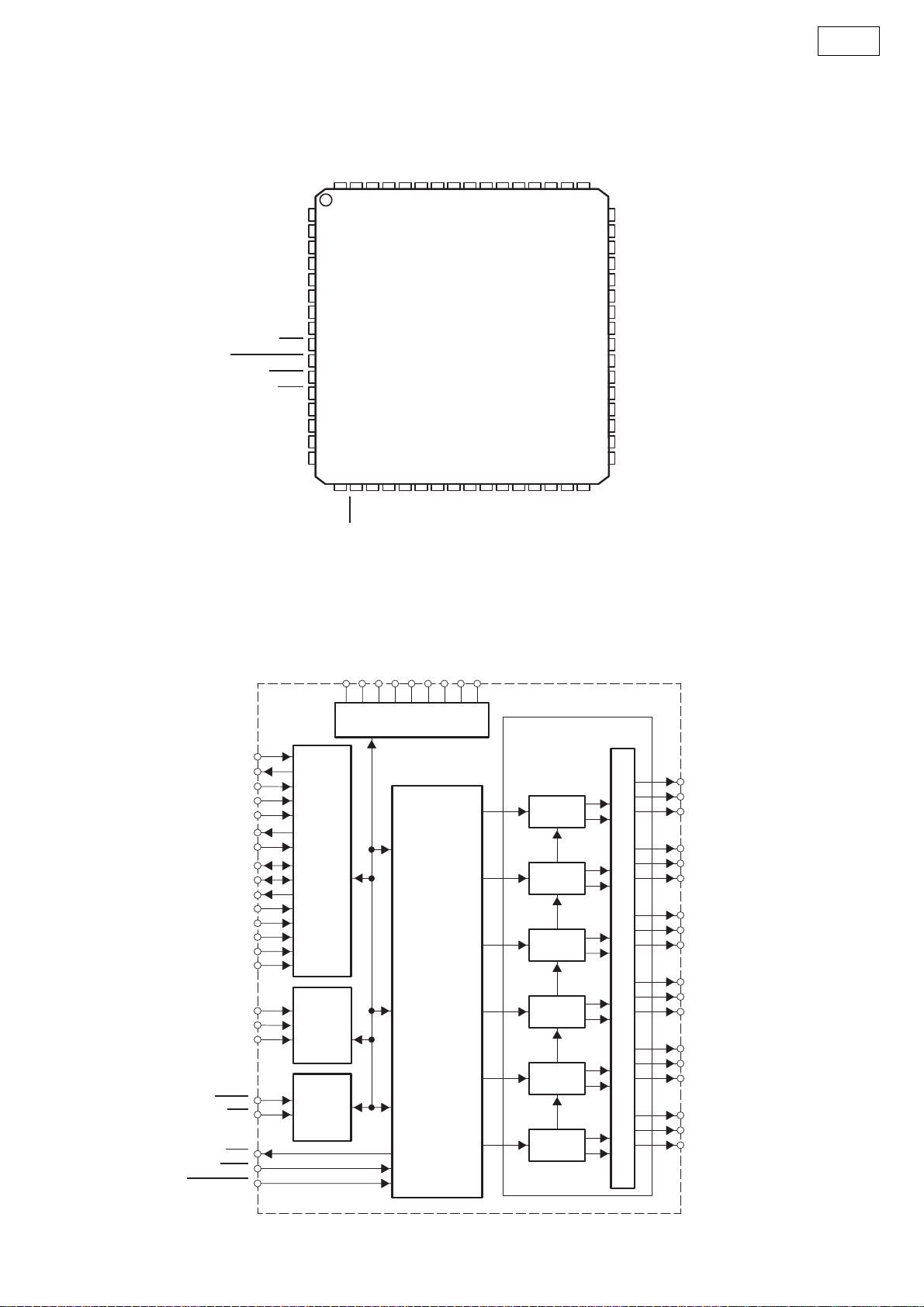

BLOCK DIAGRAM

S-101

㪜㫏㫋㪅

㪛㫀㪾㫀㫋㪸㫃㩷㪠㫅

㫏㪊

㪜㫏㫋㪅

㪘㫅㪸㫃㫆㪾㩷㪠㫅

㫏㪊

㪪㪘㪚㪛

㪛㪜㪚㪦㪛㪜㪩

㪚㪯㪛㪉㪎㪌㪊㪩

㪠㪉㪪㩷㪦㪬㪫

㪛㪭㪛

㪛㪜㪚㪦㪛㪜㪩

㪧㪅㪧㪚㪤㪆㪤㪧㪊㪆㪮㪤㪘

㪛㪜㪚㪦㪛㪜

㪜㪪㪍㪈㪊㪏

㪪㪧㪛㪠㪝㩷㪦㪬㪫

㪦㪧㪫

㪠㪥㪈

㪚㪦㪘

㪠㪥

㪚㪦㪘

㪠㪥

㪦㪧㪫

㪦㪬㪫

㪫㪬㪥㪜㪩

㪫㪬㪥㪜㪩

㪧㪘㪚㪢

㪧㪘㪚㪢

㪣㪚㪎㪉㪈㪊㪈

㪣㪚㪎㪉㪈㪊㪈

㪘㪥㪘

㪣㪆㪩

㪠㪥

㪣㪆㪩

㪘㪥㪘

㪠㪥

㪣㪆㪩

㪘㪥㪘

㪠㪥

㪣㪆㪩

㪘㪥㪘

㪦㪬㪫

㪪㪚㪘㪩㪫

㪦㪬㪫

㩿㪜㪉㩷㫆㫅㫃㫐㪀

㪛㪪㪛㩷㪦㪬㪫

㪛㪪㪛㩷㪝㪣

㪛㪪㪛㩷㪝㪩

㪛㪪㪛㩷㪪㪣

㪛㪪㪛㩷㪪㪩

㪛㪪㪛㩷㪚

㪛㪪㪛㩷㪪㪮

㪛㪪㪛㩷㪤㪠㪯㩷㪣

㪛㪪㪛㩷㪤㪠㪯㩷㪩

㪧㪚㪤㩷㪝㪣㪆㪝㪩

㪧㪚㪤㩷㪪㪣㪆㪪㪩

㪧㪚㪤㩷㪚㩷㪆㪪㪮

㪧㪚㪤㩷㪤㪠㪯㩷㪣㪆㪩

㪩㪯㪇㪄㪍䉕㪪㪜㪣㪜㪚㪫䈚䈩ജ

㪩㪛㪪

㪣㪚㪎㪉㪎㪉㪇

㪣㪆㪩

㪤㪬㪫㪜

㪘㪥㪘

㪠㪥

㪧㫆㫉㫋㪸㪹㫃㪼㩷㪠㫅

㩿㪽㫉㫆㫅㫋㩷㫇㪸㫅㪼㫃㪀

㪪㪚㪘㪩㪫㩷㪠㪥

㪣㪆㪩

㪤㪬㪫㪜

㪝㪩㪠㪥㩷㪪㪮

㪩㪜㪚㩷㪦㪬㪫㪈

㪂

㪪㪚㪘㪩㪫㪶㪤㪬㪫㪜

㪛㪪㪛㩷㪠㪥

㪧㪚㪤㩷㪠㪥

㪩㪯㪈

㪪㪘㪥㪶㪛㪦

㪪㪘㪥㪶㪛㪠

㪪㪘㪥㪶㪚㪢

㪪㪘㪥㪶㪚㪜

㫀㪧㫆㪻

㫀㫅

㪧㪚㪤㩷㪝㪣㪆㪝㪩

㪧㪚㪤㩷㪚㪆㪪㪮

㪛㪪㪛

㪧㪚㪤㩷㪪㪣㪆㪪㪩

㪛㪸㫋㪸㩷㪪㪼㫃㪼㪺㫋㫆㫉

㪛㪪㪛㪄㪧㪚㪤㩷㪚㫆㫅㫍㪼㫉㫋

㪛㪪㪛㪆㪜㪯㪫

㪪㪜㪣㪶㪝㫊㪈

㪠㪥㪠㪫

㪜㪯㪫

㪛㪪㪛㪆㪧㪚㪤

㪛㪘㪚

㪛㪪㪛㪈㪎㪐㪈

㩿㪩㪼㪺㫆㫌㫋㪆

㪪㪚㪘㪩㪫㪀

㪩㪯

㪩㪯

㪛㪠㪩

㪩㪯

㪣㪚㪏㪐㪇㪌㪎

㪆㪫㪶㪤㪬㪫㪜

㪆㪪㪰㪩

㪆㪫㪬㪥㪜㪛

㪪㪫㪜㪩㪜㪦

㪩㪜㪚㩷㪦㪬㪫

㪤㪠㪯

㪛㪘㪫㪘

㪚㪣㪢

㪩㪜㪪㪜㪫

㪚㪜

㪬㪪㪙

㪪㪧㪛㪠㪝

㪛㪠㪩

㪘㪛

㪠㪥

㪤㫌㫃㫋㫀 㪤㫌㫃㫋㫀

㪛㪠㪩

㪤㪠㪯㪆㪤㪬㪣㪫㪠

㪠㪉㪪㩷㪛㪘㪫㪘

㪦㪬㪫

㪬㪪㪙

㪤㪦㪛㪬㪣㪜

㪬㪪㪙㪶㪫㪯㪛

㪬㪪㪙㪶㪩㪯㪛

㪬㪪㪙㪶㪚㪣㪢

㪬㪪㪙㪶㪩㪪㪫

㪬㪪㪙㪶㪚㪜

㪬㪪㪙㪶㪩㪜㪨

㪬㪪㪙㪶㪤㪦㪛㪜

㪬㪪㪙㪶㪧㪦㪮㪶㪦㪥

㪩㪜㪚㩷㩷㪣㪆㪩

㪛㪠㪩㪆㪚㪦㪛㪜㪚㪶㪚㪣㪢

㪛㪠㪩㪶㪚㪜

㪛㪠㪩㪆㪚㪦㪛㪜㪚㪶㪛㪠㪥

㪛㪠㪩㪶㪛㪦㪬㪫

㪛㪠㪩㪶㪩㪪㪫

㪆㪠㪥㪫㪈

㪠㪥㪧㪬㪫

㪪㪜㪣㪜㪚㪫㪦㪩

㪂

㪤㪬㪣㪫㪠㪆㪛㪠㪩

㪠㫅㫇㫌㫋㩷㪘㪫㪫

㪇㪆㪄㪍㪆㪄㪐㪆㪄㪈㪉㪻㪙

㪄

㪛㪪㪧

㪪㪿㪸㫉㪺㩷㪜㪯㩿㪨㪝㪧㪀

IN

DATP20:FL/FR

DAIP19:C/SW

DAIP18:SL/SR

OUT

DAIP16:FL/FR

DAIP16:0/SW

DAIP15:0/0

DAIP14:RECL/RECR

㪍㪋㪤

㪪㪛㪩㪘㪤

㪘㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

㪂

㪜㪣㪜㪚㪅㪭㪩㩷㩷㪙㪛㪊㪏㪈㪈

㪄

㪣㪆㪩

㪪㪮

㪩㪜㪚㩷㪣㪆㪩

㪈㪍㪤㩷㪩㪦㪤

㪘㪥㪘㪣㪦㪞

㪛㪠㪩㪜㪚㪫

㪝㪣㪘㪞㪊㪘

㪙㪬㪪㪰㪈

㪘㪚㪢㪈

㪩㪦㪤㪶㪩㪪㪫

㪛㪪㪧㪶㪩㪪㪫

㪭㪧㪧

㪩㪆㪮

㪙㪬㪪㪰㪶㪜㪧㪩㪦㪤

㩿㪉㪆㪉㪀

㪘㪛㪈㪏㪊㪎

㪏㪺㪿

㪚㪦㪛㪜㪚

㪈㪆㪉

㩿㪛㪘㪚㪀

㪛㪪㪧㪶㪠㪦㪶㪧㪦㪮

㪛㪪㪧㪶㪚㪦㪩㪜㪶㪧㪦㪮

㪛㪪㪧㪶㪦㪪㪚㪶㪦㪥

㪛㪪㪧㪤㪠㪪㪦

㪛㪪㪧㪤㪦㪪㪠

㪛㪪㪧㪪㪧㪠㪚㪣㪢

㪛㪪㪧㪪㪧㪠㪚㪪

㩿㪛㪠㪩㪆㪚㪦㪛㪜㪚㪶㪚㪣㪢㪀

㩿㪛㪠㪩㪆㪚㪦㪛㪜㪚㪶㪛㪠㪥㪀

㪘㪆㪛㩷㪦㪬㪫㩷㪄

㪘㪆㪛㩷㪦㪬㪫㩷㪂

㪘㪛㪈㪏㪊㪎

㪚㪦㪛㪜㪚

㩿㪘㪛㪚㪀

㪚㪣㪘㪫㪚㪟

㪚㪦㪛㪜㪚㪶㪩㪪㪫

㪂㪌㪭㪆㪂㪊㪅㪊㪭

㪚㫆㫅㫍㪅

㪏㪺㪿

㪉㪆㪉

㪝㫀㫃㫋㪼㫉

㪣㪆㪩

㪪㪮

㪛㪘㪚㪶㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

㪪㪬㪙㪶㪪㪬㪤

㪜㪉㪧㪶㪛㪠

㪜㪉㪧㪶㪛㪦

㪜㪉㪧㪶㪚㪪

㪜㪉㪧㪶㪚㪢

㪄

㪄

㪄

㪣㪦㪞㪠㪚

㪜㪜㪧㪩㪦㪤

㪙㪩㪐㪊㪣㪏㪍

㩿㪈㪍㫂㪀

㪄

㪄

㪄

㪙㪪㪜

㪜㪩㪩㪤㪬㪫㪜

㪪㪜㪣㪚㪣㪢

㪦㪧㪶㪚㪣㪢

㪦㪧㪶㪚㪜

㪦㪧㪶㪛㪦

㪦㪧㪶㪛㪠

㪙㪜㪶㪦㪥

㪛㪝㪩㪪㪫

㪧㪣㪣㪶㪩㪪㪫

㪛㪭㪛㪶㪩㪪㪫

㫋㫆㩷㪛㪭㪛㩷㪛㫉㫀㫍㪼㪆

㪭㫀㪻㪼㫆㩷㪙㪣㪦㪚㪢

㪘㪥㪘㪣㪦㪞

㪛㪠㪩㪜㪚㪫

㪚㪣㪪㪶㪪㪮

㪦㪧㪥㪶㪪㪮

㪦㪧㪥㪶㪛㪩㪭

㪚㪣㪪㪶㪛㪩㪭

㪭㪶㪚㪦㪥㪫

㪣㪛㪶㪚㪦㪥㪫

㪧㪩㪦㪞㪆㪫㪥㪫㪜㪩

㪭㪛㪜㪫㪈

㪭㪛㪜㪫㪉

㪇㩷㫋㫆㩷㪄㪈㪇㪊㪻㪙

㪠㫅㫇㫌㫋㩷㪞㪸㫀㫅㩷㪘㫄㫇㪑

㩷㪇㪆㪂㪍㪻㪙

㪉㪊㪉㪚

㪣㪤㪪㪉㪇㪉

㪎㪋㪣㪭㪇㪏

㪫㪩㪠㪞㪞㪜㪩

㪫㪩㪠㪞㪞㪜㪩

㪭㪠㪛㪜㪦㪶㪘

㪭㪠㪛㪜㪦㪶㪙

㪭㪠㪛㪜㪦㪶㪚

㪭㪠㪛㪜㪦㪶㪛

㪭㪤㪬㪫㪜㪈

㪭㪤㪬㪫㪜㪉

㪤㪸㫀㫅㩷㪭㫆㫃

㪈㪻㪙㩷㫊㫋㪼㫇

㪜㪣㪜㪚㪅㪭㪩㩷㩷㪙㪛㪊㪏㪈㪈

㩿㪈㪆㪉㪀

㪊㪏㪈㪈㪚㪣㪢

㪊㪏㪈㪈㪛㪘㪫㪘

㪩㪜㪤㪦㪫㪜

㪚㪯㪘㪈㪌㪈㪈

㪎㪋㪣㪭㪇㪏

㪪㪰㪪㪫㪜㪤㩷㫌㪚㪦㪤

㪤㪊㪇㪍㪉㪎㪝㪟㪧㪞㪧

㩿㪈㪉㪏㫇㫀㫅㩷㪊㪏㪋㫂㪆㪊㪈㫂㪀

㩷㪠㪆㪦

㪫㪯㪛㪉㪊㪉㪚

㪩㪯㪛㪉㪊㪉㪚

㪢㪜㪰㪇

㪢㪜㪰㪈

㪡㪦㪞㪶㪘

㪡㪦㪞㪶㪙

㪫㪘㪚㪫㩷㪪㪮㩷㪆

㪩㪦㪫㪅㪜㪥㪚㪦㪛㪜㪩

㪦㫌㫋㫇㫌㫋㩷㪞㪸㫀㫅㩷㪘㫄㫇㪑

㩷㪇㪆㪂㪉㪆㪂㪋㪆㪂㪍㪆㪂㪏㪆

㪂㪈㪇㪆㪂㪈㪉㪻㪙

㪩㪜㪤㪦㪚㪦㪥

㪩㪜㪚㪠㪜㪭㪜㪩

㪞㪧㪈㪬㪜㪉㪎㪈㪯

㪩㪜㪤㪦㪚㪦㪥

㪟㪞㪘㪠㪥

㪣

㪩

㪪㪮

㪟㪆㪧㪄㪈

㪘㪆㪛

㪛㪠㪤㪤㪜㪩㪶㪠㪥

㪧㪣㪘㪰㩷㪢㪜㪰

㪧㫉㪼㩷㪘㫄㫇

㪥㪡㪤㪉㪇㪍㪏

㪟㪆㪧㩷㪘㫄㫇㪄㪈

㪘㪺㫋㫀㫍㪼㩷㪙㫃㫆㪺㫂

㪜㪯㪫㪶㪛㪘㪫㪘

㪜㪯㪫㪶㪚㪣㪢

㪝㪣㪶㪛㪘

㪝㪣㪶㪚㪪

㪝㪣㪶㪚㪢

㪝㪣㪶㪩㪪㪫

㪫㪦㪬㪚㪟

㪪㪜㪥㪪㪦㪩㩷㪠㪚

㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

㪧㪩㪜㪶㪤㪬㪫㪜

㪪㫋㪸㫅㪻㪹㫐

㪪㪫㪦㪧㩷㪢㪜㪰

㪘㪛㪭㪄㪪㪈㪇㪈

㪛㫀㪽㪽㪅㩷㪦㫌㫋㫇㫌㫋

㪄 㪄

㪄 㪄

㪄 㪄

㪤㪬㪫㪜

㪟㪆㪧㩷㪤㪬㪫㪜

㪪㪜㪩㪠㪄㪧㪘㪩㪘

㪚㪦㪥㪭㪜㪩㪫㩷㪠㪚

㪙㪬㪉㪇㪐㪇㪝

㪝㪣㩷㪛㪩㪠㪭㪜㪩

㪤㪍㪍㪇㪇㪌㪘㪟㪧

㪝㪣㪛

㪛㪠㪤㪤㪜㪩

㪪㪜㪥㪪㪦㪩㩷㪠㪚

㪟㪆㪧

㪟㪧㩷㪪㪮

㪉㪌㪧㩷㪛㪄㪪㫌㪹

㪣㪦㪞㪠㪚㩷㪘㪆㪙㪆㪚

㪛㫀㪽㪽㪅㩷㪠㫅㫇㫌㫋

㪚㫌㫉㫉㪅㪣㫀㫄㫀㫋㫋㪼㫉

㪝㪣㪂

㪝㪣㪄

㪝㪩㪂

㪝㪩㪄

㪪㪮㪂

㪪㪮㪄

㪤㪬㪫㪜

㪤㪬㪫㪜 㪘㪆㪛

㪘㪣㪚㪆

㪧㪼㪸㫂㫀㫅㪾㪆

㪚㫌㫉㫉㪅㪣㫀㫄㫀㫋㫋㪼㫉

㪤㪬㪫㪜

㪧㪩㪜㪶㪤㪬㪫㪜

㪌㪇㪆㪍㪇

㪧㪅㪦㪥㪆㪦㪝㪝

㪂㪊㪈㪭

㪂㪌㪅㪇㪭㪶㪥㪪㪮

㪧㪚㪤㪄㪈㪏㪇㪊

㪭㫆㫃㫋㪸㪾㪼㩷㪸㪻㫁㫌㫊㫋

㪢㪜㪰㩷㪣㪜㪛

㪪㪫㪘㪥㪛㪙㪰㩷㪣㪜㪛

㪪㪈㪇㪈㩷㪘㪬㪛㪠㪦㩷㪙㪣㪦㪚㪢㩷㪛㪠㪘

㪧㪚㪤㪄㪈㪏㪇㪉

㪘㪆㪛

㪧㪚㪤㪄㪈㪏㪇㪉

㪘㪆㪛

㪘㪤㪧㩷㪤㪬㪫㪜

㪏㫊㫋㪼㫇

㪛㪪㪮㪄㪪㪈㪇㪈

㪧㫆㫎㪼㫉㩷㪘㫄㫇

㪫㪘㪪㪌㪇㪍㪍㪆㪫㪘㪪㪌㪈㪉㪈

㪙㪫㪣

㪙㪫㪣

㪙㪫㪣

㪧㪩㪦㪫㪜㪚㪫

㪚㪦㪥㪥㪜㪚㪫㪶㪪㪧㪈

㪪㪤㪧㪪㩷㪬㪥㪠㪫

㪝㫉㫆㫅㫋㩷㪪㪧

㪚㫆㫅㫅㪼㪺㫋㩷㪛㪼㫋㪼㪺㫋

㪣㪦㪞㪠㪚

㪪㪧

㪫㪼㫉㫄㫀㫅㪸㫃

㪣

㪩

㪩㪜㪣㪘㪰

㪪

㪮

㪩㪣㪶㪪㪧

8

Page 9

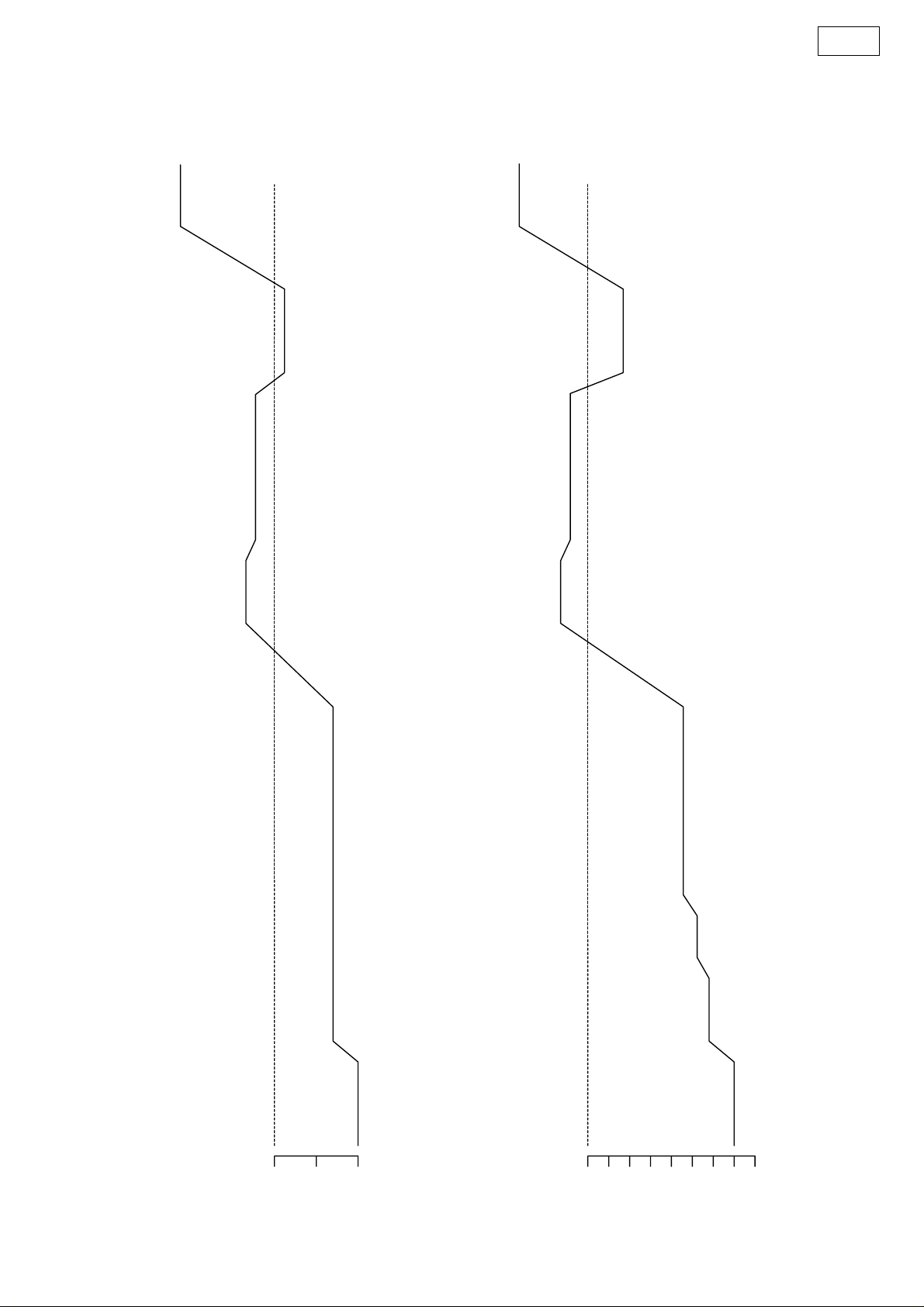

LEVEL DIAGRAM

S-101

㪂㪉㪋㪅 㪐㪻㪙

㪄㪍㪅㪐 㪻㪙

㪄㪉㪅㪊 㪻㪙

㪂㪉㪇㪅 㪏㪊㪻 㪙

㪂㪉㪋㪅 㪐㪻㪙

㪄㪈㪉㪅 㪍㪻㪙

㪄㪉㪅㪊 㪻㪙

㪂㪉㪐㪅 㪊㪌㪻 㪙

㪂㪊㪅㪊 㪈㪻㪙

㪂㪉㪅㪏 㪌㪻㪙

㪫㫆㫋㪸㫃㩷㪂㪊㪍㪅㪌㪉㪻㪙

㪂㪍㪻㪙

㪇㪻㪙㪝 㫊

㪄㪈㪇㪻 㪙㪝㫊

㪝㫉㫆㫅㫋㪄㪺㪿

㪄㪉㪇㪻 㪙㪝㫊

㪇㪻㪙㪝 㫊

㪄㪈㪇㪻 㪙㪝㫊

㪪㪮㪄㪺㪿

㪄㪉㪇㪻 㪙㪝㫊

㪂㪍㪻㪙

㪄㪊㪇㪻 㪙㪝㫊

㪄㪋㪇㪻 㪙㪝㫊

9

Page 10

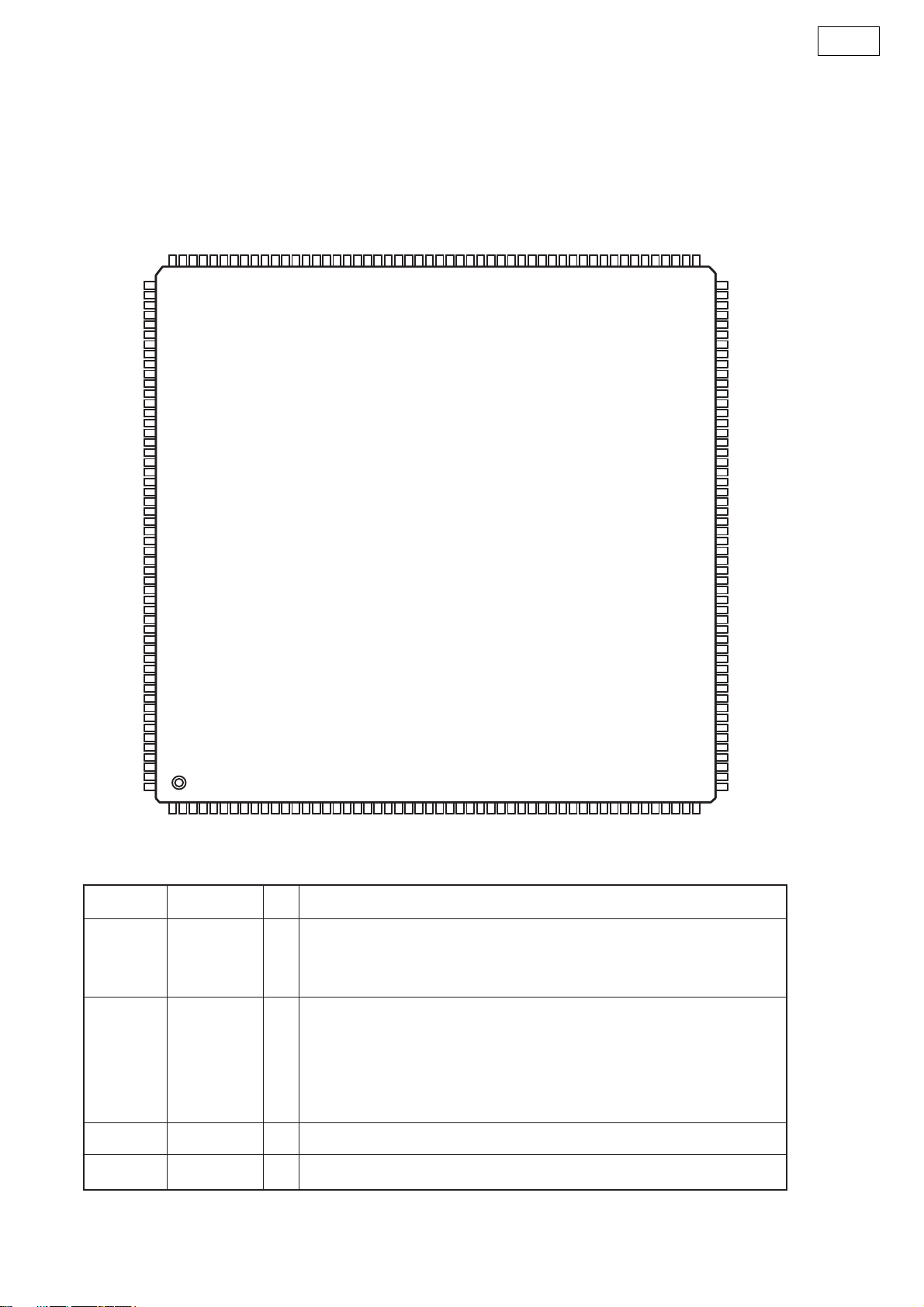

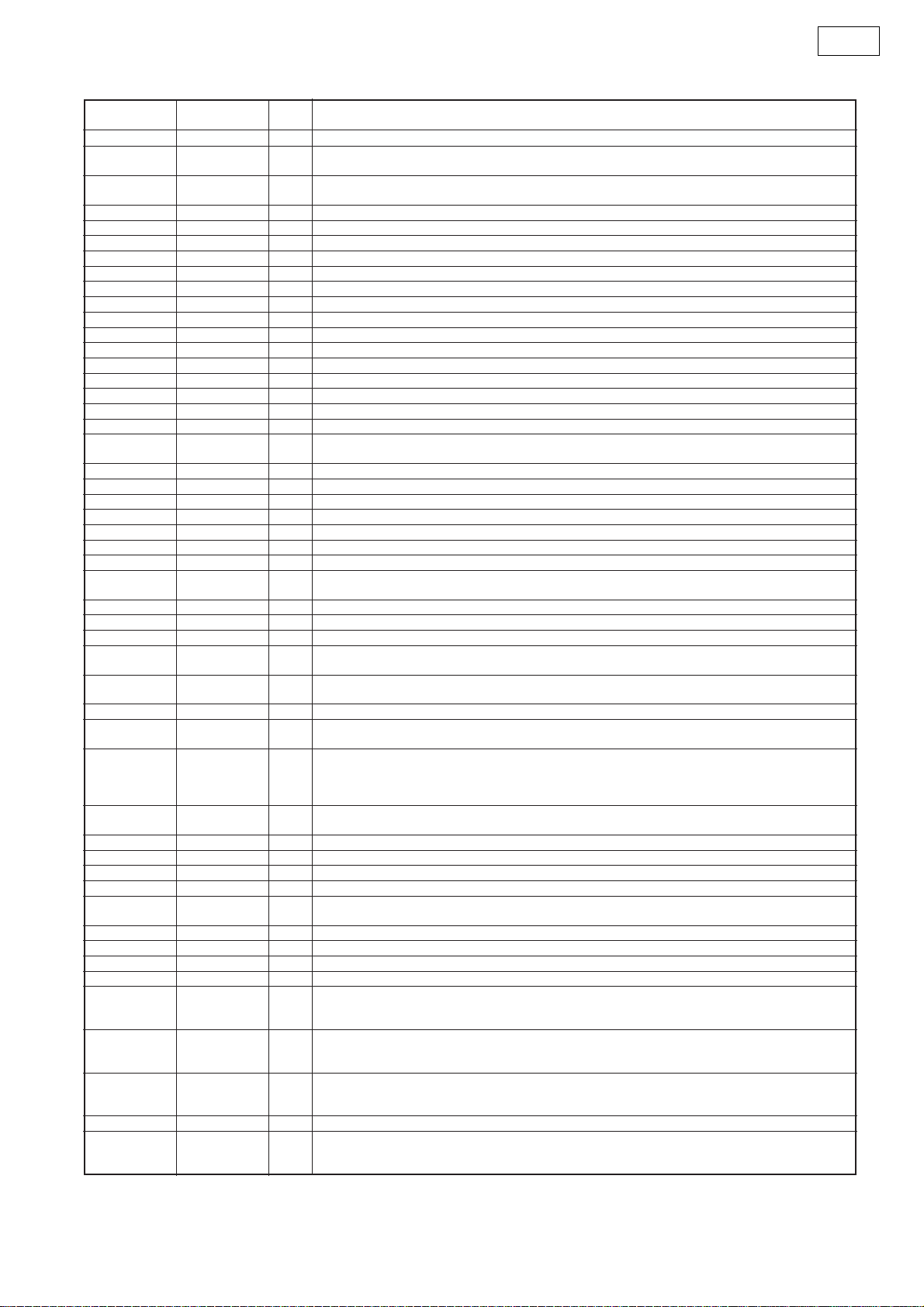

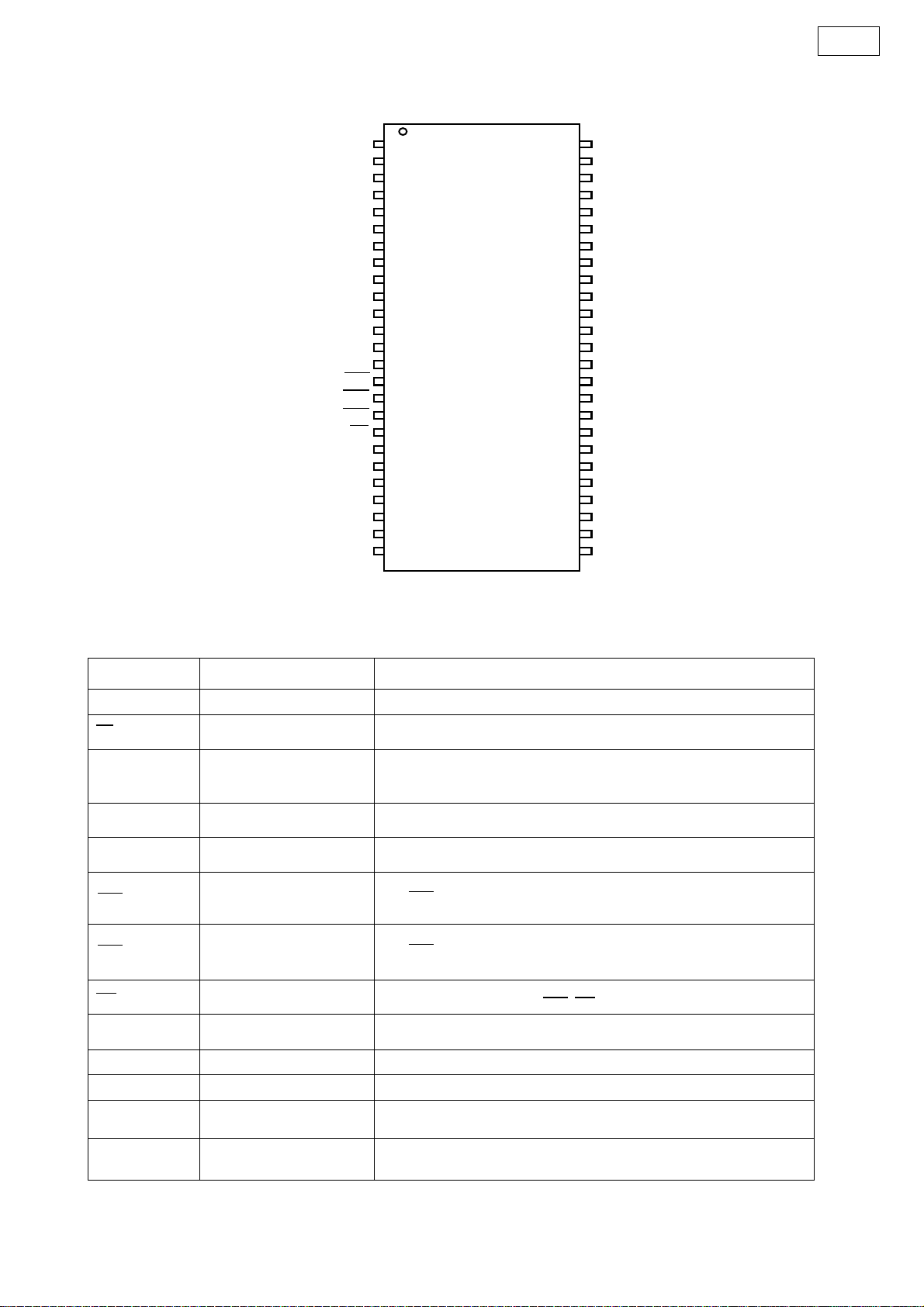

SEMICONDUCTORS / 半導体一覧表

Only major semiconductors are shown, general semiconductors etc. are omitted to list.

主な半導体を記載しています。汎用の半導体は記載を省略しています。

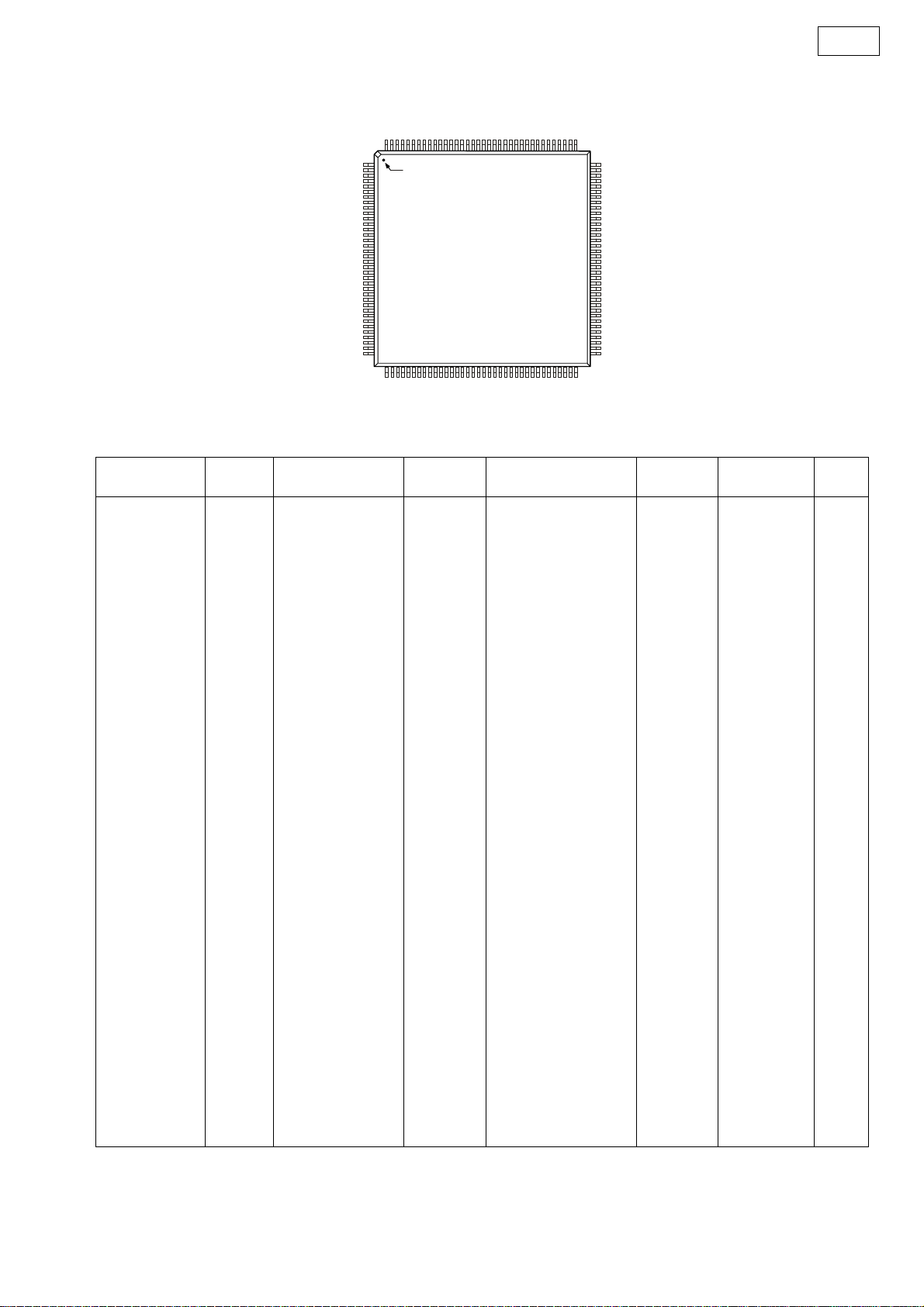

1. IC’s

ES6128F (RL-S874: U9)

VSS

HA1

HA0

HCS3FX#

HCS1FX#

HIOCS16#

HRD#

HWR#

VEE

VSS

HIORDY

HRST#

HIRQ

HRDQ#

HWRQ#

HD15

HD14

VCC

VSS

HD13

HD12

HD11

HD10

HD9

HD8

HD7

VEE

VSS

HD6

HD5

HD4

HD3

HD2

HD1

HD0

VCC

VSS

HSYNC#

VSYNC#

VSS

HA1

HA0

HCS3FX#

HCS1FX#

HIOCS16#

HRD#

HWR#

VEE

156

155

154

153

152

151

150

149

VEE

VEE

HA2

HA2

VEE

VEE

AUX[0]

AUX[0]

AUX[1]

AUX[1]

AUX[2]

AUX[2]

VSS

VSS

VEE

VEE

AUX[3]

AUX[3]

AUX[4]

AUX[4]

AUX[5]

AUX[5]

AUX[6]

AUX[6]

AUX[7]

AUX[7]

LOE#

LOE#

VSS

VSS

VCC

VCC

LCS0#

LCS0#

LCS1#

LCS1#

LCS2#

LCS2#

LCS3#

LCS3#

VSS

VSS

VEE

VEE

VSS

VSS

LD10

LD10

LD11

LD11

VSS

VSS

VEE

VEE

LD12

LD12

LD13

LD13

LD14

LD14

LD15

LD15

LWRLL#

LWRLL#

LWRHL#

LWRHL#

VSS

VSS

VEE

VEE

CAMIN0

CAMIN0

CAMIN1

CAMIN1

VSS

VSS

156

155

154

157

157

158

158

159

159

160

160

161

161

162

162

163

163

164

164

165

165

166

166

167

167

168

168

169

169

170

170

171

171

172

172

173

173

174

174

175

175

176

176

177

177

LD0

LD0

178

178

LD1

LD1

179

179

LD2

LD2

180

180

LD3

LD3

181

181

LD4

LD4

182

182

183

183

184

184

LD5

LD5

185

185

LD6

LD6

186

186

LD7

LD7

187

187

LD8

LD8

188

188

LD9

LD9

189

189

190

190

191

191

192

192

193

193

194

194

195

195

196

196

197

197

198

198

199

199

200

200

201

201

202

202

203

203

LA0

LA0

204

204

LA1

LA1

205

205

LA2

LA2

206

206

LA3

LA3

207

207

208

208

153

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051

LA4

LA5

LA6

LA4

LA5

LA6

VEE

VEE

148

152

151

150

149

148

LA7

LA8

LA9

LA7

LA8

LA9

VSS

VSS

VCC

VCC

ES6128 F Terminal Function

VSS

147

147

LA10

LA10

HIORDY

HRST#

146

145

146

145

LA11

LA12

LA11

LA12

HIRQ

144

144

LA13

LA13

HRDQ#

143

143

LA14

LA14

HWRQ#

HD15

142

141

142

141

LA15

LA16

LA15

LA16

HD14

140

140

VSS

VSS

VCC

139

139

VEE

VEE

VSS

138

138

LA17

LA17

HD13

137

137

LA18

LA18

HD12

136

136

LA19

LA19

HD11

135

135

LA20

LA20

HD10

134

134

LA21

LA21

HD9

133

133

RESET#

RESET#

HD8

132

132

TDMDX

TDMDX

HD7

131

131

VSS

VSS

VEE

130

130

VEE

VEE

VSS

HD6

HD5

HD4

HD3

HD2

HD1

HD0

129

128

127

126

125

124

123

126

TDMTSC#

TDMTSC#

122

125

124

123

122

VSS

VSS

VCC

VCC

TWS/SEL_PLL2

TWS/SEL_PLL2

TSD0/SEL_PLL0

TSD0/SEL_PLL0

129

128

127

TDMFS

TDMFS

TDMDR

TDMDR

TDMCLK

TDMCLK

PCLKQSCN

VCC

VSS

HSYNC#

VSYNC#

PCLKQSCN

121

120

119

118

117

121

120

119

118

117

TSD2

TSD3

TSD2

TSD3

TBCK

TBCK

MCLK

MCLK

TSD1/SEL_PLL1

TSD1/SEL_PLL1

PCLK2XSCN

YUV7

YUV6

PCLK2XSCN

YUV7

YUV6

116

115

114

116

115

114

NC

NC

VSS

VSS

SPDIF/PLL3

SPDIF/PLL3

YUV5

YUV5

113

113

VCC

VCC

VSS

VSS

112

112

RSD

RSD

ADVEE

ADVEE

111

111

RWS

RWS

YUV4

YUV4

110

110

RBCK

RBCK

YUV3

YUV3

109

109

NC

NC

YUV2

YUV2

108

108

XIN

XIN

YUV1

YUV1

107

107

XOUT

XOUT

YUV0

YUV0

106

106

AVEE

AVEE

DCLK

DCLK

105

105

104

104

103

103

102

102

101

101

100

100

52

52

VSS

VSS

S-101

VEE

VEE

VSS

VSS

DSCK

DSCK

DQM

DQM

DCS0#

DCS0#

99

VEE

99

VEE

98

VSS

98

VSS

97

DCS1#

97

DCS1#

96

DB15

96

DB15

95

DB14

95

DB14

94

DB13

94

DB13

93

DB12

93

DB12

92

VEE

92

VEE

91

VSS

91

VSS

90

DB11

90

DB11

89

DB10

89

DB10

88

DB9

88

DB9

87

DB8

87

DB8

86

DB7

86

DB7

85

DB6

85

DB6

84

VSS

84

VSS

83

VCC

83

VCC

82

DB5

82

DB5

81

DB4

81

DB4

80

DB3

80

DB3

79

DB2

79

DB2

78

DB1

78

DB1

77

DB0

77

DB0

76

VSS

76

VSS

75

VEE

75

VEE

74

DMBS1

74

DMBS1

73

DMBS0

73

DMBS0

72

DRAS#

72

DRAS#

71

DWE#

71

DWE#

70

DSCK_EN

70

DSCK_EN

69

DCAS#

69

DCAS#

68

VEE

68

VEE

67

VSS

67

VSS

66

DMA11

66

DMA11

65

DMA10

65

DMA10

64

DMA9

64

DMA9

63

DMA8

63

DMA8

62

DMA7

62

DMA7

61

DMA6

61

DMA6

60

VSS

60

VSS

59

VEE

59

VEE

58

DMA5

58

DMA5

57

DMA4

57

DMA4

56

DMA3

56

DMA3

55

DMA2

55

DMA2

54

DMA1

54

DMA1

53

DMA0

53

DMA0

1, 18, 27, 59,

68, 75, 92, 99,

104, 130, 148, VEE I I/O power supply.

157, 159, 164,

183, 193, 201

8, 17, 26, 34,

43, 52, 60, 67,

76, 84, 91, 98,

103, 112, 120, VSS I Ground.

129, 138, 147,

156, 163, 171,

177, 184, 192,

200, 208

23:19, 16:10,

7:2, 207:204

9, 35, 44, 83,

121, 139, 172

LA[21:0] O Device address output.

VCC I Core power supply.

FunctionI/OPin No. Pin Name

10

Page 11

S-101

Pin No. Pin Name

24 RESET# I Reset input, active low.

25 TDMDX O TDM transmit data.

28 TDMDR I TDM receive data.

29 TDMCLK I TDM clock input.

30 TDMFS I TDM frame sync.

31 TDMTSC# O TDM output enable.

TWS O Audio transmit frame sync.

SEL_PLL2 I System and DSCK output clock frequency selection is made at the rising edge of RESET#.

The matrix below lists the available clock frequencies and their respective PLL bit settings.

SEL_PLL2 SEL_PLL1 SEL_PLL0 Clock Type

000VCOoff.

001DCLK

32 0 1 0 Bypass mode

0 1 1 DCLK x 2

1 0 0 DCLK x 4.5

1 0 1 DCLK x 3

110DCLKx3.5z

1 1 1 DCLK x 4

33

36

37 TSD[2] O Audio transmit serial data output 2.

38 TSD[3] O Audio transmit serial data output 3.

39 MCLK I/O Audio master clock for audio DAC.

40 TBCK O Audio transmit bit clock.

41 SEL_PLL3 Clock Source

42,48 NC No connect pins. Leave open.

45 RSD I Audio receive serial data.

46 RWS I Audio receive frame sync.

47 RBCK I Audio receive bit clock.

49 XIN I Crystal input.

50 XOUT O Crystal output.

51 AVEE I Analog power for PLL.

66:61, 58:53 DMA[11:0] O DRAM address bus [11:0]

69 DCAS# O DRAM column address strobe,

70 DSCK_EN O DRAM clock enable.

71 DWE# O DRAM write enable.

72 DRAS# O DRAM row address strobe.

73 DMBS0 O SDRAM bank select 0.

74 DMBS1 O SDRAM bank select 1.

96:93, 90:85,

82:77

97, 100 DCS[1:0]# O SDRAM chip select [1:0]

101 DQM O Data input/output mask.

102 DSCK O Output clock to SDRAM.

105 DCLK I 27 MHz clock input to PLL.

106 UDAC O VideoUDAC output.

107 VREF I Internal voltage to video DAC.

108 CDAC O Video CDAC output.

109 COMP I Compensation input.

110 RSET I DAC current adjustment resistor input.

111 ADVEE I Analog power for video DAC.

113 YDAC O Video YDAC output.

TSD0 O Audio transmit serial data port 0.

SEL_PLL0 I Refer to the description and matrix for SEL_PLL2 pin 32.

TSD1 O Audio transmit serial data port 1.

SEL_PLL1 I Refer to the description and matrix for SEL_PLL2 pin 32.

SPDIF O S/PDIF output.

SEL_PLL3 I Clock source select.

0 Crystal oscillator

1 DCLK input

DB[15:0] I/O DRAM data bus [15:0]

FunctionI/O

11

Page 12

S-101

Pin No. Pin Name

114 VDAC O Video VDAC output.

115 YUV7 O YUV7 pixel output data.

116 PCLK2XSCN I/O 27 MHz video output pixel clock.

117 PCLKQSCN O 13.5 MHz video output pixel clock.

118 VSYNC# I/O Vertical sync, active low.

119 HSYNC# I/O Horizontal sync, active low.

127:122 HD[5:0] I/O Host data I/O [5:0].

128 HD[6] I/O Host data I/O [6].

131 HD[7] I/O Host data I/O [7].

132 HD[8] I/O Host data bus 8.

133 HD[9] I/O Host data bus line 9.

134 HD[10] I/O Host data bus line 10.

135 HD[11] I/O Host data bus line 11.

136 HD[12] I/O Host data bus line 12.

137 HD[13] I/O Host data bus line 13.

140 HD[14] I/O Host data bus line 14.

141 HD[15] I/O Host data bus line 15.

142 HWRQ# O Host write request.

143 HRRQ# O Host read request.

144 HIRQ I/O Host interrupt.

145 HRST# O Host reset.

146 HIORDY I Host I/O ready.

149 HWR# I/O Host write.

150 HRD# O Host read.

151 HIOCS16# I Device16-bit data transfer.

152 HCS1FX# O Host select 1.

153 HCS3FX# O Host select 3.

158, 155:154 HA[2:0] I/O Host address bus.

160 AUX[0] O I2C DATA.

162 AUX[2] I/O Auxiliary ports 2.

165 AUX[3] I/O Auxiliary ports 3.

169:166 AUX[7:3] I/O Auxiliary ports 7:3.

170 LOE# O Device output enable.

176:173 LCS[3:0]# O Chip select [3:0].

197:194,

191:185, LD[15:0] I/O EPROM device data bus.

182:178

198 LWRLL# O Device low-byte write enable.

199 LWRHL# O Device high-byte write enable.

202 CAMIN0 I Camera YUV 0.

203 CAMIN1 I Camera YUV 1.

161 AUX[1]OI2CCLK.

FunctionI/O

12

Page 13

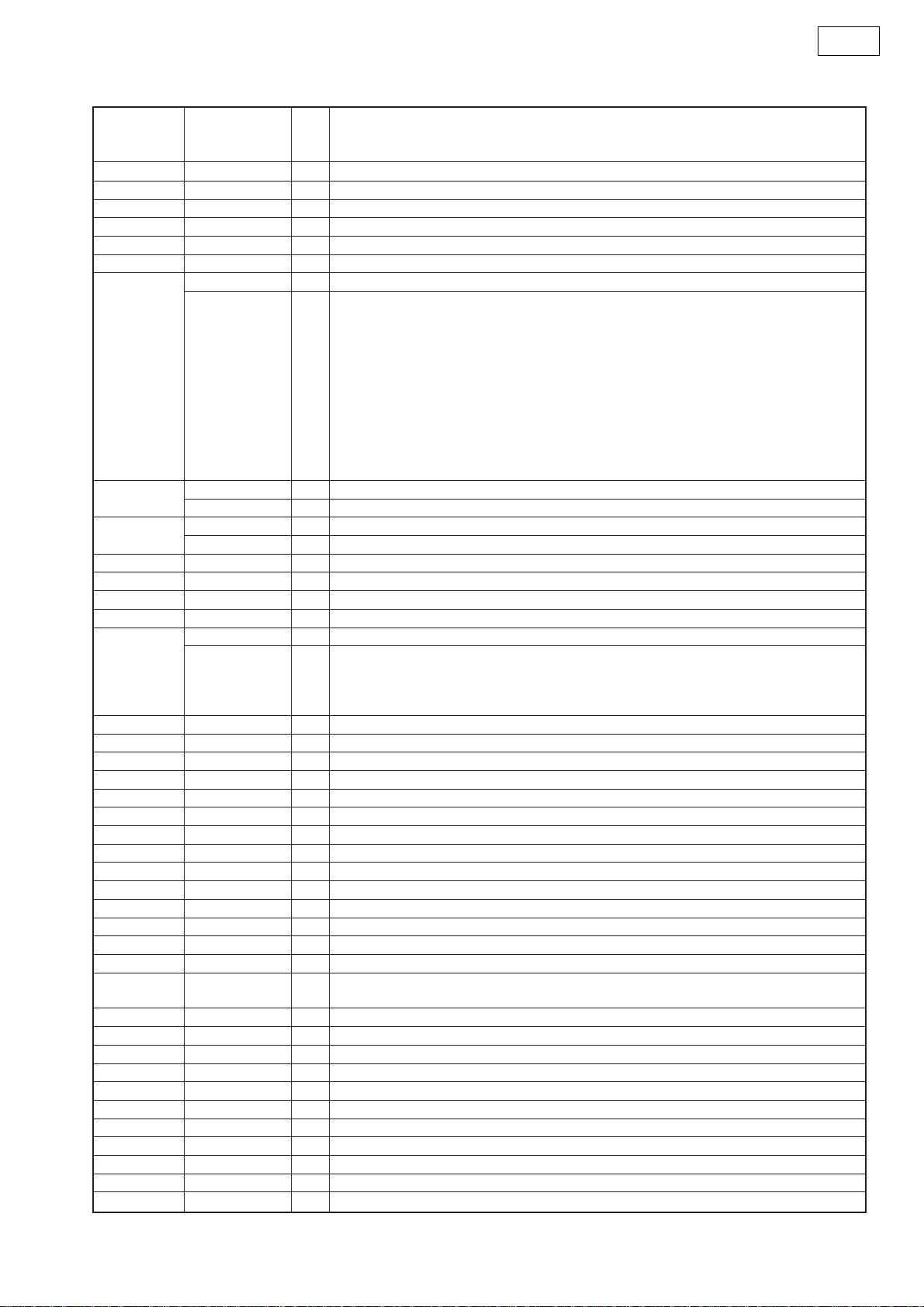

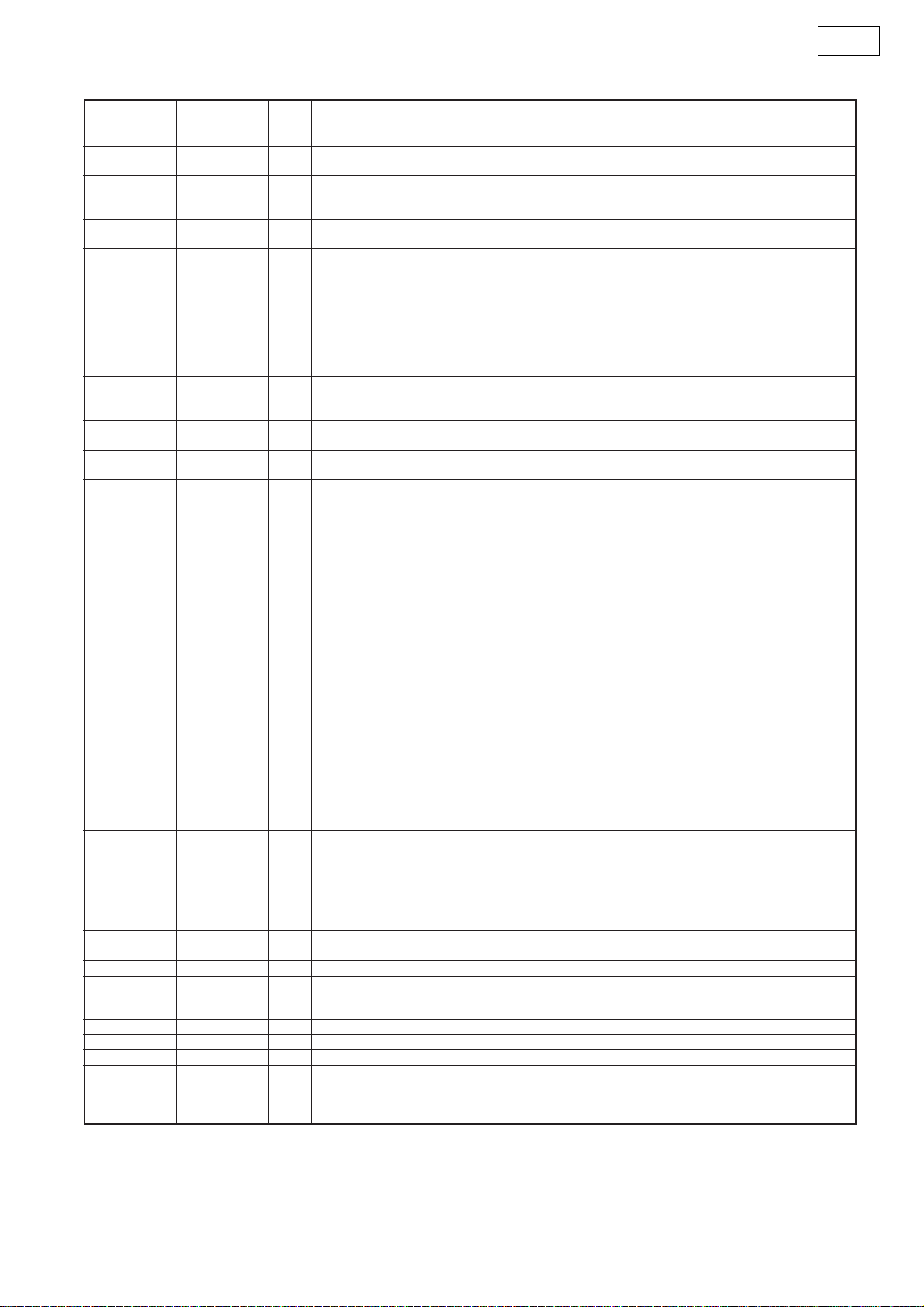

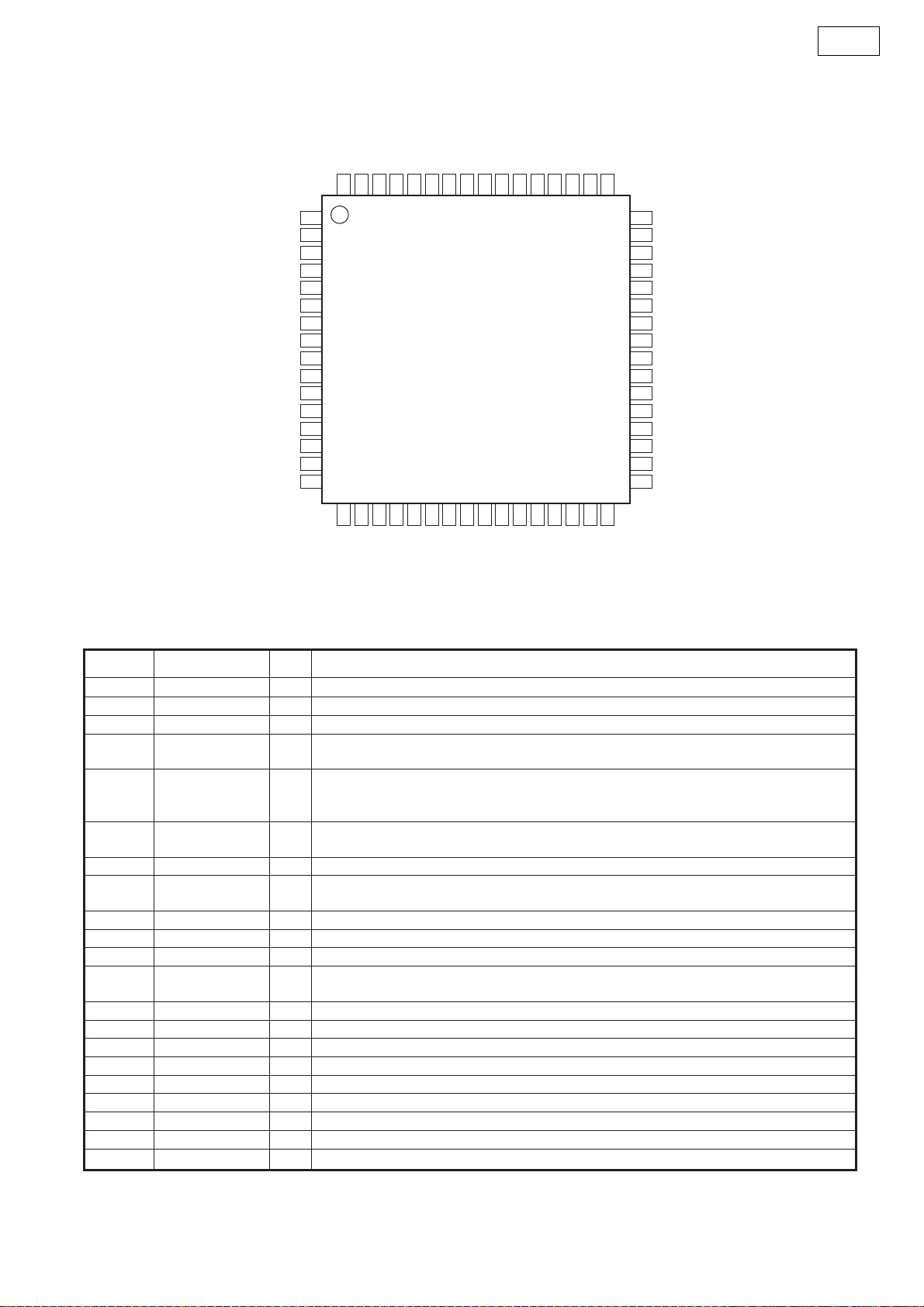

M5705 (RL-S874: U1)

AVSS-DS

XSRFIN

XSIPIN

AVDD5-DS

XSDSSLV

XSRSLINT

XSAWRC

XSRFGC

XSEFGC

XSFOCUS

XSTRACK

XSSLEG

AVDD5-DA

XSMOTOR

AVSS-DA

XSRFRPLP

XSTELP

XSVREF2

XSRFRP

XSTEXI

AVSS-AD

XSTEI

XSFEI

XSAEI

AVDD5-AD

XSSBAD

XSDFCT

XSCSJ

XSCLK

XSDATA

XSLDC

XSFGIN

XSSPDON

XSFLAG(3)

XSFLAG(2)

XSFLAG(1)

XSFLAG(0)

XMP1_7

XMP1_6

XMP1_4

XSAWRCVCO

XSVREFO

XSPDOFTR2

XSVR_PLL

XSFTROPI

XSFDO

AVSS_P L

XSPLLFTR2

AVDD5_PL

XSFDIREF

XSPDIREF

GND

XTSLRF

XTPLCK

VDD

XRA(3)

XRA(2)

XRA(1)

XRA(0)

XRA(4)

XRA(5)

XRA(6)

GND

XRA(7)

XRA(10)

XRA(11)

VDD

XRA(8)

XRA(9)

XROEJ

VDD

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

XMCSJ

XMRDJ

XMWRJ

XMINT1J

146

XMA(11)

XMA(10)

1

2

3

4

5

6

VDD

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

GND

28

29

30

31

32

33

34

35

36

37

38

39

40

41

GND

42

NC

43

44

45464748495051525354555657585960616263646566676869707172737475767778798081828384858687

VDD

VDD

GND

XOSC1

XOSC2

XMP1_3

XMFSCSJ

XMP1_2

XGPIO(2)

XMP1_1

XMRSTJ

XGPO(1)

XGPO(0)

XCRSTJ

XMPSENJ

XMALE

XMP1_0

XMD(0)

XMD(1)

XMD(2)

XMD(3)

XMD(4)

XMD(5)

XMD(6)

XMD(7)

4M DRAM

M5705

XRCASJ

XRRASJ

145

144

VDD

XMA(9)

XRSDCLK

XRWEJ

143

142

XMA(8)

XMA(7)

XRD(7)

141

XMA(6)

XRD(8)

140

XMA(5)

XRD(6)

139

XMA(4)

GND

138

XMA(3)

XRD(9)

137

XMA(2)

XRD(5)

136

XMA(1)

XRD(10)

XRD(4)

135

134

XMA(0)

XMA(12)

XRD(11)

133

88

GND

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

XRD(3)

XRD(12)

GND

XRD(2)

XRD(13)

XRD(1)

XRD(14)

XRD(0)

XRD(15)

XHD(7)

XHD(8)

XHD(6)

XHD(9)

XHD(5)

XHD(10)

XHD(4)

XHD(11)

VDD

XHD(3)

XHD(12)

XHD(2)

XHD(13)

GND

XHD(1)

XHD(14)

XHD(0)

XHD(15)

XHDRQ

XHIOWJ

XHIORJ

XHIORDY

XHDACKJ

XHINT

XHCS16J

XHA(1)

XHPDIAGJ

XHA(0)

XHA(2)

XHCS1J

XHCS3J

XHDASPJ

XMA(15)

XMA(14)

XMA(13)

S-101

ATAPI

M

Motor

Driver

Data

Separator

Digital

Servo

DVD-DSP

CD-DSP

RAM

Arbiter

Target

Search

&

MPEG

I/F

C3 ECC

EDC

MCU

ROM

M5705 Terminal Function

Pin Name

Type

2 XSRFIN I/A Analog RF signal input after passing through the equalizer

3 XSIPIN I/A Inverting input pin of data slicer

5 XSDSSLV O/A Slice level output pin

6 XSRSLINT I/A Reference current setting pin for analog data slicer

8 XSAWRC O/A Output for enlarge VCO range. Analog output from DAC buffer

9 XSRFGC O/A RF gain control output

10 XSEFGC O/A E,F gain control output

11 XSFOCUS O/A Output voltage level for focusing buffer IC

12 XSTRACK O/A Output voltage level for tracking buffer IC

13 XSSLEG O/A Output voltage level for sledge buffer IC

15 XSMOTOR O/A Output voltage level for spindle motor buffer IC

17 XSRFRPLP I/A High bandwidth low pass filter input for RFRP

18 XSTELP I/A High bandwidth low pass filter input for TE

19 XSVREF2 I/A 2.1V reference voltage input

20 XSRFRP I/A RF ripple/envelope signal input

21 XSTEXI I/A Tracking zero crossing input signal

23 XSTEI I/A Tracking error input signal

24 XSFEI I/A Focus error input signal

25 XSCEI I/A

1. Center error input signal

2. Photo Interrupt input

DescriptionPin No.

PC

MPEG

DEC.

13

Page 14

S-101

Pin Name

27 XSSBAD I/A Sub-beam addition signal input

166 XSPDIREF I/A

167 XSFDIREF I/A

169 XSPLLFTR2 I/A Data PLL loop filter pin#2

171 XSFDO O/A Output node of frequency detector charge pump circuit

172 XSFTROPI I/A Input node of loop filter OP circuit

173 XSVR_PLL I/A PLL reference voltage input

174 XSPDOFTR2 I/A Phase detector filter pin#1

175 XSVREFO O/A Reference voltage output

176 XSAWRCVCO I/A Auto Wide Range Control of VCO input pin. For enlarge VCO range in CAV mode

29 XSDFCT I Detect detection signal input

30 XSCSJ O Chip select signal for accessing control registers

31 XSCLK O Clock output for accessing control registers

32 XSDATA I/O Registers data input/output pin

33 XSLDC O Laser diode on/off control output for both CD/DVD

34 XSFGIN I Motor Hall sensor input

35 XSSPDON O Spindle motor on output

36, 37, 38, 39 XSFLAG[3:0] O These pins are used to monitor some status of servo control block

48, 51, 52 XGPIO[2:0] I/O

40 XMP1_7 I/O Internal microcontroller programmable I/O port 1.7.

41 XMP1_6 I/O Internal microcontroller programmable I/O port 1.6.

43 XMP1_5 I/O This pin is now changed to be NC.

44 XMP1_4 I/O Internal microcontroller programmable I/O port 1.4.

45 XMP1_3 I/O Internal microcontroller programmable I/O port 1.3.

47 XMP1_2 I/O Internal microcontroller programmable I/O port 1.2.

49 XMP1_1 I/O Internal microcontroller programmable I/O port 1.1.

57 XMP1_0 I/O

46 XMFSCSJ I/O Output chip select connected to external flash ROM chip enable pin

54 XMPSENJ I/O Output program store enable connected to external ROM PSENJ pin.

56 XMALE I/O This signal is used as address latch signal in address/data mux mode

70 XMCSJ I/O

71 XMRDJ I/O

72 XMWRJ I/O This signal is used as the Wire Strobe signal

73 XMINT1J I/O

74, 75, 77, 78,

79, 80, 81, 82,

83, 84, 85, 86,

87, 89, 90, 91

62, 63, 64, 65,

66, 67, 68, 69 bus for the 8-bit processor mode.

163 XTPLCK I/O PLCK test pin

164 XTSLRF I/O SLRF test pin

59 XOSC1 I Crystal input/System clock. The input frequency from outside crystal or oscillator is 33.8688MHz

60 XOSC2 O Crystal output

53 XCRSTJ I

94 XHCS1J I This pin is used to select the command block task file registers

93 XHCS3J I This pin is used to select the control block task file registers

103 XHIORJ I Asserted by the host during a host I/O read operation

104 XHIOWJ I Asserted by the host during a host I/O write operation

105 XHDRQ O

101 XHDACKJ I

99 XHCS16J O

50 XHRSTJ I Host Reset. The reset of ATA bus

100 XHINT O

XMA[15:0] I/O These pins are used as address bus

XMD[7:0] I/O

Type

Phase detector reference current generator. Connect a resistor between this pin and

ground to set reference current

Frequency detector reference current generator. Connect a resistor between this pin and

ground to set reference current

1. These pins are used as general purpose I/O bus

2. When use internal microcontroller, XGPIO[2] can be used as programmable I/O port 3.6.

Internal microcontroller programmable I/O port 1.0.

This pin is default used as the A16 (microcontroller address line 16)

1. This signal must be asserted for all microcontroller accesses to the register of this chip

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.1

1. This signal is used as the Read Strobe signal

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.0

1. This signal is an interrupt line to the microcontroller

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.7

These pins are used as data bus for the 16-bit processor mode, or the address/data mux

Chip Reset. As asserted low input generates a component reset that stops all operations within

the chip and deasserts all output signals. All input/output signals are set to input.

1.

DMA request. This pin is configured as the DMA request signal, and is used during DMA transfer

between the host and the controller. This pin is tri-stated when DMA transfers are not enabled.

2.

MPEG acknowledge. This pin is used as the ACKJ signal when MPEG interface mode is selected.

1. DMA acknowledge. This pin is configured as DACKJ, and is used as the DMA acknowledge

signal during DMA data transfers.

2. MPEG request. This pin is used as the REQ signal when MPEG interface mode is selected

1. 16-bit data select. This signal indicates that a 16-bit data transfer is active on the host data

bus. This pin is open-drain tri-state output.

2. MPEG clock. This pin is used as the CLOCK signal when MPEG interface mode is selected.

1. Host interface request. This tri-state pin is the host interrupt request, and is asserted to

indicate to the host that the controller needs attention.

2. MPEG begin. This pin is used as the BEGIN signal when MPEG interface mode is selected

DescriptionPin No.

14

Page 15

S-101

Pin Name

97 XHPDIAGJ I/O This pin is used as the Passed Diagnostics signal, and may be an input or an open-drain output

92 XHDASPJ I/O

102 XHIORDY I/O

95, 96, 98 XHA[2:0] I

106, 107, 108, 2.

109, 111, 112, 3. VCD I/F. Bit3-0 are used as VCD I/F signal when VCD function is enabled. The relationship of

113, 114, 116, bit3-0 and VCD I/F is as follow

117, 118, 119, HD0—CD-DATA

120, 121, 122, HD1—CD-LRCK

123 HD2—CD-BCK

143 XRSDCLK O This signal is the clock output for SDRAM

147 XROEJ O

142 XRWEJ O This signal is asserted low when a buffer memory write operation is active

144 XRRASJ O

145 XRCASJ O

148, 149, 151,

152, 153, 155,

156, 157, 158,

159, 160, 161

124, 125, 126,

127, 128, 129,

131, 132, 134,

135, 136, 137,

138, 139, 140,

141

4 AVDD5_DS Analog Power +5V for Data Slicer part

14 AVDD5_DA Analog Power +5V for DAC part

26 AVDD5_AD Analog Power +5V for ADC part

168 AVDD5_PL Analog Power +5V for Data PLL part

7, 55, 58, 76,

115, 146,

150, 162

1 AVSS_DS Analog Ground for Data Slicer part

16 AVSS_DA Analog Ground for DAC part

22 AVSS_AD Analog Ground for ADC part

170 AVSS_PL Analog Ground for Data PLL part

28, 42, 61,

88, 110, 130,

138, 154, 165

XHD[15.0] I/O

XRA[11:0] O 1: Normal operation

XRD[15:0] I/O These signals are the 8-bit parallel data lines to/from the buffer memory.

VDD Power +3.3V for digital core logic and pad

GND Digital Ground core logic and pad.

Type

This pin is used as the Drive Active/Slave Present signal, and is an input or an open-drain

output. This pin is used for Master/Slave drive communication and/or for driving an LED

1. I/O channel ready. This signal is driven low to extend host transfer cycles when the controller

is not ready to respond. This pin will be tri-stated when a read or write is not in progress.

2. MPEG error. This pin is used as the ERROR signal when MPEG interface mode is selected

Host address lines. The host address lines A[2:0] are used to access the various host control,

status, and data registers

1. Host data bus. This bus is used to transfer data and status between the host and the controller.

MPEG data bus 7-8. The HD[7:0] are used as the DATA [7:0] when MPEG interface mode is selected.

HD3—CD-C2PO

This signal is used as the memory output enable for external DRAM buffers. After RSTJ is

asserted, this signal will be low

This signal is used as Row address output to external DRAM buffer. After RSTJ is asserted, this

signal will be high

This signal is used as column address output to external DRAM. After RSTJ is asserted, this

signal will be high

1. RAM address lines. These are bits11-0 for addressing the buffer memory.

2. Hardware setting. The bits6-0 are used as hardware setting for some functions.

RA[9] : FLASH size is 64K/128K

1: FLASH size is 64K

0: FLASH size is 128K

RA[8] : External CPU is 8032/H8

1: 8032

0: H8

RA[7] : Microcontroller programmable I/O port 1 pin control

1: By internal microcontroller

0: By registers to decide input/output

RA[6] : System test pin output

0: System test pin output

RA[5] : For testing purpose, don’t need to set

RA[4] : IDE master/slave

1: Slave

0: Master

RA[3] : For testing purpose, don’t need to set

RA[2] : For testing purpose, don’t need to set

RA[1-0] : MCU Mode selection

11: Normal Mode (internal uP, internal address latch)

10: Outside uP Mode (ICE Mode)

01: Test mode for internal uP testing

00: Internal uP mode with external address latch

DescriptionPin No.

15

Page 16

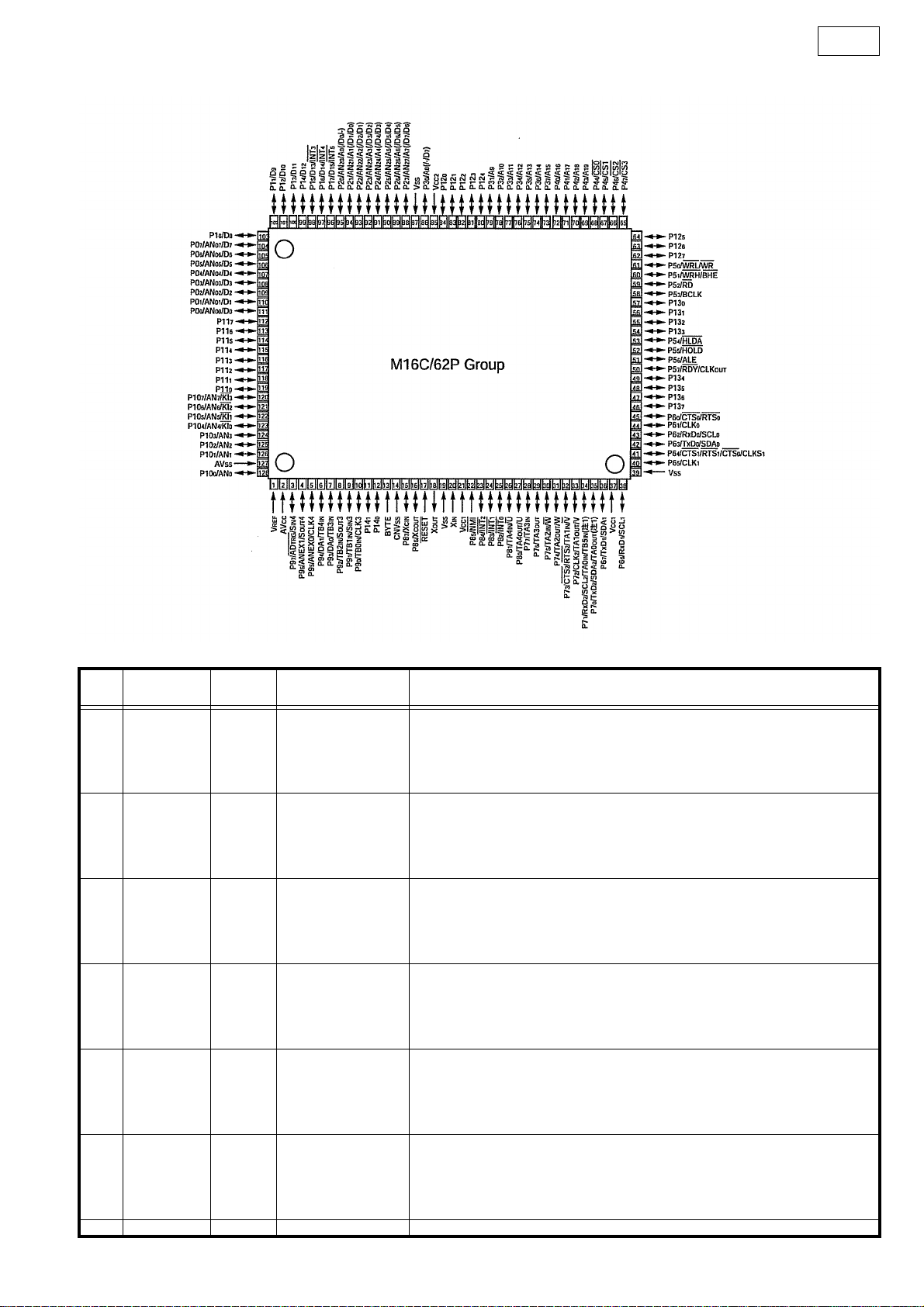

M30627FHPGP (IC202: 1U-3694)

S-101

PIN

NO

1 VREF I VREF Reference Voltage Input for A/D converter

2 AVcc I AVcc Positive power

3 SIN4 O FL_CS Chip Enable output to FLD

4 SOUT4 SO FL_DA Serial Data output to FLD

5 CLK4 SO FL_CK Serial Clock output to FLD

6 P94 I BUSY1 Interrupt request from DSP

7 P93 I ACK1 Interrupt request from DSP

8 SOUT3 SO DSPMOSI Serial Data output to DSP

9 SIN3 SI DSPMISO Serial Data input from DSP

10 CLK3 O DSPSPICLK Serial Clock output to DSP

11 P141 O DSPSPICS Chip Enable output to DSP

12 P140 O FL_RST Reset output to FLD

13 BYTE GND

14 CNVSS Select input of Flash rom write Mode

15 P87 O 3811CLK Serial Clock output to BD3811

16 P86 O 3811DATA Serial Data output to BD3811

17 /RESET Reset input

18 XOUT Xtal output

19 VSS GND

20 XIN Xtal input

21 VCC1 Positive power

22 /NMI Positive power

23 /INT2 INT PROTECT Protect Signal input

24 /INT1 INT ESS CS(OP_CE) Chip Enable input from ESS

25 /INT0 I DIR INT1 Interrupt request from DIR

26 TA4IN I 50/60 50Hz/60Hz AC Input

27 P80 O NC(L:Output) Not Used: N. C.

28 P77 O NC(L:Output) Not Used: N. C.

29 P76 O NC(L:Output) Not Used: N. C.

30 P75 I VOL JOG-B VOL encoder Pulse-B input

31 P74 I VOL JOG-A VOL encoder Pulse-A input

Port

Function

Port

setting

Port Name Explanation

16

Page 17

S-101

PIN

NO

32 P73 O NC(L:Output) Not Used: N. C.

33 P72 O NC(L:Output) Not Used: N. C.

34 RXD2 O NC(L:Output) Not Used: N. C.

35 TXD2 O NC(L:Output) Not Used: N. C.

36 TXD1 SO USB/IPOD_TXD Serial Data output to USB/IPOD

37 VCC1 Positive power

38 RXD1 SI USB/IPOD_RXD Serial Data input from USB/IPOD

39 VSS GND

40 CLK1 O NC(L:Output) Not Used: N. C.

41 P64 O NC(L:Output) Not Used: N. C.

42 TXD0 SO ESS DO(OP_DO) Serial Data output to ESS

43 RXD0 SI ESS DI(OP_DI) Serial Data input from ESS

44 CLK0 SI ESS CK(OP_CLK) Serial Clock input from ESS

45 P60 I ESS ON(BE_ON) ESS Active Signal input.

46 P137 O NC(L:Output) Not Used: N. C.

47 P136 O NC(L:Output) Not Used: N. C.

48 P135 O NC(L:Output) Not Used: N. C.

49 P134 O NC(L:Output) Not Used: N. C.

50 P57 O NC(L:Output) Not Used: N. C.

51 P56 O NC(L:Output) Not Used: N. C.

52 P55 O SELCLK Clock select signal output for digital audio signal from AD1837

53 P54 O DVD ON/OFF DVD Drive Power ON/OFF output. H: Power ON

54 P133 O NC(L:Output) Not Used: N. C.

55 P132 O NC(L:Output) Not Used: N. C.

56 P131 I HP SW HEAD PHONE insert detect signal input. H: Detected

57 P130 O TRIGGER TRIGGER OUT. H:OUT

58 P53 I AUX IN SW Front AUX IN insert detect signal input. H: Detected

59 P52 O EXT_CLK Serial Clock output to control LED.

60 P51 O EXT_DATA Serial Data output to control LED.

61 P50 O NC(L:Output) Not Used: N. C.

62 P127 O VIDEO_A Serial Clock output to control BU2090(VIDEO CONVERT)

63 P126 O VIDEO_B Serial Clock output to control BU2090(VIDEO CONVERT)

64 P125 O VIDEO_C Serial Clock output to control BU2090(VIDEO CONVERT)

65 P47 O VIDEO_D Serial Clock output to control BU2090(VIDEO CONVERT)

66 P46 I VDET_V Detect Composite signal input.

67 P45 I VDET_S Detect S-VIdeo signal input.

68 P44 O BSE DSP Mute Output

69 P43 O ERR MUTE MUTE output at DSP Error.

70 P42 O SUB_SUM Signal output to SW summing control.

71 P41 O MULTI/DIR Select DSP input.

72 P40 O MIX/MULTI Select MIX/MULTI of ESS Output. H:MIX

73 P37 O P.ON/OFF Main POWER ON/STANDBY switching output. H:ON

74 P36 O SCART MUTE MUTE output to SCART Audio Output. H:MUTE

75 P35 O IPOD_ID iPOD ID connect output

76 P34 O SP-RELAY SP RELAY ON/OFF output. H:ON

77 P33 O HP-MUTE MUTE output to HEAD PHONE output. L:MUTE

78 P32 O PRE_MUTE MUTE output to PRE OUT. L:MUTE

79 P31 O AMP_MUTE MUTE output to POWER AMP IC. L:MUTE

80 P124 I TEST MODE CLOSE

81 P123 I TEMP_DETECT Temperature Detect signal input from posister

82 P122 O Not Used: N. C.

83 P121 O DIR RST Reset output to DIR

84 P120 O CLATCH Latch Output to AD1837.

85 VCC2 Positive power

86 P30 O CODEC_RST Reset output to AD1837

87 VSS GND

88 P27 O TU_POWER TUNER Power ON/OFF output. H: Power ON

89 P26 I STEREO "STEREO" indicator input from FM/AM TUNER pack

90 P25 I TUNED "TUNED" detect input from FM/AM TUNER pack

91 P24 O TMUTE MUTE output to TUNER. L:MUTE

92 P23 O SAN CE Chip Enable output to PLL/RDS/VR IC

93 P22 O SAN DI Serial Data input from PLL/RDS/VR IC

94 P21 O SAN CK Serial Clock output to PLL/RDS/VR IC

95 P20 I SAN DO Serial Data output to PLL/RDS/VR IC

96 /INT5 I DFRES Reset Input from ESS. L:RESET

97 P16 O Not Used: N. C.

Port

Function

Port

setting

Port Name Explanation

17

Page 18

S-101

PIN

NO

98 /INT3 I REMOTE Remote Control signal input

99 P14 O SYR Reset output to RDS IC

100 P13 I DIR DOUT Serial Data input from DIR.

101 P12 O DIR/CODEC DIN Serial Data output to DIR.

102 P11 O DIR/CODEC CLK Serial Clock output to DIR.

103 P10 O DIR CE Chip Enable output to DIR.

104 P07 O E2P DI Serial Data output to EEPROM

105 P06 I E2P DO Serial Data input from EEPROM

106 P05 O E2P CK Serial Clock output to EEPROM

107 P04 O E2P CS Chip Enable output to EEPROM

108 P03 O USB/IPOD Select USB/iPOD port. H:USB

109 P02 O IPOD_CHARGE iPOD Charge Power ON/OFF output. H:Charge.

110 P01 I IPOD_CONNECT iPOD Connect detect signal input. L:Connected

111 P00 O VPP DSP rom (VPP) write Mode. L: UNLOCK(3.3V)

112 P117 O R/ W D SP rom W rite/ R E A D .

113 P116 O DSP_IO_POW DSP IO Power Output. H:OFF

114 P115 O DSP_CORE_POW DSP CORE Power Output. H:ON

115 P114 O DSP_OSC_ON DSP OSC On Output.

116 P113 O ROM_RST Reset output to DSP ROM.

117 P112 O DSP_RST Reset output to DSP.

118 P111 I BUSY EPROM EPROM BUSY signal input from DSP.

119 P110 I FLAG3A Control signal input from DSP.

120 AN7 AD DIMMER IN Input signal from sensor of illumination

121 AN6 AD SLIDE SW1 IN Select signal input of Video Signal. H:FHDMI/M:FPROGRE/L:FINTINTERLACE

122 AN5 AD SLIDE SW2 IN Select signal input of Aspect. H:FWIDE M:FLB L:FPS

123 AN4 AD CONNECT IN Detect signal input with DSW-S101. H:FConnected with only Satellite SP. M:FOK

124 AN3 AD MODE2 Initial Setting input for Region No of DVD.

125 AN2 AD MODE1 Initial Setting input the destination.(E2,E3)

126 AN1 AD KEY-0 Unit Operation Button input0

127 AVSS GND

128 AN0 AD KEY-1 Unit Operation Button input1

Port

Function

Port

setting

Port Name Explanation

L:FConected with only SW.

18

Page 19

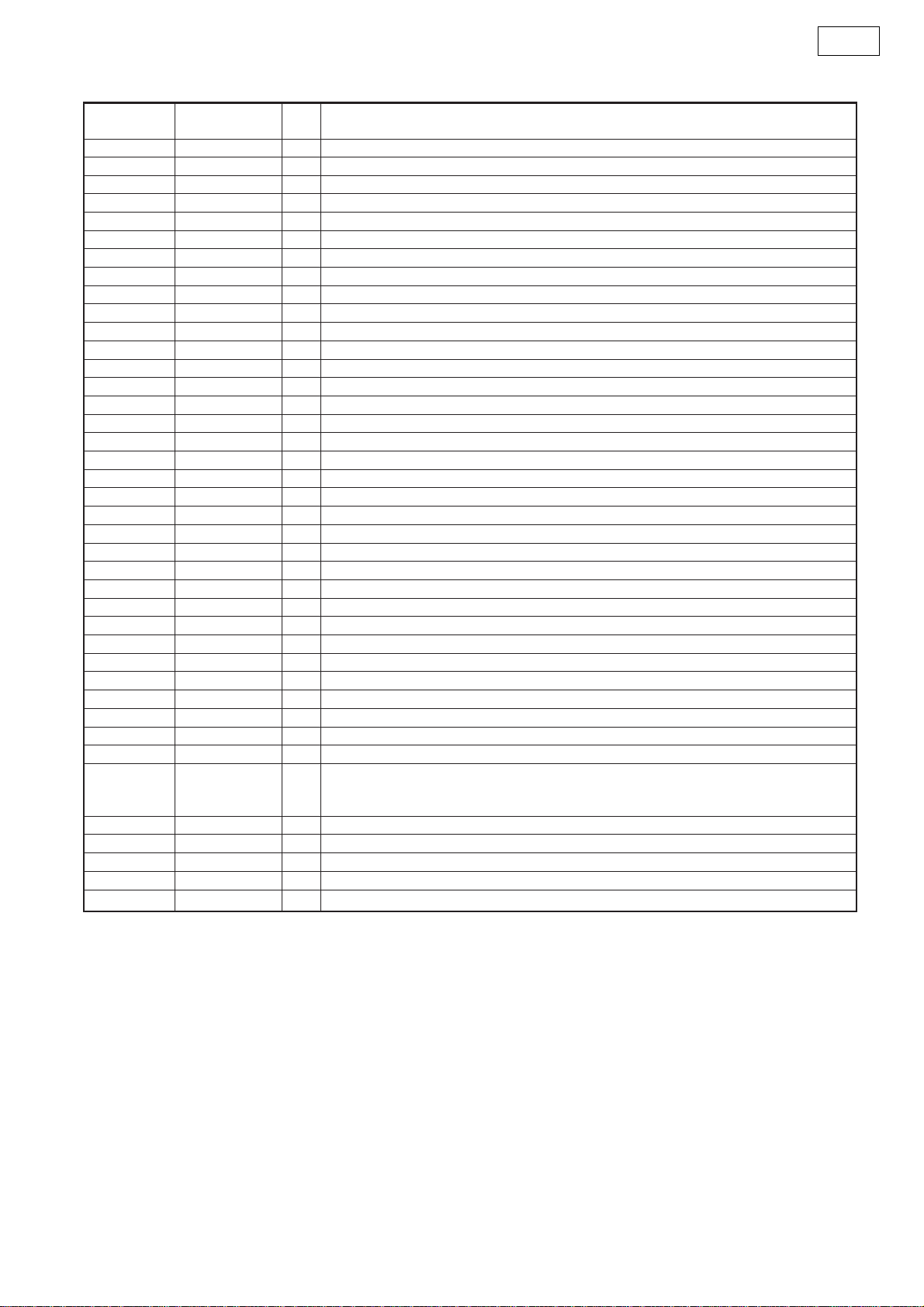

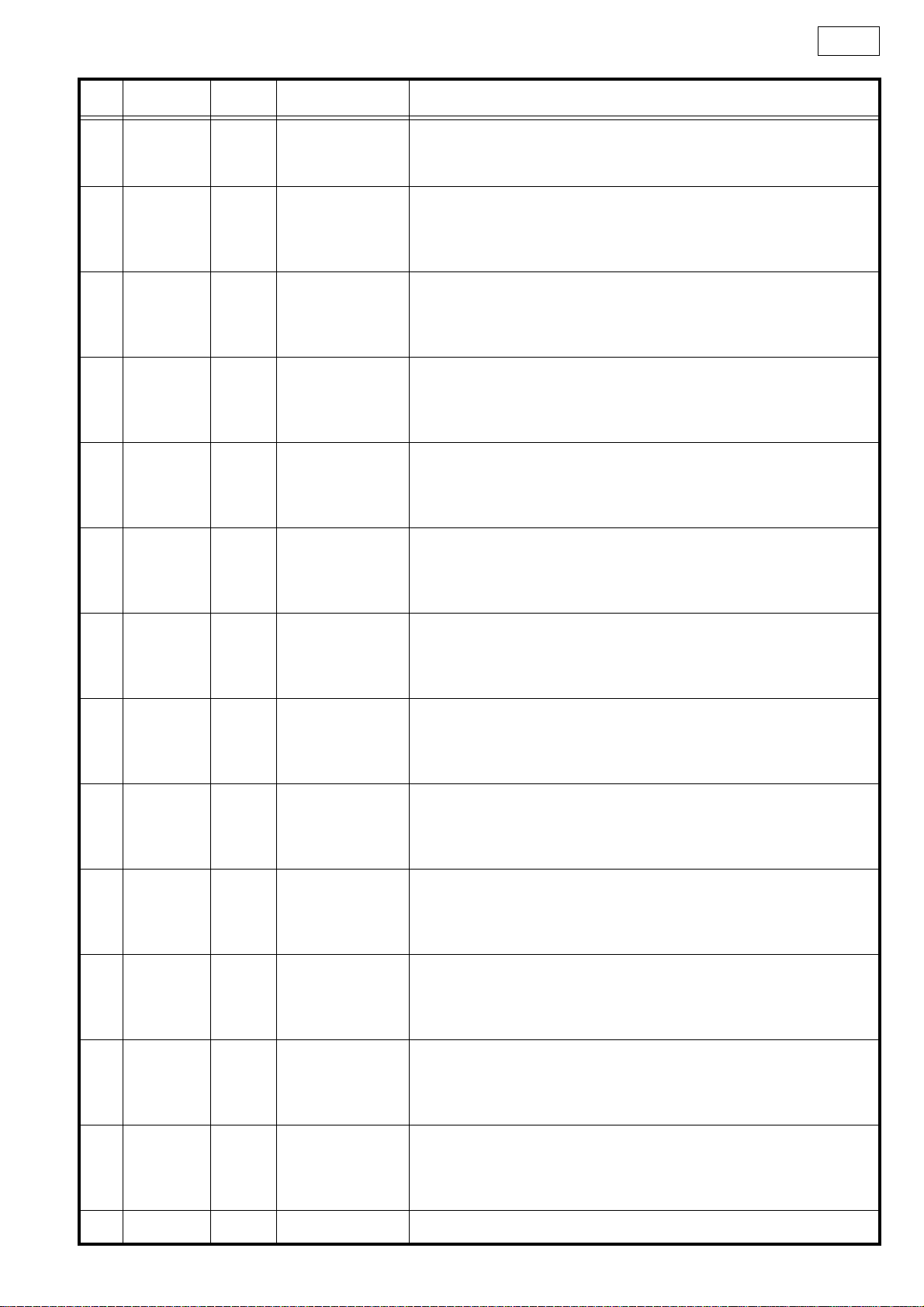

ADSP-21266SKSTZ-1C (IC906: 1U-3694)

S-101

144

1

36

37

PIN 1 INDICATOR

TOP VIEW

109

108

73

72

ADSP-21266SKSTZ-1C Terminal Function

LQFP

Pin Name

V

DDINT

Pin # Pin Name

1V

DDINT

CLKCFG0 2 GND 38 GND 74 V

CLKCFG1 3 RD 39 V

BOOTCFG0 4 ALE 40 GND 76 V

BOOTCFG1 5 AD15 41 DAI_P10 (SD2B) 77 GND 113

GND 6 AD14 42 DAI_P11 (SD3A) 78 V

V

DDEXT

7 AD13 43 DAI_P12 (SD3B) 79 GND 115

GND 8 GND 44 DAI_P13 (SCLK23) 80 V

V

DDINT

9V

DDEXT

GND 10 AD12 46 DAI_P15 (SD4A) 82 V

V

DDINT

11 V

DDINT

GND 12 GND 48 GND 84 V

V

DDINT

13 AD11 49 GND 85 RESET 121

GND 14 AD10 50 DAI_P16 (SD4B) 86 SPIDS 122

FLAG0 15 AD9 51 DAI_P17 (SD5A) 87 GND 123

FLAG1 16 AD8 52 DAI_P18 (SD5B) 88 V

AD7 17 DAI_P1 (SD0A) 53 DAI_P19 (SCLK45) 89 SPICLK 125

GND 18 V

V

DDINT

19 GND 55 GND 91 MOSI 127

DDINT

GND 20 DAI_P2 (SD0B) 56 GND 92 GND 128

V

DDEXT

21 DAI_P3 (SCLK0) 57 V

GND 22 GND 58 DAI_P20 (SFS45) 94 V

V

DDINT

AD6 24 V

23 V

DDEXT

DDINT

AD5 25 GND 61 FLAG2 97 GND 133

AD4 26 DAI_P4 (SFS0) 62 FLAG3 98 CLKOUT 134

V

DDINT

27 DAI_P5 (SD1A) 63 V

GND 28 DAI_P6 (SD1B) 64 GND 100 TDO 136

AD3 29 DAI_P7 (SCLK1) 65 V

AD2 30 V

V

DDEXT

31 GND 67 V

GND 32 V

DDINT

DDINT

AD1 33 GND 69 V

AD0 34 DAI_P8 (SFS1) 70 GND 106 CLKIN 142

WR 35 DAI_P9 (SD2A) 71 V

V

DDINT

36 V

DDINT

LQFP

Pin # Pin Name

37 V

DDEXT

DDINT

LQFP

Pin # Pin Name

73 GND 109

DDINT

75 GND 111

DDINT

DDINT

DDEXT

45 DAI_P14 (SFS23) 81 GND 117

47 V

54 V

DDINT

DDINT

DDEXT

83 GND 119

90 MISO 126

93 V

59 GND 95 A

60 V

DDINT

DDINT

DDINT

96 A

99 EMU 135

101 TDI 137

DDINT

DDINT

DDINT

DDINT

DDEXT

VDD

VSS

66 GND 102 TRST 138

DDINT

103 TCK 139

68 GND 104 TMS 140

105 GND 141

107 XTAL 143

108 V

DDEXT

72 V

DDINT

DDINT

DDINT

LQFP

Pin #

110

112

114

116

118

120

124

129

130

131

132

144

19

Page 20

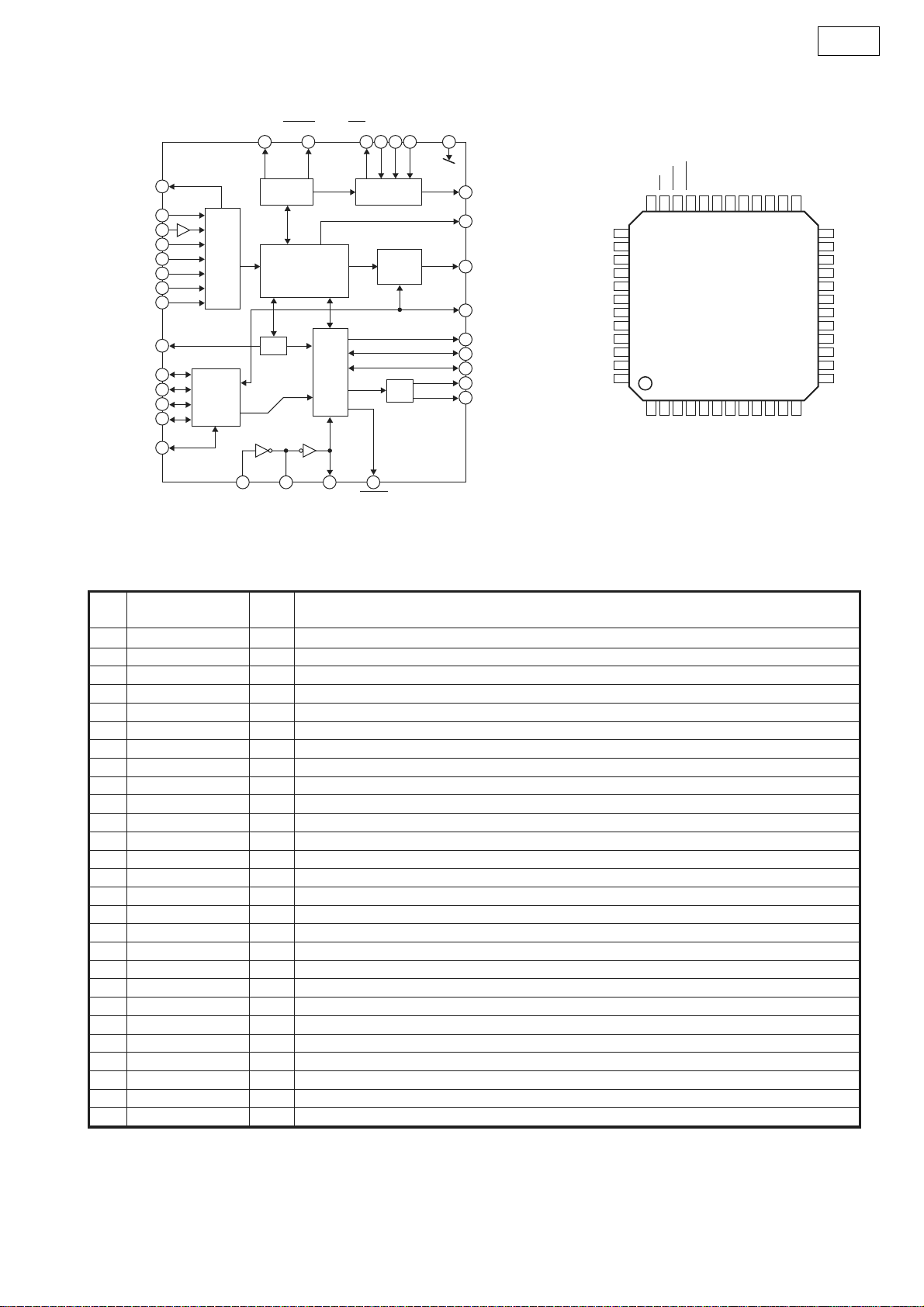

SP3721A (RL-S874: U2)

CDRF

CDRDDC

S-101

HOLD1

VNA

FNN

FNP

DIP

DIN

RX

BYP

SIGO

VPA

AIP

AIN

ATO N

ATO P

49505152535455565758596061626364

DVDRFP

DVDRFN

PD1

PD2

A2

B2

C2

D2

CP

CN

1

2

3

4

5

6

7

8

9

10

11

D

12

C

13

B

14

A

15

F

16

E

NC

VCI2

CDTE

TOP VIEW

VNB

DVDLD

DVDPD

CDLD

CDPD

VC

LDON#

VCI

VPB

VIIRR

VIP

32313029282726252423222120191817

VIB

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

FDCHG#

SDEN

SDATA

SCLK

LCP

LCN

CE

FE

TE

MEI

MEV

TPH

DFT

PI

MIN

MEVO

MLPF

SP3721A Terminal Function

Pin Name

Type

1, 2 DVDREP, DVDREN I RF Signal Inputs. Differential RF signal attenuator input pins

63 CDRF I RF Signal Inputs. Single-ended RF signal attenuator input pin

59, 60 AIP, AIN I AGC Amplifier Inputs. Differential AGC amplifier input pins

53, 54 DIP, DIN I

Analog inputs for RF Single Buffer. Differential analog inputs to the RF single-ended output buffer

and full wave rectifier

Low Impedance Enable. A TTL compatible input pin that activates the FDCHG switches. A low

32 FDCHG# I

level activates the switches and the falling edge of the internal FDCHG triggers the fast decay for

the MIRR bottom hold circuit. (open high)

49 HOLD1 I

Hold Control. A TLL compatible control pin which, when pulled high, disables the RF AGC charge

pump and holds the RF AGC amplifier gain at its present value. (open high)

11~14 D, C, B, A I Photo Detector Interface Inputs. Inputs from the main beam Photo detector matrix outputs

5~8 A2, B2, C2, D2 I

Photo Detector Interface Inputs. AC coupled inputs for the DPD from the main beam Photo

detector matrix outputs

15~16 F, E I CD tracking Error Inputs. Inputs from the CD photo detector error outputs.

3~4 PD1, PD2 I CD Photo detector Interface Inputs. Inputs from the CD photo detector error outputs

40 MEI I Mirror Envelope Inputs.The SIGO envelope input pin

35 MIN I

RF signal Input for Mirror. AC coupled inputs for the mirror detection circuit from the pull-in signal

output. (PI)

21 DVDPD I APC Input. DVD APC input pin from the monitor photo diode

23 CDPD I APC Input. CD APC input pin from the monitor photo diode

25 LDON# I APC Output On/Off. APC output control pin. A low level activates the LD output. (open high)

61, 62 ATON/ATOP O Differential Attenuator Output. Attenuator outputs

51, 52 FNN, FNP O Differential Normal Output. Filter normal outputs

57 SIGO O Single Ended Normal Output. Single-ended RF output

64 CDRFDC O CD RF Signal Output. Single ended CD RF summing output

42 FE O Focusing Error Signal Output. Focus error output reference to VCI

41 TE O Tracking Error Signal Output. Tracking error output reference to VCI

DescriptionPin No.

20

Page 21

S-101

Pin Name

43 CE O Center Error Signal Output. Center error output reference to VCI

34 NEVO O SIGO Bottom Envelope Output. Bottom envelope for mirror detection

37 DFT O

29 MIRR O Mirror Detect Output. Mirror Detect comparator output. Pseudo CMOS output

36 PI O

22 DVDLD O APC output. DVD APC output pin to control the laser power

24 CDLD O APC output. CD APC output pin to control the laser power

56 BYP I/O The RF AGC integration capacitor CBYP, is connected between BYP and VPA

9 CP I/O

10 CN I/O

45 LCP — Center Error LPF pin. An external capacitance is connected between this pin and the LCN pin

44 LCN — Center Error LPF pin. An external capacitance is connected between this pin and the LCP pin

30 MP — MIRR signal Peak hold pin. An external capacitance is connected to between this pin and VPB

31 MB — MIRR signal Bottom hold pin. An external capacitance is connected to between this pin and VPB

39 MEV — Sigo Bottom Envelope pin. An external capacitance is connected to between this pin and VPB

17 CDTE — CD Tracking. E-F Opamp output for feedback

38 TPH — PI Top Hold pin. An external capacitance is connected to between this pin and VPB

26 VC —

27 VCI — Reference Voltage input. DC bias voltage input for the servo input reference

18 VCI2 — Reference Voltage input. DC bias voltage input for the servo input reference

55 RX —

33 MLPF — MIRR signal LPF pin. An external capacitance is connected between this pin and VPB

19 NC — No Connect

48 SDEN I

47 SDATA I/O

46 SCLK I

58 VPA Power. Power supply pin for the RF block and serial port

28 VPB Power. Power supply pin for the servo block

50 VNA Ground. Ground pin for the RF block and serial port

20 VNB Ground. Ground pin for the servo bolck

Type

Defect Output. Pseudo CMOS output. When a defect is detected, the DFT output goes high. Also

the servo AGC output can be monitored at this pin, when CAR bits 7-4 are ‘0011’

Pull-in Signal Output. The summing signal output of A, B, C, D or PD1, PD2 for mirror detection.

Reference to VCI

Differential Phase tracking LPF pin. An external capacitance is connected between this pin and

the CN pin

Differential Phase tracking LPF pin. An external capacitance is connected between this pin and

the CP pin

Reference Voltage output. This pin provides the internal DC bias reference voltage (+2.5V lix).

Output Impedance is less than 50ohms

Reference Resistor Input. An external 8.2kohm, 1% resistor is connected from this pin to ground

to establish a precise PTAT (proportional to absolute temperature) reference current for the filter

Serial Data Enable. Serial Enable CMOS input. A high level input enable the serial port (Not to be

left open)

Serial Data. Serial data bi-directional CMOS pin. NRZ programming data for the internal registers

is applied to this input ( Not to be left open)

Serial Clock. Serial Clock CMOS input. The clock applied to this pin is synchronized with the data

applied to SDATA (Not to be left open)

DescriptionPin No.

21

Page 22

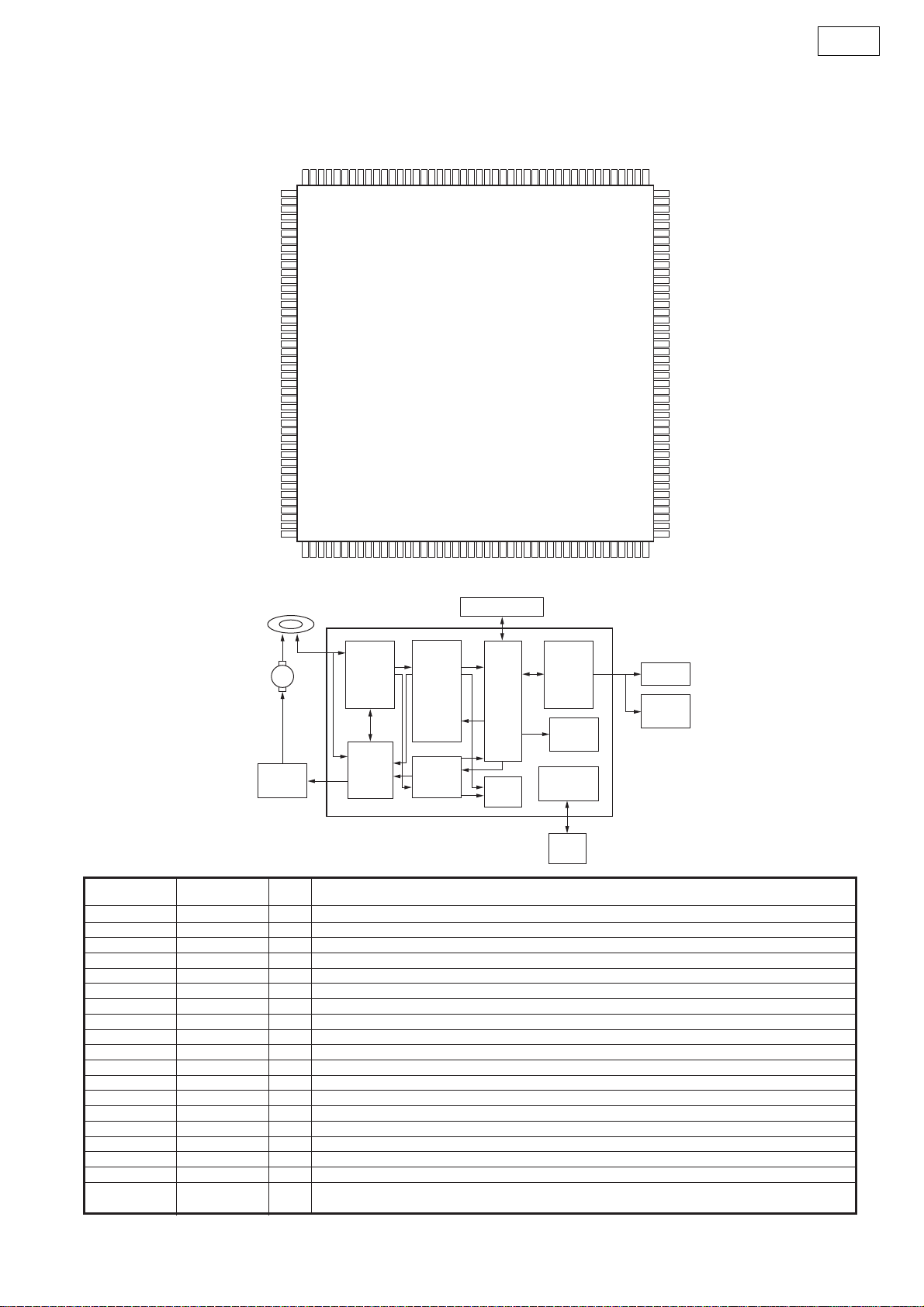

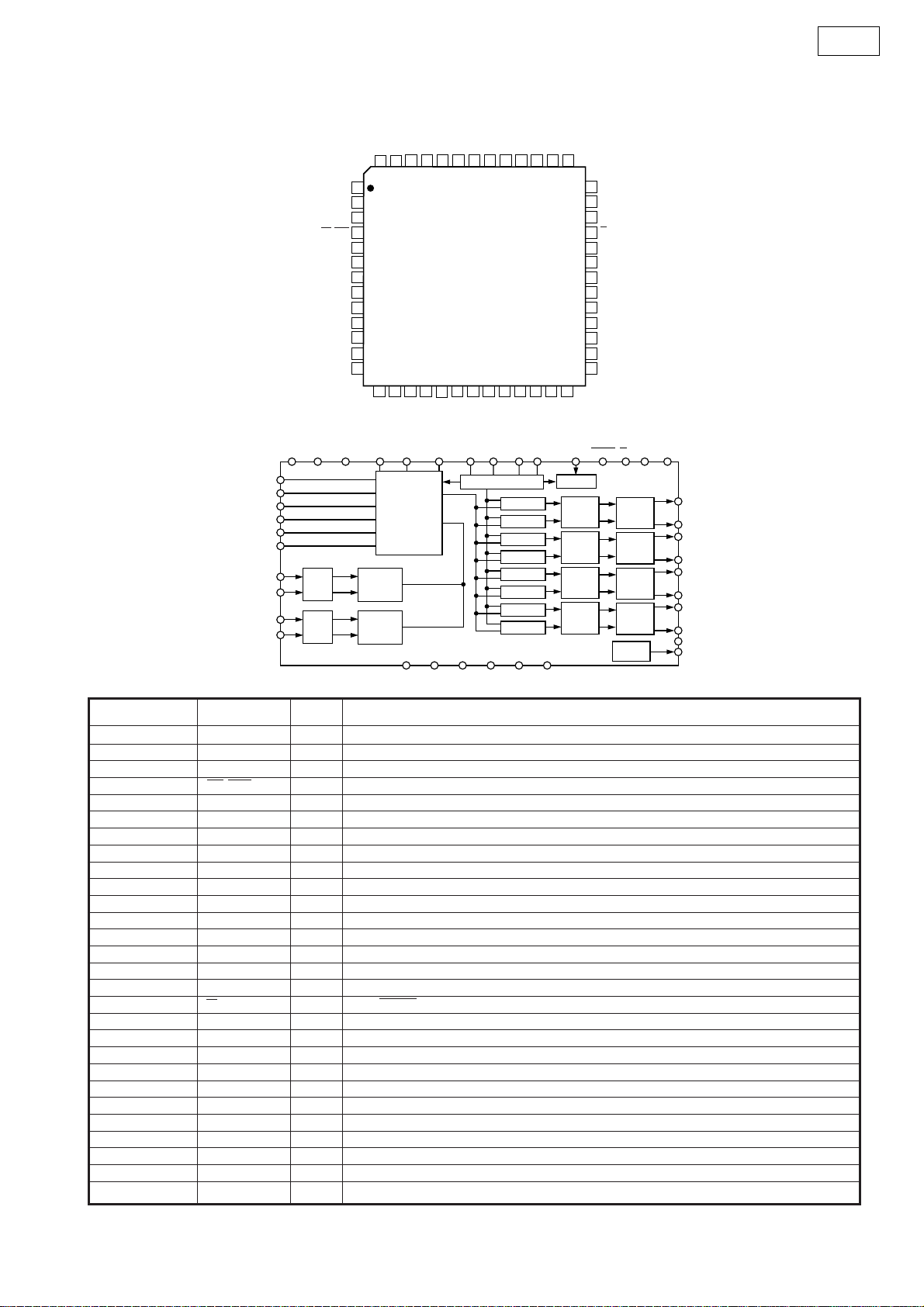

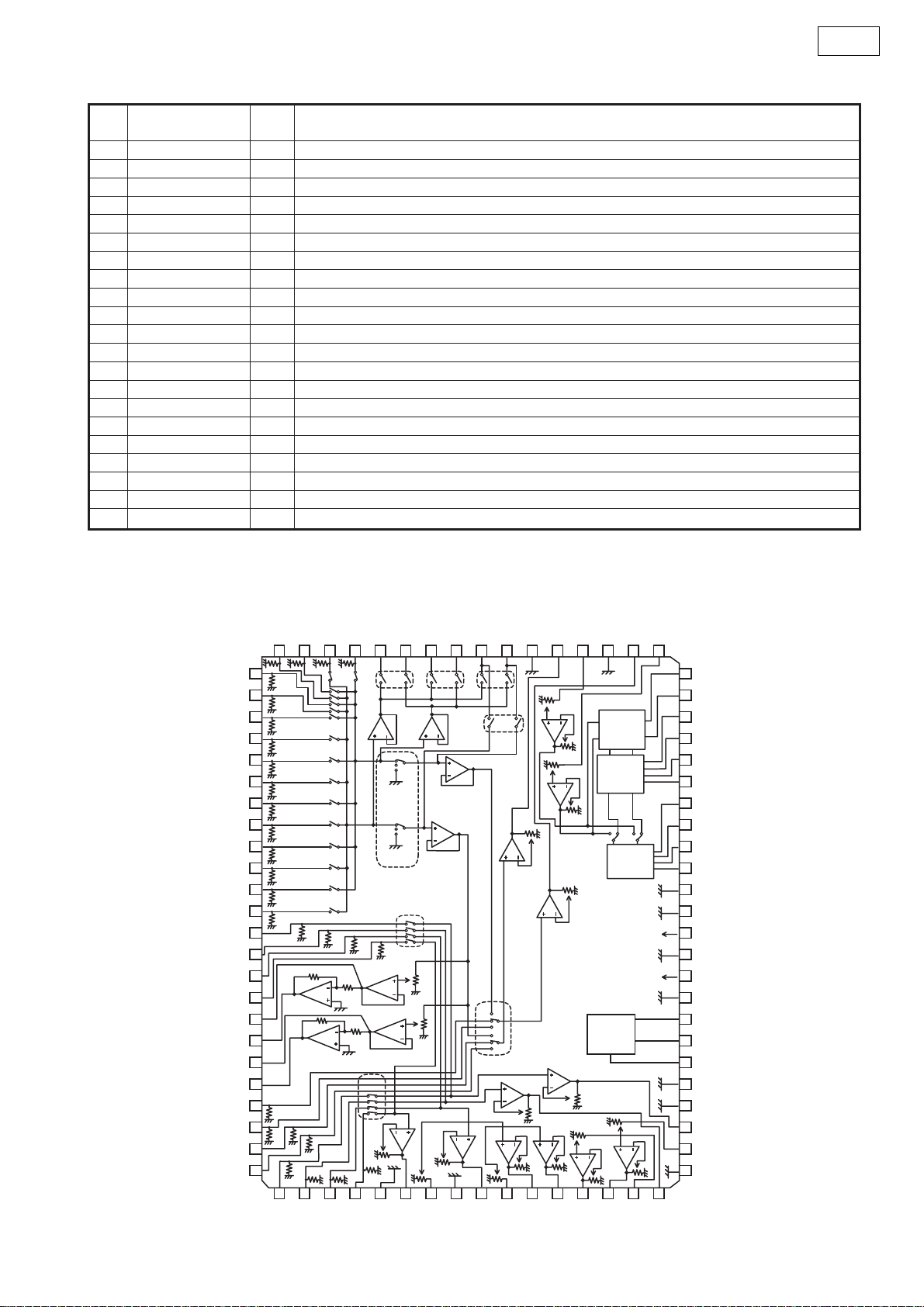

TAS5066 (IC805: 1U-3683)

1.2 Functional Block Diagram

PWM Ch.

Output Control

AVDD_PLL

AVSS_PLL

VREGA_CAP

VREGB_CAP

VREGC_CAP

DVDD_RCL

DVSS_RCL

DVDD_PWM

DVSS_PWM

Power Supply

PLL_FLT_OUT

PLL_FLT_RET

SCLK

LRCLK

MCLKOUT

SDIN1

SDIN2

SDIN3

MCLK_IN

XTAL_OUT

XTAL_IN

DBSPD

SDA

SCL

CSO

PWM_AP_1

VALID_1

PWM_AP_2

VALID_2

PWM AP_3

VALID_3

PWM_AP_4

VALID_4

PWM_AP_5

VALID_5

PWM_AP_6

VALID_6

PWM AM_3

PWM_AM_1

PWM_AM_2

PWM_AM_4

PWM_AM_5

PWM_AM_6

Clock,

PLL

and

Serial

Data

I/F

PDN

RESET

MUTE

CLIP

ERR_RCVRY

Serial

Control

I/F

Reset,

Pwr Dwn

and

Status

Auto Mute

De-Emphasis

Soft Volume

Error Recovery

Soft Mute

Clip Detect

Signal

Processing

PWM

Section

PWM Ch.

PWM Ch.

PWM Ch.

PWM Ch.

PWM Ch.

M_S

DM_SEL1

DM_SEL2

MCLK_IN

AVDD_PLL

PLL_FLT_OUT

PLL_FLT_RET

AVSS_PLL

DVSS1

ERR_RCVRY

MUTE

DVSS1

NC

NC

RST

PDN

SDA

SCL

CS0

AVDD_OSC

XTL_IN

XTL_OUT

AVSS_OSC

DVSS

PWM_AP_1

PWM_AM_1

VALID_1

PWM_AP_2

PWM_AM_2

VALID_2

PWM_AP_3

PWM_AM_3

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18 19 21 22 23 24 25 26 27 28 29 30 31 32

20

VALID_3NCNC

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

S-101

DVDD_RCL

DVSS_RCL

NC

DVDD_PWM

DVSS_PWM

PWM_AP_4

PWM_AM_4

VALID_4

PWM_AP_5

PWM_AM_5

VALID_5

PWM_AP_6

PWM_AM_6

VALID_6

NC

NC

CLIP

SDIN1

DBSPD

SDIN2

SDIN3

SCLK

LRCLK

MCLK_OUT

DVDD

22

NC

DVSS1

M_S

DVSS1

DEM_SEL2

DEM_SEL1

DVSS1

Page 23

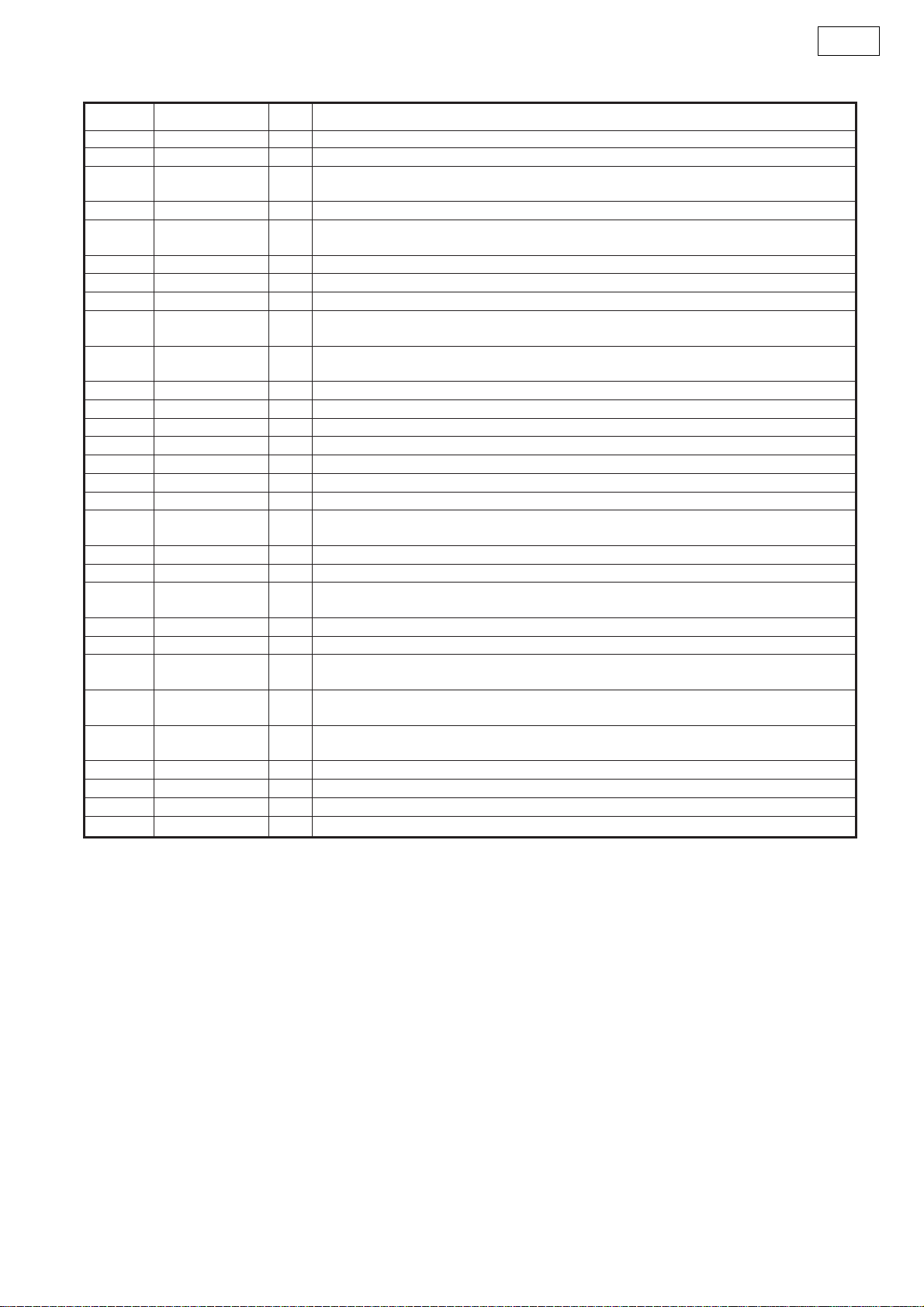

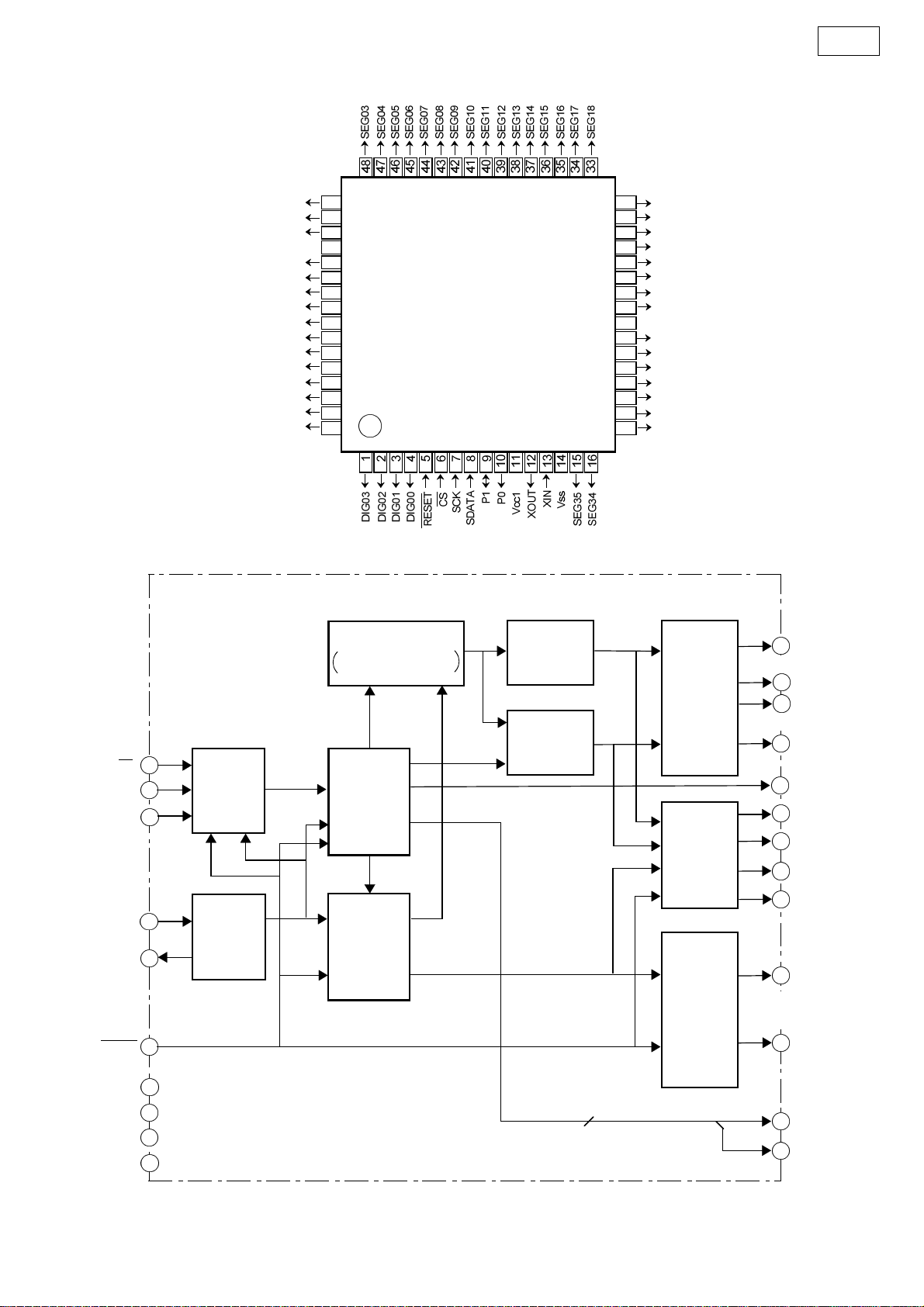

M66005-0001AHP (IC301: 1U-3681)

p

scan pulse

p

・

・

・

・

・

・

・

・

・

・

S-101

CS

SCK

SDATA

XIN

XOUT

RESET

SEG02

SEG01

SEG00

Vcc2

DIG15/SEG39

DIG14/SEG38

DIG13/SEG37

DIG12/SEG36

DIG11

DIG10

DIG09

DIG08

DIG07

DIG06

DIG05

DIG04

BLOCK DIAGRAM

14

15

16

21

20

13

Serial

receive

circuit

Clock

generator

data

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

Display code RAM

Bank 1 : 8bit x 16

Bank 2 : 8bit x 64

Code/

command

control

circuit

timing

clock

Display

controller

M66005-0001AHP

CGROM

(35bit x 160)

code

write

dot data

write

code

select

CGRAM

(35bit x 16)

32

SEG19

31

SEG20

SEG21

30

SEG22

29

SEG23

28

SEG24

27

SEG25

26

SEG26

25

V

24

23

SEG27

SEG28

22

SEG29

21

SEG30

20

SEG31

19

SEG32

18

SEG33

17

SEG00

59

.

.

Segment

output

circuit

Segment/

Digit

select/

output

circuit

Digit

output

circuit

.

.

.

.

.

.

.

.

.

.

.

33

31

24

23

64

63

62

61

12

.

.

.

.

.

.

1

.

.

SEG26

SEG27

.

.

.

SEG34

SEG35

DIG12/

SEG36

DIG13/

SEG37

DIG14/

SEG38

DIG15/

SEG39

DIG00

.

.

.

DIG11

Vcc1

Vcc2

Vss

V

19

60

22

32

2

P0

18

P1

17

23

Page 24

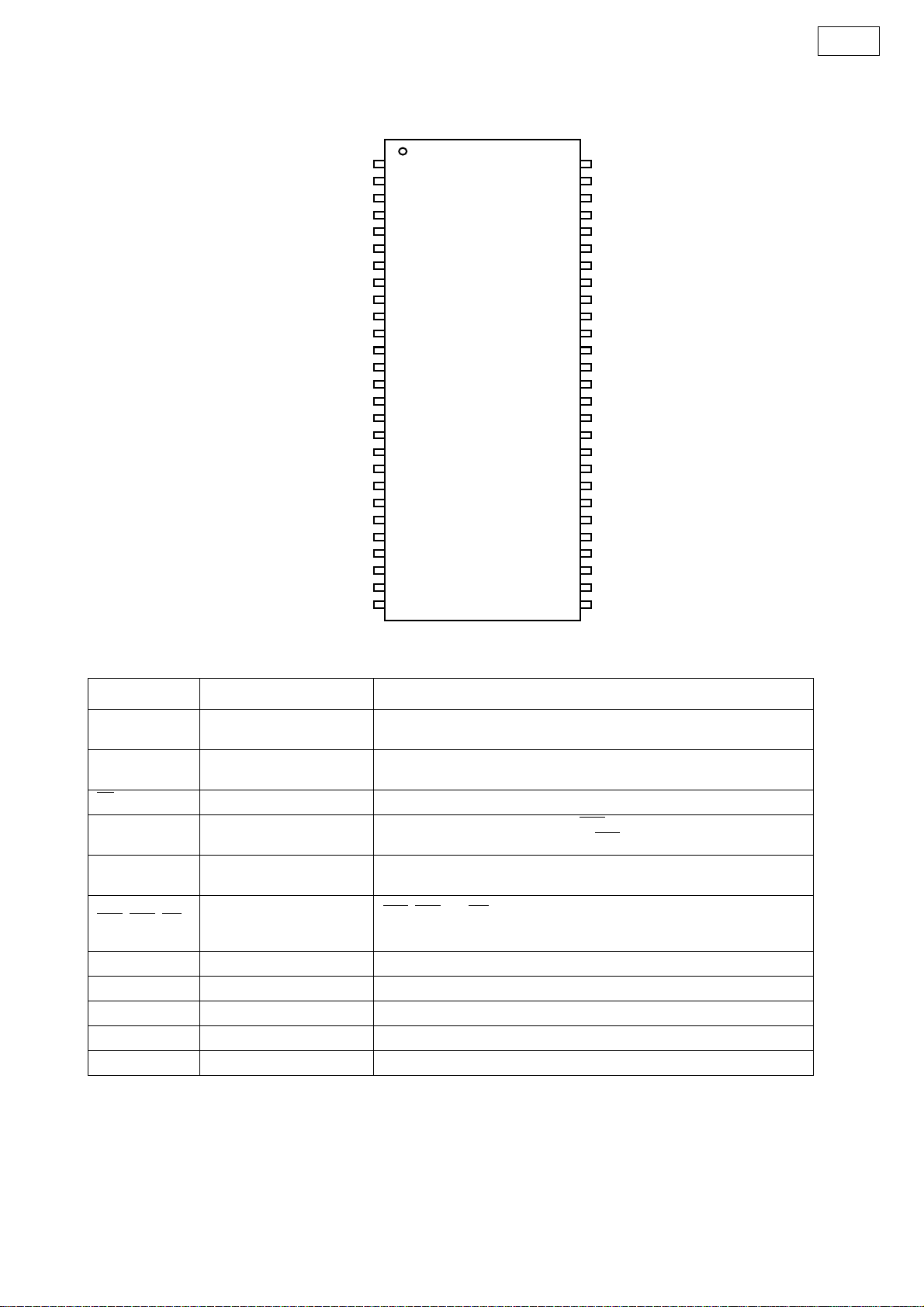

AD1837 (IC711: 1U-3694)

S-101

DSDATA3

DSDATA2

AGND

DGND

DSDATA1

39

38

37

36

35

34

33

32

31

30

29

28

27

NC

OUTL3

MCLKASDATAABCLKALRCLKODVDDDVDD DVDD

PD/RST M/S AVDD AVDD

CLOCK

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DescriptionPin No.

DVDD

DBCLK

DLRCLK

M/S

AGND

OUTR4

NC

OUTL4

NC

AGND

AVDD

OUTR3

NC

V

Σ-∆

DAC

Σ-∆

DAC

Σ-∆

DAC

Σ-∆

DAC

REF

OUTL1

OUTR1

OUTL2

OUTR2

OUTL3

OUTR3

OUTL4

OUTR4

FILTD

FILTR

DLRCLK

DBCLK

DSDATA1

DSDATA2

DSDATA3

DSDATA4

ADCLP

ADCLN

ADCRP

ADCRN

AD1837 Terminal Function

Pin Name

CLATCH

PD/RST

Σ-∆

ADC

Σ-∆

ADC

AD1837

Input/

Output

DVDD

CIN

AGND

NC

OUTL1

NC

OUTR1

AGND

AVDD

NC

OUTL2

DGND

CCLK

COUT

ASDATA

ODVDD

MCLK

ALRCLK

ABCLK

50 494847 46 45 44 43 42 41 40

51

52

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24 25 26

NC

OUTR2

SERIAL DATA

I/O PORT

DIGITAL

FILTER

DIGITAL

FILTER

TOP VIEW

FILTD

FILTR

AGND

DGND AGND AGND AGND AGNDDGND

AVDD

DSDATA4

ADCLP

ADCLN

ADCRN

CINCLATCHCCLK COUT

CONTROL PORT

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

ADCRP

1,39 DVDD Digital Power Supply. Connect to digital 5V supply.

2 CLATCH I Latch Input for Control Data

33 CIN I Serial Control Input

4 PD/RST I Power-Down/Reset

5,10,16,24,30,35 AGND Analog Ground

6,12,25,31 NC Not connected

7,13,26,32 OUTLx O DACx Left Channel Output

8,14,27,33 NC Not connected

9,15,28,34 OUTRx O DACx Right Channel Output

11,19,29 AVDD Analog Power Supply. Connect to analog 5V supply.

17 FILTD Filter Capacitor Connection. Recommend 10µF/100nF.

18 FILTR Reference Filter Capacitor Connection. Recommended 10µF/100nF.

20 ADCLN I ADC Left Channel Negative Input

21 ADCLP I ADC Left Channel Positive Input

22 ADCRN I ADC Right Channel Negative Input

23 ADCRP I ADC Right Channel Positive Input

36 M/S I ADC Master/Slave Select

37 DLRCLK I/O DAC LR Clock

38 DBCLK I/O DAC Bit Clock

40,52 DGND Digital Ground

41-44 DSDATAx I DACx Input Data (Left and Right Supply)

45 ABCLK I/O ADC Bit Clock

46 ALRCLK I/O ADC LR Clock

47 MCLK I Master Clock Input

48 ADVDD Digital Output Driver Power Supply

49 ASDATA O ADC Serial Data Output

50 COUT O Output for Control Data

51 CCLK I Control Clock Input for Control Data

24

Page 25

HY57V651620BTC-75 (RL-S874: U11)

S-101

DD

V

DQ0

V

DDQ

DQ1

DQ2

SSQ

V

DQ3

DQ4

DDQ

V

DQ5

DQ6

V

SSQ

DQ7

DD

V

LDQM

/WE

/CAS

/RAS

/CS

BA0

BA1

A10/AP

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

SS

V

DQ15

V

SSQ

DQ14

DQ13

DDQ

V

DQ12

DQ11

SSQ

V

DQ10

DQ9

V

DDQ

DQ 8

SS

V

NC

UDQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

V

SS

PIN DESCRIPTION

PIN PIN NAME DESCRIPTION

CLK Clock

CKE Clock Enable

CS

BA0,BA1 Bank Address

A0 ~ A11 Address

RAS

, CAS, WE

LDQM, UDQM Data Input/Output Mask Controls output buffers in read mode and masks input data in write mode

DQ0 ~ DQ15 Data Input/Output Multiplexed data input / output pin

V

DD/VSS Power Supply/Ground Power supply for internal circuits and input buffers

V

DDQ/VSSQ Data Output Power/Ground Power supply for output buffers

NC No Connection No connection

Chip Select Enables or disables all inputs except CLK, CKE and DQM

Row Address Strobe,

Column Address Strobe,

Write Enable

The system clock input. All other inputs are registered to the SDRAM on the

rising edge of CLK

Controls internal clock signal and when deactivated, the SDRAM will be one

of the states among power down, suspend or self refresh

Selects bank to be activated during RAS

Selects bank to be read/written during CAS

Row Address : RA0 ~ RA11, Column Address : CA0 ~ CA7

Auto-precharge flag : A10

RAS

, CAS and WE define the operation

Refer function truth table for details

activity

activity

25

Page 26

T431616A-8S(RL-S874:U5)

S-101

DD

V

DQ0

DQ1

SSQ

V

DQ2

DQ3

DDQ

V

DQ4

DQ5

V

SSQ

DQ6

DQ7

DDQ

V

LDQM

WE

CAS

RAS

CS

BA

A10/AP

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

SS

V

DQ15

DQ14

V

SSQ

DQ13

DQ12

DDQ

V

DQ11

DQ10

SSQ

V

DQ9

DQ8

V

DDQ

N.C / RFU

UDQM

CLK

CKE

N.C

A9

A8

A7

A6

A5

A4

V

SS

PIN DESCRIPTION

PIN PIN NAME DESCRIPTION

CLK System Clock

CS

CKE Clock Enable

A0 ~ A10/AP

BA Bank Select Address

RAS

CAS

WE

L(U)DQM Data Input/Output Mask

DQ0 ~ DQ15

DD/VSS Power Supply/Ground

V

VDDQ/VSSQ

N.C/RFU

Chip Select

Address

Row Address Strobe

Column Address Strobe

Write Enable

Data Input/Output

Data Output Power/Ground

No Connection/Reserved

for Future Use

Active on the positive going edge to sample all input.

Disables or enables device operation by masking or enabling all input

except CLK,CKE and L(U)DQM

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

Row/column aaddresses are multiplexed on the same pins.

Row address : RA0 ~ RA10,column address : CA0 ~ CA7

Selects bank to activated during row address latch time.

Select bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK

with RAS low.

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK

with CAS low.

Enables column access.

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, t

Blocks data input when L(U)DQM active.

Data inputs/outputs are multiplexed on the same pins.

Powe and ground for the input buffers and the core logic.

Isolated power supply and ground for the output buffers to provide

improved noise immunity.

This pin is recommended to be left No Connection on the device.

SHZ after the clock and masks the output.

26

Page 27

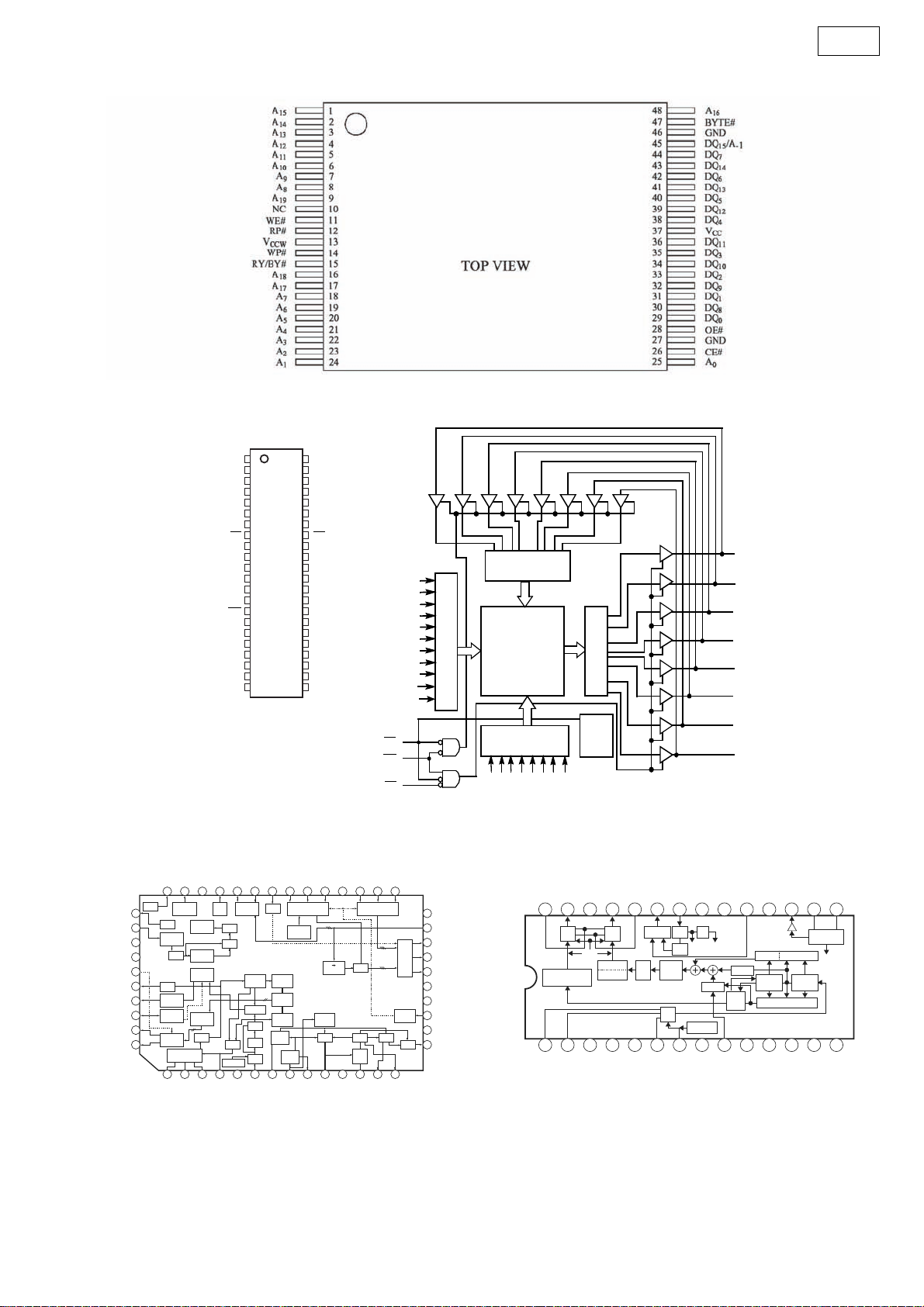

MX29LV800ABTC-70 (RL-S874: U10)

1

A15

2

A14

3

A13

4

A12

5

A11

6

A10

7

A9

8

A8

9

A19

10

NC

11

WE

NC

NC

A18

A17

A7

A6

A5

A4

A3

A2

A1

12

13

14

15

16

17

18

19

20

21

22

23

24

RESET

RY/B Y

BLOCK DIAGRAM

S-101

48

A16

47

BYTE

46

GND

45

Q15/A-1

44

Q7

43

Q14

42

Q6

41

Q13

40

Q5

39

Q12

38

Q4

37

VCC

36

Q11

35

Q3

34

Q10

33

Q2

32

Q9

31

Q1

30

Q8

29

Q0

28

OE

27

GND

26

CE

25

A0

CE

OE

WE

RESET

A0-A19

CONTROL

INPUT

LOGIC

ADDRESS

LATCH

AND

BUFFER

PROGRAM/ERASE

HIGH VOLTAGE

X-DECODER

FLASH

ARRAY

Y-DECODER

Y-PASS GATE

SENSE

AMPLIFIER

PROGRAM

DATA L AT C H

PGM

DATA

HV

ARRAY

SOURCE

HV

WRITE

S TAT E

MACHINE

(WSM)

STATE

REGISTER

COMMAND

DA TA

DECODER

COMMAND

DATA LATCH

Q0-Q15/A-1

I/O BUFFER

27

Page 28

LC89057W (IC707: 1U-3694)

S-101

RXOUT

RX0

RX1

RX2

RX3

RX4

RX5/VI

RX6/UI

LPF

TMCK/PIO0

TBCK/PIO1

TLRCK/PIO2

TDATA/PIO3

TXO/PIOEN

10

13

44

45

46

47

48

1

2

3

4

5

8

9

EMPHA/UO33AUDIO/VO35INT40CL39CE38DI

32

Clock

Selector

27

Microcontroller

Input

Selector

Modulation

or

Parallel Port

29

XIN

C bit, U bit

Demodulation

&

Lock Detect

PLL

28

XOUT

XMCK34CKST

I/F

Data

Selector

I/N

XMODE

41

37

36

21

24

16

17

20

22

23

DO

RERR

RD ATA

SDIN

RMCK

RBCK

RLRCK

SBCK

SLRCK

36 RERR1RXOUT

35 INT2RX0

34 CKST3RX1

TOP VIEW

33 AUDIO/VO4RX2

32 EMPHA/UO5RX3

31 DGND6DGND

30 DVDD7DVDD

29 XIN8RX4

28 XOUT9RX5/VI

27 XMCK10RX6/UI

26 DVDD11DVDD

25 DGND12DGND

24 SDIN37DO

23 SLRCK38DI

22 SBCK39CE

21 RD ATA40CL

20 RLRCK41XMODE

19 DVDD42DGND

18 DGND43DVDD

17 RBCK44TMCK/PIO0

16 RMCK45TBCK/PIO1

15 AGND46TLRCK/PIO2

14 AVDD47TDATA/PIO3

13 LPF48TXO/PIOEN

LC89057W Terminal Function

Pin

No.