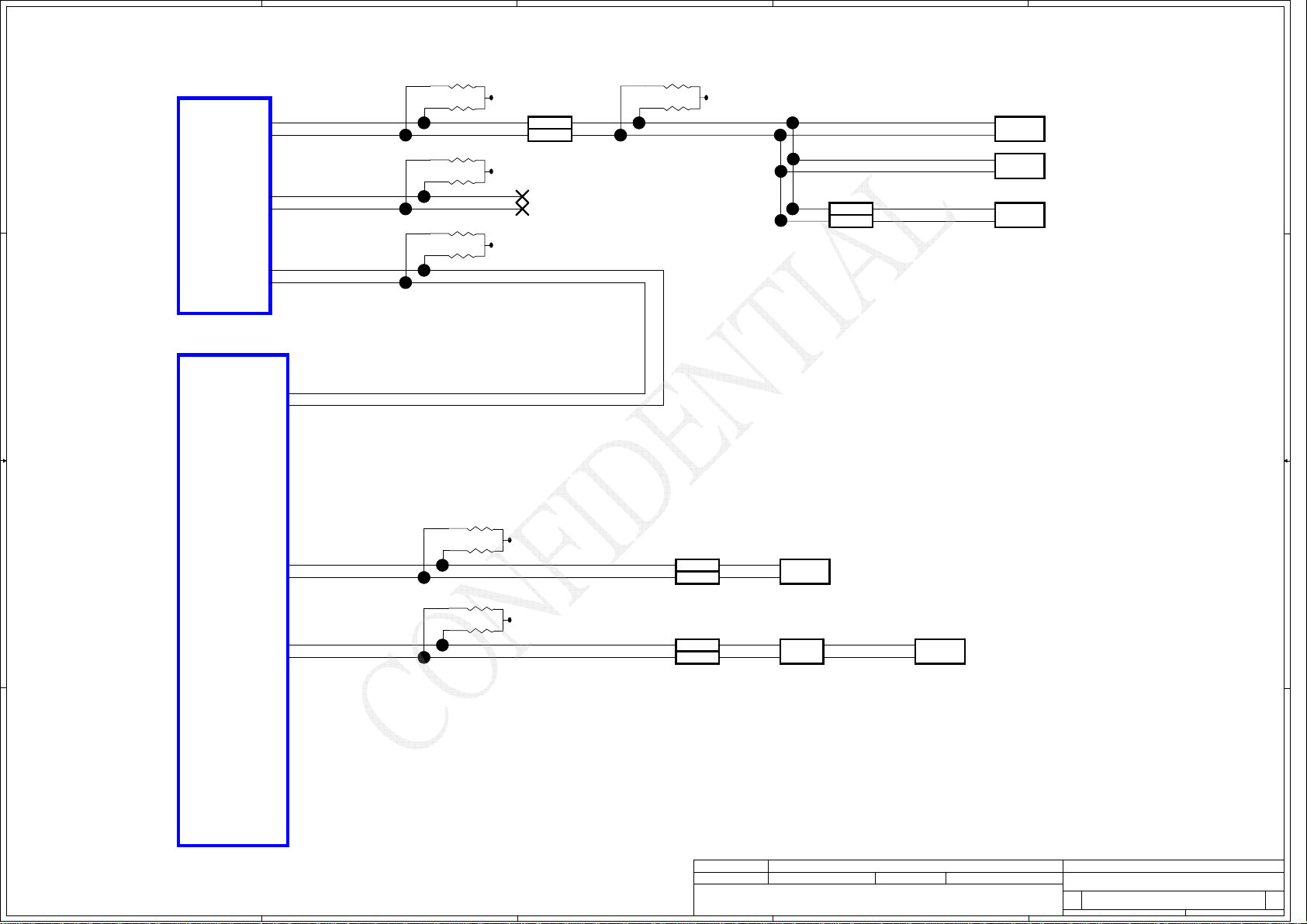

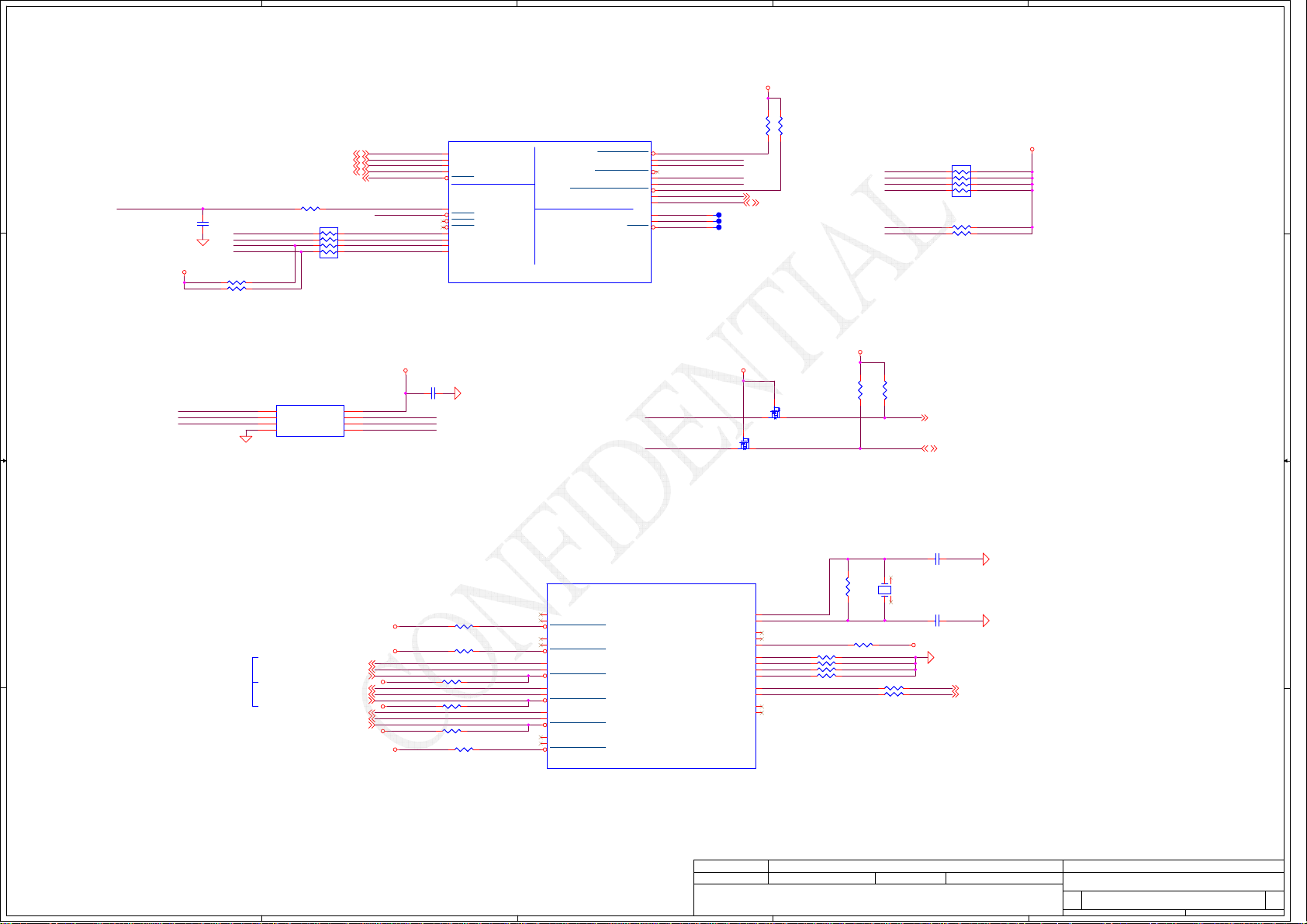

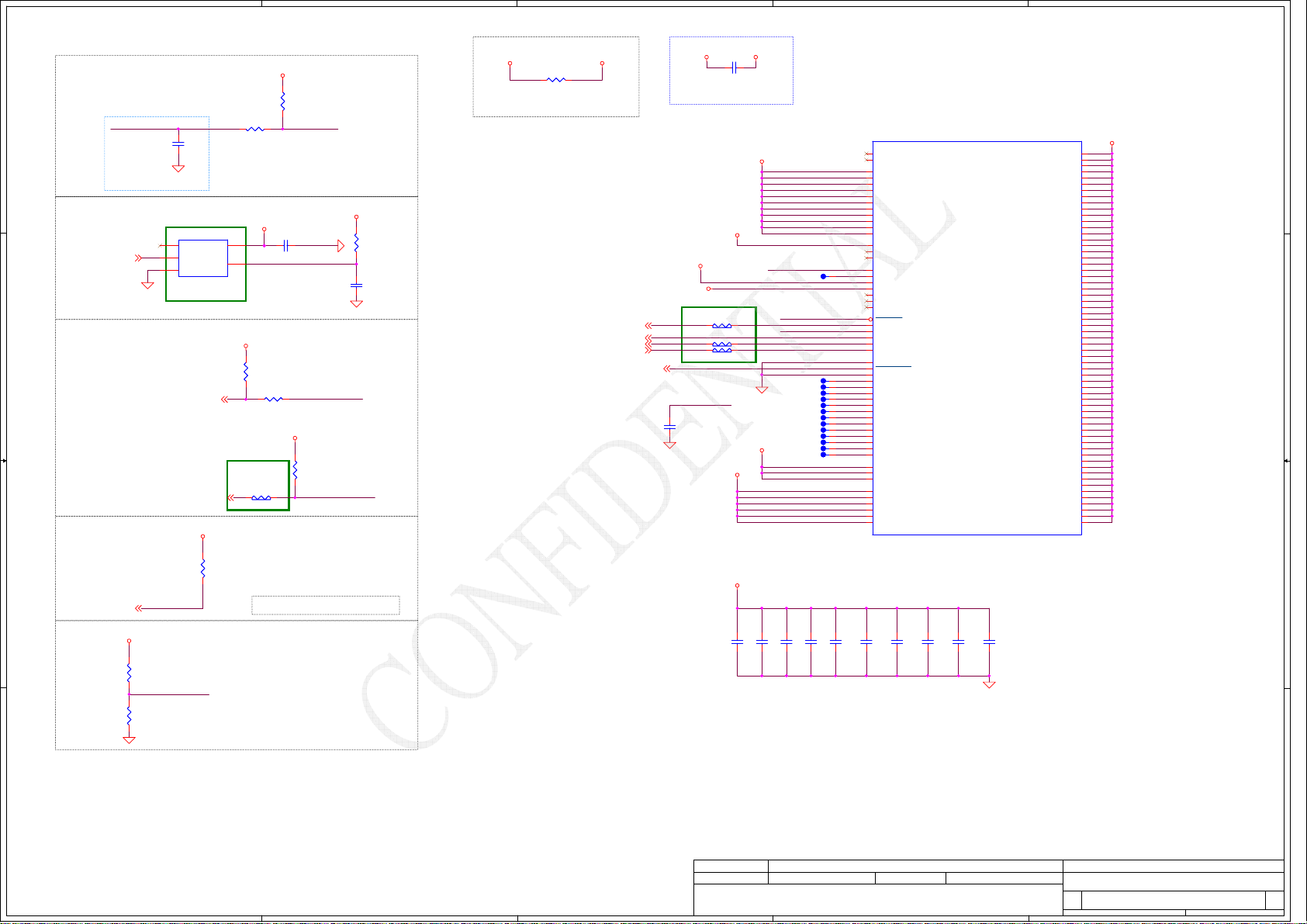

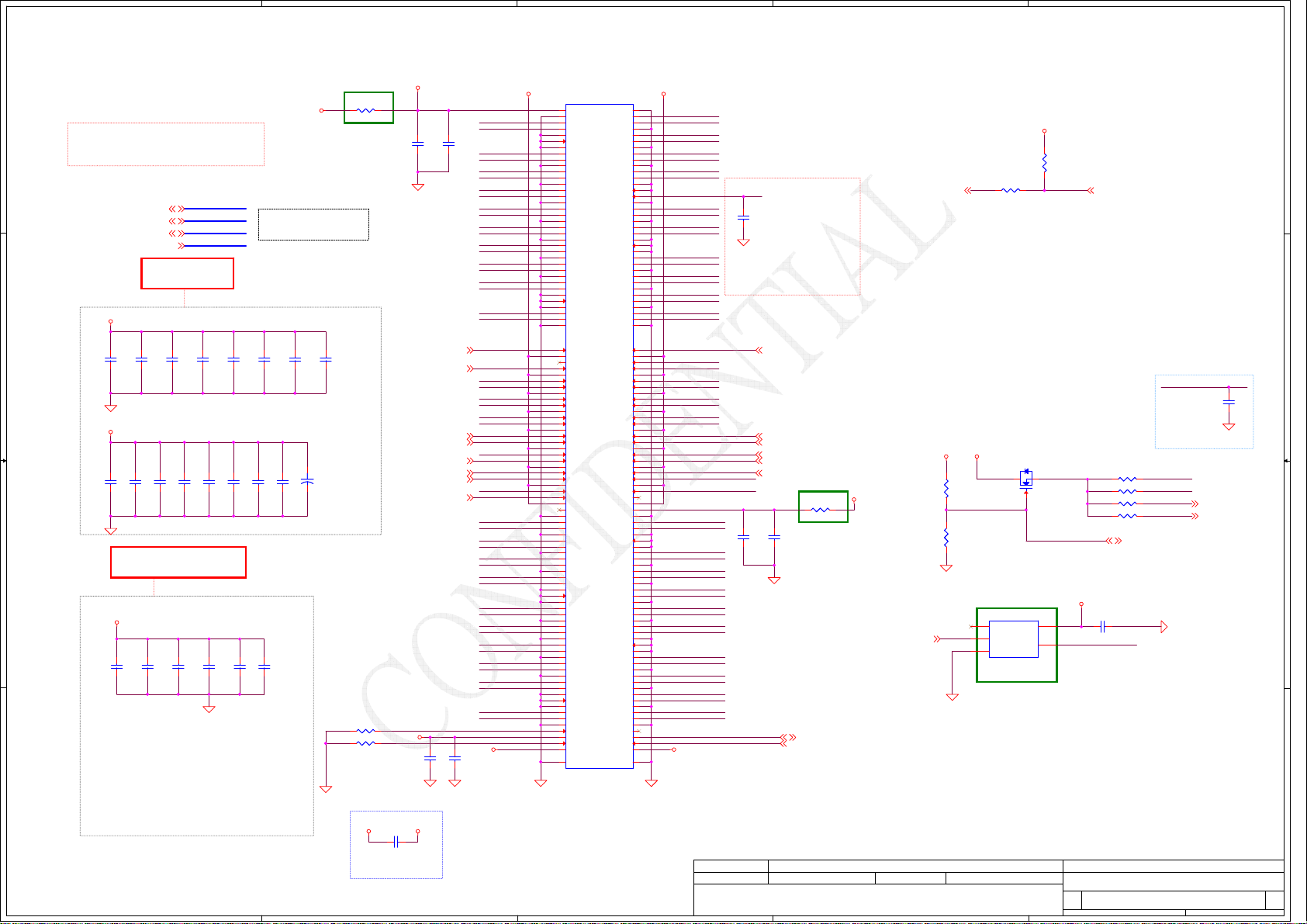

Dell LATITUDE 3550 ZAL50, LATITUDE 3550 ZAL60 Schematics

5

4

3

2

1

MODEL NAME : Marble Falls/ Discrete

PROJECT CODE : ZAL50, ZAL60

PCB NO : LA-B072P

D D

ZZZ

R1@ZZZ

R1@

UC1

UC1

UV17

UV17

VRAM

VRAM

X76_HYX@

X76_HYX@

UV17

UV17

UV18

UV18

VRAM

VRAM

X76_HYX@

X76_HYX@

UV18

UV18

UV19

UV19

VRAM

VRAM

X76_HYX@

X76_HYX@

UV19

UV19

UV20

UV20

VRAM

VRAM

X76_HYX@

X76_HYX@

UV20

UV20

RV59

RV59

20K

20K

X76_HYX@

X76_HYX@

RV59

RV59

ZZZ

ZZZ

X7653531L01

X7653531L01

X76_HYX_R@

X76_HYX_R@

ZZZ

ZZZ

X7653531L51

PCB 14B LA-B072P REV0 M/B

PCB 14B LA-B072P REV0 M/B

CPU

CPU

VRAM

VRAM

X76_MIC@

X76_MIC@

UV17

UV17

VRAM

VRAM

X76_SAM@

X76_SAM@

VRAM

VRAM

X76_MIC@

X76_MIC@

UV18

UV18

VRAM

VRAM

X76_SAM@

X76_SAM@

VRAM

VRAM

X76_MIC@

X76_MIC@

UV19

UV19

VRAM

VRAM

X76_SAM@

X76_SAM@

VRAM

VRAM

X76_MIC@

X76_MIC@

UV20

UV20

VRAM

VRAM

X76_SAM@

X76_SAM@

24.9K

24.9K

X76_MIC@

X76_MIC@

RV59

RV59

30.1K

30.1K

X76_SAM@

X76_SAM@

X7653531L51

X76_MIC_R@

X76_MIC_R@

ZZZ

ZZZ

X7653531L02

X7653531L02

X76_SAM_R@

X76_SAM_R@

For Post RTS

C C

Dell / Compal Confidential

Schematic Document

Intel Broadwell ULT

B B

Marble Falls 14"/15" Value

DIS

2013-10-03 Rev: 0.1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

of

154Monday, April 07, 2014

of

154Monday, April 07, 2014

of

154Monday, April 07, 2014

A

A

A

5

4

3

2

1

D D

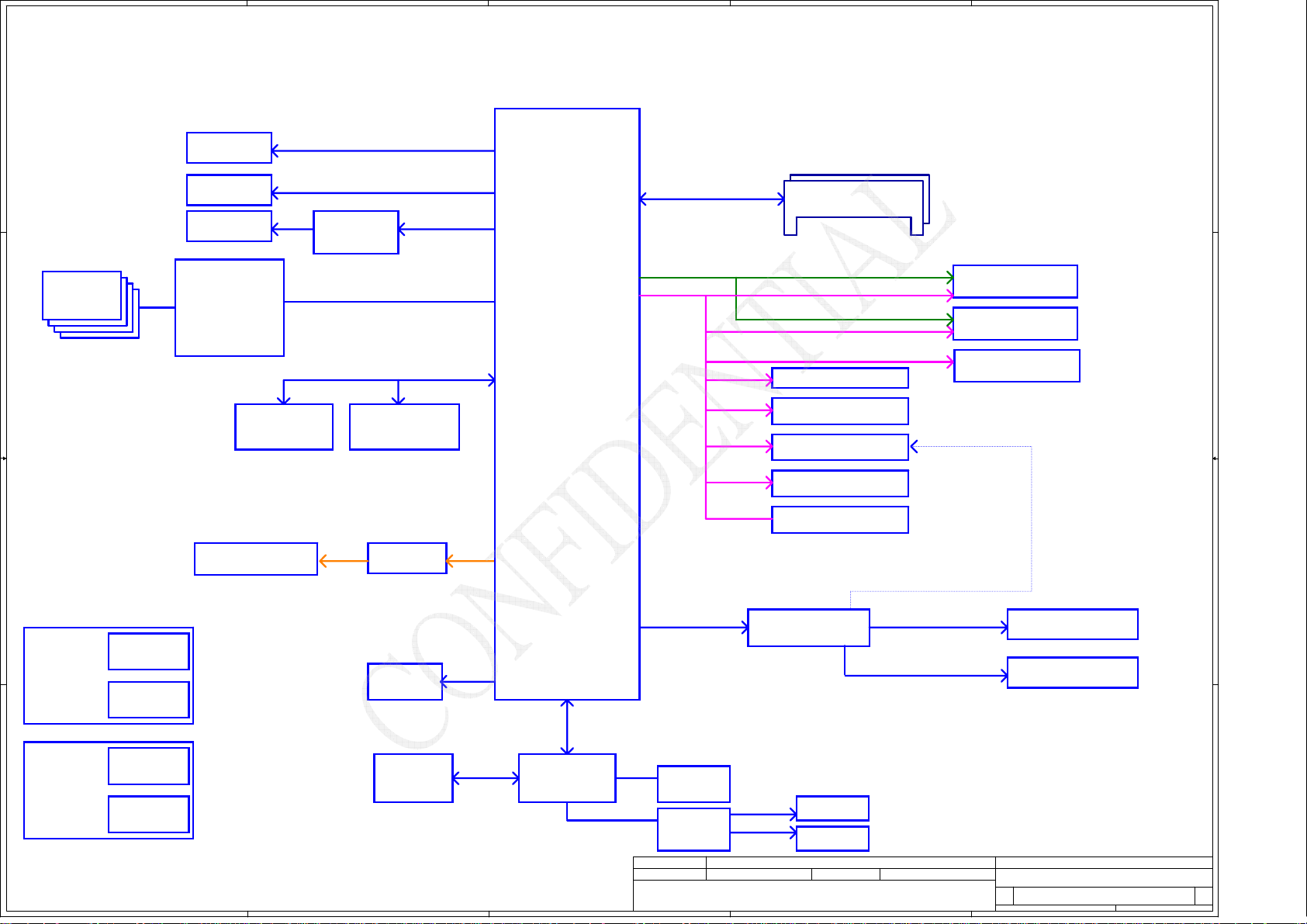

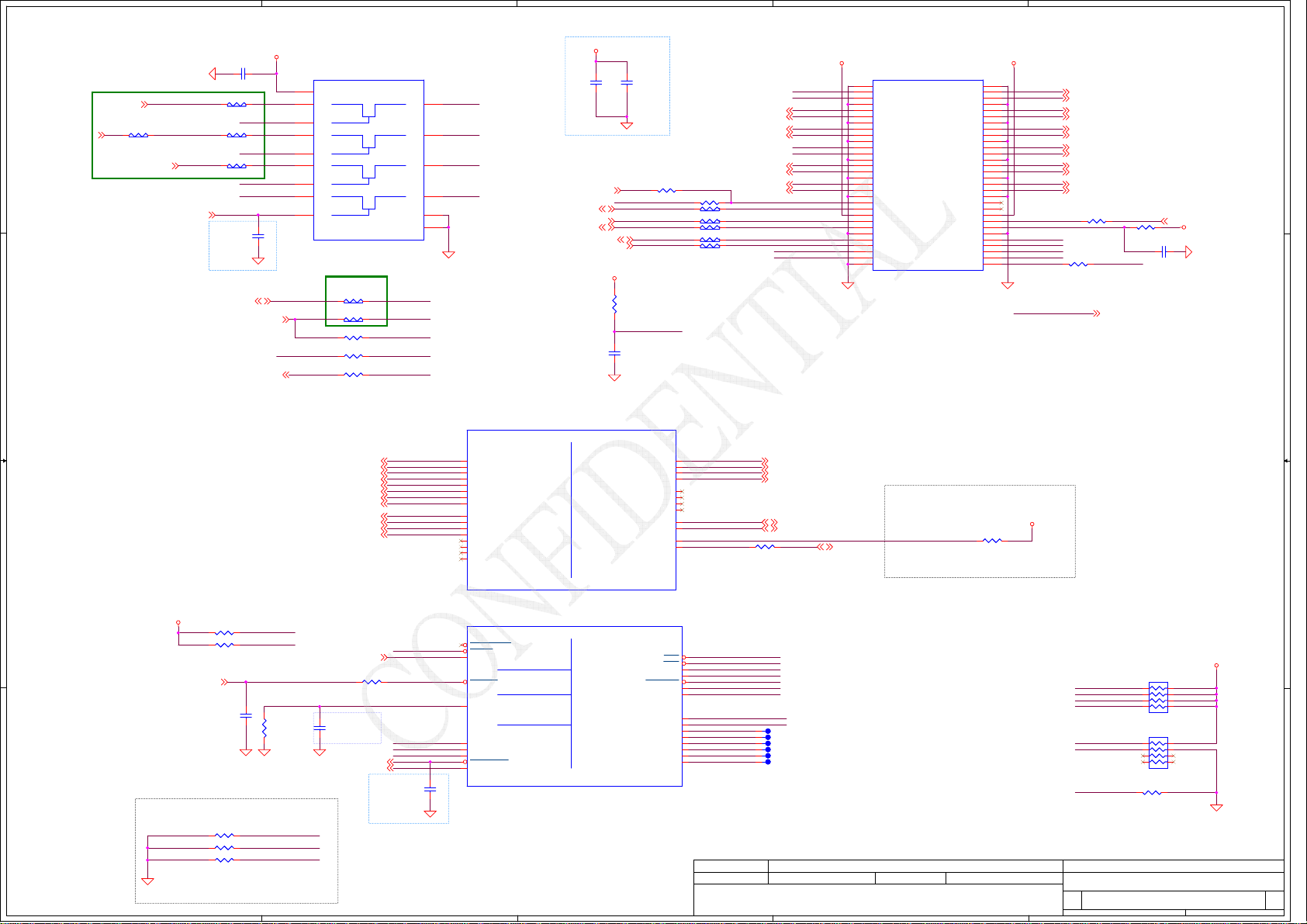

eDP Conn.

Page 21

HDMI Conn.

Page 19

DDR3L

256MX16

2GB

Page 51,52

CRT Conn.

Page 20

n

VIDIA

N15S-GM

GB2B-64

DP to CRT

IT6513FN

PCI-E X4

Page 20

BGA 595

C C

Page 46~50

PCI-E

x1 x1

NGFF 2230

WiFi/BT4.0 RTL8111GUS-CG

SATA HDD Conn.

B B

Port 4 Port 3

Ethernet

Port 0

Page 26

SATA Rediver

Page 22Page 25

Page 26

eDP

DDI

DDI

SATA3.0

Intel

Broadwell ULT-U

Processor

BGA 1168

Memory Bus (DDR3L)

Dual Channel

1.35V DDR3L 1600 MHz

USB 3.0

USB2.0

Port 3

Port 4

Port 7

Port 5

Port 6

DDRIIIL-DIMM X2

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7

8GB Max

Fingerprint

NGFF

WiFi/BT4.0

Digital Camera

(With Digital MIC)

Touch Screen

Card Reader

RTS5176E

Page 17, 18

Port 1

Port 0

Port 2

Port 1

Port 2

Page 26

Page 25

Page 21

Page 21

Page 27

USB 3.0 Conn. 1

USB 3.0 Conn. 2

USB 2.0 Conn. 3

Digital Mic.

Page 24

Page 24

Page 27

LS-B071P

IOR/B

USB2.0 Conn

USB2.0 Port 2

Card Reader

USB2.0 Port 6

SPI ROM

8MB

Page 9

HD Audio

SPI

Page 6~16

LPC Bus

Audio Codec

ALC3234

Page 23

Headphone Jack /

Mic. Jack combo

Int. Speaker R / L

Page 23

Page 23

33MHz

LS-B072P

A A

LED/B

LED *2

Lid Switch

5

SMSC SIO

ECE1099

4

BC Bus

Page 28 Page 29

SMSC KBC

MEC5085

BC Bus

PS/2

Touch Pad

Page 27

KB control

ECE1117

Page 30

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

KBD

Page 30

KB BKL

Page 30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

245Monday, April 07, 2014

245Monday, April 07, 2014

245Monday, April 07, 2014

of

of

of

A

A

A

5

4

3

2

1

D D

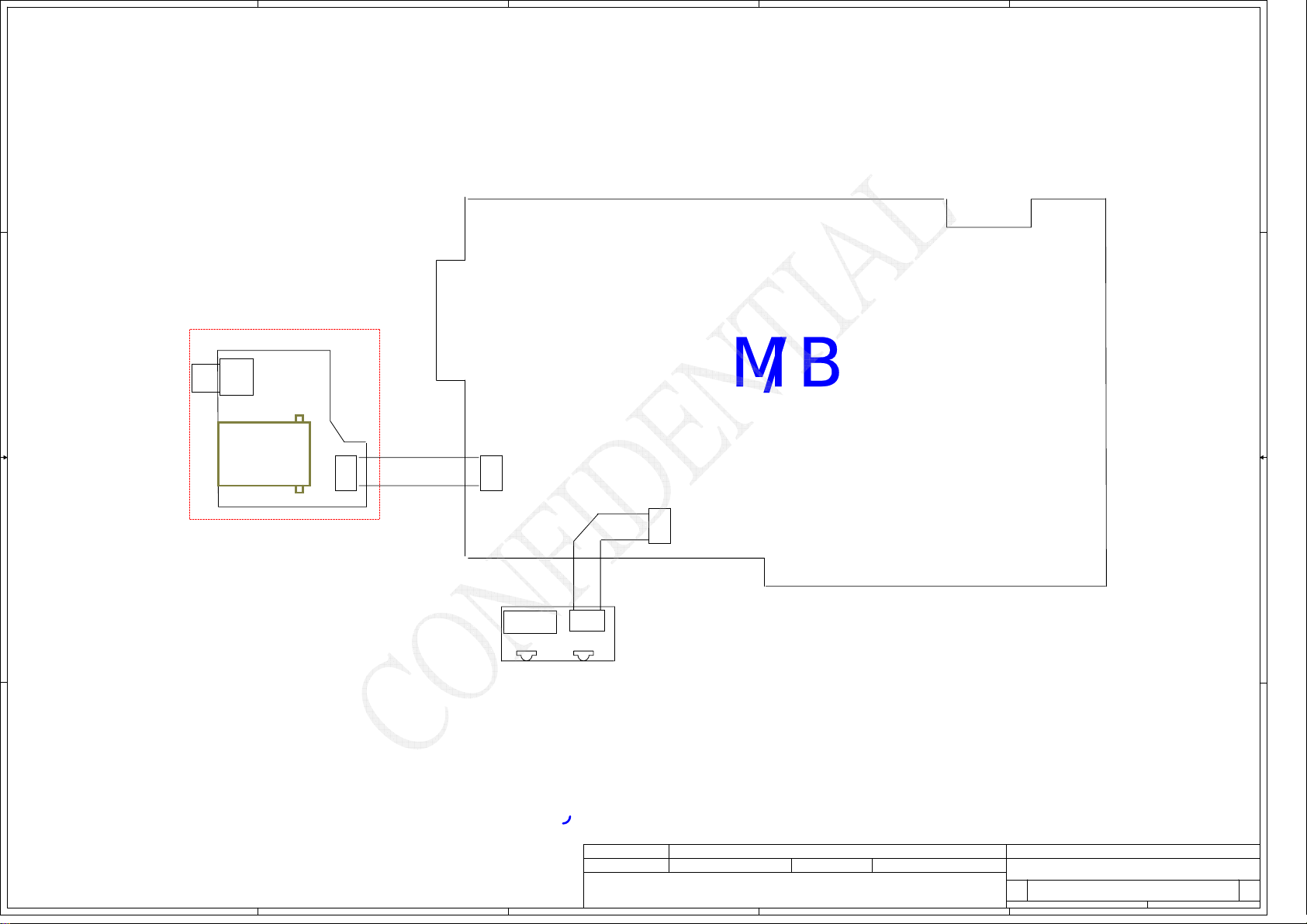

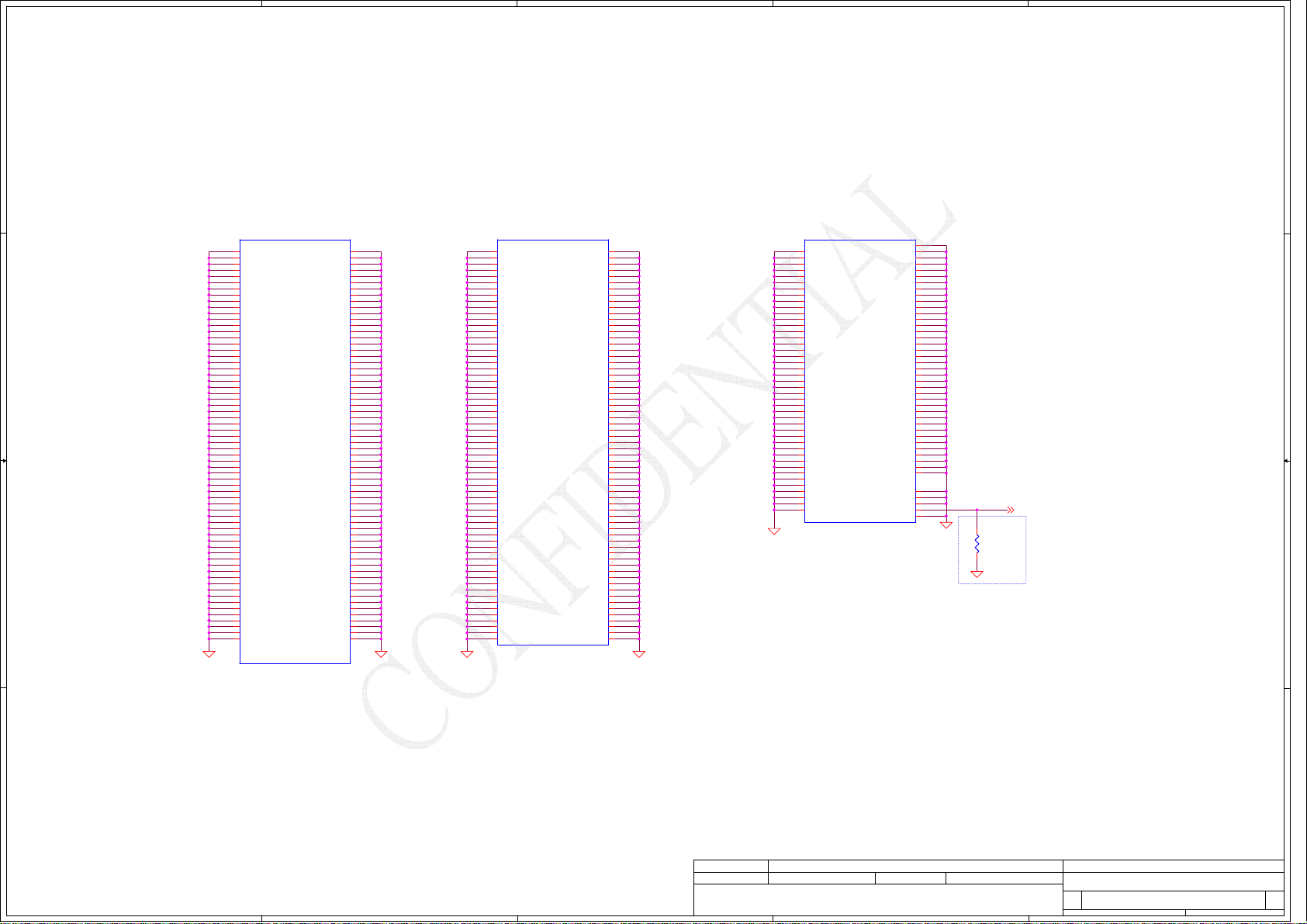

IOR /B

C C

JUSB3

JREAD

16pin

3in1

B B

JIO1

pin 1

FFC

JIO

pin 1

LidSwitch

LED2

JLED1

LED1

pin 1

JLED

8pin

pin 1

M

/

B

LED /B

A A

5

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

of

of

of

354Monday, April 07, 2014

354Monday, April 07, 2014

354Monday, April 07, 2014

A

A

A

5

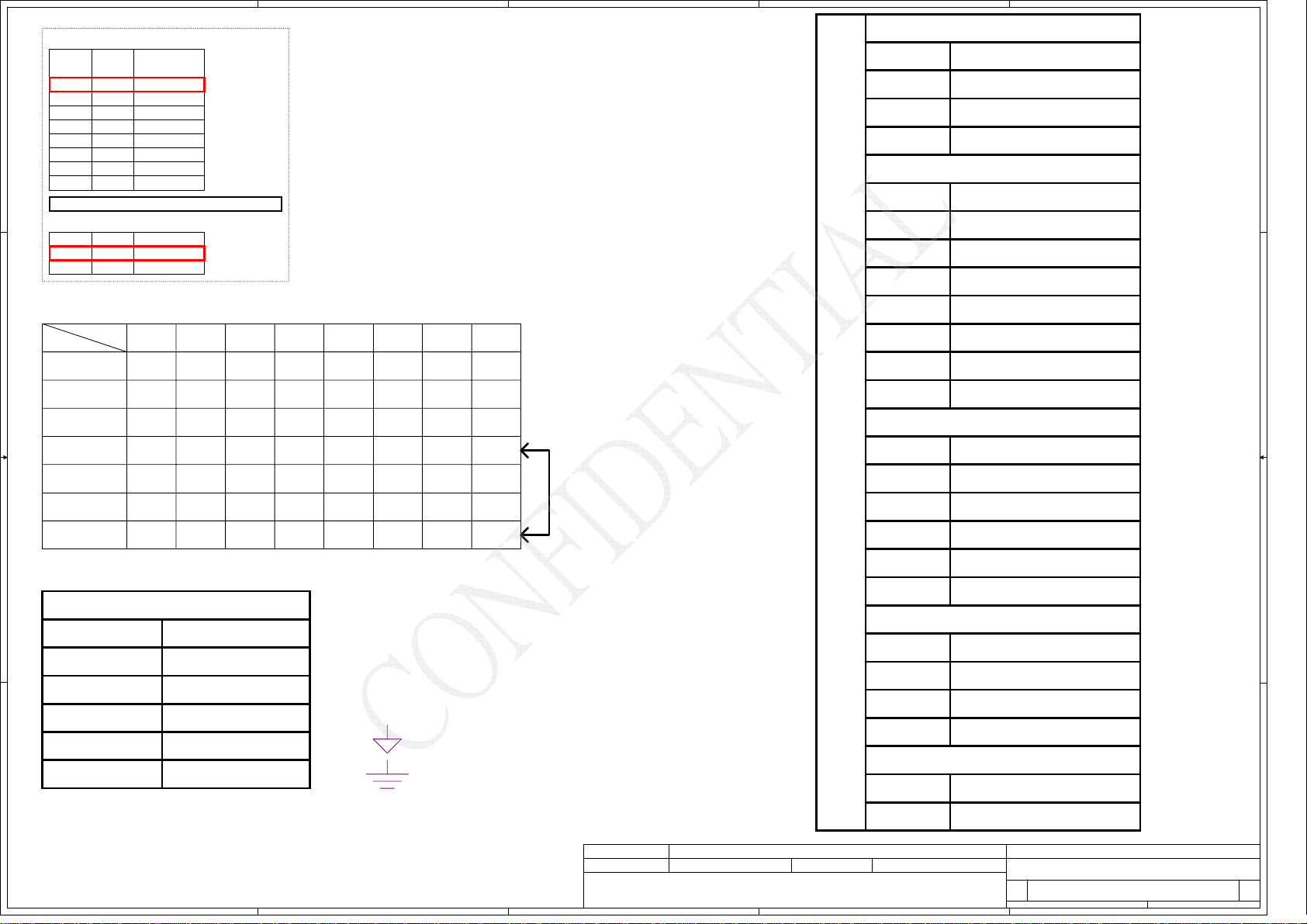

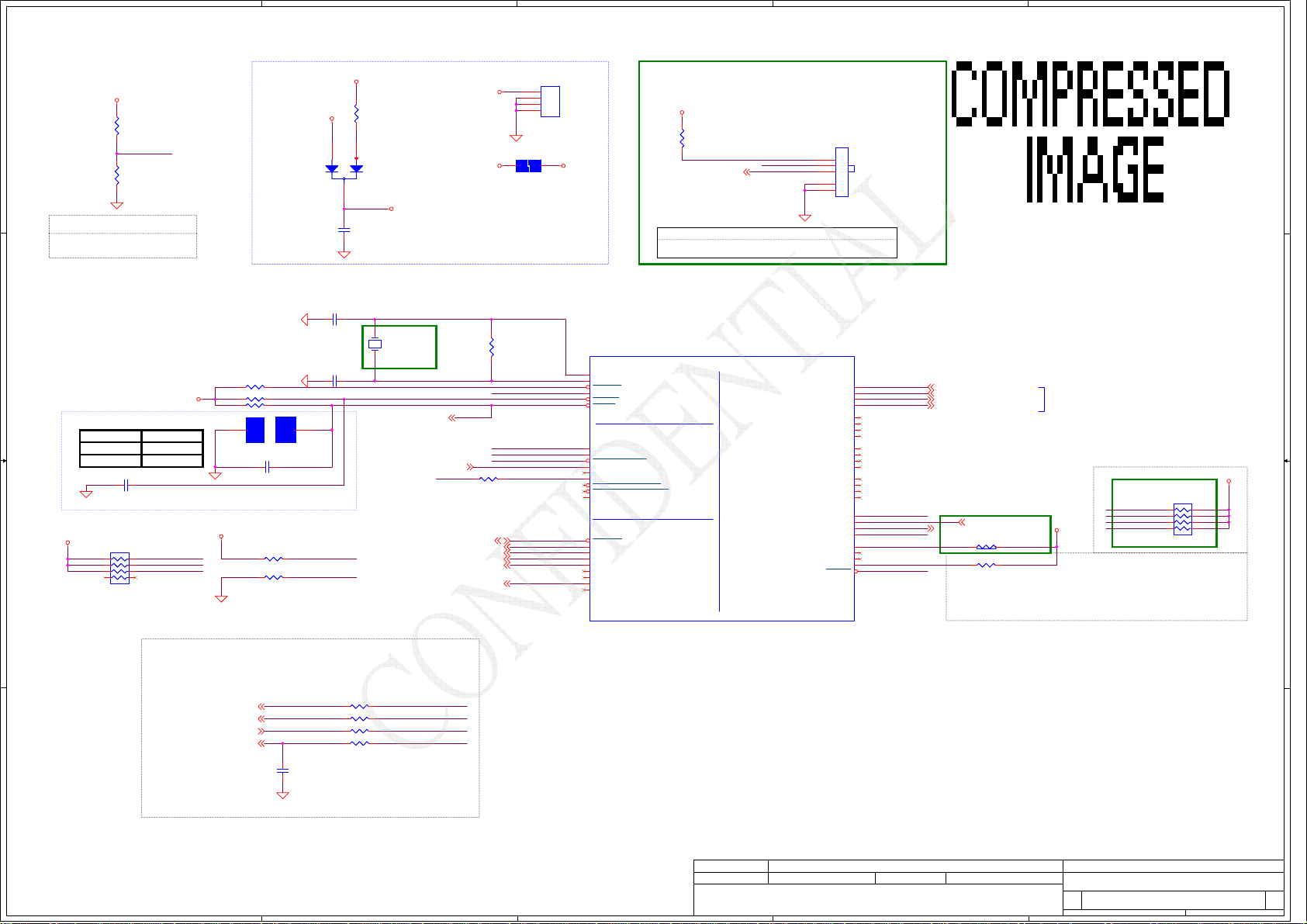

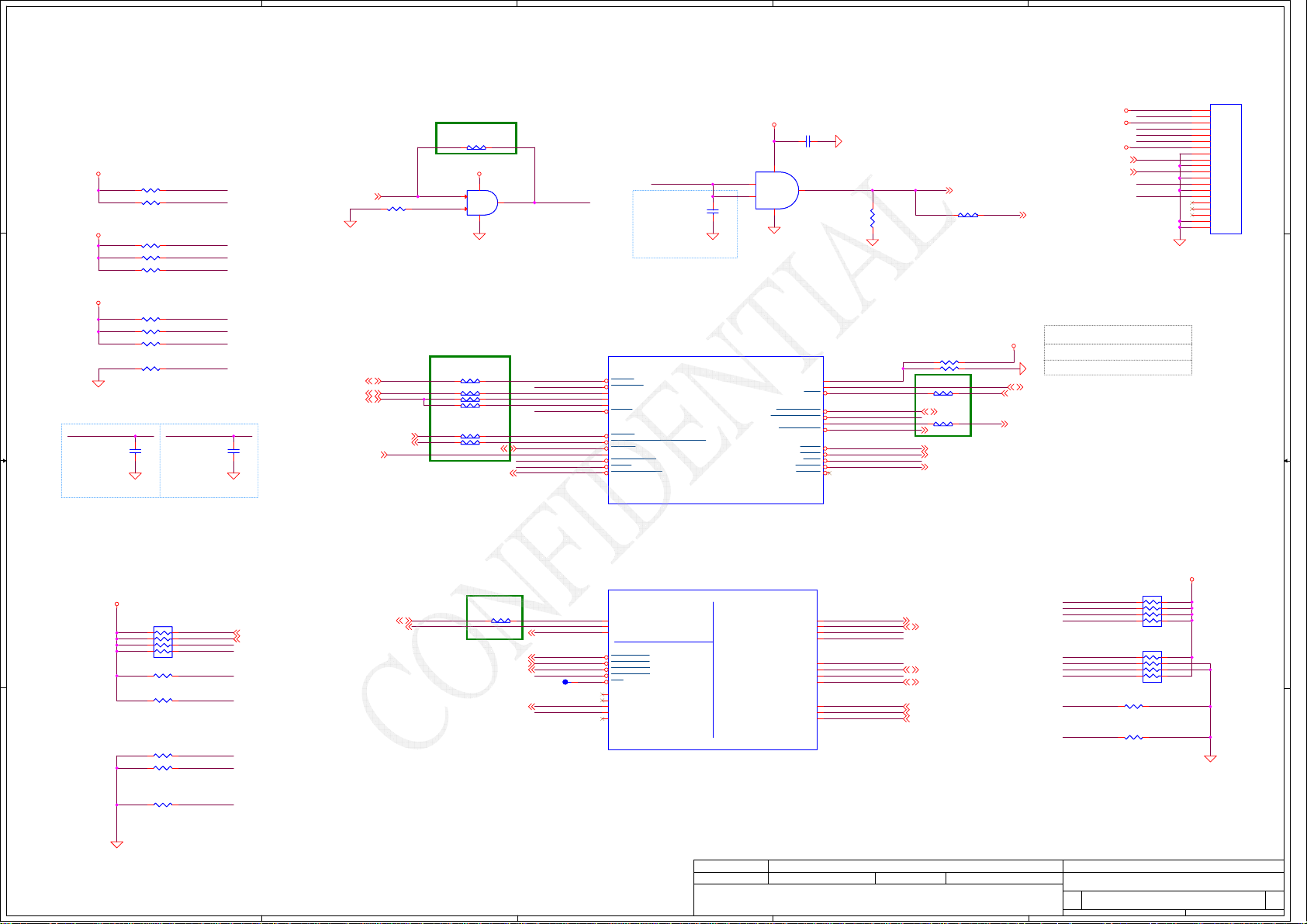

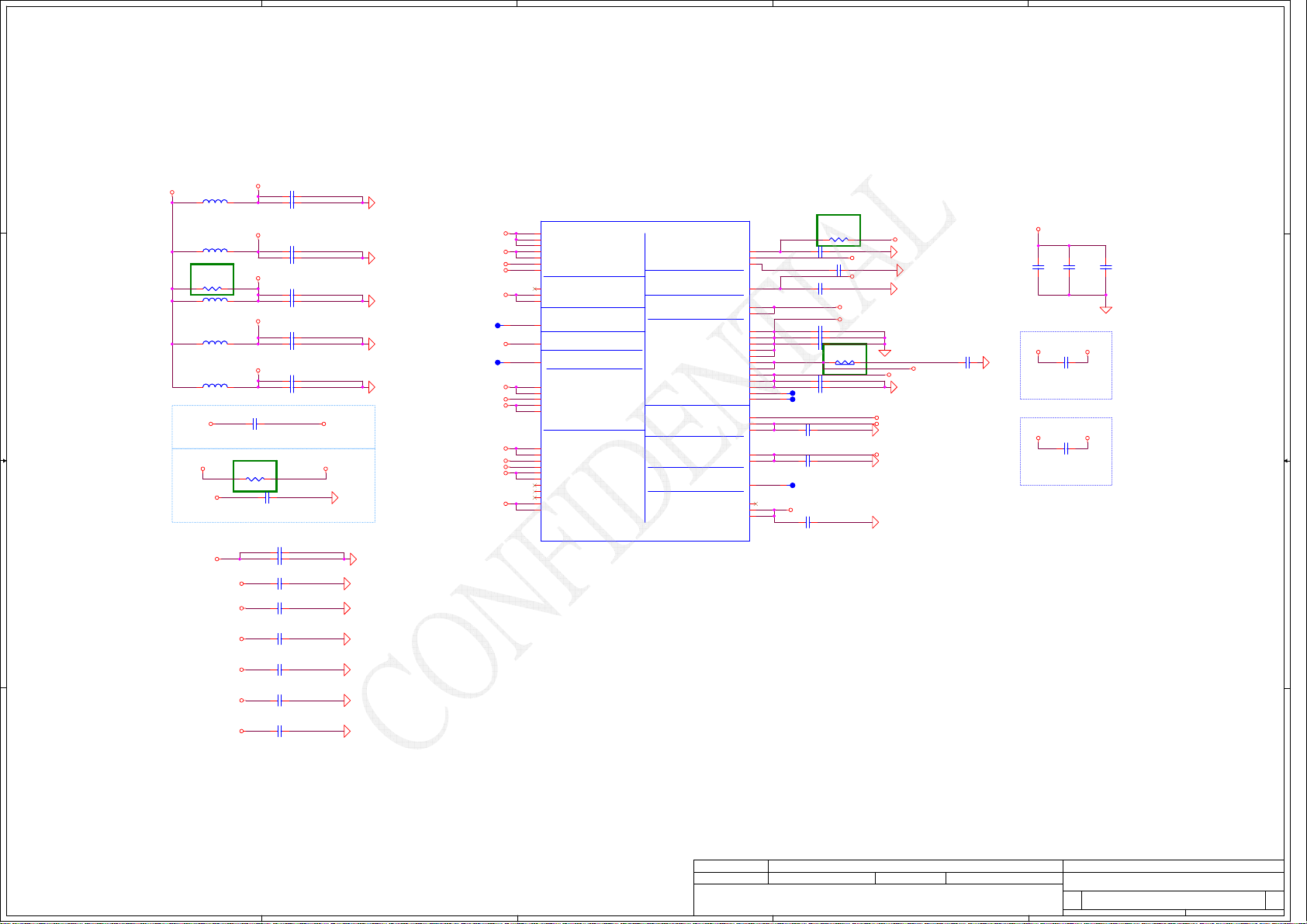

Board ID Table

Phase ID

RE79 CE54

240K 4700p X00

130K 4700p

D D

4700p

4700p

33K

4700p

8.2K

4700p

4.3K

2K

4700p

1K

4700p

BOARD_IDrisetimeismeasuredfrom5%~68%.

Config ID

RE89 RE90 Config

Pop

De-Pop

Pop

De-Pop

REV

X01

X0262K

X03

A00

Discrete

UMA

4

3

2

1

USB3.0

Port1

Port2

USB connector 1

USB connector 2

Port3

Port4

USB2.0

Port0

Port1

Port2

Port3

USB connector 1

USB connector 2

USB connector 3 (IO/B)

Finger print

SMBUS Control Table

Touch

C C

CHARGER_SMBCLK

CHARGER_SMBDAT

PBAT_SMBCLK

PBAT_SMBDAT

GPU_SMBDAT

SML1_SMBCLK

SML1_SMBDATA

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

B B

SOURCE

MEC5085

MEC5085

MEC5085GPU_SMBCLK

MEC5085

ULT

ULT

ULT

BATT

V

Charger

DDR3L

V

V

XDP

V

WLAN

NGFF

pad

VV

VGA

ULT

V

Link

Port4

Port5

Port6

Port7

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

NGFF (BT + WLAN)

Touch Screen Panel

Card Reader

Camera

PCI EXPRESS

10/100/1000 LAN

NGFF (BT + WLAN)

PEG (N15S)

Lane 6

CLOCK SIGNAL

SATA

CLKOUT_PCIE0

HDDSATA0

CLKOUT_PCIE1

SATA1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE4

10/100/1000 LAN

NGFF (BT + WLAN)

Symbol Note :

: means Digital Ground

SATA2

SATA3

DDI

CLKOUT_PCIE5

A A

5

: means Analog Ground

4

DDI1

DDI2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

HDMI

DP to CRT

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

A

A

A

of

of

of

454Monday, April 07, 2014

454Monday, April 07, 2014

454Monday, April 07, 2014

5

4

3

2

1

D D

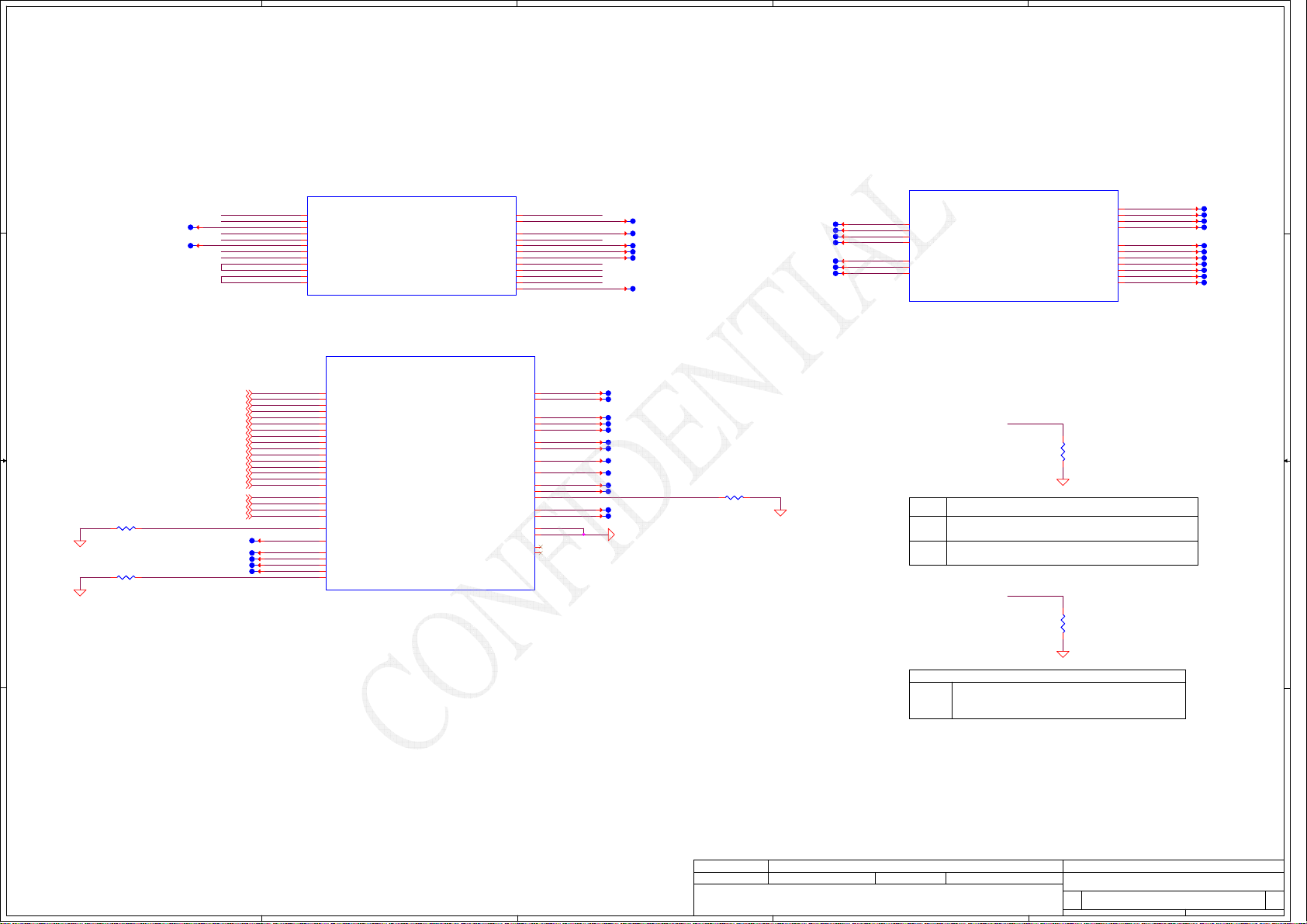

SMBUS Address [0x9a]

AP2

AH1

MEM_SMBCLK

MEM_SMBDATA

SML0CLK

MCP

C C

AN1

AK1

AN1

AK1

SML0DATA

SML1_SMBCLK

SML1_SMBDATA

79

SML1_SMBCLK

80

SML1_SMBDATA

2.2K

2.2K

1K

1K

2.2K

2.2K

+3.3V_ALW_PCH

N-MOS

N-MOS

+3.3V_ALW_PCH

+3.3V_ALW_PCH

2.2K

2.2K

DDR_XDP_WLAN_TP_SMBCLK

DDR_XDP_WLAN_TP_SMBDAT

+3VS

0 ohm

0 ohm

DDR_XDP_SMBCLK_R1

DDR_XDP_SMBDAT_R1

202

DIMMA

200

202

DIMMB

200

53

51

JXDP1

SMBUS Address [A0]

SMBUS Address [A4]

SMBUS Address [TBD]

2.2K

2.2K

77

B B

MEC 5085

CHARGER_SMBCLK

78

CHARGER_SMBDAT

+3VALW_5085

0 ohm

0 ohm

SCL

SDA

11

10

POWERPU700

Charger

SMBUS Address [0x12]

2.2K

+3VALW_5085

100 ohm

100 ohm

3

1

4

PD1

Z4304

65

Z4305

3

PBATT1

SMBUS Address [0x16]

BATT

CONN

PBAT_SMBCLK

PBAT_SMBDAT

2.2K

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

554Monday, April 07, 2014

554Monday, April 07, 2014

554Monday, April 07, 2014

of

of

of

A

A

A

5

4

3

2

1

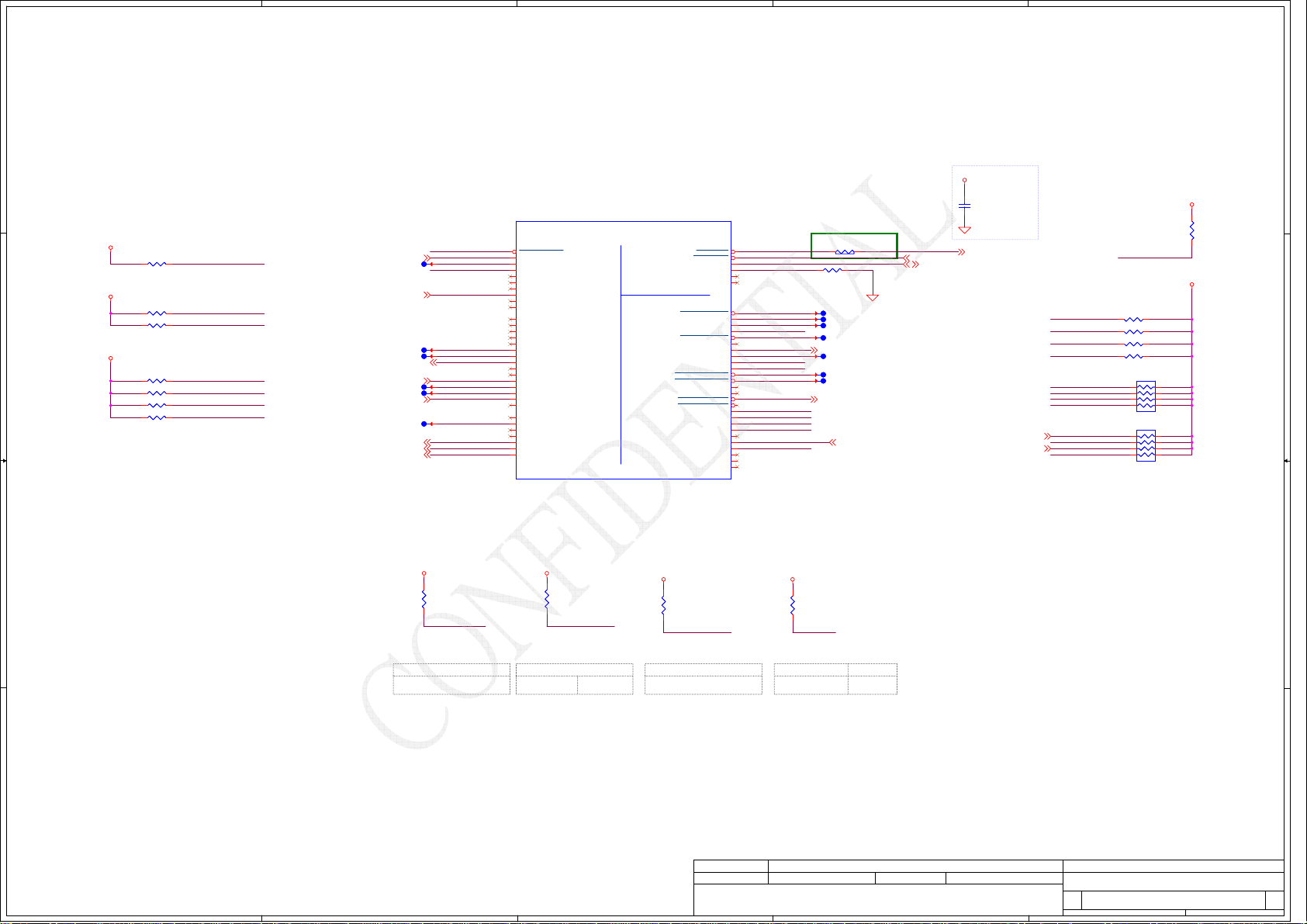

H_VCCST_PWRGD[13]

SIO_PWRBTN#[10,29]

CPU_PWR_DEBUG#[13]

SYS_PWROK[10,29]

DDR_XDP_WLAN_TP_SMBCLK[9,17,18]

HASWELL_MCP_E

HASWELL_MCP_E

HASWELL_MCP_E

HASWELL_MCP_E

+1.05VS

1

2

Place near JXDP1

+3VALW_PCH

1 OF 19

1 OF 19

JTAG

JTAG

2 OF 19

2 OF 19

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

1

CC14

@

CC14

@

CC15

@

CC15

@

2

RC5needtoclosetoJCPU1

1 2

RC114 1K_0402_5%XDP@RC114 1K_0402_5%XDP@

H_CPUPWRGD H_VCCST_PWRGD_XDP

SYS_PWROK

XDP@

XDP@

RC64

RC64

1K_0402_5%

1K_0402_5%

1 2

SYS_PWROK_XDP

1

@

@

CC16

CC16

0.1U_0402_10V7K

0.1U_0402_10V7K

2

Place near JXDP1.47

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

PROC_TRST

3

Rev1p2

Rev1p2

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

Rev1p2

Rev1p2

1 2

RC48 1K_0402_5%@RC48 1K_0402_5%@

1 2

RC49 0_0402_1%@RC49 0_0402_1%@

1 2

RC50 0_0402_1%@RC50 0_0402_1%@

1 2

RC52 0_0402_1%@RC52 0_0402_1%@

1 2

RC53 0_0402_1%@RC53 0_0402_1%@

1 2

RC54 0_0402_1%@RC54 0_0402_1%@

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

EDP_COMP

A43

EDP_DISP_UTIL

RC72 0_0402_5%@RC72 0_0402_5%@

J62

XDP_PRDY#

K62

XDP_PREQ#

E60

XDP_TCLK

E61

XDP_TMS

E59

XDP_TRST#

F63

XDP_TDI

F62

XDP_TDO XDP_TDI

J60

XDP_OBS0_R

H60

XDP_OBS1_R

H61

H62

K59

H63

K60

J61

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

CFG0[16]

CFG1[16]

CFG2[16]

CFG3[16]

CFG4[16]

CFG5[16]

CFG6[16]

CFG7[16]

1 2

EDP_TX0# [21]

EDP_TX0 [21]

EDP_TX1# [21]

EDP_TX1 [21]

T111@ T111@

T112@ T112@

T113@ T113@

T114@ T114@

T115@ T115@

T116@ T116@

XDP_PREQ#

XDP_PRDY#

XDP_OBS0_R

XDP_OBS1_R

CFD_PWRBTN#_XDP

CPU_PWR_DEBUG#_R

SYS_PWROK_XDP

DDR_XDP_SMBDAT_R1

DDR_XDP_SMBCLK_R1

PCH_JTAG_TCK

XDP_TCLK

EDP_AUX# [21]

EDP_AUX [21]

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

CFG3

JXDP

JXDP

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

39

PWRGOOD/HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030-01-L-D-A

SAMTE_BSH-030-01-L-D-A

CONN@

CONN@

COMPENSATION PU FOR eDP

EDP_BIA_PWM [10,21]

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.05VS+1.05VS

2

GND1

4

OBSFN_C0

6

OBSFN_C1

8

GND3

10

OBSDATA_C0

12

OBSDATA_C1

14

GND5

16

OBSDATA_C2

18

OBSDATA_C3

20

GND7

22

OBSFN_D0

24

OBSFN_D1

26

GND9

28

OBSDATA_D0

30

OBSDATA_D1

32

GND11

34

OBSDATA_D2

36

OBSDATA_D3

38

GND13

VCC_OBS_CD

DBR#/HOOK7

GND15

TRST#

TMS

GND17

40

42

44

46

XDP_RST#_R

48

XDP_DBRESET#

50

52

TDO_XDP

TD0

54

TRST#_XDP

56

TDI_XDP

TDI

58

TMS_XDP

60

CFG3_R

XDP_DBRESET#

+VCCIOA_OUT

12

RC7124.9_0402_1% RC7124.9_0402_1%

ITPCLK/HOOK4

ITPCLK#/HOOK5

RESET#/HOOK6

2

CFG17 [16]

CFG16 [16]

CFG8 [16]

CFG9 [16]

CFG10 [16]

CFG11 [16]

CFG19 [16]

CFG18 [16]

CFG12 [16]

CFG13 [16]

CFG14 [16]

CFG15 [16]

12

XDP@

XDP@

RC51

RC51

1K_0402_5%

1K_0402_5%

1 2

XDP@

XDP@

RC56 1K_0402_5%

RC56 1K_0402_5%

CFG3

XDP_DBRESET# [10]

PU/PD for JTAG signals

XDP_TMS

XDP_PREQ#

TDO_XDP

XDP_TDO

XDP_TCLK

XDP_TRST#

51_0402_5%

51_0402_5%

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

RC362

RC362

1K_0402_1%

1K_0402_1%

1 2

1 8

2 7

3 6

4 5

RP44

51_8P4R_5%

51_8P4R_5%

1 8

2 7

3 6

4 5

RP45

RP45

51_8P4R_5%

51_8P4R_5%

1

12

XDP@

XDP@

CC17

CC17

0.1U_0402_10V7K

0.1U_0402_10V7K

@RP44

@

12

PCH_PLTRST#_EC [10,22,25,29]

+3VS

+1.05VS

RC129@

RC129@

654Monday, April 07, 2014

654Monday, April 07, 2014

654Monday, April 07, 2014

A

A

A

of

of

of

+3VS

CC13

CC13

12

XDP@

PCH_JTAG_TDO[8]

D D

PCH_JTAG_TDI[8]

C C

B B

A A

1 2

@

@

RC44

X02.08

PCH_JTAG_TMS[8]

TDI_XDP TDI_XDP_R

0_0402_5%RC44

0_0402_5%

RUNPWROK[29]

PCH_JTAG_RST#[8]

+1.05VS

RC58 49.9_0402_1%@RC58 49.9_0402_1%@

RC60 62_0402_5%RC60 62_0402_5%

H_PROCHOT#[29,38,41]

22P_0402_50V8J

22P_0402_50V8J

DDR3 COMPENSATION SIGNALS

CAD Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mil

5

XDP@

0.1U_0402_10V7K

0.1U_0402_10V7K

1 2

@

@

RC43

RC45

RC46

0.1U_0402_10V7K

0.1U_0402_10V7K

1 2

1 2

TDO_XDP

0_0402_5%RC43

0_0402_5%

RUNPWROK

1 2

@

@

0_0402_5%RC45

0_0402_5%

RUNPWROK

1 2

@

@

TMS_XDP

0_0402_5%RC46

0_0402_5%

RUNPWROK

TRST#_XDP XDP_TRST#

RUNPWROK

1

CC29

ESD@CC29

ESD@

2

Place CC29

close to UC4

PCH_JTAG_JTAGX[8]

PCH_JTAG_TCK[8]

H_CATERR#

H_PROCHOT#

H_PROCHOT# H_PROCHOT#_R

1

EMI@

EMI@

12

CA26

CA26

2

12

RC68200_0402_1% RC68200_0402_1%

12

RC69121_0402_1% RC69121_0402_1%

12

RC70100_0402_1% RC70100_0402_1%

UC4

XDP@UC4

XDP@

14

VCC

2

1A

1

1OE

5

2A

4

2OE

9

3A

10

3OE

12

4A

13

4OE

74CBTLV3126BQ_DHVQFN14_2P5X3

74CBTLV3126BQ_DHVQFN14_2P5X3

reference Shark Bay ULT Validation Customer Debug Port

Implementation Requirement Rev 1.0

GND PAD

3

1B

6

2B

8

3B

11

4B

7

GND

15

X02.08

12

@

PCH_JTAG_RST#

0_0402_5% RC57

0_0402_5%

0_0402_5% RC59

0_0402_5%

PCH_JTAG_TDO TDI_XDP_R

RC66

RC66

10K_0402_5%

10K_0402_5%

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

@

@

@

DDI1_LANE_N0[19]

DDI1_LANE_P0[19]

DDI1_LANE_N1[19]

DDI1_LANE_P1[19]

DDI1_LANE_N2[19]

DDI1_LANE_P2[19]

DDI1_LANE_N3[19]

DDI1_LANE_P3[19]

DDI2_LANE_N0[20]

DDI2_LANE_P0[20]

DDI2_LANE_N1[20]

DDI2_LANE_P1[20]

PECI_EC[29]

1 2

RC67 56_0402_5%RC67 56_0402_5%

1

CC27

CC27

100P_0402_50V8J

100P_0402_50V8J

ESD@

ESD@

2

ESD solution

DDR3_DRAMRST#_CPU[17]

DDR_PG_CTRL[17]

XDP_TRST#

RC57

12

XDP_TCLK

RC59

12

TDO_XDP

RC620_0402_5% @ RC620_0402_5% @

12

RC630_0402_5% @ RC630_0402_5% @

12

XDP_TCLK

RC650_0402_5% @ RC650_0402_5% @

CC35

CC35

0.047U_0402_16V4Z

0.047U_0402_16V4Z

Place CC35

on BOT

4

DDI1_LANE_N0

DDI1_LANE_P0

DDI1_LANE_N1

DDI1_LANE_P1

DDI1_LANE_N2

DDI1_LANE_P2

DDI1_LANE_N3

DDI1_LANE_P3

DDI2_LANE_N0

DDI2_LANE_P0

DDI2_LANE_N1

DDI2_LANE_P1

H_CATERR#

H_CPUPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

1

2

@

@

XDP_TDOPCH_JTAG_TDO

XDP_TDI

XDP_TMS

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

UC1A

UC1A

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

@

@

UC1B

UC1B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

@

@

DDR_XDP_WLAN_TP_SMBDAT[9,17,18]

DDI EDP

DDI EDP

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3

DDR3

5

4

3

2

1

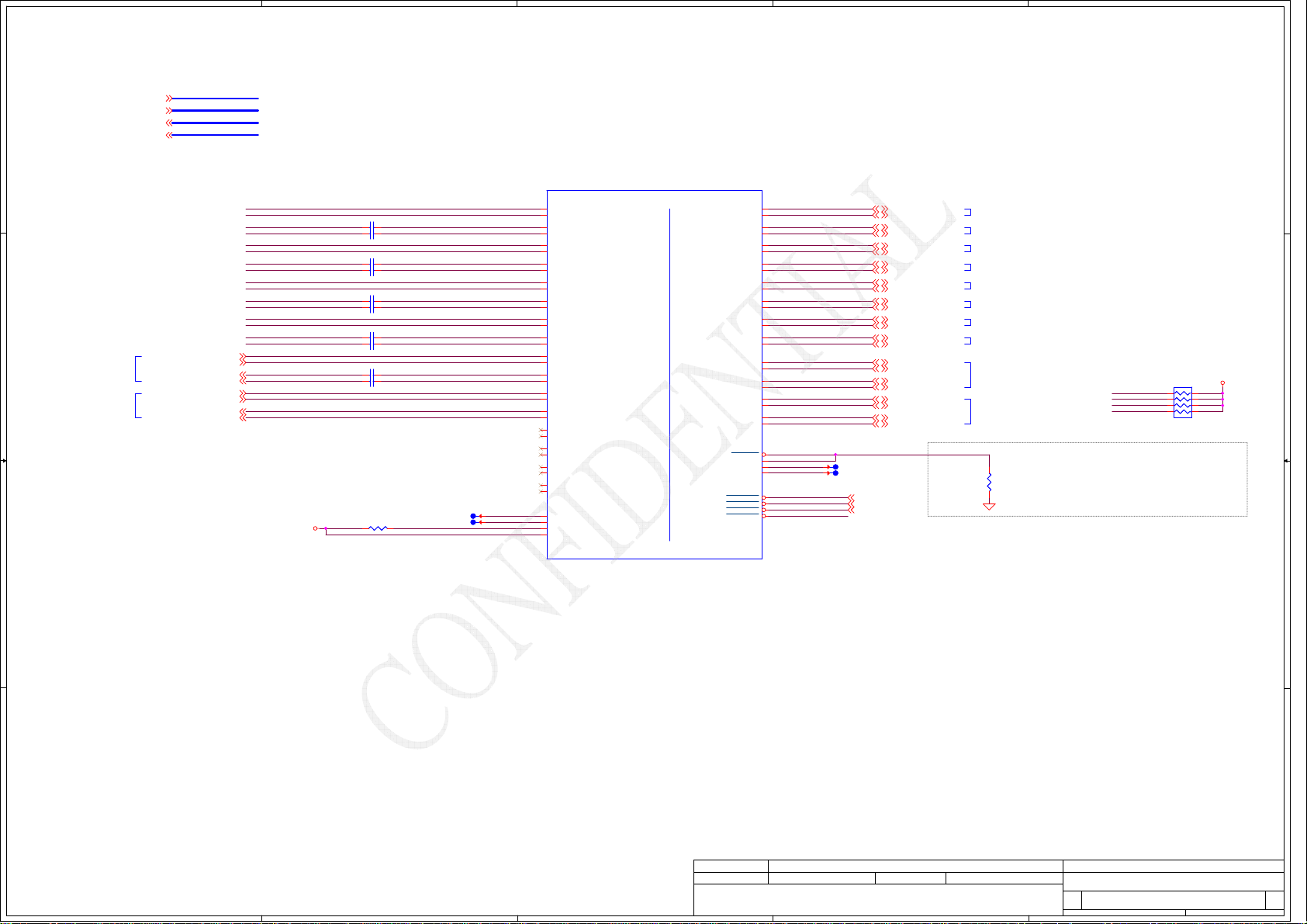

InterleavedMemory

HASWELL_MCP_E

UC1D

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

UC1D

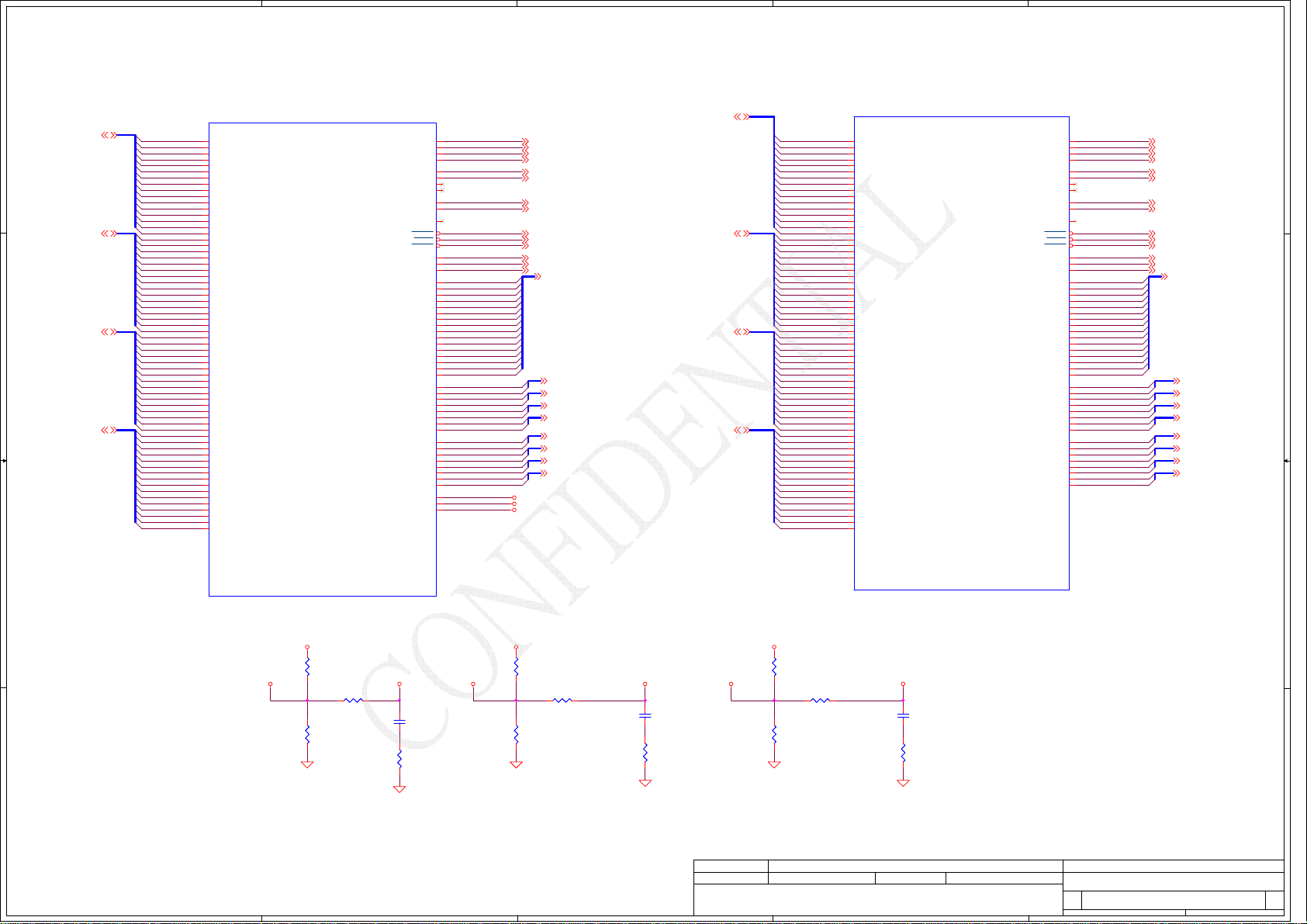

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HASWELL_MCP_E

UC1C

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

UC1C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

D D

DDR_A_D[0..15][17]

DDR_B_D[0..15][18]

DDR_A_D[16..31][17]

C C

DDR_B_D[16..31][18]

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

HASWELL_MCP_E

DDR CHANNEL A

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_CLK_DDR#0

M_CLK_DDR0

M_CLK_DDR#1

M_CLK_DDR1

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_A_RAS#

DDR_A_WE#

DDR_A_CAS#

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_DQS#0

DDR_A_DQS#1

DDR_B_DQS#0

DDR_B_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_B_DQS#2

DDR_B_DQS#3

DDR_A_DQS0

DDR_A_DQS1

DDR_B_DQS0

DDR_B_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_B_DQS2

DDR_B_DQS3

M_CLK_DDR#0 [17]

M_CLK_DDR0 [17]

M_CLK_DDR#1 [17]

M_CLK_DDR1 [17]

DDR_CKE0_DIMMA [17]

DDR_CKE1_DIMMA [17]

DDR_CS0_DIMMA# [17]

DDR_CS1_DIMMA# [17]

DDR_A_RAS# [17]

DDR_A_WE# [17]

DDR_A_CAS# [17]

DDR_A_BS0 [17]

DDR_A_BS1 [17]

DDR_A_BS2 [17]

DDR_A_MA[0..15] [17]

DDR_A_DQS#[0..1] [17]

DDR_B_DQS#[0..1] [18]

DDR_A_DQS#[2..3] [17]

DDR_B_DQS#[2..3] [18]

DDR_A_DQS[0..1] [17]

DDR_B_DQS[0..1] [18]

DDR_A_DQS[2..3] [17]

DDR_B_DQS[2..3] [18]

+SM_VREF_CA

+SM_VREF_DQ0

+SM_VREF_DQ1

DDR_A_D[32..47][17]

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_B_D[32..47][18]

DDR_A_D[48..63][17]

DDR_B_D[48..63][18]

DDR_A_D47

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

HASWELL_MCP_E

DDR CHANNEL B

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_CLK_DDR#2

M_CLK_DDR2

M_CLK_DDR#3

M_CLK_DDR3

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

DDR_B_RAS#

DDR_B_WE#

DDR_B_CAS#

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_A_DQS#4

DDR_A_DQS#5

DDR_B_DQS#4

DDR_B_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_B_DQS#6

DDR_B_DQS#7

DDR_A_DQS4

DDR_A_DQS5

DDR_B_DQS4

DDR_B_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_B_DQS6

DDR_B_DQS7

M_CLK_DDR#2 [18]

M_CLK_DDR2 [18]

M_CLK_DDR#3 [18]

M_CLK_DDR3 [18]

DDR_CKE2_DIMMB [18]

DDR_CKE3_DIMMB [18]

DDR_CS2_DIMMB# [18]

DDR_CS3_DIMMB# [18]

DDR_B_RAS# [18]

DDR_B_WE# [18]

DDR_B_CAS# [18]

DDR_B_BS0 [18]

DDR_B_BS1 [18]

DDR_B_BS2 [18]

DDR_B_MA[0..15] [18]

DDR_A_DQS#[4..5] [17]

DDR_B_DQS#[4..5] [18]

DDR_A_DQS#[6..7] [17]

DDR_B_DQS#[6..7] [18]

DDR_A_DQS[4..5] [17]

DDR_B_DQS[4..5] [18]

DDR_A_DQS[6..7] [17]

DDR_B_DQS[6..7] [18]

B B

Rev1p2

3 OF 19

+1.35V

3 OF 19

12

RC14

RC14

1.82K_0402_1%

1.82K_0402_1%

12

RC20

RC20

1.82K_0402_1%

1.82K_0402_1%

1 2

RC17

RC17

2.2_0402_1%

2.2_0402_1%

@

@

A A

Rev1p2

+1.35V

12

RC15

RC15

1.82K_0402_1%

+SM_VREF_CA +SM_VREF_DQ1

1

CC8

CC8

0.022U_0402_16V7K

0.022U_0402_16V7K

2

change 22nF

12

RC23

RC23

24.9_0402_1%

24.9_0402_1%

1.82K_0402_1%

12

RC21

RC21

1.82K_0402_1%

1.82K_0402_1%

1 2

RC18

RC18

2.2_0402_1%

2.2_0402_1%

1

2

12

confirm by intel request PDG P141

@

@

+1.35V

12

RC16

RC16

1.82K_0402_1%

+SM_VREF_DQ0_DIMM1+SM_VREF_CA_DIMM +SM_VREF_DQ1_DIMM2

CC9

CC9

0.022U_0402_16V7K

0.022U_0402_16V7K

change 22nF change 22nF

RC24

RC24

24.9_0402_1%

24.9_0402_1%

1.82K_0402_1%

12

RC22

RC22

1.82K_0402_1%

1.82K_0402_1%

1 2

RC19

RC19

2.2_0402_1%

2.2_0402_1%

+SM_VREF_DQ0

1

2

12

4 OF 19

4 OF 19

CC10

CC10

0.022U_0402_16V7K

0.022U_0402_16V7K

RC25

RC25

24.9_0402_1%

24.9_0402_1%

Rev1p2

Rev1p2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

754Monday, April 07, 2014

754Monday, April 07, 2014

754Monday, April 07, 2014

of

of

of

A

A

A

5

4

3

2

1

ServiceModeSwitch:

AddaswitchtoME_FWPsignaltounlocktheMEregionand

allowtheentireregionoftheSPIflashtobeupdatedusingFPT.

+3VALW_PCH

12

RC9

RC9

1K_0402_5%

1K_0402_5%

ME_FWP_EC[29]

ME_FWPPCHhasinternal20KPD.

FLASHDESCRIPTORSECURITYOVERRIDE

HIGH→DISABLEME(MEcanupdate)‐‐>Pin1&Pin2short

LOW→ENABLEME(DEFAULT)‐‐>Pin2&Pin3short

HASWELL_MCP_E

HASWELL_MCP_E

RTC

RTC

JTAG

JTAG

5 OF 19

5 OF 19

ME_EN

SATAAUDIO

SATAAUDIO

SW3

SW3

1

2

3

4

G

G

5

G

G

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

Rev1p2

Rev1p2

SSAL120100_3P

SSAL120100_3P

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

PCH_GPIO34

HDD_DET#

PCH_GPIO36

PCH_GPIO37

SATA_IREF

SATA_RCOMP

SATA_ACT#

X02.13

SATA_PRX_DTX_N0_C [26]

SATA_PRX_DTX_P0_C [26]

SATA_PTX_DRX_N0_C [26]

SATA_PTX_DRX_P0_C [26]

PCH_GPIO36 [10]

RC126 0_0603_5%@RC126 0_0603_5%@

RC131 3.01K_0402_1%RC131 3.01K_0402_1%

HDD_DET# [26]

1 2

1 2

+1.05VS_ASATA3PLL

X02.08

within 500 mils

SATA HDD

X02.04

1 8

HDD_DET#

2 7

SATA_ACT#

3 6

PCH_GPIO37

4 5

PCH_GPIO34

RP37

RP37

10K_8P4R_5%

10K_8P4R_5%

SATA Impedance Compensation

CAD note:

Place the resistor within 500 mils of the PCH. Avoid

routing next to clock pins.

reference FFRD sch 0.5

+3VS

+CHGRTC

CC1

CC1

15P_0402_50V8J

15P_0402_50V8J

1 2

ESR MAX=50k ohm

CC2

CC2

15P_0402_50V8J

15P_0402_50V8J

1 2

2

PCH_JTAG_JTAGXPCH_JTAG_TDI

PCH_JTAG_TCK

+RTCBATT

3

1

1

CC26

CC26

1U_0603_10V6K

1U_0603_10V6K

2

RC10

RC10

1K_0402_5%

1K_0402_5%

1 2

W=20mils

2

DC1

DC1

BAT54CW_SOT323-3

BAT54CW_SOT323-3

12

YC1

YC1

32.768KHZ_12.5PF_9H03220008

32.768KHZ_12.5PF_9H03220008

+RTCVCC

X02.03

PCH_RTCRST#[10]

PCH_AZ_CODEC_SDIN0[23]

+RTCBATT

+CHGRTC

1 2

RC8 1K_0402_5%RC8 1K_0402_5%

PCH_JTAG_RST#[6]

PCH_JTAG_TCK[6]

PCH_JTAG_TDI[6]

PCH_JTAG_TDO[6]

PCH_JTAG_TMS[6]

PCH_JTAG_JTAGX[6]

1

2

3

4

ACES_50271-0020N-001

ACES_50271-0020N-001

PJP12

PJP12

2

JUMP_43X39

JUMP_43X39

@

@

PCH_RTCX1

12

RC4

RC4

10M_0402_5%

10M_0402_5%

PCH_RTCX2

INTRUDER#

PCH_INTVRMEN

SRTCRST#

PCH_RTCRST#

PCH_AZ_BITCLK

PCH_AZ_SYNC

PCH_AZ_RST#

PCH_AZ_SDOUTME_EN

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_JTAGX

112

JRTC

JRTC

1

2

GND

GND

CONN@

CONN@

+3VLP

UC1E

UC1E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

@

@

+RTCVCC

12

RC1

D D

INTVRMEN‐INTEGRATEDSUS1.05VVRM

ENABLE

High‐EnableInternalVRs

Low‐EnableExternalVRs

C C

+1.05VS

B B

RC1

330K_0402_1%

330K_0402_1%

PCH_INTVRMEN

12

@

@

RC2

RC2

330K_0402_1%

330K_0402_1%

+RTCVCC

CMOS1

Shunt ClearCMOS

Open

CMOSsetting

KeepCMOS

1 2

CC3 1U_0402_6.3V6KCC3 1U_0402_6.3V6K

1 8

2 7

PCH_JTAG_TDO

3 6

PCH_JTAG_TMS

4 5

RP48

RP48

51_8P4R_5%

51_8P4R_5%

RTC Battery

W=20mils

W=20mils

1 2

RC7 1M_0402_5%RC7 1M_0402_5%

1 2

1 2

RC5 20K_0402_5%RC5 20K_0402_5%

RC6 20K_0402_5%RC6 20K_0402_5%

1

1

2

@

@

CMOS1 SHORT PADS~D

CMOS1 SHORT PADS~D

1 2

1U_0402_6.3V6K

1U_0402_6.3V6K

CC4

CC4

CMOS place near DIMM

+1.05VS

12

@

@

RC130 1K_0402_1%

RC130 1K_0402_1%

RC135 51_0402_1%

RC135 51_0402_1%

12

@

@

HDA for Codec

1 2

EMI@

EMI@

1

CC5

CC5

27P_0402_50V8J

27P_0402_50V8J

2

R2356 33_0402_5%EMI@ R2356 33_0402_5%EMI@

1 2

R2357 33_0402_5%EMI@ R2357 33_0402_5%EMI@

1 2

R2358 33_0402_5%EMI@ R2358 33_0402_5%EMI@

1 2

R2359 33_0402_5%EMI@ R2359 33_0402_5%EMI@

PCH_AZ_CODEC_SDOUT[23]

PCH_AZ_CODEC_SYNC[23]

PCH_AZ_CODEC_RST#[23]

PCH_AZ_CODEC_BITCLK[23]

A A

PCH_AZ_SDOUT

PCH_AZ_SYNC

PCH_AZ_RST#

PCH_AZ_BITCLK

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

854Monday, April 07, 2014

854Monday, April 07, 2014

854Monday, April 07, 2014

of

of

of

A

A

A

5

4

3

2

1

D D

UC1G

UC1G

EMI@

EMI@

C2326

C2326

68P_0402_50V8J

68P_0402_50V8J

1

2

+3VS

R2334 1K_0402_1%R2334 1K_0402_1%

R2335 1K_0402_1%R2335 1K_0402_1%

PCH_SPI_MOSI_1

PCH_SPI_MISO_1

PCH_SPI_WP1#

PCH_SPI_HOLD1#

1 2

1 2

LPC_LAD0[29]

LPC_LAD1[29]

LPC_LAD2[29]

LPC_LAD3[29]

LPC_LFRAME#[29]

1 2

R2333 15_0402_1%R2333 15_0402_1%

RP39

RP39

1 8

2 7

3 6

4 5

15_0804_8P4R_5%

15_0804_8P4R_5%

PCH_SPI_CLKPCH_SPI_CLK_R

PCH_SPI_CS0#

PCH_SPI_MOSI

PCH_SPI_MISO

PCH_SPI_WP#

PCH_SPI_HOLD#

AU14

AW12

AY12

AW11

AV12

LAD0

LAD1

LAD2

LAD3

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

@

@

HASWELL_MCP_E

HASWELL_MCP_E

LPC

LPC

SPI C-LINK

SPI C-LINK

7 OF 19

7 OF 19

SMBUS

SMBUS

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML1ALERT/PCHHOT/GPIO73

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

Rev1p2

Rev1p2

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

PCH_SMB_ALERT#

MEM_SMBCLK

MEM_SMBDATA

SML0CLK

SML0DATA

SML1_SMBCLK

SML1_SMBDATA

10K_0402_5%

10K_0402_5%

T97@ T97@

T98@ T98@

T99@ T99@

+3VALW_PCH

12

R2329

R2329

SML1_SMBCLK [29]

SML1_SMBDATA [29]

12

R2330

R2330

10K_0402_5%

10K_0402_5%

MEM_SMBCLK

MEM_SMBDATA

SML1_SMBCLK

SML1_SMBDATAPCH_GPIO73

SML0CLK

R2527 1K_0402_1%R2527 1K_0402_1%

SML0DATA

R2528 1K_0402_1%R2528 1K_0402_1%

RP40

RP40

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

1 2

1 2

+3VALW_PCH

MEM Bus : DDR/XDP/WLAN/TP

R2331

R2331

2.2K_0402_5%

2.2K_0402_5%

+3VS

12

12

R2332

R2332

2.2K_0402_5%

2.2K_0402_5%

DDR_XDP_WLAN_TP_SMBCLK [6,17,18]

DDR_XDP_WLAN_TP_SMBDAT [6,17,18]

C C

SPI ROM ( 8MByte )

U2302

U2302

PCH_SPI_CS0#

PCH_SPI_MISO_1

PCH_SPI_WP1#

1

/CS

2

DO(IO1)

3

/WP(IO2)

4

GND

W25Q64FVSSIQ_SO8

W25Q64FVSSIQ_SO8

/HOLD(IO3)

DI(IO0)

8

VCC

7

6

CLK

5

PN : SA000039A30 ,W25Q64FVSSIQ

+3VS

PCH_SPI_HOLD1#

PCH_SPI_CLK_R

PCH_SPI_MOSI_1

C2327

C2327

0.1U_0402_10V7K

0.1U_0402_10V7K

1 2

MEM_SMBCLK

MEM_SMBDATA

+3VS

2

G

G

6 1

D

D

5

DMN66D0LDW-7_SOT363-6

DMN66D0LDW-7_SOT363-6

3 4

SGD

SGD

QC1A

QC1A

DMN66D0LDW-7_SOT363-6

DMN66D0LDW-7_SOT363-6

S

S

QC1B

QC1B

CC6

CC6

15P_0402_50V8J

15P_0402_50V8J

CC7

CC7

15P_0402_50V8J

15P_0402_50V8J

+PCH_VCCACLKPLL

12

12

12

12

CLK_PCI_MEC [29]

CLK_PCI_LPDEBUG [29]

1M_0402_5%

1M_0402_5%

RC12

B B

1 2

R2341 10K_0402_5%R2341 10K_0402_5%

+3VS

1 2

R2343 10K_0402_5%R2343 10K_0402_5%

+3VS

+3VS

+3VS

+3VS

CLK_PCIE_GFX#

CLK_PCIE_GFX

GFXCLK_REQ#

+3VS

1 2

R2340 10K_0402_5%R2340 10K_0402_5%

1 2

R2342 10K_0402_5%R2342 10K_0402_5%

1 2

R2345 10K_0402_5%R2345 10K_0402_5%

1 2

R2344 10K_0402_5%R2344 10K_0402_5%

LAN ------->

WLAN(Mini Card)--->

A A

CLK_PCIE_LAN#[22]

CLK_PCIE_LAN[22]

LAN_CLKREQ#[22]

CLK_PCIE_WLAN#[25]

CLK_PCIE_WLAN[25]

WLAN_CLKREQ#[25]

CLK_PCIE_GFX#[45]

CLK_PCIE_GFX[45]

GFXCLK_REQ#[45]

UC1F

UC1F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

@

@

HASWELL_MCP_E

HASWELL_MCP_E

CLOCK

CLOCK

SIGNALS

SIGNALS

6 OF 19

6 OF 19

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

Rev1p2

Rev1p2

A25

XTAL24_IN

B25

XTAL24_OUT

K21

M21

C26

CLK_BIASREF

C35

C34

AK8

AL8

AN15

AP15

B35

A35

1 2

R2523 10K_0402_5%R2523 10K_0402_5%

1 2

R2524 10K_0402_5%R2524 10K_0402_5%

1 2

R2525 10K_0402_5%R2525 10K_0402_5%

1 2

R2526 10K_0402_5%R2526 10K_0402_5%

CLKOUT_LPC0

CLKOUT_LPC1

RC12

3

4

YC2

YC2

24MHZ_12PF_X3G024000DC1H

24MHZ_12PF_X3G024000DC1H

1

2

1 2

RC13

RC13

3.01K_0402_1%

3.01K_0402_1%

1 2

R2336 22_0402_5%EMI@R2336 22_0402_5%EMI@

R2339 22_0402_5%

R2339 22_0402_5%

EMI@

EMI@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

954Monday, April 07, 2014

954Monday, April 07, 2014

954Monday, April 07, 2014

of

of

of

A

A

A

5

4

3

2

1

JAPS

JAPS

+3VALW_PCH

+3V_DSW

+3V_DSW

PCH_RTCRST#[8]

POWER_SW#_MB[27,29]

DSWODVREN‐ONDIEDSWVRENABLE

HIGH=ENABLED(DEFAULT)

LOW=DISABLED

PCH_DPWROK [29]

1

IN1

2

IN2

+3VS

5

VCC

GND

3

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

CC11

@CC11

@

1 2

0.1U_0402_10V7K

0.1U_0402_10V7K

4

OUT

UC3

UC3

MC74VHC1G08DFT2G_SC70-5

MC74VHC1G08DFT2G_SC70-5

AW7

DSWVRMEN

AV5

DPWROK

AJ5

WAKE

V5

AG4

AE6

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

Rev1p2

Rev1p2

AP5

AJ6

AT4

AL5

AP4

AJ7

SLP_S5/GPIO63

12

R159

R159

100K_0402_5%

100K_0402_5%

DSWODVREN

PCH_PCIE_WAKE#_R

CLKRUN#

SUS_STAT#/LPCPD#

SUSCLK_R

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S3#

SIO_SLP_A#

SIO_SLP_SUS#

PCH_PLTRST#_EC [6,22,25,29]

1 2

@

@

RC367 0_0402_1%

RC367 0_0402_1%

1 2

R2337 330K_0402_5%R2337 330K_0402_5%

1 2

R2338 330K_0402_5%@R2338 330K_0402_5%@

X02.08

1 2

RC97@0_0402_5%RC97@0_0402_5%

CLKRUN# [29]

1 2

RC107 @ 0_0402_5%RC107 @ 0_0402_5%

SIO_SLP_S5# [29]

SIO_SLP_S4# [29]

SIO_SLP_S3# [29]

SIO_SLP_SUS# [29]

PLTRST_GPU# [45]

+RTCVCC

PCH_PCIE_WAKE# [28,29]

SUSCLK [25]

D D

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

@

@

1

2

CLKRUN#

ME_SUS_PWR_ACK

SUSACK#

SUS_STAT#/LPCPD#

PCH_BATLOW#

AC_PRESENT

PCH_PCIE_WAKE#_R

PCH_RSMRST#_R

SYS_PWROK

CC31

0.047U_0402_16V4Z

0.047U_0402_16V4Z

Place CC31

on BOT

XDP_DBRESET#[6]

RC80@ 8.2K_0402_5%RC80@ 8.2K_0402_5%

SUSACK#[29]

SYS_PWROK[6,29]

RESET_OUT#[13,29]

1

@CC31

@

2

PCH_RSMRST#[29]

ME_SUS_PWR_ACK[29]

AC_PRESENT[29]

PCH_BATLOW# Need pull high to VCCDSW3_3

(If no deep Sx , connect to VCCSUS3_3)

12

SUSACK# SUSACK#_R

RC36 10K_0402_5%RC36 10K_0402_5%

RC95@ 8.2K_0402_5%RC95@ 8.2K_0402_5%

+3VALW_PCH

RC27 10K_0402_5%RC27 10K_0402_5%

RC28 10K_0402_5%RC28 10K_0402_5%

RC29 10K_0402_5%@RC29 10K_0402_5%@

+3V_DSW

RC39 10K_0402_5%RC39 10K_0402_5%

RC32 10K_0402_5%RC32 10K_0402_5%

C C

RC34 10K_0402_5%RC34 10K_0402_5%

RC92 10K_0402_5%

RC92 10K_0402_5%

RESET_OUT#

CC34

@CC34

@

0.047U_0402_16V4Z

0.047U_0402_16V4Z

Place CC34

close to RP50.2&RP50.3

X02.08

1 2

RC78 @ 0_0402_5%RC78 @ 0_0402_5%

+3VS+3VS

1

B

2

ME_RESET#

A

X02.08

1 2

RC37 @ 0_0402_5%RC37 @ 0_0402_5%

1 2

RC40 @ 0_0402_5%RC40 @ 0_0402_5%

1 2

RC47 @ 0_0402_5%RC47 @ 0_0402_5%

1 2

RC55 @ 0_0402_5%RC55 @ 0_0402_5%

1 2

RC41 @ 0_0402_5%RC41 @ 0_0402_5%

1 2

RC42 @ 0_0402_5%RC42 @ 0_0402_5%

SIO_PWRBTN#[6,29]

SIO_SLP_WLAN#[28]

5

P

4

O

G

UC5@

UC5@

74AHC1G09GW_TSSOP5

74AHC1G09GW_TSSOP5

3

SYS_RESET#ME_RESET#

SYS_RESET#

SYS_PWROK_R

RESET_OUT#_R

PM_APWROK_R

PCH_PLTRST#

PCH_RSMRST#_R

ME_SUS_PWR_ACK_R

AC_PRESENT

PCH_BATLOW#

SIO_SLP_S0#

Place CC33

close to UC3.1 & UC3.2

UC1H

UC1H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

@

@

PCH_PLTRST#

CC33

ESD@CC33

ESD@

0.047U_0402_16V4Z

0.047U_0402_16V4Z

HASWELL_MCP_E

HASWELL_MCP_E

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

1

2

8 OF 19

8 OF 19

SIO_SLP_S3#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_A#

SYS_RESET#

SIO_SLP_S0#

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

GND

20

GND

CONN@

CONN@

ACES_50506-01841-P01

ACES_50506-01841-P01

B B

+3VS

RP43

RP43

1

8

SIO_RCIN#

2

7

PCH_GPIO36

3

6

DGPU_PWROK

4 5

PCH_GPIO80

10K_8P4R_5%

10K_8P4R_5%

1 2

@

@

1 2

1 2

@

@

1 2

@

@

1 2

EDP_BIA_PWM

DGPU_PWR_EN

DGPU_PWR_EN

DGPU_CORE_EN

ENVDD_PCH

RC75 10K_0402_5%

RC75 10K_0402_5%

RC370 10K_0402_5%RC370 10K_0402_5%

RC368 10K_0402_5%

RC368 10K_0402_5%

RC369 10K_0402_5%

RC369 10K_0402_5%

A A

RC87 100K_0402_5%@RC87 100K_0402_5%@

SIO_RCIN# [11,29]

PCH_GPIO36 [8]

EDP_BIA_PWM[6,21]

PANEL_BKLEN[21]

X02.08

1 2

RC81@0_0402_5%RC81@0_0402_5%

ENVDD_PCH[21,29]

PCH_GPIO77[11]

DGPU_PWROK[28,44,45]

PCH_GPIO79[11]

DGPU_PWR_EN[49]

EDP_BKLCTLEDP_BIA_PWM

ENVDD_PCH

PCH_GPIO77

DGPU_PWROK

PCH_GPIO80

T117 @T117 @

DGPU_PWR_EN

DGPU_CORE_EN

B8

A9

C6

U6

P4

N4

N2

AD4

U7

L1

L3

R5

L4

UC1I

UC1I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

@

@

eDP SIDEBAND

eDP SIDEBAND

GPIO

GPIO

HASWELL_MCP_E

HASWELL_MCP_E

9 OF 19

9 OF 19

DISPLAY

DISPLAY

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

Rev1p2

Rev1p2

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

CPU_DPB_CTRLCLK

CPU_DPB_CTRLDAT

CPU_DPC_CTRLCLK

CPU_DPC_CTRLDAT

CPU_DPB_AUX#

CPU_DPC_AUX#

CPU_DPB_AUX

CPU_DPC_AUX

DPC_HPD

CPU_EDP_HPD

CPU_DPB_CTRLCLK [19]

CPU_DPB_CTRLDAT [19]

CPU_DPC_AUX# [20]

CPU_DPC_AUX [20]

DPB_HPD [19]

DPC_HPD [20]

CPU_EDP_HPD [21]

CPU_DPB_CTRLDAT

CPU_DPB_CTRLCLK

CPU_DPC_CTRLCLK

CPU_DPC_CTRLDAT

CPU_DPB_AUX#

CPU_DPB_AUX

CPU_DPC_AUX

CPU_DPC_AUX#

DPC_HPD

RC84 100K_0402_5%@RC84 100K_0402_5%@

CPU_EDP_HPD

RC89 100K_0402_5%RC89 100K_0402_5%

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 2

+3VS

RP52

RP52

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

RP51

RP51

100K_0804_8P4R_5%

100K_0804_8P4R_5%

12

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/08/01 2014/07/31

2013/08/01 2014/07/31

2013/08/01 2014/07/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

SCHEAMTICS,MB AB072

4019RU

4019RU

4019RU

1

10 54Monday, April 07, 2014

10 54Monday, April 07, 2014

10 54Monday, April 07, 2014

of

of

of

A

A

A

5

4

3

2

1

D D

+1.05VS

Close to R2353

1

CC28

CC28

100P_0402_50V8J

100P_0402_50V8J

@

HASWELL_MCP_E

UC1J

UC1J

+3V_DSW

1 2

RC153 10K_0402_5%RC153 10K_0402_5%

+3VS

1 2

RC98 100K_0402_5%RC98 100K_0402_5%

RC116 10K_0402_5%RC116 10K_0402_5%

C C

+3VALW_PCH

RC109 10K_0402_5%RC109 10K_0402_5%

RC105 10K_0402_5%RC105 10K_0402_5%

RC103 10K_0402_5%RC103 10K_0402_5%

RC117 10K_0402_5%RC117 10K_0402_5%

LAN_WAKE#

12

12

12

12

12

SIO_EXT_SCI#

PCH_GPIO76

SIO_EXT_WAKE#

SIO_EXT_SMI#

KB_DET#

PCH_GPIO12

SIO_EXT_WAKE#[29]

LAN_WAKE#[22,29]

DGPU_HOLD_RST#[45]

KB_DET#[30]

SIO_EXT_SMI#[29]

HDD_DEVSLP[26]

SIO_EXT_SCI#[29]

HDA_SPKR[23]

T182 PAD~D@ T182 PAD~D@

T174 PAD~D@ T174 PAD~D@

T124 PAD~D@ T124 PAD~D@

T126 PAD~D@ T126 PAD~D@

T127 PAD~D@ T127 PAD~D@

T27@ PAD~DT27@ PAD~D

PCH_GPIO76

SIO_EXT_WAKE#

PCH_GPIO12

HOST_ALERT1_R_N

LAN_WAKE#

PCH_GPIO47

DGPU_HOLD_RST#

KB_DET#

PCH_GPIO14

PCH_GPIO25

SIO_EXT_SMI#

PCH_GPIO10

SIO_EXT_SCI#

HDA_SPKR

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

@

@

HASWELL_MCP_E

GPIO

GPIO

10 OF 19

10 OF 19

CPU/

CPU/

MISC

MISC

LPIO

LPIO

THERMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

Rev1p2

Rev1p2

D60

H_THERMTRIP#_R

V4

T4

IRQ_SERIRQ

AW15

PCH_OPI_COMP

AF20

AB21

R6

GC6_EVENT#

L6

GPU_GC6_FB_EN

N6

PCH_GPIO85

L8

BBS_BIT

R7

PCH_GPIO87

L5

N7

TS_EN

K2

PCH_GPIO90

J1

CPPE#

K3

CPUSB#

J2

PCH_GPIO93

G1

PCH_GPIO94

K4

G2

J3

LCD_CBL_DET#

J4

F2

I2C0_SDA

F3