Page 1

CONTROL IC FOR LINE THERMAL PRINTER

(FOR LT SERIES)

SPECIFICATIONS

MODEL CBM-202LA

GATE ARRAY

Updated on Oct. 25, 1996

Japan CBM Corporation

Information Systems Div.

Page 2

CONTENTS

1 OUTLINE.................................................................................................................................................................3

2 GENERAL SPECIFICATIONS ................................................................................................................................4

2.1 SHAPE AND DIMENSIONS............................................................................................................................................... 4

2.2 STRUCTURE...................................................................................................................................................................... 4

2.3 OPERATING VOLTAGE .................................................................................................................................................... 4

2.4 OPERATING FREQUENCY............................................................................................................................................... 4

2.5 ENVIRONMENTAL SPECIFICATIONS............................................................................................................................. 4

2.6 APPLICABLE MODELS ..................................................................................................................................................... 4

3 OUTLINE OF CIRCUITS.........................................................................................................................................5

3.1 THERMAL HYSTERESIS CONTROL................................................................................................................................ 5

3.2 HEAD STROBE CONTROL ............................................................................................................................................... 5

3.3 BIT DATA PROCESSING FUNCTION............................................................................................................................... 5

3.4 8-BIT PARALLEL INPUT CIRCUIT ...................................................................................................................................5

3.5 GENERAL PURPOSE I/O CIRCUITS ................................................................................................................................. 5

4 DETAILED SPECIFICATIONS OF HARDWARE...................................................................................................6

4.1 ABSOLUTE MAXIMUM RATINGS................................................................................................................................... 6

4.2 RECOMMENDED OPERATING RANGE .......................................................................................................................... 6

4.3 DIRECT CURRENT CHARACTERISTIC ........................................................................................................................... 6

4.4 TERMINALS AND THEIR FUNCTIONS............................................................................................................................ 8

4.5 POWER TERMINAL.........................................................................................................................................................10

4.6 INTERNAL ADDRESS MAP ............................................................................................................................................ 11

4.7 PRINT DATA TRANSFER METHOD............................................................................................................................... 12

4.8 RESET CIRCUIT............................................................................................................................................................... 14

4.9 SYSTEM CLOCK CIRCUIT.............................................................................................................................................. 15

4.10 HEAD VOLTAGE INTERRUPTING CIRCUIT ............................................................................................................... 15

4.11 HEAD BREAK-OFF DETECTING CIRCUIT .................................................................................................................. 15

4.12 PARALLEL INPUT CIRCUIT..........................................................................................................................................16

4.13 ADDRESS LATCH CIRCUIT.......................................................................................................................................... 16

4.14 GENERAL PURPOSE I/O OUTPUT CIRCUIT................................................................................................................ 17

4.15 BIT DATA PROCESSING METHOD.............................................................................................................................. 17

4.16 PSEUDO-SRAM CONNECTING METHOD ................................................................................................................... 19

4.17 OTHER CONTROL TERMINALS................................................................................................................................... 19

5 OPERATION TIMING...........................................................................................................................................20

6 PACKAGE SPECIFICATION................................................................................................................................21

6.1 SHAPE AND DIMENSIONS............................................................................................................................................. 21

6.2 MOUNT PAD DIMENSIONS............................................................................................................................................ 22

7 REFERENTIAL CIRCUIT DIAGRAM...................................................................................................................23

8 REMARKS FOR MOUNTING ............................................................................................................................... 25

8.1 TEMPERATURE CONDITIONS FOR MOUNTING ......................................................................................................... 25

8.2 STORAGE CONDITIONS................................................................................................................................................. 26

8.3 OTHERS........................................................................................................................................................................... 26

9 PACKING SPECIFICATIONS ...............................................................................................................................27

2

Page 3

1 OUTLINE

In order to assure proper operation, be sure to use this Gate Array following the contents of this specifications.

Absolutely, do not carry out anything other than specified in this specifications.

This Gate Array has the following specifications.

x With thermal hysteresis control function being added, high quality printing is made available.

x With strobe split control function being added, printing is performed in small current.

x Strobe signal excursion function can protect Head safely.

x With the head resistance value measurement circuit being mounted, head break-off error can be detected.

x Parallel interface is available by use of the parallel input port.

x Address latch function is provided.

x The general purpose I/O port can serve for input of a DIP SW, etc..

x Data processing function can serve to facilitate various kinds of data processing.

3

Page 4

2 GENERAL SPECIFICATIONS

2.1 SHAPE AND DIMENSIONS

100-pin plastic QFP package

23.6 u 17.6 u 2.7 (mm)

(See Section 6. PACKAGE SPECIFICATION.)

2.2 STRUCTURE

C-MOS LSI

2.3 OPERATING VOLTAGE

5V ur 10% DC

2.4 OPERATING FREQUENCY

16MHz r 5%

2.5 ENVIRONMENTAL SPECIFICATIONS

Temperature Operating temperature - 40ºC 㨪 + 85ºC

Storage temperature - 65ºC 㨪 + 150 ºC

2.6 APPLICABLE MODELS

LT280, LT380 series

Printing system: Thermal line dot system

4

Page 5

3 OUTLINE OF CIRCUITS

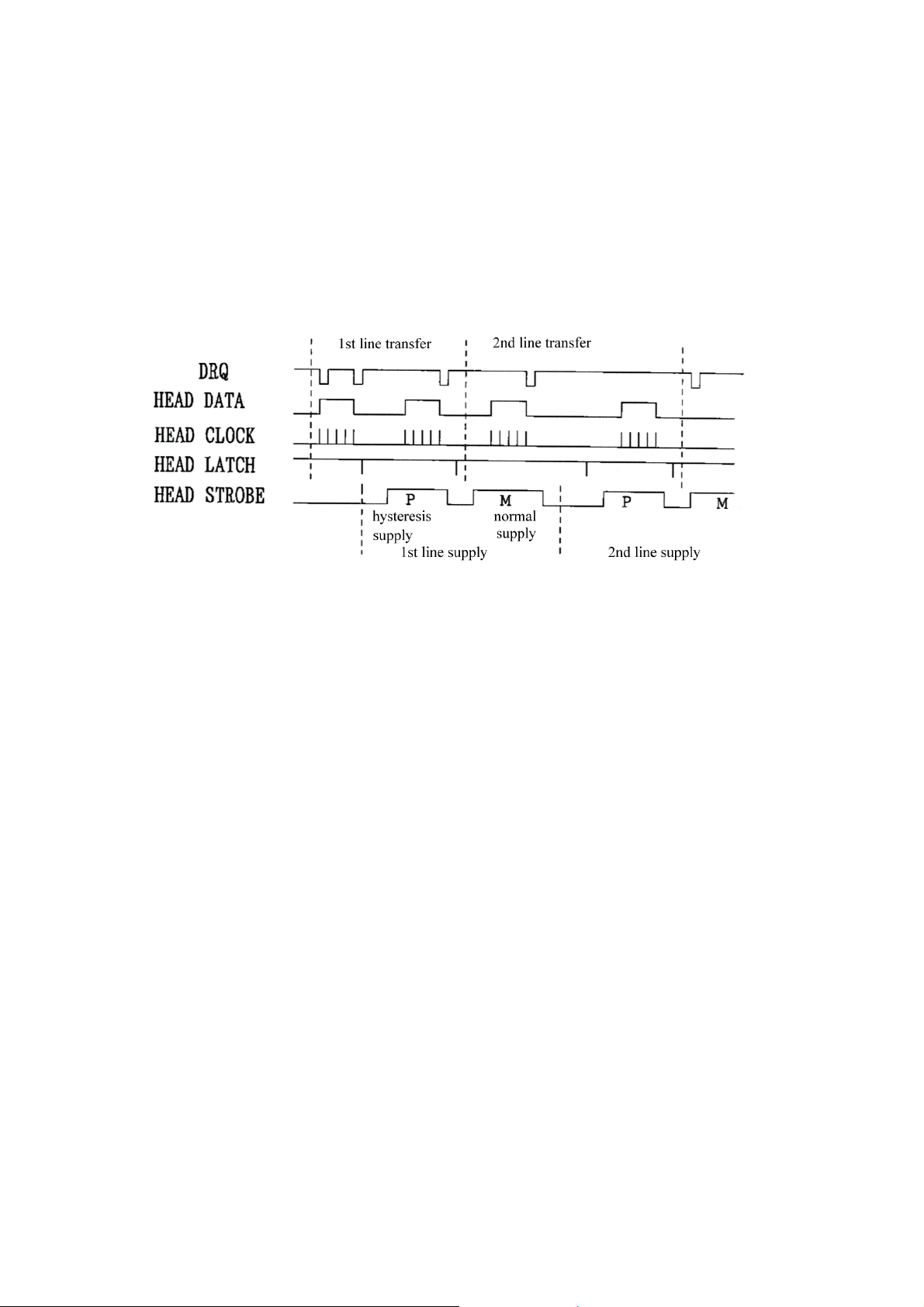

3.1 THERMAL HYSTERESIS CONTROL

When Line Thermal Head performs printing at high speed, heat remaining from printing which is one dot line before

may give some influence, resulting in blurred prints or trailing. This gate array, therefore, can serve to control

printing to the best result through monitoring state of operation of the preceding stage.

For printing of one dot line, one-dot-line data are transferred twice. The first data perform logical operation with

preceding data, serving as data for processing of print data for hysteresis supply. The second data substantially serve

for printing. Hysteresis supply (pre-pulse) and normal supply (main pulse) together compose one dot line supply.

To transfer data of one dot line, carry it out at high speed from CPU to the gate array by DMA, etc..

3.2 HEAD STROBE CONTROL

As one system to drive Line Thermal Head, one dot line is split into two or more blocks and current is supplied to each

of these blocks. Supply current capacity, thus, can be reduced. Switching in timing of current supply to these split

blocks is automatically performed by the gate array.

This is also equipped with a circuit which serves to prevent the thermal head from being damaged on occurrence of

strobe signal control failure due to CPU excursion, etc..

3.3 BIT DATA PROCESSING FUNCTION

This product is further provided with data processing function which is effective in developing printing data in bits.

For example, 8-bit data 180° turning function, 90° turning function, and 16-bit conversion (double font letter) function

are easily realized.

3.4 8-BIT PARALLEL INPUT CIRCUIT

Receiving of signals from Host is carried out in 8-bit parallel system. Received data from Host are STB, 8-bit data,

while data sent to Host are BUSY, ACK. When data are sent from Host, BUSY is output automatically. When CPU

starts reading the data, ACK is automatically output and BUSY is cancelled.

Use a general purpose port or CPU to deal with other control signals.

3.5 GENERAL PURPOSE I/O CIRCUITS

This is provided with 8-bit I/O usable for various kinds of input/output. As some pins are shared with other functions,

confirm each application before using it.

5

Page 6

4 DETAILED SPECIFICATIONS OF HARDWARE

4.1 ABSOLUTE MAXIMUM RATINGS

ITEM SYMBOL CONDITIONS RATINGS UNIT

Supply Voltage Vdd -0.5 to +6.5 V

I/O Voltage Vi/ Vo -0.5 to Vdd+0.5 V

Output Current Io Output current 9mA type 20 mA

Output Current Io Output current 13.5mA type 30 mA

Operating Temperature Topt -40 to +85 ºC

Storage Temperature Tstg -65 to +150 ºC

4.2 RECOMMENDED OPERATING RANGE

ITEM SYMBOL MIN. MAX. UNIT

Supply Voltage Vdd 4.5 5.5 V

Input Voltage Vi 0 Vdd V

Ambient Temperature Ta -40 +85 ºC

High Level Input Voltage Vih 0.7Vdd Vdd V

Low Level Input Voltage Vil 0 0.3Vdd V

Input Rise/ Fall Time tri, tfi 0 200 ns

Current Consumption Icc - 30 mA

4.3 DIRECT CURRENT CHARACTERISTIC

(Unless otherwise specified, Vdd=5V r10%, Ta=-40㨪+85ºC)

ITEM SYMBOL CONDITION MIN TYP. MAX UNIT

Static Current Consumption

Static Current Consumption

Off-State Output Current

Input Clamp Voltage

Output Short-Circuit Current

Input Leakage Current Ii Vi=GND Note 3 -45 -131 -320

Low Level Output Current

(CMOS) Note 1

Low Level Output Voltage Vol Iol=0mA 0.1 V

High Level Output Voltage Voh Ioh=0ma(CMOS) Note 1 Vdd-0.1 V

Idds

Idds

Ioz

Vic

Ios

Iol Vol=0.4V Note 4

Vi=Vdd

Vi=GND

Vo=VddorGND

Ii=18mA

V0=0V Note 2

Vol=0.4V Note 5

9.0

13.5

0.1 200

26440

10

-1.2

-250

PA

PA

PA

V

mA

PA

mA

mA

6

Page 7

SWITCHING CHARACTERISTICS (Unless otherwise specified, Vdd=5V r10%, Ta=-40㨪+85 ºC)

ITEM SYMBOL CONDITION MIN TYP. MAX UNIT

Toggle Frequency ftog Internal togle F/F (F/O=2) 120 MHz

Internal gate

F/O=1, Wiring length 0mm

Transfer Delay Time

INPUT/ OUTPUT PIN CAPACITY (Unless otherwise specified, Vdd=Vi=0V, Ta=+25ºC)

ITEM SYMBOL CONDITION MIN TYP. MAX UNIT

Input Terminal Cin f=1MHz 10 20 pF

Output Terminal Cout 0V for those other than measured pins 10 20 pF

I/O Terminal Ci/o 10 20 pF

Note 1: CMOS level output buffer (Vdd=5Vr10%, Ta=-40㨪+85 ºC)

Note 2: Output short-circuit current is available only in 1 pin of LSI for 1 second or less.

Note 3: Provided with pull-up resistance (50K ǡ)

Note 4: CMOS level output buffer (9.0mA type)

Note 5: CMOS level output buffer (13.5 mA type)

* A code indicates direction, where the one into which current flows is "positive."

tpd

F/O=2, Wiring length 2mm

Internal gate (power gate)

F/O= 2, Wiring length 2mm 0.40 ns

Input buffer

F/O =2, Wiring length 2mm 1.00 ns

0.27

0.50

ns

ns

7

Page 8

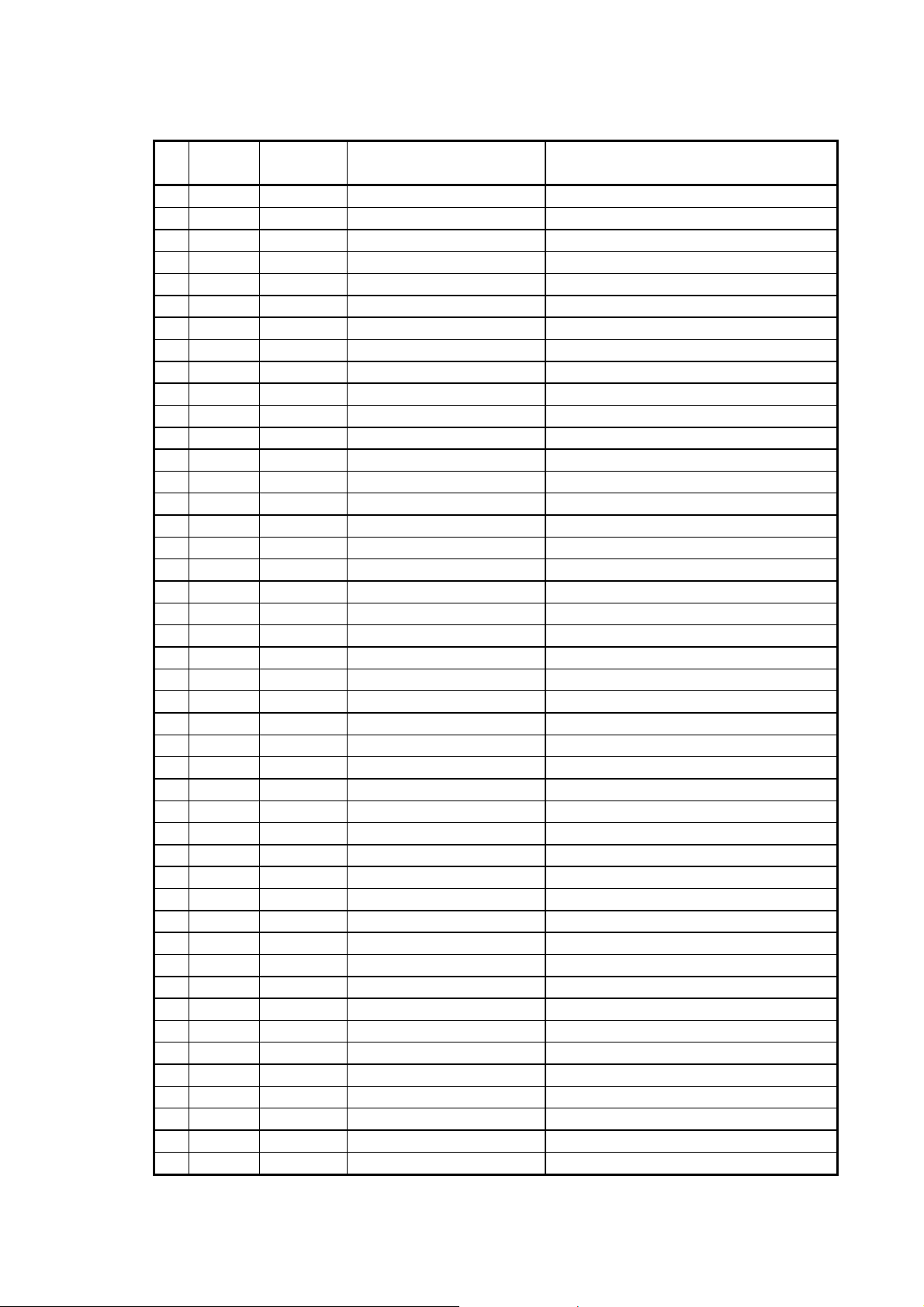

4.4 TERMINALS AND THEIR FUNCTIONS

PIN

NO.

SIGNAL

NAME

I/O

DIRECTION

PIN CHARACTERISTIC FUNCTION

1 GND - GND

2 RAMOE Output CMOS9mA type with pull-up OE/RFSH pin of PS-RAM

3 DRQ Output CMOS9mA type with pull-up DMA request

4 HVC Output CMOS9mA type Head voltage control

5 HRCHK Output CMOS9mA type Changeover of Head cut-off detect voltage

6 HODATA Input CMOS type with pull-up Input of preceding data

7 EHCLK Output CMOS13.5mA type with pull-up Head clock output

8 EHDATA Output CMOS13.5mA type with pull-up Head data output

9 STB1 Output CMOS 13.5mA type Head strobe signal

10 STB2 Output CMOS13.5mA type Head strobe signal

11 STB3 Output CMOS13.5mA type Head strobe signal

12 Vdd - Vdd

13 STBLOG Input CMOS type with pull-up Head strobe signal logic

14 PART2 Input CMOS type with pull-up 2/3 split drive changeover

15 GND - GND

16 GND - GND

17 D0 I/O CMOS type with pull-up Data bus

18 D1 I/O CMOS type with pull-up Data bus

19 D2 I/O CMOS type with pull-up Data bus

20 D3 I/O CMOS type with pull-up Data bus

21 D4 I/O CMOS type with pull-up Data bus

22 D5 I/O CMOS type with pull-up Data bus

23 D6 I/O CMOS type with pull-up Data bus

24 D7 I/O CMOS type with pull-up Data bus

25 Vdd - VDD

26 PA17 Input CMOS type with pull-up Preset SW input

27 PA16 Input CMOS type with pull-up Preset SW input

28 PA15 Input CMOS type with pull-up Preset SW input

29 PA14 Input CMOS type with pull-up Preset SW input

30 PA13 Input CMOS type with pull-up Preset SW input

31 PA12 Input CMOS type with pull-up Preset SW input

32 PAI1 Input CMOS type with pull-up Preset SW input

33 PAI0 Input CMOS type with pull-up Preset SW input

34 PB17 Input CMOS type with pull-up Preset SW input

35 PBI6 Input CMOS type with pull-up Preset SW input

36 PBI5 Input CMOS type with pull-up Preset SW input

37 PB14 Input CMOS type with pull-up Preset SW input

38 PB13 Input CMOS type with pull-up Preset SW input

39 PBI2 Input CMOS type with pull-up Preset SW input

40 GND - GND

41 Vdd - VDD

42 PBI1 Input CMOS type with pull-up Preset SW input

43 PBI0 Input CMOS type with pull-up Preset SW input

44 PC17 Input CMOS type with pull-up Preset & Centro-data input

45 PC16 Input CMOS type with pull-up Preset & Centro-data input

8

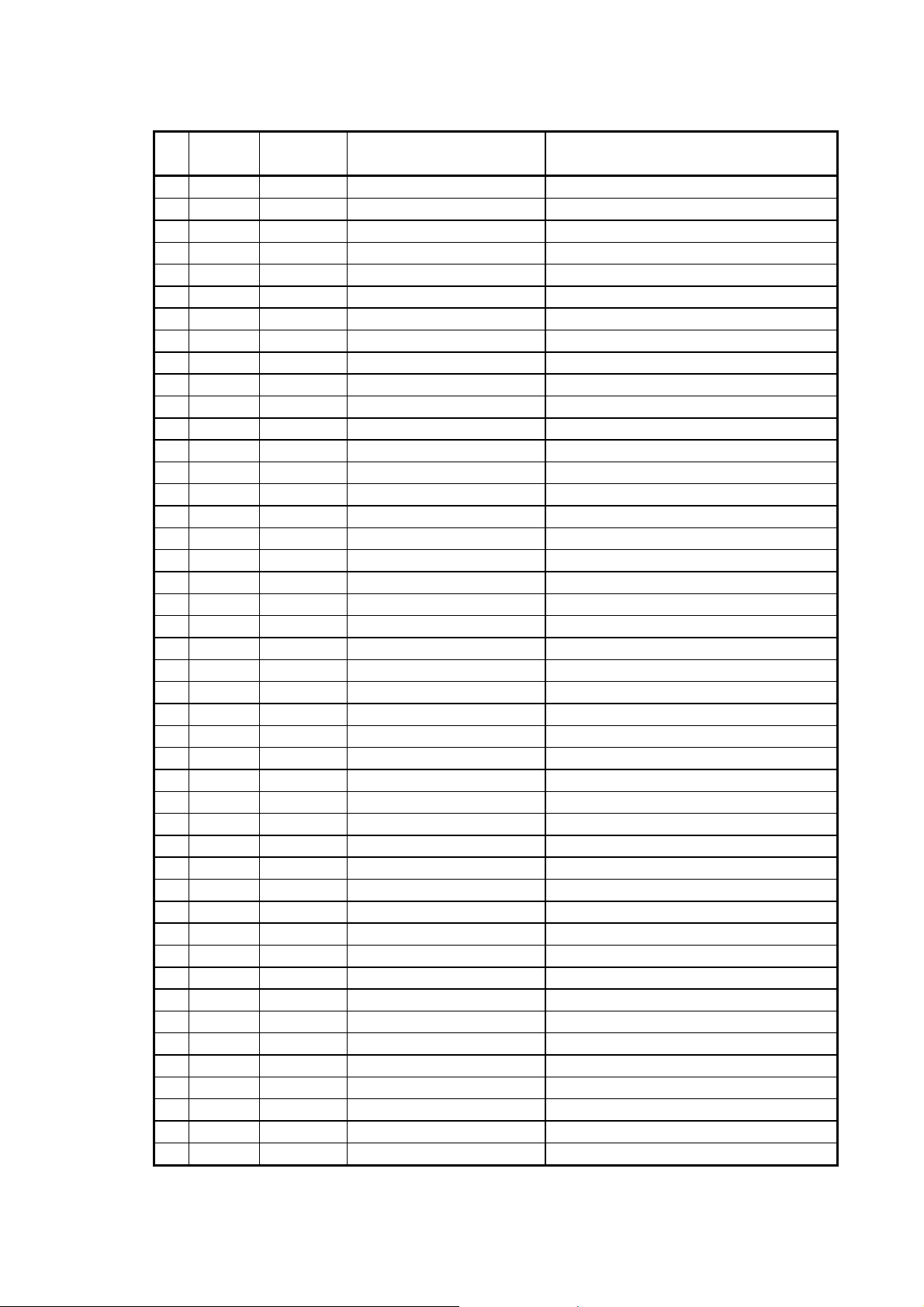

Page 9

PIN

NO.

SIGNAL

NAME

I/O

DIRECTION

PIN CHARACTERISTIC FUNCTION

46 PC15 Input CMOS type with pull-up Preset & Centro-data input

47 PC14 Input CMOS type with pull-up Preset & Centro-data input

48 PC13 Input CMOS type with pull-up Preset & Centro-data input

49 PC12 Input CMOS type with pull-up Preset & Centro-data input

50 PCI1 Input CMOS type with pull-up Preset & Centro-data input

51 PCI0 Input CMOS type with pull-up Preset & Centro-data input

52 STB Input CMOS type with pull-up Head strobe ON signal

53 ASTB Input CMOS type with pull-up Address latch signal

54 GND - GND

55 BUSY Output CMOS13.5mA type with pull-up Centro BUSY output

56 INTR Output CMOS13.5mA type with pull-up Centro interrupt request

57 ACK Output CMOS13.5mA type with pull-up Centro ACK output

58 PA07 Output CMOS13.5mA type with pull-up Address latch output & general purpose output

59 PA06 Output CMOS13.5mA type with pull-up Address latch output & general purpose output

60 Vdd - VDD

61 PA05 Output CMOS13.5mA type with pull-up Address latch output & general purpose output

62 PA04 Output CMOS13.5mA type with pull-up Address latch output &general purpose output

63 PA03 Output CMOS13.5mA type with pull-up Address latch output &general purpose output

64 PA02 Output CMOS13.5mA type with pull-up Address latch output &general purpose output

65 PA01 Output CMOS13.5mA type with pull-up Address latch output &general purpose output

66 GND - GND

67 PA00 Output CMOS13.5mA type with pull-up Address latch output &general purpose output

68

69

70

71

72

73

74

75

76

77

78

79

80 GND - GND

81 A14 Input CMOS type with pull-up Address bus input

82 A13 Input CMOS type with pull-up Address bus input

83 A12 Input CMOS type with pull-up Address bus input

84 A11 Input CMOS type with pull-up Address bus input

85 A6 Input CMOS type with pull-up Address bus input

86 A5 Input CMOS type with pull-up Address bus input

87 A3 Input CMOS type with pull-up Address bus input

88 A2 Input CMOS type with pull-up Address bus input

89 A1 Input CMOS type with pull-up Address bus input

90 GND - GND

9

Page 10

PIN

SIGNAL

NO.

NAME

91 Vdd - VDD

92 A0 Input CMOS type with pull-up Address bus input

93 CLK16M Input CMOS type with pull-up 16MHz clock input

94 RES Input CMOS type with pull-up Reset input

95 RES0 Input CMOS type with pull-up Reset input (watchdog)

96 CS0 Input CMOS type with pull-up ROM chip select

97 CS1 Input CMOS type with pull-up Gate array chip select

98 HWR Input CMOS type with pull-up Write signal

99 RD Input CMOS type with pull-up Read signal

100 RFSH Input CMOS type with pull-up Refresh cycle input

4.5 POWER TERMINAL

NO SYMBOL CONNECTION

1 GND Connected to GND.

12 Vdd Connected to +5V.

15 GND Connected to GND.

16 GND Connected to GND.

25 Vdd Connected to +5V.

40 GND Connected to GND.

41 Vdd Connected to +5V.

54 GND Connected to GND.

60 Vdd Connected to +5V.

66 GND Connected to GND.

80 GND Connected to GND.

90 GND Connected to GND.

91 Vdd Connected to +5V.

I/O

DIRECTION

PIN CHARACTERISTIC FUNCTION

10

Page 11

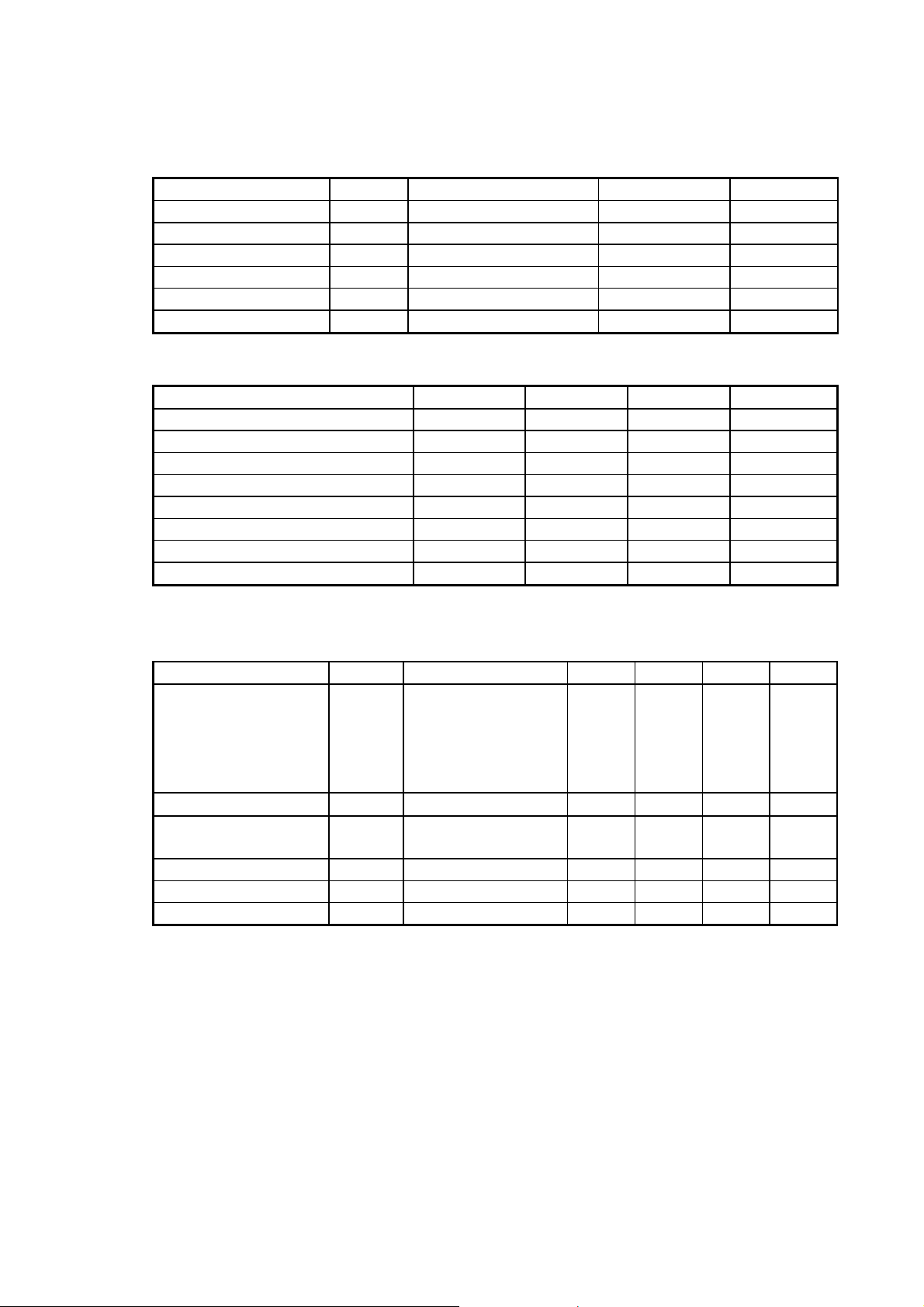

4.6 INTERNAL ADDRESS MAP

A3 A2 A1 A0 RD HWR CS1 OPERATION AND APPLICABLE PORT

0000010Prohibited

0000100Print data buffer

0001010Prohibited

0001100DMA request

0010010PAI port input

0010100PA0 port output & address latch output

0011010PBI port input

0011100Prohibited

0100010PCI port input & Centro-data input

0100100PC0 port output (PBUSY)

0101010180° turning output

0101100Bit data buffer for processing

0110010Double width lower 8-bit output

0110100

0111010Double width upper 8-bit output

0111100Head control mode register

1 X X X 0 1 0 90 °turning output

1 X X X 1 0 0 90 °turning data buffer

X X X X X X 1 Data bus high impedance

X X X X 1 1 0 Data bus high impedance

X mark indicates either "0" or "1".

Ports other than those listed above are subject to independent operation.

11

Page 12

4.7 PRINT DATA TRANSFER METHOD

When printing is performed with Line Thermal Head at high speed, it is necessary for you either to control printing

speed so that heat from printing of the preceding stage does not give any influence or to perform stored heat correction

so that remaining heat is eliminated. This gate array is provided with a circuit which holds printing energy at low

level to attain high-quality printing when power is supplied for the main stage printing to the dot which has been

subject to power supply also in the preceding stage.

Power supply to Line Thermal Head included pre-pulse and main pulse. To those dots to which power has not been

supplied in the preceding stage, "pre-pulse + main pulse" is supplied. To those dots to which power has been

supplied in the preceding stage, main pulse alone is supplied. Head Control Mode Registers for switching main pulse

and pre-pulse, etc. are assigned in Address XX07h.

Assignment of Head Control Mode Register in each bit is as follows:

Data transfer to Thermal Head is performed as follows:

1. Print data for 1 dot line or multiple dot lines are developed in memory beforehand.

2. HOS1/ HOS0 of Head Control Mode Registers are set to "0, 1" to assign pre-pulse.

3. DMA request is given.

With "#OFFh" being written in Address XX01h, one-shot from DRQ pin is output. DRQ signal is a request of

1-byte DMA transfer.

4. Print data developed beforehand from CPU are transferred to print data buffer (Address XX00h) by data bus.

5. They are subject to parallel/ serial conversion inside the gate array and are transferred to Head in 1-byte serial.

(Transferred in 4MHz clock rate)

6. With data received and transfer started, Request signal (DRQ) of next data is given. Next data are written in the

print data buffer.

7. On completion of data transfer of 1 dot line, data are latched to Head and strobe control starts. (Pre-pulse

supply)

8. During pre-pulse supply, print data for main pulse are transferred. The transfer method is the same as that for

pre-pulse, except that Head Control Registers HOS1/ HOS0 are set to "0, 0" and main pulse is assigned for

transfer.

9. On completion of transfer and pre-pulse supply, print data are latched to Head before main pulse supply.

10. On start of printing or on printing where line feed, etc. has eliminated influence of printing of the preceding stage,

pre-pulse and main pulse are supplied under main pulse assignment.

Note) On supply of power, to clear, once, the gate array internal buffer, write "00h" into the print data buffer with Head

Control Mode Register SAbit being held at "0".

12

Page 13

Data transfer sequence is shown as follows:

The following procedures are needed for printing operation:

1. Turning on HVC port pin, supply Vp voltage to Head.

2. Supply Vm voltage to the paper feed motor of Printer Mechanism and enter Start Hold.

3. While in Start Hold, transfer, to Head, print data of the 1st dot line.

4. On completion of transfer, latch the print data to Head.

5. Following Start Hold period, supply pre-pulse. (Current is supplied when STB bit of Head Control Mode Register

is set to "1".)

6. On completion of pre-pulse supply, perform main pulse supply.

7. While in main pulse supply, transfer, to Head, print data to the 2nd dot line. (Pre-pulse data of the 2nd dot line)

8. On termination of main pulse supply time and, also, when paper feed has been completed, perform pre-pulse

supply for the 2nd dot line.

9. While in pre-pulse supply, transfer print data one more time to Head for main pulse.

10. While in main pulse supply, transfer print data to the next dot line.

11. On termination of main pulse supply and, also, when paper feed has been completed, perform pre-pulse supply

for the next dot line.

12. When print data continue, repeat 9㨪11.

13. On completion of the next line printing, provide the paper feed motor with Stop Hold time. On termination of

that time, Head voltage and motor voltage are turned off for operation end.

Note) Set STBLOG (Pin 13) to suit to Thermal Head.

STBLOG: Strobe Signal Logic Switching Pin

"L" : positive logic output "H" : negative logic output

STB1 㨪3 : Strobe Split Output Pin

Connect, to STB pin of Thermal Head, STB 1 and 2 on 2-splitting and STB 1, 2, and 3 on 3-splitting.

PART2 : 2/3 Split Drive Switching Pin

"L" : 3-split drive "H" : 2-split drive

13

Page 14

The whole sequence is shown as follows:

4.8 RESET CIRCUIT

With RES pin (No 94 pin) set to "Low" level, STB 1㨪3 (No's 9 㨪11 pins) are made in high impedance state cutting

off current supply to Thermal Head. Perform pull-up or pull-down according to Thermal Head. Further, with a

watchdog timer output (CPU, etc.) connected to RESO pin (No 95 pin), checking is performed on every ROM access

time, thus protecting Thermal Head.

For other output pins, those with pull-up are made "High", while those without are made high impedance. Refer to

the above mentioned "Terminals and Their Functions."

Recommended Reset IC: SEIKO Electronic Co., Ltd. S-804HNM

The gate array, when Reset pin (Pin 94) is held at "low" level for 1 Ps or more and returned to "high" level under

supply voltage of 5V r5%, is reset released and initialized.

14

Page 15

4.9 SYSTEM CLOCK CIRCUIT

In order to acquire speed to transfer data to Head, input 16MHz clock in CLK16M pin (Pin 93.) Divide this clock

internally into four to create 4MHz, which is used as the basic clock for data transfer. As this clock serves as the

basic clock for data transfer, clock frequency which can assure enough pre-pulse /main pulse data transfer for the

printing period is needed.

4.10 HEAD VOLTAGE INTERRUPTING CIRCUIT

HVC pin (No. 4 pin) is used to prevent, by not applying Vh voltage to Head unless Thermal Head is in use, erroneous

printing (on resetting, etc.) and electrolytic etching. This is also used on detection of Head break-off as described in the

next section. Without use of this pin, Head Break-Off Detecting Circuit can neither be used.

For printing, after print data are transferred to Head, Head voltage is applied to Head through use of this pin. On

completion of printing, Head voltage is interrupted to be made in standby state.

On detection of Head break-off, it is held interrupted so that Head voltage (Vh) is not applied to Thermal Head.

HVC pin and HVC bit of Head Control Mode Register are synchronized. With Head Control Mode Register bit being

set and cleared, the pin also changes syncronized.

4.11 HEAD BREAK-OFF DETECTING CIRCUIT

HRCHK pin (No 5pin) is used for measurement of Thermal Head resistance value. With this pin being used while

Vh voltage of Thermal Head is held

interrupted by the above Head Voltage Interrupting Circuit, Vdd is applied to Thermal Head. In measurement,

voltage is read where Vdd voltage has been divided into Head resistance value and the reference fixed resistance.

Measurement is conducted by one time on supply of power and the detecting circuit is held in OFF afterwards.

HRCHK pin and HRCHK bit of Head Control Mode Register are synchronized. With Head Control Mode Register bit

being set and cleared, the pin changes being alos synchronized.

Measuring Procedures:

1. Thermal Had buffer is cleared according to the print data transfer procedures. ("00h" is written in by 1-dot

line.)

2. Set Head voltage Vp to off by using HVC pin.

3. Supply, by HRCHK pin, Vdd voltage to Thermal Head.

4. Writing 01h by 1 byte to Thermal Head, set the data so that only the dot among all the other dots is printed.

5. Latch print data to Head by LATCH signal.

6. Supply STB to Thermal Head. (Control, at this time, current supply time so that Head does not actually print

on paper.)

7. Calculating resistance value of the heating element by using the partial pressure rate of the heating element

resistance value and the reference resistance value of Head, see if there is any "drift."

8. Then, by performing one-shot output in HRCLK (bit 3) of Head Control Mode Register, shift the print data by

one dot.

9. Supplying current again to Head, carry out measurement of heating element resistance value.

10. By repeating the above by the number of heating elements, you can inspect all the dots.

15

Page 16

4.12 PARALLEL INPUT CIRCUIT

This port is used as being shared by PCI (0㨪7), 8-bit parallel general purpose input. STB input, ACK output and

BUSY output are used as independent ports.

When STB input is made "low", PCI port data are latched. Also, at the same time, BUSY output is made "high".

With STB input returned to "high", INTR pin gets "low" and latching of data in the input port is notified to CPU. It

can be used as the data reading request signal. BUSY and INTR are reset in the timing with which CPU reads PCI

port data, where, at the same time, ACK signal is also output.

When you do not use this function, keep STB pin in "low". Then, it can be used as a general purpose 8-bit input port

(PCI).

MIN MAX UNIT

T1 100 - ns

T2 100 - ns

T3 100 - ns

T4 - 80 ns

T5 - 80 ns

T6 - 80 ns

BUSY output is available in timings other than those listed above. With data written in PCO7 (bit 7 of XX04h

address) port, BUSY output is available.

For other outputs, use other ports.

4.13 ADDRESS LATCH CIRCUIT

This port is used as shared by the 8-bit parallel type of general purpose output PAO (0 㨪7). This is applicable to CPU which

uses address bus and data bus by multiplexing.

Perform address latching at the fall edge where ASTB input is made "low". When you do not use this function, keep ASTB pin at

"low". Then, it can be used as a general purpose 8-bit output port (PAO).

16

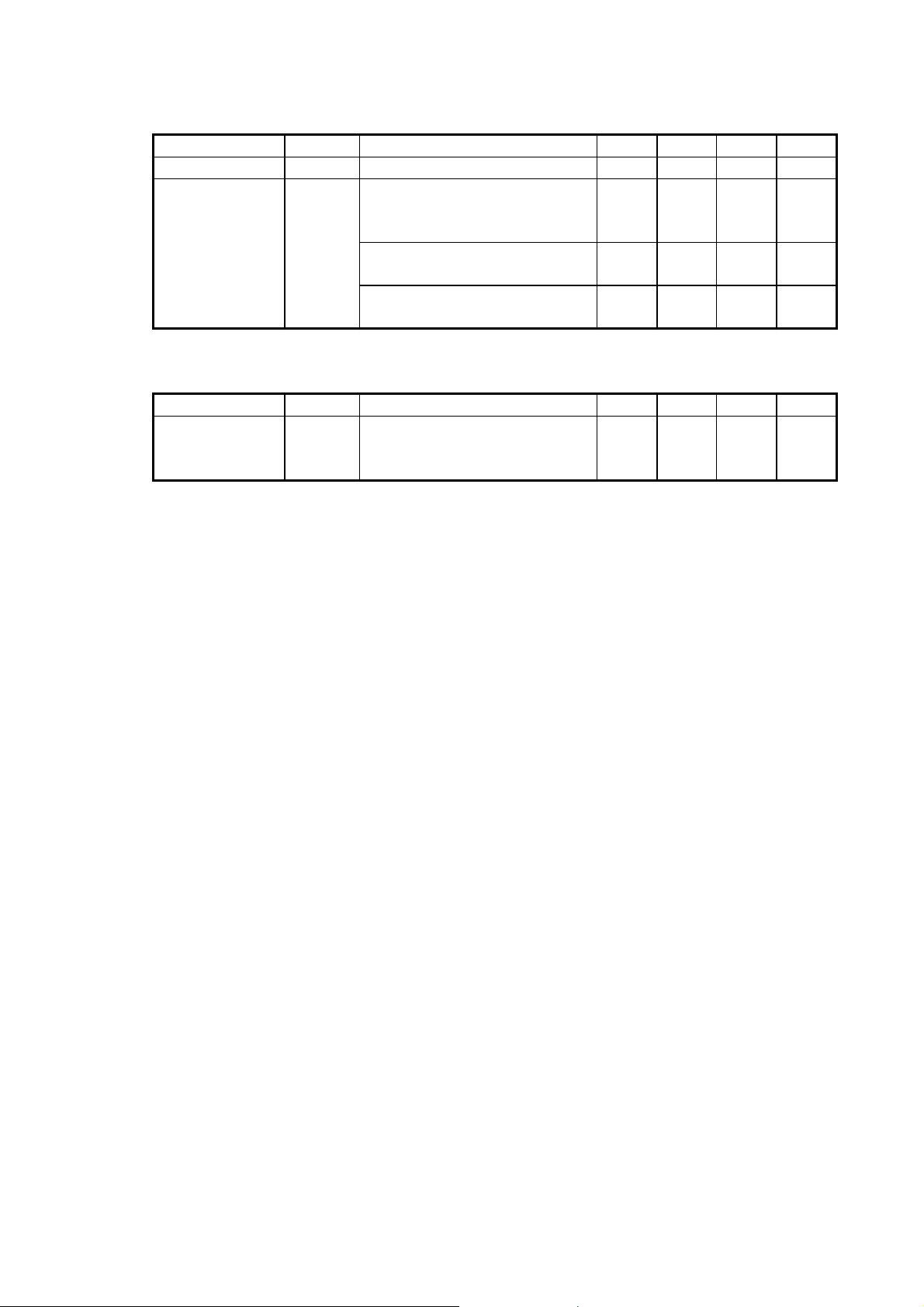

Page 17

MIN MAX UNIT

T1 80 ns

T2 80 ns

T3 80 ns

4.14 GENERAL PURPOSE I/O OUTPUT CIRCUIT

Besides the PAO ports and PCI ports mentioned above, there are some other ports available.

PORT NAME I/O INCIDENTAL CONDITIONS ADDRESS

PAO Output ASTB pin at "Low". XX02h

PCO Output Bit 7 held at PBUSY. Others are unused. XX04h

PAI Input None XX02h

PBI Input None XX03h

PCI Input STB pin at "Low". XX04h

4.15 BIT DATA PROCESSING METHOD

This gate array is equipped with a data processing circuit which faciliates processing of bit data when print data are

developed in memory.

a.) 180° turning circuit (MSB/ LSB switching)

b.) Double character conversion circuit (8 bit → 16 bits conversion)

c.) 90° turning circuit (8 bits x 8 bits turned by 90°.)

The 180° turning circuit and the double character conversion circuit perform data processing in 1 byte unit, while the

90° turning circuit performs it in 8 bytes unit. The methods are shown as follows:

a) 180° Turning Circuit

1. Write, into the XX05h processing bit data buffer, the bit data for which turning is to be performed.

2. With data being read out from output of 180° turned XX05h address, data which have been turned by 180° are

obtained. (Address being the same.)

D7 D6 D5 D4 D3 D2 D1 D0 Data prior to turning

p

D0 D1 D2 D3 D4 D5 D6 D7 Data after turning

b) Double Character Conversion Circuit

1. Write the bit data to be doubled into the bit data buffer for processing of Address XX05h.

2. With data being read out from the lateral double lower 8-bit output and the lateral double upper 8-bit output of

Addresses XX06h and XX07h, data having been processed in 16 bits are obtained.

D7 D6 D5 D4 D3 D2 D1 D0

p

D7 D7 D6 D6 D5 D5 D4 D4 D3 D3 D2 D2 D1 D1 D0 D0

XX07h(upper) XX06h (lower)

17

Page 18

c) 90° Turning Circuit

In the vertical columns, 8 bits

1. Write, in the 90° turning data buffer which extends from Address XX08h to XX0Fh, the data to be turned.

2. In the same way, with XX08h㨪XX0Fh being read, data which have been turned by 90° can be obtained. This is

highly convenient as both rightward and leftward turning is freely available by the writing and reading order.

D07 D17 D27 D37 D47 D57 D67 D77

D06 D16 D26 D36 D46 D56 D66 D76

D05 D15 D25 D35 D45 D55 D65 D75

D04 D14 D24 D34 D44 D54 D64 D74

D03 D13 D23 D33 D43 D53 D63 D73

D02 D12 D22 D32 D42 D52 D62 D72

D01 D11 D21 D31 D41 D51 D61 D71

D00 D10 D20 D30 D40 D50 D60 D70

08h 09h 0Ah 0Bh 0Ch 0Dh 0Eh 0Fh

D07 D17 D27 D37 D47 D57 D67 D77 08h

D06 D16 D26 D36 D46 D56 D66 D76 09h

D05 D15 D25 D35 D45 D55 D65 D75 0Ah

Writing:

are written by 8 byte.

Reading:

In the horizontal columns, 8 bits In the

horizontal columns, 8 bits

D04 D14 D24 D34 D44 D54 D64 D74 0Bh

D03 D13 D23 D33 D43 D53 D63 D73 0Ch

D02 D12 D22 D32 D42 D52 D62 D72 0Dh

D01 D11 D23 D31 D41 D51 D61 D71 0Eh

D00 D10 D22 D30 D40 D50 D60 D70 0Fh

When writing starts with 08h toward 0Fh and reading also with 08h toward 0Fh, leftward turning is produced. On the

other hand, when writing starts with 0Fh and ends with 08h and reading also starts with 0Fh and ends with 08h,

rightward turning is produced.

18

Page 19

4.16 PSEUDO-SRAM CONNECTING METHOD

In the system consisted of the CPU and gate array, S-RAM may be used as the work area as the print data buffer, bit

data development, etc.. This gate array supports Self-Refresh so that a pseudo-SRAM can be easily connected.

Use the PS-RAM which integrates OE and RFSH pins into one.

4.17 OTHER CONTROL TERMINALS

As for functions of control pins of this gate array, refer to the

following table:

SIGNAL NAME PIN NO FUNCTION

RES 94 Connects system reset. When being set to low level, this is reset.

RESO 95 Connects watchdog timer output. When being set to low level, this is reset.When in high

level, reset is canceled with rising of CS0.

CS0 96 Connects Chip Select signal of the watchdog timer. To output from CPU, connect Chip

Select signal of System ROM.

CS1 97 Chip Select When set to low level, transfers and controls data between the gate array and

CPU.

HWR 98 Write Control When set to low level, data are written through data bus.

RD 99 Read Control When set to low level, data are read through data bus.

19

Page 20

5 OPERATION TIMING

Operation timings immediately following initialization are shown below:

20

Page 21

6 PACKAGE SPECIFICATION

6.1 SHAPE AND DIMENSIONS

OUTLINE DRAWING

Material

Main body: epoxy type resin / satin finish for marking face

Lead: iron/ nickel alloy/ solder plating

21

Page 22

6.2 MOUNT PAD DIMENSIONS

NO OF PINS PER SIDE PIN PITCH PAD WIDTH PAD LENGTH FITTING WIDTH

ED e b2 12MieMid

20 30 0.65 0.35 1.9 14.6 20.6

UNIT: mm

22

Page 23

7 REFERENTIAL CIRCUIT DIAGRAM

23

Page 24

24

Page 25

8 REMARKS FOR MOUNTING

8.1 TEMPERATURE CONDITIONS FOR MOUNTING

x Infrared Reflow System

Recommended Conditions

Peak temperature : 230ºC and less (package surface temp.)

Time : Within 30 seconds (at 210ºC or above)

No of times : 1

Flux : Rosin type flux with less chlorine content(chlorine 0.2Wt% or less)

x VPS Reflow System

x Wave Soldering System

Recommended Conditions

Peak temperature : 215ºC and less (boiling temp. of solvent)

Time : 25㨪40 seconds (at 200ºC or above)

No of times : 1

Flux : Rosin type flux with less chlorine content(chlorine 0.2Wt% or less)

Recommended Conditions

Temperature : 260 ºC (fused solder temp.)

Time : within 10 seconds

Preheating temperature : 120ºC or less (package surface temp.)

No of times : 1

Flux : Rosin type flux with less chlorine content(chlorine 0.2Wt% or less)

25

Page 26

8.2 STORAGE CONDITIONS

Resin material of the plastic mold package absorbs moisture when exposed in a room. If the package being mounted

with moisture absorbed, therefore, it may adversely influence Device reliability (especially in its moisture resistance).

The products, therefore, are shipped in dry-pack for which aluminum laminated bags with desiccant placed inside.

For storage prior to mounting, pay attention to the following:

1. Handle with enough care so as not to apply excessive impact or to stab with a sharp edged item. The package may

be broken.

2. Store this, before opening, at 30ºC with humidity of 60% or below, and try to use this in as short a period as

possible.

3. After opening a bag, use this quickly. If you like to store this even temporarily after opening, be sure to put

desiccant, fold the opening, and seal it with tape, etc..

8.3 OTHERS

1. Pay attention so that no mechanical stress is applied to lead terminals, etc. of the package. It may result in

damage on the external lead terminal, disconnection of the internal lead, or deterioration in moisture resistance.

2. On soldering, try to keep thermal stress minimum.

3. Beware of static electricity which may destroy IC's. Provide the work place, workers, jigs and equipments with

appropriate preventive measures against static electricity.

26

Page 27

9 PACKING SPECIFICATIONS

Unit mm

Heat resistant conductive plastic

Applicable Package No Per Packing

100-pin plastic QFP 60

27

Page 28

1. Item Packaging Container

2. Item Packaging Box

APPLICABLE

PACKAGE

Label position Top or side face of box

Label content Product name, amount, lot No, stanards/category

ITEM PACKAGING CONTAINER ITEM PACKAGING BOX

NAME OF TRAY MAX.NO

LA-244A (heat resistant, lead holder)

/TRAY

u 60 205 u 60 u 360 u 300

DIMENSIONS

(mm) (WuHuL)

MAX.NO

/BOX

28

Loading...

Loading...