AVER AL4CS231A-10-PF, AL4CS231A-10-J, AL4CS221A-7.5-PF, AL4CS221A-7.5-J, AL4CS221A-10-PF Datasheet

...

AL4CS211

AL4CS221

AL4CS231

AL4CS241

AL4CS251

Data Sheets

Version 1.1

|

|

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

|

Amendments |

|

|

|

07.11.01 |

Preliminary Version 1.0 |

|

|

10.17.01 |

Version 1.1, Added DC and AC timing data |

|

|

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

December 14, 2001 |

2 |

|

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251

AL4CS211/AL4CS221/AL4CS231/AL4CS241/

AL4CS251 (512 x9, 1k x9, 2k x9, 4k x9, 8k x9)

Synchronous FIFO

Contents:

1.0 Description ________________________________________________________________ 4

2.0 Features___________________________________________________________________ 4

3.0 Applications________________________________________________________________ 4

4.0Chip Information ___________________________________________________________ 5

4.1Marking Information _____________________________________________________________ 5

4.1Ordering Information _____________________________________________________________ 5

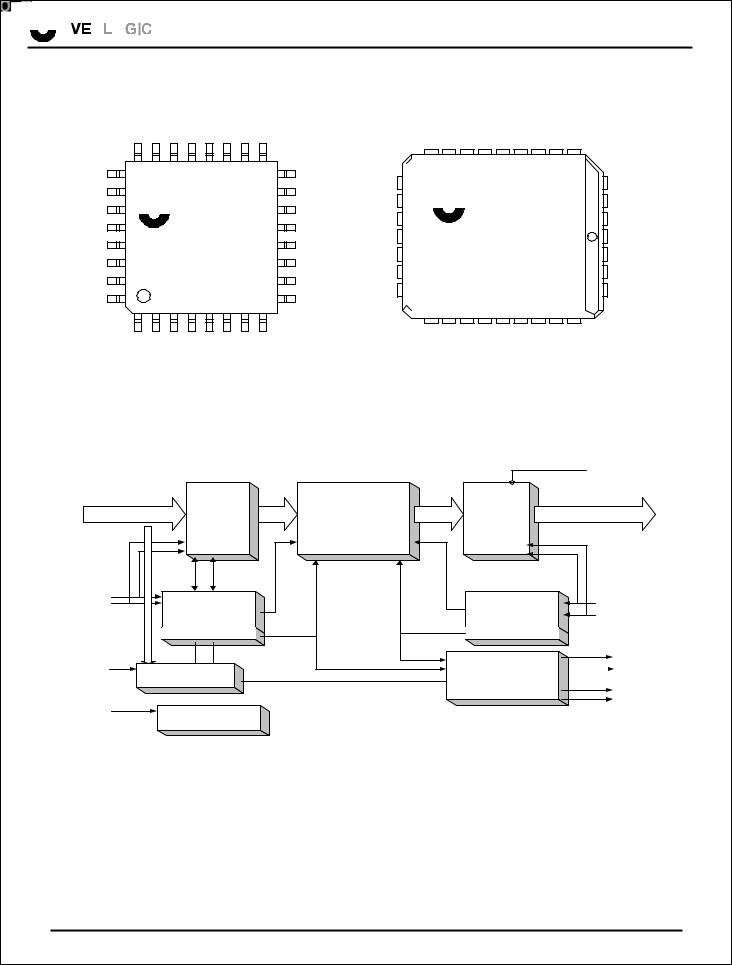

5.0 Pin-out Diagram ____________________________________________________________ 6

6.0 Block Diagram _____________________________________________________________ 6

7.0 Pin Definition and Description ________________________________________________ 7

8.0Memory Operations _________________________________________________________ 8

8.1Inputs and Outputs _______________________________________________________________ 8

8.2Controls ________________________________________________________________________ 9

8.3Flags__________________________________________________________________________ 11

9.0Multiple Devices Bus Expansion and Cascading _________________________________ 12

9.1Width Expansion Configuration ___________________________________________________ 12

9.2Depth Expansion ________________________________________________________________ 12

10.0Electrical Characteristics ___________________________________________________ 14

10.1Absolute Maximum Ratings ______________________________________________________ 14

10.2Recommended Operating Conditions ______________________________________________ 14

10.3DC Characteristics _____________________________________________________________ 14

10.4AC Electrical Characteristics_____________________________________________________ 15

10.5Timing Diagrams_______________________________________________________________ 16

11.0Mechanical Drawing ______________________________________________________ 23

11.17x7mm 32-pin TQFP Package ____________________________________________________ 23

11.232-pin PLCC Package___________________________________________________________ 24

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

December 14, 2001 |

3 |

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251

1.0 Description

The AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 series memory products are highperformance, low-power 9-bit read/write FIFO (First-In-First-Out) memory chips. They are specially designed to buffer high speed streaming data for a wide range of communication applications, such as optical disk controllers, Local Area Networks (LANs), SONET (Synchronous Optical Network).

The input data is synchronous with a free-running clock (WCLK), and input-enable pins (/WEN1, /WEN2). Data is written into the FIFO on every clock when enable pins are asserted. The output is synchronous with the other free-running clock (RCLK) and enables (/REN1, /REN2). An Output Enable pin (/OE) is provided at the read port for tri-state control of the output port. The FIFOs can output two fixed flags, Empty Flag( /EF) and Full Flag (/FF), and two programmable flags, AlmostEmpty (/PAE) and Almost-Full (/PAF). The offsets of the /PAE and /PAF flags are loaded when Load pin (/LD) goes low.

2.0 Features

∙512 x9-bit cell array (AL4CS211)

∙1,024 x9-bit cell array (AL4CS221)

∙2,048 x9-bit cell array (AL4CS231)

∙4,096 x9-bit cell array (AL4CS241)

∙8,192 x9-bit cell array (AL4CS251)

∙100/133 MHz Operation

∙10/7.5 ns read/write cycle time

∙Independent Read and Write operations

∙Empty and Full flags support

∙Programmable Almost-Empty and Almost-Full flags

∙Output enable (data skipping)

∙3.3V power supply with 5V tolerant

∙Available in a 32-pin Thin Quad Flat Pack (TQFP) and 32-pin plastic leaded chip carrier (PLCC) packages

3.0 Applications

∙Routers

∙ATM switches

∙Cable modems

∙Wireless base stations

∙SONET(Synchronous Optical Network) multiplexers

∙Multimedia systems

∙Time base correction (TBC)

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

December 14, 2001 |

4 |

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251

4.0Chip Information

4.1Marking Information

AL4CS2X1

Part Number: X = 1, 2, 3, 4, 5 as

AL4CS211, AL4CS221, AL4CS231,

AL4CS241, AL4CS251

X-XX-XX

Package: XX =

J: PLCC

PF: TQFP

Speed Grade: XX = -10, -7.5, ..

Version Number: X = A, B, C..

XXXXX

Lot Number

XXXX

Date Code

4.1 Ordering Information

The ordering information for AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 are:

Part number |

Package |

Power Supply |

Status |

|

|

|

|

AL4CS211/221/231/241/251(A-10-PF) |

32-pin plastic |

+3.3V±10% |

Sample in Aug., 2001 |

|

TQFP(7x7mm) |

|

|

|

|

|

|

AL4CS211/221/231/241/251(A-7.5-PF) |

32-pin plastic |

+3.3V±10% |

Sample in Aug., 2001 |

|

TQFP(7x7mm) |

|

|

|

|

|

|

AL4CS211/221/231/241/251(A-10-J) |

32-pin plastic |

+3.3V±10% |

Sample in Aug., 2001 |

|

PLCC |

|

|

|

|

|

|

AL4CS211/221/231/241/251(A-7.5-J) |

32-pin plastic |

+3.3V±10% |

Sample in Aug., 2001 |

|

PLCC |

|

|

|

|

|

|

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

December 14, 2001 |

5 |

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251

5.0 Pin-out Diagram

The AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 pin-out diagram is following:

|

|

|

/WEN1 |

|

WCLK |

WEN2</LD> |

VCC |

Q8 |

Q7 |

Q6 |

Q5 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

/RS |

|

24 |

23 |

|

22 |

|

21 |

|

20 |

|

19 |

|

18 |

|

|

17 |

||

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D8 |

|

26 |

|

|

|

|

AVERLOGIC |

|

||||||||||

|

|

|

|

|

||||||||||||||

D7 |

|

27 |

|

|

|

|

|

|||||||||||

|

|

|

|

|

||||||||||||||

D6 |

|

28 |

|

|

|

|

|

|||||||||||

|

|

|

|

|

AL4CS2X1 |

|

||||||||||||

|

|

|

|

|

|

|

|

|||||||||||

D5 |

|

29 |

|

|

|

|

x-xx-xx |

|

||||||||||

|

|

|

|

|

|

|||||||||||||

D4 |

|

30 |

|

|

|

|

xxxx |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||

D3 |

|

31 |

|

|

|

|

xxxx |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||

D2 |

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

1 |

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

|

8 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

D0 |

/PAF |

/PAE |

GND |

/REN1 |

RCLK |

/REN2 |

|||||||

|

|

|

|

TQFP PACKAGE TOP VIEW |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

/OE |

|

/REN2 |

|

RCLK |

|

/REN1 |

|

GND |

/PAE |

|

/PAF |

D0 |

|

D1 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

16 |

|

Q4 |

|

|

|

13 |

12 |

11 |

10 |

9 |

|

8 |

7 |

|

6 |

5 |

|

|

|

|

D2 |

||||||||

|

/EF |

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

15 |

|

Q3 |

/FF |

|

|

15 |

|

|

|

|

AVERLOGIC |

3 |

|

|

D3 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

14 |

|

Q2 |

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

13 |

|

Q1 |

Q0 |

|

|

16 |

|

|

|

|

AL4CS2X1 |

2 |

|

|

D4 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

Q1 |

|

|

17 |

|

|

|

|

x-xx-xx |

|

1 |

|

|

|

D5 |

||||||||||||||

12 |

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

Q2 |

|

|

18 |

|

|

|

|

xxxx |

|

|

|

|

|

32 |

|

|

D6 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

11 |

|

/FF |

Q3 |

|

|

19 |

|

|

|

|

xxxx |

|

|

|

|

|

31 |

|

|

D7 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

10 |

|

/EF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

Q4 |

|

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

|

|

D8 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

9 |

|

/OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

21 |

22 |

23 |

24 |

25 |

|

26 |

27 |

|

28 |

29 |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q5 |

|

Q6 |

|

Q7 |

|

Q8 |

|

Vcc |

WEN2</LD> |

|

WCLK |

/WEN1 |

|

/RS |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

PLCC PACKAGE TOP VIEW |

|

|

|

|

|

|

|

|||||||||

6.0 Block Diagram

|

|

(512, 1k ,2k, |

Input data bus |

Input |

4k, 8k) x9 |

|

Buffer |

Memory |

|

|

Array |

WCLK |

|

|

Write Control |

|

|

/WEN1 |

Logic |

|

WEN2 |

|

|

|

|

|

Write Pointer |

|

|

/LD

Offset Regissers

/RS

Reset Logic

|

|

/OE |

Output |

Output data bus |

|

Buffer |

|

|

Read Control |

RCLK |

|

|

||

Logic |

|

/REN1 |

|

|

|

Read Pointer |

/REN2 |

|

|

|

/FF |

Flag Logic |

|

/EF |

|

||

|

|

/PAF

/PAE

Figure 1. AL4CS2x1 FIFO Block Diagram

The internal structure of the AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 consists of Input/Output buffers, Read/Write Control Logic and main (512, 1k, 2k, 4k, 8k) x9 different configuration memory cell array and state-of-the-art logic design that takes care of addressing and controlling the read/write data.

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

December 14, 2001 |

6 |

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251

7.0 Pin Definition and Description

The pin-out definition and function are described as following:

Write Bus Signals

Pin |

Pin name |

TQFP |

PLCC |

I/O |

Description |

Symbol |

|

Pin no. |

Pin no. |

Typ |

|

D[8:0] |

Data Inputs |

[26:32], 1, |

[30:32], |

I |

9-bit input data bus. |

|

|

2 |

[1:6] |

|

|

/WEN1 |

Write Enable |

24 |

28 |

I |

/WEN1 is the only Write Enable pin, if FIFO is |

|

|

|

|

|

configured to support programmable flags. |

|

|

|

|

|

When /WEN1 is LOW, data is written into the |

|

|

|

|

|

FIFO on every rising edge of WCLK. If the |

|

|

|

|

|

FIFO is configured to have two write enables, |

|

|

|

|

|

/WEN1 must be LOW and WEN2 must be |

|

|

|

|

|

HIGH to write data into the FIFO. When FIFO |

|

|

|

|

|

is full (/FF = LOW), data will not be written |

|

|

|

|

|

into FIFO. |

WEN2 |

Write Enable |

22 |

26 |

I |

The FIFO is configured at the Reset to either |

</LD> |

|

|

|

|

have two write enables or support |

|

|

|

|

|

programmable flags. If Write Enable 2<Load> |

|

|

|

|

|

(WEN2</LD>) is HIGH at Reset (/RS = |

|

|

|

|

|

LOW), this pin will operate as a second Write |

|

|

|

|

|

Enable pin. If Write Enable 2<Load> |

|

|

|

|

|

(WEN2</LD>) is LOW at Reset (/RS = LOW), |

|

|

|

|

|

the FIFO is configured to support |

|

|

|

|

|

programmable flags function and /WEN1 is the |

|

|

|

|

|

only Write Enable pin. |

WCLK |

Write Clock |

23 |

27 |

I |

Data is written into the FIFO on a rising edge of |

|

|

|

|

|

WCLK when the Write Enable(s) are asserted. |

|

|

|

|

|

Data will not be written into FIFO if /FF is not |

|

|

|

|

|

LOW. |

Read Bus Signals

|

Pin |

Pin name |

TQFP |

PLCC |

I/O |

Description |

|

|

symbol |

|

Pin no. |

Pin no. |

typ |

|

|

|

Q[8:0] |

Data Outputs |

[21:12] |

[24:16] |

O |

9-bit output data bus. |

|

|

|

|

|

|

|

|

|

|

/REN1 |

Read Enable |

6 |

10 |

I |

When both /REN1 and /REN2 are LOW, data is |

|

|

|

|

|

|

|

read from the FIFO on every rising edge of |

|

|

|

|

|

|

|

RCLK. Data will not be read from the FIFO if |

|

|

|

|

|

|

|

the /EF is LOW. |

|

|

|

|

|

|

|

|

|

|

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

|

December 14, 2001 7 |

||||

|

|

|

|

|

|

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

/REN2 |

Read Enable |

8 |

12 |

I |

When /REN1 and /REN2 are LOW, data is read |

||

|

|

|

|

|

|

|

from the FIFO on every rising edge of RCLK. |

|

|

|

|

|

|

|

|

Data will not be read from the FIFO if the /EF is |

|

|

|

|

|

|

|

|

LOW. |

|

|

/OE |

Output |

9 |

13 |

I |

When /OE is LOW, the data output bus is |

||

|

|

Enable |

|

|

|

active. If /OE is HIGH, the output data bus will |

||

|

|

|

|

|

|

|

be in high-impedance. |

|

|

RCLK |

Read Clock |

7 |

11 |

I |

Data is read from the FIFO on a rising edge of |

||

|

|

|

|

|

|

|

RCLK when /REN1 and /REN2 are LOW, and |

|

|

|

|

|

|

|

|

if the FIFO is not empty. |

|

Miscellaneous & Flags Signals

Pin |

Pin name |

TQFP |

PLCC |

I/O |

Description |

Symbol |

|

Pin no. |

Pin no. |

typ |

|

/RS |

Reset |

25 |

29 |

I |

When /RS is set LOW, internal read and write |

|

|

|

|

|

pointers are set to the first location of the RAM |

|

|

|

|

|

array, /FF and /PAF go HIGH, and /PAE and |

|

|

|

|

|

/EF go LOW. A reset is required before an |

|

|

|

|

|

initial WRITE after power-up. |

/FF |

Full Flag |

11 |

15 |

O |

/FF indicates whether or not the FIFO memory |

|

|

|

|

|

is full. |

/EF |

Empty Flag |

10 |

14 |

O |

/EF indicates whether or not the FIFO memory |

|

|

|

|

|

is empty. |

/PAE |

Programmabl |

4 |

8 |

O |

When /PAE is LOW, the FIFO is Almost-Empty |

|

e Almost- |

|

|

|

based on the offset programmed into the FIFO. |

|

Full Flag |

|

|

|

|

/PAF |

Programmabl |

3 |

7 |

O |

When /PAF is LOW, the FIFO is Almost –Full |

|

e Almost- |

|

|

|

based on the offset programmed into the FIFO. |

|

Full Flag |

|

|

|

|

Power/Ground Signals

Pin |

Pin name |

TQFP |

PLCC |

I/O |

Description |

Symbol |

|

Pin no. |

Pin no. |

typ |

|

VCC |

Power |

21 |

25 |

- |

3.3V ± 10% power supply |

GND |

Ground |

5 |

9 |

- |

Ground. |

8.0Memory Operations

8.1Inputs and Outputs

8.1.1 DATA INPUTS (D8 ~ D0)

D8 ~ D0 are 9-bit wide of input data port.

AL4CS211/AL4CS221/AL4CS231/AL4CS241/AL4CS251 |

December 14, 2001 |

8 |

Loading...

Loading...