Page 1

BDTIC www.bdtic.com/ATMEL

Features

• High Performance, Low Power AVR

• Advanced RISC Architecture

– 124 Powerful Instructions - Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 8 MIPS Throughput at 8 MHz

• High Endurance Non-volatile Memory Segments

– 16K/32K Bytes of In-System Self-Programmable Flash (ATmeg a1 6 H VB/32HVB)

– 512/1K Bytes EEPROM

– 1K/2K Bytes Internal SRAM

– Write/Erase Cycles 10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85°C/100 years at 25°C

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– Programming Lock for Software Security

• Battery Management Features

– Two, three or Four Cells in Series

– High-current Protection (Charge and Discharge)

– Over-current Protection (Charge and Discharge)

– Short-circuit Protection (Discharge)

– High Voltage Outputs to Drive N-Channel Charge/Discharge FETs

– High Voltage Output to drive P-Channel Precharge FET

– Integrated Cell Balancing FETs

• Peripheral Features

– Two configurable 8- or 16-bit Timers with Separate Prescaler, Optional Input

Capture (IC), Compare Mode and CTC

– SPI - Serial Programmabl e Interface

– 12-bit Voltage ADC, Six External and One Internal ADC Input

– High Resolution Coulomb Counter ADC for Current Measurements

– TWI Serial Interface for SM-Bus

– Programmable Watchdog Timer

• Special Microcontroller Features

– debugWIRE On-chip Debug System

– In-System Programmable via SPI ports

– Power-on Reset

– On-chip Voltage Regulator with Short-circuit Monitoring Interface

– External and Internal Interrupt Sources

– Sleep Modes: Idle, ADC Noise Reduction, Power-save, and Power-off

• Additional Secure Authentication Features available only under ND A

• Packages

– 44-lead TSSOP

• Operating Voltage: 4 - 25V

• Maximum Withstand Voltage (High-voltage pins): 35V

• Temperature Range: -30°C to 85°C

• Speed Grade: 1-8 MHz

®

8-bit Microcontroller

(1)

8-bit

Microcontroller

with 16K/32K

Bytes In-System

Programmable

Flash

ATmega16HVB

ATmega32HVB

Advance

Information

Summary

8042AS–AVR–09/08

Page 2

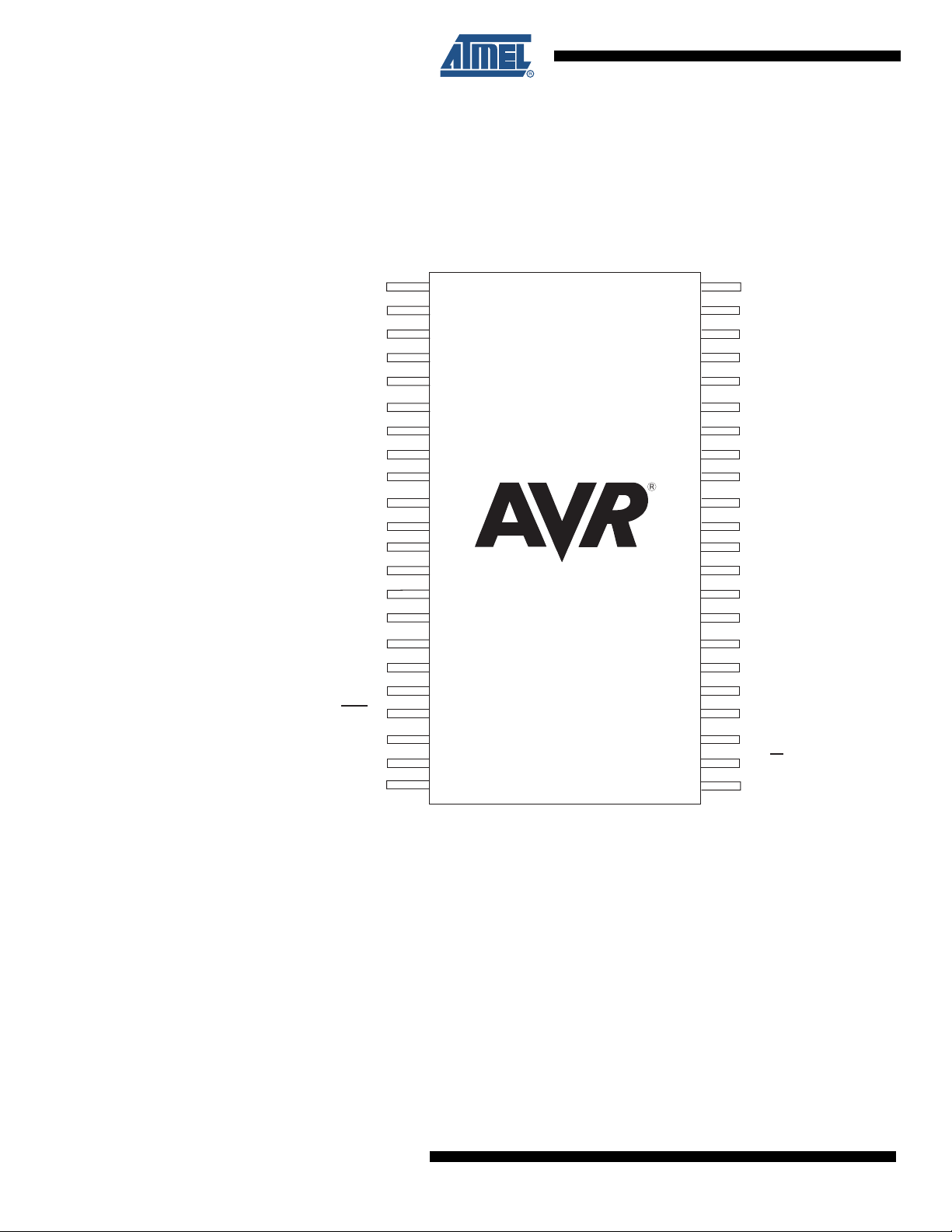

1. Pin Configurations

1

44

3

NI

NNI

VREFGND

VREF

GND

VREG

PA0(ADC0/SGND/PCINT0)

PA1(ADC1/SGND/PCINT1)

PA2(PCINT2/T0)

PA3(PCINT3/T1)

NC

VFET

BATT

VCC

GND

OD

NC

OC

RESET/dw

PB0(PCINT4/ICP00)

PB1(PCINT5/CKOUT)

PB2(PCINT6)

PI

PPI

NV

PV1

PV2

PV3

PV4

PVT

VCC

GND

PC5

PC4(SCL)

PC3(INT3/SDA)

PC2(INT2)

PC1(INT1)

PC0(INTO/EXTPROT)

PB7(MISO/PCINT11)

NC

PB6(MOSI/PCINT10)

PB5(SCK/PCINT9)

PB4(SS/PCINT8)

PB3(PCINT7)

2

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

1.1 TSSOP

Figure 1-1. TSSOP - pinout ATmega16HVB/32HVB

1.2 Pin Descriptions

1.2.1 VFET

1.2.2 VCC

1.2.3 VREG

2

ATmega16HVB/32HVB

High voltage supply pin. This pin is used as supply for th e internal voltage regulator, descri bed in

”Voltage Regulator” on page 132.

Digital supply voltage. Normally connected to VREG.

Output from the internal Voltage Regulator. Used for external decoupling to ensure stable regulator operation. For details, see ”Voltage Regulator” on page 132.

8042AS–AVR–09/08

Page 3

1.2.4 VREF

Internal Voltage Reference for external d ecoupling. For details, see ”Voltage Reference and

Temperature Sensor” on page 124.

1.2.5 VREFGND

Ground for decoupling of Internal Voltage Reference. For details, see ”Voltage Reference and

Temperature Sensor” on page 124. Do not connect to GND or SGND on PCB.

1.2.6 GND

Ground

1.2.7 Port A (PA3..PA0)

Port A serves as a low-voltage 4-bit bi-direct ional I/O po rt with intern al pull-up resistors (selected

for each bit). As inputs, Port A pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port A pins are tri-stated when a reset co ndition becomes active,

even if the clock is not running.

Port A also serves the functions of various special features of the ATmega16HVB/32HVB as

listed in ”Alternate Functions of Port A” on page 76.

ATmega16HVB/32HVB

1.2.8 Port B (PB7..PB0)

Port B is a low-voltage 8-bit bi-directional I/O port with internal pull-up resistors (selected for

each bit). As inputs, Port B pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port B pins are tri-stated when a reset co ndition becomes active,

even if the clock is not running.

Port B also serves the functions of various special features of the ATmega16HVB/32HVB as

listed in ”Alternate Functions of Port B” on page 77.

1.2.9 Port C (PC5)

Port C (PC5) is a high voltage Open Drain output port. Port C serves the functions of various

special features of the ATmega16HVB/32HVB as listed in ”Alternate Functions of Port C” on

page 67.

1.2.10 Port C (PC4..PC0)

Port C is a 5-bit high voltage Open Drain bi-directional I/O port. Port C serves the functions of

various special features of the ATmega16HVB/32HVB as listed in ”Alternate Functions of Port

C” on page 67.

1.2.11 OC/OD

High voltage output to drive Charge/Discharge. For details, see ”FET Driver” on page 147.

1.2.12 PI/NI

8042AS–AVR–09/08

Filtered positive/negative input from external current sense resistor, used to by the Coulomb

Counter ADC to measure charge/discharge currents flowing in the battery pack. For details, see

”Coulomb Counter - Dedicated Fuel Gauging Sigma-delta ADC” on page 110.

3

Page 4

1.2.13 PPI/NNI

Unfiltered positive/negative input from external current sense resistor, used by the battery pro tection circuit, for over-current and short-circuit detection. For details, see ”Battery Protection” on

page 135.

1.2.14 NV/PV1/PV2/PV3/PV4

NV, PV1, PV2, PV3, and PV4 are the inputs for battery cells 1, 2, 3 and 4, used by the Voltage

ADC to measure each cell voltage. For details, see ”Voltage ADC – 7-channel General Purpose

12-bit Sigma-Delta ADC” on page 118.

1.2.15 PVT

Defines the source voltage level for the Charge FET driver. F or details, see ”FET Driver” on

page 147.

1.2.16 BATT

Input for detecting when a charger is connected. Defines the source voltage level for the Discharge FET driver. For details, see ”FET Driver” on page 147.

1.2.17 RESET

/dw

Reset input. A low level on this pin for longer than the minimum pulse length will generate a

reset, even if the clock is not running. The minimum pulse length is given in Table 11 on page

38. Shorter pulses are not guaranteed to generate a reset. This pin is also used as debugWIRE

communication pin.

4

ATmega16HVB/32HVB

8042AS–AVR–09/08

Page 5

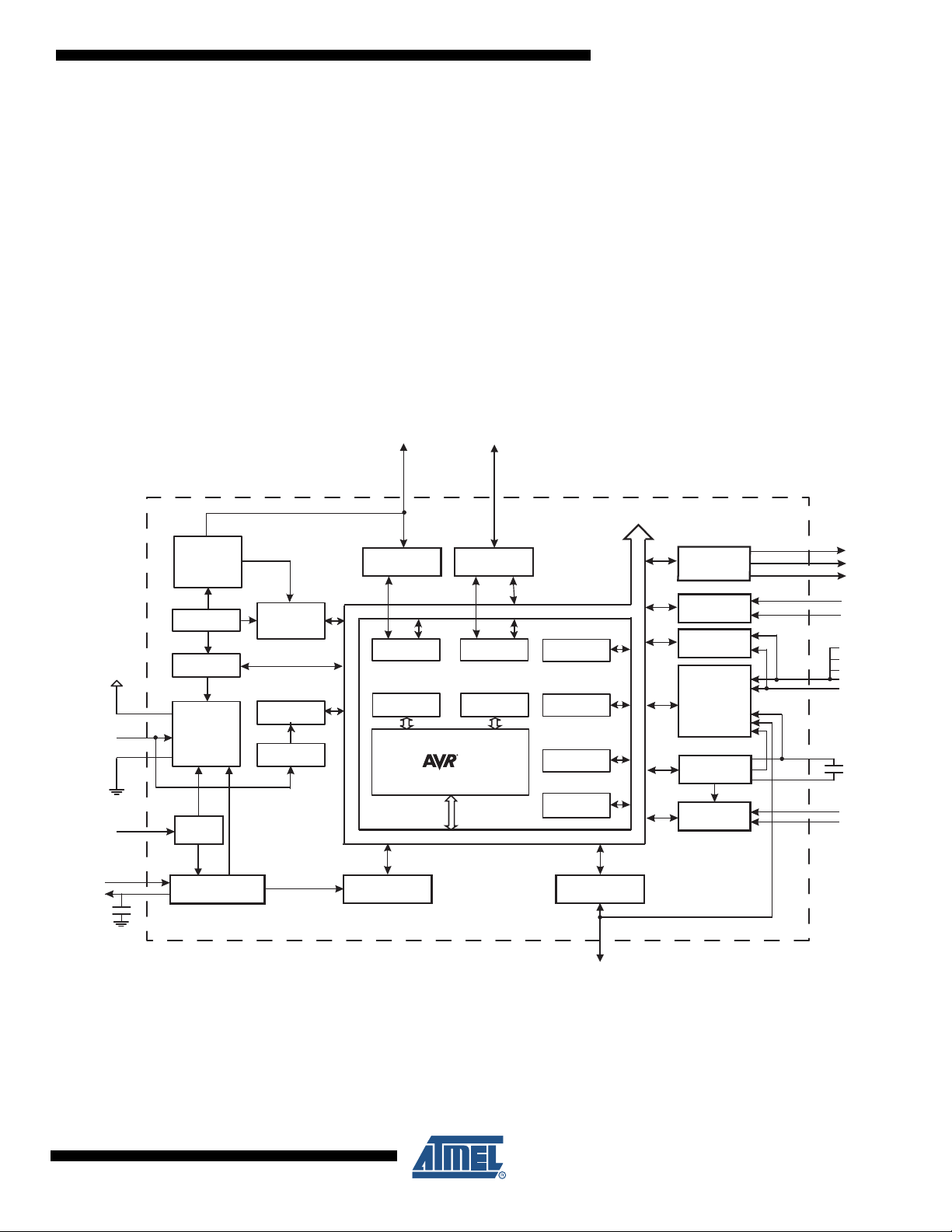

2. Overview

PORTA (4)

SRAMFlash

CPU

EEPROM

PV2

NV

OC

OD

FET

Control

Voltage

ADC

Voltage

Reference

Coulumb

Counter ADC

GND

VCC

RESET/dW

Power

Supervision

POR &

RESET

Watchdog

Oscillator

Watchdog

Timer

Oscillator

Circuits /

Clock

Generation

VREF

VREFGND

PI

NI

PA3..0

PA1..0

8/16-bit T/C1

8/16-bit T/C0

PORTB (8)

PB7..0

SPI

Voltage

Regulator

Charger

Detect

VFET

VREG

BATT

PV1

DATA BUS

VPTAT

Current

Protection

Security

Module

PORTC (6)

PC5..0

Voltage Regulator

Monitor Interface

PB0

Oscillator

Sampling

Interface

Program

Logic

debugWIRE

Cell

Balancing

PV3

PV4

OPC

TWI

PPI

NNI

PORTA (4)

SRAMFlash

CPU

EEPROM

PV2

NV

OC

OD

FET

Control

Voltage

ADC

Voltage

Reference

Coulumb

Counter ADC

GND

VCC

RESET/dW

Power

Supervision

POR &

RESET

Watchdog

Oscillator

Watchdog

Timer

Oscillator

Circuits /

Clock

Generation

VREF

VREFGND

PI

NI

PA3..0

PA1..0

8/16-bit T/C1

8/16-bit T/C0

PORTB (8)

PB7..0

SPI

Voltage

Regulator

Charger

Detect

VFET

VREG

BATT

PV1

DATA BUS

VPTAT

Current

Protection

Security

Module

PORTC (6)

PC5..0

Voltage Regulator

Monitor Interface

PB0

Oscillator

Sampling

Interface

Program

Logic

debugWIRE

Cell

Balancing

PV3

PV4

OPC

TWI

PPI

NNI

The ATmega16HVB/32HVB is a monitoring and protection circuit for 3 and 4-cell Li-ion applications with focus on high security/authentication, low cost and high utilization of the cell energy.

The device contains secure authentication features as well as autonomous battery protection

during charging and discharging. The External Protection Input can be used to implement othe r

battery protection mechanisms using external comp onent s, e.g. p rotectio n against char gers with

too high charge voltage can be easily implemented with a few low cost passive components.

The feature set makes the ATmega 16HVB/32HVB a k ey component in an y system focu sing on

high security, battery protection, high system utilization and low cost.

Figure 2-1. Block Diagram

ATmega16HVB/32HVB

8042AS–AVR–09/08

ATmega16HVB/32HVB provides the necessary redundancy on-chip to make sure that the battery is protected in critical failure modes. The chip is specifically des igned to provide safety for

the battery cells in case of pin shorting, loss of power (either caused by battery pack short or V

CC

5

Page 6

short), illegal charger connection or software runaway. This makes ATmega16HVB/32HVB the

ideal 1-chip solution for applications with focus on high safety.

The ATmega16HVB/32HVB features an integrated voltage regulator that operates at a wide

range of input voltages, 4 - 25 volts. This voltage is regulated to a constant supply voltage of

nominally 3.3 volts for the integrated logic and analog functions. The regulator capabilities, combined with a extremely low power consumption in the power saving modes, greatly enh ances the

cell energy utilization compared to existing solutions.

The chip utilizes Atmel's patented Deep Under-voltage Recovery (DUVR) mode that supports

pre-charging of deeply discharged ba ttery cells without using a se parate Pre-charge FET.

Optionally, Pre-charge FETs are supported for integration into many existing battery charging

schemes.

The battery protection monitors the charge and discharge current to detect illegal conditions and

protect the battery from these when required. A 12-bit Voltage ADC allows software to monitor

each cell voltage individually with high accuracy. The ADC also provides one interna l input channel to measure on-chip temperature and two input channels intended for external thermistors.

An 18-bit ADC optimized for Coulomb Counting accumu lates charge an d discharg e currents and

reports accumulated current with high resolution and accuracy. It can also be used to provide

instantaneous current measurements with 13 bit resolution. Integrated Cell Balancing FETs

allow cell balancing algorithms to be implemented in software.

The MCU provides the following features: 16K/32K bytes of In -System Programma ble Flash with

Read-While-Write capabilities, 512/1K bytes EEPROM, 1K/2K bytes SRAM. 32 general purpose

working registers, 12 general purpose I/O lines, 5 general purpose high voltage open drain I/O

lines, one general purpose super high voltage open drain output, debugWIRE for On-chip

debugging and SPI for In-system Programming, a SM-Bus compliant TWI module, two flexible

Timer/Counters with Input Capture and compare modes.

Internal and external interrupts, a 12-bit Sigma Delta ADC for voltage an d temperature measur ements, a high resolution Sigma Delta ADC for Coulomb Counting and instan taneous current

measurements, integrated cell balancing FETs, Additional Secure Authentication Features, an

autonomous Battery Protection module, a programmable Watchdog Timer with internal Oscillator, and software selectable power saving modes.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the

32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent

registers to be accessed in one single instruction executed in one clock cycle. The resulting

architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The device is manufactured using Atmel’s high voltage high density non-volatile memo ry technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System,

through an SPI serial interface, by a conven tional no n-volatile memory progr ammer or by a n Onchip Boot program running on the AVR core. The Boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash

section will continue to run while the Application Flash section is updated, providing true ReadWhile-Write operation. By combining an 8-bit RISC CPU with In-System Self-ProgrammableFlash and highly accurate analog front-end in a monolithic chip.

The Atmel ATmega16HVB/32HVB is a powerful microcontroller that provides a highly flexible

and cost effective solution. It is part of the AVR Smart Battery family that provides secure

6

ATmega16HVB/32HVB

8042AS–AVR–09/08

Page 7

ATmega16HVB/32HVB

authentication, highly accurate monitoring and autonomous protection for Lithium-ion battery

cells.

The ATmega16HVB/32HVB AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, and Onchip Debugger.

2.1 Comparison Between ATmega16HVB and ATmega32HVB

The ATmega16HVB and ATmega32HVB differ only in memory size for Flash, EEPRO M and

internal SRAM. Table 2-1 summarizes the different configuration for the two devices.

Table 2-1. Configuration summary

Device Flash EEPROM SRAM

ATmega16HVB 16K 512 1K

ATmega32HVB 32K 1K 2K

3. Disclaimer

All Min, Typ and Max values contained in this datasheet are preliminary estimat es based on simulations and characterization of other AVR microcontrollers manufactured on the same process

technology. Final values will be available after the device is characterized.

4. Resources

5. Data Retention

A comprehensive set of development tools, application notes and datasheets are available for

download on http://www.atmel.com/avr.n1

Note: 1.

Reliability Qualification results show that the projected data retention failure rate is much less

than 1 PPM over 20 years at 85°C or 100 years at 25°C.

8042AS–AVR–09/08

7

Page 8

6. Register Summary

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

(0xFF) Reserved – – – – – – – –

(0xFE) BPPLR – – – – – – BPPLE BPPL 140

(0xFD) BPCR – – EPID SCD DOCD COCD DHCD CHCD 141

(0xFC) BPHCTR – – HCPT[5:0] 142

(0xFB) BPOCTR – – OCPT[5:0] 142

(0xFA) BPSCTR – SCPT[6:0] 142

(0xF9) BPCHCD CHCDL[7:0] 145

(0xF8) BPDHCD DHCDL[7:0] 144

(0xF7) BPCOCD COCDL[7:0] 144

(0xF6) BPDOCD DOCDL[7:0] 143

(0xF5) BPSCD SCDL[7:0] 143

(0xF4) Reserved – – – – – – – –

(0xF3) BPIFR – – – SCIF DOCIF COCIF DHCIF CHCIF 146

(0xF2) BPIMSK – – – SCIE DOCIE COCIE DHCIE CHCIE 145

(0xF1) CBCR

(0xF0) FCSR

(0xEF) Reserved – – – – – – – –

(0xEE) Reserved

(0xED) Reserved

(0xEC) Reserved – – – – – – – –

(0xEB) Reserved – – – – – – – –

(0xEA) CADRDC CADRDC[7:0] 117

(0xE9) CADRCC CADRCC[7:0] 116

(0xE8) CADCSRC (0xE7) CADCSRB – CADACIE CADRCIE CADICIE – CADACIF CADRCIF CADICIF 114

(0xE6) CADCSRA CADEN CADPOL CADUB CADAS[1:0] CADSI[1:0] CADSE 113

(0xE5) CADICH CADIC[15:8] 115

(0xE4) CADICL CADIC[7:0] 115

(0xE3) CADAC3 CADAC[31:24] 116

(0xE2) CADAC2 CADAC[23:16] 116

(0xE1) CADAC1 CADAC[15:8] 116

(0xE0) CADAC0 CADAC[7:0] 116

(0xDF) Reserved – – – – – – – –

(0xDE) Reserved – – – – – – – –

(0xDD) Reserved – – – – – – – –

(0xDC) Reserved – – – – – – – –

(0xDB) Reserved – – – – – – – –

(0xDA) Reserved – – – – – – – –

(0xD9) Reserved – – – – – – – –

(0xD8) Reserved – – – – – – – –

(0xD7) Reserved – – – – – – – –

(0xD6) Reserved

(0xD5) Reserved

(0xD4) CHGDCSR – – – BATTPVL CHGDISC1 CHGDISC1 CHGDIF CHGDIE 131

(0xD3) Reserved

(0xD2) BGCSR

(0xD1) BGCRR BGCR[7:0] 126

(0xD0) BGCCR

(0xCF) Reserved

(0xCE) Reserved

(0xCD) Reserved – – – – – – – –

(0xCC) Reserved

(0xCB) Reserved

(0xCA) Reserved – – – – – – – –

(0xC9) Reserved

(0xC8) ROCR ROCS

(0xC7) Reserved – – – – – – – –

(0xC6) Reserved

(0xC5) Reserved – – – – – – – –

(0xC4) Reserved

(0xC3)

(0xC2) Reserved – – – – – – – –

(0xC1) Reserved

(0xC0) Reserved

Reserved

– – – – CBE4 CBE3 CBE2 CBE1 153

– – – – DUVRD CPS DFE CFE 150

– – – – – – – –

– – – – – – – –

- - - -

– – – – – – – –

– – – – – – – –

– – – – – – – –

– –BGDBGSCDE– – BGSCDIF BGSCDIE 127

– – BGCC[5:0] 240

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– –ROCD– – ROCWIF ROCWIE 134

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

- - CADVSE 115

8

ATmega16HVB/32HVB

8042AS–AVR–09/08

Page 9

ATmega16HVB/32HVB

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

(0xBF) Reserved – – – – – – – –

(0xBE) TWBCSR TWBCIF TWBCIE – – – TWBDT1 TWBDT0 TWBCIP 185

(0xBD) TWAMR TWAM[6:0] –185

(0xBC) TWCR TWINT TWEA TWSTA TWSTO TWWC TWEN –TWIE 182

(0xBB) TWDR 2–wire Serial Interface Data Register 184

(0xBA) TWAR TWA[6:0] TWGCE 184

(0xB9) TWSR TWS[7:3] –TWPS1TWPS0 183

(0xB8) TWBR 2–wire Serial Interface Bit Rate Register 182

(0xB7) Reserved – – – – – – –

(0xB6) Reserved – – – – – – – –

(0xB5) Reserved – – – – – – – –

(0xB4) Reserved – – – – – – – –

(0xB3) Reserved – – – – – – – –

(0xB2) Reserved – – – – – – – –

(0xB1) Reserved – – – – – – – –

(0xB0) Reserved – – – – – – – –

(0xAF) Reserved – – – – – – – –

(0xAE) Reserved

(0xAD) Reserved

(0xAC) Reserved – – – – – – – –

(0xAB) Reserved – – – – – – – –

(0xAA) Reserved – – – – – – – –

(0xA9) Reserved – – – – – – – –

(0xA8) Reserved – – – – – – – –

(0xA7) Reserved – – – – – – – –

(0xA6) Reserved – – – – – – – –

(0xA5) Reserved – – – – – – – –

(0xA4) Reserved – – – – – – – –

(0xA3) Reserved – – – – – – – –

(0xA2) Reserved – – – – – – – –

(0xA1) Reserved – – – – – – – –

(0xA0) Reserved – – – – – – – –

(0x9F) Reserved – – – – – – – –

(0x9E) Reserved – – – – – – – –

(0x9D) Reserved – – – – – – – –

(0x9C) Reserved – – – – – – – –

(0x9B) Reserved – – – – – – – –

(0x9A) Reserved – – – – – – – –

(0x99) Reserved – – – – – – – –

(0x98) Reserved – – – – – – – –

(0x97) Reserved – – – – – – – –

(0x96) Reserved – – – – – – – –

(0x95) Reserved – – – – – – – –

(0x94) Reserved – – – – – – – –

(0x93) Reserved

(0x92) Reserved

(0x91) Reserved – – – – – – – –

(0x90) Reserved

(0x8F) Reserved

(0x8E) Reserved

(0x8D) Reserved – – – – – – – –

(0x8C) Reserved

(0x8B) Reserved

(0x8A) Reserved – – – – – – – –

(0x89) OCR1B Timer/Counter1 – Output Compare Register B 97

(0x88) OCR1A Timer/Counter1 – Output Compare Register A 97

(0x87) Reserved – – – – – – – –

(0x86) Reserved

(0x85) TCNT1H Timer/Counter1 (8 Bit) High Byte 97

(0x84) TCNT1L Timer/Counter1 (8 Bit) Low Byte 97

(0x83) Reserved – – – – – – – –

(0x82) Reserved – – – – – – – –

(0x81) TCCR1B

(0x80) TCCR1A TCW1 ICEN1 ICNC1 ICES1 ICS1

(0x7F) Reserved – – – – – – – –

(0x7E) DIDR0

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – – – –

– – – – – CS12 CS11 CS10 83

– –WGM10 96

– – – – – – PA1DID PA0DID 123

8042AS–AVR–09/08

9

Page 10

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

(0x7D) Reserved – – – – – – – –

(0x7C) VADMUX – – – – VADMUX[3:0] 121

(0x7B) Reserved – – – – – – – –

(0x7A) VADCSR – – – – VADEN VADSC VADCCIF VADCCIE 121

(0x79) VADCH – – – – VADC Data Register High byte 122

(0x78) VADCL VADC Data Register Low byte 122

(0x77) Reserved – – – – – – – –

(0x76) Reserved – – – – – – – –

(0x75) Reserved – – – – – – – –

(0x74) Reserved – – – – – – – –

(0x73) Reserved – – – – – – – –

(0x72) Reserved – – – – – – – –

(0x71) Reserved – – – – – – – –

(0x70) Reserved – – – – – – – –

(0x6F) TIMSK1 – – – – ICIE1 OCIE1B OCIE1A TOIE1 98

(0x6E) TIMSK0 – – – – ICIE0 OCIE0B OCIE0A TOIE0 98

(0x6D) Reserved – – – – – – – –

(0x6C) PCMSK1 PCINT[15:8] 62

(0x6B) PCMSK0 – – – – PCINT[3:0] 63

(0x6A) Reserved – – – – – – – –

(0x69) EICRA ISC31 ISC30 ISC21 ISC20 ISC11 ISC10 ISC01 ISC00 60

(0x68) PCICR – – – – – –PCIE1PCIE0 62

(0x67) Reserved – – – – – – – –

(0x66) FOSCCAL Fast Oscillator Calibration Re gister 34

(0x65) Reserved – – – – – – – –

(0x64) PRR0 – PRTWI PRVRM – PRSPI PRTIM1 PRTIM0 PRVADC 42

(0x63) Reserved – – – – – – – –

(0x62) Reserved – – – – – – – –

(0x61) CLKPR CLKPCE – – – – – CLKPS1 CLKPS0 34

(0x60) WDTCSR WDIF WDIE WDP3 WDCE WDE WDP2 WDP1 WDP0 51

0x3F (0x5F) SREG I T H S V N Z C 12

0x3E (0x5E) SPH SP15 SP14 SP13 SP12 SP11 SP10 SP9 SP8 15

0x3D (0x5D) SPL SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0 15

0x3C (0x5C) Reserved – – – – – – – –

0x3B (0x5B) Reserved – – – – – – – –

0x3A (0x5A) Reserved – – – – – – – –

0x39 (0x59) Reserved – – – – – – – –

0x38 (0x58) Reserved – – – – – – – –

0x37 (0x57) SPMCSR – – SIGRD CTPB RFLB PGWRT PGERS SPMEN 204

0x36 (0x56) Reserved – – – – – – – –

0x35 (0x55) MCUCR – –CKOEPUD – – IVSEL IVCE 80/34

0x34 (0x54) MCUSR – – – OCDRF WDRF BODRF EXTRF PORF 51

0x33 (0x53) SMCR – – – – SM[2:0] SE 41

0x32 (0x52) Reserved – – – – – – – –

0x31 (0x51) DWDR debugWIRE Data Register 188

0x30 (0x50) Reserved – – – – – – – –

0x2F (0x4F) Reserved – – – – – – – –

0x2E (0x4E) SPDR SPI Data Register 109

0x2D (0x4D) SPSR SPIF WCOL – – – – –SPI2X 108

0x2C (0x4C) SPCR SPIE SPE DORD MSTR CPOL CPHA SPR1 SPR0 107

0x2B (0x4B) GPIOR2 General Purpose I/O Register 2 26

0x2A (0x4A) GPIOR1 General Purpose I/O Register 1 26

0x29 (0x49) OCR0B Timer/Counter0 Output Compare Register B 97

0x28 (0x48) OCR0A Timer/Counter0 Output Compare Register A 97

0x27 (0x47) TCNT0H Timer/Counter0 (8 Bit) High Byte 97

0x26 (0x46) TCNT0L Timer/Counter0 (8 Bit) Low Byte 97

0x25 (0x45) TCCR0B

0x24 (0x44) TCCR0A TCW0 ICEN0 ICNC0 ICES0 ICS0

0x23 (0x43) GTCCR TSM

0x22 (0x42) EEARH – – – – – – EEPROM High byte 22

0x21 (0x41) EEARL EEPROM Address Register Low Byte 22

0x20 (0x40) EEDR EEPROM Data Register 22

0x1F (0x3F) EECR – – EEPM1 EEPM0 EERIE EEMPE EEPE EERE 23

0x1E (0x3E) GPIOR0 General Purpose I/O Register 0 26

0x1D (0x3D) EIMSK

0x1C (0x3C) EIFR

– – – – – CS02 CS01 CS00 83

– –WGM00 96

– – – – – – PSRSYNC

– – – – INT3 INT2 INT1 INT0 61

– – – – INTF3 INTF2 INTF1 INTF0 61

10

ATmega16HVB/32HVB

8042AS–AVR–09/08

Page 11

ATmega16HVB/32HVB

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

0x1B (0x3B) PCIFR – – – – – –PCIF1PCIF0 62

0x1A (0x3A) Reserved – – – – – – – –

0x19 (0x39) Reserved – – – – – – – –

0x18 (0x38) Reserved – – – – – – – –

0x17 (0x37) OSICSR – – – OSISEL0 – – OSIST OSIEN 35

0x16 (0x36) TIFR1

0x15 (0x35) TIFR0

0x14 (0x34) Reserved – – – – – – – –

0x13 (0x33) Reserved – – – – – – – –

0x12 (0x32) Reserved – – – – – – – –

0x11 (0x31) Reserved – – – – – – – –

0x10 (0x30) Reserved – – – – – – – –

0x0F (0x2F) Reserved – – – – – – – –

0x0E (0x2E) Reserved – – – – – – – –

0x0D (0x2D) Reserved – – – – – – – –

0x0C (0x2C) Reserved – – – – – – – –

0x0B (0x2B) Reserved – – – – – – – –

0x0A (0x2A) Reserved

0x09 (0x29) Reserved

0x08 (0x28) PORTC – – PORTC5 PORTC4 PORTC3 PORTC2 PORTC1 PORTC0 68

0x07 (0x27) Reserved – – – – – – – –

0x06 (0x26) PINC – – – PINC4 PINC3 PINC2 PINC1 PINC0 68

0x05 (0x25) PORTB PORTB7 PORTB6 PORTB5 PORTB4 PORTB3 PORTB2 PORTB1 PORTB0 80

0x04 (0x24) DDRB DDB7 DDB6 DDB5 DDB4 DDB3 DDB2 DDB1 DDB0 80

0x03 (0x23) PINB PINB7 PINB6 PINB5 PINB4 PINB3 PINB2 PINB1 PINB0 80

0x02 (0x22) PORTA – – – – PORTA3 PORTA2 PORTA1 PORTA0 80

0x01 (0x21) DDRA – – – – DDA3 DDA2 DDA1 DDA0 80

0x00 (0x20) PINA – – – – PINA3 PINA2 PINA1 PINA0 80

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses

should never be written.

2. I/O registers within the address range $00 - $1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

3. Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on

all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions

work with registers 0x00 to 0x1F on ly.

4. When using the I/O specific commands IN and OUT , the I/O addresses $00 - $3F must be used. When addressing I/O registers as data space using LD and ST instructions, $20 must be added to these addresses. The ATmega16HVB/32HVB is a

complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the

IN and OUT instructions. For the Extended I/O space from $60 - $FF in SRAM, only the ST/STS/STD and LD/LDS/LDD

instructions can be used.

– – – – ICF1 OCF1B OCF1A TOV1 98

– – – – ICF0 OCF0B OCF0A TOV0 98

– – – – – – – –

– – – – – – – –

8042AS–AVR–09/08

11

Page 12

7. Instruction Set Summary

Mnemonics Operands Description Operation Flags #Clocks

ARITHMETIC AND LOGIC INSTRUCTIONS

ADD Rd, Rr Add two Registers Rd ← Rd + Rr Z,C,N,V,H 1

ADC Rd, Rr Add with Carry two Registers Rd ← Rd + Rr + C Z,C,N,V,H 1

ADIW Rdl,K Add Immediate to Word Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S 2

SUB Rd, Rr Subtract two Registers Rd ← Rd - Rr Z,C,N,V,H 1

SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H 1

SBC Rd, Rr Subtract with Carry two Registers Rd ← Rd - Rr - C Z,C,N,V,H 1

SBCI Rd, K Subtract with Carry Constant from Reg. Rd ← Rd - K - C Z,C,N,V,H 1

SBIW Rdl,K Subtract Immediate from Word Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S 2

AND Rd, Rr Logical AND Re gisters Rd ← Rd • Rr Z,N,V 1

ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V 1

OR Rd, Rr Logical OR Registers Rd ← Rd v Rr Z,N,V 1

ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V 1

EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V 1

COM Rd One’s Complement Rd ← 0xFF − Rd Z,C,N,V 1

NEG Rd Two’s Complement Rd ← 0x00 − Rd Z,C,N,V,H 1

SBR Rd,K Set Bit(s) in Register Rd ← Rd v K Z,N,V 1

CBR Rd,K Clear Bit(s) in Register Rd ← Rd • (0xFF - K) Z,N,V 1

INC Rd Increment Rd ← Rd + 1 Z,N,V 1

DEC Rd Decrement Rd ← Rd − 1 Z,N,V 1

TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V 1

CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V 1

SER Rd Set Register Rd ← 0xFF None 1

MUL Rd, Rr Multiply Unsigned R1:R0 ← Rd x Rr Z,C 2

MULS Rd, Rr Multiply Signed R1:R0 ← Rd x Rr Z,C 2

MULSU Rd, Rr Multiply Signed with Unsigned R1:R0 ← Rd x Rr Z,C 2

FMUL Rd, Rr Fractional Multiply Unsigned R1:R0 ← (Rd x Rr) << 1 Z,C 2

FMULS Rd, Rr Fractional Multiply Signed R1:R0 ← (Rd x Rr) << 1 Z,C 2

FMULSU Rd, Rr Fractional Multiply Signed with Unsigned R1:R0 ← (Rd x Rr) << 1 Z,C 2

BRANCH INSTRUCTIONS

RJMP k Relative Jump PC ← PC + k + 1 None 2

IJMP Indirect Jump to (Z) PC ← Z None 2

JMP k Direct Jump PC ← kNone3

RCALL k Relative Subroutine Call PC ← PC + k + 1 None 3

ICALL Indirect Call to (Z) PC ← ZNone3

CALL k Direct Subroutine Call PC ← kNone4

RET Subroutine Return PC ← STACK None 4

RETI Interrupt Return PC ← STACK I 4

CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3 None 1/2/3

CP Rd,Rr Compare Rd − Rr Z, N,V,C,H 1

CPC Rd,Rr Compare with Carry Rd − Rr − C Z, N,V,C,H 1

CPI Rd,K Compare Register with Immediate Rd − K Z, N,V,C,H 1

SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC ← PC + 2 or 3 None 1/2/3

SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC ← PC + 2 or 3 None 1/2/3

SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC ← PC + 2 or 3 None 1/2/3

SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC ← PC + 2 or 3 None 1/2/3

BRBS s, k Branch if S tatus Flag Set if (SREG(s) = 1) then PC←PC+k + 1 None 1/2

BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC←PC+k + 1 None 1/2

BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1 None 1/2

BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1 None 1/2

BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1 None 1/2

BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1 None 1/2

BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1 None 1/2

BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1 None 1/2

BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1 None 1/2

BRPL k Branch if Plus if (N = 0) then PC ← PC + k + 1 None 1/2

BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1 None 1/2

BRLT k Branch if Less Than Zero, Signed if (N ⊕ V= 1) then PC ← PC + k + 1 None 1/2

BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1 None 1/2

BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1 None 1/2

BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1 None 1/2

BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1 None 1/2

BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1 None 1/2

BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1 None 1/2

12

ATmega16HVB/32HVB

8042AS–AVR–09/08

Page 13

ATmega16HVB/32HVB

7. Instruction Set Summary (Continued)

Mnemonics Operands Description Operation Flags #Clocks

BRIE k Branch if Interrupt Enabled if ( I = 1) then PC ← PC + k + 1 None 1/2

BRID k Branch if Interrupt Disabled if ( I = 0) then PC ← PC + k + 1 None 1/2

BIT AND BIT-TEST INSTRUCTIONS

SBI P,b Set Bit in I/O Register I/O(P,b) ← 1None2

CBI P,b Clear Bit in I/O Register I/O(P,b) ← 0None2

LSL Rd Logical Shift Left Rd(n+1) ← Rd(n), Rd(0) ← 0 Z,C,N,V 1

LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0 Z,C,N,V 1

ROL Rd Rotate Left Through Carry Rd(0)←C,Rd(n+1)← Rd(n),C←Rd(7) Z,C,N,V 1

ROR Rd Rotate Right Through Carry Rd(7)←C,Rd(n)← Rd(n+1),C←Rd(0) Z,C,N,V 1

ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n=0..6 Z,C,N,V 1

SWAP Rd Swap Nibbles Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0) None 1

BSET s Flag Set SREG(s) ← 1 SREG(s) 1

BCLR s Flag Clear SREG(s) ← 0 SREG(s) 1

BST Rr, b Bit Store from Register to T T ← Rr(b) T 1

BLD Rd, b Bit load from T to Register Rd(b) ← TNone1

SEC Set Carry C ← 1C1

CLC Clear Carry C ← 0 C 1

SEN Set Negative Flag N ← 1N1

CLN Clear Negative Flag N ← 0 N 1

SEZ Set Zero Flag Z ← 1Z1

CLZ Clear Zero Flag Z ← 0 Z 1

SEI Global Interrupt Enable I ← 1I1

CLI Global Interrupt Disable I ← 0 I 1

SES Set Signed Test Flag S ← 1S1

CLS Clear Signed Test Flag S ← 0 S 1

SEV Set Twos Complement Overflow. V ← 1V1

CLV Clear Twos Complement Overflow V ← 0 V 1

SET Set T in SREG T ← 1T1

CLT Clear T in SREG T ← 0 T 1

SEH Set Half Carry Flag in SREG H ← 1H1

CLH Clear Half Carry Flag in SREG H ← 0 H 1

DATA TRANSFER INSTRUCTIONS

MOV Rd, Rr Move Between Registers Rd ← Rr None 1

MOVW Rd, Rr Copy Register Word

LDI Rd, K Load Immediate Rd ← KNone1

LD Rd, X Load Indirect Rd ← (X) None 2

LD Rd, X+ Load Indirect and Post-Inc. Rd ← (X), X ← X + 1 None 2

LD Rd, - X Load Indirect and Pre-Dec. X ← X - 1, Rd ← (X) None 2

LD Rd, Y Load Indirect Rd ← (Y) None 2

LD Rd, Y+ Load Indirect and Post-Inc. Rd ← (Y), Y ← Y + 1 None 2

LD Rd, - Y Load Indirect and Pre-Dec. Y ← Y - 1, Rd ← (Y) None 2

LDD Rd,Y+q Load Indirect with Displacement Rd ← (Y + q) None 2

LD Rd, Z Load Indirect Rd ← (Z) None 2

LD Rd, Z+ Load Indirect and Post-Inc. Rd ← (Z), Z ← Z+1 None 2

LD Rd, -Z Load Indirect and Pre-Dec. Z ← Z - 1, Rd ← (Z) None 2

LDD Rd, Z+q Load Indirect with Displacement Rd ← (Z + q) None 2

LDS Rd, k Load Direct from SRAM Rd ← (k) None 2

ST X, Rr Store Indirect (X) ← Rr None 2

ST X+, Rr Store Indirect and Post-Inc. (X) ← Rr, X ← X + 1 None 2

ST - X, Rr Store Indirect and Pre-Dec. X ← X - 1, (X) ← Rr None 2

ST Y, Rr Store Indirect (Y) ← Rr None 2

ST Y+, Rr Store Indirect and Post-Inc. (Y) ← Rr, Y ← Y + 1 None 2

ST - Y, Rr Store Indirect and Pre-Dec. Y ← Y - 1, (Y) ← Rr None 2

STD Y+q,Rr Store Indirect with Displacement (Y + q) ← Rr None 2

ST Z, Rr Store Indirect ( Z ) ← Rr None 2

ST Z+, Rr Store Indirect and Post-Inc. (Z) ← Rr, Z ←

ST -Z, Rr Store Indirect and Pre-Dec. Z ← Z - 1, (Z) ← Rr None 2

STD Z+q,Rr Store Indirect with Displacement (Z + q) ← Rr None 2

STS k, Rr Store Direct to SRAM (k) ← Rr None 2

LPM Load Program Memory R0 ← (Z) None 3

LPM Rd, Z Load Program Memory Rd ← (Z) None 3

LPM Rd, Z+ Load Program Memory and Post-Inc Rd ← (Z), Z ← Z+1 None 3

SPM Store Program Memory (Z) ← R1:R0 None IN Rd, P In Port Rd ← PNone1

Rd+1:Rd ← Rr+1:Rr

Z + 1 None 2

None 1

8042AS–AVR–09/08

13

Page 14

7. Instruction Set Summary (Continued)

Mnemonics Operands Description Operation Flags #Clocks

OUT P, Rr Out Port P ← Rr None 1

PUSH Rr Push Register on Stack STACK ← Rr None 2

POP Rd Pop Register from Stack Rd ← STACK None 2

MCU CONTROL INSTRUCTIONS

NOP No Operation None 1

SLEEP Sleep (see specific descr. for Sleep function) None 1

WDR Watchdog Reset (see specific descr. for WDR/timer) None 1

BREAK Break For On-chip Debug Only None N/A

14

ATmega16HVB/32HVB

8042AS–AVR–09/08

Page 15

ATmega16HVB/32HVB

8. Ordering Information –TBD

8.1 ATmega16HVB

Speed (MHz) Power Supply Ordering Code Package Operation Range

1 - 8 MHz 4 - 25V ATmega16HVB - TBD 44X1 -30°C to 85°C

Package Type

44X1 44-lead, 4.4 mm Body Width, Plastic Thin Shrink Small Outline Package (TSSOP)

8042AS–AVR–09/08

15

Page 16

8.2 ATmega32HVB

Speed (MHz) Power Supply Ordering Code Package Operation Range

1 - 8 MHz 4 - 25V ATmega32HVB - TBD 44X1 -30°C to 85°C

Package Type

44X1 44-lead, 4.4 mm Body Width, Plastic Thin Shrink Small Outline Package (TSSOP)

16

ATmega16HVB/32HVB

8042AS–AVR–09/08

Page 17

9. Packaging Information

TITLE

DRAWING NO.

R

REV.

Note: These drawings are for general information only. Refer to JEDEC Drawing MO-153BE.

2325 Orchard Parkway

San Jose, CA 95131

5/16/07

44X1, 44-lead, 4.4 mm Body Width, Plastic Thin Shrink

Small Outline Package (TSSOP)

44X1 A

COMMON DIMENSIONS

(Unit of Measure = mm)

SYMBOL

MIN

NOM

MAX

NOTE

A –– 1.20

A1 0.05 –

b 0.17 – 0.27

C 0.09 – 0.20

D 10.90 11.00 11.10

E1 4.30 4.40 4.50

E 6.20 6.40 6.60

e 0.50 TYP

L 0.50 0.60 0.70

Ø 0

o

– 8

o

Side View

Top View

End View

Ø

1

44

23

L

C

E1 E

D

e

b

A

A1

0.15

TITLE

DRAWING NO.

R

REV.

Note: These drawings are for general information only. Refer to JEDEC Drawing MO-153BE.

2325 Orchard Parkway

San Jose, CA 95131

5/16/07

44X1, 44-lead, 4.4 mm Body Width, Plastic Thin Shrink

Small Outline Package (TSSOP)

44X1 A

COMMON DIMENSIONS

(Unit of Measure = mm)

SYMBOL

MIN

NOM

MAX

NOTE

A –– 1.20

A1 0.05 – 0.15

b 0.17 – 0.27

C 0.09 – 0.20

D 10.90 11.00 11.10

E1 4.30 4.40 4.50

E 6.20 6.40 6.60

e 0.50 TYP

L 0.50 0.60 0.70

Ø 0

o

– 8

o

Side View

Top View

End View

Ø

14423

L

C

E1 E

D

e

b

A

A1

9.1 44X1

ATmega16HVB/32HVB

8042AS–AVR–09/08

17

Page 18

10. Errata

10.1 ATmega16HVB

10.1.1 Rev. A

10.2 ATmega32HVB

10.2.1 Rev. A

No known errata.

No known errata.

18

ATmega16HVB/32HVB

8042AS–AVR–09/08

Page 19

11. Revision history

11.1 Rev.A - 09/08

1. Initial revision

ATmega16HVB/32HVB

8042AS–AVR–09/08

19

Loading...

Loading...