Page 1

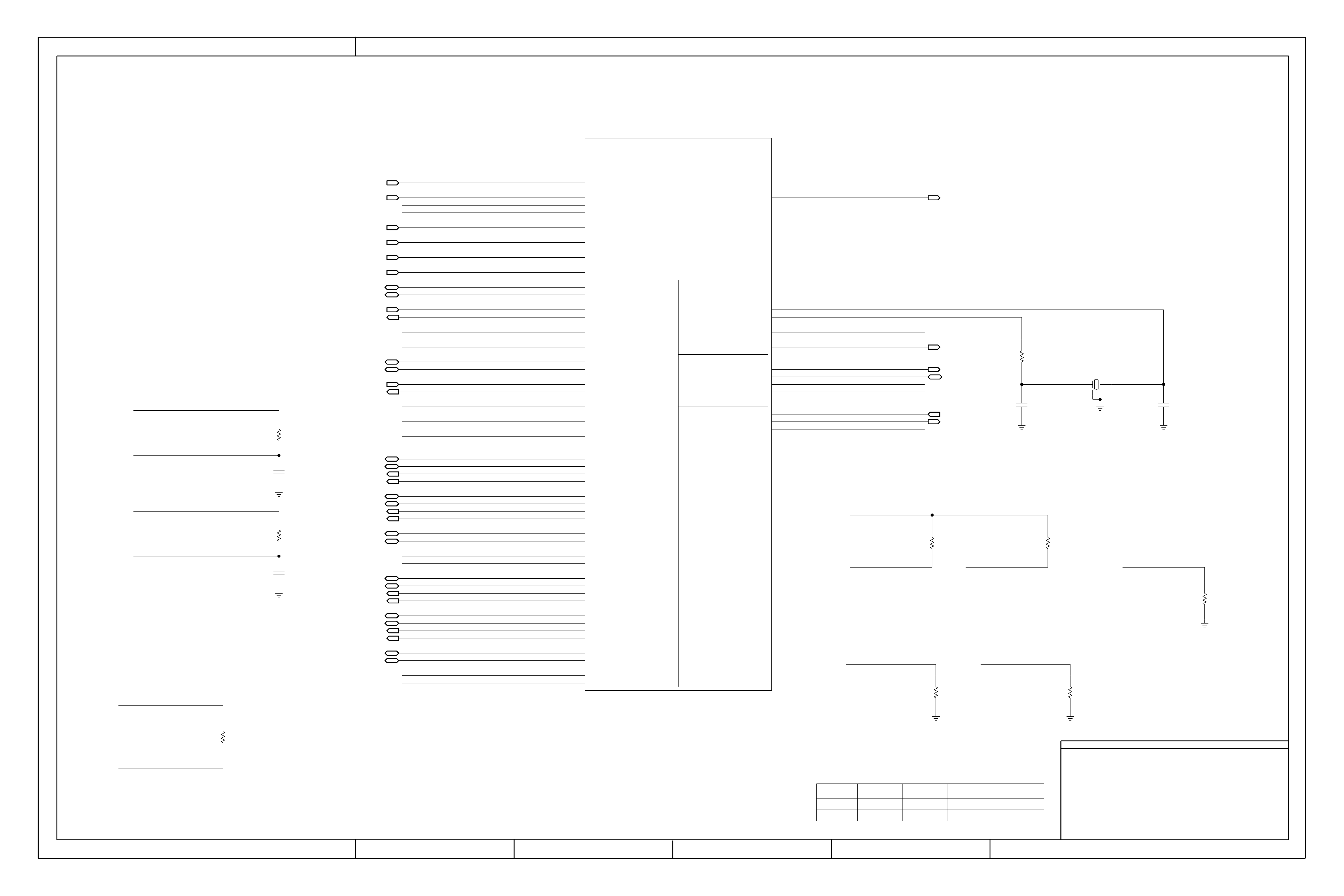

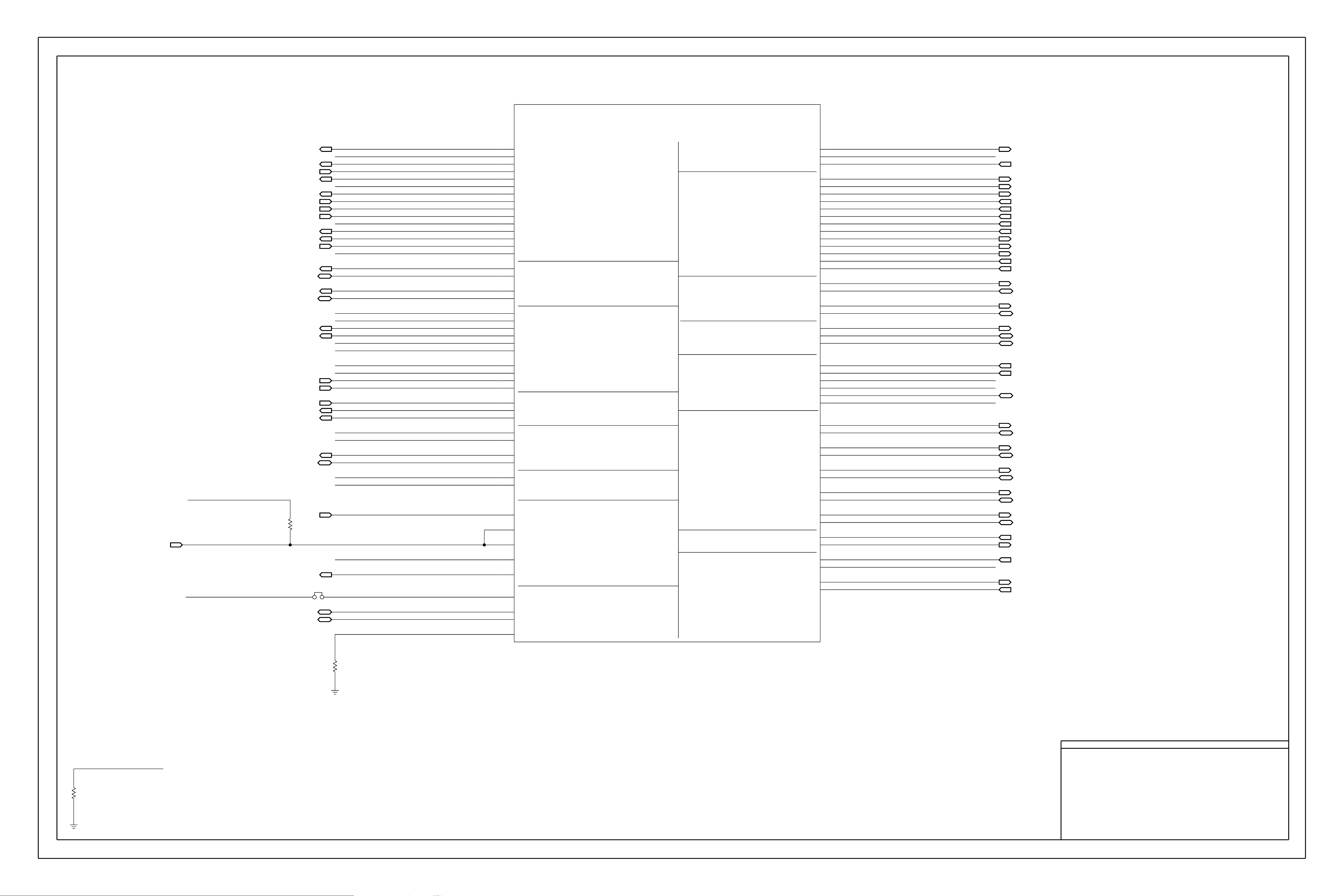

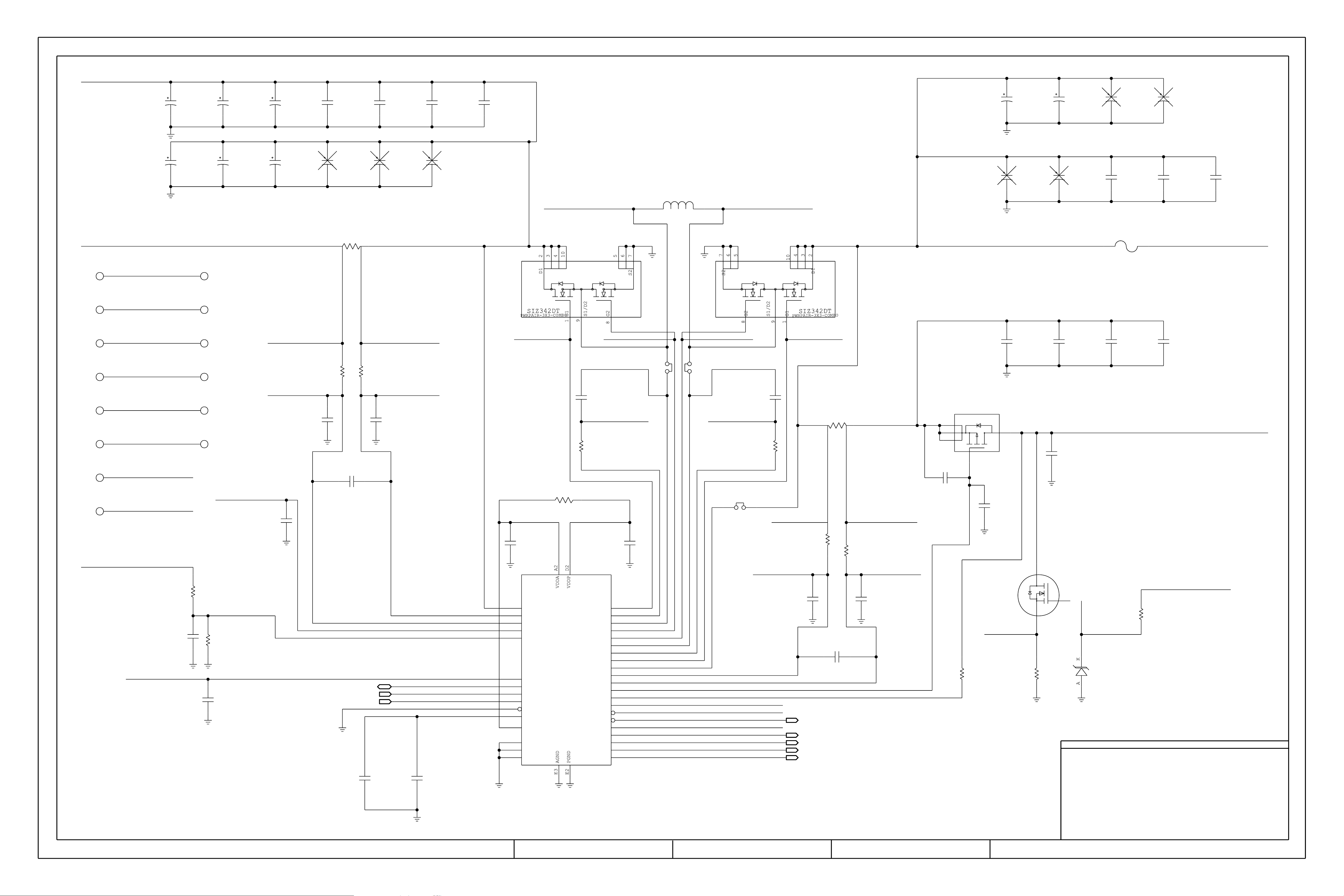

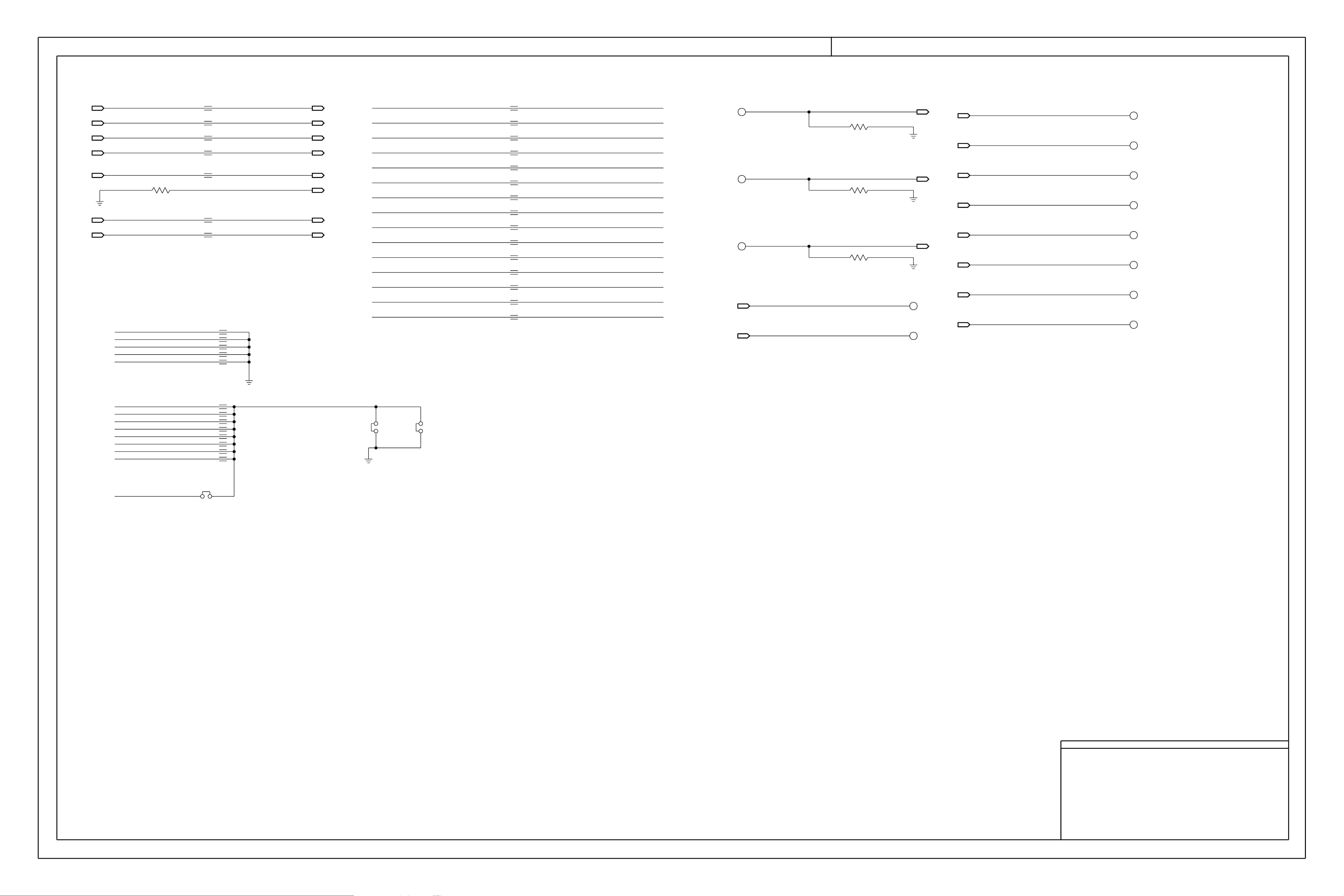

T668 MLB

www.teknisi-indonesia.com

7

7

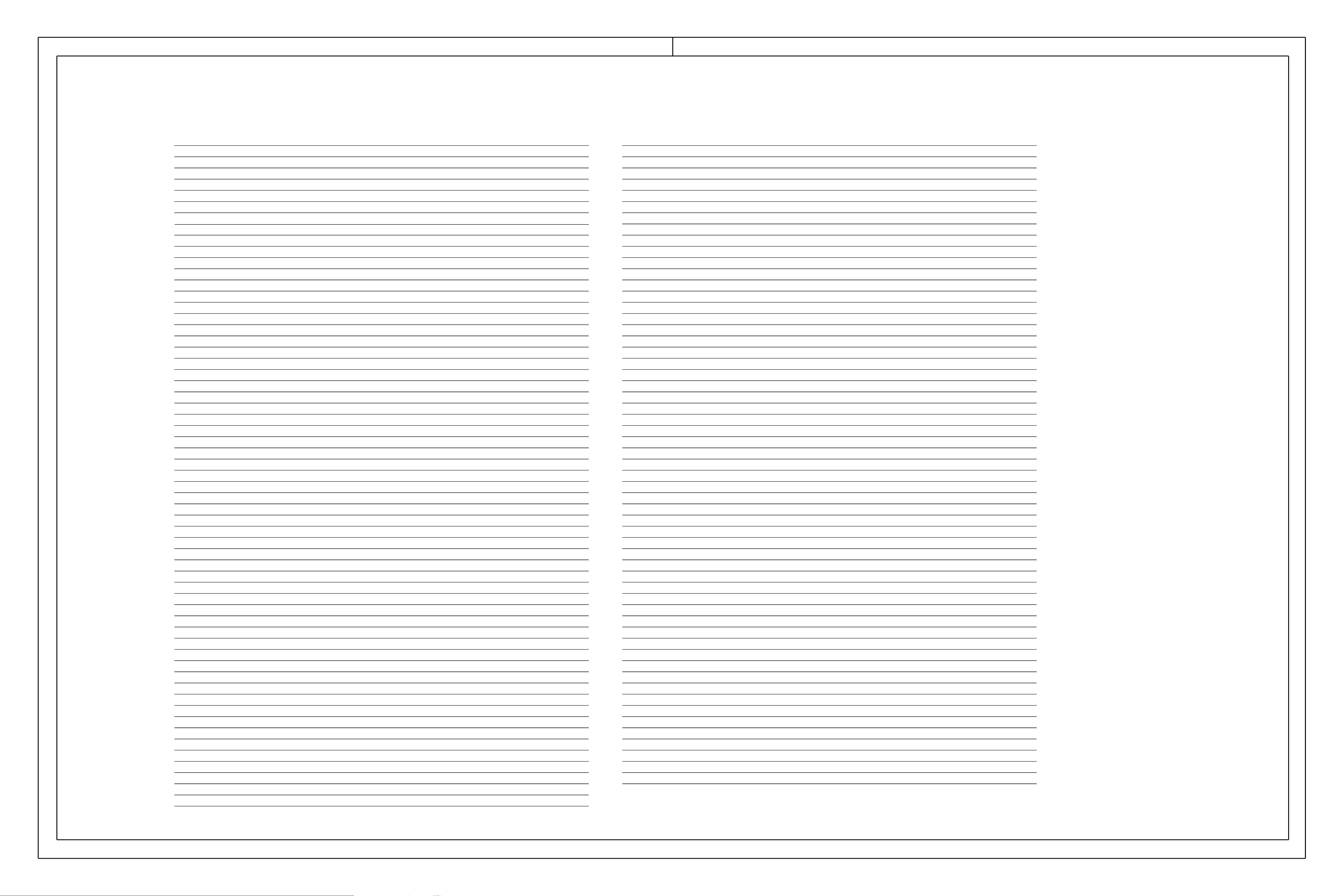

DATESYNCCONTENTSCSAPAGEDATESYNCCONTENTSCSAPAGE

1

2

3

1

2

4

5

5

6

7

8

9

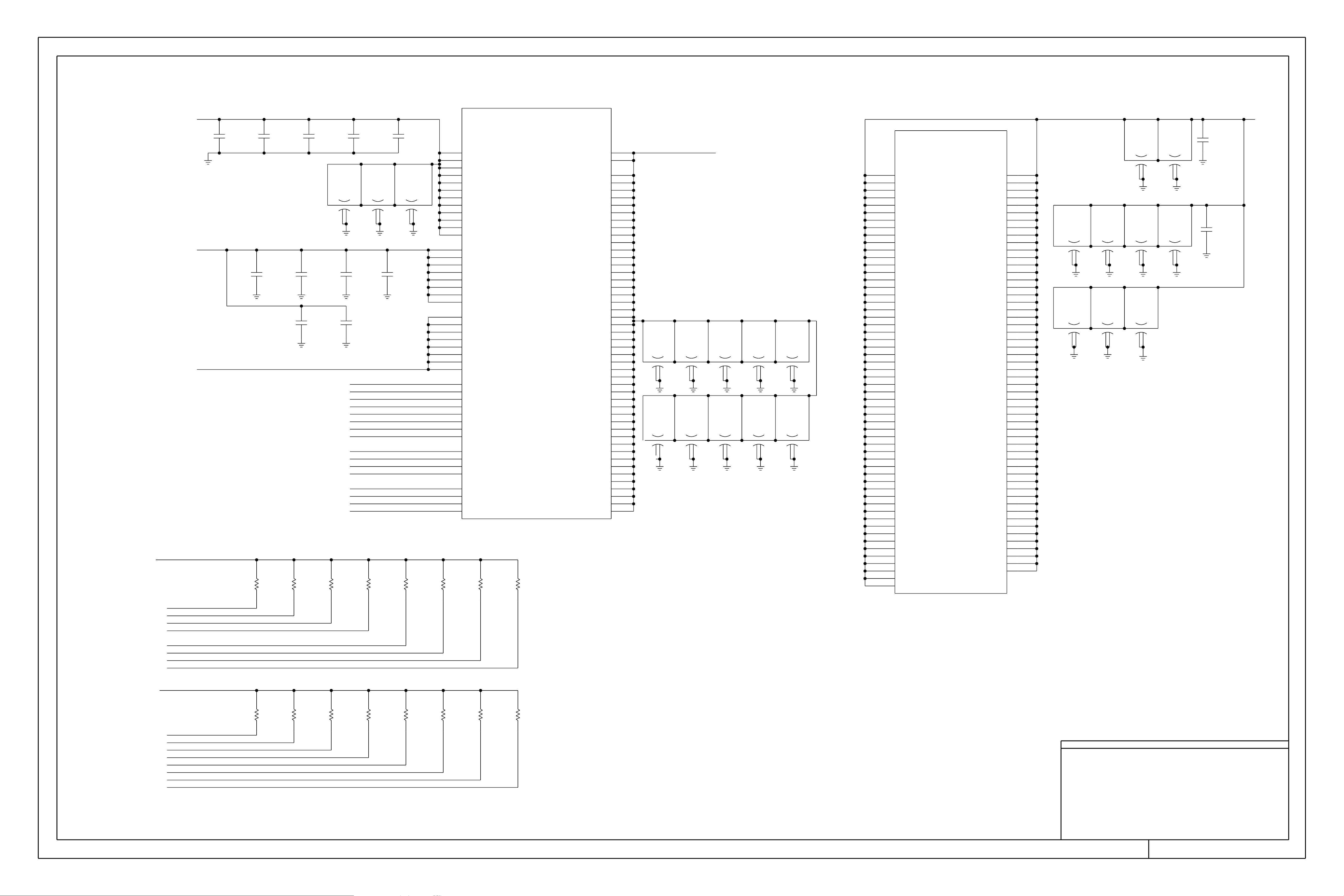

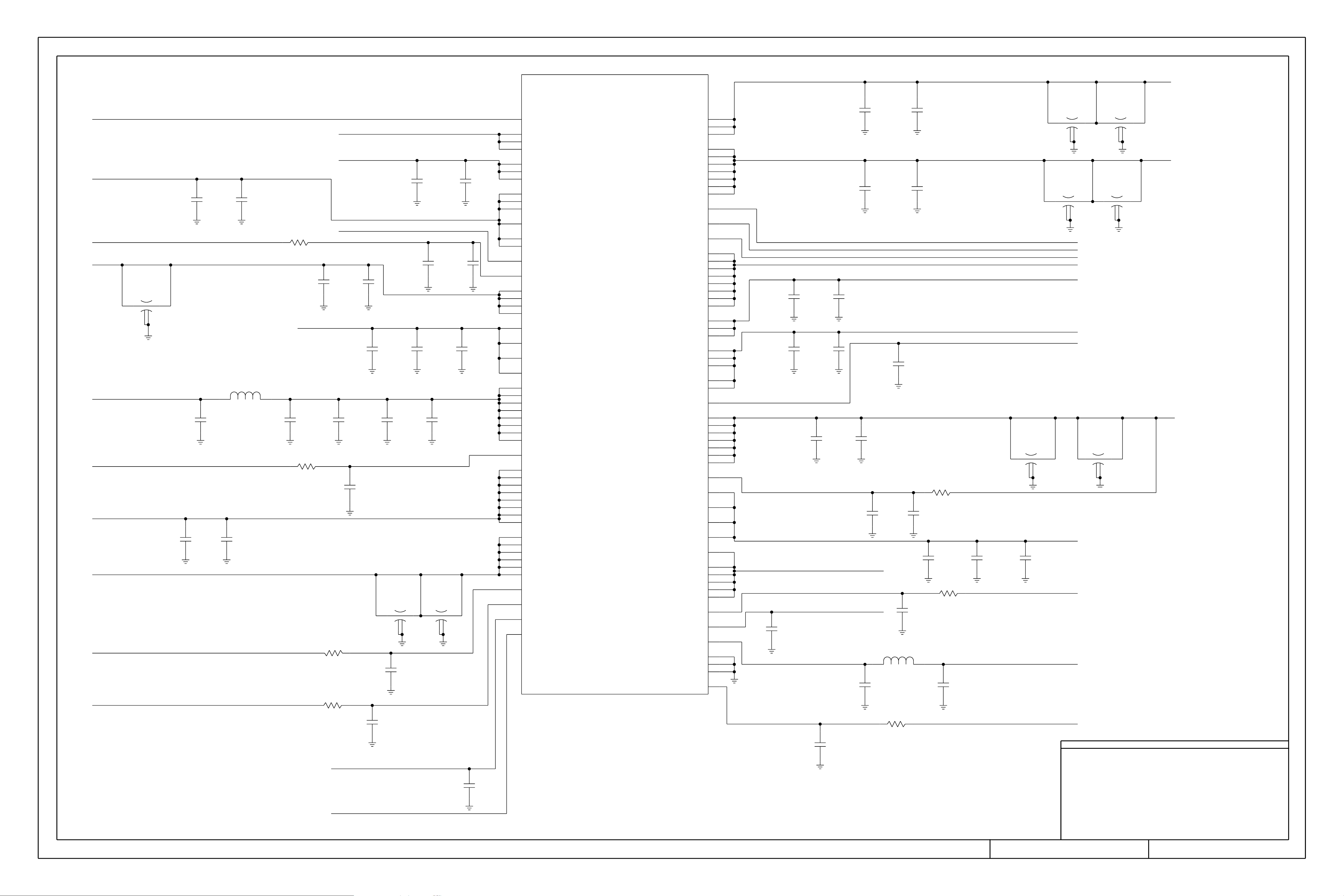

10 SOC: POWER (DDR,SRAM)

11

12

13

14

6

7

8

9

10

11

12

13

14

15

TABLE OF CONTENTS

REFERENCE DESIGN SYNC TABLES

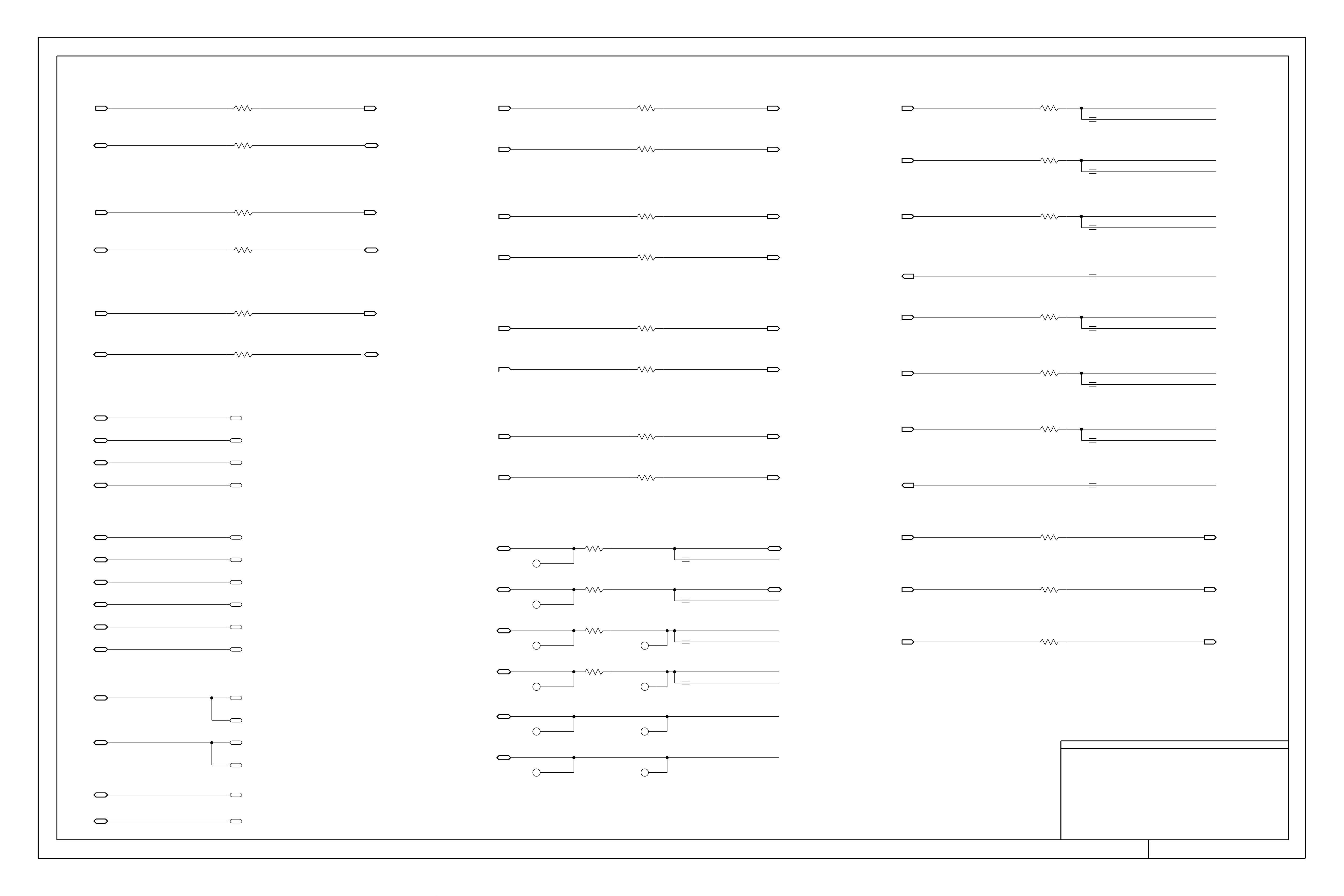

PD PARTS

SOC: Support

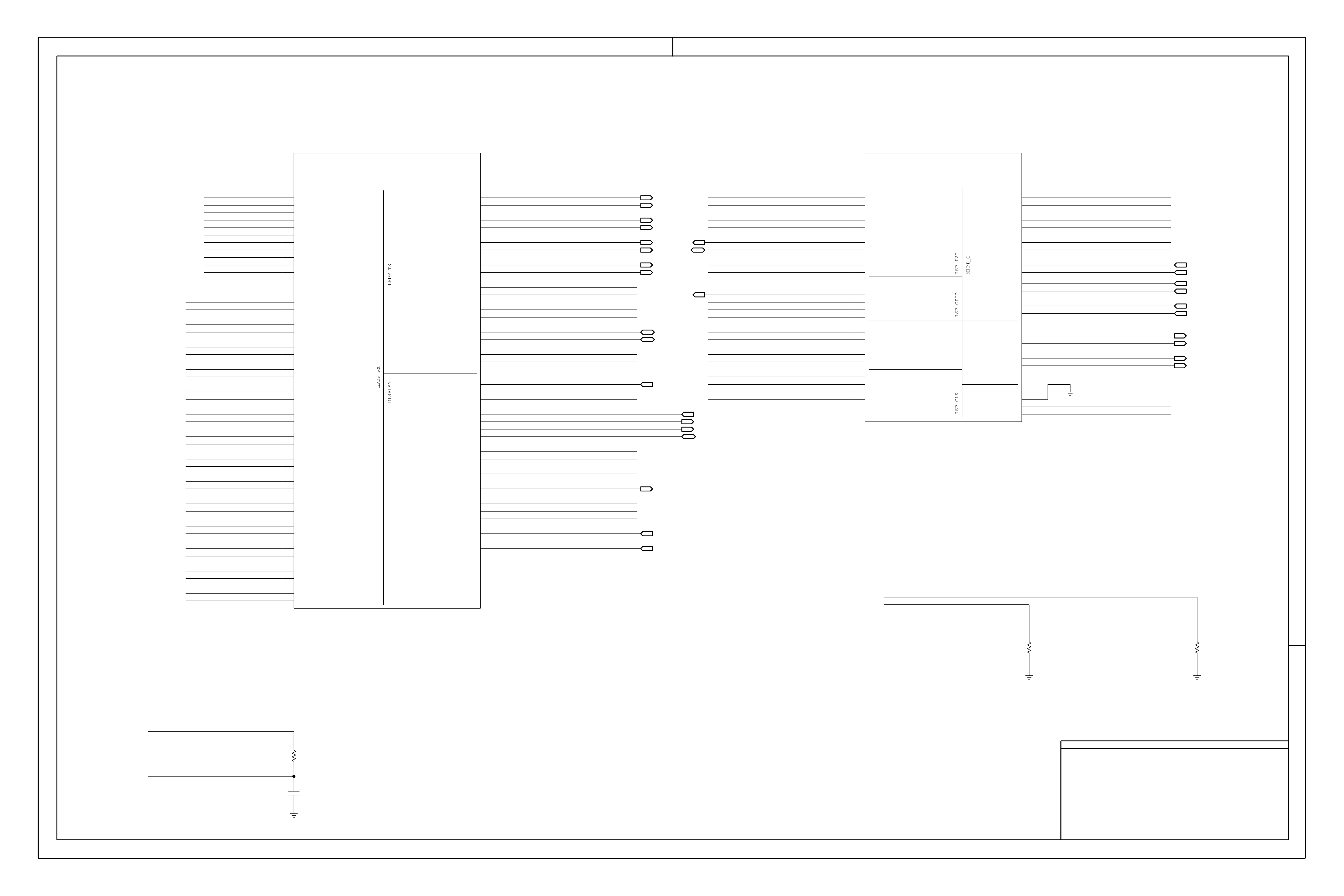

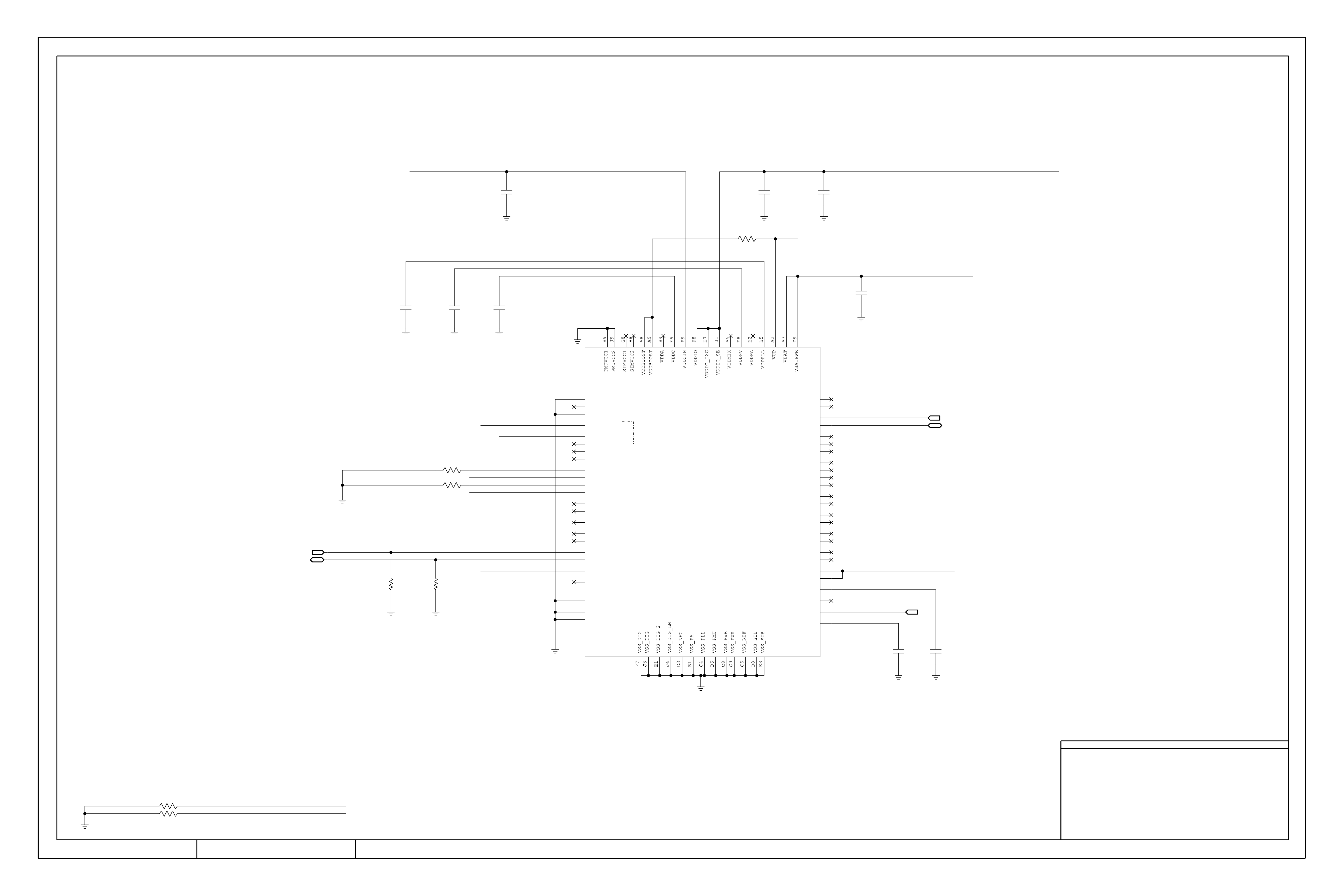

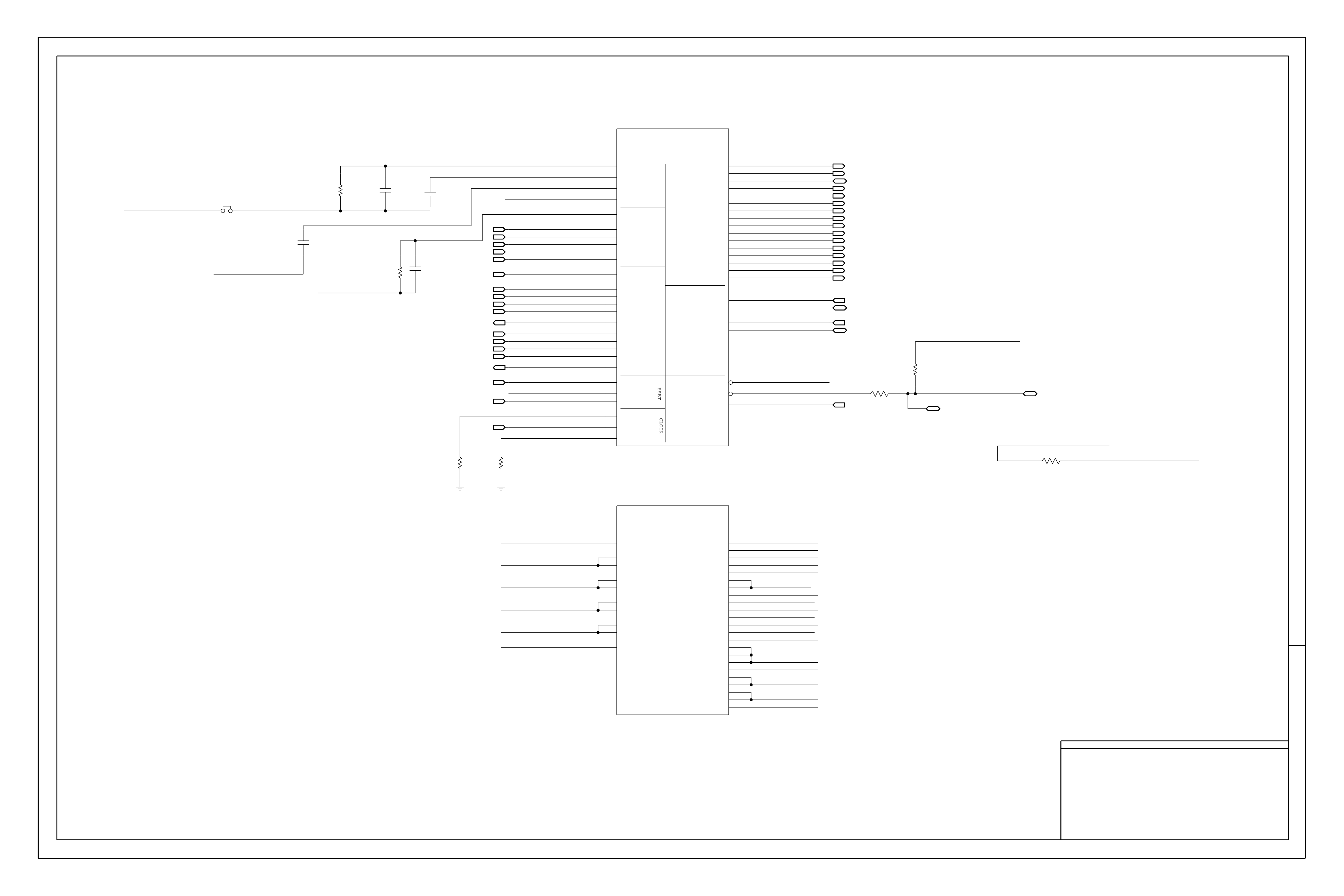

SOC: CIO, USB, RESETS, CLOCKS, SWD

SOC: AP I/Os

SOC: LPDP & MIPI

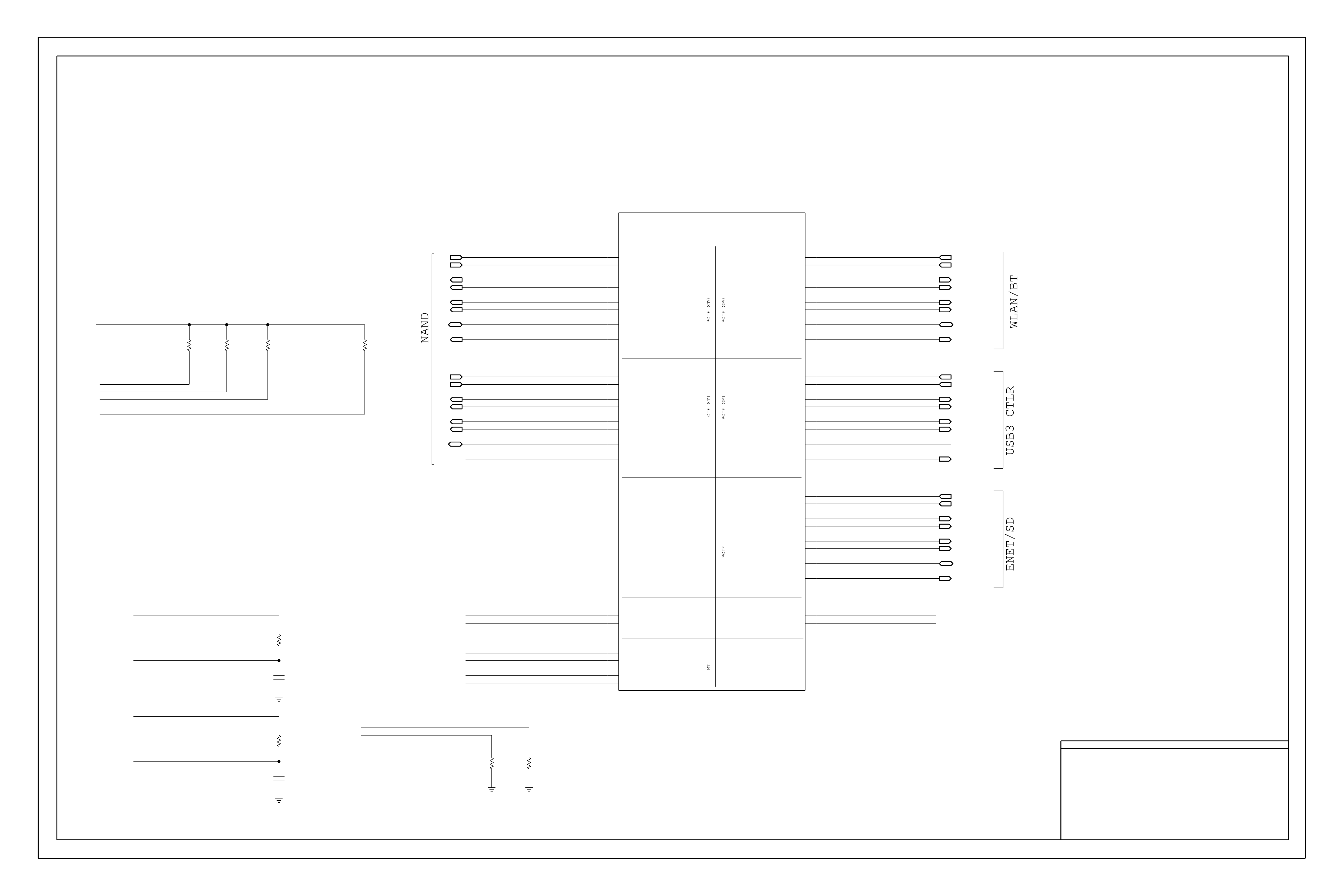

SOC: PCIE

SOC: AOP

SOC: POWER (IO)

SOC: POWER (SOC, CPU, GPU)

SOC: POWER (SRAM)

SOC: POWER (Fixed, PLL's, Filtered)

T668_MLB

T668_KSAITO_MLB_0.11.1

T585_REF_SOC_H13G_0.56.0

AITKEN_T668_MLB

T585_REF_SOC_H13G_0.56.0

AITKEN_T668_MLB

ANDREW_T668_MLB

T585_REF_SOC_H13G_0.56.0

T585_REF_SOC_H13G_0.56.0

T585_REF_SOC_H13G_0.56.0

T585_REF_SOC_H13G_0.56.0

T585_REF_SOC_H13G_0.56.0

T585_REF_SOC_H13G_0.56.0

10/08/2019

10/08/2019

10/09/2019

61

62

63

644

65

66

67

68

69

70

71

72

73

74

158

200

201

220

221

224

230

231

236

237

238

239

242

243

USB-C: SUPPORT

WIFI/BT: MODULE07/17/2019

WIFI/BT: ANTENNA and GND

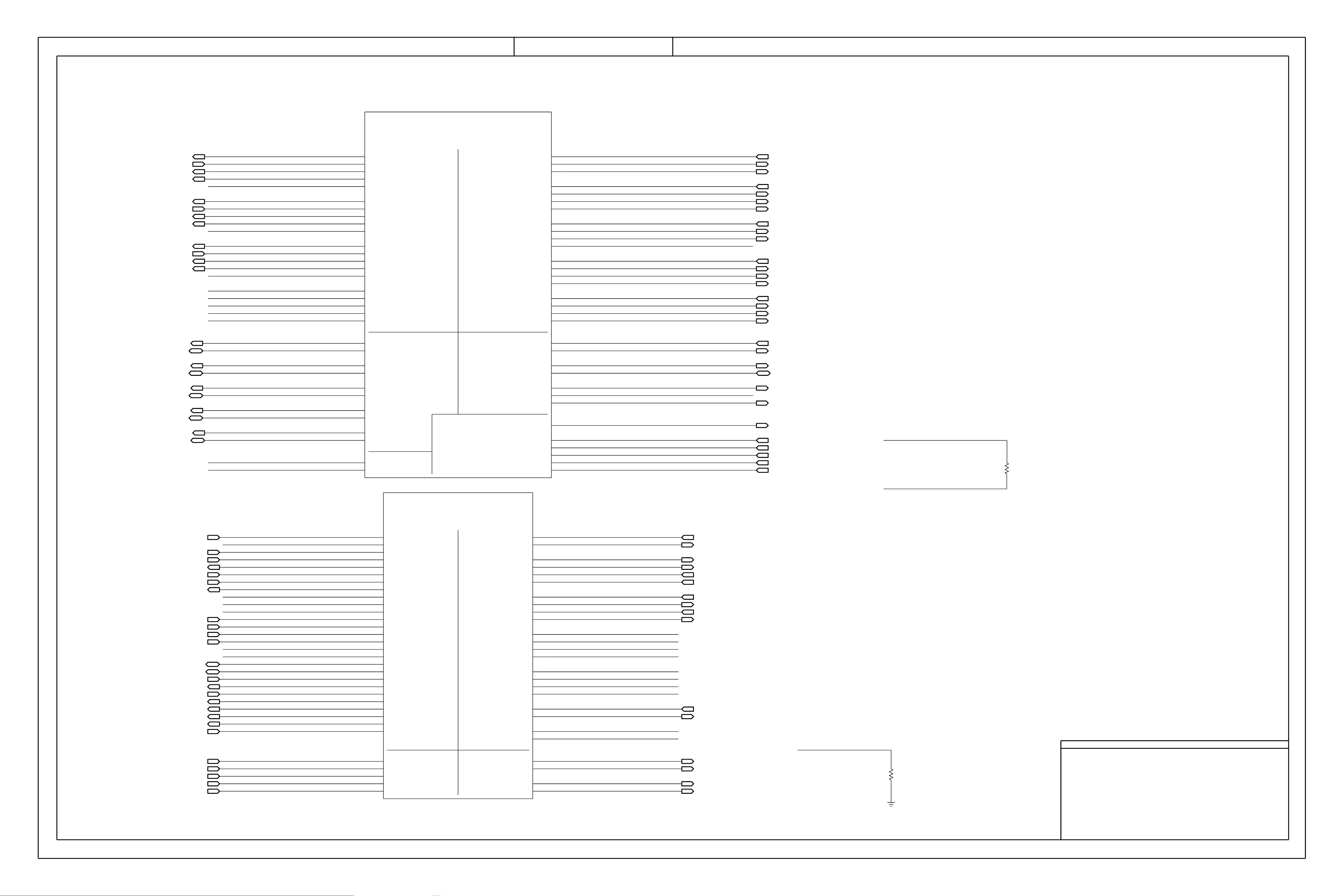

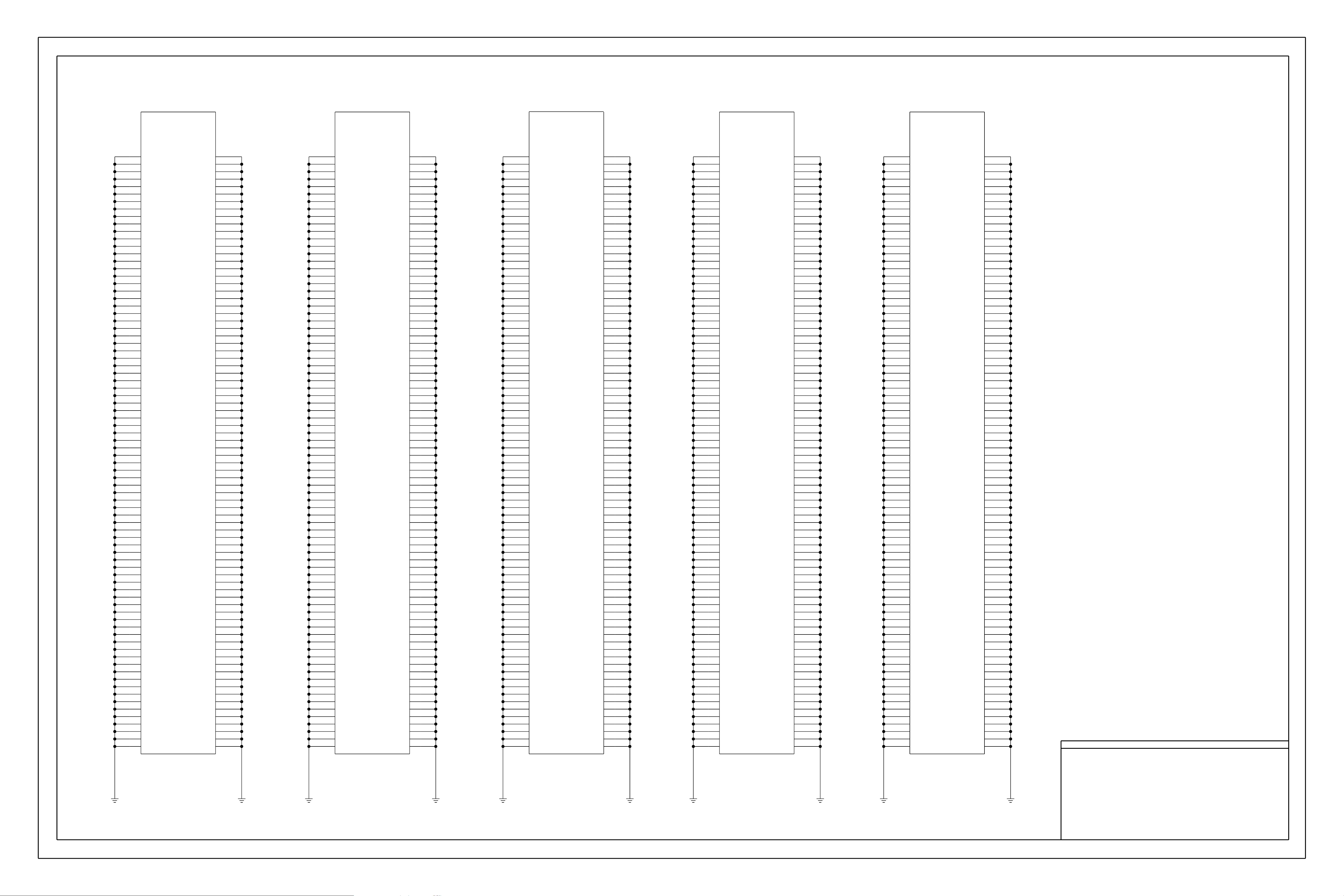

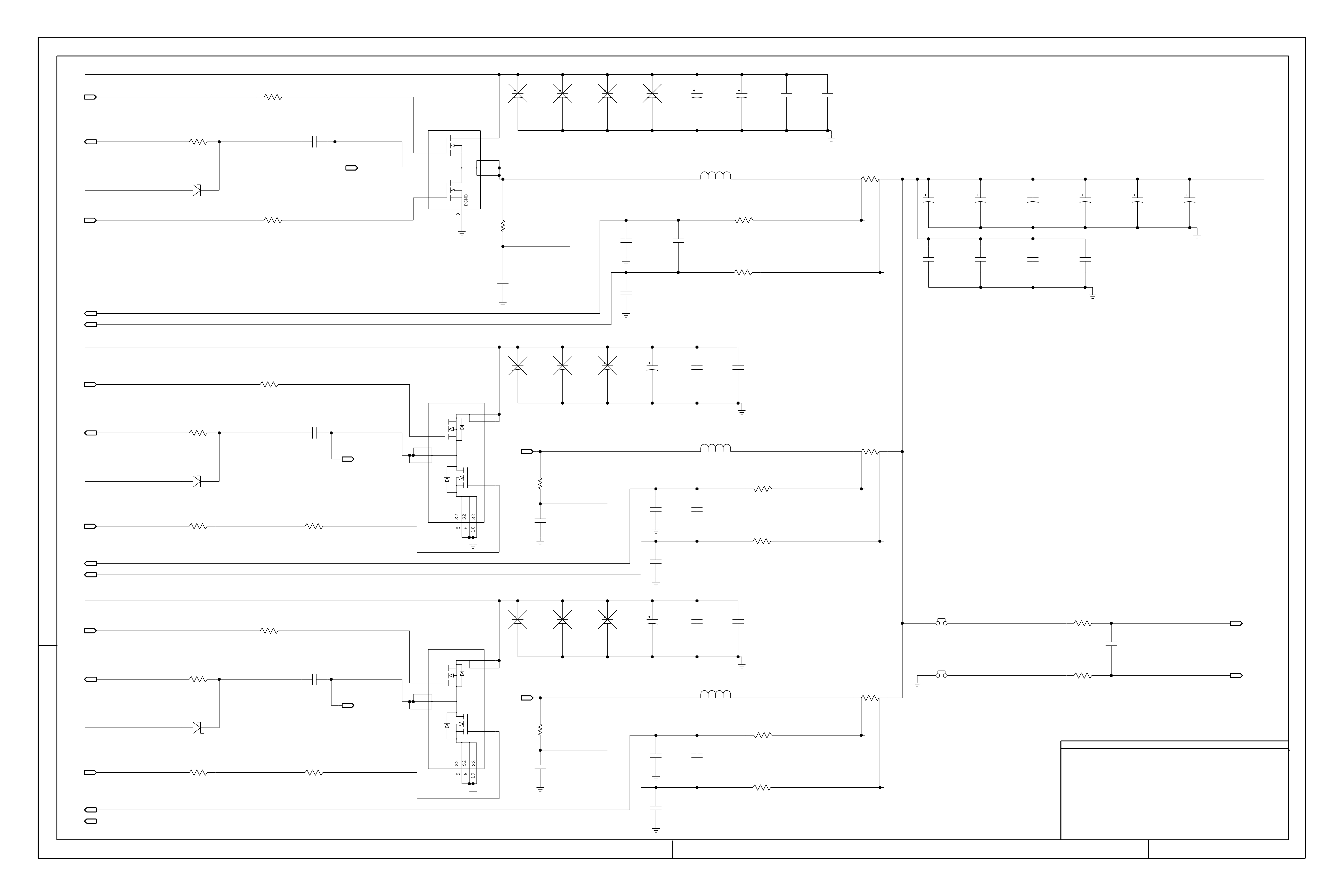

STORAGE: SSD0 S5E <0>

STORAGE: SSD0 S5E <1>

STORAGE: NON OCARINA SUPPORT

STORAGE: SSD SUPPORT

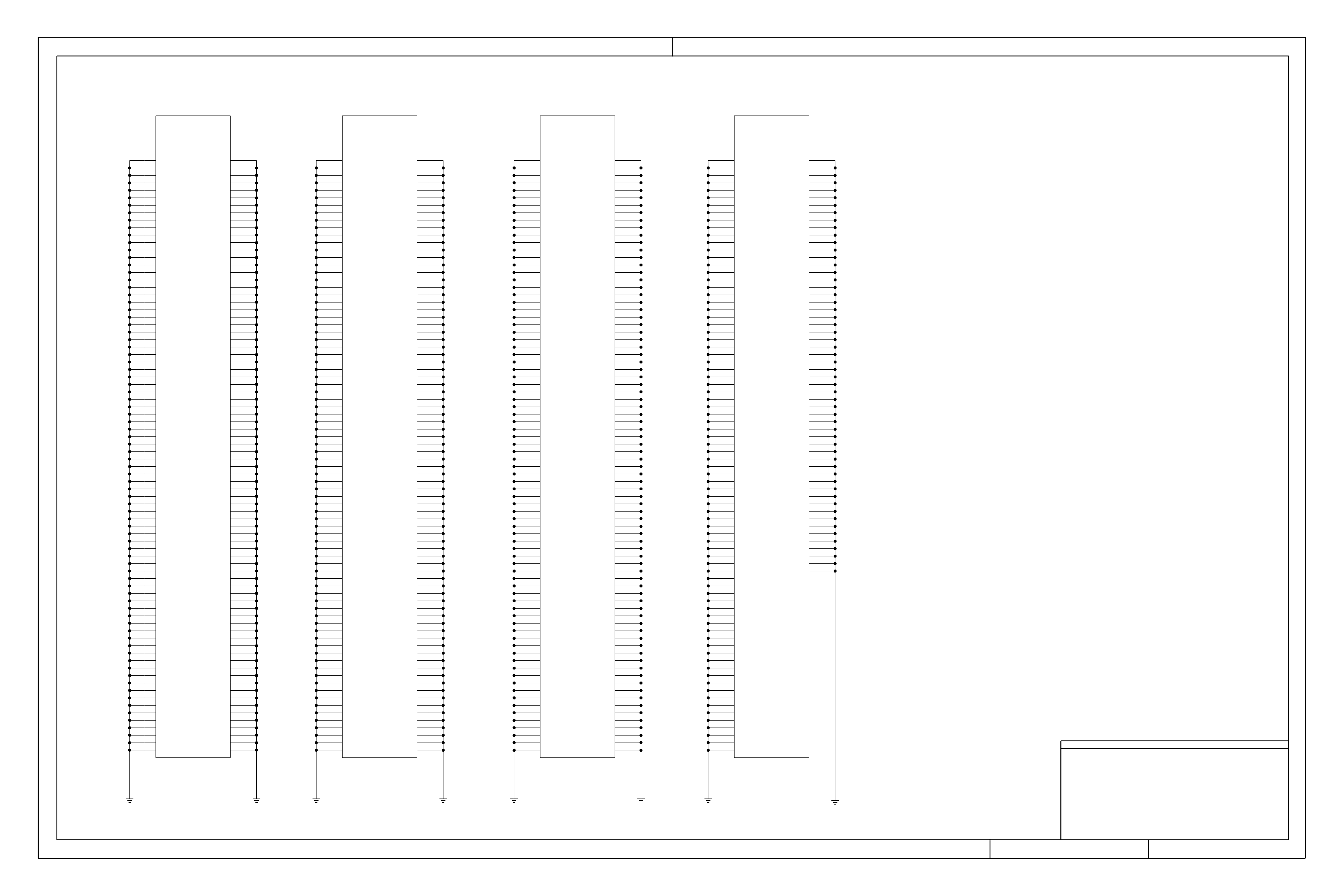

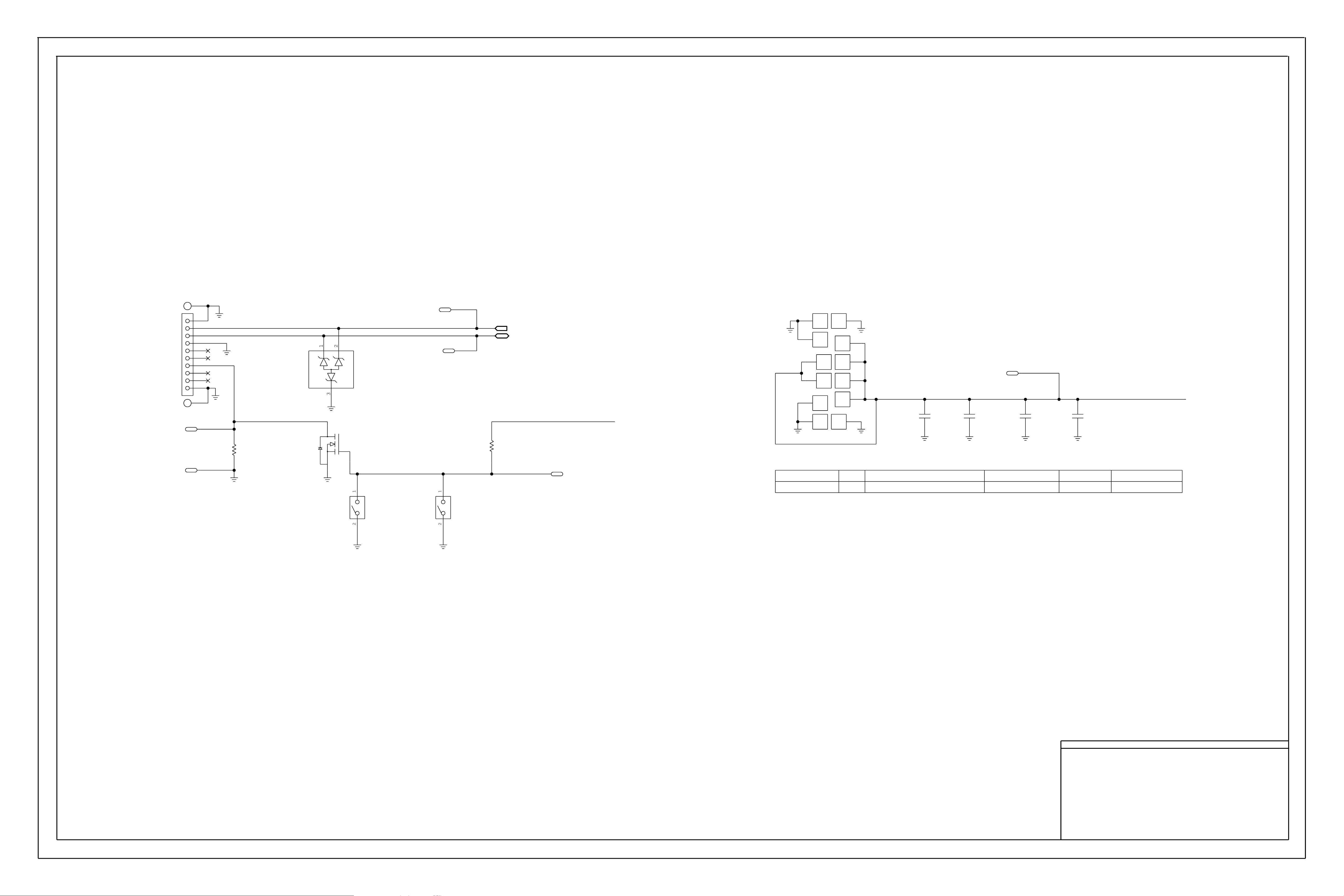

SECDIS: MIPI MUX

DISPLAY: CONNECTOR, PWR

DISPLAY POWER SEQUENCER

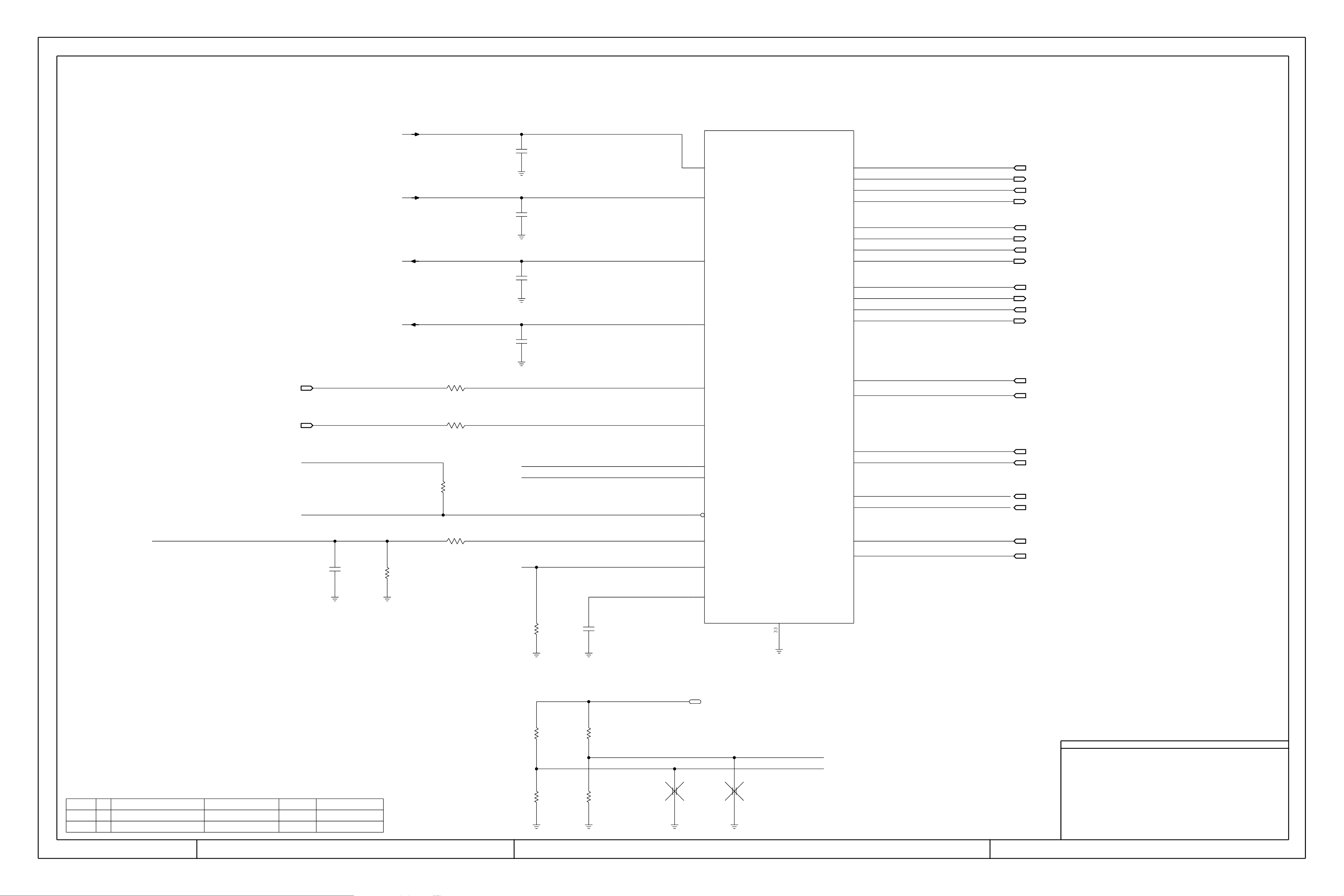

BEN: CONTROLLER

BEN: KEYBOARD

SECDIS: AMR

SECDIS: FPGA

T585_REF_USBC_ACE2_0.23.0

REF_WIRELESS_RASPUTIN

REF_WIRELESS_RASPUTIN

REF_STORAGE_S5E

REF_STORAGE_S5E

REF_STORAGE_NON_OCARINA_SUPPORT

WUDI_T668_MLB

T585_REF_SECDIS_MIPIMUX_0.7.0

AITKEN_T668_MLB

REF_PANELPWR_BNJ

REF_BLC_BEN

REF_BLC_BEN

T585_REF_SECDIS_AMR_0.9.0

REF_SECDIS_SAK

02/01/2020

02/01/2020

04/27/2020

04/27/2020

02/25/2020

01/28/2020

10/02/2019

04/22/2020

11/21/2019

11/21/2019

04/22/2020

15

16

17

18

19

20

21

22

23

24

25

26

27

28

16

17

19

21

SOC: GND

SOC: GND-2

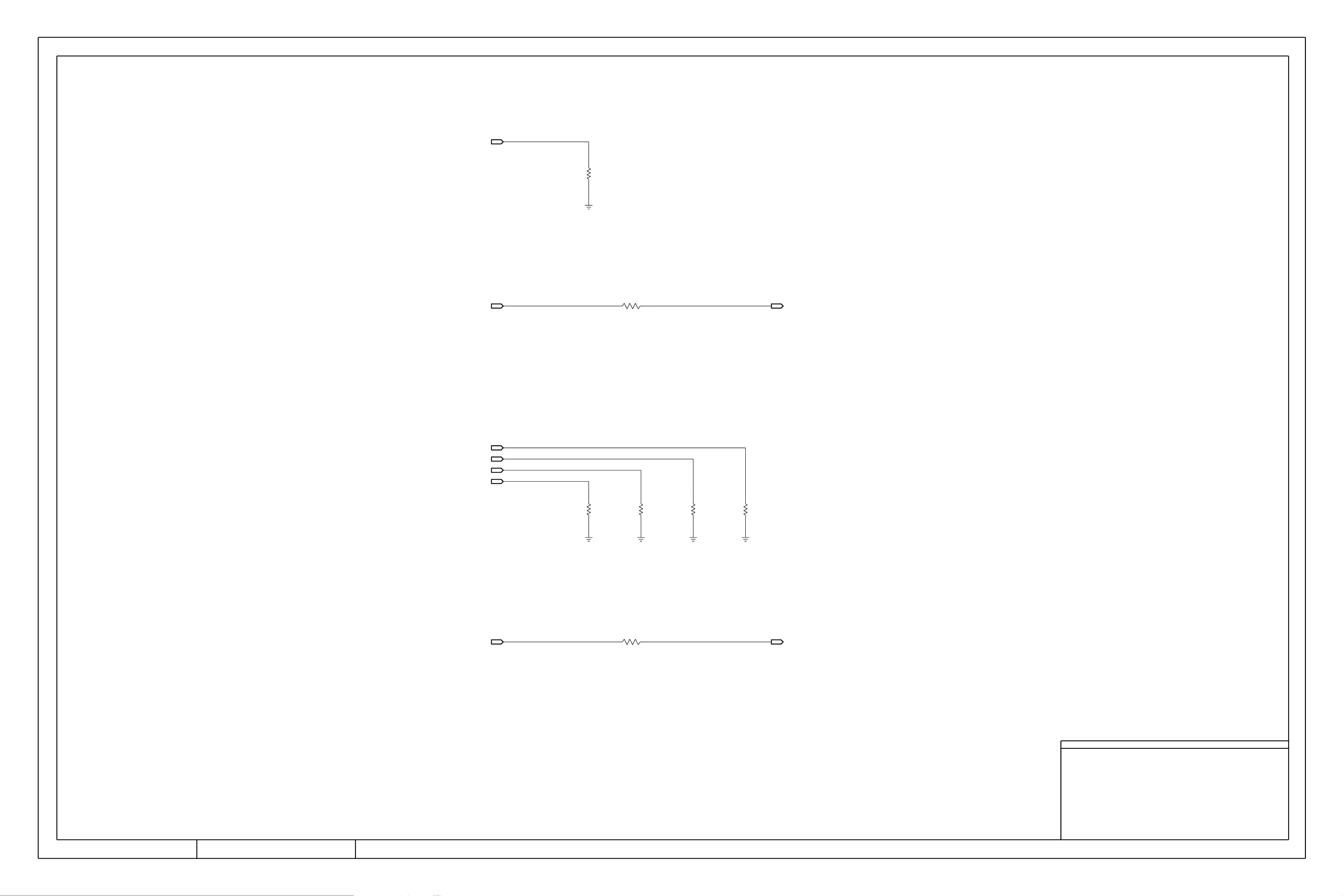

SPI NOR

PROJECT SUPPORT (1/2)

22 PROJECT SUPPORT (2/2)

50

Secure Element

BATTERY CONNECTORS51

52

53

57

58

59

77

78

PBUS SUPPLY & BATTERY CHARGER

BATTERY CHARGER SUPPORT

POWER: 3V8 AON (1/2)

POWER: 3V8 AON (2/2)

POWER: 3V8 AON SUPPORT

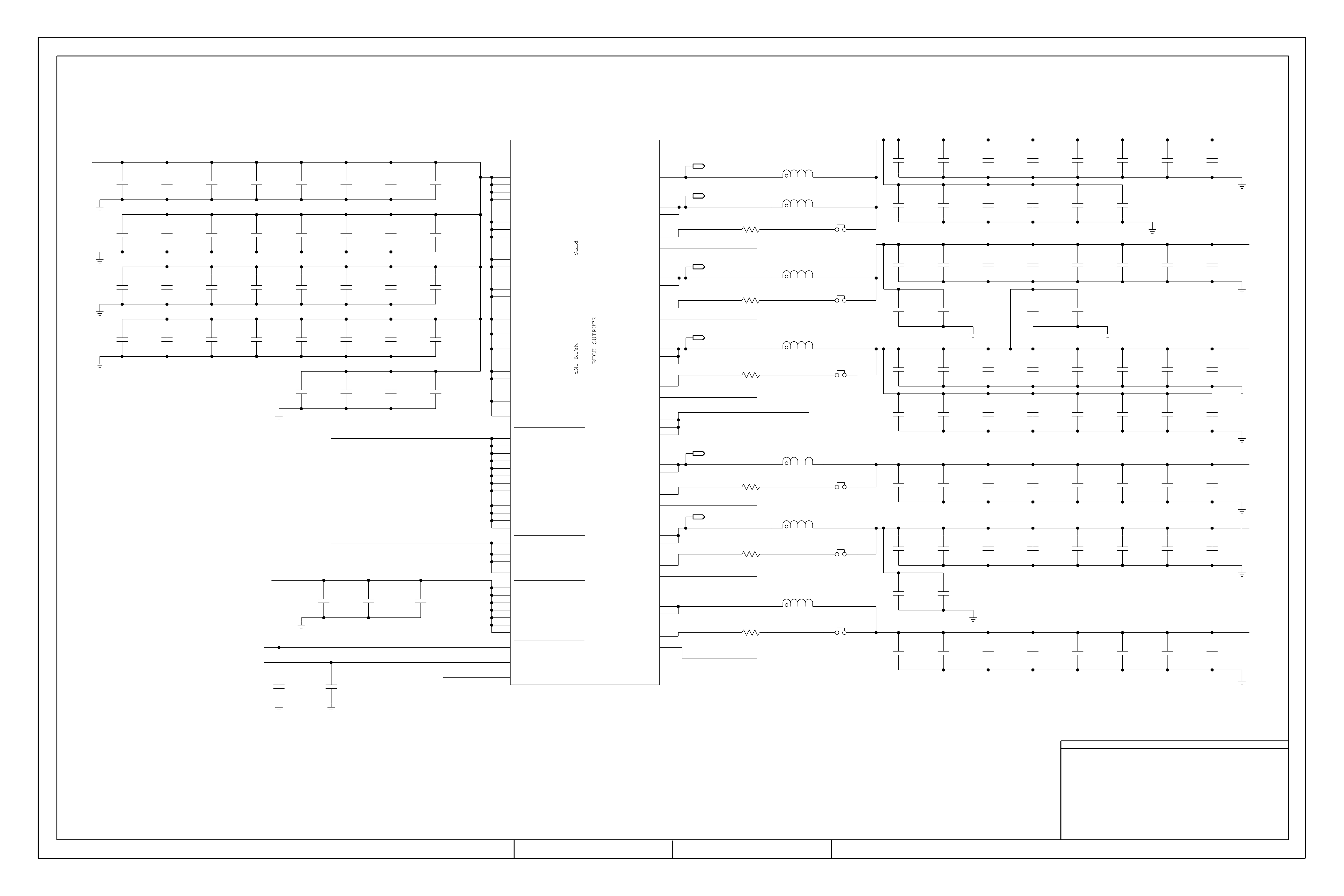

PMU: SLAVE INPUT PWR & BUCKS

PMU: SLAVE LDO

T585_REF_SOC_H13G_0.56.0

T585_REF_SOC_H13G_0.56.0

REF_SOC_H13G

AITKEN_T668_MLB

AITKEN_T668_MLB

REF_SE_CERES

AITKEN_T668_MLB

REF_CHARGER_SUONA

REF_CHARGER_SUONA

REF_VR_ICEMAN

REF_VR_ICEMAN

T585_REF_VR_ICEMAN_0.36.0

KEI_T668_MLB

KEI_T668_MLB

01/27/2020

09/18/2019

11/11/2019

02/26/2020

09/18/2019

02/25/2020

04/01/2020

04/09/2020

03/30/2020

04/07/2020

75

77

78

79

80

244

246

247

248

249

25081

82

83

84

85

86

251

252

253

254

256

87 DFR SUPPORT 125704/07/2020

88 258

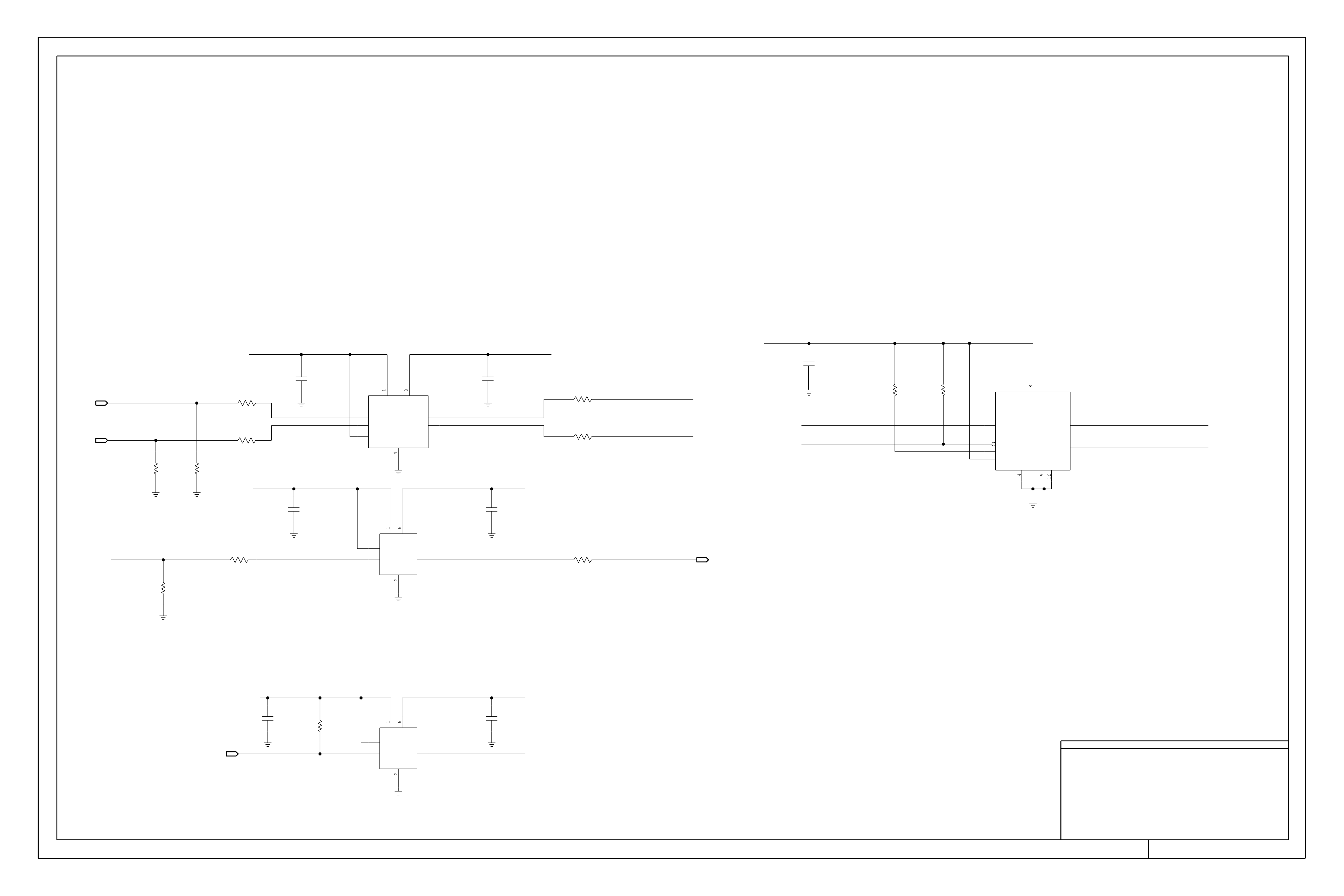

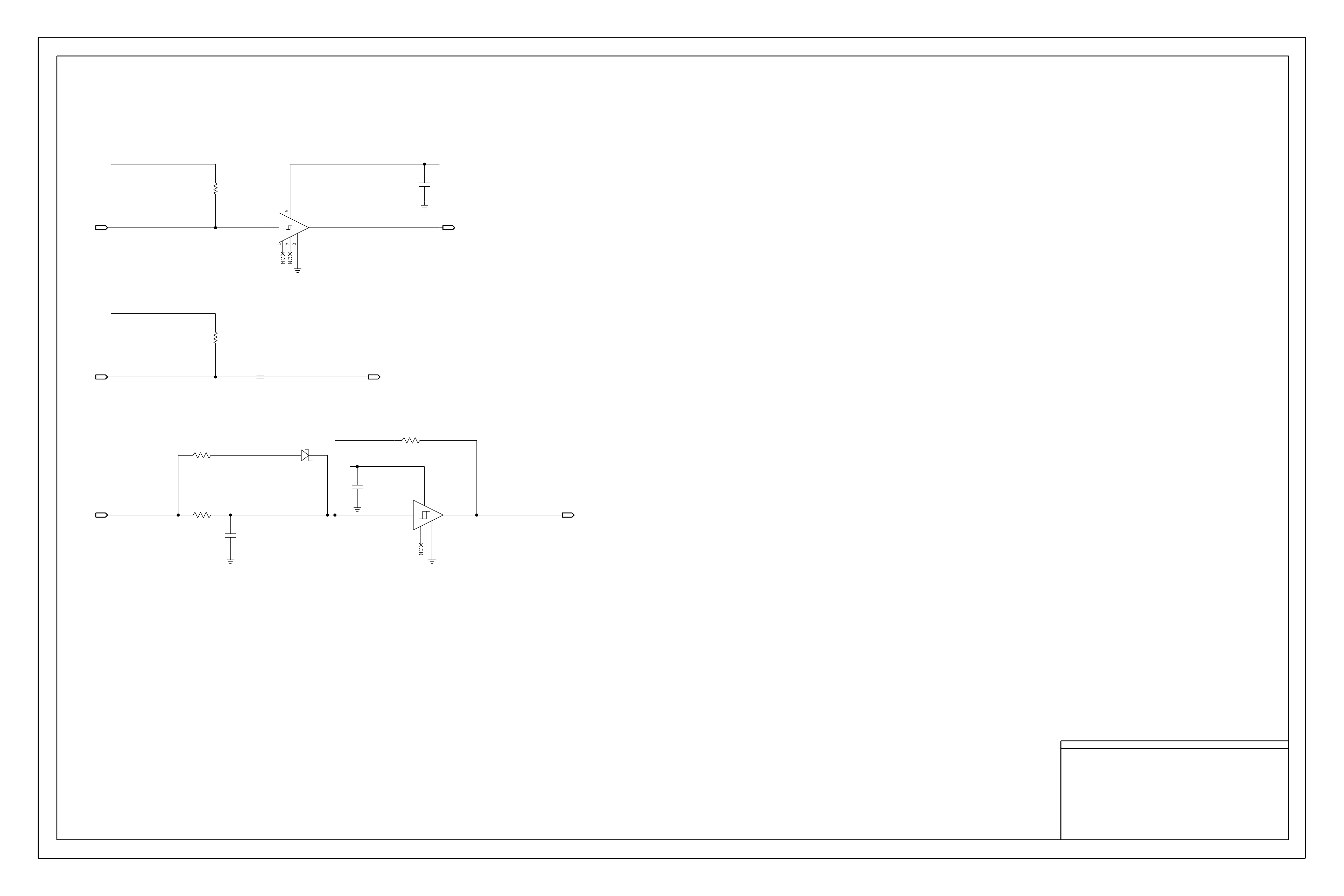

AUDIO SUPPORT

AUDIO JACK CODEC24576

AUDIO AMPLIFIERS (1/2)

AUDIO AMPLIFIERS (2/2)

AUDIO CONNECTORS: AMPS

AUDIO CONNECTORS: DMIC, JACK

KEYBOARD BLC CONNECTORS

KEYBOARD IOX, SUPPORT

KEYBOARD SIGNAL CONNECTOR, ESD

TRACKPAD SUPPORT

TRACKPAD CONNECTOR

TOUCHID SUPPORT

DFR SUPPORT 2

REF_SPKRAMP_TAS5770

REF_CODEC_CLIFDEN

REF_SPKRAMP_TAS5770

REF_SPKRAMP_TAS5770

KELVIN_T668_MLB

KELVIN_T668_MLB

T668_MLB

REF_KBD_SUPPORT

WUDI_T668_MLB

WUDI_T668_MLB

WUDI_T668_MLB

T585_REF_MESA_SUPPORT_0.11.0

T585_REF_DFR_V3_SUPPORT_0.25.0

T585_REF_DFR_V3_SUPPORT_0.25.0

04/16/2020

04/13/2020

04/16/2020

04/16/2020

09/18/2019

09/24/2019

05/16/2019

02/01/2020

01/28/2020

04/16/2020

04/16/2020

30

31

32

33

34

35

36

37

38

39

40

41

42

7929

80

81

82

83

84

121

123

124

127

128

129

130

131

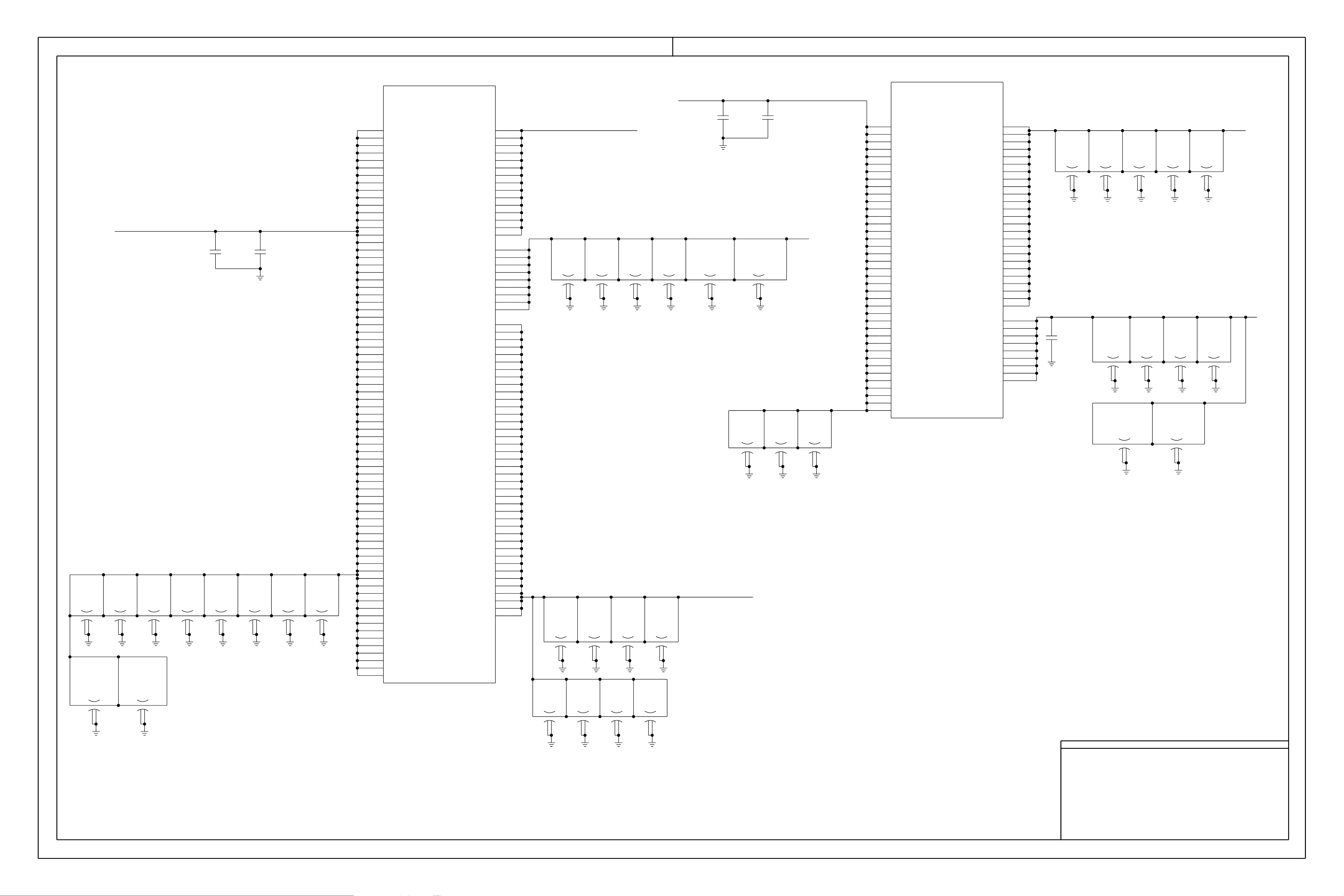

PMU: SLAVE GPIO & GND

PMU: SLAVE SUPPORT

PMU: MASTER INPUT PWR & BUCKS

PMU: MASTER BUCKS & GND

PMU: MASTER LDO & GPIO

PMU: MASTER SUPPORT

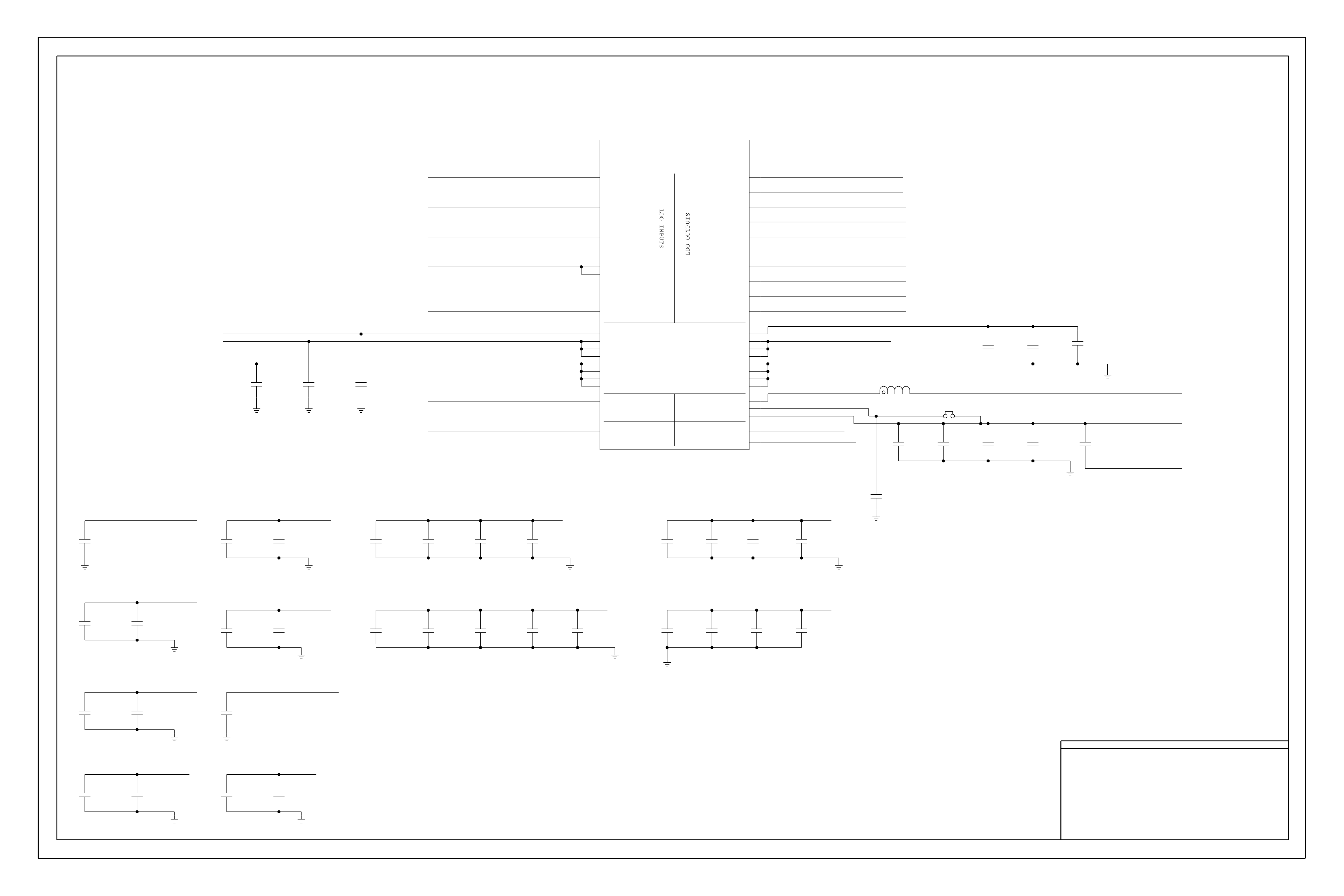

POWER: EXTERNAL LDO

POWER: 5V S2

POWER: 5V S2 SUPPORT

POWER: 3V3 S2

POWER: FETS

POWER: SUPPORT

I2C: SIO, DISP

I2C: ISP, AOP

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

REF_VR_5V_TPS62135

T668_MLB

REF_VR_3V3_TPS62135

KEI_T668_MLB

KEI_T668_MLB

T668_MLB

T668_MLB

04/07/2020

01/27/2020

04/02/2020

04/26/2020

04/23/2020

04/16/2020

09/23/2019

04/16/2020

03/26/2020

01/09/2020

09/10/2019

09/10/2019

06/20/2019

06/20/2019

89

90

91

266

270

271

92 278

93

94

95

96

279

280

282

294

30097

98

301

99 302

100

310 EMC

101

401

FCT

DEBUG: BUTTONS

DEBUG: MISC

DEBUG: LEDS (1/3)

DEBUG: LEDS (2/3)

DEBUG: LEDS (3/3)

DEBUG: P3V8AON ISENSE

DEBUG: VITAMIN-C

DESENSE (1/3)

DESENSE (2/3)

DESENSE (3/3)

POWER ALIASES 1400

POWER ALIASES 2102

KELVIN_T668_MLB

T668_MLB 06/20/2019

T668_MLB

T668_MLB

T668_MLB

T668_MLB

T668_MLB

MANAN_T668_MLB

KEI_T668_MLB

KEI_T668_MLB 09/30/2019

KEI_T668_MLB 09/30/2019

KEI_T668_MLB 10/02/2019

KEI_T668_MLB 11/06/2019

KEI_T668_MLB

01/29/2020

06/20/2019

07/24/2019

07/24/2019

07/24/2019

06/20/2019

02/03/2020

11/04/2019

11/06/2019

43

44

45

46

47

48

49

50

51

52

54

55

56

132

135

136

138

139

140

141

142

144

145

15053

151

152

153

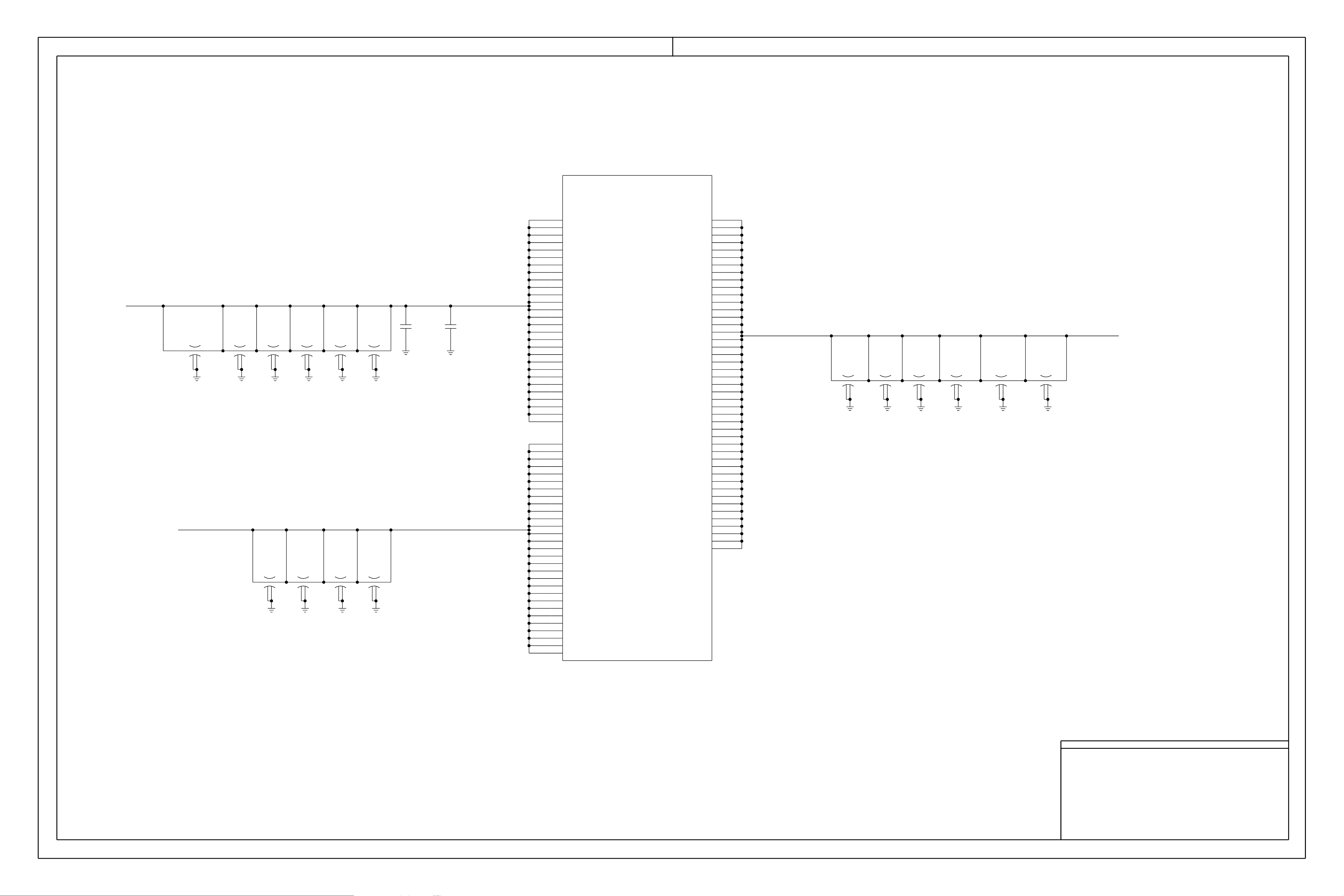

I2C: SMC

SENSORS: POWER HIGH SIDE (1/2)

SENSORS: POWER HIGH SIDE (2/2)

SENSORS: POWER LOW SIDE (1/2)

SENSORS: POWER LOW SIDE (2/2)

SENSORS: POWER SUPPORT

SENSORS: THERMAL (1/2)

SENSORS: THERMAL (2/2)

SENSORS: MOTION

FAN

USB-C: High Speed ATC0

USB-C: High Speed ATC1

USB-C: Support 1 ATC01

USB-C: Support 2 ATC01

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

KEI_T668_MLB

WUDI_T668_MLB

AITKEN_T668_MLB

REF_USBC_ACE2

REF_USBC_ACE2

REF_USBC_ACE2

REF_USBC_ACE2

12/20/2019

04/04/2020

03/10/2020

03/10/2020

01/23/2020

02/04/2020

04/02/2020

01/23/2020

09/23/2019

09/18/2019

02/14/2020

02/14/2020

02/01/2020

02/01/2020

103

104

105

107

108

109

110

111

112

113

114

115

116

402

403

404

405106

406

500

POWER ALIASES 3

POWER ALIASES 4

POWER ALIASES 5

SIGNAL ALIASES 1

SIGNAL ALIASES 2

17.2 RULES

501 17.2 PHYSICAL CSETS

502

503

600

601

17.2 SPACING CSETS, ISO

17.2 SPACING CSETS, CLASS-CLASS

BOM VARIANT TABLES

BOM OPTION TABLES

602

610

BOM ALTERNATES

700

T668_MLB

KEI_T668_MLB

T668_MLB

T668_MLB

T668_MLB

T668_MLB

T668_MLB

06/05/2019

11/06/2019

09/12/2019KEI_T668_MLB

09/18/20 9AITKEN_T668_MLB

05/29/2019

05/13/2019

05/13/2019T668_MLB

05/13/2019

05/13/2019T668_MLB

06/05/2018T668_MLB

06/05/2018T668_MLB

06/05/2018T668_MLB

06/05/2018

06/05/2018

57

58

59

60

154

155

156

157

USB-C: Port Controller ATC0

USB-C: Port Controller ATC1

USB-C: Connector(s)

USB-C: HS Level Shifters

REF_USBC_ACE2

REF_USBC_ACE2

KEI_T668_MLB

REF_USBC_ACE2

02/01/2020

02/01/2020

02/01/2020

02/04/2020

117

999

CHECKPLUS SUPPORT

08/29/2019T668_MLB

Page 2

D

www.teknisi-indonesia.com

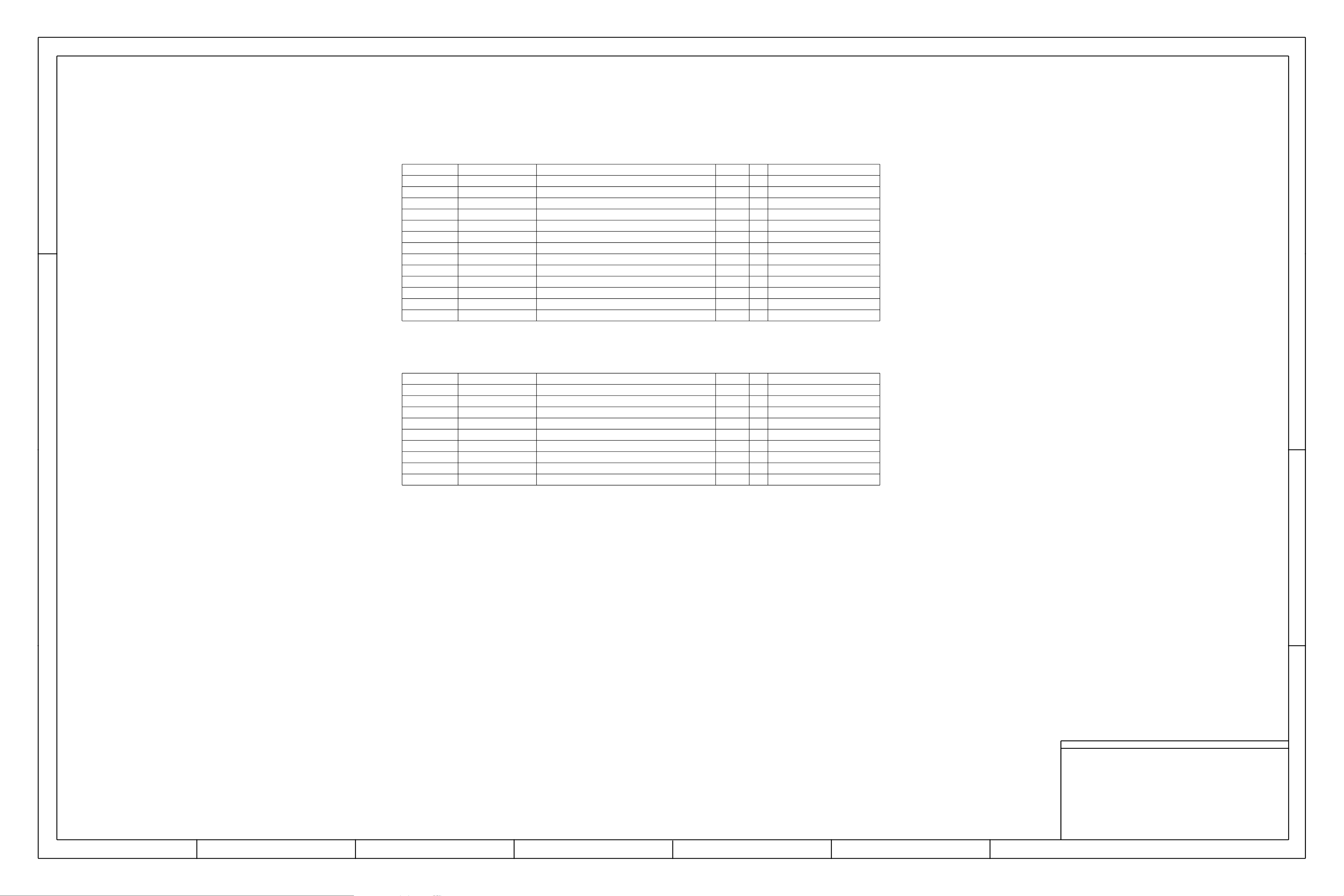

REFERENCE DESIGNS J293 SYNCS FROM

SUB-DESIGN PAGESSUB-DESIGN NAMESOURCE PROJECT VERSION SYNC_DATE/TIME

T585 REF_VR_ICEMAN 57,58 1.14.0

T585 52,53REF_CHARGER_SUONA

224

T585 0.8.0

REF_VR_3V3_TPS62135

REF_SECDIS_MIPIMUX 231T585

REF_DFR_V3_SUPPORTT585 257,258

T585 50

T585 237REF_PANELPWR_BNJ 0.9.0

REF_SE_CERES

REF_SECD S_ AK 243 40.0

244,246,247REF_SPKRAMP_TAS5770

123T585

0.36.0

0.5.0T585 REF_STORAGE_NON_OCARINA_SUPPORT

1.6.0245T585

0.8.0T585 127

0.13.0REF_VR_5V_LT8642S

0.7.0

0.25.0

0.13.0

0.34.0T585 220,221REF_STORAGE_S5E

HARD/

SOFT

2020/04/27

2020/04/27

2020/04/27

2020/04/27

2020/04/27

2020/04/27

2020/04/27

2020/04/27

2020/04/27

2020/04/27

2020/04/27

2 20/04/27

2020/04/27

REFERENCE DESIGNS NO LONGER SYNCS FROM

SUB-DESIGN P G SSUB-DES GN N MESOUR E PROJECT VERSION YNC_DATE/TIME

5-17,19T585 REF_SOC_H13G

T585 REF_PMU_SERA_SIMETRA 77-79,81-83

T585 238,239REF_BLC_BEN

T585 294REF DEBUG_STUFF

T585 242REF_SECDIS_AMR

150-155,157REF_USBC_ACE2T 85

200-201T585 REF_WIRELESS_ ASPUTIN

REF_MESA_SUPPORT 256T585

REF_KBD_SUPPORT 251T585

HARD/

SOFT

<-- WE STOPPED SYNCING SOC AT 0.56.0 DUE TO REF DESIGN DESENSE CAP ADDITIONS CONFLICTING WITH DESENSE TEAM'S REQUESTS FOR J293

<-- WE STOPPED SYNCING PMU AT 0.57.0 DUE TO SLOW UPDATES AND REF DESIGN IS OFF GRID

<-- WE STOPPED SYNCING BLC AT 0.16.0 TO RELAX PLACE NEARS

<-- WE STOPPED SYNCING VITAMIN C AT 0.1.0 SINCE THE REF DESIGN IS INCOMPLETE ND MANY CHANGES ARE NEEDED TO SUPPORT VIT C MK II

<-- WE STOPPED SYNCING AMR REF SINCE THE REF HAS A DIFFERENT APN FOR AMR FOOTPRINT THAN PD USES IN J293'S MCO

<-- WE STOPPED SYNCING USB AT 0.31.0 AS THE 50V CC CAPS WHICH ARE 2.8X MORE EXPENSIVE THAN THE 25V ONES, ALSO LSF0 02 COMBO ADDED

<-- WE STOPPED SYNCING RASPUTIN TO ADD RF CONN BOM OPT ON, CHANGE 100M CLK TPS TO PPS, AND FIX OVERLAPPING IPU TEXT NOTES

<-- WE STOPPED SYNCING MESA SUPPORT AT 0.11.0 SINCE THE REF DESIGN REMOVED A PULL UP AND WE NEED 1V85 ON THE LDO

<-- WE STOPPED SYNCING KBD AT 0.25.0 TO FIX CREF GENERATION ERROR ON PIN Y8

REFERENCE DESIGNS WHERE NET NUDGE WAS NEEDED TO REMOVE CREFER ERRORS

S5E, USBC, SECDIS SAK

B

SYNC_MASTER T668_MLB SYNC_DA E=07/17/2019

PAGE TITLE

A

REFERENCE DESIGN SYNC TABLES

678

35 4

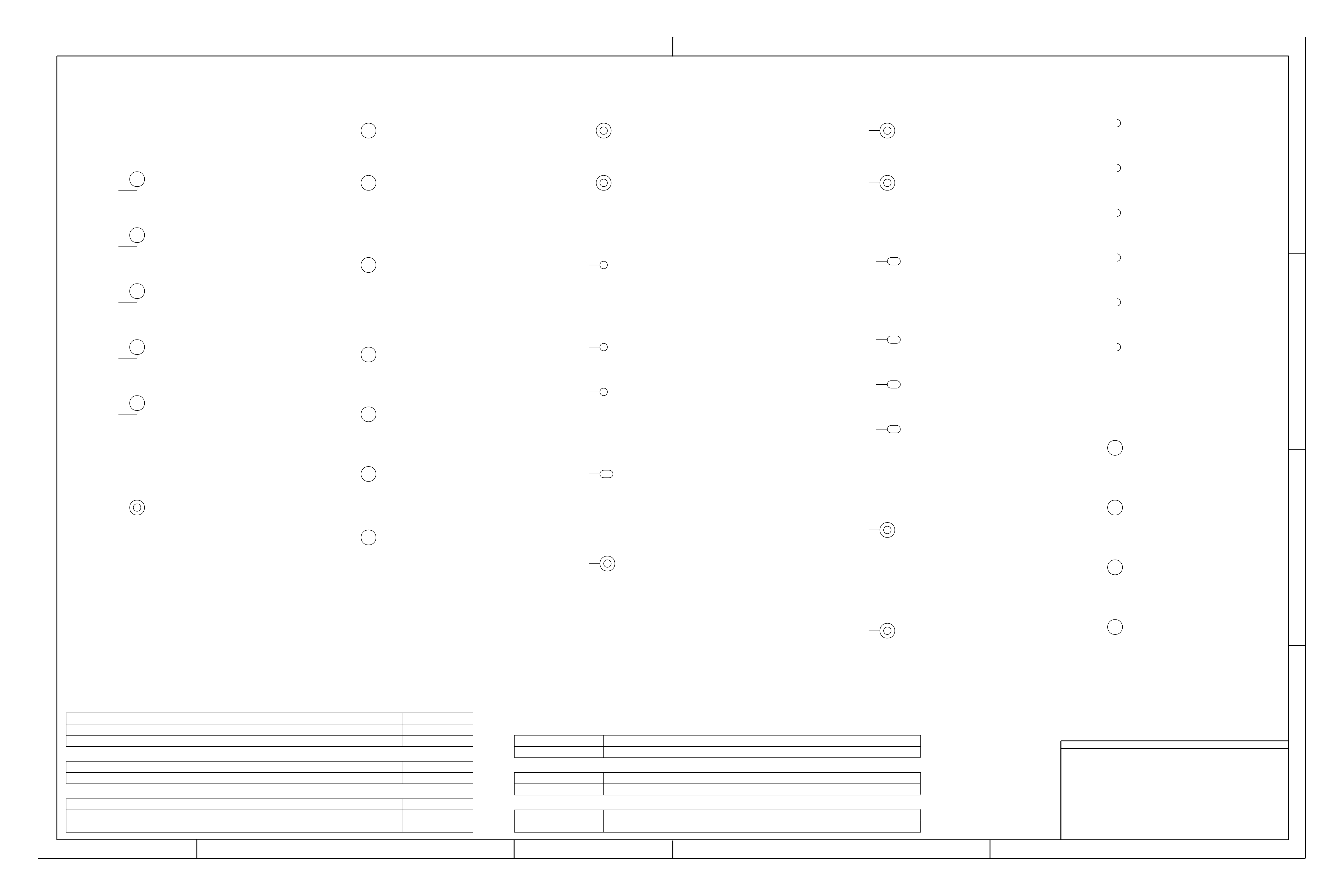

Page 3

3 24

www.teknisi-indonesia.com

TOP SIDE STANDOFFS

ALLOW_APPLE_PREFIX=Z

Z0400

2.8OD1.2ID-1.49H-SM

860-01216

CRITICAL

ALLOW_APPLE_PREFIX=Z

Z0401

2.8OD1.2ID-1.49H-SM

860-01216

CRITICAL

ALLOW_APPLE_PREFIX=Z

Z0402

2.8OD1.2ID-1.49H-SM

860-01216

CRITICAL

ALLOW_APPLE_PREFIX=Z

Z0403

2.8OD1.2ID-1.49H-SM

USB-C BOSS

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0420

3.4OD1.75ID-1.12H-SM

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0421

3.4OD1.75ID-1.12H-SM

DFR BOSS

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0430

3.4OD1.75ID-1.5H-SM

860-00392

860-00392

860-01484

TRACKPAD BOSS

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0440

3.5OD1.85ID-1.41H-SM

860-00381

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0441

3.5OD1.85ID-1.41H-SM

860-00381

CPU THERM STAGE HOLE 3.15 MM

OMIT

CRITICAL

ZT0400

3P9R3P15

998-0845

CORNER NEAREST KEYBOARD

DISPLAY BOSS

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0450

2.7X1.8R-1.4ID-0.84H-SM

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0451

2.7X1.8R-1.4ID-0.84H-SM

FAN MTG HOLE 2.0X2.6 MM

OMIT

ALLOW_APPLE_PREFIX=ZT

CRITICAL

ZT0430

TH-NSP

1

SL-2.6X2.0-4.7X4.1

SHIELD CAN ALIGNMENT HOLES

OMIT

ALLOW_APPLE_PREFIX=Z

Z04A0

TH-NSP

SL-1.2X0.4-1.5X0.7

OMIT

ALLOW_APPLE_PREFIX=Z

Z04A1

TH-NSP

SL-1.2X0.4-1.5X0.7

OMIT

ALLOW_APPLE_PREFIX=Z

Z04A2

TH-NSP

SL-1.2X0.4-1.5X0.7

OMIT

ALLOW_APPLE_PREFIX=Z

Z04A3

TH-NSP

SL-1.2X0.4-1.5X0.7

OMIT

ALLOW_APPLE_PREFIX=Z

998-04440

998-04440

998-04440

998-04440

D

CRITICAL

ALLOW_APPLE_PREFIX=Z

Z0404

2.8OD1.2ID-1.49H-SM

CRITICAL

ALLOW_APPLE_PREFIX=Z

Z0405

2.8OD1.2ID-1.49H-SM

CRITICAL

860-01216

860-01216

860-01216

BOTTOM SIDE STANDOFFS

ALLOW_APPLE_PREFIX=Z

Z0410

2.8OD1.2ID-3.15H-SM

860-01485

CRITICAL

ALLOW_APPLE_PREFIX=Z

Z0411

2.8OD1.2ID-3.15H-SM

860-01485

CRITICAL

CPU THERM STAGE HOLES 3.6 MM

OMIT

CRITICAL

ZT0401

4.0R3.6-NSP

998-03850

OMIT

CRITICAL

ZT0402

4.0R3.6-NSP

998-03850

CPU THERM STAGE HOLE OVAL

MLB MTG HOLES 2.1X3.51 MM

OMIT

ALLOW_APPLE_PREFIX=ZT

CRITICAL

ZT0420

TH-NSP

1

SL-2.1X3.51-4.6X6.01

OMIT

ALLOW_APPLE_PREFIX=ZT

CRITICAL

ZT0421

TH-NSP

1

SL-2.1X3.51-4.6X6.01

OMIT

ALLOW_APPLE_PREFIX=ZT

CRITICAL

ZT0422

TH-NSP

1

SL-2.1X3.51-4.6X6.01

Z04A4

TH-NSP

SL-1.2X0.4-1.5X0.7

OMIT

ALLOW_APPLE_PREFIX=Z

Z04A5

TH-NSP

SL-1.2X0.4-1.5X0.7

POGO PINS

ALLOW_APPLE_PREFIX=PP

PP0400

POGO-2.3OD-4.0H-SM

SM-1

998-04440

998-04440

C

DFR WASHER

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0431

4.75OD2.73ID-H0.2

RING-TH

860-01519

ALLOW_APPLE_PREFIX=Z

Z0412

2.8OD1.2ID-3.15H-SM

CRITICAL

ALLOW_APPLE_PREFIX=Z

Z0413

2.8OD1.2ID-3.15H-SM

CRITICAL

860-01485

860-01485

OMIT

CRITICAL

ZT0403

TH-NSP

SL-3.65X3.15-4.5X4.0

ALLOW_APPLE_PREFIX=ZT

998-21974

WIFI COAX STANDOFF

CRITICAL

Z0498

5.25X2.8R-1.4ID-1.5H-SM

860-01704

ALLOW_APPLE_PREFIX=Z

WIFI WASHER

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0432

4.75OD2.73ID-H0.2

RING-TH

AJ FLEX COWLING BOSS

ALLOW_APPLE_PREFIX=Z

CRITICAL

Z0470

3.5OD1.85ID-1.92H-SM

ALLOW_APPLE_PREFIX=PP

PP0401

POGO-2.3OD-4.0H-SM

SM-1

ALLOW_APPLE_PREFIX=PP

PP0402

POGO-2.3OD-4.0H-SM

SM-1

ALLOW_APPLE_PREFIX=PP

PP0403

POGO-2.3OD-4.0H-SM

SM-1

870-09667

870-09667

B

870-09667

FENCE SPMU

FENCE COMBO

CRITICALPART NUMBER REFERENCE DESDESCRIPTION

FENCE,SPMU,X1727 FENCE_SPMU_C770806-24457 FENCE_SPMU CRITICAL

CRITICALPART NUMBER REFERENCE DESDESCRIPTION

870-09667

LANDING CLIP

FENCE_SPMU_SUSFENCE,SPMU,SUS,SBP,X1727806-24550 FENCE_SPMU CRITICAL

CRITICALPART NUMBER BOM OPTIONREFERENCE DESDESCRIPTION

CL P:YESCLIPCLIP,LAND NG,MLB,X1727806-25216 CRITICAL

PAGE TITLE

A

PD PARTS

LANDING CLIP SMALL

FENCE_COMBOFENCE_COMBOFENCE,COMBO,X1727806-24549 CRITICAL

CRITICALPART NUMBER BOM OPTIONREFERENCE DESDESCRIPTION

FENCE USBC

CRITICALPART NUMBER REFERENCE DESDESCRIPTION

FENCE_USBC_C770CRITICAL806-24455 FENCE_USBCFENCE,BURNSIDE BRIDGE,X1727

CRITICALFENCE_USBC806-24548 FENCE,BURNSIDE BRIDGE,SUS,SBP,X1727 FENCE_USBC_SUS

CLIP_SMALL:YESCLIP_SMALLCLIP,LANDING,SMALL,MLB,X1727806-25217 CRITICAL

METAL SLED

CRITICALPART NUMBER BOM OPTIONREFERENCE DESDESCRIPTION

SLED,METAL,X1727 SLED1,SLED2 CRITICAL SLED:YES806-24419

BOM_COST_GROUP=MECHANICALS

34

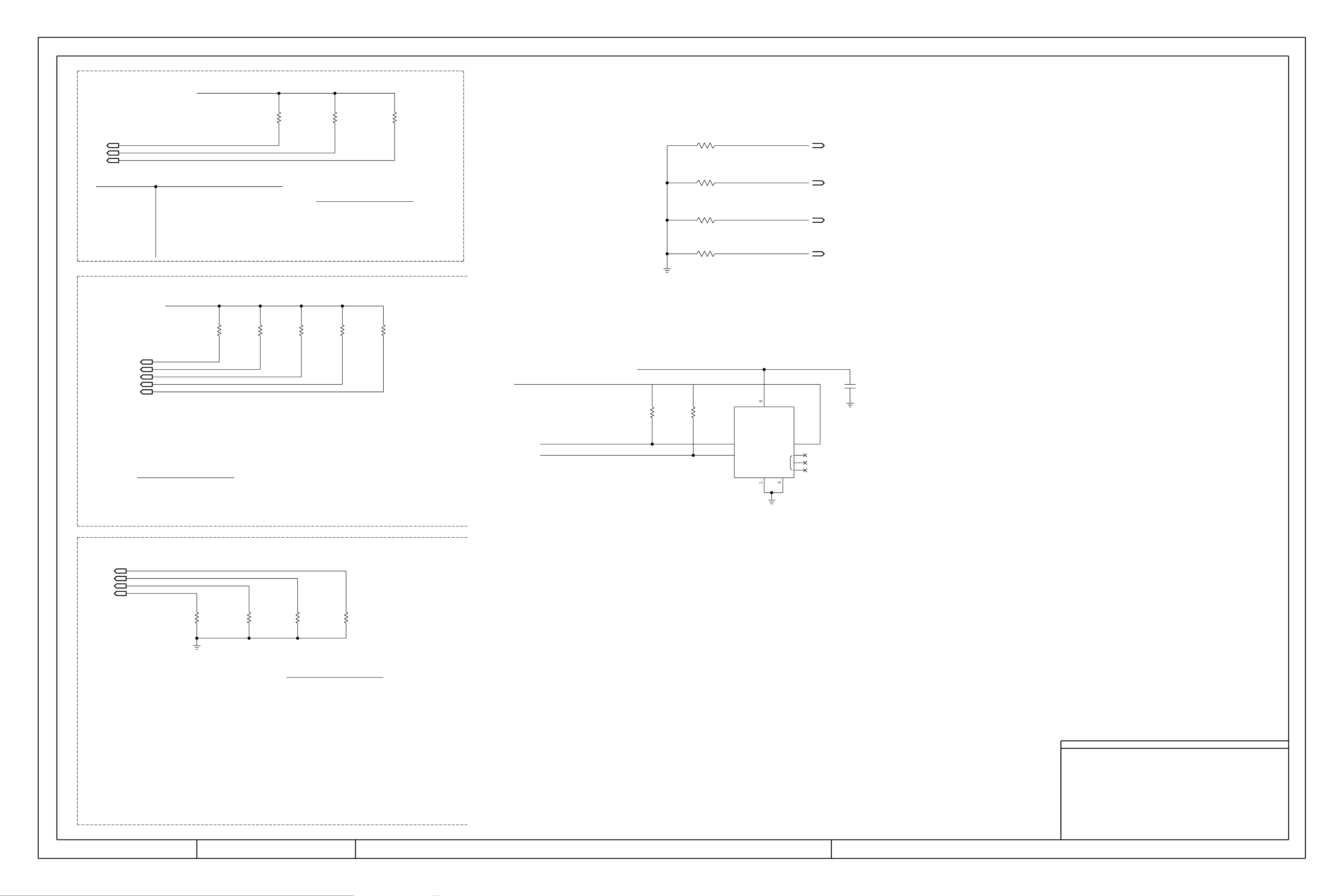

Page 4

BOOT CONFIG ID

www.teknisi-indonesia.com

688

618

618

SPI_DFR_MISO

OUT

SPI_DFR_MOSI_R

OUT

SPI_DFR_CLK_R

OUT

BOOT_CFG[2:0]

000

001

010

011

POR ---> 100

101

110

111

102 11 8 6 5 4

PP1V25_AWAKE_IO

MODE

SPI1 NOR (12 MHZ)

SPI1 NOR (12 MHZ) TESTMODE

SPI0 NAND

SPI0 NAND TESTMODE

SPI1 NOR (40 MHZ)

SPI1 NOR (40 MHZ) TESTMODE

SPI1 NOR (6 MHZ)

SPI1 NOR (6MHZ) TESTMODE

BOOT_CONFIG2 BOOT_CONFIG1 BOOT_CONFIG0

1

R0502

4.7K

5%

1/20W

MF

201

2

1

R0501

4.7K

5%

1/20W

MF

201

2

S/W READ FLOW

1. SET GPIO AS INPUT

2. DISABLE PU AND ENABLE PD

3. READ

1

R0500

4.7K

5%

1/20W

MF

20

2

R0533

10K

5%

1/20W

MF

201

R0534

10K

5%

1/20W

MF

201

R0535

10K

5%

1/20W

MF

201

R0536

10K

5%

1/20W

MF

201

21

SOC_JTAG_SEL

21

SOC_TESTMODE

SOC_HOLD_RESET

21

21

SOC_KIS_DFU_SELECT

OUT

OUT

OUT

OUT

9 18

5

5

5

BOARD ID

2 11 8 6 5 4

6

6

6

6

6

BOARD_ID[7:0] IS 8 TOTAL BITS

BOARD_ID[7:5] ARE SET INSIDE THE SOC

BOARD_ID[4:0] ARE SET WITH THESE RESISTORS

BOARD_ID[0] IS 0 FOR FORM FACTOR AND 1 FOR DEV PLATFORM

BOARD_ID[7:0] FOR J293 IS 0B00100100

<RDAR://53744986>

BOARD_ID4

OUT

BOARD_ID3

OUT

BOARD_ID2

OUT

BOARD_ID1

OUT

BOARD_ID0

OUT

S/W READ FLOW

PP1V25_AWAKE_IO

BOARDID4

1

2

R0514

1K

5%

1/20W

MF

201

1

R0513

1K

5%

1/20W

MF

201

2

BOARDID2BOARDID3

1

R0512

1K

5%

1/20W

MF

201

2

BOARDID1 BOARDID0

1

R0511

1K

5%

1/20W

MF

201

2

1

R0510

1K

5%

1/20W

MF

201

2

PP1V25_AWAKE_IO

I2C_SEEPROM_SCL

6

I2C_SEEPROM_SDA

6

SEP EEPROM (128-Kbit)

PP1V8_AWAKE

1

R0540

2.2K

5%

1/20W

MF

201

2

(Write: 0xA2, Read 0xA3)

A1 PER <RDAR://590 9073>

1

R0541

2.2K

5%

1/20W

MF

201

2

7

SCL

6

SDA

VCC

U0500

STOCT

DFN

335S00488

VSS EPAD

VIO

NC

1

C0500

1.0UF

20%

4V

2

X6S

0201

5

2

NC

3

NC

4

NC

1. SET GPIO AS INPUT

2. DISABLE PU AND ENABLE PD

3. READ

BOARD REVISION

6

OUT

OUT

6

OUT

6

OUT

BOARD_REV0

BOARD_REV1

BOARD_REV2

BOARD_REV3

NOTE: STUFFING RESISTOR MEANS 0

BOARD_REV3

1

R0523

1K

5%

1/20W

MF

201

2

BOARD_REV2

1

R0522

1K

5%

1/20W

MF

201

2

BOARD_REV1

1

R0521

1K

5%

1/20W

MF

201

2

BOARD_REV0

1

R0520

1K

5%

1/20W

MF

201

2

board rev should start at 0b0000 and increment each rev.

S/W READ FLOW

1. SET GPIO AS INPUT

2. ENABLE PU AND DISABLE PD

3. READ

J293 BOARD_REV [3:0] = 0000 : PRE P1

0001 : P1 A0

0010 : P1 A1

0011 : P1 A1 AUDIO

0100 : P2

0101 : EVT

PAGE TITLE

SOC: Support

BOM_COST_GROUP=SOC

378

Page 5

SOC: CIO, USB, DRAM, RESETS, CLOCKS, SWD, FPWM

www.teknisi-indonesia.com

OMIT_TABLE

U0600

TMLR68A0-B09

BGA

SYM 1 OF 23

933748990100

IN

533568990

4

IN

335589

IN

4

IN

PMU_RESET_L

SOC_FORCE_DFU

SOC_REQUEST_DFU1

519

SOC_REQUEST_DFU2

5

SOC_TESTMODE

PMU_ACTIVE_READY

SOC_HOLD_RESET

R2

AA49

AK55

AJ54

AD

AL54

AC1

LP4_IN_RESET_N

FORCE_DFU

REQUEST_DFU1

REQUEST_DFU2

TESTMODE

CFSB

HOLD_RESET

IPD

IPD

RESET

DFU_STATUS

V51

SOC_DFU_STATUS

OUTIN

19 56 89 94

AMUX_OUT can go to TP or to AMUX_IN on PMU

4

18

BI

18

BI

60

IN

60

OUT

SOC_KIS_DFU_SELECT

IN

EUSB_ATC0_P

EUSB_ATC0_N

CIO_ATC0_LSRX_1V2

CIO_ATC0_LSTX_1V2

SOC_ATC0_USB_RESREF

5

AB49

BB54

BB55

BE18

BE13

BB53

KIS_DFU_SELECT

ATC0_USB_EDP

ATC0_USB_EDM

USB_C0_LSRX

USB_C0_LSTX

ATC0_USB_RESREF

CLOCKS

XI0

XO0

TST_CLKOUT

BE36

BF36

P54

SOC_XTAL24M_IN

SOC_XTAL24M_OUT

TP_TST_CLKOUT

18

SOC_ATCPHY0_RCAL_POS

SOC_ATCPHY0_RCAL_ EG

SOC_ATCPHY1_RCAL_POS

SOC_ATCPHY1_RCAL_NEG

1

R0600

200

1%

1/20W

MF

201

2

1

C0600

10PF

5%

25V

2

C0G

0201

1

R0601

200

1%

1/20W

MF

201

2

1

C0601

10PF

5%

25V

2

C0G

0201

99

1%

MF

201

1

2

24.000MHZ-20PPM-9.5PF-60OHM

OC_24M_O_R

CRITICAL

1

C0650

15PF

5%

50V

2

C0G

0201

1

R0631

10K

5%

1/20W

MF

201

2

CRITICAL

Y0600

1.60X1.20MM

31

42

SOC_FORCE_DFU

5335689905519

CRITICAL

1

C0651

15PF

5%

50V

2

C0G

0201

1

R0632

47K

5%

1/20W

MF

201

2

NC_ATC0_HPD

107

18

BI

18

BI

60

IN

60

OUT

53

BI

53

BI

53

OUT

53

OUT

53

BI

53

BI

53

OUT

53

OUT

53

BI

53

BI

54

BI

54

BI

54

OUT

54

OUT

54

BI

54

BI

54

OUT

54

OUT

EUSB_ATC1_P

EUSB_ATC1_N

CIO_ATC1_LSRX_1V2

CIO_ATC1_LSTX_1V2

SOC_ATC1_USB_RESREF

5

NC_ATC1_HPD

107

USB_VBUS_DETECT

5

USBC_ATC0_D2R_P<1>

USBC_ATC0_D2R_N<1>

USBC_ATC0_R2D_C_P<1>

USBC_ATC0_R2D_C_N<1>

USBC_ATC0_D2R_P<2>

USBC_ATC0_D2R_N<2>

USBC_ATC0_R2D_C_P<2>

USBC_ATC0_R2D_C_N<2>

USBC_ATC0_AUX_P

USBC_ATC0_AUX_N

SOC_ATCPHY0_RCAL_POS

5

SOC_ATCPHY0_RCAL_NEG

5

USBC_ATC1_D2R_P<1>

USBC_ATC1_D2R_N<1>

USBC_ATC1_R2D_C_P<1>

USBC_ATC1_R2D_C_N<1>

USBC_ATC1_D2R_P<2>

USBC_ATC1_D2R_N<2>

USBC_ATC1_R2D_C_P<2>

USBC_ATC1_R2D_C_N<2>

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

V48

BC54

BC55

BD3

BE10

BC53

R48

AG1

BE50

BF50

BC49

BD49

BE48

BF48

BC47

BD47

AY51

AY52

BE52

BF52

BF44

BE44

BD43

BC43

BF46

BE46

BD45

BC45

USB_C0_HPD/TMU_CLK_OUT0

ATC1_USB_EDP

ATC1_USB_EDM

USB_C1_LSRX

USB_C1_LSTX

ATC1_USB_RESREF

USB_C1_HPD/TMU_CLK_OUT1

EUSB_VBUS_DETECT

ATCPHY0_RX0_P

ATCPHY0_RX0_N

ATCPHY0_TX0_P

ATCPHY0_TX0_N

ATCPHY0_RX1_P

ATCPHY0_RX1_N

ATCPHY0_TX1_P

ATCPHY0_TX1_N

ATCPHY0_AUX_P

ATCPHY0_AUX_N

ATCPHY0_RCAL_P

ATCPHY0_RCAL_N

ATCPHY1_RX0_P

ATCPHY1_RX0_N

ATCPHY1_TX0_P

ATCPHY1_TX0_N

ATCPHY1_RX1_P

ATCPHY1_RX1_N

ATCPHY1_TX1_P

ATCPHY1_TX1_N

ATC

SWD

FPW

ANALOGMUX_OUT

SWD_TCK_OUT1

SWD_TMS2

SWD_TMS3

SWD_TMS4

FPWM0/MASTER_SYNC_GEN_0

FPWM1

FPWM2

AL48

AJ1

U54

V54

AH3

V50

Y49

U50

TP_SOC_AMUX_OUT

SWD_NAND0_SWCLK

SWD_NAND0_SWDIO

NC_SWD_TMS3

TP_SWD_TMS4

IPD

WLAN_TIME_SYNC

KBD_BKLT_PWM

TP_FPWM2

102 11 8 6 5 4

PP1V25_AWAKE_IO

SOC_REQUEST_DFU1

OUT

OUT

BI

106

IN

OUT

1

2

18 106

67 107

67 10

62

72

R0630

10K

5%

1/20W

MF

201

R0651

1/20

SOC_REQUEST_DFU2

102 11 8 6 5 4

PP1V25_AWAKE_IO

USB_VBUS_DETECT

5

1

R0639

0

5%

1/20W

MF

0201

2

54

BI

54

BI

USBC_ATC1_AUX_P

USBC_ATC1_AUX_N

SOC_ATCPHY1_RCAL_POS

5

SOC_ATCPHY1_RCAL_NEG

5

BA52

BA51

BF4

BE4

ATCPHY1_AUX_P

ATCPHY1_AUX_N

ATCPHY1_RCAL_P

ATCPHY1_RCAL_N

SOC_ATC0_USB_RESREF SOC_ATC1_USB_RESREF

5 5

R0641

200

1%

1/20W

MF

201

2

1

R0640

200

1%

1/20W

MF

201

2

SYNC_MASTER=AITKEN_T6 8_MLB SYNC_DATE=10/08/2019

PAGE TITLE

A

SOC: CIO, USB, RESETS, CLOCKS, SWD

AB E_ LT_HE D

PART NUMBER

Y0600197S0590 EPSON,24MHZ.XTAL197S0591

Y0600197S0588 TXC,24MHZ,XTAL197S0591

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

AB E_ LT_IT M

AB E_ LT_IT M

BOM_COST_GROUP=SOC

35 46

Page 6

**OK2INTEGRATE**

www.teknisi-indonesia.com

all signals are 1.2 unless otherwise specified.

all signals on this page reference PP1V2_AWAKE_GRP if they are 1.2V

if they are 1.8V they reference PP1V8_AWAKE_GRP

U0600

TMLR68A0-B09

BGA

SYM 3 OF 23

SOC: I/Os

18

UT

18

IN

18

OUT

18

OUT

18

OUT

1

IN

1

OUT

18

OUT

18

OUT

76

IN

18

OUT

18

OUT

TDM_SPKRAMP_L_BCLK_R

TDM_SPKRAMP_L_D2R

TDM_SPKRAMP_L_R2D_R

TDM_SPKRAMP_L_FSYNC_R

NC_SOC_I2S0_MCK

106

TDM_SPKRAMP_R_BCLK_R

TDM_SPKRAMP_R_D2R

TDM_SPKRAMP_R_R2D_R

TDM_SPKRAMP_R_FSYNC_R

NC_SOC_I2S1_MCK

6

TDM_CODEC_BCLK_R

TDM_CODEC_D2R

TDM_CODEC_R2D_R

TDM_CODEC_FSYNC_R

TP_SOC_I2S2_MCK

NC_I2S3_BCLK

106

NC_I2S3_D2R

6

NC_I2S3_R2D

6

NC_I2S3_LRCLK

106

NC_I2S3_MCLK

106

AK4

AJ3

AJ5

AJ4

AK3

AG3

AF3

AG4

AF2

AG2

AK5

AL6

AJ7

AM4

AK6

AH6

AH4

AG5

AJ6

AF5

I2S0_BCLK

I2S0_DIN

I2S0_DOUT

I2S0_LRCK

I2S0_MCK

I2S1_BCLK

I2S1_DIN

I2S1_DOUT

I2S1_LRCK

I2S1_MCK

I2S2_BCLK

I2S2_DIN

I2S2_DOUT

I2S2_LRCK

I2S2_MCK

I2S3_BCLK

I2S3_DIN

I2S3_DOUT

I2S3_LRCK

I2S3_MCK

IPD

IPD

IPD

I2S

SPI

IPD

IPD

IPD

IPD

IPD

SPI0_MISO

SPI0_MOSI

SPI0_SCLK

SPI1_MISO

SPI1_MOSI

SPI1_SCLK

SPI1_SSIN

SPI2_MISO

SPI2_MOSI

SPI2_SCLK

SPI2_SSIN

SPI3_MISO

SPI3_MOSI

SPI3_SCLK

SPI3_SSIN

SPI4_MISO

SPI4_MOSI

SPI4_SCLK

SPI4_SSIN

AL4

AK2

AK1

AD4

AE4

AF4

AE3

AF53

AF54

AF55

AF52

Y1

W1

AB1

AA1

AC4

AB4

AA4

AB3

SPI_DFR_MISO

SPI_DFR_MOSI_R

SPI_DFR_CLK_R

SPI_SOCROM_MISO

SPI_SOCROM_MOSI_R

SPI_SOCROM_CLK_R

SPI_SOCROM_CS_L

SPI_TOUCHID_MISO

SPI_TOUCHID_MOSI_R

SPI_TOUCHID_CLK_R

NC_SOC_SPI2_SSIN

SPI_IPD_MISO

SPI_IPD_MOSI_R

SPI_IPD_CLK_R

SPI_IPD_CS_L

SPI_TCON_MISO

SPI_TCON_MOSI_R

SPI_TCON_CLK_R

SPI_TCON_CS_L

106

IN

OUT

OUT

IN

OUT

OUT

OUT

IN

OUT

OUT

IN

OUT

OUT

OUT

IN

OUT

OUT

OUT

4

4

4

17

17

17

17

80

18

18

84

18

18

84

69

69

69

69

1.8V IO

1.8V IO

41

OUT

1

BI

1

OUT

41

BI

41

OUT

41

BI

41

OUT

41

BI

4

OUT

1

BI

I2C_UPC_SCL

I2C_UPC_SDA

I2C_SPKRAMP_L_SCL

I2C_SPKRAMP_L_SDA

I2C_CODEC_SCL

I2C_CODEC_SDA

I2C_SPKRAMP_R_SCL

I2C_SPKRAMP_R_SDA

I2C_DFR_SCL

I2C_DFR_SDA

NC_SPMI2_CLK

106

TP_SPMI2_DATA

W52

V52

AA48

Y48

AB50

Y50

AF6

AE6

AF50

AG49

AK7

AL7

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

I2C3_SCL

I2C3_SDA

I2C4_SCL

I2C4_SDA

AP_SPMI2_SCLK

AP_SPMI2_SDATA

SPMI

SI2C0_SCL

SEP

THROTTLE

IPU FOR ALL

THROTTLE_TRIGGER

THROTTLE_TRIGGER0/MTR_ADC_DOUT

THROTTLE_TRIGGER1/MTR_ADC_CLKOUT

THROTTLE_TRIGGER2/PLL_DIGOBS_0

THROTTLE_TRIGGER3/PLL_DIGOBS_1

THROTTLE_TRIGGER4

SI2C0_SDA

SSPI0_MISO

SSPI0_MOSI

SSPI0_SCLK

SGPIO0

SGPIO1

SOCHOT1

AC3

AC2

Y5

Y4

AC5

AD5

AD6

AK52

AK53

AL53

AJ55

AJ53

AJ49

DBL_CLICK_DET

DISABLE_STROBE

I2C_SEEPROM_SCL

I2C_SEEPROM_SDA

FTCAM_DISABLE_L

NC_SSPI0_MOSI

DMIC_DISABLE_L

SOC_SOCHOT_L

BUCK1_THERMAL_THROTTLE_L

BUCK0_THERMAL_THROTTLE_L

SOC_THROTTLE_TRIGGER2

PMU_VDDHI_UVWARN_L

PMU_VDDMAIN_UVWARN_L

106

33

IN

74

OUT

4

OUT

BI

74

OUT

74

OUT

6 33 89 91 96 100

OUT

33 34

IN

33 34

IN

19

IN

106

IN

33 34

IN

11 8 5 4

PP1V25_AWAKE_IO

SOC_SOCHOT_L

633899196100

1

R0790

47K

5%

1/20W

MF

201

2

UPC_FORCE_PWR will likely be

removed in the future

TOUCHID_PWR_EN gets

pulled up to S2 on

TOUCHID page

This is OK because

the GPIO is failsafe

PD needed on DFR PAGE

107

107

1 6

106

U0600

TMLR68A0-B09

BGA

SYM 2 OF 23

IN

79

IN

89

7989

IN

OUT

777880

IN

76

IN

55

OUT

UPC_I2C_INT_L

NC_SOC_GPIO01

106

SPKR_ID0

SPKR_ID1

SPKRAMP_RESET_L

SPKRAMP_INT_L

CODEC_INT_L

SWD_UPC_SWCLK

NC_SOC_GPIO08

106

TP_SOC_GPIO09

TP_SOC_GPIO10

4

IN

4

IN

4

IN

4

IN

55

BI

BI

IN

84

OUT

86

IN

8694

OUT

575861

OUT

8788

OUT

94

88106

OUT

IN

BOARD_REV0

BOARD_REV1

BOARD_REV2

BOARD_REV3

NC_SOC_GPIO15

106

NC_SOC_GPIO16

106

SWD_UPC_SWDIO0

TP_SWD_UPC_SWDIO1

DFR_TOUCH_INT_L

IPD_SPI_EN

TOUCHID_INT

TOUCHID_PWR_EN

UPC_FORCE_PWR

DFR_PWR_EN

SPI_DFR CS_L

NC_ENET_SYNC_1588

AJ51

AA50

V53

U53

T53

W53

W50

U52

AC48

R53

R52

N55

AH54

Y52

AA51

R54

AC50

U51

AK50

T52

V49

AJ52

AJ50

AC49

R51

AL49

AF49

GPIO[0]

GPIO[1]

GPIO[2]

GPIO[3]

GPIO[4]

GPIO[5]

GPIO[6]

GPIO[7]

GPIO[8]

GPIO[9]

GPIO[10]

GPIO[11]

GPIO[12]

GPIO[13]

GPIO[14]

GPIO[15]

GPIO[16]

GPIO[17]

GPIO[18]

GPIO[19]

GPIO[20]

GPIO[21]

GPIO[22]

GPIO[23]

GPIO[24]

GPIO[25]

GPIO[26]

IPU

IPU

IPU

IPU

IPU

IPD

IPD

GPIO

UART

IPD

IPD

IPD

IPU

IPU

UART0_RXD

UART0_TXD

UART1_CTSN

UART1_RTSN

UART1_RXD

UART1_TXD

UART2_CTSN

UART2_RTSN

UART2_RXD

UART2_TXD

UART3_CTSN

UART3_RTSN

UART3_RXD

UART3_TXD

UART4_CTSN

UART4_RTSN

UART4_RXD

UART4_TXD

UART6_RXD

UART6_TXD

UART7_RXD

UART7_TXD

AB53

AC53

AC54

AA53

AA54

AC55

W55

Y54

Y53

Y55

AC51

AC52

AF48

AB52

AJ48

AK48

AL52

AL50

AF51

AG50

AM2

AJ2

UART_DEBUGPRT_D2R

UART_DEBUGPRT_R2D

DFR_1V8_TOUCH_RESET_L

DFR_1V8_DISP_RESET_L

DFR_1V8_DISP_INT

BT_TIME_SYNC_1V8

UART_WLAN_D2R_CTS_L

UART_WLAN_R2D_RTS_L

UART_WLAN_D2R

UART_WLAN_R2D

NC_UART3_D2R_CTS_L

NC_UART3_R2D_RTS_L

NC_UART3_D2R

NC_UART3_R2D

NC_UART4_D2R_CTS_L

NC_UART4_R2D_RTS_L

NC_UART4_D2R

NC_UART4_R2D

UART_TCON_HDMI_D2R

UART_TCON_HDMI_R2D

NC_UART7_RXD

NC_UART7_TXD

106

106

106

106

106

106

106

106

106

106

IN

OUT

OUT

OUT

IN

IN

IN

OUT

IN

OUT

IN

OUT

18 56 89

18 56 89

87 88 89

87 88 89

87 8 89

62 63

62

62

62

62

69 89

69 89

1.8V IO

1.8V IO

s UART2 if your wireless module is 1.2V IO

R2D is for desktop only

NAND0_RESET_L

6646567

4

IN

4

IN

4

IN

4

IN

4

IN

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

W49

BOARD_ID0/SOC_DEBUG1

R55

BOARD_ID1/SOC_DEBUG2

T55

BOARD_ID2/SOC_DEBUG3

V55

BOARD_ID3/SPI0_SSIN

U55

BOARD_ID4

OARD ID

NAND

NAND_SYS_CLK0

NAND_SYS_CLK1

SSD_BFH

SSD_RESETN

AG52

AH53

AH51

AG53

NAND0_CLK24M_0_R

NAND0_CLK24M_1_R

NAND_BFH

NAND0_RESET_L

OUT

OUT

OUT

OUT

67

67

64 65 67

6 64 65 67

NOSTUFF

1

R0791

47K

5%

1/20W

MF

201

2

PAGE TITLE

SOC: AP I/Os

BOM_COST_GROUP=SOC

Page 7

**OK2INTEGRATE**

www.teknisi-indonesia.com

SOC: LPDP & MIPI

NC_LPDPRX_AUX0

106

NC_LPDPRX_AUX1

106

NC_LPDPRX_AUX2

106

NC_LPDPRX_AUX3

1 6

NC_LPDPRX_AUX4

106

NC_LPDPRX_AUX5

1 6

NC_LPDPRX_AUX6

106

NC_LPDPRX_AUX7

106

NC_LPDPRX_AUX8

106

NC_LPDPRX_AUX9

106

NC_LPDPRX_AUX10

106

NC_LPDPRX_AUX11

106

NC_LPDPRX_RX_P_0

107

NC_LPDPRX_RX_N_0

107

NC_LPDPRX_RX_P_1

107

NC_LPDPRX_RX_N_1

107

NC_LPDPRX_RX_P_2

107

NC_LPDPRX_RX_N_2

10

NC_LPDPRX_RX_P_3

107

NC_LPDPRX_RX_N_3

107

NC_LPDPRX_RX_P_4

107

NC_LPDPRX_RX_N_4

107

NC_LPDPRX_RX_P_5

107

NC_LPDPRX_RX_N_5

107

NC_LPDPRX_RX_P_6

107

NC_LPDPRX_RX_N_6

107

NC_LPDPRX_RX_P_7

107

NC_LPDPRX_RX_N_7

107

NC_LPDPRX_RX_P_8

107

NC_LPDPRX_RX_N_8

107

AP7

LPDPRX_AUX_D0_P

AR7

LPDPRX_AUX_ _P

AT7

LPDPRX_AUX_D2_P

AV7

LPDPRX_AUX_D3_P

AW7

LPDPRX_AUX_D4_P

AY7

LPDPRX_AUX_D5_P

AP8

LPDPRX_AUX_D6_P

AR8

LPDPRX_AUX_D7_P

AT8

LPDPRX_AUX_D8_P

AV8

LPDPRX_AUX_D9_P

AW8

LPDPRX_AUX_D10_P

AY8

LPDPRX_AUX_ 1_P

AP1

LPDPRX_RX_D0_P

AP2

LPDPRX_RX_D0_N

AR1

LPDPRX_RX_D1_P

AR2

LPDPRX_RX_D1_N

AT1

LPDPRX_RX_D2_P

AT2

LPDPRX_RX_D N

AV1

LPDPRX_RX_D3_P

AV2

LPDPRX_RX_D3_N

AW1

LPDPRX_RX_D4_P

AW2

LPDPRX_RX_D4_N

AY1

LPDPRX_RX_D5_P

AY2

LPDPRX_RX_D5_N

AP4

LPDPRX_RX_D6_P

AP5

LPDPRX_RX_D6_N

AR4

LPDPRX_RX_D7_P

AR5

LPDPRX_RX_D7_N

AT4

LPDPRX_RX_D8_P

AT5

LPDPRX_RX_D8_N

U0600

TMLR68A0-B09

BGA

SYM 4 OF 23

IPD

DISP_SPI_SCLK/DISP_I2C_SCL

DISP_SPI_SSIN/DISP_I2C_SDA

LPDP_TX0P

LPDP_TX0N

LPDP_TX1P

LPDP_TX1N

LPDP_TX2P

LPDP_TX2N

LPDP_TX3P

LPDP_TX3N

LPDP_TX4P

LPDP_TX4N

LPDP_TX5P

LPDP_TX5N

LPDP_AUX_P

LPDP_AUX_N

LPDP_RCAL_P

LPDP_RCAL_N

DISP_HPD

DISP_POL

DISP_SPI_MISO/DWI_CLK

DISP_SPI_MOSI/DWI_DO

DISP_SPMI_SCLK

DISP_SPMI_SDATA

DISP_FSYNC

DISP_LSYNC

GND_VOID=TRUE

AR55

AR54

AT55

AT54

AU54

AU55

AV55

AV54

AW55

AW54

AY55

AY54

AU52

AU51

AV52

AV51

AG55

AH55

AC6

AC7

AD7

AB6

W4

W3

T49

R50

LPDP_INT_DATA_C_P<0>

LPDP_INT_DATA_C_N<0>

GND_VOID=TRUE

LPDP_INT_DATA_C_P<1>

LPDP_INT_DATA_C_N<1>

GND_VOID=TRUE

LPDP_INT_DATA_C_P<2>

LPDP_INT_DATA_C_N<2>

GND_VOID=TRUE

LPDP_INT_DATA_C_P<3>

LPDP_INT_DATA_C_N<3>

GND_VOID=TRUE

NC_LPDP_TX4POS

NC_LPDP_TX4NEG

NC_LPDP_TX5POS

NC_LPDP_TX5NEG

LPDP_INT_AUX_C_P

LPDP_INT_AUX_C_N

SOC_LPDP_INT_RCAL_POS

SOC_LPDP_INT_RCAL_NEG

LPDP_INT_HPD

NC_DISPLAY_POL

NC_SPI_DISP_BKLT_MISO

NC_SPI_DISP_BKLT_MOSI_R

I2C_DISP_BKLT_SCL

I2C_DISP_BKLT_SDA

NC_DISP_SPMI_CLK

NC_DISP_SPMI_DATA

NC_DISP_FSYNC

NC_DISP_BKLT_LSYNC

OUT

OUT

OUT

OUT

OUT

OUT

OUT

06

06

106

106

7

106

106

106

106

OUT

UT

BI

BI

IN

69

69

69

69

69

69

69

69

69

69

69 89

106

42

42

106

IN

OUT

OUT

BI

NC_ISP_I2C0_SCL

106

NC_ISP_I2C0_SDA

106

NC_ISP_I2C1_SCL

106

NC_ISP_I2C1_SDA

106

I2C_CAM_SCL

OUT

I2C_CAM_SDA

BI

NC_ISP_I2C3_SCL

106

NC_ISP_I2C3_SDA

106

NC_FTCAM_RESET_L

OUT

NC_ISP_GPIO1

106

TP_ISP_GPIO2

TP_ISP_GPIO3

NC_ISP_SPMI0_CLK106

NC_ISP_SPMI0_DATA

106

NC_ISP_SPMI1_CLK

10

NC_ISP_SPMI1_DATA

106

TP_SENSOR0_CLK

NC_SENSOR1_CLK

106

NC_SENSOR2_CLK

106

NC_SENSOR3_CLK

106

106

106

41 1

41 106

Y2

ISP_I2C0_SCL/ISP_GPIO_8

Y3

ISP_I2C0_SDA/ISP_GPIO_9

AA5

ISP_I2C1_SCL/ISP_GPIO_10

AA6

ISP_I2C1_SDA/ISP_GPIO_11

AA3

ISP_I2C2_SCL

AA2

ISP_I2C2_SDA

AA7

ISP_I2C3_SCL

AB7

ISP_I2C3_SDA

Y6

ISP_GPIO_0

W6

ISP_GPIO_1

Y7

ISP_GPIO_2

W7

ISP_GPIO_3

AG7

ISP_SPMI0_SCLK/ISP_GPIO_5

AF7

ISP_SPMI0_SDATA/ISP_GPIO_4

AG6

ISP_SPMI1_SCLK/ISP_GPIO_7

AH7

ISP_SPMI1_SDATA/ISP_GPIO_6

AD1

SENSOR0_CLK

AE1

SENSOR1_CLK

AD3

SENSOR2_CLK

AF1

SENSOR3_CLK

U0600

TMLR68A0-B09

BGA

SYM 5 OF 23

ISP SPMI

MIPI0C_DPCLK

MIPI0C_ NCLK

MIPI0C_DPDATA0

MIPI0C_DNDATA0

MIPI0C_DPDATA1

MIPI0C_DNDATA1

MIPI1C_DPCLK

MIPI1C_DNCLK

MIPI1C_DPDATA0

MIPI1C_DNDATA0

MIPI1C_DPDATA1

MIPI1C_DNDATA1

MIPID_DPCLK

MIPID_DNCLK

MIPID_DPDATA0

MIPID_DNDATA0

MIPI_D

MIPI0C_REXT

MIPI1C_REXT

MIPID_REXT

L15

NC_MIPI0C_CLK_POS

L14

NC_MIPI0C_CLK_NEG

K15

NC_MIPI0C_DATA_0_POS

K14

NC_MIPI0C_DATA_0_NEG

M14

NC_MIPI0C_DATA_1_POS

M15

NC_MIPI0C_DATA_1_NEG

GND_VOID=TRUE

L11

MIPI_FTCAM_CLK_P

L12

MIPI_FTCAM_CLK_N

GND_VOID=TRUE

M12

MIPI_FTCAM_DATA_P<0>

M11

MIPI_FTCAM_DATA_N<0>

K11

NC_MIPI_FTCAM_DATA_POS1

K12

NC_MIPI_FTCAM_DATA_NEG1

GND_VOID=TRUE

K9

MIPI_DFR_CLK_P

K8

MIPI_DFR_CLK_N

GND_VOID=TRUE

GND_VOID=TRUE

L9

MIPI_DFR_DATA_P<0>

L8

MIPI_DFR_DATA_N<0>

GND_VOID=TRUE

K17

L17

SOC_MIPI1C_REXT

M9

SOC_MIPID_REXT

GND_VOID=TRUE

GND_VOID=TRUE

106

106

106

106

106

106

7

7

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

68

68

68

68

106

106

87

87

87

87

NC_LPDPRX_RX_P_9

10

NC_LPDPRX_RX_N_9

107

NC_LPDPRX_RX_P_10

107

NC_LPDPRX_RX_N_10

107

NC_LPDPRX_RX_P_11

107

NC_LPDPRX_RX_N_11

107

LPDPRX0_RCAL_POS

19

LPDPRX0_RCAL_NEG

19

LPDPRX1_RCAL_POS

19

LPDPRX1_RCAL_NEG

19

AV4

LPDPRX_RX_D P

AV5

LPDPRX_RX_D9_N

AW4

LPDPRX_RX_D10_P

AW5

LPDPRX_RX_D10_N

AY4

LPDPRX_RX_D11_P

AY5

LPDPRX_RX_D11_N

AU1

LPDPRX0_RCAL_P

AU2

LPDPRX0_RCAL N

AU4

LPDPRX1_RCAL_P

AU5

LPDPRX1_RCAL_N

DISP_TOUCH_BSYNC0

DISP_TOUCH_BSYNC1

DISP_TOUCH_EB

DFR_BSYNC/DISP_INT

DFR_DISP_TE

T50

R49

U49

AM5

AL51

NC_DISP_TOUCH_BSYNC0

NC_DISP_TOUCH_BSYNC1

NC_DISP_TOUCH_EB

NC_BKLT_FAULT_INT_L

DFR_DISP_TE

106

06

06

106

IN

88

IN

SOC_MIPI1C_REXT

7

SOC_MIPID_REXT

7

PLACE_NEAR=U0600.K17:6MM

PACK_OPTION=DFR

1

R0800

200

1%

1/20W

MF

201

2

PLACE_NEAR=U0600.L17:6MM

PACK_OPTION=FTCAM

1

R0820

200

1%

1/20W

MF

201

2

SOC_LPDP_INT_RCAL_POS

7

SOC_LPDP_INT_RCAL_NEG

7

1

R0895

200

1%

1/20W

MF

201

2

1

C0895

10PF

5%

25V

2

C0G

0201

SYNC_MASTER=AITKEN_T668_MLB SYNC_DATE=10/08/2019

PAGE TITLE

SOC: LPDP & MIPI

BOM_COST_GROUP=SOC

Page 8

PER PCISIG SPEC, AC COUPLING CAPS SHOULD BE BETWEEN

www.teknisi-indonesia.com

75 NF AND 265 NF FOR GEN1/2 AND BETWEEN

176 NF AND 265 NF FOR GEN 3/4

R0970 IS NEEDED DUE TO RDAR://53793006

SOC: PCIE

U0600

TMLR68A0-B09

BGA

SYM 6 OF 23

GND_VOID=TRUE

64

IN

64

IN

64

OUT

64

OUT

PCIE_NAND0_D2R_P<0>

PCIE_NAND0_D2R_N<0>

PCIE_NAND0_R2D_C_P<0>

PCIE_NAND0_R2D_C_N<0>

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

BE26

BF26

BC27

BD27

ST_PCIE_RX0_P

ST_PCIE_RX0_N

ST_PCIE_TX0_P

ST_PCIE_TX0_N

GP_PCIE_RX0_P

GP_PCIE_RX0_N

GP_PC E_TX0_P

GP_PCIE_ X0_N

GND_VOID=TRUE

BE30

BF30

GND_VOID=TRUE

GND_VOID=TRUE

BC31

BD31

GND_VOID=TRUE

PCIE_WLBT_D2R_P

PCIE_WLBT_D2R_N

PCIE_WLBT_R2D_C_P

PCIE_WLBT_R2D_C_N

IN

IN

OUT

OUT

62

62

62

62

102 11 6 5 4

PP1V25_AWAKE_IO

NAND0_CLKREQ1_L

867

WLBT_CLKREQ_L

86263

NAND0_CLKREQ0_L

867

USBHC_CLKREQ_L

8

1

R0930

47K

1/20W

MF

201 201

2

1

R0940

47K

5%5%

1/20W

MF

201

2

1

R0950

47K

5%

1/20W

MF

2

1

R0970

47K

5%

1/20W

MF

201

2

6467

OUT

6467

OUT

867

BI

67

864

OUT

65

65

IN

65 106

IN

65

OUT

65

OUT

6567

OUT

6567

OUT

867

BI

PCIE_CLK100M_NAND0_0_P

PCIE_CLK100M_NAND0_0_N

NAND0_CLKREQ0_L

NAND0_PCIE_RESET_L

PCIE_NAND0_D2R_P<1>

PCIE_NAND0_D2R_N<1>

PCIE_NAND0_R2D_C_P<1>

PCIE_NAND0_R2D_C_N<1>

PCIE_CLK100M_NAND0_1_P

PCIE_CLK100M_NAND0_1_N

NAND0_CLKREQ1_L

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

GND_VOID=TRUE

BB37

BC37

AH50

AH52

BE28

BF28

BC29

BD29

BB38

BC38

AH49

ST_PCIE_REF_CLK0_P

ST_PCIE_REF_CLK0_N

ST_PCIE_CLKREQ0_N

ST_PCIE_PERST0_N

ST_PCIE_RX1_P

ST_PCIE_RX1_N

ST_PCIE_TX1_P

ST_PCIE_TX1_N

ST_PCIE_REF_CLK1_P

ST_PCIE_REF_CLK1_N

ST_PCIE_CLKREQ1_N

GP_PCIE_REF_CLK0 P

GP_PCIE_REF_CLK0_N

GP_PCIE_CLKREQ0_N

GP_PCIE_PERST0_N

GP_PCIE_RX1 P

GP_PCIE_RX1_N

GP_PCIE_TX1_P

GP_PCIE_TX1_N

GP_PCIE_REF_CLK1_P

GP_PCIE_REF_CLK1_N

GP_PCIE_CLKREQ1_N

BE40

BF40

AB55

AA52

BE32

BF32

BC33

BD33

BE38

BF38

AA55

PCIE_CLK100M_WLBT_P

PCIE_CLK100M_WLBT_N

WLBT_CLKREQ_L

WLBT_RESET_L

NC_PCIE_USBHC_D2R_POS

NC_PCIE_USBHC_D2R_NEG

NC_PCIE_USBHC_R2D_C_POS

NC_PCIE_USBHC_R2D_C_NEG

NC_PCIE_CLK100M_USBHC_POS

NC_PCIE_CLK100M_USBHC_NEG

USBHC_CLKREQ_L

OUT

OUT

BI

OUT

IN

IN

OUT

OUT

OUT

OUT

62

62

8 62 63

8 62 63

1 6

106

106

106

106

8

TO BE CHECKED WITH SEG- DO NOT MATCH WITH SILVAL

IS THE PULL-UP VOLTAGE CORRECT?

NC_NAND0_PCIE_RESET1_L

106

AH48

ST_PCIE_PERST1_N

GP_PCIE_PERST1_N

GP_PCIE_RX2_P

GP_PCIE_RX2_N

GP_PCIE_TX2_P

GP_PCIE_TX2_N

GP_PCIE_REF_CLK2_P

GP_PCIE_REF_CLK2_N

GP_PCIE_CLKREQ2_N

GP_PCIE_PERST2_N

P55

BE34

BF34

BC35

BD35

BE39

BF39

AH1

AE7

NC_USBHC_RESET_L

NC_PCIE_ENET_D2R_POS

NC_PCIE_ENET_D2R_NEG

NC_PCIE_ENET_R2D_C_POS

NC_PCIE_ENET_R2D_C_NEG

NC_PCIE_CLK100M_ENET_POS

NC_PCIE_CLK100M_ENET_NEG

NC_ENET_CLKREQ_L

NC_ENET_RESET_L

OUT

IN

IN

OUT

OUT

OUT

OUT

BI

OUT

106

106

106

106

106

106

106

106

106

SOC_ST_PCIE_RCAL_POS

8

SOC_ST_PCIE_RCAL_NEG

8

SOC_GP_PCIE_RCAL_POS

8

SOC_GP_PCIE_RCAL_NEG

8

1

R0990

200

1%

1/20W

MF

201

2

1

C0990

10PF

5%

25V

2

C0G

0201

1

R0991

200

1%

1/20W

MF

201

2

1

C0991

10PF

5%

25V

2

C0G

0201

NAND0_PCIE_RESET_L

8646567

WLBT_RESET_L

86263

SOC_ST_PCIE_RCAL_POS

SOC_ST_PCIE_RCAL_NEG

8

NC_MTR_VREF_ANAP

106

NC_MTR_VREF_ANAN

106

NC_MTR VREF_POS

106

NC_MTR_VREF_NEG

106

1

R0941

47K

5%

1/20W

MF

201

2

1

R0951

47K

5%

1/20W

MF

201

2

BC24

BB24

AM3

AL3

AL1

AM1

ST_PCIE_RCAL_P

ST_PCIE_RCAL_N

PAD_MTR_ANALOG_TEST_P

PAD_MTR_ANALOG_TEST_N

PAD_MTR_VREF_P

PAD_MTR_VREF_N

GP_PCIE_RCAL_P

GP_PCIE_RCAL_N

BC25

BB25

SOC_GP_PCIE_RCAL_POS

SOC_GP_PCIE_RCAL_NEG

88

8

SYNC_MASTER=ANDREW_T668_MLB SYNC_DATE=10/09/2019

PAGE TITLE

SOC: PCIE

BOM_COST_GROUP=SOC

Page 9

**OK2INTEGRATE**

www.teknisi-indonesia.com

AOP, NUB, AND SMC GPIO'S ARE REFERENCED TO PP1V25_S2_AOP

SOC: AOP

U0600

TMLR68A0-B09

BGA

SYM 7 OF 23

output if gyro, input for radar

I2C0 is ALS for portables

106

106

106

106

106

106

106

106

106

OUT

OUT

IN

OUT

51106

OUT

51106

IN

51106

IN

74

IN

6263

OUT

6263

OUT

IN

OUT

BI

OUT

BI

74

OUT

74

OUT

NC_R1_DUMP_TRIG

NC_AOP_FUNC1

106

NC_R1_RTC_SYNC

NC_R1_INT

NC_SPI_R1_CS_L

NC_AOP_FUNC5

106

SPI_GYRO_CS_L

GYRO_INT

GYRO_MOTION_INT

LID_OPEN

NC_AOP_FUNC10

106

WLAN_CONTEXT_A

WLAN_CONTEXT_B

NC_ALS_INT_L

NC_AOP_FUNC14

106

I2C_AOP_ALS_SCL

I2C_AOP_ALS_SDA

NC_I2C_AOP_ENET_SCL

NC_I2C_AOP_ENET_SDA

NC_PDM_CLK1

106

NC_PDM_CLK2

106

PDM_DMIC_CLK3

PDM_DMIC_CLK4

NC_PDM_CLK5

106

NC_PDM_CLK6

106

BB18

BC16

BC12

BC13

BA16

BA13

BA15

BD13

BD16

BA14

BB12

BD20

BA11

BD18

BA10

BC20

BB19

BB16

BE15

BB9

BC9

BC6

BD9

BC8

BD8

AOP_FUNC[0]

AOP_FUNC[1]

AOP_FUNC[2]

AOP_FUNC[3]

AOP_FUNC[4]

AOP_FUNC[5]

AOP_FUNC[6]

AOP_FUNC[7]

AOP_FUNC[8]

AOP_FUNC[9]

AOP_FUNC[10]

AOP_FUNC[11]

AOP_FUNC[12]

AOP_FUNC[13]

AOP_FUNC[14]

AOP_I2CM0_SCL

AOP_I2CM0_SDA

AOP_I2CM1_SCL

AOP_I2CM1_SDA

AOP_PDM_IN_CLK1/AOP_I2S1_BCLK

AOP_PDM_IN_CLK2/AOP_I2S0_MCK

AOP_PDM_IN_CLK3/AOP_I2S0_LRCK

AOP_PDM_IN_CLK4/AOP_I2S0_DOUT

AOP_PDM_IN_CLK5/AOP_I2S0_DIN

AOP_PDM_IN_CLK6/AOP_I2S0_BCLK

IPD

IPD

IPU

AOP GPIO

AOP I2C

AOP PDM

NUB_CLK_OUT0

NUB_DOCK_ATTENTION/CTM_TRIGGER

NUB_DOCK_CONNECT

NUB_GPIO_0/AOP_FUNC15/NUB_CLK_OUT1

NUB_GPIO_1/AOP_PDM_IN_CLK0

NUB_GPIO_2/AOP_PDM_IN_DATA0

NUB_GPIO_3/AOP LEAP_MADI_IN

IPU

NUB_GPIO_6/AOP_PDM_OUT_DATA0/AOP_FUNC16

NUB GPIO

NUB SPMI

NUB SWD

NUB_GPIO_4/AOP_LEAP_MADI_OUT

NUB_GPIO_5/AOP_PDM_OUT_CLK0

NUB_GPIO_7/A P_ U C17

NUB_GPIO_8/AOP_FUNC18

NUB_GPIO_9/AOP_FUNC19

NUB_GPIO_10/AOP_FUNC20

NUB_GPIO_11/KIS_GPIO0/AOP_FUNC21

NUB_GPIO_12/KIS_GPIO1/AOP_FUNC22

NUB_SPMI0_SCLK

NUB_SPMI0_SDATA

NUB_SPMI1_SCLK

NUB_SPMI1_SDATA

NUB_SWD_TCK_OUT0

NUB_SWD_TMS0

NUB_SWD_TMS1

BA17

BC15

BC17

BD14

BD15

BD21

BD17

BB13

BD19

BD22

BB10

BD12

BD11

BC10

BB7

BD10

BB15

BC14

BA12

BC11

BC18

BC19

BC21

DFR_TOUCH_CLK32K_RESET_L

TP_SOC_DOCK_ATTENTION

SOC_DOCK_CONNECT

NC_BKLT_PWR_ON_SMC_LED_SEL

CODEC_RESET_L

SOC_SW_DBG

IPD_SPI_INT_L

SMC_FIXTURE_MODE_L

CHGR_INT_L

NC_ENET_I2C_LOM_INT_L

NC_ACDC_ID

NC_ACDC_BURST_EN_L

NC_SPI_DP2HDMI_HOLD_L

NC_HDMI_CEC_AOP_TX

NC_HDMI_CEC_AOP_RX

NC_HDMI_HPD_AOP

SPMI_NUB_MPMU_CLK_R

SPMI_NUB_MPMU_DATA_R

SPMI_NUB_SPMU_CLK_R

SPMI_NUB_SPMU_DATA_R

SWD_NUB_SWCLK

SWD_NUB_PMU_SWDIO

NC_SWD_NUB_R1_SWDIO

OUT

18 106

IN

OUT

OUT

OUT

N

IN

IN

IN

IN

OUT

OUT

OUT

IN

IN

OUT

BI

OUT

BI

OUT

BI

BI

88

9 96

106

76 80

94

106

18 89

106

106

106

106

106

106

106

106

18

18

1

18

29 33

29 33

106

DOC_ATTENTION should be a TP

for non dev programs,

SOC_SW_DBG SHOULD GO TO

A LED IF POSSIBLE.

NEEDS A TEST POINT AT MINIMUM

FIXTURE_MODE_L should be aliased to a TP

for non dev programs,

The TP is required

102 11 9

533748990100

IN

PP1V25_S2

PMU_RESET_L

R1083

10K

5%

/2 W

MF

201

NC_PDM_DATA1

106

NC_PDM_DATA2

106

74

IN

74

IN

51

IN

18

OUT

18

OUT

18

OUT

18

BI

1

2

1833

IN

PDM_DMIC_DATA3

PDM_DMIC_DATA4

SPI_AOP_GYRO_R1_MISO

SPI_AOP_GYRO_R1_MOSI_R

SPI_AOP_GYRO_R1_CLK_R

NC_AOP_SPMI0_SCLK

106

NC_AOP_SPMI0_SDATA

106

SPMI_SE_CLK_R

SPMI_SE_DATA_R

NC_AOP_UART2_D2R

106

NC_AOP_UART2_R2D

106

PMU_CLK32K_SOC

CKP S_W IVE=CLK_DATA_CON

CKPLUS_WAIVE=CLK_DATA_CON

BE21

BE16

BE19

BD5

BF15

BF14

BF17

BF18

BF19

BF20

BF21

BB3

BB4

BE6

BF10

BB5

AOP_PDM_IN_DATA1/AOP_I2S1_MCK

AOP_PDM_IN_DATA2/AOP_I2S1_LRCK

IPD

AOP_PDM_IN_DATA3/AOP_I2S1_DOUT/AOP_PDM_IN_CLK7

IPD

AOP_PDM_IN_DATA4/AOP_I2S1_DIN/AOP_PDM_IN_CLK8

AOP_SPI0_MISO

AOP_SPI0_MOSI

AOP_SPI0_SCLK

AOP_SPMI0_SCLK/AOP_UART0_TXD

AOP_SPMI0_SDATA/AOP_UART0_RXD

AOP_SPMI1_SCLK/AOP_UART1_TXD

AOP_SPMI1_SDATA/AOP_UART1_RXD

AOP_UART2_RXD

AOP_UART2_TXD

RT_CLK32768

CFSB_AON

COLD_RESETN

AOP SPI

AOP SPMI

AOP UART

AOP RESET

JTAG

SMC I2C

SMC UART

JTAG_SEL

IPU

IPU

IPU

IPD

SMC_I2CM0_SCL

SMC_I2CM0_SDA

SMC_I2CM1_SCL/SMC_UART1_TXD

SMC_I2CM1_SDA/SMC_UART1_RXD

SMC_I2CM2_SCL

SMC_I2CM2_SDA

SMC_I2CM3_SCL

SMC_I2CM3_SDA

SMC_I2CM4_SCL

SMC_I2CM4_SDA

IPU

SMC_UART0_RXD

SMC_UART0_TXD

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRSTN

BE4

BF5

BF16

BC1

BB1

BF7

BC3

BC2

BD4

BB2

BD6

BC5

BC7

BD7

BE7

BF9

BF4

BF8

SOC_JTAG_SEL

SWD_SOC_SWCLK

TP_JTAG_SOC_TDI

TP_JTAG_SOC_TDO

SWD_SOC_SWDIO

TP_JTAG_SOC_TRST_L

I2C_SMC_PWR_SCL

I2C_SMC_PWR_SDA

I2C_SMC_UPC_SCL

I2C_SMC_UPC_SDA

I2C_SMC_SNS1_SCL

I2C_SMC_SNS1_SDA

I2C_SMC_IPD_SCL

I2C_SMC_IPD_SDA

I2C_SMC_SNS0_SCL

I2C_SMC_SNS0_SDA

UART_SMC_DEBUGPRT_D2R

UART_SMC_DEBUGPRT_R2D

18

18

18

IN

IN

BI

O T

BI

OUT

BI

OUT

BI

OUT

OUT

BI

IN

OUT

I

4 18

18 56 89

18 56 89

106

106

43 89

3

43

43

106

106

43

43

56 89

56 89

102 11 9

PP1V25_S2

TP_AON_SLEEP1_RESET_L

18

33100

OUT

XW1022

SHORT-14L-0.1MM SM

1860

BI

1860

BI

SOC_WDOG

21

SOC_DBG_PROBE_VALID

EUSB_DBG_P

EUSB_DBG_N

SOC_USBDBG_RESREF

1

2

R1042

200

1%

1/20W

MF

1

BB21

BF12

BF6

BF24

BE24

BE23

AON_SLEEP1_RESETN

WDOG

DBG_PROBE_VALID

DBG_USB_EDP

DBG_USB_EDM

DBG_USB_RESREF

AOP DEBUG

SMC GPIO

IPU

SMC_GPIO0

SMC_GPIO1

SMC_FPWM0

SMC_FPWM1

BF11

BF13

BE12

BE9

UPC_SMC_I2C_INT_L

NC_SMC_GPIO1

SMC_FAN_PWM

SMC_FAN_TACH

106

IN

OUT

IN

107

52 106

52

SOC_DOCK_CONNECT

1

R1066

47K

5%

1/20W

MF

201

2

PAGE TITLE

SOC: AOP

9 96

BOM_COST_GROUP=SOC

Page 10

**OK2INTEGRATE**

www.teknisi-indonesia.com

SOC: POWER (DDR,SRAM)

101 10

PP1V8_S2SW_VDD1

104

PP1V2_AWAKE_PLL

102

101 1

PP1V06_S2SW_DRAM

PP0V6_S1_VDDQL

DDR0_ZQ

10

DDR1_ZQ

10

DDR4_ZQ

10

DDR5_ZQ

10

CRITICAL

1

C1100

1.0UF

20%

4V

2

X6S

0201

PLACE_NEAR=U0600 A5:5MM

PLACE_NEAR=U0600 A7:5MM

PLACE_NEAR=U0600 A33:5MM

PLACE_NEAR=U0600 A35:5MM

CRITICAL

1

C1101

2

1

C1113

0.22UF

20%

6.3V

2

X6S-CERM

0201

1

R1161

240

%

1/20W

MF

201

2

1.0UF

20%

4V

X6S

0201

CRITICAL

1

2

1

C1112

0.1UF

10%

6.3V

2

X6S

0201

1

C1111

2.2UF

20%

4V

2

X6S-CERM

0201

1

R1162

240

1%

1/20W

MF

201

2

C1102

1.0UF

20%

4V

X6S

0201

80UM_STEN

C1105

11UF

1

2

1

R1163

240

1/20W

MF

201

2

1

2

20%

2.5V

X6T

0402

3

4

1

C1110

0.1UF

10%

6.3V

2

X6S

0201

1

C1115

1.0UF

20%

4V

2

X6S

0201

DDR0_RREF

10

DDR1_RREF

10

DDR2_RREF

10

DDR3_RREF

10

DDR4_RREF

10

DDR5_RREF

10

DDR6_RREF

10

DDR7_RREF

10

DDR0_ZQ

10

DDR1_ZQ

10

DDR4_ZQ

10

DDR5_ZQ

10

DDR0_ZQ1

10

DDR1_ZQ1

10

DDR4_ZQ1

10

DDR5_ZQ1

10

%

C1103

12PF

5%

25V

NP0-C0G

0201

80UM_STEN

C1106

11UF

20%

2.5V

X6T

0402

1

4

2

1

R1164

240

1%

1/20W

MF

201

2

1

2

80UM_STEN

C1107

1

3

1

C1114

0.01UF

10%

25V

2

X7R

0201

C1104

3.0PF

+/-0.1PF

25V

NP0-C0G

0201

11UF

20%

2.5V

X6T

0402

3

4

2

1

R1165

240

%

1/20W

MF

201

2

D21

D22

D48

D49

D7

D8

E21

E35

E48

E8

D34

D35

AJ19

AG19

AE13

T25

AA29

Y31

T33

AC43

AJ14

AH14

AC14

R25

T29

T30

T36

AA42

J1

H1

G1

A26

A31

A32

G55

H55

A5

A7

A33

A35

A6

A8

A34

A36

1

R1166

240

1%

1/20W

MF

201

2

U0600

TMLR68A0-B09

BGA

SYM 9 OF 23

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDD1_S2

VDDIO12_PLL_DDR0

VDDIO12_PLL_DDR1

VDDIO12_PLL_DDR2

VDDIO12_PLL_DDR3

VDDIO12_PLL_DDR4

VDDIO12_PLL_DDR5

VDDIO12_PLL_DDR6

VDDIO12_PLL_DDR7

VDDIO11_RET_DDR0_S2

VDDIO11_RET_DDR1_S2

VDDIO11_RET_DDR2_S2

VDDIO11_RET_DDR3_S2

VDDIO11_RET_DDR4_S2

VDDIO11_RET_DDR5_S2

VDDIO11_RET_DDR6_S2

VDDIO11_RET_DDR7_S2

DDR0_RREF

DDR1_RREF

DDR2_RREF

DDR3_RREF

DDR4_RREF

DDR5_RREF

DDR6_RREF

DDR7_RREF

DDR0_ZQ[0]

DDR1_ZQ[0]

DDR4_ZQ[0]

DDR5_ZQ[0]

DDR0_ZQ[1]

DDR1_ZQ[1]

DDR4_ZQ[1]

DDR5_ZQ[1] VDD2_S2

1

R1167

240

%

1/20W

MF

201

2

1

R1168

240

1%

1/20W

MF

201

2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

VDD2_S2

B30

B31

B52

F23

F25

F50

F52

G24

G26

G51

G53

H23

H25

H50

H52

J24

J26

J51

J53

P5

P24

P32

P51

B4

B3

B25

B26

B53

F4

F6

F31

F33

G3

G5

G30

G32

H4

H6

H31

H33

J3

J5

J30

J32

P6

P23

P33

P50

PP1V06_S2SW_DRAM

3

4

3

4

80UM_STEN

C1121

4.3UF

20%

2.5V

X6T

0402

1

4

2

80UM_STEN

C1126

4.3UF

20%

2.5V

X6T

0402

1

4

2

80UM_STEN

C1120

4.3UF

20%

2.5V

X6T

0402

1

2

80UM_STEN

C1125

4.3UF

20%

2.5V

X6T

0402

1

2

80UM_STEN

C1122

4.3UF

1

3

80UM_STEN

C1127

4.3UF

1

3

10110

20%

2.5V

X6T

0402

2

20%

2.5V

X6T

0402

2

3

4

3

4

80UM_STEN

C1123

4.3UF

20%

2.5V

X6T

0402

1

4

2

80UM_STEN

C1128

4.3UF

20%

2.5V

X6T

0402

1

4

2

80UM_STEN

C1124

4.3UF

1

3

80UM_STEN

C1129

4.3UF

1

3

20%

2.5V

X6T

0402

2

20%

2.5V

X6T

0402

2

PP0V6_S1_VDDQL

3

4

3

4

3

4

80UM_STEN

C1132

4.3UF

20%

2.5V

X6T

0402

1

4

2

80UM_STEN

C1136

4 3UF

20%

5

X6T

0402

1

4

2

1

C1150

12PF

5%

25V

2

NP0-C0G

3

3

0201

1

C1151

3.0PF

+/-0.1PF

25V

2

NP0-C0G

0201

80UM_STEN

C1131

4.3UF

U0600

TMLR68A0-B09

BGA

SYM 8 OF 23

AA14

AA16

AA40

AB15

AB41

AC16

AC40

AD15

AE16

AF15

AG14

AH15

AK15

AL14

AL16

AM15

AM17

3

4

3

4

B21

B23

B33

B35

B50

B6

B8

C22

C24

C3

C32

C34

C49

C5

C51

C53

C7

D23

D25

D31

D33

D4

D50

D52

D6

E24

E26

E3

E30

E32

E51

E53

K24

K26

K3

K30

K32

K5

K51

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

VDDQL_S1

K53

L23

L25

L31

L33

L4

L50

L52

L6

M24

M26

M3

M30

M32

M5

M51

M53

N25

N31

N4

N52

T16

T18

T20

T22

T26

T28

T32

T38

T40

U14

U15

U17

U19

U21

U23

U25

U27

U29

U31

U33

U35

U37

U39

V16

V22

V24

V26

V32

V34

V40

W14

W40

Y15

80UM_STE

C1133

4.3UF

20%

2.5V

X6T

0402

1

4

2

80UM_STEN

C1140

4.3UF

20%

2.5V

X6T

0402

1

4

2

80UM_STEN

C1134

1

3

80UM_STEN

C1141

1

3

4.3UF

20%

5V

X6T

0402

4

2

4 3UF

20%

2.5V

X6T

0402

4

2

3

3

20%

2.5V

X6T

0402

1

2

80UM_STEN

C1135

4.3UF

20%

2.5V

X6T

0402

1

2

80UM_STEN

C1142

4.3UF

20%

2.5V

X6T

0402

1

2

10110

101 10

DDR0_ZQ1

10

DDR1_ZQ1

10

DDR4_ZQ1

10

DDR5_ZQ1

10

PP0V6_S1_VDDQL

DDR0_RREF

10

DDR1_RREF

10

DDR2_RREF

10

DDR3_RREF

10

DDR4_RREF

10

DDR5_RREF

10

DDR6_RREF

10

DDR7_RREF

10

PLACE_NEAR=U0600 A6:5MM

PLACE_NEAR=U0600 A8:5MM

PLACE_NEAR=U0600 A34:5MM

PLACE_NEAR=U0600 A36:5MM

1

R1169

240

1%

1/20W

MF

201

2

PLACE_NEAR=U0600 J1: MM

PLACE_NEAR=U0600 H1: MM

PLACE_NEAR=U0600.G1:5MM

PLACE_NEAR=U0600 A26:5MM

PLACE_NEAR=U0600 A31:5MM

PLACE_NEAR=U0600 A32:5MM

PLACE_NEAR=U0600 G55:5MM

PLACE_NEAR=U0600.H55:5MM

1

R1170

240

1%

1/20W

MF

201

2

1

R1171

240

1%

1/20W

MF

201

2

1

R1172

240

1%

1/20W

MF

201

2

1

R1173

240

1%

1/20W

MF

201

2

1

R1174

240

1%

1/20W

MF

201

2

1

R1175

240

1%

1/20W

MF

201

2

1

R1176

240

1%

1/20W

MF

201

2

PAGE TITLE

SOC: POWER (DDR,SRAM)

BOM_COST_GROUP=SOC

2

1

Page 11

**OK2INTEGRATE**

www.teknisi-indonesia.com

102 9

102

PP1V25_S2

PP1V25_S2

Internally generated rail

PP0V6_S2_GRP1

VOLTAGE=0.6V

PP0V6_S2_GRP2

20%

2.5V

X6S

0201

1

2

1

C1210

2.2UF

20%

4V

2

X6S-CERM

0201

1

C1213

2.2UF

20%

4V

2

X6S-CERM

0201

C1200

4UF

C1201

4UF

20%

2.5V

X6S

0201

1

C1211

0.1UF

10%

6.3V

2

X6S

0201

SOC: POWER (IO)

VOLTAGE=0.6V

1

2

U0600

TMLR68A0-B09

BGA

SYM 14 OF 23

C1234

2.2UF

20%

X6S-CERM

4V

0201

AR40

AP40

BB22

AY23

1

2

AY25

AY27

BA24

BA26

VDD06_GRP1_S2

VDD06_GRP2_S2 VDD2_S2_SENSE2

VDDDIO_HIB_S4

VDDIO12_ OP_S2

VDDIO12_AOP_S2

VDDIO12_AOP_S2

VDDIO12_AOP_ 2

VDDIO12_AOP_S2

VDD2_S2_SENSE1

VDD_PCPU_SENSE

VDD_ECPU_ ENSE

VDD_GPU_SENSE

VDD_SOC_S1_SENSE

VDD_DISP_S1_SENSE

VDD_DCS_SENSE

VDDQL_SENSE

B10

B37

AD36

AN23

AC23

AH22

Y17

AN17

AN15

VSNS_VDD2_1

VSNS_VDD2_2

VSNS_VDD_PCPU

VSNS_VDD_ECPU

VSNS_VDD_GPU

VSNS_VDD_SOC

VSNS_VDD_DISP

VSNS_VDD_DCS

VSNS_VDDQL

48

48

45 48

45 48

45 48

45 48

48

48

48

102 8 6 5 4

PP1V25_AWAKE_IO

CRITICAL

20%

6.3V

0402

1

2

C1233

10UF

CER-X6S

138S00073

XW1232

SM

21

XW1231

SM

VOLTAGE=1.25V

97

PP1V25_AWAKE_GRP5

VOLTAGE=1.25V

21

PP1V25_AWAKE_GRP4

97

C1232

2.2UF

20%

X6S-CERM

0201

102 97

PP1V8_AWAKE

AP39

XW1230

SM

20%

4V

0201

1

2

C1231

2.2UF

X6S-CERM

1

2

VOLTAGE=1.25V

21

PP1V25_AWAKE_GRP3

97

20%

4V

0201

1

2

C1230

2.2UF

X6S-CERM

AF41

AG42

AH40

AL40

AN40

AT40

AV40

AP16

AR17

AT16

AU17

AV16

AW17

AP41

AR41

VDDIO12_GRP1_S2

VDDIO12_GRP3

VDDIO12_GRP3

VDDIO12_GRP3

VDDIO12_GRP3

VDDIO12_GRP3

VDDIO12_GRP4

VDDIO12_GRP4

VDDIO12_GRP5

VDDIO12_GRP5

VDDIO12_GRP5

VDDIO12_GRP5

VDDIO12_GRP5

VDDIO12_GRP5

VDDIO18_GRP1

VDDIO18_GRP1

VSS_PCPU_SENSE

VSS_DDR_SENSE

VSS_SENSE1

VSS_S NSE2

AD37

AN16

B9

B36

VSNS_VSS_PCPU

VSNS_VSS_DDR

VSNS_VSS_1

VSNS_VSS_2

45 48

48

48

48

C1240

2.2UF

2 %

X6S-CERM

0201

1

V

2

SOC: POWER (IO)

BOM_COST_GROUP=SOC

12

Page 12

**OK2INTEGRATE**

www.teknisi-indonesia.com

4

SOC: POWER (CPU, GPU)

80UM_STEN

C1310

11UF

20%

2.5V

X6T

0402

1

3

4

2

80UM_STEN

C1318

11UF

20%

2.5V

X6T

0402

1

2

101 12

80UM_STEN

C1311

11UF

1

3

20%

2 5V

X T

0402

2

4

80UM_STEN

C1312

11UF

20%

2.5V

X6T

0402

1

3

2

80UM_STEN

C1319

11UF

20%

2.5V

X6T

0402

1

3

4

2

PPVDD_PCPU_AWAKE

25V

0201

3

1

2

80UM_STEN

C1314

11UF

2.5V

0402

1

2

C1300

3.0PF

+/-0.1PF

NP0-C0G

80UM_STEN

C1313

11UF

20%

2.5V

X6T

0402

1

3

4

4

2

C1301

NP0-C0G

20%

X6T

3

4

12PF

5%

25V

0201

80UM_STEN

C1315

11UF

20%

2.5V

X6T

0402

1

2

0.575V @ 4400MA

U0600

TMLR68A0-B09

BGA

SYM 11 OF 23

AE33

AE35

AE36

AE37

AF33

AF36

AF39

AG34

AG38

AH34

AH39

AJ33

AJ34

AK29

AK33

1

2

80UM_STEN

C1316

11UF

20%

2.5V

X6T

0402

1

3

4

4

2

80UM_STEN

C1317

1

3

11UF

20%

2.5V

X6T

0402

4

2

3

AK35

AK36

AK38

AK40

AK41

AK42

AK43

AK44

AK45

AK46

AL30

AL32

AL37

AL41

AL42

AL43

AL44

AL45

AL46

AM29