Page 1

DIGIT AL TRANSMISSION MEASURING INSTRUMENTS

334

NNEEW

W

DIGITAL DATA ANALYZER

MP1632A

50 MHz to 3.2 GHz

Core networks and computer networks are becoming increasingly

rapid as the volume of data transmitted in this multimedia data is

growing. In addition to the STM-16/OC-48 (2.488 Gbit/s), Fibre channel, Giga-bit Ethernet, etc. are being commercialized. Compact and

low-cost BERTSs (Bit Error Rate Test Sets) are required for production inspections of all kinds of transfer devices, optical modules, and

logic devices.

The MP1632A realizes a compact and low-cost solution that incorporates existing measuring equipment (MP1652A Pulse Pattern

Generator and MP1653A Error Detector) into one cabinet.

Features

• 3.2 Gb/s PPG and ED in one cabinet

•

Eye diagram measurement and burst signal measurement supported

Performance and functions

• Easy to view, superb operability

The MP1632A comes with a large, color LCD with touch screen.

Moreover, it employs the Microsoft Windows®operating system version 3.1. In addition to the graphic display of measurement results,

customized screens enable one-key and one-parameter operation.

• High-quality pulse pattern generator

Programmable patterns of 8 Mb max, PRBS patterns [(27– 1) to

(2

31

– 1), variable mark ratio], and zero substitution patterns can be

generated. Moreover , v ariable cross-point of data output w a v ef orm is

also supported.

H: 100 ps/div, V: 1 V/div

MU163220A output waveform (3.2 GHz)

• Error detector with many functions

High input sensitivity (25 mVp-p*) and wide phase margin (250 ps*)

performance is provided. Phase margin and threshold margin can be

measured using various error rates. Eye diagram displa y is also supported. Moreover, the autosearch function enables PRBS pattern

search in addition to ordinary phase and threshold search.

*

Typical values at 3 Gb/s, PRBS 223– 1

• Internal synthesizer with high signal purity (Option)

Generates highly pure signals with SSB phase noise characteristics

of –85 dBc/Hz or less (10 kHz offset).

• Support of various applications

Testing of SDH/SONET (STM-0, 1, 4, 16/OC-1, 3, 12, 48) devices

and modules, research and development on WDM components,

Fibre channels, Giga-bit Ethernet, evaluation of E/O and O/E module, GaAs IC, and high-speed ASIC/FPGAs

GPIB

OPTION

Page 2

335

DIGIT AL TRANSMISSION MEASURING INSTRUMENTS

9

Specifications

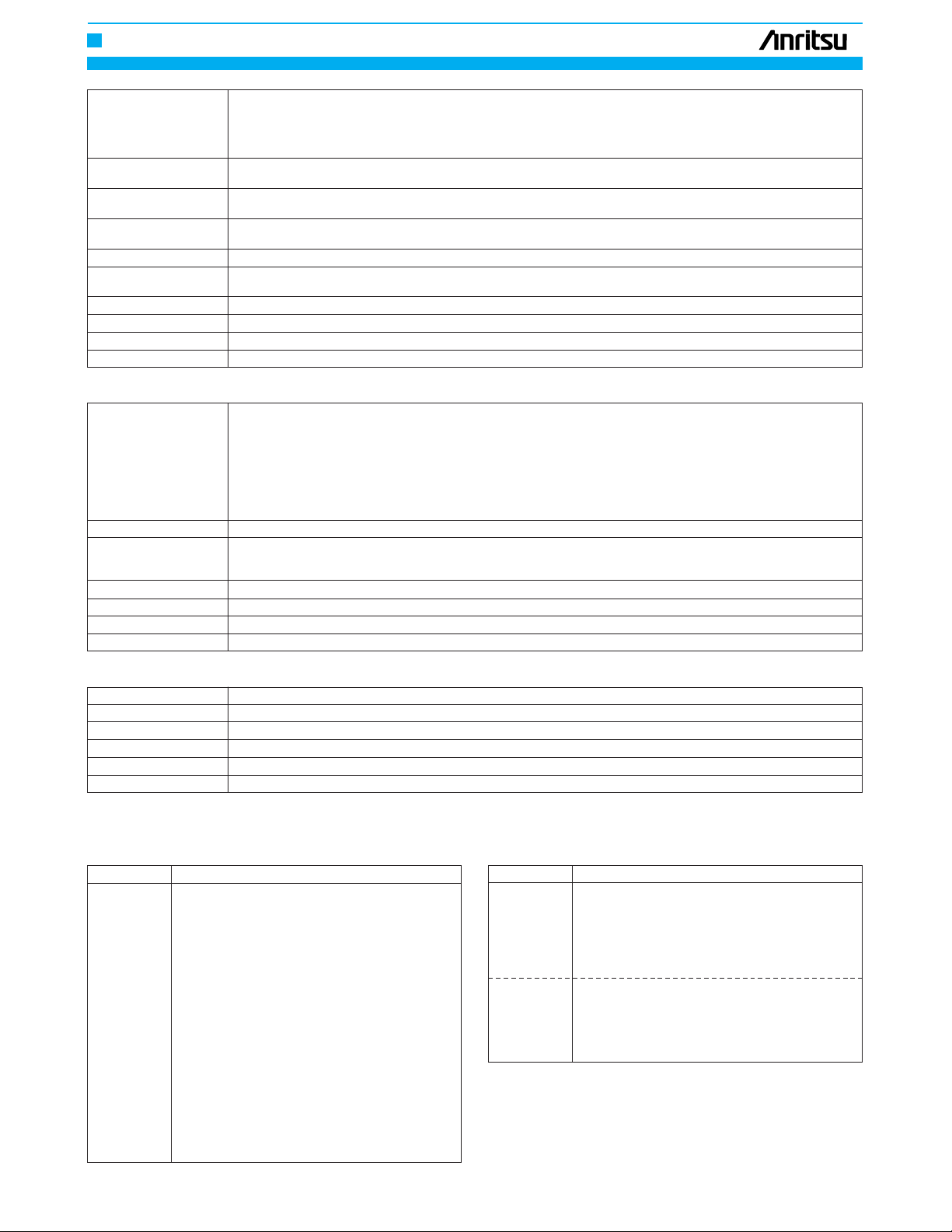

• MU163220A 3.2G Pulse Pattern Generator

Operating frequency 10 MHz to 3.2 GHz

External clock input 0.5 to 2 Vp-p

Pseudo random pattern (PRBS)

Pattern length: 2

n

– 1 (n: 7, 9, 11, 15, 20, 23, 31)

Mark ratio: 1/2, 1/4, 1/8, 0/8, 1/2, 3/4, 7/8, 8/8

AND bit shift upon mark ratio setting: 1, 3 bits

Data pattern

Generation pattern

Data length: 2 to 8,338,608 bits

Zero substitution pattern

Continuous 0 bit length: 1 to (pattern length – 1) bits

Pattern length: 2

n

(n: 7, 9, 11, 15)

Error insertion

Error ratio: 10

–n

(n: 3, 4, 5, 6, 7, 8, 9), single error

External error input: Provided

Number of outputs: 2 (DATA/DATA, independent)

Amplitude: 0.5 to 2 Vp-p (10 mV steps)

Offset voltage

V

OH

: –2 to +2 V (5 mV steps)

Display: V

OH

, VTH, and VOLselectable

Rise/fall time: ≤80 ps (10% to 90% of amplitude)

Data output

Pattern jitter: ≤30 psp-p

Waveform distor tion: 10% or 0.1 V of amplitude, whichever is greater

Load impedance: 50 Ω (with back termination)

Connector: SMA

DATA/DATA tracking: DATA amplitude and offset voltage can be set to same value as DATA.

Crosspoint adjustment function: Provided

Number of output: 2 (CLOCK/CLOCK, independent)

Amplitude: 0.5 to 2 Vp-p (10 mV steps)

Offset voltage

V

OH

: –2 to +2 V (5 mV steps)

Clock output Display: V

OH

, VTH, and VOLselectable

Rise/fall time: ≤80 ps (10% to 90% of amplitude)

Load impedance: 50 Ω (with back termination)

Connector: SMA

Clock delay: –1 to +1 ns (2 ps steps)

External burst trigger input

Input level: 0/–1 V, connector: SMA

Internal burst signal Burst cycle: 2 µs to 50 ms (1 µs steps); Enable length: 1 µs to 49.999 ms (1 µs steps)

Burst trigger output Output level: 0/–1 V, connector: SMA

Number of outputs: 1 (1/8 clock, variable pattern synchronization output selectable)

Sync signal output Output level: 0/–1 V

Connector: SMA

Operating temperature +5 to +45˚C

Power ≤200 VA

Dimensions and mass 232 (W) x 49 (H) x 449 (D) mm, ≤4.5 kg

• MU163240A 3.2G Error Detector

Operating frequency 10 MHz to 3.2 GHz

Input waveform: NRZ

Input voltage: 0.5 to 4 Vp-p

Data input Variable threshold voltage: –4 to +4 V (1 mV steps)

Termination: Connected to GND, –2 V or +3 V via 50 Ω

Connector: SMA

Input waveform: Square wave (<0.5 GHz), square wave or sine wave (≥0.5 GHz), duty: 50%

Input amplitude: 0.5 to 4 Vp-p

Clock input

Variable input delay: –1 to +1 ns (2 ps steps)

Polarity inversion: POS/NEG inversion selectable

Termination: Connected to GND, –2 V or +3 V via 50 Ω

Connector: SMA

Auto search function Phase, threshold, PRBS patter n

Pseudo random pattern (PRBS)

Pattern length: 2

n

– 1 (n: 7, 9, 11, 15, 20, 23, 31)

Marker ratio: 1/2, 1/4, 1/8, 0/8, 1/2, 3/4, 7/8, 8/8

AND bit shift upon marker ratio setting: 1, 3 bits

Receive pattern Data pattern

Data length: 2 to 8,338,608 bits

Zero substitution pattern

Continuous 0 bit length: 1 to (pattern length – 1) bits

Pattern length: 2

n

(n: 7, 9, 11, 15)

Sync mode Normal, frame

Sync threshold AUTO or 10–n(n: 2, 3, 4, 5, 6, 7, 8)

Error detection mode Omission, insertion, total

Continued on next page

Page 3

DIGIT AL TRANSMISSION MEASURING INSTRUMENTS

336

Error rate: 0.0000 x 10

–16

to 1.0000 x 10

–0

Number of errors: 0 to 9.9999 x 10

16

Measurement items Error interval (async): 0 to 9999999 (Interval: 100 ms, 1 s)

Error free interval (EFI): 0.0000 to 100.0000%

Clock frequency: 0.01 to 3.2 GHz (resolution: 1 Hz, accuracy: 10 ppm ±1 kHz)

Eye margin measurement

Provided

function

Error performance

Provided

calculation function

Measurement channel

1 to 8 channels, each channel settable independently

mask

Error output Number of output: 1 (1/8 bit rate OR error), Output level: 0/–1; Connector: SMA

Number of outputs: 1 (switchable among 1/8 clock, fixed patter n sync, sync gain output)

Sync signal output

Output level: 0/–1 V; Connector: SMA

Burst trigger input Input level: 0/–1 V, connector: SMA

Operating temperature +5˚ to +45˚C

Power ≤250 VA

Dimensions and mass 232 (W) x 49 (H) x 449 (D) mm, ≤4.5 kg

• MP1632A (Main frame)

OS: Microsoft Windows®operating system Version 3.1

Display: 10.4 inch, color LCD (touch screen), 640 x 480 dots, 256 colors

Printer: Parallel port for external printer (D-sub, 25-pins)

Keyboard: 101 type (English), PS/2 (mini DIN 6-pin connector)

System environment Mouse: Serial, PS/2 (mini DIN, 6-pin connector)

FDD: 2 modes (1.44 MB, 740 KB)

HDD

C drive: ≥474 KB (used for system: measurement data, pattern)

D drive: ≥30 MB (not accessible to users, interface: IDE)

Remote control RS-232C (standard), GPIB (option): IEEE488.2, Ethernet (option): 10 Base-T

EN55011: 1991, Group 1, Class A

EMC EN50082-1: 1992

Harmonic current emissions: EN61000-3-2 (1995)

Safety EN61010-1: 1993 (Installation Category ΙΙ, Pollution Degree ΙΙ)

Power supply 100 to 120 Vac/200 to 240 Vac, 47.5 to 63 Hz, ≤150 VA

Operating temperature +5˚ to +45˚C

Dimensions and mass 426 (W) x 221.5 (H) x 451(D) mm, ≤20 kg

• 3.2G Internal Synthesizer (Option 03)

Frequency range 50 MHz to 3.2 GHz (1 kHz steps)

Frequency accuracy ±2 ppm

SSB phase noise ≤–85 dBc/Hz (10 kHz offset, 1 kHz bandwidth)

Non-harmonic spurious ≤–60 dBc (limited to spurious 10 kHz or more distant from carrier frequency)

Power ≤50 VA

Mass ≤5 kg

Microsoft Windows is a registered trademark of Microsoft Corporation in USA and other countries.

Ordering information

Please specify model/order number, name, and quantity when ordering.

Model/Order No.

Name

Main frame

MP1632A Digital Data Analyzer

Standard accessories

J0491 Power cord (shielded): 1 pc

F0071 Fuse, 8 A: 2 pcs

Z0319A PS/2 mouse: 1 pc

Z0320 Input pen: 1 pc

Z0347 Recovery disk

*1: 1 set

Z0393 Application disk

*1: 1 set

Z0395 Remote sample disk

*1: 1 set

W1360AE MP1632A operation manual: 1 copy

W1361AE MP1632A remote control operation manual: 1 copy

Options

MP1632A-01 GPIB interface board

MP1632A-02 Ethernet interface board

MP1632A-03 3.2G internal synthesizer

Peripherals

Z0321A Keyboard (PS/2)

J0008 GPIB cable, 2 m

Model/Order No.

Name

MU163220A 3.2G Pulse Pattern Generator

Standard accessories

J0693A

Coaxial cord (HRM202B • 3D2W • HRM202B), 1 m:

1 pc

J0696A Coaxial cord (AA-165-500), 0.5 m: 2 pcs

W1386AE MU163220A/163240A operation manual: 1 copy

Z0306A List strap: 1 pc

MU163240A 3.2G Error Detector

Standard accessories

J0693A

Coaxial cord (HRM202B • 3D2W • HRM202B), 1 m:

1 pc

J0696A Coaxial cord (AA-165-500), 0.5 m: 2 pcs

W1386AE MU163220A/163240A operation manual

*2: 1 copy

*

1: Only for MP1632A customer

*

2: Not supplied when 3.2G pulse pattern generator purchased as same time

Loading...

Loading...