Analog Devices OP215 a Datasheet

Dual Precision JFET-Input

a

FEATURES

High Slew Rate: 10 V/s Min

Fast Settling Time: 0.9 s to 0.1% Type

Low Input Offset Voltage Drift: 10 V/C Max

Wide Bandwidth: 3.5 MHz Min

Temperature-Compensated Input Bias Currents

Guaranteed Input Bias Current: 18 nA Max (125C)

Bias Current Specified Warmed Up over Temperature

÷

Low Input Noise Current: 0.01 pA/

High Common-Mode Rejection Ratio 86 dB Min

Pin Compatible with Standard Dual Pinouts

Models with MIL-STD-883 Class B Processing Available

GENERAL DESCRIPTION

The OP215 offers the proven JFET-input performance advantages

of high speed and low input bias current with the tracking and

convenience advantages of a dual op amp configuration.

Low input offset voltages, low input currents, and low drift are

featured in these high-speed amplifiers.

On-chip zener-zap trimming is used to achieve low V

bias-current compensation scheme gives a low input bias current

Hz Type

while a

OS,

Operational Amplifier

OP215

at elevated temperature. Thus, the OP215 features an input bias

current of 1.4 nA at 70∞C ambient (not junction) temperature

which greatly extends the application usefulness of this device.

Applications include high-speed amplifiers for current output

DACs, active filters, sample-and-hold buffers, and photocell

amplifiers. For additional precision JFET op amps, see the

OP249 and AD712 data sheets.

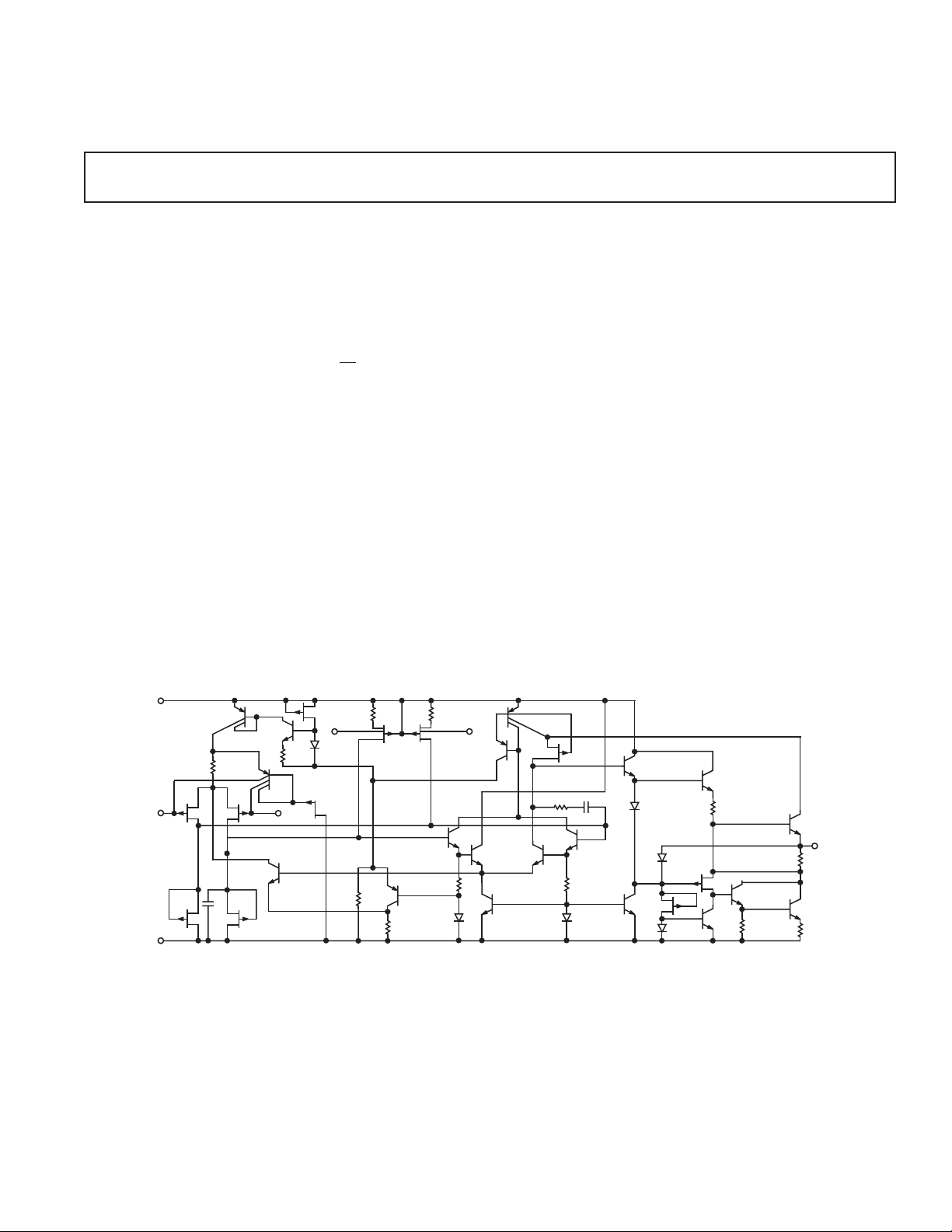

V+

NOMINV

INPUT+

V–

R1

J2

J1

C1

J3

J4

7.4

pF

Q5

Q8

Q12

J5

Q6

R3

–INV

INPUT

NULL

Q7

J11

R8

R9

J8 J7

Q11

R4

R7

Q1

NULL

Figure 1. Simplified Schematic (1/2 OP215)

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

Q10

Q9

J6

C2

R2

7.4pF

Q3

R5

3.6

Q13

k

Q16

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

Q4

Q2

R6

3.6k

Q15

NOTE

R7, R8 ARE ELECTRONICALLY ADJUSTED

ON-CHIP FOR MINIMUM OFFSET VOLTAGE

Q19

Q14

Q17

Q18

Q21

J9

Q24

J10

Q20

R13

Q23

R11

Q22

Q25

OUTPUT

R10

R12

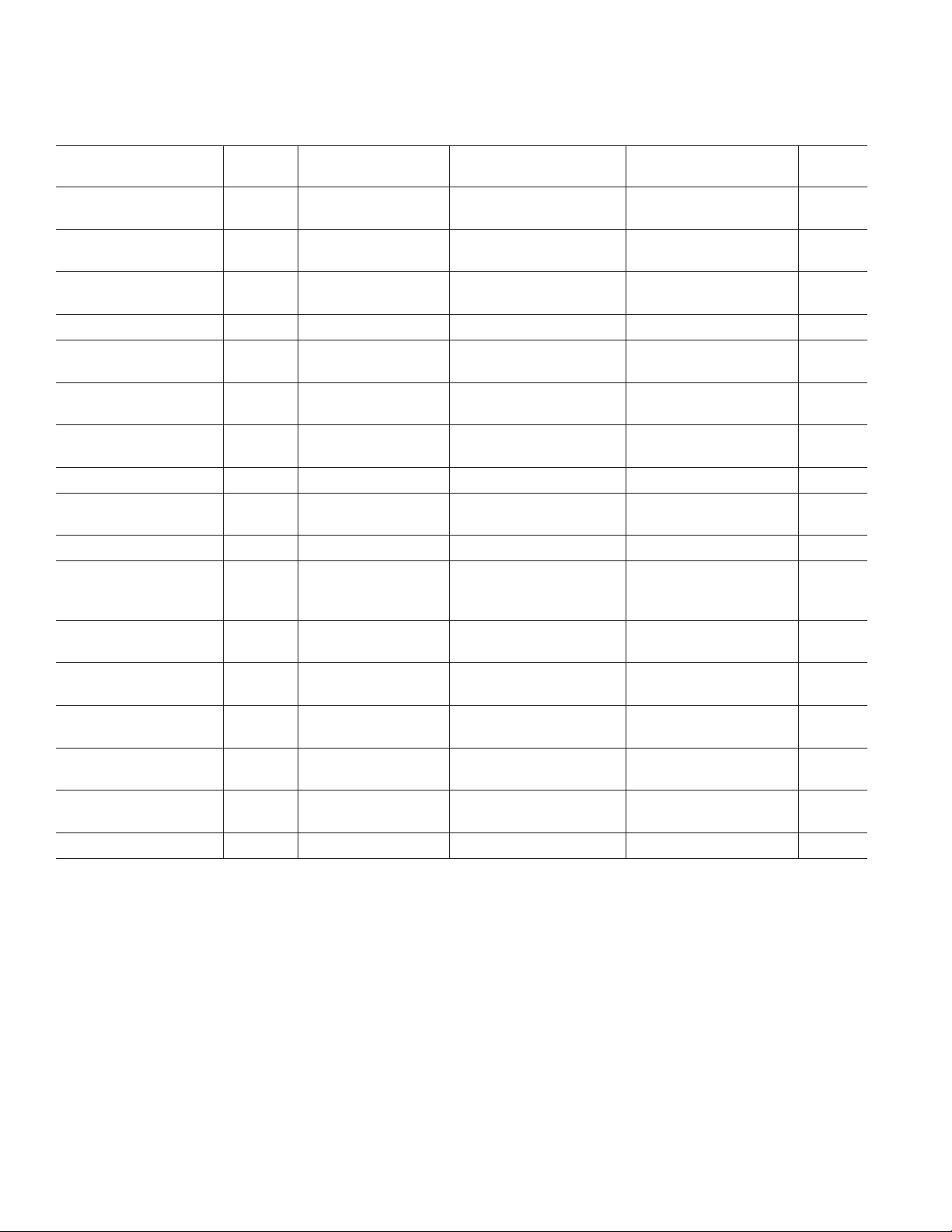

OP215–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(at VS = ±15 V, TA = 25C, unless otherwise noted.)

OP215E OP215G

Parameter Symbol Conditions Min Type Max Min Type Max Unit

Input Offset Voltage V

OS

RS = 50 W 0.2 1.0 2.0 4.0 mV

‘G’ Grade 2.5 6.0 mV

Input Offset Current

1

I

OS

Tj = 25∞C3503100 pA

Device Operating 5 100 5 200 pA

Input Bias Current

1

I

B

Tj = 25∞C ± 15 ± 100 ± 15 ± 300 pA

Device Operating ± 18 ± 300 ± 18 ±600 pA

Input Resistance R

Large-Signal Voltage A

IN

VO

1,2

10

RL ⱖ 2 kW, 150 500 50 200 V/mV

10

1,2

W

Gain VO = ± 10 V

Output Voltage Swing V

O

RL = 10 kW±12 ± 13 ± 12 ± 13 V

RL = 2 kW±11 ± 12.7 ± 11 ± 12.7 V

Supply Current I

SY

6.0 8.5 7.0 10.0 mA

‘G’ Grade 7.0 12.0 mA

Slew Rate SR A

Gain Bandwidth GBW 3.5 5.7 3.0 5.4 MHz

Product

3

Closed-Loop Bandwidth CLBW A

Setting Time t

S

= 1 10 18 5 15 V/s

VCL

= 1 13 12 MHz

VCL

To 0.01% 2.3 2.4 s

To 0.05%

2

1.1 1.2 s

To 0.10% 0.9 1.0 s

Input Voltage Range IVR 10.2 14.8 10.1 14.8 V

–10.2 –11.5 –10.1 –11.5 V

Common-Mode CMRR V

= ± IVR 82 100 80 96 dB

CM

Rejection Ratio E, G Grades

Power Supply Rejection PSRR V

= ± 10 V to ± 16 V 10 51 V/V

S

Ratio VS = ± 10 V to ± 15 V 16 100 V/V

Input Noise Voltage nf

= 100 Hz 20 20 nV/÷Hz

O

Density fO = 1,000 Hz 15 15 nV/÷Hz

Input Noise Current I

n

fO = 100 Hz 0.01 0.01 pA/÷Hz

Density fO = 1,000 Hz 0.01 0.01 pA/÷Hz

Input Capacitance C

NOTES

1

Input bias current is specified for two different conditions. The Tj = 25∞C specification is with the junction at ambient temperature; the device operating specification is

with the device operating in a warmed up condition at 25∞ C ambient. The warmed up bias-current value is correlated to the junction temperature value via the curves

of IS versus Tj and IS versus TA. PMI has a bias-current compensation circuit that gives improved bias current and bias current over temperature versus standard

JFET input op amps. IS and IOS are measured at VCM = 0.

2

Setting time is defined here for a unity gain inverter connection using 2 kW resistors. It is the time required for the error voltage (the voltage at the inverting input pin

on the amplifier) to settle to within a specified percent of its final value from the time a 10 V step input is applied to the inverter. See setting time test circuit.

3

Sample tested.

Specifications are subject to change without notice.

IN

33pF

–2–

REV. A

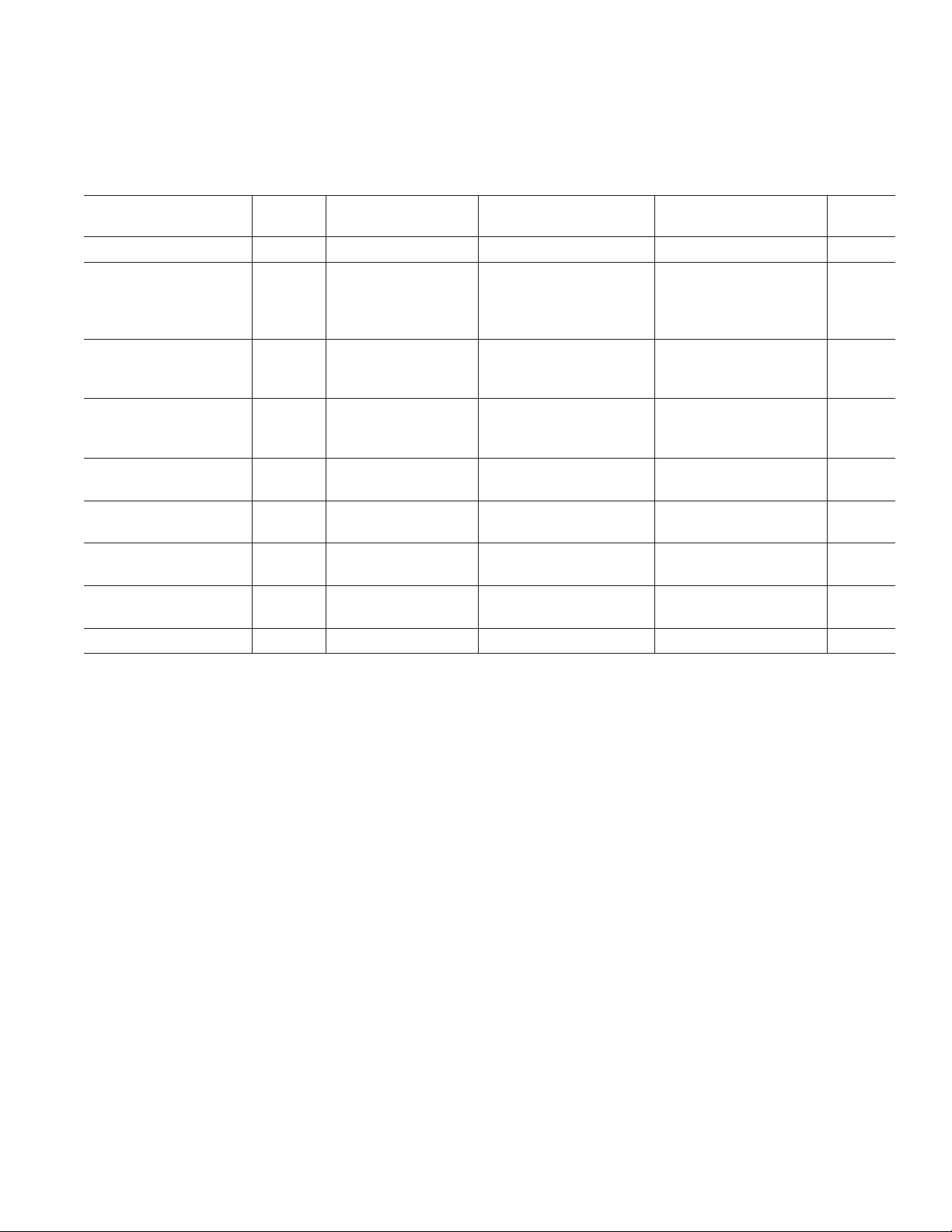

OP215

SPECIFICATIONS

(at VS = ±15 V, 0C ⱕ TA ⱕ 70C for E Grade, –40C ⱕ TA ⱕ +85C for G Grade, unless

ELECTRICAL CHARACTERISTICS

Parameter Symbol Conditions Min Type Max Min Type Max Unit

Input Offset Voltage V

Average Input Offset

Voltage Drift

Without External Trim

With External Trim TCV

Input Offset Current

Input Bias Current

2

Input Voltage Range IVR 10.2 14.7 10.1 14.7 V

Common-Mode CMRR V

Rejection Ratio

Power Supply Rejection PSRR V

Ratio VS = ± 10 V to ± 15 V 20 159 V/V

Large-Signal A

Voltage Gain VO = ± 10 V

Output Voltage Swing V

NOTES

1

Sample tested.

2

Input bias current is specified for two different conditions. The Tj = 25∞C specification is with the junction at ambient temperature; the Device Operating specification is

with the device operating in a warmed up condition at 25∞ C ambient. The warmed up bias-current value is correlated to the junction temperature value via the curves

of IS versus Tj and IS versus TA. PMI has a bias-current compensation circuit that gives improved bias current and bias current over temperature versus standard

JFET input op amps. IS and IOS are measured at VCM = 0.

Specifications are subject to change without notice.

OS

1

TCV

OS

OSn

2

I

OS

I

S

VO

O

otherwise noted.)

OP215E OP215G

RS = 50 W 0.4 1.65 3.5 8.0 mV

315 6 V/∞C

RP = 100 kW 34V/∞C

Tj = 70∞C 0.06 0.45 0.08 0.65 nA

= 70∞C 0.08 0.80 0.10 1.2 nA

T

A

Device Operating

Tj = 70∞C ± 0.12 ± 0.70 ± 0.14 ± 0.9 nA

T

= 70∞C ± 0.16 ± 1.40 ± 0.19 ± 1.8 nA

A

Device Operating

–10.2 –11.4 –10.1 –11.3 V

= ± IVR 80 98 7694 dB

CM

= ± 10 V to ± 16 V 13 100

S

RL ⱖ 2 kW 50 180 35 130 V/mV

RL ⱖ 10 kW±12 ± 13 ± 12 ± 13 V

REV. A

–3–

Loading...

Loading...