Programmable Touch Controller for

V

A

FEATURES

Programmable capacitance-to-digital converter (CDC)

Femtofarad (fF) resolution

8 capacitance sensor inputs

25 ms update rate, all 8 sensor inputs

No external RC components required

Automatic conversion sequencer

On-chip automatic calibration logic

Automatic compensation for environmental changes

Automatic adaptive threshold and sensitivity levels

Register map compatible with AD7143

On-chip RAM to store calibration data

2

I

C-compatible serial interface

Separate V

Interrupt output

16-lead, 4 mm × 4 mm LFCSP

2.6 V to 3.3 V supply voltage

Low operating current

Full power mode: 1 mA

Low power mode: 21.5 μA

APPLICATIONS

Cell phones

Personal music and multimedia players

Smart handheld devices

Television, A/V, and remote controls

Gaming consoles

Digital still cameras

GENERAL DESCRIPTION

The AD7148 is designed for use with capacitance sensors implementing functions such as buttons, scroll bars, and wheels.

The sensors need only one PCB layer, enabling ultrathin

applications.

The AD7148 is an integrated capacitance-to-digital converter

(CDC) with on-chip environmental calibration. The CDC has

eight inputs channeled through a switch matrix to a 16-bit,

250 kHz sigma-delta (∑-∆) converter. The CDC is capable of

sensing changes in the capacitance of the external sensors and

uses this information to register a sensor activation. The external

sensors can be arranged as a series of buttons, as a scroll bar or

wheel, or as a combination of sensor types. By programming the

registers, the user has full control over the CDC setup.

High resolution sensors require minimal software to run on the

host processor.

A

Rev.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

level for serial interface

DRIVE

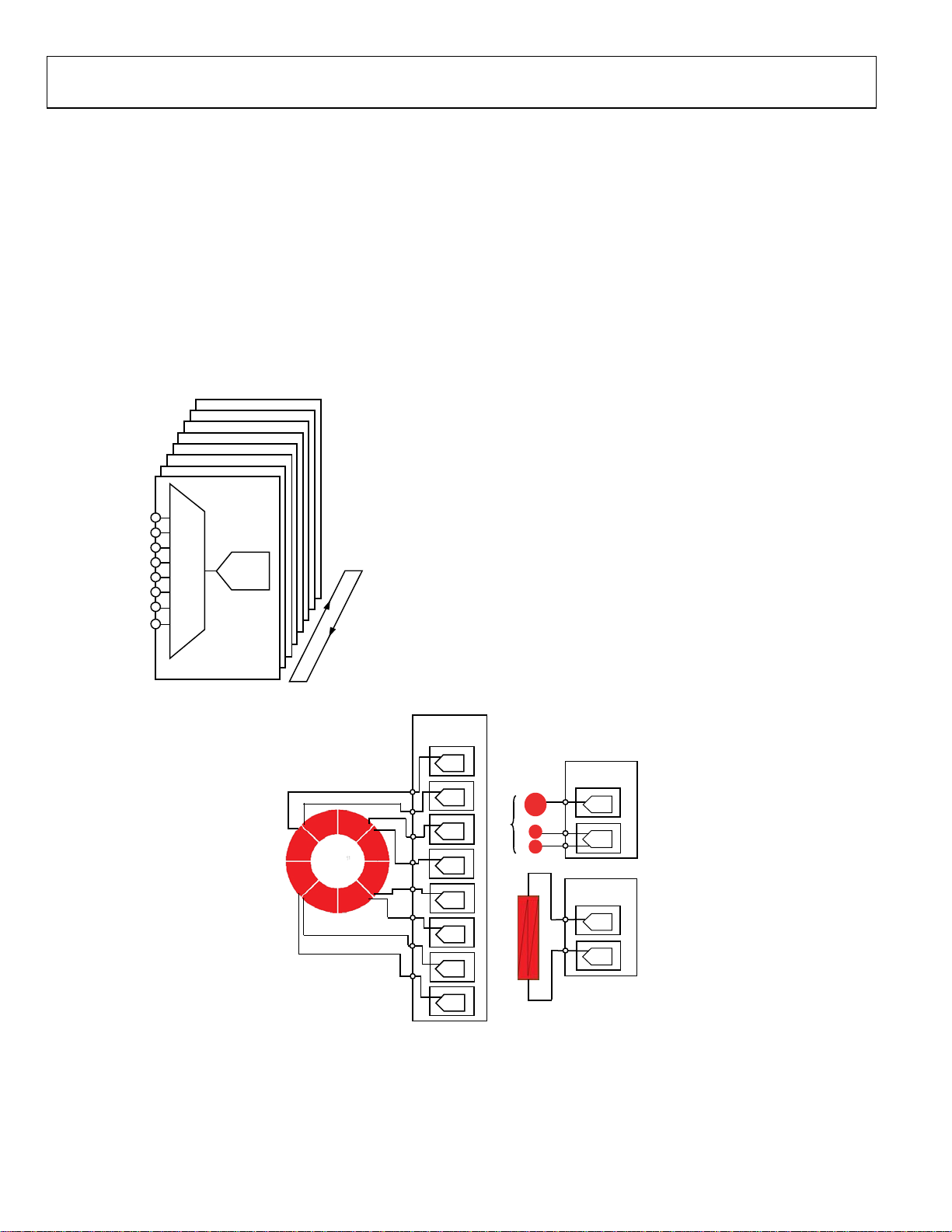

Single Electrode Capacitance Sensors

AD7148

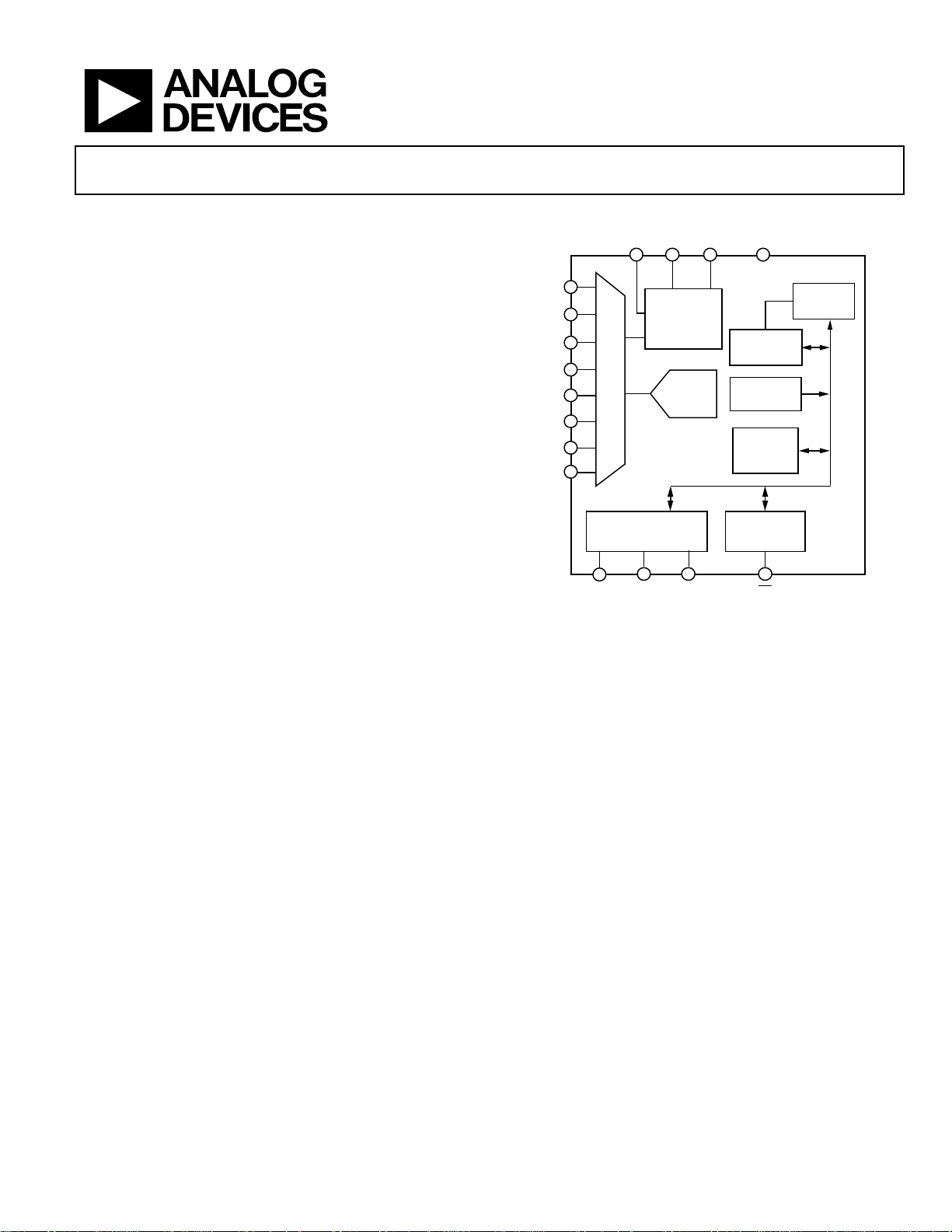

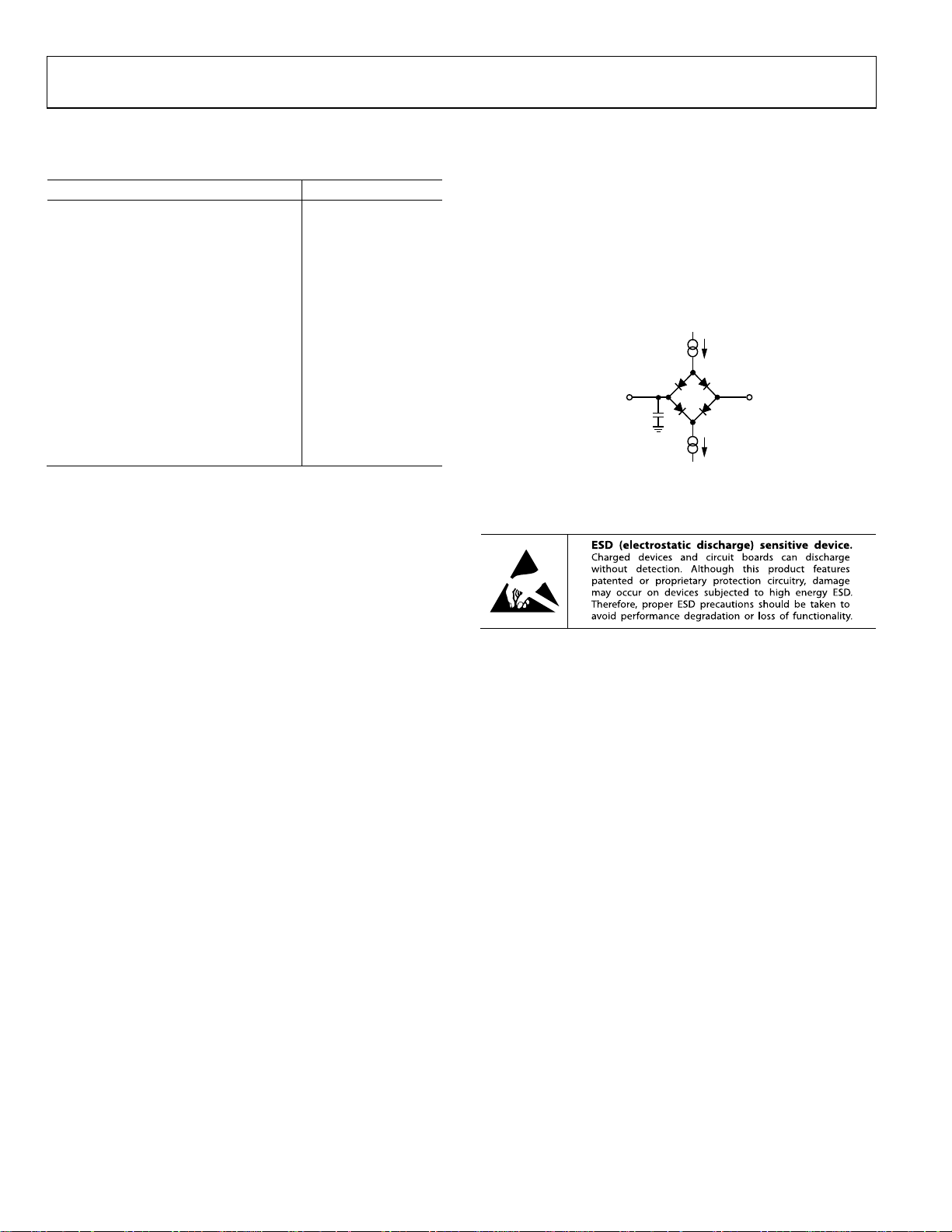

FUNCTIONAL BLOCK DIAGRAM

C

SHIELD

5

13

CIN0

CIN1

14

CIN2

15

CIN3

16

MATRIX

CIN4

CIN5

CIN6

CIN7

SWITCH

1

2

3

4

SERIAL I NTERFA CE

AND CONTROL LOG IC

9

V

DRIVE

10 11 12

SDA SCLK

The AD7148 is designed for single electrode capacitance sensors

(grounded sensors). There is an active shield output to minimize

noise pickup in the sensor. For floating, or two, electrode sensors,

use the AD7143.

The AD7148 has on-chip calibration logic to compensate for

changes in the ambient environment. The calibration sequence is

performed automatically and at continuous intervals as long as

the sensors are not touched. This ensures that there are no false

or nonregistering touches on the external sensors due to a

changing environment.

The AD7148 has an I

2

C®-compatible serial interface, as well as

an interrupt output. There is a V

for the serial interface independent of V

The AD7148 is available in a 16-lead, 4 mm × 4 mm LFCSP and

operates from a 2.6 V to 3.6 V supply. The operating current

consumption in low power mode is typically 26 µA.

On .A.

e Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S

Tel: om

781.329.4700 www.analog.c

Fax: ed.

781.461.3113 ©2007–2010 Analog Devices, Inc. All rights reserv

GND

CC

8 7 6

EXCITATION

SOURCE

16-BIT

Σ-Δ

CDC

Figure 1.

DRIVE

BIAS

AD7148

POWER-ON

RESET

LOGIC

CALIBRATION

RAM

CALIBRATION

ENGINE

CONTROL

AND

DATA

REGIST ERS

INTERRUP T

AND GPIO

LOGIC

INT

7155-001

pin to set the voltage level

.

CC

AD7148

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Typical Average Current in Low Power Mode ......................... 4

Maximum Average Current in Low Power Mode .................... 4

2

I

C Timing Specifications (AD7148-1) ..................................... 5

Absolute Maximum Ratings ............................................................ 6

ESD Caution .................................................................................. 6

Pin Configuration and Function Descriptions ............................. 7

Typical Performance Characteristics ............................................. 8

Theory of Operation ...................................................................... 10

Capacitance Sensing Theory ..................................................... 10

BIAS Pin ....................................................................................... 11

Operating Modes ........................................................................ 11

Capacitance-to-Digital Converter ................................................ 13

Oversampling the CDC Output ............................................... 13

Capacitance Sensor Offset Control .......................................... 13

Conversion Sequencer ............................................................... 13

CDC Conversion Sequence Time ............................................ 14

CDC Conversion Results ........................................................... 15

Capacitance Sensor Input Configuration .................................... 16

CINx Input Multiplexer Setup .................................................. 16

Single-Ended Connections to the CDC .................................. 16

Noncontact Proximity Detection ................................................. 17

Recalibration ............................................................................... 18

Proximity Sensitivity .................................................................. 20

FF_SKIP_CNT ............................................................................ 20

Environmental Calibration ........................................................... 22

Capacitance Sensor Behavior Without Calibration ............... 22

Capacitance Sensor Behavior with Calibration ...................... 22

SLOW FIFO ................................................................................ 23

SLOW_FILTER _UPDATE_LVL .............................................. 23

Adaptive Threshold and Sensitivity ............................................. 24

Interrupt Output ............................................................................. 26

CDC Conversion-Complete Interrupt .................................... 26

Sensor Touch Interrupt.............................................................. 26

AC

I

Output .............................................................................. 27

SHIELD

2

C-Compatible Serial Interface ................................................... 28

V

Input ................................................................................. 30

DRIVE

PCB Design Guidelines ................................................................. 31

Capacitive Sensor Board Mechanical Specifications ............. 31

Chip Scale Packages ................................................................... 31

Power-Up Sequence ....................................................................... 32

Typical Application Circuit ........................................................... 33

Register Map ................................................................................... 34

Detailed Register Descriptions ..................................................... 35

Bank 1 Registers ......................................................................... 35

Bank 2 Registers ......................................................................... 43

Bank 3 Registers ......................................................................... 48

Outline Dimensions ....................................................................... 56

Ordering Guide .......................................................................... 56

REVISION HISTORY

1/10—Rev. 0 to Rev. A

Changes to Figure 4 and Table 6 ..................................................... 7

Changes to BIAS Pin Section ........................................................ 11

Changes to Table 15 ........................................................................ 28

Changes to Figure 45 ...................................................................... 33

Added Exposed Pad Notation to Outline Dimensions ............. 56

12/07—Revision 0: Initial Version

Rev. A | Page 2 of 56

AD7148

SPECIFICATIONS

VCC = 2.6 V to 3.6 V, TA = −40oC to +85°C, unless otherwise noted.

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments

CAPACITANCE-TO-DIGITAL CONVERTER

Update Rate 24.25 25 25.75 ms

Resolution 16 Bits

CINx Input Range ±8 pF

No Missing Codes 16 Bits Guaranteed by design, not production tested

Total Unadjusted Error ±20 %

Output Noise (Peak-to-Peak) 7 Codes Decimation rate = 128

3 Codes Decimation rate = 256

Output Noise (RMS) 0.8 Codes Decimation rate = 128

0.5 Codes Decimation rate = 256

C

Offset Range ±20 pF 6-bit DAC

STRAY

C

Offset Resolution 0.32 pF

STRAY

Low Power Mode Delay Accuracy 4 % % of 200 ms, 400 ms, 600 ms, or 800 ms

EXCITATION SOURCE

Frequency 250 kHz

Output Voltage 0 VCC V Oscillating

AC

SHIELD

Short-Circuit Source Current 10 mA

Short-Circuit Sink Current 10 mA

Maximum Output Load 150 pF Capacitance load on AC

LOGIC INPUTS (SCLK, SDA,)

Input High Voltage, VIH 0.7 × V

V

DRIVE

Input Low Voltage, VIL 0.4 V

Input High Voltage, IIH −1 μA VIN = V

Input Low Voltage, IIL 1 μA VIN = GND

Hysteresis 150 mV

OPEN-DRAIN OUTPUTS (SCLK, SDA, INT)

Output Low Voltage, VOL 0.4 V I

Output High Leakage Current, IOH +0.1 ±1 μA V

POWER

VCC 2.6 3.3 3.6 V

V

1.65 3.6 V Serial interface operating voltage

DRIVE

ICC 0.9 1 mA In full power mode, VCC + V

15.5 21.5 μA Low power mode, converter idle, VCC + V

2.3 7.5 μA Full shutdown, VCC + V

8 conversion stages in sequencer;

decimation rate = 256

to ground

SHIELD

DRIVE

= −1 mA

SINK

= V

DRIVE

DRIVE

DRIVE

OUT

DRIVE

Rev. A | Page 3 of 56

AD7148

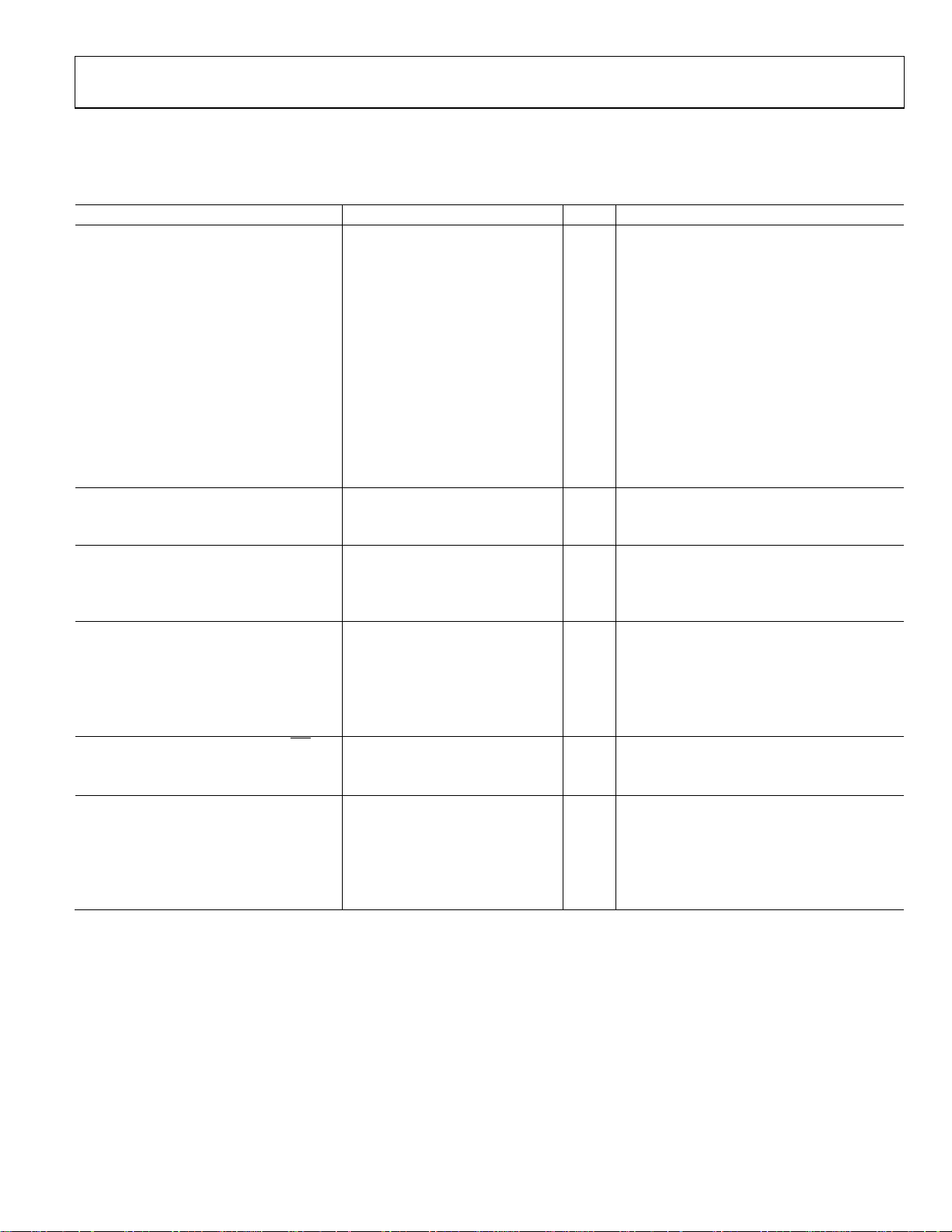

TYPICAL AVERAGE CURRENT IN LOW POWER MODE

VCC = 3.6 V, T = 25°C, load of 50 pF, unless otherwise noted.

Table 2.

Current Values of Conversion Stages (μA)

Low Power Mode Delay Decimation Rate 1 2 3 4 5 6 7 8

200 ms 64 20.83 24.18 27.52 30.82 34.11 37.37 40.6 43.81

128 25.3 31.92 38.45 44.87 51.21 57.45 63.6 69.66

256 34.11 46.99 59.51 71.66 83.47 94.94 106.1 116.96

400 ms 64 18.17 19.86 21.55 23.23 24.9 26.57 28.23 29.88

128 20.43 23.79 27.12 30.43 33.72 36.98 40.22 43.43

256 24.9 31.53 38.06 44.5 50.83 57.08 63.23 69.3

600 ms 64 17.28 18.41 19.54 20.67 21.79 22.91 24.03 25.14

128 18.79 21.04 23.28 25.51 27.73 29.94 32.13 34.32

256 21.79 26.25 30.67 35.04 39.37 43.66 47.9 52.11

800 ms 64 16.84 17.69 18.53 19.38 20.23 21.07 21.91 22.75

128 17.97 19.66 21.35 23.03 24.7 26.37 28.03 29.69

256 20.23 23.59 26.93 30.24 33.53 36.79 40.03 43.24

MAXIMUM AVERAGE CURRENT IN LOW POWER MODE

VCC = 3.6 V, load of 50 pF, unless otherwise noted.

Table 3.

Current Values of Conversion Stages (μA)

Low Power Mode Delay Decimation Rate 1 2 3 4 5 6 7 8

200 ms 64 27.71 31.65 35.56 39.44 43.28 47.1 50.89 54.64

128 32.96 40.72 48.37 55.89 63.3 70.59 77.77 84.84

256 43.28 58.37 72.99 87.17 100.92 114.26 127.22 139.8

400 ms 64 24.61 26.6 28.58 30.55 32.51 34.47 36.42 38.36

128 27.26 31.21 35.12 39 42.85 46.67 50.46 54.22

256 32.51 40.29 47.94 55.47 62.88 70.18 77.36 84.44

600 ms 64 23.58 24.91 26.23 27.55 28.87 30.18 31.5 32.8

128 25.35 27.99 30.62 33.24 35.84 38.43 41 43.56

256 28.87 34.11 39.29 44.41 49.48 54.5 59.46 64.38

800 ms 64 23.06 24.06 25.05 26.05 27.04 28.03 29.02 30

128 24.39 26.38 28.36 30.33 32.29 34.25 36.2 38.14

256 27.04 30.98 34.9 38.78 42.64 46.46 50.25 54.01

Rev. A | Page 4 of 56

AD7148

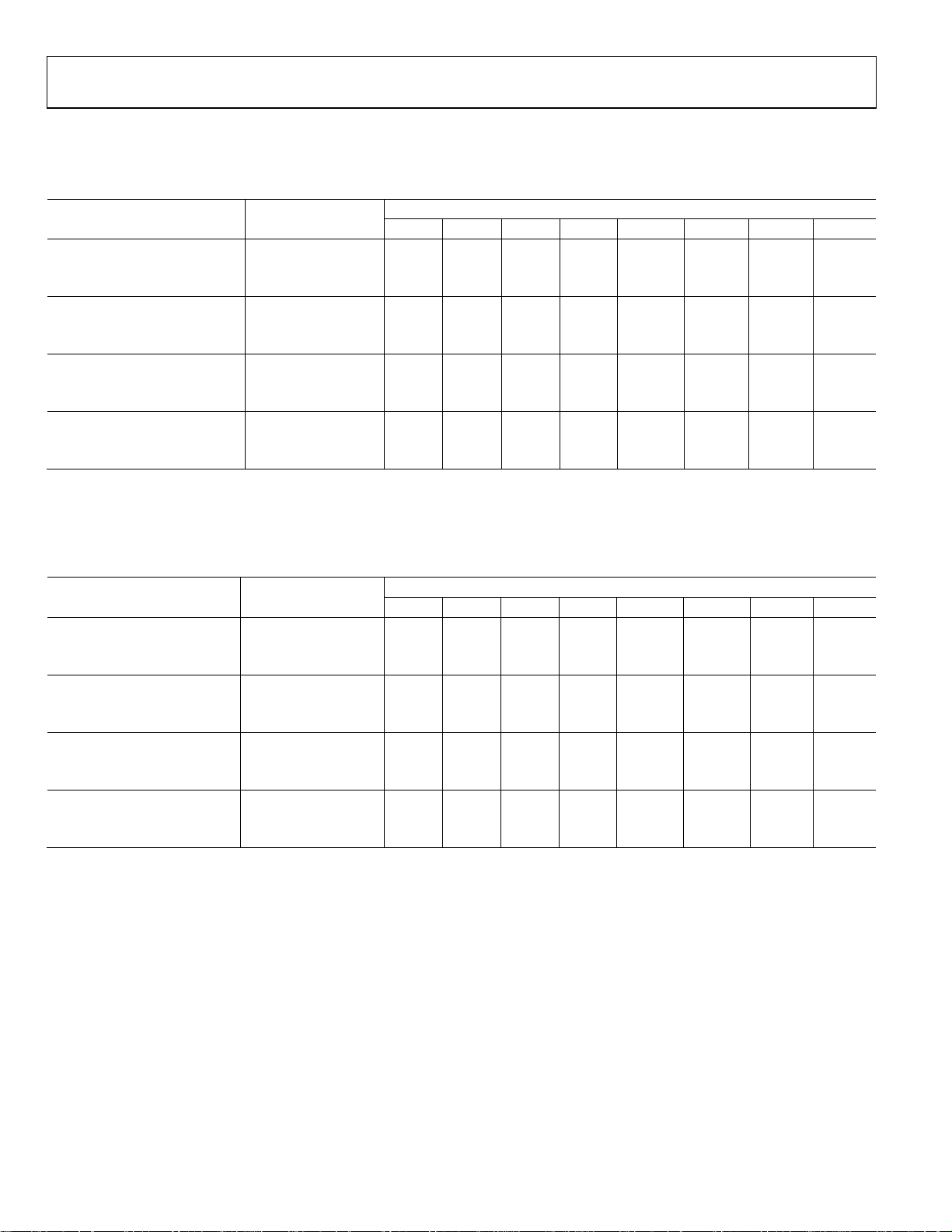

I2C TIMING SPECIFICATIONS (AD7148-1)

TA = −40°C to +85°C, V

All input signals timed from a voltage level of 1.6 V.

Table 4.

Parameter

f

SCLK

1

Limit Unit Description

400 kHz max

t1 0.6 μs min Start condition hold time, t

t2 1.3 μs min Clock low period, t

t3 0.6 μs min Clock high period, t

t4 100 ns min Data setup time, t

t5 300 ns min Data hold time, t

t6 0.6 μs min Stop condition setup time, t

t7 0.6 μs min Start condition setup time, t

t8 1.3 μs min Bus free time between stop and start conditions, t

tR 300 ns max Clock/data rise time

tF 300 ns max Clock/data fall time

1

Guaranteed by design, not production tested.

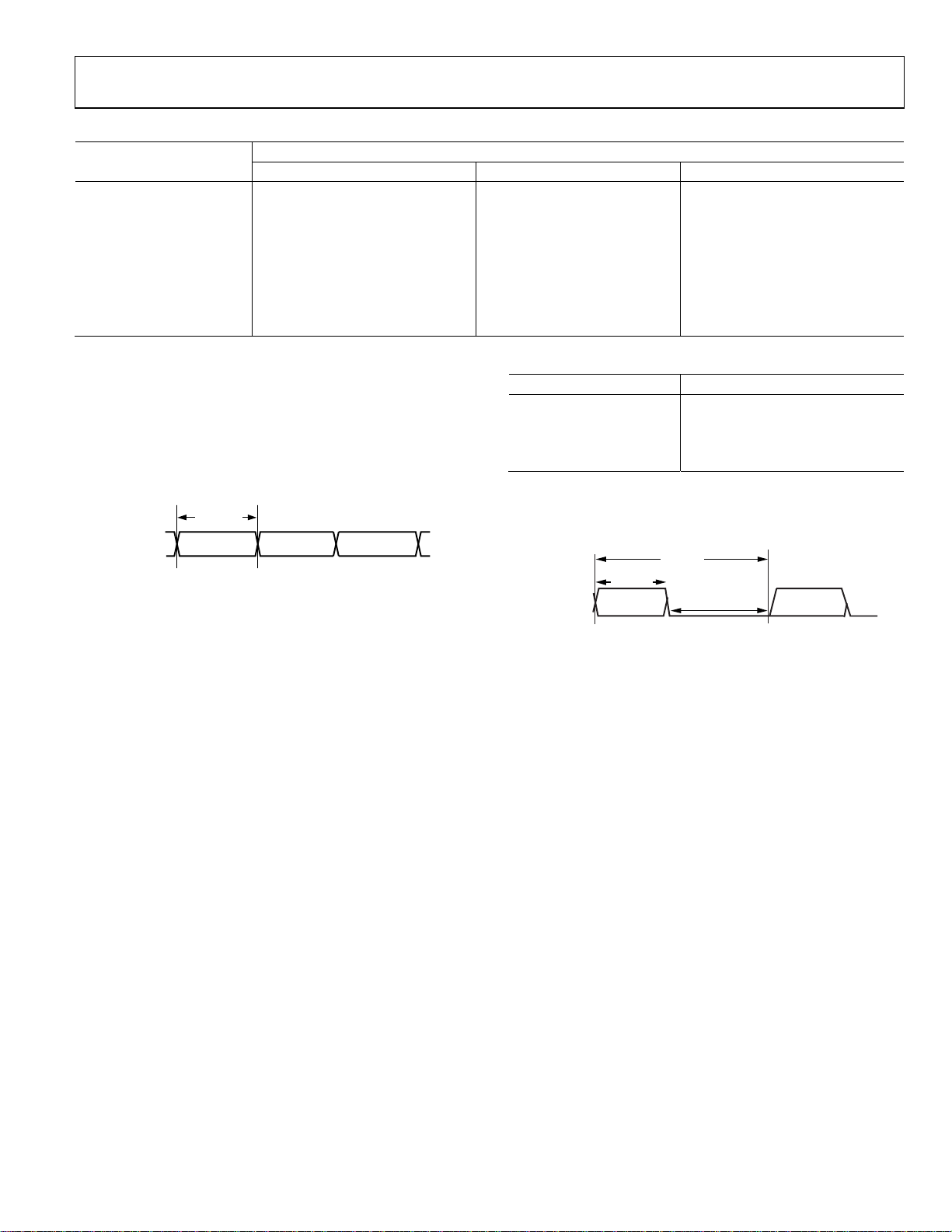

I2C Timing Diagram

SCLK

SDA

STOP START STOPSTART

= 1.65 V to 3.6 V, VCC = 2.6 V to 3.6 V, unless otherwise noted. Sample tested at 25°C to ensure compliance.

DRIVE

HD; STA

LOW

HIGH

SU; DAT

HD; DAT

SU; STO

SU; STA

BUF

t

t

2

t

1

t

8

R

t

5

t

F

t

3

Figure 2. I

t

4

2

C Detailed Timing Diagram

t

1

t

7

t

6

07155-002

Rev. A | Page 5 of 56

AD7148

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter Rating

VCC to GND −0.3 V to +3.6 V

Analog Input Voltage to GND −0.3 V to VCC + 0.3 V

Digital Input Voltage to GND −0.3 V to V

Digital Output Voltage to GND −0.3 V to V

Input Current to Any Pin Except Supplies1 10 mA

ESD Rating (Human Body Model) 2.5 kV

Operating Temperature Range −40°C to +105°C

DRIVE

DRIVE

+ 0.3 V

+ 0.3 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Storage Temperature Range −65°C to +150°C

Junction Temperature 150°C

LFCSP

Power Dissipation 450 mW

θJA Thermal Impedance 135.7°C/W

IR Reflow Peak Temperature 260°C ± 0.5°C

Lead Temperature (Soldering, 10 sec) 300°C

1

Transient currents of up to 100 mA do not cause SCR latch-up.

Figure 3. Load Circuit for Digital Output Timing Specifications

ESD CAUTION

TO OUTPUT

PIN

50pF

C

200µA I

L

200µA I

OL

1.6V

OH

07155-003

Rev. A | Page 6 of 56

AD7148

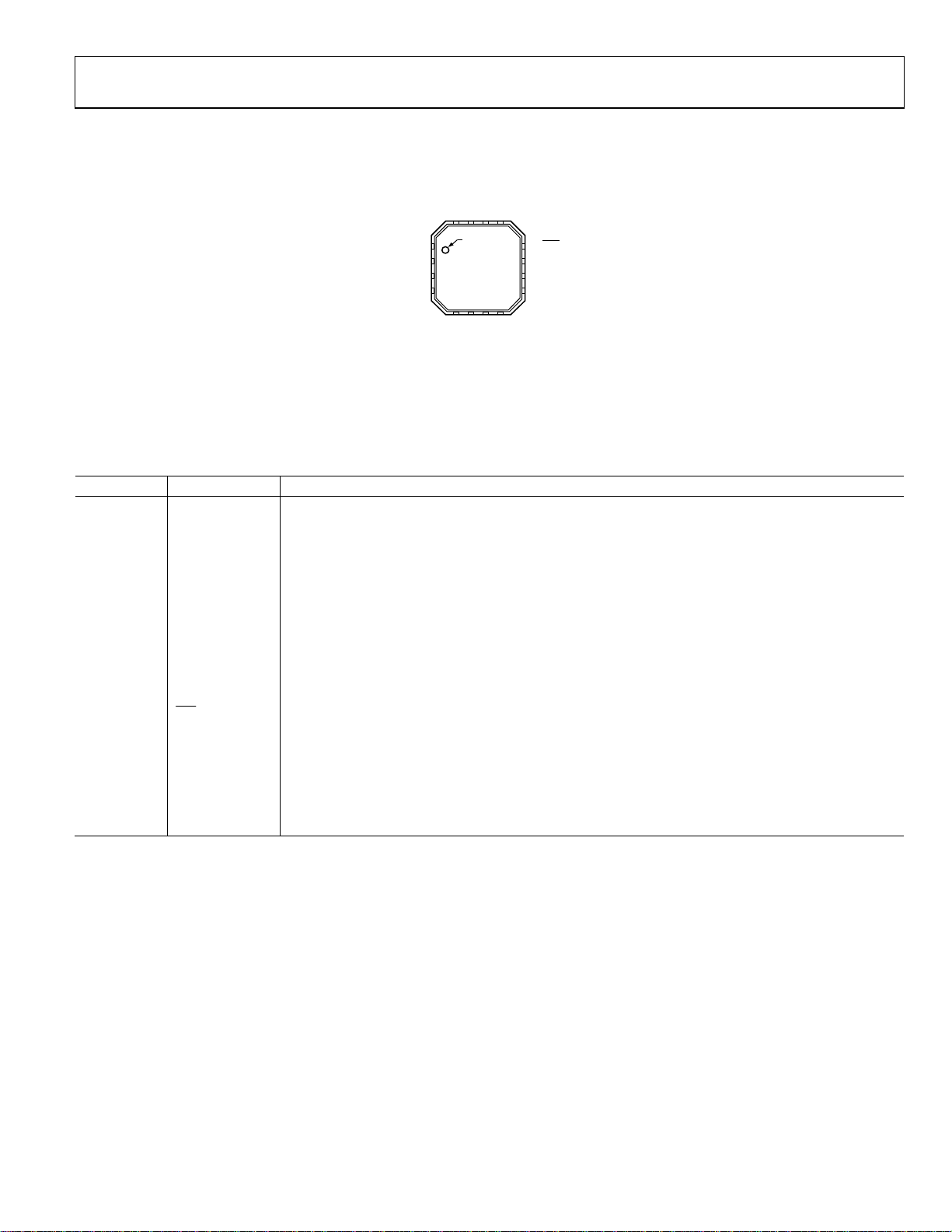

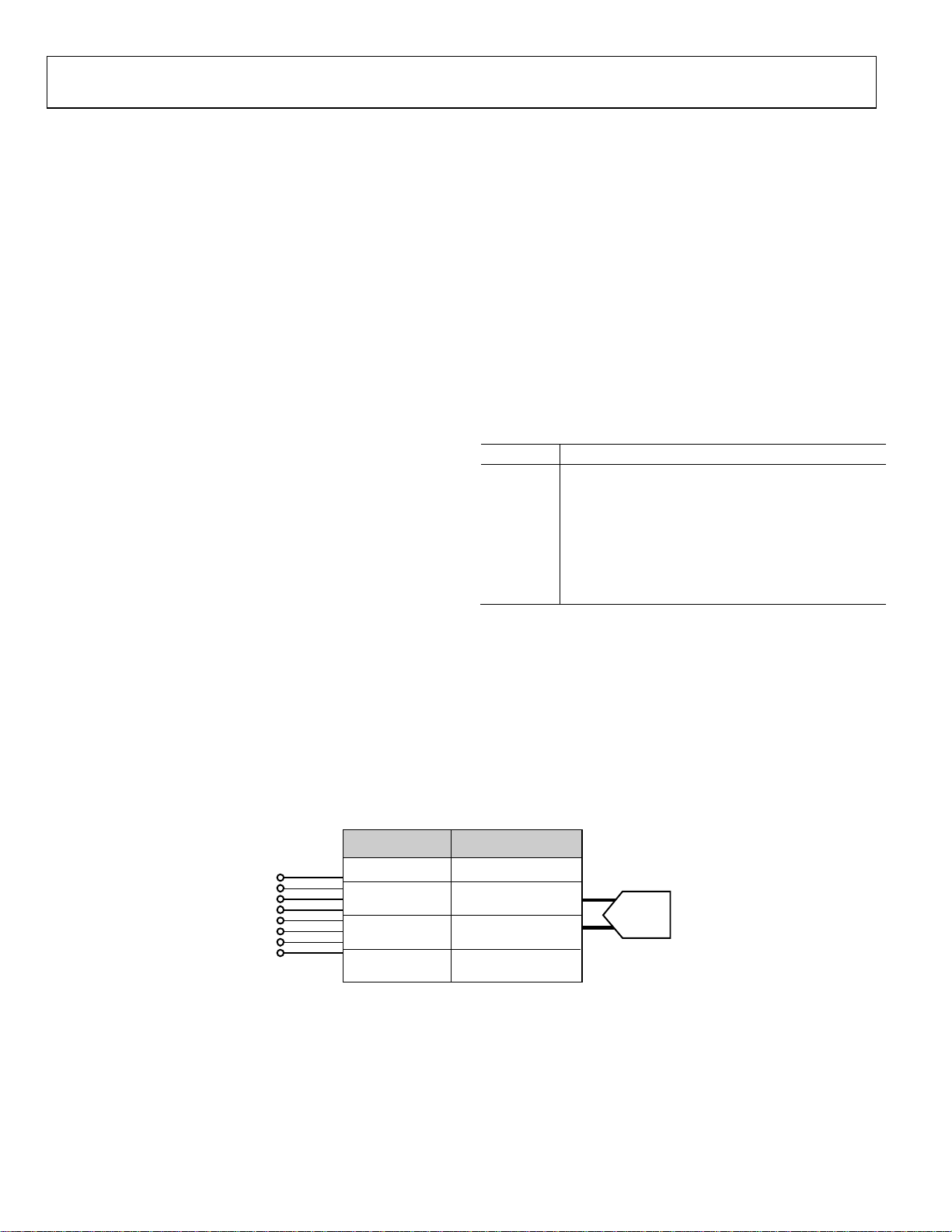

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

N3

CIN2

CI

CIN0

CIN1

14

13

15

16

PIN 1

1CIN4

INDICAT OR

2CIN5

AD7148

3CIN6

TOP VIEW

(Not to Scale)

4CIN7

5

6

BIAS

SHIELD

NOTES

1. THE EXPO SED PAD IS NOT CONNECTED I NTERNALLY.

FOR INCREASED RE LIABILITY OF THE SOLDE R JOINT

AND MAXIMUM THERMAL CAPABILIT Y, IT I S RECOMMENDED

THAT THE PAD BE S OLDERED TO THE GROUND PLANE.

AC

Figure 4. Pin Configuration

Table 6. Pin Function Descriptions

Pin No. Mnemonic Description

1 CIN4 Capacitance Sensor Input.

2 CIN5 Capacitance Sensor Input.

3 CIN6 Capacitance Sensor Input.

4 CIN7 Capacitance Sensor Input.

5 AC

CDC Active Shield Output. Connect to external shield.

SHIELD

6 BIAS Bias Node for Internal Circuitry. Requires 100 nF capacitor to ground.

7 GND Ground Reference Point for All Circuitry.

8 VCC Supply Voltage.

9 V

Serial Interface Operating Voltage Supply.

DRIVE

10 SDA I2C Serial Data Input/Output. SDA requires pull-up resistor.

11 SCLK Clock Input for Serial Interface.

12

INT

General-Purpose Open-Drain Interrupt Output. Programmable polarity; requires pull-up resistor.

13 CIN0 Capacitance Sensor Input.

14 CIN1 Capacitance Sensor Input.

15 CIN2 Capacitance Sensor Input.

16 CIN3 Capacitance Sensor Input.

17 EPAD

The exposed pad is not connected internally. For increased reliability of the solder joint and maximum

thermal capability, it is recommended that the pad be soldered to the ground plane.

12 INT

11 SCLK

10 SDA

V

9

DRIVE

8

7

CC

V

GND

07155-004

Rev. A | Page 7 of 56

AD7148

m

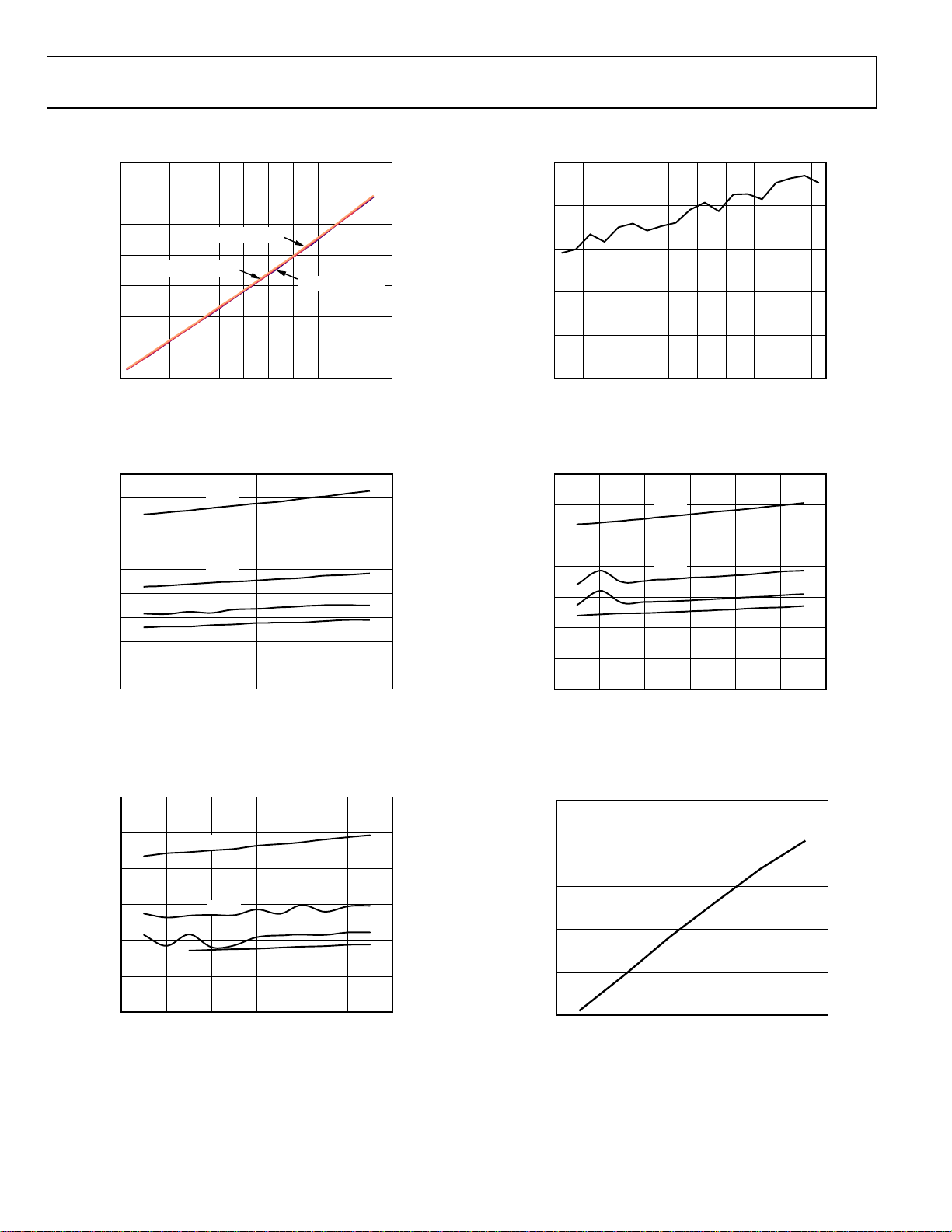

TYPICAL PERFORMANCE CHARACTERISTICS

935

2.5

915

895

875

(µA)

CC

I

855

835

815

795

DECIMATION = 128

2.6 3.7

2.7 2.8 2.9 3.0 3.1 3.2 3.3 3.4 3.5 3.6

DECIMATION = 64

V

(V)

CC

DECIMATION = 256

Figure 5. Supply Current vs. Supply Voltage

180

160

140

120

100

(μA)

CC

80

I

60

40

20

0

2.5 3.7

2.7 2.9 3.1 3.3 3.5

200ms

400ms

600ms

800ms

(V)

V

CC

Figure 6. Low Power Supply Current vs. Supply Voltage,

Decimation Rate = 256

2.0

1.5

(µA)

CC

I

1.0

0.5

07155-005

0

2.7

2.8 2.9 3.0 3.1 3.2 3.3 3.4 3. 5 3.6

VCC(V)

07155-008

Figure 8. Shutdown Supply Current vs. Supply Voltage

70

60

50

40

(μA)

CC

I

30

20

10

07155-006

0

2.5 3.72.72.93.13.33.5

200ms

400ms

VCC(V)

600ms

800ms

07155-009

Figure 9. Low Power Supply Current vs. Supply Voltage,

Decimation Rate = 64

0.12

0.10

0.08

A)

(

0.06

CC

I

0.04

0.02

0

2.5 3.7

2.7 2.9 3.1 3.3 3.5

200ms

400ms

600ms

800ms

V

(V)

CC

Figure 7. Low Power Supply Current vs. Supply Voltage

Decimation Rate = 128

07155-007

1150

1100

1050

(µA)

CC

I

1000

950

900

0

100 200 300 400 500

AC

CAPACITIVE LOAD (pF)

SHIELD

Figure 10. Supply Current vs. Capacitive Load on CIN

07155-010

Rev. A | Page 8 of 56

AD7148

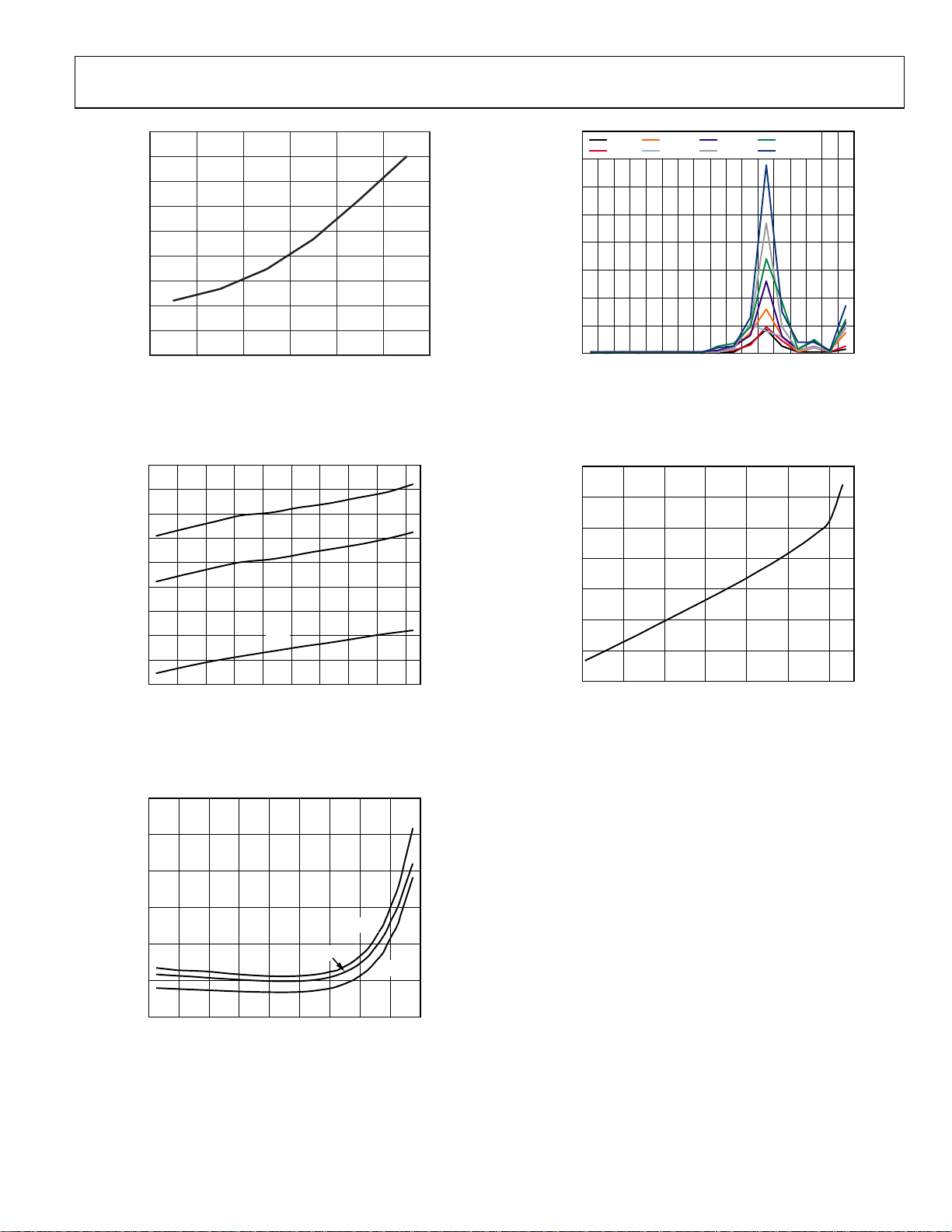

µ

A

A

58000

56000

54000

52000

50000

48000

CDC CODE (d)

46000

44000

42000

40000

0

100 200 300 400 500

AC

CAPACITIVE L OAD (pF)

SHIELD

Figure 11. CDC Output Code vs. Capacitive Load on AC

SHIELD

6

07155-04

160

25mV 75mV 125mV 175mV

50mV 100mV 150mV 200mV

140

120

100

80

60

CDC NOISE p-p (LSB)

40

20

0

25

50

100

200

400

800

1600

3200

6400

SINE WAVE F REQUENCY (Hz)

51200

12800

25600

102400

204800

Figure 14. Power Supply Sine Wave Rejection, VCC = 3.6 V

07155-013

409600

819200

1640000

960

940

920

900

880

(µA)

CC

860

I

840

820

800

780

–60 –40 –20 0 20 40 60 80 100 120

3.6V

3.3V

2.6V

TEMPERATURE (°C)

Figure 12. Supply Current vs. Temperature

12

10

8

A)

(

6

CC

I

4

2

0

–45 135

–25–51535557595115

TEMPERATURE (°C)

3.6V

3.3V

1

07155-01

2.6V

2

07155-01

35

30

25

NCE (pF)

20

CIT

15

10

INPUT CAP

5

0

0 10000 20000 30000 40000 50000 60000

CDC OUTPUT CO DE

Figure 15. CDC Linearity, V

= 3.3 V

CC

07155-014

Figure 13. Shutdown Supply Current vs. Temperature

Rev. A | Page 9 of 56

AD7148

THEORY OF OPERATION

The AD7148 is a capacitance-to-digital converter (CDC) with

on-chip environmental compensation, intended for use in portable

systems requiring high resolution user input. The internal circuitry

consists of a 16-bit, ∑-∆ converter that converts a capacitive

input signal into a digital value. There are eight input pins on

the AD7148: CIN0 to CIN7. A switch matrix routes the input

signals to the CDC. The result of each capacitance-to-digital

conversion is stored in on-chip registers. The host subsequently

reads the results over the serial interface. The AD7148 has an

2

I

C interface, ensuring that the part is compatible with a wide

range of host processors.

The AD7148 interfaces with up to eight external capacitance

sensors. These sensors can be arranged as buttons, scroll bars,

wheels, or as a combination of sensor types. The external sensors

consist of an electrode on a single or multiple layer PCB that

interfaces directly to the AD7148.

The AD7148 can be set up to implement any set of input sensors

by programming the on-chip registers. The registers can also

be programmed to control features such as averaging, offsets,

and gains for each of the external sensors. There is an on-chip

sequencer to control how each of the capacitance inputs

is polled.

The AD7148 has on-chip digital logic and 528 words of RAM

that are used for environmental compensation. The effects of

humidity, temperature, and other environmental factors can

affect the operation of capacitance sensors. Transparent to the

user, the AD7148 performs continuous calibration to compensate for these effects, allowing the AD7148 to give error-free

results at all times.

The AD7148 requires minimal companion software that runs

on the host or other microcontroller to implement high resolution

sensor functions, such as scroll bars or wheels. However, no

companion software is required to implement buttons. Button

sensors are implemented on chip, entirely in digital logic.

The AD7148 can be programmed to operate in either full power

mode or low power, automatic wake-up mode. The automatic

wake-up mode is particularly suited for portable devices that

require low power operation, providing the user with significant

power savings and full functionality.

The AD7148 has an interrupt output,

data has been placed into the registers.

INT

, to indicate when new

INT

is used to interrupt

the host on sensor activation. The AD7148 operates from a 2.6 V to

3.6 V supply and is available in a 16-lead, 4 mm × 4 mm LFCSP.

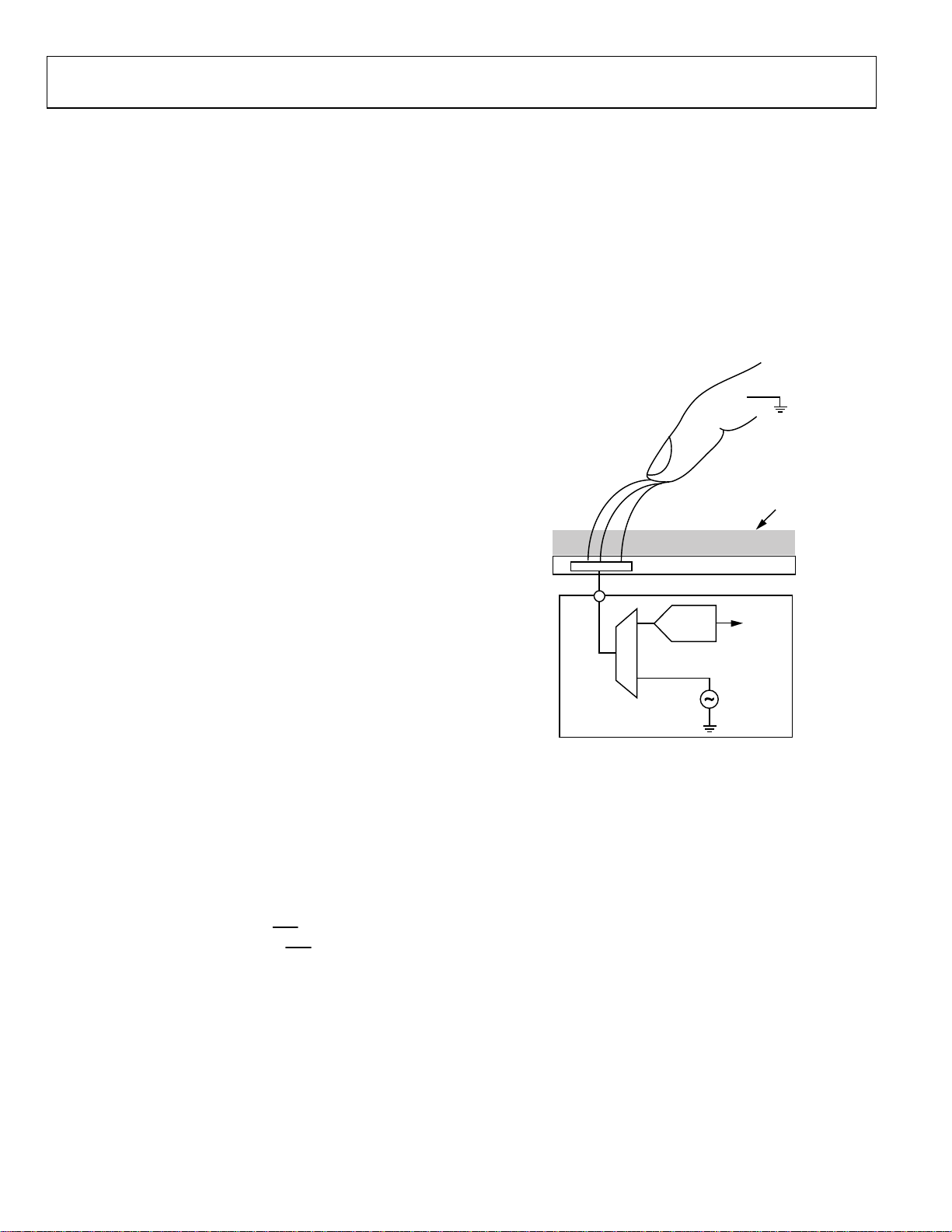

CAPACITANCE SENSING THEORY

The AD7148 measures capacitance changes from sensors where

one plate is connected to ground. The sensor electrode on the

PCB makes up one plate of a virtual capacitor. The other plate

of the capacitor is the user’s finger, which is grounded with

respect to the sensor input.

The AD7148 first outputs an excitation signal to charge the plate

of the capacitor. When the user comes close to the sensor, the

virtual capacitor is formed, with the user acting as the second

capacitor plate.

PLASTIC CO VER

SENSOR PCB

Σ-Δ

ADC

MUX

AD7148

Figure 16. Capacitance Sensing Method

A square wave excitation signal is applied to the CINx input during

the conversion, and the modulator continuously samples the

charge going through the CINx pin. The output of the modulator

is processed via a digital filter, and the resulting digital data is

stored in the CDC_RESULT_Sx registers for each conversion

stage, located at Address 0x00B to Address 0x012.

16-BIT

DATA

EXCITATION

SIGNAL

250kHz

07155-0015

Rev. A | Page 10 of 56

AD7148

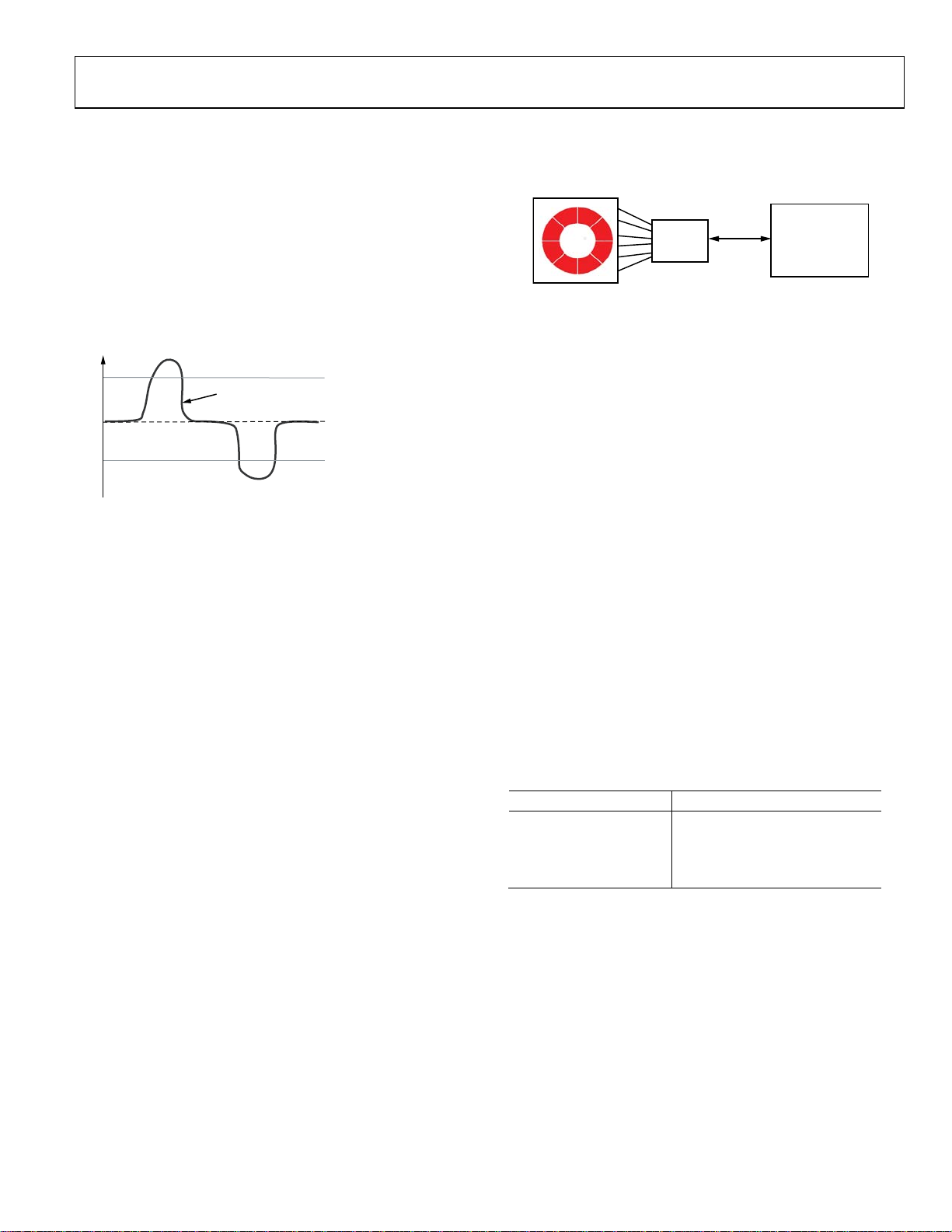

Registering a Sensor Activation

When a user approaches a sensor, the total capacitance associated

with that sensor changes and is measured by the AD7148. When

the capacitance changes to such an extent that a set threshold

is exceeded, the AD7148 registers this as a sensor activation.

On-chip threshold limits are used to determine when sensor activation occurs. Figure 17 shows the change in CDC_RESULT_Sx

that occurs when a user activates a sensor. The sensor is deemed

to be active only when the value of CDC_RESULT_Sx is either

greater than the value of STAGEx_HIGH_THRESHOLD or less

than the value of STAGEx_LOW_THRESHOLD.

SENSOR ACTIV E (A)

STAGEx_HIG H_THRESHOLD

CDC_RESULT_Sx

AMBIENT OR

UTPUT CODES

CDC O

SENSOR ACTIVE (B)

Figure 17. Sensor Activation Thresholds

NO-TOUCH VALUE

STAGEx_LOW_THRESHO LD

In Figure 17, two different sensor activations are shown. Sensor

Activate (A) occurs when a sensor is connected to the positive

input of the converter. In this case, when a user activates the

sensor, there is an increase in the CDC code, and the value of

CDC_RESULT_Sx exceeds the value of STAGEx_HIGH_

THRESHOLD. Sensor Active (B) occurs when the sensor is

connected to the negative input of the converter. In this case, when

a user activates the sensor, there is a decrease in the CDC code,

and the value of CDC_RESULT_Sx becomes less than the value of

STAGEx_LOW_THRESHOLD.

For each conversion stage, the STAGEx_HIGH_THRESHOLD

and the STAGEx_LOW_THRESHOLD registers are in Register

Bank 3. The values in these registers are updated automatically

by the AD7148 due to its environmental calibration and adaptive

threshold logic.

At power-up, the values in the STAGEx_HIGH_THRESHOLD

and STAGEx_LOW_THRESHOLD registers are the same as those

in the STAGEx_OFFSET_HIGH and STAGEx_OFFSET_LOW

registers in Register Bank 2. The user must program the STAGEx_

OFFSET_HIGH and STAGEx_OFFSET_LOW registers on device

power-up. See the Environmental Calibration section for more

information.

Complete Solution for Capacitance Sensing

Analog Devices, Inc., provides a complete solution for capacitance

sensing. The two main elements of the solution are the sensor PCB

and the AD7148.

If the application requires high resolution sensors such as scroll

bars or wheels, software is required that runs on the host processor.

No position algorithm is required for button sensors.

07155-016

The memory requirements for the host depend on the sensor

and are typically 10 kB of code and 600 bytes of data memory,

depending on the sensor type.

SENSOR PCB

2

AD7148

Figure 18. Three-Part Capacitance Sensing Solution

SPI OR I

HOST PROCESSOR

C

1 MIPS

10kB ROM

600 BYTES RAM

07155-017

Analog Devices supplies the sensor PCB footprint design libraries

to the customer and supplies any necessary software on an opensource basis.

BIAS PIN

The BIAS pin (Pin 6) is connected internally to the bias node in

the AD7148. To ensure correct operation of the AD7148, connect

a 100 nF capacitor between the BIAS pin and ground. The voltage

at the BIAS pin is V

/2.

CC

OPERATING MODES

The AD7148 has three operating modes. Full power mode, in

which the device is always fully powered, is suited for applications

where power is not a concern (for example, game consoles that

have an ac power supply). Low power mode, in which the part

automatically powers down, is tailored to give significant power

savings over full power mode and is suited for mobile applications

where power must be conserved. In shutdown mode, the part

shuts down completely.

The POWER_MODE bits of the PWR_CONTROL register

(Address 0x000[1:0]) set the operating mode on the AD7148.

Tabl e 7 shows the POWER_MODE settings for each operating

mode. To put the AD7148 into shutdown mode, set the

POWER_MODE bits to either 01 or 11.

Table 7. POWER_MODE Settings

POWER_MODE Bits Operating Mode

00 Full power mode

01 Shutdown mode

10 Low power mode

11 Shutdown mode

The power-on default setting of the POWER_MODE bits is 00,

full power mode.

Full Power Mode

In full power mode, all sections of the AD7148 remain fully

powered and converting at all times. While a sensor is being

touched, the AD7148 processes the sensor data. If no sensor is

touched, the AD7148 measures the ambient capacitance level

and uses this data for the on-chip compensation routines. In full

power mode, the AD7148 converts at a constant rate. See the CDC

Conversion Sequence Time section for more information.

Rev. A | Page 11 of

56

AD7148

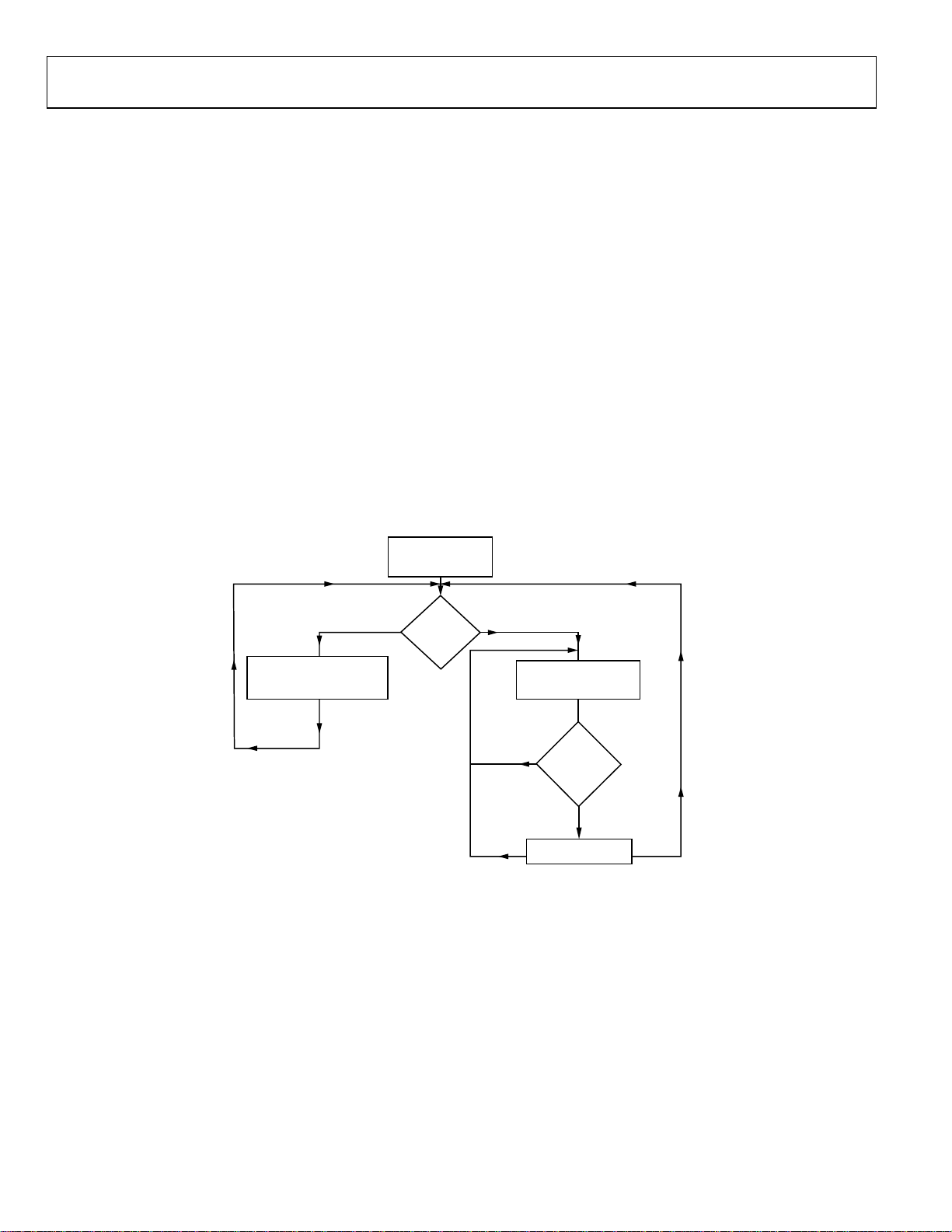

Low Power Mode

When in low power mode, the POWER_MODE bits are set

to 10 upon device initialization. If the external sensors are not

touched, the AD7148 reduces its conversion frequency, thereby

greatly reducing its power consumption. The part remains in

a reduced power state while the sensors are not touched. After a

delay defined by the LP_CONV_DELAY bits (200 ms, 400 ms,

600 ms or 800 ms), the AD7148 performs a conversion and uses

this data to update the compensation logic.

When an external sensor is touched, the AD7148 begins a conversion sequence every 25 ms to read back data from the sensors.

In low power mode, total current consumption is an average of the

current used during a conversion and the current used while the

AD7148 is waiting for the next conversion to begin. For example,

when LP_CONV_DELAY is 400 ms, the AD7148 typically uses

0.85 mA current for 25 ms and 14 A for 400 ms during the

conversion interval. Note that these conversion timings can be

altered through the register settings. See the CDC Conversion

Sequence Time section for more information.

AD7148 SETUP

AND INITI ALIZAT ION

POWER_MODE = 10

The time required for the AD7148 to transition from a full power

state to a reduced power state after the user stops touching the

external sensors is configurable. The PWR_DOWN_TIMEOUT

bits in the AMB_COMP_CTRL0 register (Address 0x002[13:12])

control the time delay before the AD7148 transitions to the reduced

power state after the user stops touching the sensors.

Low Latency from Touch to Response

In low power mode, the AD7148 remains in a low power state until

proximity is detected on any one of the external sensors. When

proximity is detected, the AD718 is automatically configured into

the full power mode operation, thus converting each sequence

every 36 ms. Using this method, the latency delay is minimized

because the AD7148 is operating in full power mode by the time

the user physically makes contact with a sensor.

CONVERSION SEQUENCE

EVERY LP_CONV_DELAY

UPDATE COMP ENSATIO N

LOGI C DATA PATH

USER IN

NO

PROXIMITY

TO SENSOR?

Figure 19. Low Power Mode Operation

YES

CONVERSIO N SEQUENCE

SENSOR READBACK

YES

EVERY 36ms FOR

USER IN

PROXIMITY

TO SENSOR?

NO

PROXIMITY TIMER

COUNT DOWN

TIMEOUT

07155-018

Rev. A | Page 12 of 56

AD7148

CAPACITANCE-TO-DIGITAL CONVERTER

The capacitance-to-digital converter on the AD7148 has a Σ-

architecture with 16-bit resolution. There are eight possible inputs

to the CDC that are connected to the input of the converter

through a switch matrix. The sampling frequency of the CDC

is 250 kHz.

OVERSAMPLING THE CDC OUTPUT

The decimation rate, or oversampling ratio, is determined by

the DECIMATION bits of the PWR_CONTROL register

(Address 0x000[9:8]), as listed in Tab l e 8 .

Table 8. CDC Decimation Rate

CDC Output Rate

DECIMATION Bits Decimation Rate

per Stage (ms)

00 256 3.072

01 128 1.536

10 64 0.768

11 64 0.768

The decimation process on the AD7148 is an averaging process,

during which a number of samples are taken, and the averaged

result is output. Due to the architecture of the digital filter used,

the number of samples taken (per stage) is equal to 3× the decimation rate. That is, 3 × 256 samples or 3 × 128 samples are averaged

to obtain each stage result.

The decimation process reduces the amount of noise present in

the final CDC result. However, the higher the decimation rate,

the lower the output rate per stage; thus, a trade-off is possible

between a noise-free signal and speed of sampling.

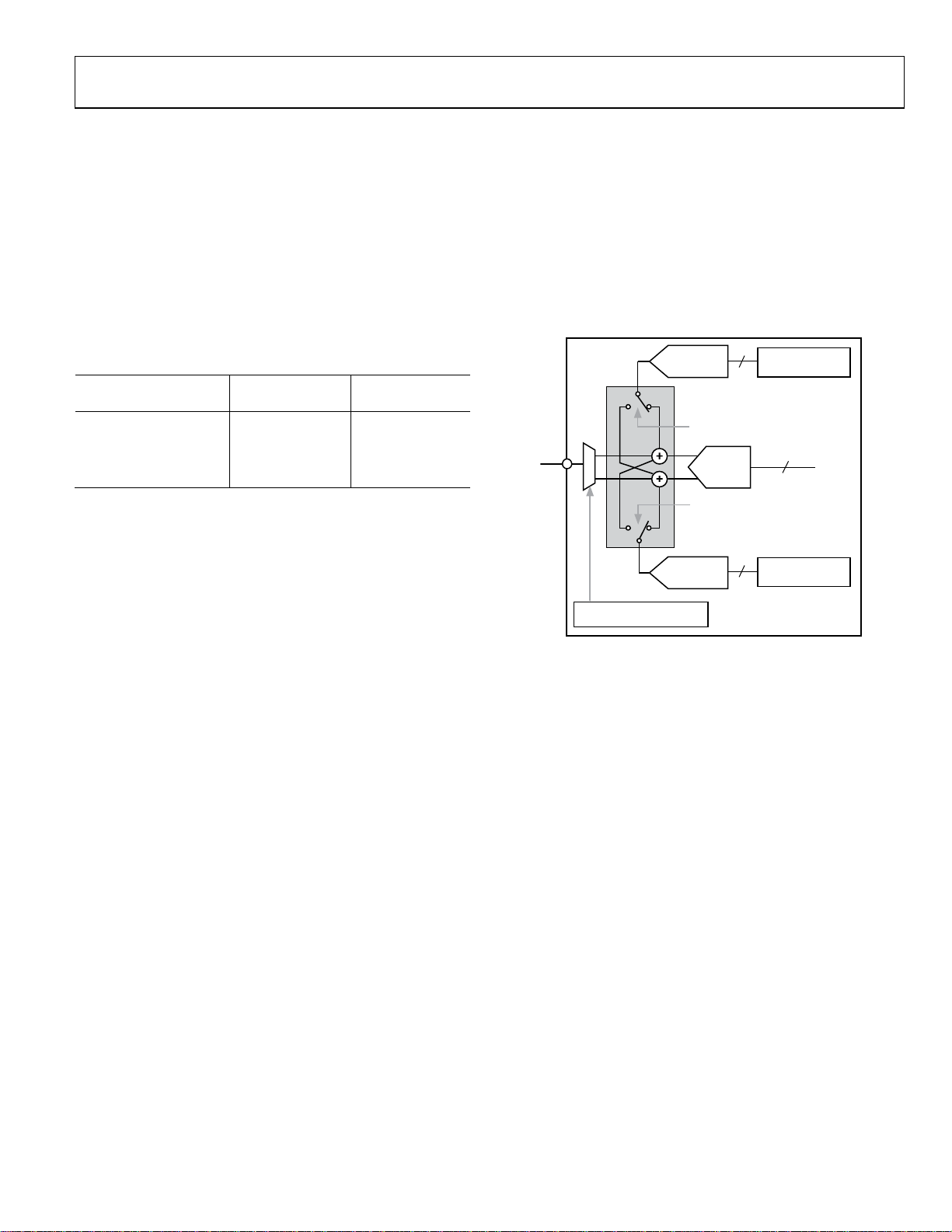

CAPACITANCE SENSOR OFFSET CONTROL

There are two programmable DACs on board the AD7148 to

null the effect of any stray capacitances on the CDC measurement.

These offsets are due to stray capacitance to ground. Best practice

is to ensure that the CDC output for any stage is approximately

equal to midscale (~32,700) when no sensor is active.

The simplified block diagram in Figure 20 shows how to apply

the STAGEx_OFFSET registers to null the offsets. The 6-bit

POS_AFE_OFFSET and NEG_AFE_OFFSET bits program the

offset DAC to provide 0.32 pF resolution offset adjustment over a

range of 20 pF. Apply the positive and negative offsets to either the

positive or the negative CDC input using the NEG_AFE_OFFSET

and POS_AFE_OFFSET bits.

This process is required only once during the initial capacitance

sensor characterization.

6

POS_AFE_OFFSET

POS_AFE_OFFSET_SWAP BIT

+

16-BIT

CDC

_

NEG_AFE_OFFSET_SWAP BIT

16

6

NEG_AFE_OFFSET

7155-019

CIN

CINx_CONNECTION_SETUP

Figure 20. Analog Front-End Offset Control

BITS

+DAC

(20pF RANGE)

–DAC

(20pF RANGE)

CONVERSION SEQUENCER

The AD7148 has an on-chip sequencer to implement conversion

control for the input channels. Up to eight conversion stages

can be performed in one sequence. Each of the eight conversion

stages can measure the input from a different sensor. By using

the Bank 2 registers, each stage can be uniquely configured to

support multiple capacitance sensor interface requirements. For

example, a slider sensor can be assigned to STAGE0 through

STAGE7, or a button sensor can be assigned to STAGE0. For each

conversion stage, the input mux that connects the CINx inputs to the

converter can have a unique setting.

Rev. A | Page 13 of 56

AD7148

The AD7148 on-chip sequence controller provides conversion

control, beginning with STAGE0. Figure 21 shows a block diagram

of the CDC conversion stages and CINx inputs. A conversion

sequence is defined as a sequence of CDC conversions starting

at STAGE0 and ending at the stage determined by the value that

is programmed using the SEQUENCE_STAGE_NUM bits in

the PWR_CONTROL register (Address 0x000[7:4]). Depending

on the number and type of capacitance sensors that are used,

not all conversion stages are required. Use the SEQUENCE_

STAGE_NUM bits to set the number of conversions in one

sequence, depending on the sensor interface requirements. For

example, these bits are set to 0005 if the CINx inputs are mapped

to only six stages. In addition, set the STAGEx_CAL_EN register

according to the number of stages that are used.

STAGE7

STAGE6

STAGE5

STAGE4

STAGE3

STAGE2

STAGE1

STAGE0

CIN0

CIN1

CIN2

CIN3

CIN4

CIN5

CIN6

CIN7

SWITCH MATRIX

Figure 21. CDC Conversion Stages

Σ-Δ

16-BIT

ADC

E

C

N

E

U

Q

E

S

N

O

I

S

R

E

V

N

O

C

07155-020

The number of required conversion stages depends completely

on the number of sensors attached to the AD7148. Figure 22 shows

how many conversion stages are required for each sensor and

how many inputs to the AD7148 each sensor requires.

A button sensor generally requires one sequencer stage; however,

it is possible to configure two button sensors to operate differentially. Only one button from the pair can be activated at a time;

pressing both buttons together results in neither button being

activated. This configuration requires one conversion stage (see

Figure 22, B2 and B3).

A wheel sensor requires eight stages, and a slider requires two

stages. The result from each stage is used by the host software to

determine user position on the slider or wheel. The algorithms that

perform this process are available from Analog Devices, free of

charge, on signing a software license.

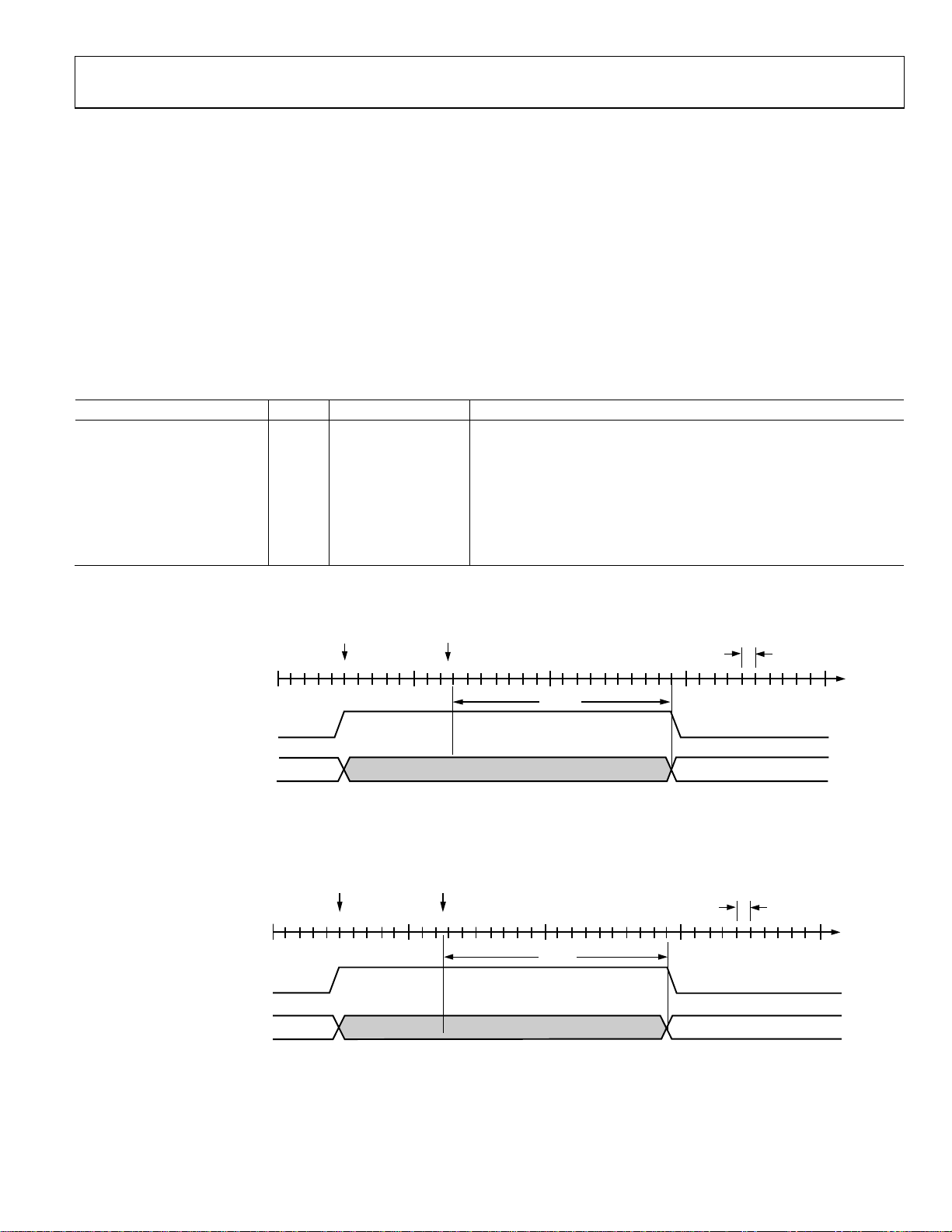

CDC CONVERSION SEQUENCE TIME

The time required for one complete measurement for all eight

stages by the CDC is defined as the CDC conversion sequence

time. The SEQUENCE_STAGE_NUM and DECIMATION bits

determine the conversion time, as shown in Tab le 9 .

For example, while operating with a decimation rate of 128,

if the SEQUENCE_STAGE_NUM bits are set to 0005 for the

conversion of six stages in a sequence, the conversion sequence

time is 9.216 ms.

AD7148

SEQUENCER

STAGE0

+

CDC

–

STAGE1

+

CDC

–

STAGE1

+

CDC

–

STAGE1

WHEEL

+

CDC

–

STAGE1

+

CDC

–

STAGE1

+

CDC

–

STAGE1

+

CDC

–

STAGE1

+

CDC

–

Figure 22. Sequencer Setup for Sensors

Rev. A | Page 14 of 56

BUTTONS

SLIDER

B1

B2

B3

AD7148

SEQUENCER

STAGE0

+

CDC

–

STAGE1

+

CDC

–

AD7148

SEQUENCER

STAGE3

+

CDC

–

STAGE4

+

CDC

–

07155-021

AD7148

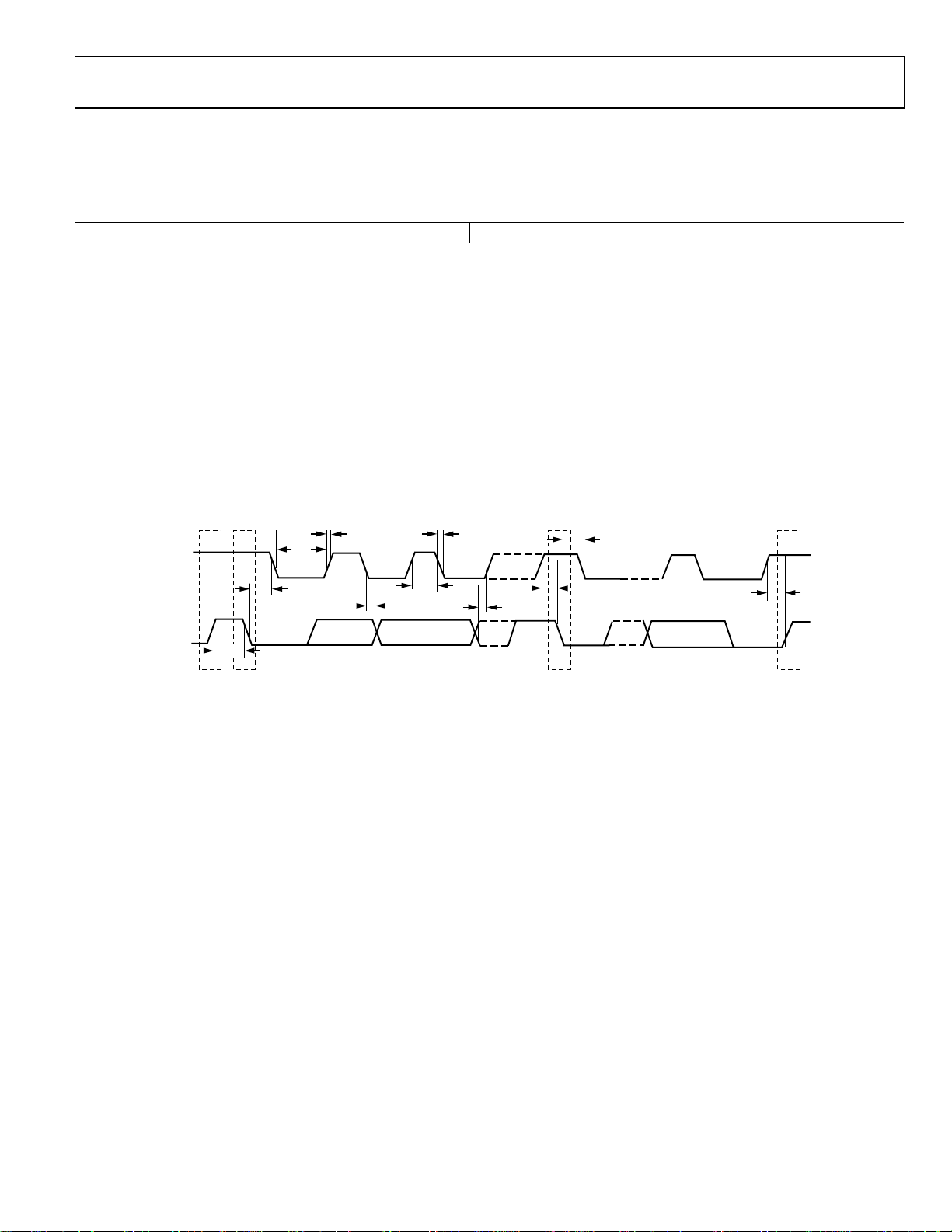

Table 9. CDC Conversion Times for Full Power Mode

Conversion Time (ms)

SEQUENCE_STAGE_NUM

0 0.768 1.536 3.072

1 1.536 3.072 6.144

2 2.304 4.608

3 3.072 6.144

4 3.84 7.68 15.36

5 4.608 9.216

6 5.376 10.752

7 6.144 12.288 24.576

Decimation = 64 Decimation = 128 Decimation = 256

9.216

12.288

18.432

21.504

Full Power Mode CDC Conversion Sequence Time

The full power mode CDC conversion sequence time for all eight

stages is set by configuring the SEQUENCE_STAGE_NUM

and DECIMATION bits, as outlined in Table 9 .

Figure 23 shows a simplified timing diagram of the full power

CDC conversion time. The full power mode CDC conversion

time, t

CONVERSI ON

, is set using Tabl e 9.

CONV_FP

t

CONV_FP

CONVERSI ON

CDC

SEQUENCE N

Figure 23. Full Power Mode CDC Conversion Sequence Time

CONVERSI ON

SEQUENCE N+1

CONVERSI ON

SEQUENCE N+2

07155-022

Low Power Mode CDC Conversion Sequence Time with Delay

The frequency of each CDC conversion, while operating in the

low power automatic wake-up mode, is controlled by using the

LP_CONV_DELAY bits located at Address 0x000[3:2], in addition to the registers listed in Tab le 9 . This feature provides some

flexibility for optimizing the conversion time to meet system

requirements vs. AD7148 power consumption.

For example, maximum power savings is achieved when the

LP_CONV_DELAY bits (Address 0x000[3:2] are set to 11. With

a setting of 11, the AD7148 automatically wakes up, performing

a conversion every 800 ms.

Table 10. LP_CONV_DELAY Settings

LP_CONV_DELAY Bits Delay Between Conversions (ms)

00 200

01 400

10 600

11 800

Figure 24 shows a simplified timing example of the low power

CDC conversion time. As shown, the low power CDC conversion

time is set by t

CDC

CONVERSI ON

Figure 24. Low Power Mode CDC Conversion Sequence Time

and the LP_CONV_DELAY bits.

CONV_FP

t

CONV_LP

t

CONV_FP

CONVERSION

SEQUENCE N

LP_CONV_DELAY

CONVERSION

SEQUENCE N+1

CDC CONVERSION RESULTS

Certain high resolution sensors require the host to read back

the CDC conversion results for processing. The registers required

for host processing are located in the Bank 3 registers. The host

processes the data readback from these registers using a software

algorithm to determine position information.

In addition to the results registers found in the Bank 3 registers,

the AD7148 provides the 16-bit CDC output data directly, starting

at Address 0x00B of the Bank 1 registers. Reading back the CDC

16-bit conversion data register allows for customer-specific application data processing.

7155-023

Rev. A | Page 15 of 56

AD7148

CAPACITANCE SENSOR INPUT CONFIGURATION

Each input connection from the external capacitance sensors to

the AD7148 converter can be uniquely configured by using the

registers in Bank 2 (see Tabl e 39 through Tabl e 42). These registers

are used to configure input pin connection setups, sensor offsets,

sensor sensitivities, and sensor limits for each stage. Each sensor

can be individually optimized. For example, a button sensor

connected to STAGE0 can have different sensitivity and offset

values from those of a button with a different function that is

connected to a different stage.

CINx INPUT MULTIPLEXER SETUP

The CINx_CONNECTION_SETUP register bits provide options

for connecting the sensor input pins to the CDC (see Tab l e 39

and Tabl e 40 ).

The AD7148 has an on-chip multiplexer to route the input

signals from each pin to the input of the converter. Each input

pin can be tied to either the negative or the positive input of the

CDC, or it can be left floating. Each input can also be internally

connected to the BIAS signal to help prevent cross coupling. If

an input is not used, always connect it to BIAS.

Connecting a CINx input pin to the positive CDC input results

in an increase in CDC output code when the corresponding sensor

is activated. Connecting a CINx input pin to the negative CDC

input results in a decrease in CDC output code when the corresponding sensor is activated.

The AD7148 performs a sequence of eight conversions. The

multiplexer can have different connection settings for each of

the eight conversions by using the CINx_CONNECTION_

SETUP bits. For example, CIN0 can be connected to the

negative CDC input or left floating. The same holds true for all

eight conversion stages.

Two bits in each sequence stage register control the mux setting for

the input pin, as shown in Figure 25.

CINx_CONNECTION

_SETUP BITS

CIN0

CIN1

CIN2

CIN3

CIN4

CIN5

CIN6

CIN7

00

01 CINx CONNECTED T O

10

11

Figure 25. Input Mux Configuration Options

SINGLE-ENDED CONNECTIONS TO THE CDC

A single-ended connection to the CDC is defined as having one

CINx input connected to either the positive or the negative CDC

input. A differential connection to the CDC is defined as having

one CINx input connected to the positive CDC input and a second

CINx input connected to the negative input of the CDC.

When a single-ended connection to the CDC is made in any

stage, the SE_CONNECTION_SETUP bits in the STAGEx_

CONNECTION_SETUP registers should be applied. These bits

ensure that, during a single-ended connection to the CDC, the

input paths to both terminals are matched. This matching of

input paths, in turn, improves the power supply rejection of the

converter measurement.

Table 11. Application of SE_CONNECTION_SETUP Bits

Bit Values Description

00 Do not use.

01

10

11

If more than one CINx input is connected to either the positive

or negative input of the converter for the same conversion, set

SE_CONNECTION_SETUP = 11. For example, if CIN0 and

CIN3 are connected to the positive input of the CDC,

SE_CONNECTION_SETUP = 11.

CIN SETTI NG

CINx FLOAT ING

NEGATIVE CDC INP UT

CINx CONNECTED T O

POSITIVE CDC INPUT

CINx CONNECTED T O

BIAS

Single-ended connection. For this stage, there is one

CINx connected to the positive CDC input.

Single-ended connection. For this stage, there is one

CINx connected to the negative CDC input.

Differential connection. For this stage, there is one

CINx connected to the negative CDC input and one

CINx connected to the positive CDC input.

+

CDC

–

7155-024

Rev. A | Page 16 of 56

AD7148

NONCONTACT PROXIMITY DETECTION

The AD7148 internal signal processing continuously monitors

all capacitance sensors for noncontact proximity detection. This

feature provides the ability to detect when a user is approaching

a sensor, at which time all internal calibration is immediately

disabled while the AD7148 is automatically configured to detect

a valid contact.

The proximity control register bits are described in Ta ble 1 2. The

FP_PROXIMITY_CNT and LP_PROXIMITY_CNT register bits

(Address 0x002[11:4]) control the length of the calibration disable

period after the user leaves the sensor and proximity is no longer

active in full and low power modes.

Table 12. Proximity Control Registers (See Figure 30)

Bits Length Register Address Description

FP_PROXIMITY_CNT 4 bits 0x002[7:4] Calibration disable time in full power mode.

LP_PROXIMITY_CNT 4 bits 0x002[11:8] Calibration disable time in low power mode.

FP_PROXIMITY_RECAL 10 bits 0x004[9:0]

LP_PROXIMITY_RECAL 6 bits 0x004[15:10]

PROXIMITY_RECAL_LVL 8 bits 0x003[7:0]

PROXIMITY_DETECTION_RATE 6 bits 0x003[13:8]

USER LEAVES SENSOR

AREA HERE

CDC CONVERSI ON SEQ UENCE

PROXIM ITY DET ECTIO N

(INTERNAL)

(INTERNAL)

USER APPROACHES

SENSOR HERE

12345 678910111213141516

The calibration is disabled during this time and is enabled

again at the end of this period, provided that the user is no longer

approaching, or in contact with, the sensor. Figure 26 and Figure

show examples of how these registers are used to set the full

and l

ow power mode calibration disable periods.

The calibration disable period in full power mode is equal to

FP_PROXIMITY_CNT × 16 × time taken for one conversion

sequence in full power mode.

The calibration disable period in low power mode is equal to

LP_PROXIMITY_CNT × 4 × time taken for one conversion

sequence in low power mode.

Full power mode proximity recalibration time.

Low power mode proximity recalibration time.

Proximity recalibration level. This value, multiplied by 16, controls the

sensitivity of Comparator 2 in Figure 30.

Proximity detection rate. This value, multiplied by 16, controls the

sensitivity of Comparator 1 in Figure 30.

t

CONV_FP

t

CALDIS

CDC CONVERSI ON SEQ UENCE

PROXIM ITY DET ECTIO N

CALIBRATION

(INTERNAL)

(INTERNAL)

(INTERNAL)

CALIBRATION

(INTERNAL)

CALIBRATION DISABLED

CALIBRATION ENABL ED

Figure 26. Full Power Mode Proximity Detection Example with FP_PROXIMITY_CNT = 1

USER APPROACHES

SENSOR HERE

12345678910111213141516

NOTES

1. SEQUENCE CONVERSION TIME

2. PROXIMITY IS SET WHEN USER APPROACHES THE SENSOR AT WHICH TIME THE INTERNAL CALI BRATION IS DISABLED.

t

= (

t

3.

CALDIS

× LP_PROXIMITY_CNT × 4)

CONV_LP

USER LEAVES

SENSOR AREA HERE

t

=

CONV_LP

t

CONV_FP

1718192021222324

t

CALDIS

+ LP_CONV_DELAY

t

CONV_LP

CALIBRATION ENABL EDCALIBRATION DISA BLED

Figure 27. Low Power Mode Proximity Detection with LP_PROXIMITY_CNT = 4

Rev. A | Page 17 of 56

07155-025

026

07155-

Loading...

Loading...