Analog Devices AD568 Datasheet

12-Bit Ultrahigh Speed

a

FEATURES

Ultrahigh Speed: Current Settling to 1 LSB in 35 ns

High Stability Buried Zener Reference on Chip

Monotonicity Guaranteed Over Temperature

10.24 mA Full-Scale Output Suitable for Video

Applications

Integral and Differential Linearity Guaranteed Over

Temperature

0.3" “Skinny DIP” Packaging

Variable Threshold Allows TTL and CMOS

Interface

MIL-STD-883 Compliant Versions Available

PRODUCT DESCRIPTION

The AD568 is an ultrahigh-speed, 12-bit digital-to-analog converter (DAC) settling to 0.025% in 35 ns. The monolithic device is fabricated using Analog Devices’ Complementary Bipolar

(CB) Process. This is a proprietary process featuring high-speed

NPN and PNP devices on the same chip without the use of dielectric isolation or multichip hybrid techniques. The high speed

of the AD568 is maintained by keeping impedance levels low

enough to minimize the effects of parasitic circuit capacitances.

The DAC consists of 16 current sources configured to deliver a

10.24 mA full-scale current. Multiple matched current sources

and thin-film ladder techniques are combined to produce bit

weighting. The DAC’s output is a 10.24 mA full scale (FS) for

current output applications or a 1.024 V FS unbuffered voltage

output. Additionally, a 10.24 V FS buffered output may be generated using an onboard 1 kΩ span resistor with an external op

amp. Bipolar ranges are accomplished by pin strapping.

Laser wafer trimming insures full 12-bit linearity. All grades of

the AD568 are guaranteed monotonic over their full operating

temperature range. Furthermore, the output resistance of the

DAC is trimmed to 100 Ω ± 1.0%. The gain temperature coefficient of the voltage output is 30 ppm/°C max (K).

The AD568 is available in three performance grades. The

AD568JQ and KQ are available in 24-pin cerdip (0.3") packages

and are specified for operation from 0°C to +70°C. The

AD568SQ features operation from –55°C to +125°C and is also

packaged in the hermetic 0.3" cerdip.

Monolithic D/A Converter

AD568

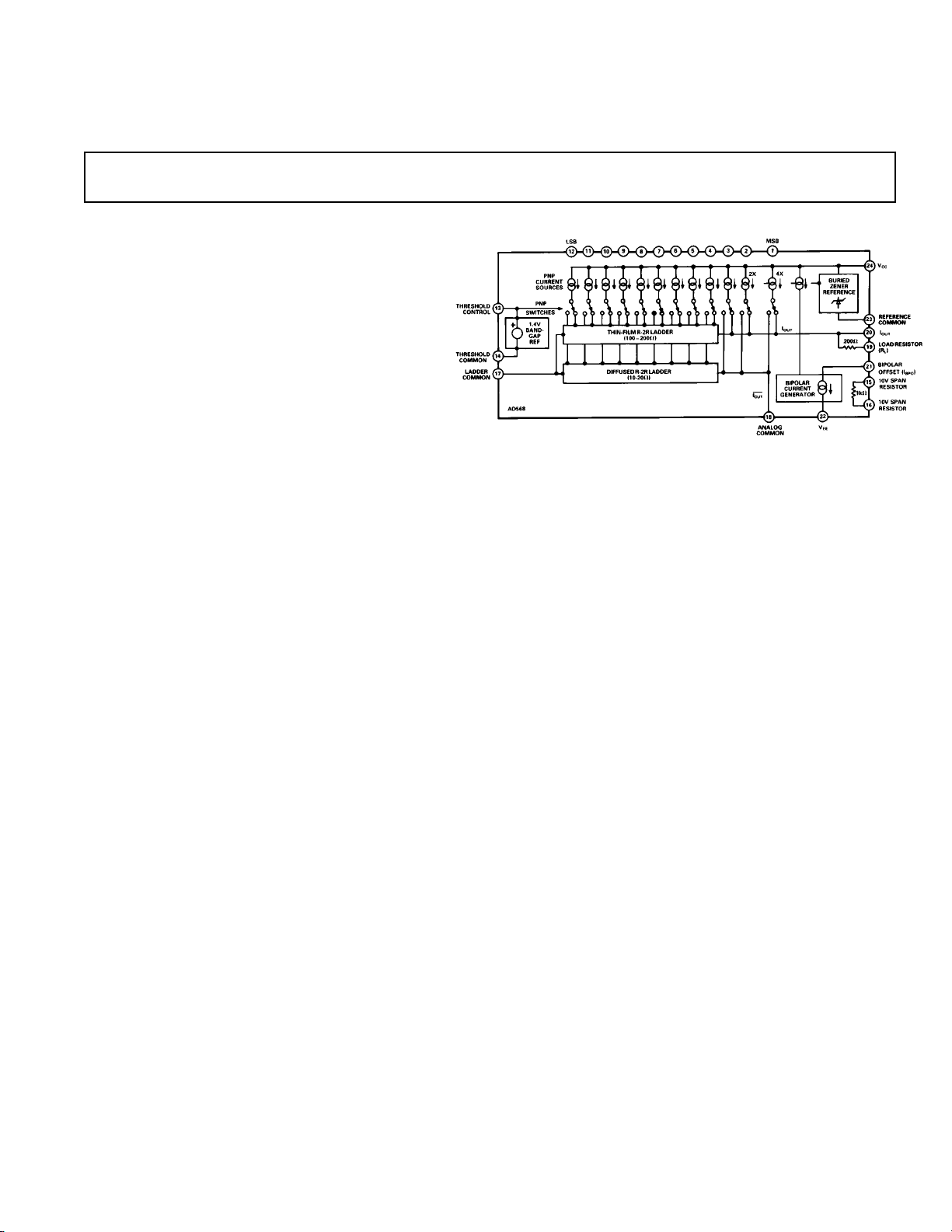

FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

1. The ultrafast settling time of the AD568 allows leading edge

performance in waveform generation, graphics display and

high speed A/D conversion applications.

2. Pin strapping provides a variety of voltage and current output

ranges for application versatility. Tight control of the absolute output current reduces trim requirements in externallyscaled applications.

3. Matched on-chip resistors can be used for precision scaling in

high speed A/D conversion circuits.

4. The digital inputs are compatible with TTL and +5 V

CMOS logic families.

5. Skinny DIP (0.3") packaging minimizes board space requirements and eases layout considerations.

6. The AD568 is available in versions compliant with MILSTD-883. Refer to the Analog Devices Military Products

Databook or current AD568/883B data sheet for detailed

specifications.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD568–SPECIFICATIONS

(@ = +258C, VCC, VEE = 615 V unless otherwise noted)

Model AD568J AD568K AD568S

Min Typ Max Min Typ Max Min Typ Max Units

RESOLUTION 12 12 12 Bits

ACCURACY

1

Linearity –1/2 +1/2 –1/4 +1/4 –1/2 +1/2 LSB

T

to T

MIN

MIN

to T

MAX

MAX

Differential Nonlinearity –1 +1 –1/2 +1/2 –1 +1 LSB

T

Monotonicity GUARANTEED OVER RATED SPECIFICATION TEMPERATURE RANGE

–3/4 +3/4 –1/2 +1/2 –3/4 +3/4 LSB

–1 +1 –1 + 1 –1 –1 LSB

Unipolar Offset –0.2 +0.2 * * * * % of FSR

Bipolar Offset –1.0 +1.0 * * * * % of FSR

Bipolar Zero –0.2 +0.2 * * * * % of FSR

Gain Error –1.0 +1.0 * * * * % of FSR

TEMPERATURE COEFFICIENTS

2

Unipolar Offset –5 +5 –3 +3 –5 +5 ppm of FSR/°C

Bipolar Offset –30 +30 –20 +20 –30 +30 ppm of FSR/°C

Bipolar Zero –15+15••••ppm of FSR/°C

Gain Drift –50 +50 –30 +30 –50 +50 ppm of FSR/°C

Gain Drift (I

) –150 +150 * * * * ppm of FSR/°C

OUT

DATA INPUTS

Logic Levels (T

V

IH

V

IL

Logic Currents (T

I

IH

I

IL

VTH Pin Voltage 1.4 * * V

MIN

to T

MIN

MAX

to T

)

MAX

2.0 7.0****V

0.0 0.8 ****V

)

–10 0 +10 *** *** µA

–0.5 –60 –100 * * * * –100 –200 µA

CODING BINARY, OFFSET BINARY

CURRENT OUTPUT RANGES 0 to 10.24, ± 5.12 mA

VOLTAGE OUTPUT RANGES 0 to 1.024, ± 0.512 V

COMPLIANCE VOLTAGE –2 +1.2 * * * * V

OUTPUT RESISTANCE

Exclusive of R

Inclusive of R

L

L

160 200 240 * * Ω

99 100 101 * * Ω

SETTLING TIME

Current to

±0.025% 35 * * ns to 0.025% of FSR

±0.1% 23 * * ns to 0.1% of FSR

Voltage

50 Ω Load3, 0.512 V p-p,

to 0.025% 37 * * ns to 0.025% of FSR

to 0.1% 25 * * ns to 0.1% of FSR

to 1% 18 * * ns to 1% of FSR

75 Ω Load3, 0.768 V p-p,

to 0.025% 40 * * ns to 0.025% of FSR

to 0.1% 25 * * ns to 0.1% of FSR

to 1% 20 * * ns to 1% of FSR

100 Ω (Internal RL)3, 1.024 V p-p,

to 0.025% 50 * * ns to 0.025% of FSR

to 0.1% 38 * * ns to 0.1% of FSR

to 1% 24 * * ns to 1% of FSR

Glitch Impulse

4

350 * * pV-sec

Peak Amplitude 15 * * % of FSR

FULL-SCALE TRANSlTlON

5

10% to 90% Rise Time 11 * * ns

90% to 10% Fall Time 11 * * ns

POWER REQUIREMENTS

+13.5 V to +16.5 V 27 32 ** * * mA

–13.5 V to –16.5 V –7 –8 ** * * mA

Power Dissipation 525 625 * * * * mW

PSRR 0.05 * * % of FSR/V

TEMPERATURE RANGE

Rated Specification

2

0 +70 0 +70 –55 +125 °C

Storage –65 +150 * * * * °C

NOTES

*Same as AD568J.

1

Measured in I

2

Measured in V

3

Total Resistance. Refer to Figure 3,

4

At the major carry, driven by HCMOS logic. See text for further explanation.

5

Measured in V

mode.

OUT

mode, unless otherwise specified. See text for further information.

OUT

mode.

OUT

Specifications shown in boldface are tested on all production units at final electrical test.

Specifications subject to change without notice.

–2–

REV. A

AD568

WARNING!

ESD SENSITIVE DEVICE

MSBLSB

23

45

2X 4X

BIPOLAR

I

OUT

CURRENT

GENERATOR

18

ANALOG

COMMON

THRESHOLD

CONTROL

THRESHOLD

COMMON

LADDER

COMMON

13

14

17

SWITCHES

1.4V

BAND-

GAP

REF

AD568

PNP

CURRENT

SOURCES

PNP

THIN-FILM R-2R LADDER

(100 - 200Ω)

DIFFUSED R-2R LADDER

(10 - 20Ω)

6789101112 1

Figure 1. Functional Block Diagram

ABSOLUTE MAXIMUM RATINGS

1

VCC to REFCOM . . . . . . . . . . . . . . . . . . . . . . . . 0 V to +18 V

V

to REFCOM . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to –18 V

EE

REFCOM to LCOM . . . . . . . . . . . . . . . . . +100 mV to –10 V

ACOM to LCOM . . . . . . . . . . . . . . . . . . . . . . . . . . . ±100 mV

THCOM to LCOM . . . . . . . . . . . . . . . . . . . . . . . . . . ±500 mV

SPANs to LCOM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±12 V

I

to LCOM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±5 V

BPO

I

to LCOM . . . . . . . . . . . . . . . . . . . . . . . . . . . –5 V to V

OUT

TH

Digital Inputs to THCOM . . . . . . . . . . . . . –500 mV to +7.0 V

Voltage Across Span Resistor . . . . . . . . . . . . . . . . . . . . . . 12 V

V

to THCOM . . . . . . . . . . . . . . . . . . . . . . –0.7 V to +1.4 V

TH

Logic Threshold Control Input Current . . . . . . . . . . . . . 5 mA

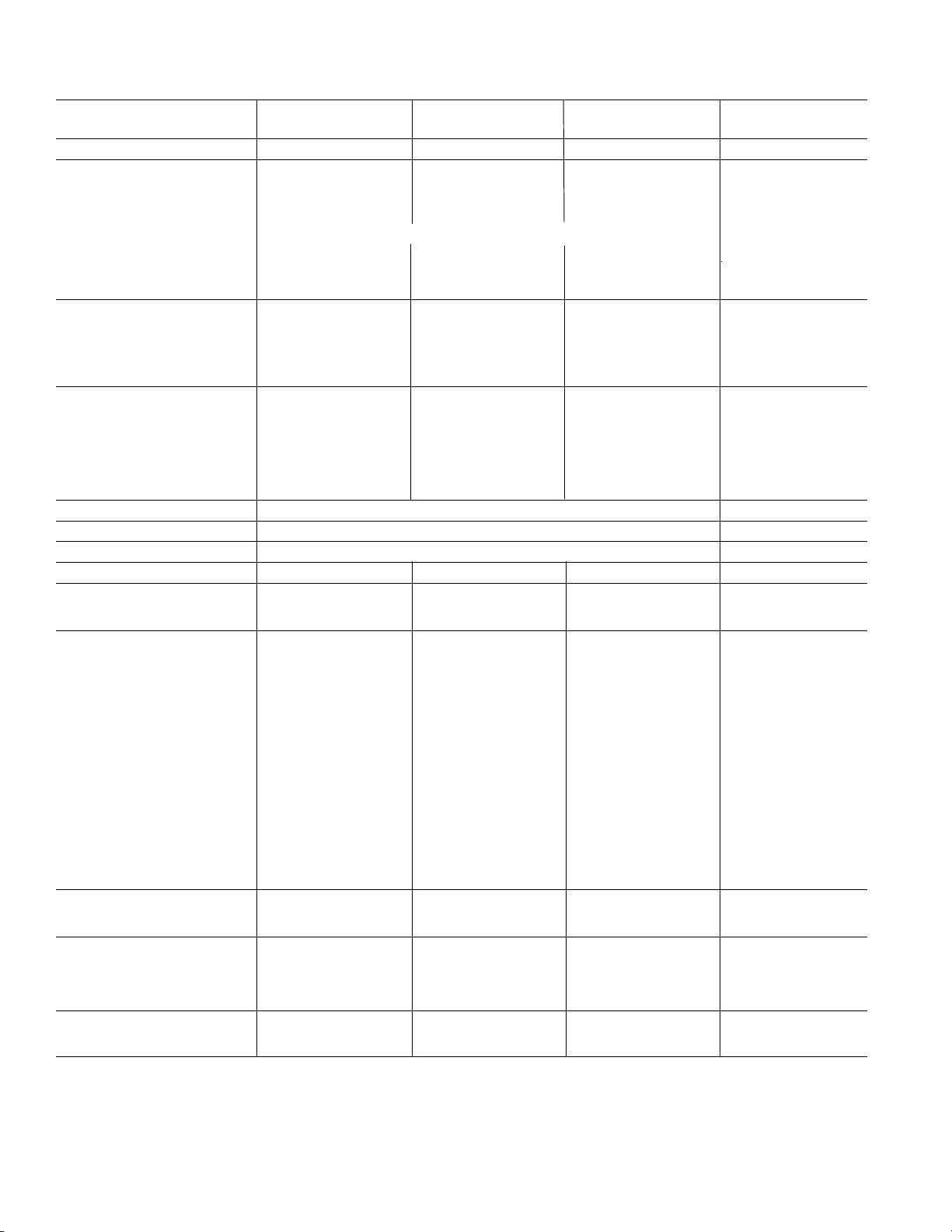

PIN CONFIGURATION

24

V

1kΩ

23

20

19

21

15

16

CC

REFERENCE

COMMON

I

OUT

LOAD RESISTOR

)

(R

L

BIPOLAR

OFFSET (I

BPO

10V SPAN

RESISTOR

10V SPAN

RESISTOR

)

BURIED

ZENER

REFERENCE

I

OUT

22

V

EE

200Ω

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . 100 mW

Storage Temperature Range

Q (Cerdip) Package . . . . . . . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 175°C

Thermal Resistance

θ

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75°C/W

JA

θ

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25°C/W

JC

1

Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

Definitions

LINEARITY ERROR (also called INTEGRAL NONLINEARITY OR INL): Analog Devices defines linearity error as the

maximum deviation of the actual analog output from the ideal

output (a straight line drawn from 0 to FS) for any bit combination expressed in multiples of 1 LSB. The AD568 is laser

trimmed to 1/4 LSB (0.006% of FS) maximum linearity error at

+25°C for the K version and 1/2 LSB for the J and S versions.

DIFFERENTIAL LINEARITY ERROR (also called DIFFERENTIAL NONLINEARITY or DNL): DNL is the measure of

the variation in analog value, normalized to full scale, associated

with a 1 LSB change in digital input code. Monotonic behavior

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD568 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. A

ORDERING GUIDE

Linearity Voltage

Temperature Error Max Gain T.C.

Range 8C@ 258C Max ppm/8C

Model

l

Package Option

2

AD568JQ 24-Lead Cerdip (Q-24) 0 to +70 ±1/2 ±50

AD568KQ 24-Lead Cerdip (Q-24) 0 to +70 ± 1/4 ±30

AD568SQ 24-Lead Cerdip (Q-24) –55 to +125 ±1/2 ±50

NOTES

1

For details on grade and package offerings screened in accordance with MIL-STD-883, refer to the Analog Devices

Military Products Databook or current AD568/883B data sheet.

2

Q = Cerdip.

requires that the differential linearity error not exceed 1 LSB in

the negative direction.

MONOTONICITY: A DAC is said to be monotonic if the output either increases or remains constant as the digital input

increases.

UNIPOLAR OFFSET ERROR: The deviation of the analog

output from the ideal (0 V or 0 mA) when the inputs are set to

all 0s is called unipolar offset error.

BIPOLAR OFFSET ERROR: The deviation of the analog output from the ideal (negative half-scale) when the inputs are set

to all 0s is called bipolar offset error.

–3–

AD568

13

16

15

14

24

23

22

21

20

19

18

17

12

11

10

9

8

1

2

3

4

7

6

5

AD568

+15V

REFCOM

–15V

I

BPO

R

L

ACOM

LCOM

SPAN

SPAN

THCOM

VTH

I

OUT

DIGITAL

INPUTS

0.2µF

0.1µF

0.1µF

0.1µF

–15V+15V

ANALOG

GND PLANE

DIGITAL

GND PLANE

DIGITAL

SUPPLY

GROUND

100pF

+5V

ANALOG

OUTPUT

ANALOG

SUPPLY

GROUND

BIPOLAR ZERO ERROR: The deviation of the analog output

from the ideal half-scale output of 0 V (or 0 mA) for bipolar

mode when only the MSB is on (100 . . .00) is called bipolar

zero error.

GAIN ERROR: The difference between the ideal and actual

output span of FS –1 LSB, expressed in % of FS, or LSB, when

all bits are on.

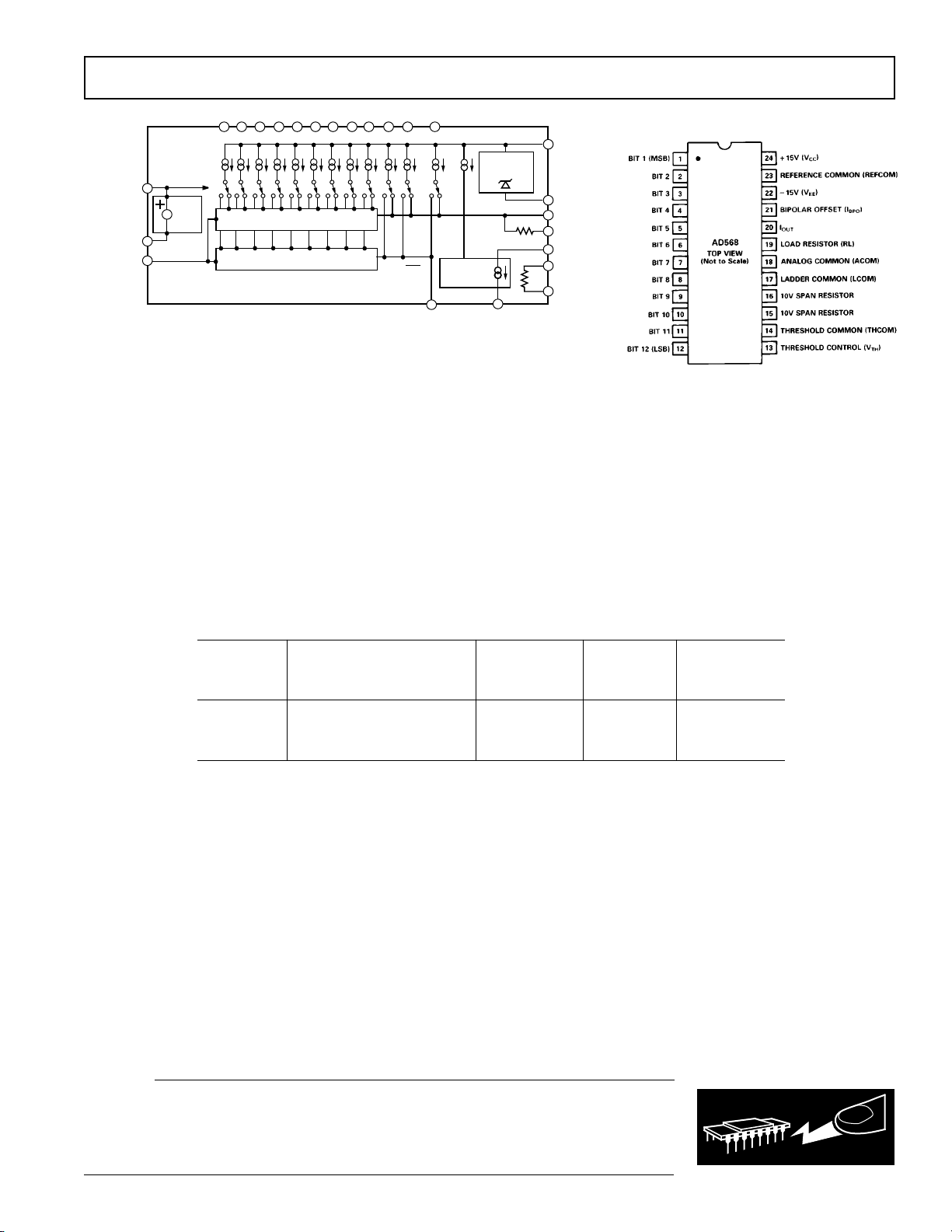

GLITCH IMPULSE: Asymmetrical switching times in a DAC

give rise to undesired output transients which are quantified by

0.8

0.6

0.4

OUTPUT – VOLTS

0 25050

100 150 200

TIME – ns

Figure 2. Glitch Impulse

their glitch impulse. It is specified as the net area of the glitch in

nV-sec or pA-sec.

COMPLIANCE VOLTAGE: The range of allowable voltage at

the output of a current-output DAC which will not degrade the

accuracy of the output current.

SETTLING TIME: The time required for the output to reach

and remain within a specified error band about its final value,

measured from the digital input transition.

–15V+15V

0.2µF

0.1µF

DIGITAL

INPUTS

1

2

3

4

5

6

7

8

9

10

11

12

REFCOM

AD568

THCOM

+15V

–15V

I

BPO

I

OUT

ACOM

LCOM

SPAN

SPAN

VTH

24

0.1µF

23

0.1µF

22

21

20

R

19

L

18

17

NC

16

15

NC

14

100pF

13

R

1kΩ

ANALOG

GND PLANE

TH

ANALOG

OUTPUT

ANALOG

SUPPLY

DIGITAL

GND PLANE

FERRITE BEADS

STACKPOLE 57-1392

OR

AMIDON FB-43B-101

OR EQUIVALENT

R

EXT

(OPTIONAL)

GROUND

DIGITAL

SUPPLY

GROUND

Connecting the AD568

UNBUFFERED VOLTAGE OUTPUT

Unipolar Configuration

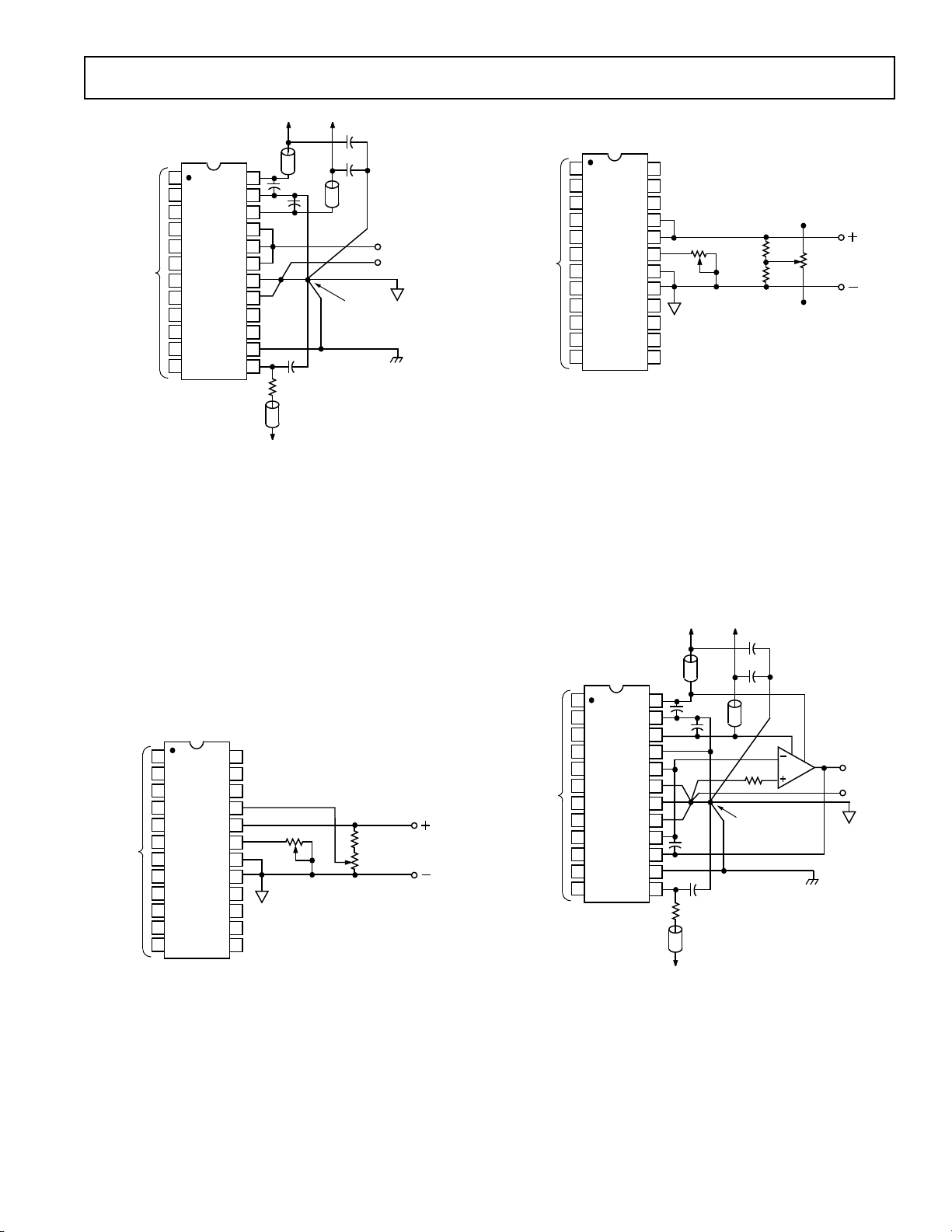

Figure 3 shows the AD568 configured to provide a unipolar 0 to

+1.024 V output range. In this mode, the bipolar offset terminal, Pin 21, should be grounded if not used for offset trimming.

The nominal output impedance of the AD568 with Pin 19

grounded has been trimmed to 100 Ω, ± 1%. Other output impedances can be generated with an external resistor, R

tween Pins 19 and 20. An R

total output resistance of 75 Ω, while an R

vide 50 Ω of output resistance. Note that since the full-scale

output current of the DAC remains 10.24 mA, changing the

load impedance changes the unbuffered output voltage accordingly. Settling time and full-scale range characteristics for these

load impedances are provided in the specifications table.

Bipolar Configuration

Figure 4 shows the connection scheme used to provide a bipolar

output voltage range of 1.024 V. The bipolar offset (–0.512 V)

occurs when all bits are OFF (00 . . . 00), bipolar zero (0 V) occurs when the MSB is ON with all other bits OFF (10 . . . 00),

and full-scale minus 1 LSB (0.51175 V) is generated when all

bits are ON (11 . . . 11). Figure 5 shows an optional bipolar

mode with a 2.048 V range. The scale factor in this mode will

not be as accurate as the configuration shown in Figure 4, because the laser-trimmed resistor R

equalling 300 Ω will yield a

EXT

L

EXT

is not used.

of 100 Ω will pro-

EXT

, be-

+5V

Figure 3. Unipolar Output Unbuffered 0 V to +1.024 V

Figure 4. Bipolar Output Unbuffered ±0.512 V

Figure 4 also demonstrates how the internal span resistor may

be used to bias the V

eliminates the requirement for an external R

pin (Pin 13) from a 5 V supply. This

TH

in applications

TH

that do not require the precision span resistor.

–4–

REV. A

AD568

13

16

15

14

24

23

22

21

20

19

18

17

12

11

10

9

8

1

2

3

4

7

6

5

AD568

I

BPO

R

L

ACOM

LCOM

I

OUT

DIGITAL

INPUTS

5.11kΩ

BIT 1

MSB

BIT 12

LSB

ANALOG

OUTPUT

(–0.512 TO

0.512V)

75Ω

GAIN

20Ω

20kΩ

V

EE

V

CC

ZERO

13

16

15

14

24

23

22

21

20

19

18

17

12

11

10

9

8

1

2

3

4

7

6

5

AD568

+15V

REFCOM

–15V

I

BPO

R

L

ACOM

LCOM

SPAN

SPAN

THCOM

VTH

I

OUT

DIGITAL

INPUTS

0.2µF

0.1µF

0.1µF

0.1µF

–15V+15V

ANALOG

GND PLANE

DIGITAL

GND PLANE

DIGITAL

SUPPLY

GROUND

100pF

+5V

ANALOG

OUTPUT

ANALOG

SUPPLY

GROUND

5pF

–VS+V

S

100Ω

R

TH

1kΩ

AD840

AMPLIFIER NOISE GAIN: 11

–15V+15V

0.2µF

0.1µF

REFCOM

AD568

THCOM

+15V

–15V

I

BPO

I

OUT

ACOM

LCOM

SPAN

SPAN

VTH

24

0.1µF

23

0.1µF

22

21

20

R

19

L

18

17

NC

16

15

NC

14

100pF

13

R

1kΩ

+5V

ANALOG

GND PLANE

GND PLANE

TH

DIGITAL

ANALOG

OUTPUT

ANALOG

SUPPLY

GROUND

DIGITAL

SUPPLY

GROUND

DIGITAL

INPUTS

1

2

3

4

5

6

7

8

9

10

11

12

Figure 5. Bipolar Output Unbuffered ±1.024 V

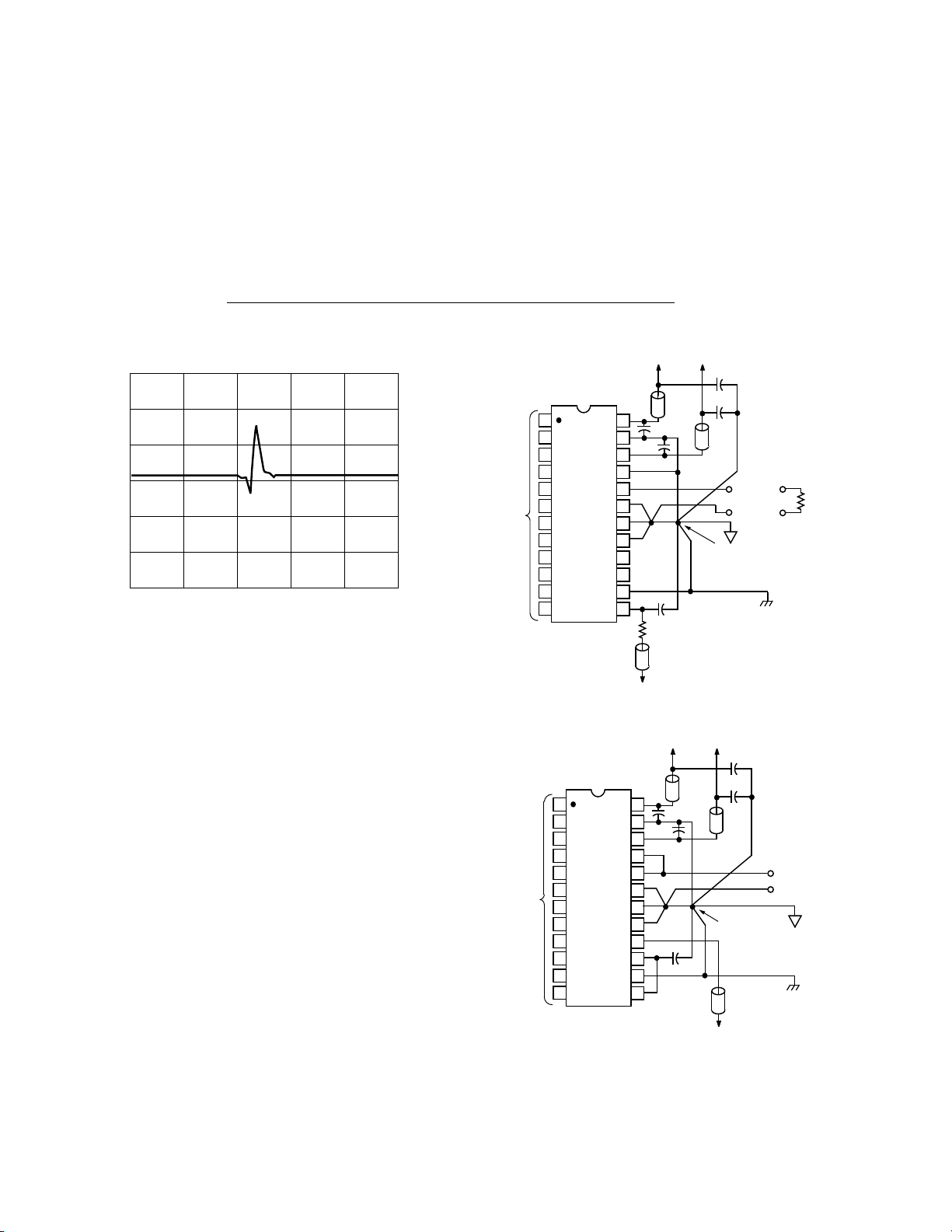

Optional Gan and Zero Adjustment

The gain and offset are laser trimmed to minimize their effects

on circuit performance. However, in some applications, it may

be desirable to externally reduce these errors further. In those

cases, the following procedures are suggested.

UNIPOLAR MODE: (Refer to Figure 6)

Step 1 – Set all bits (BIT 1–BIT 12) to Logic “0” (OFF)—note

the output voltage. This is the offset error.

Step 2 – Set all bits to Logic “1” (ON). Adjust the gain trim resistor so that the output voltage is equal to the desired full scale

minus 1 LSB plus the offset error measured in step 1.

Step 3 – Reset all bits to Logic “0” (OFF). Adjust the offset

trim resistor for 0 V output.

full scale at the DAC output. Note: this may slightly compromise the bipolar zero trim.

Figure 7. Bipolar Unbuffered Gain and Zero Adjust

BUFFERED VOLTAGE OUTPUT

For full-scale outputs of greater than 1 V, some type of external

buffer amplifier is required. The AD840 fills this requirement

perfectly, settling to 0.025% from a 10 V full-scale step in less

than 100 ns.

A 1 kΩ span resistor has been provided on chip for use as a

feedback resistor in buffered applications. Using R

SPAN

(Pins 15,

16) introduces a 100 mW code-dependent power source onto

the chip which may generate a slight degradation in linearity.

Maximum linearity performance can be realized by using an external span resistor.

1

BIT 1

MSB

2

AD568

3

4

5

6

7

8

9

10

11

BIT 12

12

LSB

DIGITAL

INPUTS

Figure 6. Unbuffered Unipolar Gain and Zero Adjust

BIPOLAR MODE (Refer to Figure 7)

Step 1 – Set bits to offset binary “zero” (10 . . . 00). Adjust the

zero resistor to produce 0 V at the DAC output. This removes

the bipolar zero error.

Step 2 – Set all bits to Logic “1” (ON). Adjust gain trim resistor

so the output voltage is equal to the desired full-scale minus

l LSB .

Step 3 – (Optional) If precise trimming of the bipolar offset is

preferred to trimming of bipolar zero: set all bits to Logic “0”

(OFF). Trim the zero resistor to produce the desired negative

REV. A

24

23

22

I

21

BPO

I

20

OUT

R

19

ACOM

LCOM

L

20Ω

18

17

16

15

14

13

GAIN

5.11kΩ

100Ω

OFFSET

ANALOG

OUTPUT

(0 TO 1.024V)

Figure 8. Unipolar Output Buffered 0 to –10.24V

Unipolar Inverting Configuration

Figure 8 shows the connections for producing a – 10.24 V fullscale swing. This configuration uses the AD568 in the current

output mode into a summing junction at the inverting input terminal of the external op amp. With the load resistor R

L

grounded, the DAC has an output impedance of 100 Ω. This

produces a noise gain of 11 from the noninverting terminal of

the op amp, and hence, satisfies the stability criterion of the

AD840 (stable at a gain of 10). The addition of a 5 pF compen-

–5–

Loading...

Loading...