ANALOG DEVICES AD5535 Service Manual

32-Channel, 14-Bit DAC with Full-Scale Output

Voltage Programmable from 50 V to 200 V

FEATURES GENERAL DESCRIPTION

High integration

32-channel, 14-bit DAC with integrated high voltage

output amplifier

Guaranteed monotonic

Housed in 15 mm × 15 mm CSP_BGA package

Full-scale output voltage

Programmable from 50 V to 200 V via reference input

700 μA drive capability

Integrated silicon diode for temperature monitoring

DSP-/microcontroller-compatible serial interface

1.2 MHz channel update rate

Asynchronous

RESET

facility

–10°C to +85°C temperature range

APPLICATIONS

Optical micro-electromechanical systems (MEMS)

Optical crosspoint switches

Micropositioning applications using piezoelectric actuators

Level setting in automotive test and measurement

The AD5535 is a 32-channel, 14-bit DAC with an on-chip high

voltage output amplifier. This device is targeted for optical

micro-electromechanical systems. The output voltage range is

programmable via the REF_IN pin. The output range is 0 V to

50 V when REF_IN = 1 V, and 0 V to 200 V when REF_IN = 4 V.

Each amplifier can source 700 μA, which is ideal for the

deflection and control of optical MEMS mirrors.

The selected DAC register is written to via the 3-wire interface.

The serial interface operates at clock rates of up to 30 MHz and

is compatible with DSP and microcontroller interface standards.

The device is operated with AV

2.7 V to 5.25 V, V

and V

= 210 V. REF_IN is buffered internally on the AD5535

PP

= −4.75 V to −5.25 V, V+ = 4.75 V to 5.25 V,

−

and should be driven from a stable reference source.

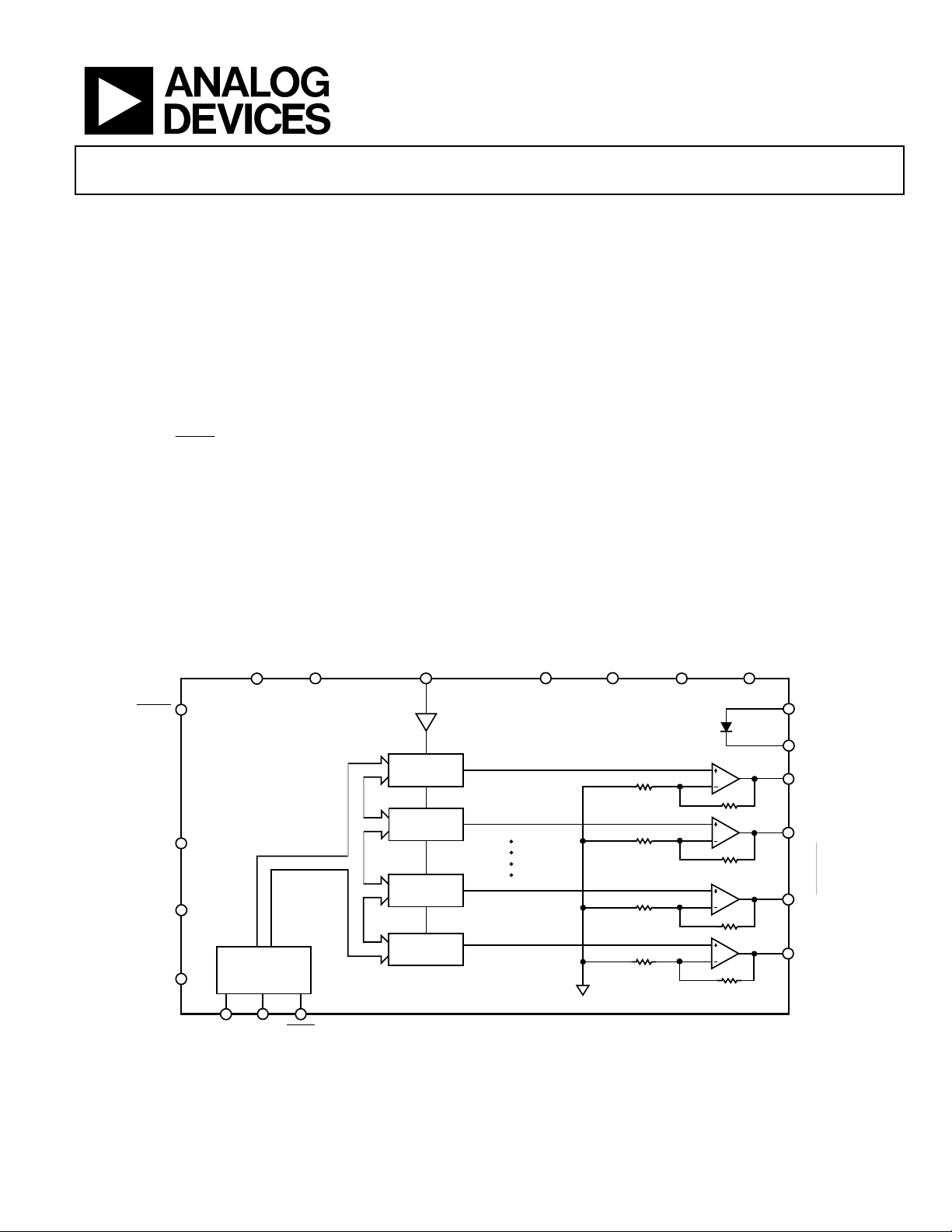

AD5535

= 4.75 V to 5.25 V, DVCC =

CC

RESET

DAC_GND

AGND

DGND

DV

AD5535

INTERFACE

CONTROL

LOGIC

SCLK

CC

D

IN

AV

CC

14-BIT BUS

SYNC

FUNCTIONAL BLOCK DIAGRAM

REF_IN

DAC

DAC

DAC

DAC

Figure 1.

V

PP

PGND

R1

R1

R1

R1

V

–

RF

RF

RF

RF

V

+

ANODE

CATHODE

V

0

OUT

1

V

OUT

30

V

OUT

31

V

OUT

05068-001

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice.

No license is granted by implication or otherwise under any patent or patent rights of Analog

Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

AD5535

TABLE OF CONTENTS

Features .............................................................................................. 1

Reset Function............................................................................ 12

Applications....................................................................................... 1

General Description......................................................................... 1

Functional Block Diagram .............................................................. 1

Specifications..................................................................................... 3

Timing Characteristics ................................................................ 5

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Typical Performance Characteristics............................................. 9

Te r mi n ol o g y .................................................................................... 11

Functional Description ..................................................................12

DAC Section................................................................................ 12

REVISION HISTORY

8/05—Rev. 0 to Rev. A

Changes to Table 3............................................................................ 6

Changes to Ordering Guide.......................................................... 16

Serial Interface............................................................................ 12

Microprocessor Interfacing....................................................... 12

Applications..................................................................................... 14

MEMS Mirror Control Application......................................... 14

IPC-221-Compliant Board Layout........................................... 14

Power Supply Sequencing and Decoupling

Recommendations

Guidelines for Printed Circuit Board Layout......................... 15

Outline Dimensions .......................................................................16

Ordering Guide .......................................................................... 16

...................................................................... 15

5/05—Revision 0: Initial Version

Rev. A | Page 2 of 16

AD5535

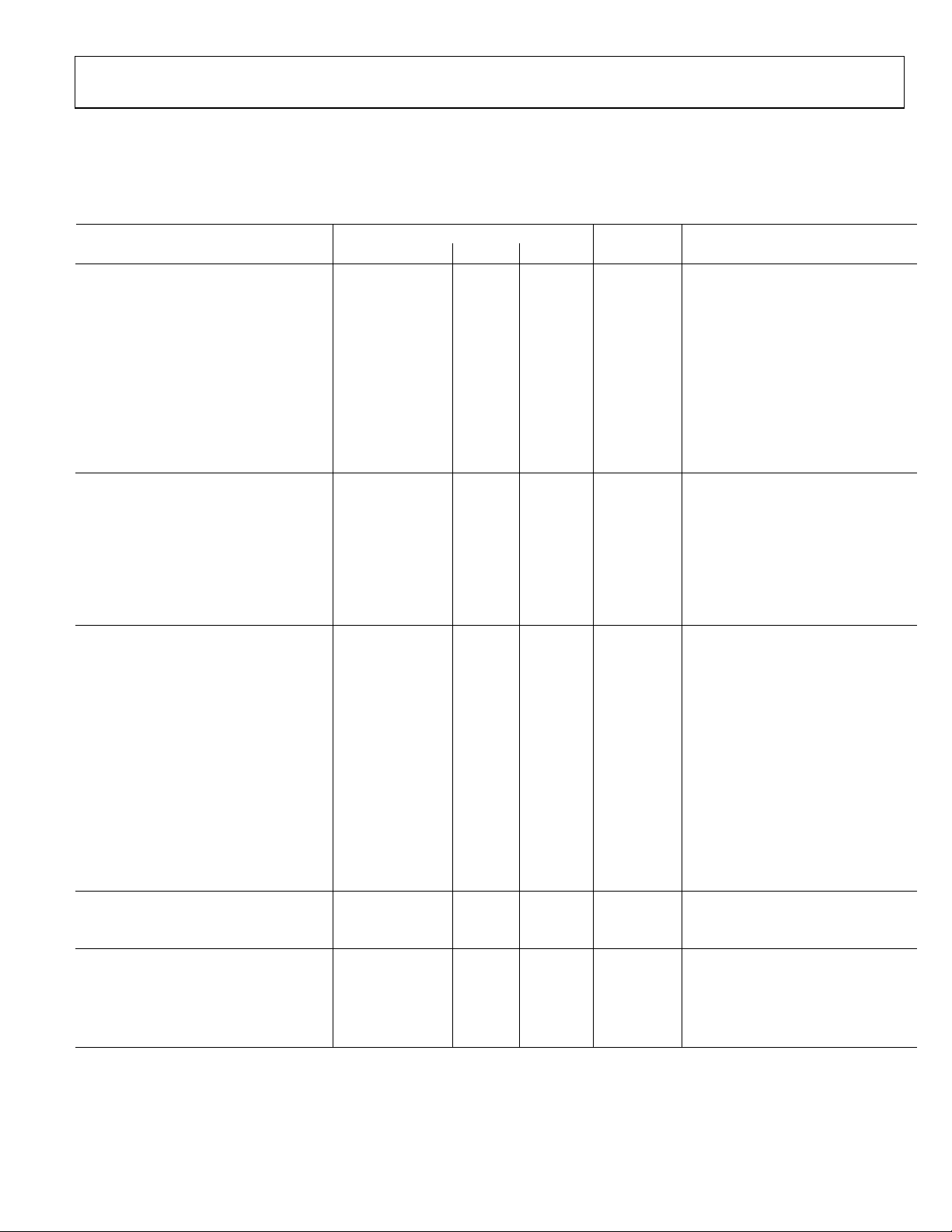

SPECIFICATIONS

VPP = 210 V, V− = −5 V, V+ = +5 V; AVCC = 5.25 V; DVCC = 2.7 V to 5.25 V; PGND = AGND = DGND = DAC_GND = 0 V;

REF_IN = 4.096 V; all outputs unloaded. All specifications T

Table 1.

Parameter

1

Min Typ Max

DC PERFORMANCE3

Resolution 14 Bits

Integral Nonlinearity (INL) ±0.1 % of FSR

Differential Nonlinearity (DNL) –1 ±0.5 +1 LSB Guaranteed monotonic

Zero-Code Voltage 1 2.5 V

Output Offset Error –2 +2 V

Offset Drift 0.02 mV/°C

Voltage Gain 47.5 50 52.5 V/V

Gain Temperature Coefficient 5 ppm/°C

Channel-to-Channel Gain Match

4

–5 +5 %

Full-Scale Voltage Drift 3 ppm/°C

OUTPUT CHARACTERISTICS

Output Voltage Range

3

2.5 VPP − 10 V

Output Impedance 50 Ω

Resistive Load

Capacitive Load

4, 5

4

200 pF

1 MΩ

Short-Circuit Current 0.7 mA

DC Crosstalk

DC Power Supply Rejection (PSRR), V

4

3 LSB

70 dB

PP

AC CHARACTERISTICS4

Settling Time

¼ to ¾ Scale Step 30 μs No load

65 μs 200 pF load

1 LSB Step 10 μs No load

10 μs 200 pF load

Slew Rate 10 V/μs No load

3 V/μs 200 pF load

–3 dB Bandwidth 5 kHz

Output Noise Spectral Density 4.5 μV/√Hz Measured at 10 kHz

0.1 Hz to 10 Hz Output Noise Voltage 1 mV p-p

Digital-to-Analog Glitch Impulse 10 nV-s 1 LSB change around major carry

Analog Crosstalk 13 μV-s

Digital Feedthrough 1 nV-s

VOLTAGE REFERENCE, REF_IN

Input Voltage Range

6

4

AVCC must exceed REF_IN by 1.15 V min

1 4.096 V

Input Current 1.25 μA

TEMPERATURE MEASUREMENT DIODE

4

Peak Inverse Voltage, PIV 5 V Cathode to anode

Forward Diode Drop, VF 0.65 0.8 V IF = 100 μA, anode to cathode

Forward Diode Current, IF 100 μA Anode to cathode

VF Temperature Coefficient, T

C

−2.20 mV/°C Anode to cathode

to T

MIN

A Grade

, unless otherwise noted.

MAX

2

Unit Conditions/Comments

Rev. A | Page 3 of 16

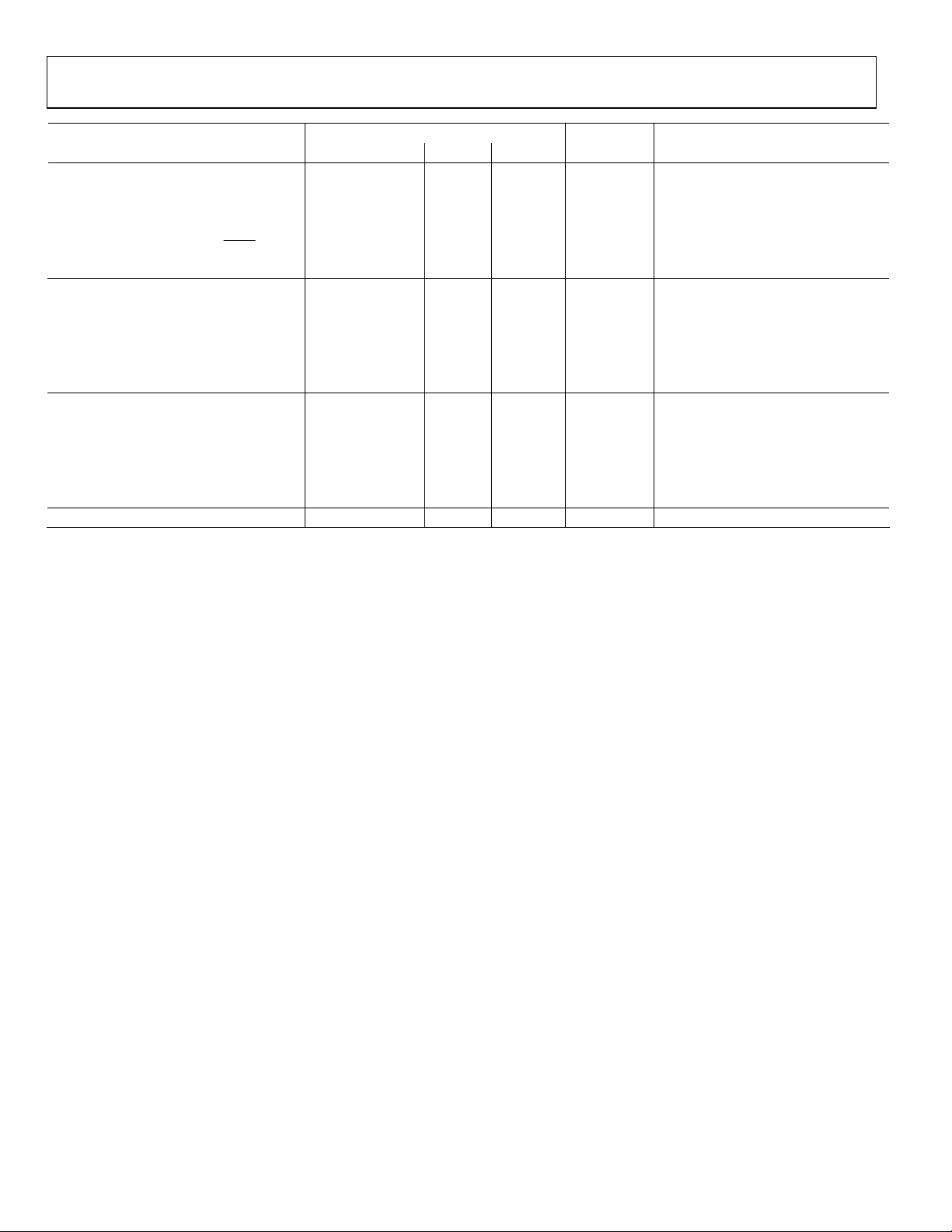

AD5535

2

Unit Conditions/Comments

Parameter

1

DIGITAL INPUTS

A Grade

Min Typ Max

4

Input Current ±5 ±10 μA

Input Low Voltage 0.8 V

Input High Voltage 2.0 V

Input Hysteresis (SCLK and SYNC Only)

200 mV

Input Capacitance 10 pF

POWER SUPPLY VOLTAGES7

VPP (50 × REF_IN) + 10 225 V

V

–

–5.25 –4.75 V

V+ 4.75 5.25 V

AVCC 4.75 5.25 V

DVCC 2.7 5.25 V

POWER SUPPLY CURRENTS

7

IPP 75 100 μA/channel

I

−

2.3 3.5 mA

I+ 0.5 1 mA

AICC 15 18 mA

DICC 0.25 0.5 mA

POWER DISSIPATION

1

See the Terminology section.

2

A Grade temperature range: −10°C to +85°C; typical = +25°C.

3

Linear output voltage range: +7 V to VPP − 10 V.

4

Guaranteed by design and characterization, not production tested.

5

Ensure that TJ max is not exceeded. See the Absolute Maximum Ratings section.

6

Reference input determines output voltage range. Using a 4.096 V reference (REF198) gives an output voltage range of 2.50 V to 200 V. The output range is programmable

via the reference input. The full-scale output range is programmable from 50 V to 200 V. The linear output voltage range is restricted from 7 V to VPP − 10 V.

7

Outputs unloaded.

7

594 mW

Rev. A | Page 4 of 16

AD5535

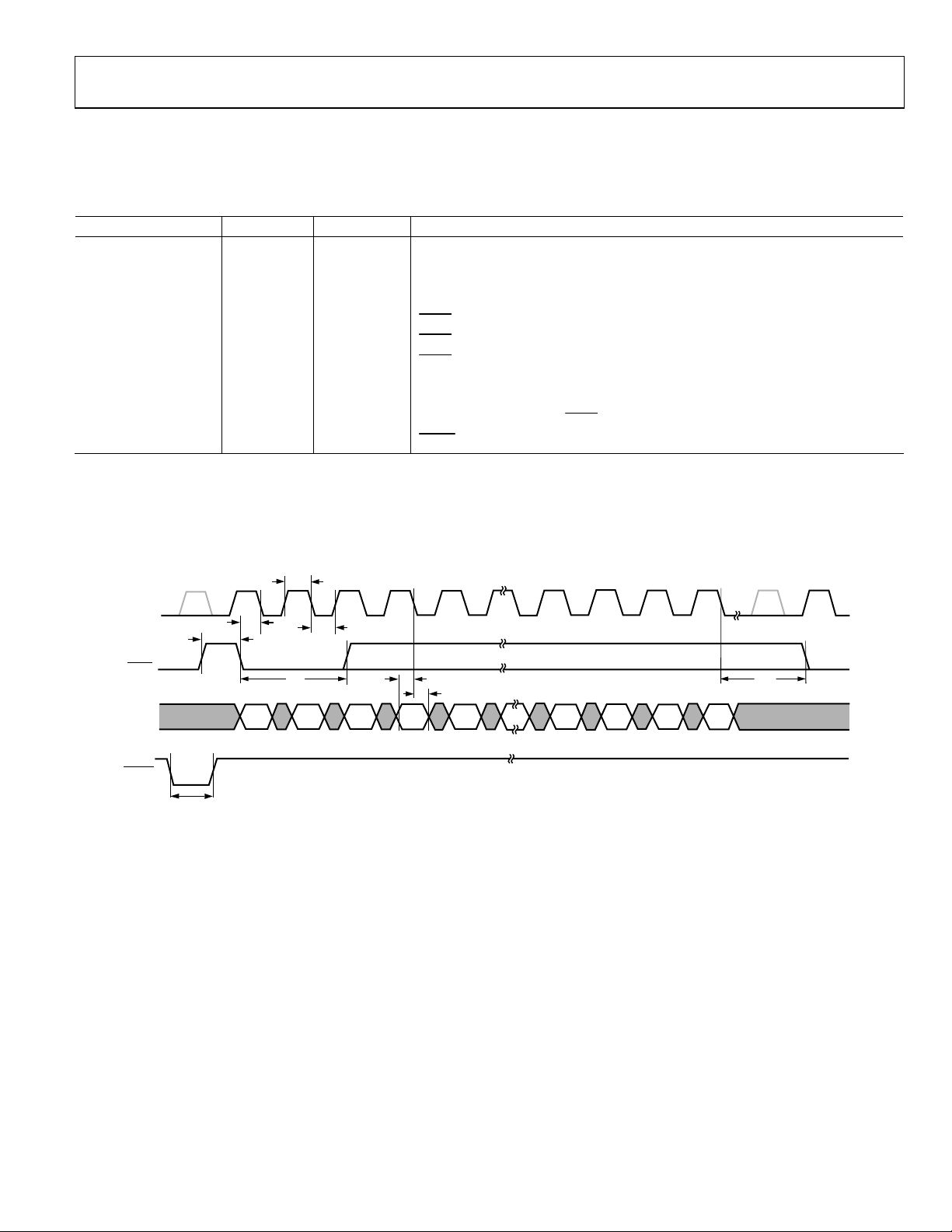

TIMING CHARACTERISTICS

VPP = 210 V, V− = –5 V, V+ = +5 V; AVCC = 5.25 V; DVCC = 2.7 V to 5.25 V; AGND = DGND = DAC_GND = 0 V; REF_IN = 4.096 V.

All specifications T

Table 2.

Parameter A Grade Unit Conditions/Comments

f 1.2 MHz max Channel Update Rate

UPDATE

f 30 MHz max SCLK Frequency

CLKIN

1, , 2 3

t1 13 ns min SCLK High Pulse Width

t 13 ns min SCLK Low Pulse Width

2

t

3

t4 50 ns min

t

5

t6 10 ns min DIN Setup Time

t7 5 ns min DIN Hold Time

t

8

t9 20 ns min

1

See Figure 2.

2

Guaranteed by design and characterization, not production tested.

3

All input signals are specified with tr = tf = 5 ns (10% to 90% of DVCC) and timed from a voltage level of (VIL + V )/2.

MIN

to T

, unless otherwise noted.

MAX

15 ns min

10 ns min

200 ns min

SYNC Falling Edge to SCLK Falling Edge Setup Time

SYNC Low Time

SYNC High Time

th

SCLK Falling Edge to SYNC Falling Edge for Next Write

19

RESET Pulse Width

IH

t

1

SCLK

SYNC

D

RESET

4

t

3

t

23

t

2

4

1

t

t

5

IN

MSB

t

9

Figure 2. Serial Interface Timing Diagram

5

6

t

7

16 17 18 19

LSB

t

8

1

05068-002

Rev. A | Page 5 of 16

Loading...

Loading...