PRELIMINARY TECHNICAL DATA

a

Nonvolatile Memory, Dual 1024

Position Digital Potentiometers

FEATURES

Dual, 1024 Position Resolution

25K, 250K Ohm Terminal Resistance with 50ppm/°C Tempco

Nonvolatile Memory Preset

SPI Compatible Serial Data Input with Readback Function

Increment/Decrement Commands, Push Button Command

+3 to +5V Single Supply Operation

±2.5V Dual Supply Operation

30 bytes of general purpose nonvolatile memory

APPLICATIONS

Mechanical Potentiometer Replacement

Instrumentation: Gain, Offset Adjustment

Programmable Voltage to Current Conversion

Programmable Filters, Delays, Time Constants

Line Impedance Matching

Power Supply Adjustment

DIP Switch Setting

GENERAL DESCRIPTION

The AD5235 provides a dual channel, digitally controlled variable

resistor (VR) with resolutions of 1024 positions. These devices

perform the same electronic adjustment function as a potentiometer or

variable resistor. The AD5235’s versatile programming via a Micro

Controller allows multiple modes of operation and adjustment.

In the direct program mode a predetermined setting of the RDAC

register can be loaded di rect ly from the micro controller. Another key

mode of operation allows the RDAC register to be refreshed with the

setting previously stored in the EEMEM register. When changes are

made to the RDAC register to establish a new wiper position, the

value of the setting can be saved into the EEMEM by executing an

EEMEM save operation. Once the settings are saved in the EEMEM

register, these values will be transferred automatically to the RDAC

register to set the wiper position at system power ON. Such operation

is enabled by the internal preset strobe and the preset can also be

accessed externally.

An internal scratch pad RDAC register can be programmed by the

micro controller to set the resist ance between terminals W-and-B.

Once the target value is achi eved, the RDAC content register can be

placed in the non-volatile memory for automatic recall during Power

Up.

The AD5235 is available in the thin TSSOP-16 package. All parts are

guaranteed to operate over the extended industrial temperature range

of -40°C to +85°C.

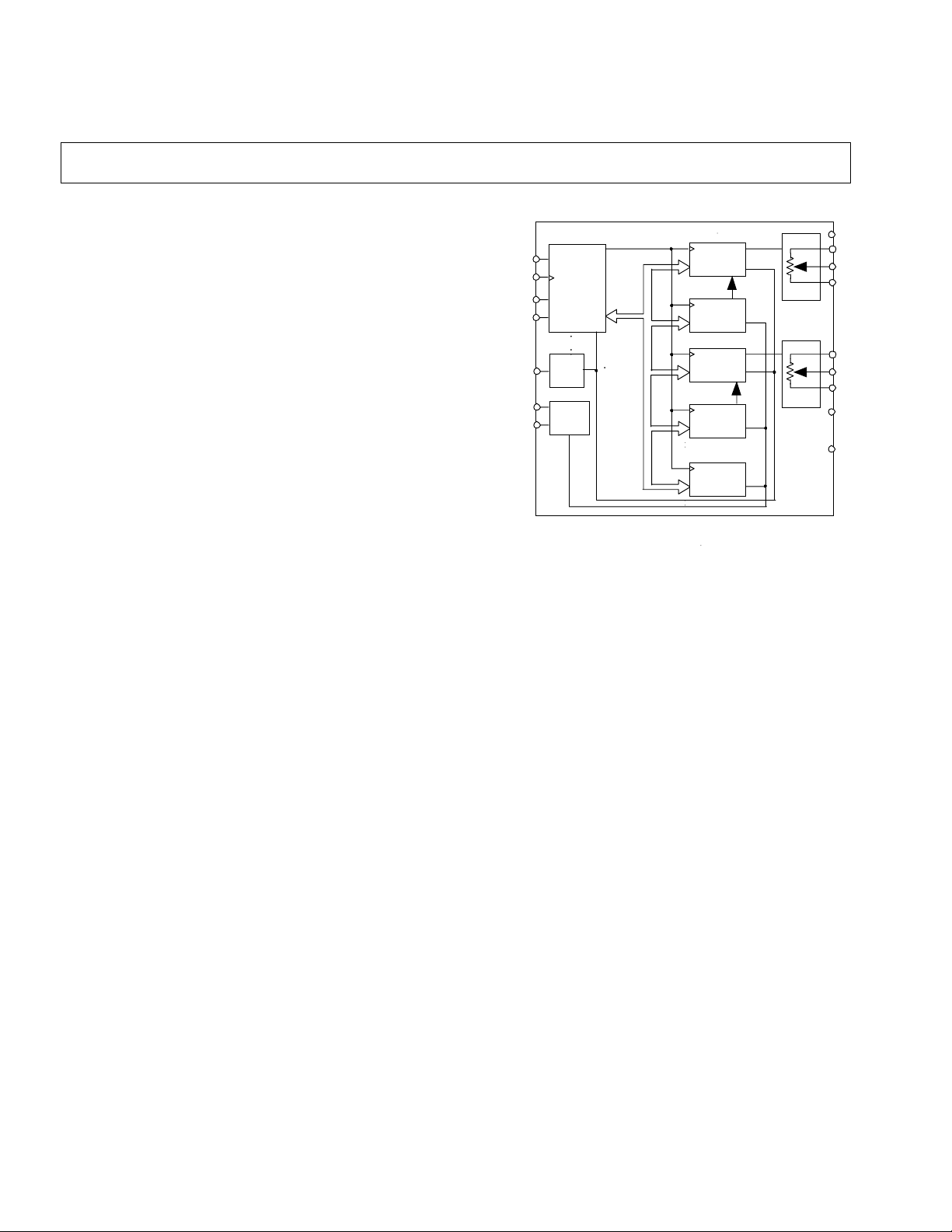

FUNCTIONAL BLOCK DIAGRAMS

CS

CLK

SDI

SDO

WP

RDY

PR

ADDRESS

DECODE

SERIAL

INP UT

REGISTER

PWR ON

PRESET

EEMEM

CONTROL

GND

REGISTER

EEMEM1

REGISTER

EEMEM2

RDAC1

RDAC2

SPARE

EEMEM

AD5235

RDAC1

RDAC2

V

DD

A1

W1

B1

A2

W2

B2

V

SS

GND

REV PrD 6 Nov 2000

Information furnished by A nalog Devices i s believed to be ac curate and reliable. However , no

responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or

other rights of third par ties whic h may res ult from i ts use. No l icense i s granted by i mplic ation

or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106,

Tel: 781/329-4700 Fax:781/326-8703

Norwood, MA 02062-9106 U.S.A.

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory Digital Potentiometers

ELECTRICAL CHARACTERISTICS 25K, 250K OHM VERSIONS

= +V

, VB = 0V, -40°C < TA < +85°C unless otherwise noted.)

DD

AD5235

(VDD = +3V±10% or +5V±10% and VSS=0V, VA

Parameter Symbol Conditions Min Typ1 Max Units

DC CHARACTERISTICS RHEOSTAT MODE Specifications apply to all VRs

Resistor Diff erential NL2 R-DNL RWB, VA=NC -1 ±1/4 +1 LSB

Resistor Nonlinear ity2 R-INL RWB, VA=NC -2 ±1/2 +2 LSB

Nominal resistor tolerance ∆R TA = 25°C, VAB = VDD,Wiper (VW) = No connect -30 30 %

Resistance Temperature Coefficent RAB/∆T V

Wiper Resistance RW I

Wiper Resistance RW I

DC CHARACTERISTICS POTENTIOMETER DIVIDER MODE Specifications apply to all VRs

Resolution N 10 Bits

Integral Nonlinearity3 INL –2 ±1/2 +2 LSB

Differential Nonlinearity3 DNL –1 ±1/4 +1 LSB

Voltage Divider Temperat ure Coefficent ∆VW/∆T Code = Half-scale 15 ppm/°C

Full-Scale Error V

Zero-Scale Error V

Code = Full-scale –3 -1 +0 LSB

WFSE

Code = Zero-s cale 0 +1 +3 LSB

WZSE

RESISTOR TERMINALS

Voltage Range4 V

Capacitance5 Ax, Bx C

VSS V

A,B,W

f = 1 MHz, measured to GND, Code = Hal f-scale 45 pF

A,B

Capacitance5 Wx CW f = 1 MHz, measured to GND, Code = Half-scale 60 pF

Common-mode Leakage Current7 I

V

CM

DIGITAL INPUTS & OUTPUTS

Input Logic High VIH with respect to GND 0.3•VDD V

Input Logic Low VIL with respect to GND 0.7•VDD V

Output Logic High VOH R

Output Logic High VOH IOH = 40µA, V

Output Logic Low VOL I

Input Current IIL V

Input Capacitance5 C

5 pF

IL

POWER SUPPLIES

Single-Supply Power Range VDD V

Dual-Supply Power Range VDD/VSS VSS = 0V ±2.2 ±2.7 V

Positive Supply Current IDD V

Programming Mode Current I

Read Mode Current I

VIH = VDD or VIL = GND 15 mA

DD(PG)

VIH = VDD or VIL = GND 650 µA

DD(READ)

Negative Supply Current ISS V

Power Dissipation6 P

V

DISS

Power Supply Sensitiv ity PSS ∆VDD = +5V ±10% 0.002 0.01 %/%

DYNAMIC CHARACTERISTICS

5, 7

Bandwidth –3dB BW_25K R = 12KΩ 400 KHz

Total Harmonic Distortion THDW V

VW Settling Time tS V

25K/250K 0.6/3/6 µs

Resistor Noise Voltage e

RWB = 10KΩ, f = 1KHz 9 nV√Hz

N_WB

Crosstalk CT V

VR making full scale change -65 dB

= VDD, Wiper (VW) = No Connect 50 ppm/°C

AB

= 1 V/R, VDD = +5V 50 100 Ω

W

= 1 V/R, VDD = +3V 200 Ω

W

V

DD

= VB = VDD/2 0.01 1 µA

A

= 2.2KΩ to +5V 4.9 V

PULL-UP

= +5V 4 V

= 1.6mA, V

OL

= 0V or VDD ±1 µA

IN

= 0V 2.7 5.5 V

SS

= VDD or VIL = GND 2 20 µA

IH

= VDD or VIL = GND, V

IH

= VDD or VIL = GND 0.05 mW

IH

=1Vrms, VB = 0V, f=1KHz 0.003 %

A

= VDD, VB=0V, 50% of final value

A

= VDD, VB = 0V, Measue VW with adjacent

A

LOGIC

= +5V 0.4 V

LOGIC

= 2.5V, V

DD

= -2.5V 10 µA

SS

REV PrD 6 NOV, 2000 2

Information contained i n this Product Concept data s heet describes a product in the early def i ni tion stage. There is no guarantee that the

information contained here will become a final product in its present form. For lat est information contact Walt Heinzer/Analog Devic es, Santa Clara,

CA. TEL(408)562-7254; FAX (408)727-1550; walt.heinzer@analog.com

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory Digital Potentiometers

AD5235

ELECTRICAL CHARACTERISTICS 25K, 250K OHM VERSIONS

= +V

, VB = 0V, -40°C < TA < +85°C unless otherwise noted.)

DD

Parameter Symbol Conditions Min Typ1 Max Units

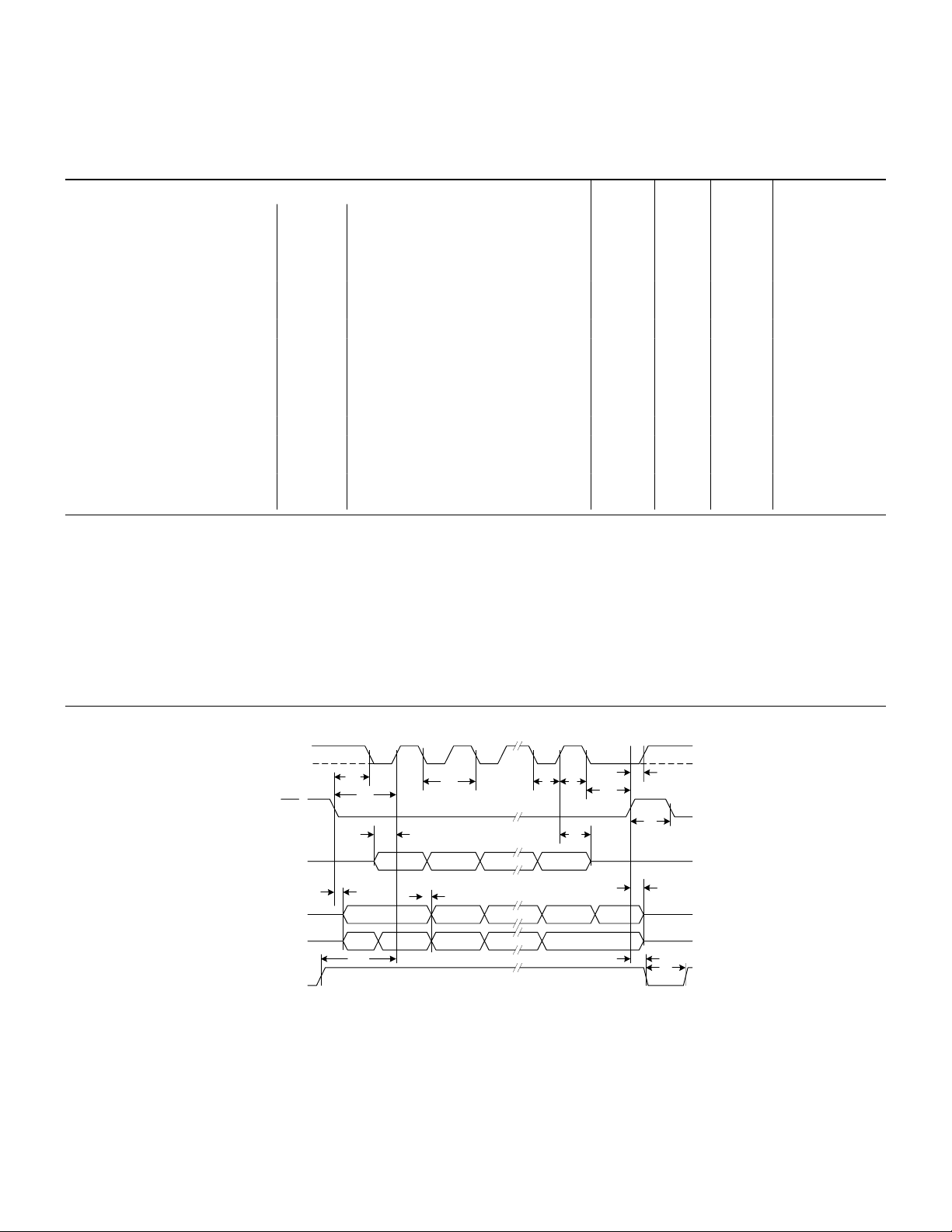

INTERFACE TIMING CHARACTERISTICS applies to all parts(Notes 5, 8)

Clock Cycle Time t 1 20 ns

Input Clock Pulse Width t 2 , t 3 Clock level high or low 10 ns

CS Setup Time t

10 ns

4

Data Setup Time t 5 From Positive CLK transition 5 ns

Data Hold Time t 6 From Positive CLK transition 5 ns

CLK Shutdown Time t 7 0 ns

CS Rise to Clock Rise Setup t

CS High Pulse Width t

CLK to SDO Propagation Delay9 t

Store to Nonvolatile EEMEM Save Time10 t

CS to SDO - SPI line acquire t

CS to SDO - SPI line release t

RDY Rise to CLK Rise t

Startup Time t

CLK Setup Time t

10 ns

8

10 ns

9

R

10

Applies to Command 2H, 3H 25 ms

11

ns

12

ns

13

ns

14

ms

15

For 1 CLK period (t4 - t3 = 1 CLK period) ns

16

L

Preset Pulse Width tPR 50 ns

NOTES:

1. Typicals represent average readings at +25°C and VDD = +5V.

2. Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step

change from ideal between successive tap positions. Parts are guaranteed monotonic. See figure 20 test circuit. I

3. INL and DNL are measured at V

DNL specification limits of ±1LSB maximum are Guaranteed Monotonic operating conditions. See Figure 19 test circuit.

4. Resistor terminals A,B,W have no limitations on polarity with respect to each other.

5. Guaranteed by design and not subject to production test.

6. P

7. All dynamic characteristics use V

8. See timing diagram for location of measured values. All input control voltages are specified with t

9. Propagation delay depends on value of V

10. Low only for commands 8, 9,10, 2, 3: CMD_8 ~ 1ms; CMD_9,10 ~0.1ms; CMD_2,3 ~20ms.

is calculated from (IDD x VDD=+5V).

DISS

measured using both V

with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0V.

W

= +5V.

DD

= +3V or +5V.

DD

, R

DD

PULL_UP

, and CL see applications text.

= 1KΩ, CL < 20pF 1 25 ns

= VDD/R for both VDD=+3V or VDD=+5V.

W

=2.5ns(10% to 90% of 3V) and timed from a voltage level of 1.5V. Switching characteristics are

R=tF

(VDD = +3V±10% to +5V±10% and VSS=0V, VA

Timing Diagram

CLK

t

t

CS

SDI

SDO

SDO

16

t

4

t

5

t

1

MSB

t

12

1

2

t

14

MSB

MSB

t

10

3

LSB

LSB

t2t

t

6

LSB

RDY

SDO1 CLK IDLES LOW SDO2 CLK IDLES HIGH

Figure 1. Timing Diagram

REV PrD 6 NOV, 2000 3

Information contained i n this Product Concept data s heet describes a product in the early def i ni tion stage. There is no guarantee that the

information contained here will become a final product in its present form. For lat est information contact Walt Heinzer/Analog Devic es, Santa Clara,

CA. TEL(408)562-7254; FAX (408)727-1550; walt.heinzer@analog.com

8

t

7

t

9

t

13

t

15

t

11

Loading...

Loading...