Page 1

ISO2-CMOS ST-BUSTM FAMILY MT9094

Digital Telephone (DPhone-II)

Data Sheet

Features

• Programmable µ-Law/A-Law codec and filters

• Programmable CCITT (G.711)/sign-magnitude

coding

• Programmable transmit, receive and side-tone

gains

• DSP-based:

• Speakerphone switching algorithm

• DTMF and single tone generator

• Tone Ringer

• Differential interface to telephony transducers

• Differential audio paths

• Single 5 volt power supply

Applications

• Fully featured digital telephone sets

• Cellular phone sets

• Local area communications stations

February 2005

Ordering Information

MT9094AP 44 Pin PLCC Tubes

MT9094APR 44 Pin PLCC Tape & Reel

MT9094AP1 44 Pin PLCC* Tubes

MT9094APR1 44 Pin PLCC* Tape & Reel

*Pb Free Matte

-40°C to +85°C

Description

The MT9094 DPhone-II is a fully featured integrated

digital telephone circuit. Voice band signals are

converted to digital PCM and vice versa by a switched

capacitor Filter/Codec. The Filter/Codec uses an

ingenious differential architecture to achieve low noise

operation over a wide dynamic range with a single 5 V

supply. A Digital Signal Processor provides handsfree

speaker-phone operation. The DSP is also used to

generate tones (DTMF, Ringer and Call Progress) and

control audio gains. Internal registers are accessed

through a serial microport conforming to INTEL MCS51™ specifications. The device is fabricated in

Zarlink's low power ISO

2

-CMOS technology.

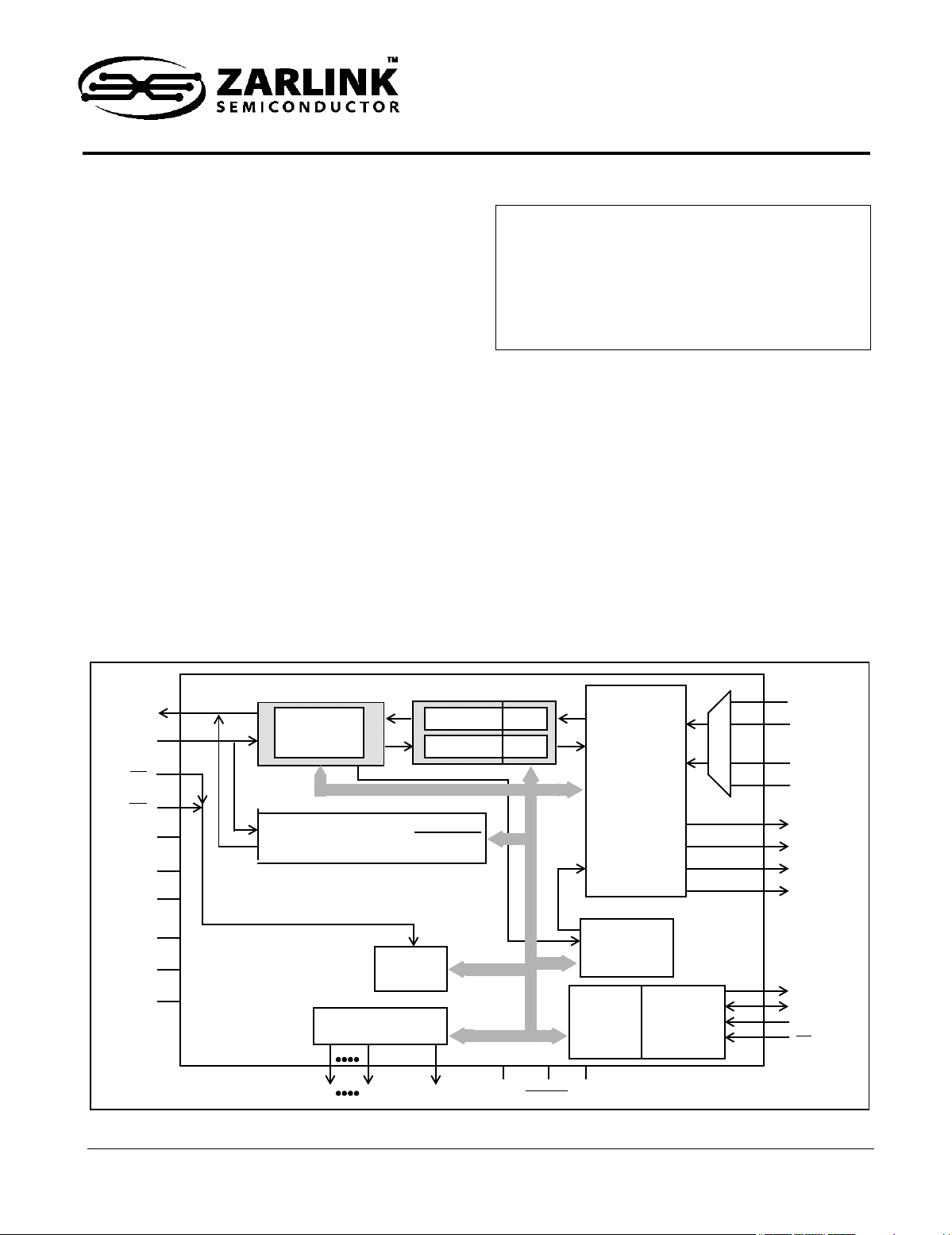

DSTo

DSTi

F0i

C4i

VSSD

VDD

VSSA

VSS

SPKR

VBias

VRef

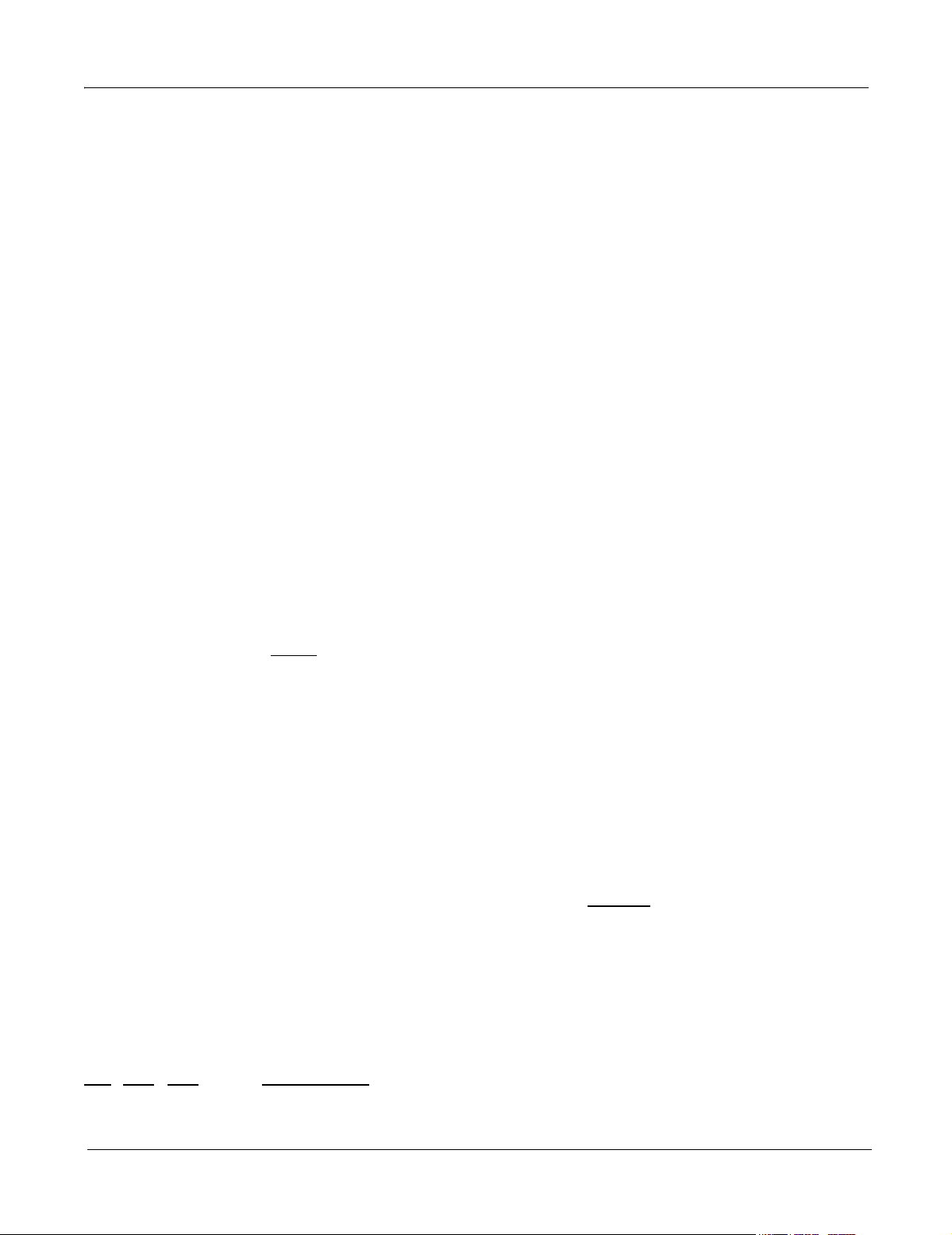

Digital Signal Processor Filter/Codec Gain

22.5/-72dB

∆1.5dB

Tx & Rx

C-Channel

Registers

LCD Driver

S1 S12

ENCODER

DECODER

STATUS

Control

Registers

Timing

Circuits

BP WD PWRST

Figure 1 - Functional Block Diagram

7dB

-7dB

Transducer

Interface

New Call

Tone

Generator

S/P &

P/S

Converter

IC

Serial

Port

(

MCS-51

Compatible)

MIC-

MIC+

M-

M+

HSPKR+

HSPKR-

SPKR+

SPKR-

DATA 2

DATA 1

SCLK

CS

1

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 1995-2005, Zarlink Semiconductor Inc. All Rights Reserved.

Zarlink Semiconductor Inc.

Page 2

MT9094 Data Sheet

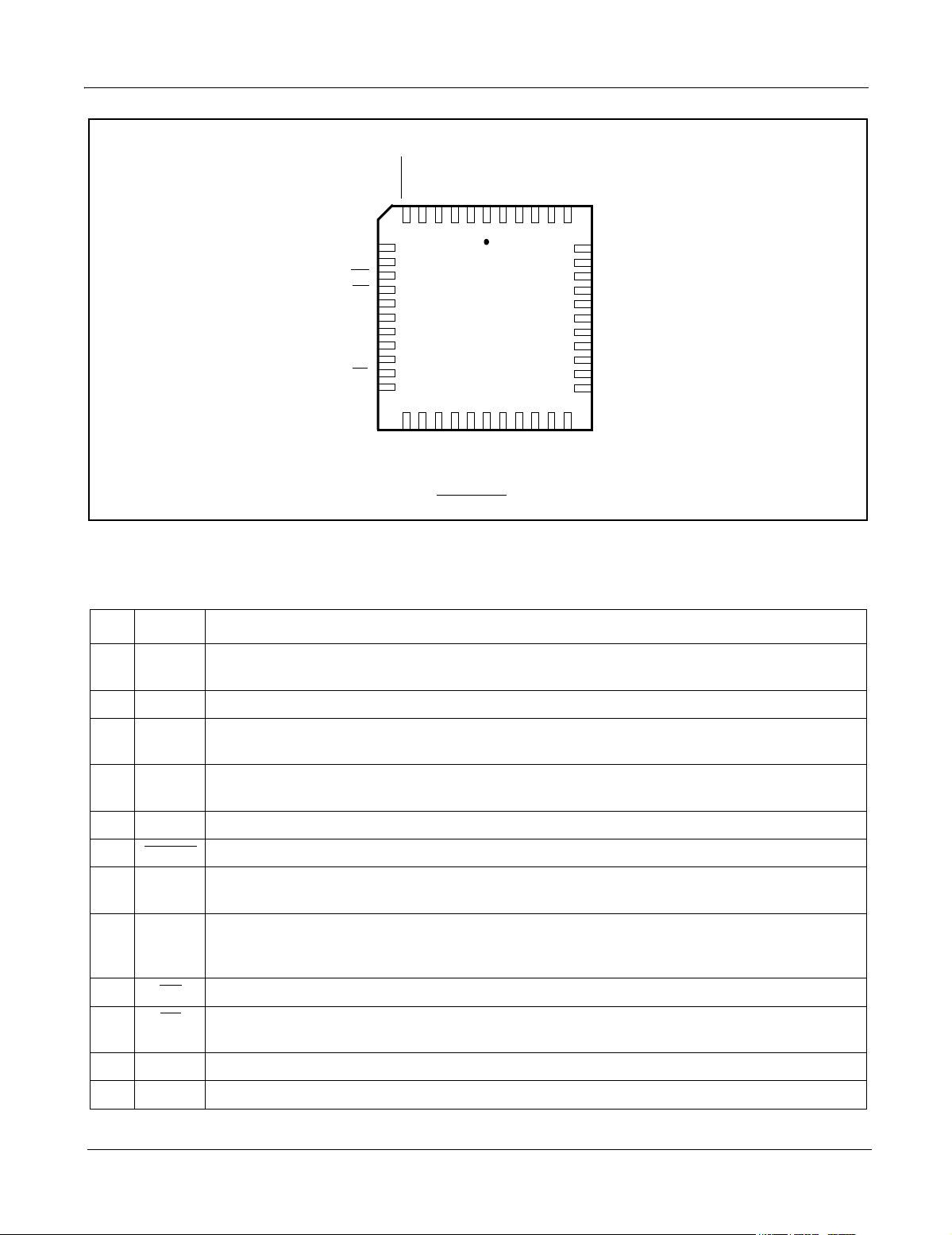

PWRSTICVBias

VRef

DSTi

DSTo

C4i

F0i

VSSD

NC

SCLK

DATA 2

DATA 1

CS

WD

65432

7

8

9

10

11

12

13

14

15

16

17

1819202122

IC

NC

NC

44 PIN PLCC

NCM-VSSA

23

S1

VSSD

MIC+

M+

1

4443424140

2425262728

S3S4S5S6S7

S2

Figure 2 - Pin Connections

Pin Description

Pin # Name Description

MIC-

39

38

37

36

35

34

33

32

31

30

29

VSS SPKR

SPKR+

SPKRHSPKR+

HSPKRVDD

BP

S12

S11

S10

S9

S8

1M+Non-Inverting Microphone (Input). Non-inverting input to microphone amplifier from the handset

microphone.

2NCNo Connect. No internal connection to this pin.

3V

4V

5ICInternal Connection. Tie externally to V

6PWRST

Bias Voltage (Output). (VDD/2) volts is available at this pin for biasing external amplifiers. Connect 0.1

Bias

µF capacitor to V

Reference voltage for codec (Output). Nominally [(VDD/2)-1.5] volts. Used internally. Connect 0.1 µF

Ref

capacitor to V

SSA

SSA

.

.

for normal operation.

SS

Power-up Reset (Input). CMOS compatible input with Schmitt Trigger (active low).

7DSTiST-BUS Serial Stream (Input). 2048 kbit/s input stream composed of 32 eight bit channels; the first

four of which are used by the MT9094. Input level is TTL compatible.

8DSToST-BUS Serial Stream (Output). 2048 kbit/s output stream composed of 32 eight bit channels. The

MT9094 sources digital signals during the appropriate channel, time coincident with the channels used

for DSTi.

9C4i

10 F0i

4096 kHz Clock (Input). CMOS level compatible.

Frame Pulse (Input). CMOS level compatible. This input is the frame synchronization pulse for the

2048 kbit/s ST-BUS stream.

11 V

Digital Ground. Nominally 0 volts.

SSD

12 NC No Connect. No internal connection to this pin.

2

Zarlink Semiconductor Inc.

Page 3

MT9094 Data Sheet

Pin Description (continued)

Pin # Name Description

13 SCLK Serial Port Synchronous Clock (Input). Data clock for MCS-51 compatible microport. TTL level

compatible.

14 DATA 2 Serial Data Transmit. In an alternate mode of operation, this pin is used for data transmit from MT9094.

In the default mode, serial data transmit and receive are performed on the DATA 1 pin and DATA 2 is tristated.

15 DATA 1 Bidirectional Serial Data. Port for microprocessor serial data transfer compatible with MCS-51 standard

(default mode). In an alternate mode of operation, this pin becomes the data receive pin only and data

transmit is performed on the DATA 2 pin. Input level TTL compatible.

16 CS

Chip Select (Input). This input signal is used to select the device for microport data transfers. Active

low. (TTL level compatible.)

17 WD Watchdog (Output). Watchdog timer output. Active high.

18 IC Internal Connection. Tie externally to V

19,

NC No Connection. No internal connection to these pins.

for normal operation.

SS

20

21 V

Digital Ground. Nominally 0 volts.

SSD

22-33 S1-S12 Segment Drivers (Output). 12 independently controlled, two level, LCD segment drivers. An in-phase

signal, with respect to the BP pin, produces a non-energized LCD segment. An out-of-phase signal, with

respect to the BP pin, energizes its respective LCD segment.

34 BP Backplane Drive (Output). A two-level output voltage for biasing an LCD backplane.

35 V

Positive Power Supply (Input). Nominally 5 volts.

DD

36 HSPKR- Inverting Handset Speaker (Output). Output to the handset speaker (balanced).

37 HSPKR+ Non-Inverting Handset Speaker (Output). Output to the handset speaker (balanced).

38 SPKR- Inverting Speaker (Output). Output to the speakerphone speaker (balanced).

39 SPKR+ Non-Inverting Speaker (Output). Output to the speakerphone speaker (balanced).

40 V

Power Supply Rail for Analog Output Drivers. Nominally 0 Volts.

SS

SPKR

41 MIC- Inverting Handsfree Microphone (Input). Handsfree microphone amplifier inverting input pin.

42 MIC+ Non-inverting Handsfree Microphone (Input). Handsfree microphone amplifier non-inverting input

pin.

43 V

Analog Ground. Nominally 0 V.

SSA

44 M- Inverting Microphone (Input). Inverting input to microphone amplifier from the handset microphone.

NOTES:

Intel and MCS-51 are registered trademarks of Intel Corporation, Santa Clara, CA, USA.

Overview

The Functional Block Diagram of Figure 1 depicts the main operations performed within the DPhone-II. Each of

these functional blocks will be described in the sections to follow. This overview will describe some of the end-user

features which may be implemented as a direct result of the level of integration found within the DPhone-II.

3

Zarlink Semiconductor Inc.

Page 4

MT9094 Data Sheet

The main feature required of a digital telephone is to convert the digital Pulse Code Modulated (PCM) information,

being received by the telephone set, into an analog electrical signal. This signal is then applied to an appropriate

audio transducer such that the information is finally converted into intelligible acoustic energy. The same is true of

the reverse direction where acoustic energy is converted first into an electrical analog and then digitized (into PCM)

before being transmitted from the set. Along the way if the signals can be manipulated, either in the analog or the

digital domains, other features such as gain control, signal generation and filtering may be added. More complex

processing of the digital signal is also possible and is limited only be the processing power available. One example

of this processing power may be the inclusion of a complex handsfree switching algorithm. Finally, most electroacoustic transducers (loudspeakers) require a large amount of power to develop an effective acoustic signal. The

inclusion of audio amplifiers to provide this power is required.

The DPhone-II features Digital Signal Processing (DSP) of the voice encoded PCM, complete Analog/Digital and

Digital/Analog conversion of audio signals (Filter/CODEC) and an analog interface to the external world of electroacoustic devices (Transducer Interface). These three functional blocks combine to provide a standard full-duplex

telephone conversation utilizing a common handset. Selecting transducers for handsfree operation, as well as

allowing the DSP to perform its handsfree switching algorithm, is all that is required to convert the full-duplex

handset conversation into a half-duplex speakerphone conversation. In each of these modes, full programmability

of the receive path and side-tone gains is available to set comfortable listening levels for the user as well as

transmit path gain control for setting nominal transmit levels into the network.

The ability to generate tones locally provides the designer with a familiar method of feedback to the telephone user

as they proceed to set-up, and ultimately, dismantle a telephone conversation. Also, as the network slowly evolves

from the dial pulse/DTMF methods to the D-Channel protocols it is essential that the older methods be available for

backward compatibility. As an example; once a call has been established, say from your office to your home, using

the D-Channel signalling protocol it may be necessary to use in-band DTMF signalling to manipulate your personal

answering machine in order to retrieve messages. Thus the locally generated tones must be of network quality and

not just a reasonable facsimile. The DPhone-II DSP can generate the required tone pairs as well as single tones to

accommodate any in-band signalling requirement.

Each of the programmable parameters within the functional blocks is accessed through a serial microcontroller port

compatible with Intel MCS-51 specifications.

Functional Description

In this section, each functional block within the DPhone-II is described along with all of the associated

control/status bits. Each time a control/ status bit(s) is described it is followed by the address register where it will be

found. The reader is referred to the section titled ‘Register Summary' for a complete listing of all address map

registers, the control/status bits associated with each register and a definition of the function of each control/status

bit. The Register Summary is useful for future reference of control/status bits without the need to locate them within

the text of the functional descriptions.

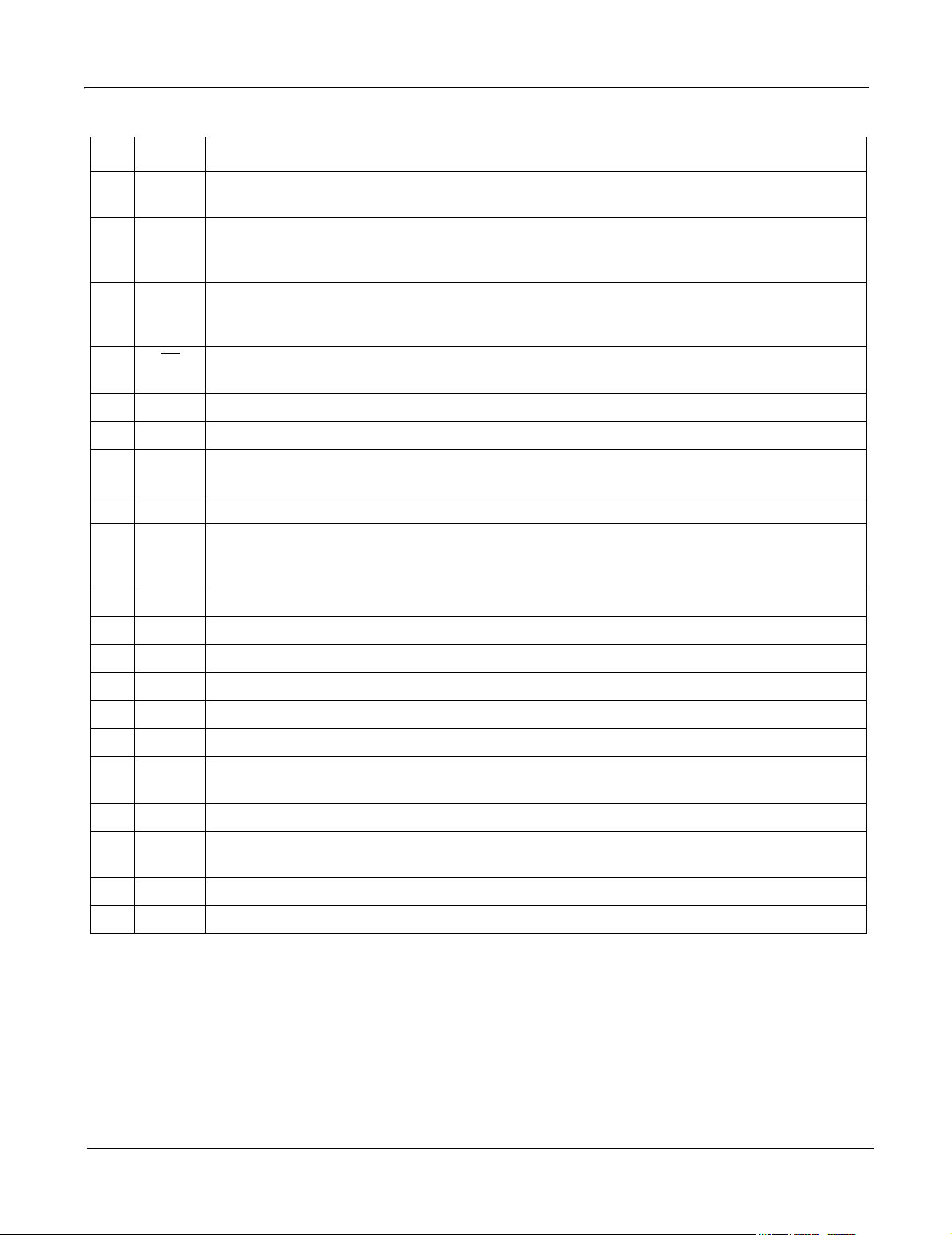

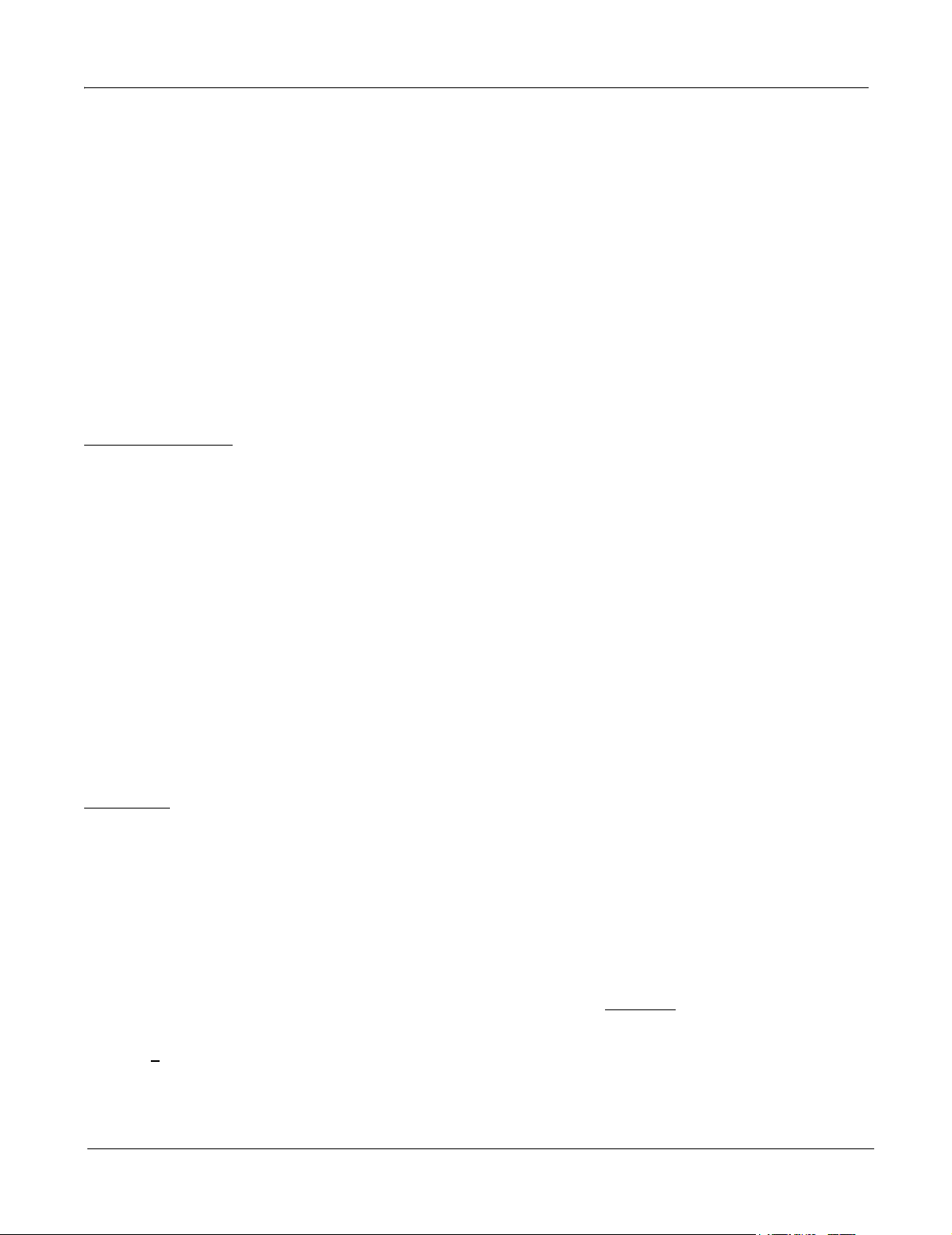

Filter-CODEC

The Filter/CODEC block implements conversion of the analog 3.3kHz speech signals to/from the digital domain

compatible with 64 kb/s PCM B-Channels. Selection of companding curves and digital code assignment are

register programmable. These are CCITT G.711 A-law or µ-Law, with true-sign/ Alternate Digit Inversion or truesign/Inverted Magnitude coding, respectively. Optionally, sign- magnitude coding may also be selected for

proprietary applications.

The Filter/CODEC block also implements transmit and receive audio path gains in the analog domain. These gains

are in addition to the digital gain pad provided in the DSP section and provide an overall path gain resolution of

0.5 dB. A programmable gain, voice side-tone path is also included to provide proportional transmit speech

feedback to the handset receiver so that a dead sounding handset is not encountered. Figure 3 depicts the nominal

half-channel and side-tone gains for the DPhone-II.

4

Zarlink Semiconductor Inc.

Page 5

MT9094 Data Sheet

SERIAL

PORT

PCM

PCM

DSP GAIN*

Receive

–72 to

+22.5 dB

(1.5dB

steps)

DTMF,

Tone

Ringer &

Handsfree

–72 to

+22.5 dB

(1.5dB

steps)

Transmit

FILTER/CODEC

Receive

Filter Gain

0 to –7 dB

(1 dB steps)

Side-tone

–9.96 to

+9.96dB

(3.32 dB steps)

Side-tone

Nominal

Gain

µ-Law –11 dB

Α-Law –18.8 dB

Transmit

Filter Gain

0 to +7dB

(1 dB steps)

TRANSDUCER INTERFACE

-6 dB

Speaker Gain

0 to –24 dB

(8 dB steps)

Transmit

µ-Law 6.1dB

Α-Law 15.4dB

Gain

µ-Law –6.3 dB

Α-Law –3.7 dB

Receiver

Driver

Speaker

Phone

Driver

0.2dB*

Tone

Ringer

(input

from DSP)

M

U

X

-6 dB

HSPKR+

HSPKR–

SPKR+

SPKR–

MIC+

MIC–

M+

M–

Handset

Receiver

(150Ω)

75

75

Speakerphone

Speaker

(40Ω nominal)

(32Ω min)

Handsfree

mic

Transmitter

microphone

DIGITAL DOMAIN

Internal to Device External to Device

Note: *gain the same for A-Law and m

−

Law

ANALOG DOMAIN

Figure 3 - Audio Gain Partitioning

On PWRST

(pin 6) the Filter/CODEC defaults such that the side-tone path, dial tone filter and 400 Hz transmit filter

are off, all programmable gains are set to 0 dB and µ-Law companding is selected. Further, the Filter/CODEC is

powered down due to the PuFC bit (Transducer Control Register, address 0Eh) being reset. This bit must be set

high to enable the Filter/CODEC.

The internal architecture is fully differential to provide the best possible noise rejection as well as to allow a wide

dynamic range from a single 5 volt supply design. This fully differential architecture is continued into the Transducer

Interface section to provide full chip realization of these capabilities.

A reference voltage (V

biasing the internal analog sections, are both generated on-chip. V

), for the conversion requirements of the CODER section, and a bias voltage (V

Ref

is also brought to an external pin so that it

Bias

may be used for biasing any external gain plan setting amplifiers. A 0.1 µF capacitor must be connected from V

to analog ground at all times. Likewise, although V

may only be used internally, a 0.1 µF capacitor from the V

Ref

Bias

), for

Bias

Ref

5

Zarlink Semiconductor Inc.

Page 6

MT9094 Data Sheet

pin to ground is required at all times. It is suggested that the analog ground reference point for these two capacitors

be physically the same point. To facilitate this the V

Ref

and V

The transmit filter is designed to meet CCITT G.714 specifications. The nominal gain for this filter path is 0 dB (gain

control = 0 dB). An anti-aliasing filter is included. This is a second order lowpass implementation with a corner

frequency at 25 kHz. Attenuation is better than 32 dB at 256 kHz and less than 0.01 dB within the passband.

An optional 400 Hz high-pass function may be included into the transmit path by enabling the Tfhp bit in the

Transducer Control Register (address 0Eh). This option allows the reduction of transmitted background noise such

as motor and fan noise.

The receive filter is designed to meet CCITT G.714 specifications. The nominal gain for this filter path is 0 dB (gain

control = 0 dB). Filter response is peaked to compensate for the sinx/x attenuation caused by the 8 kHz sampling

rate.

The Rx filter function can be altered by enabling the DIAL EN control bit in the Transducer Control Register

(address 0Eh). This causes another lowpass function to be added, with a 3 dB point at 1000 Hz. This function is

intended to improve the sound quality of digitally generated dial tone received as PCM.

Transmit sidetone is derived from the Tx filter and is subject to the gain control of the Tx filter section. Sidetone is

summed into the receive path after the Rx filter gain control section so that Rx gain adjustment will not affect

sidetone levels. The side-tone path may be enabled/disabled with the SIDE EN bit located in the Transducer

Control Register (address 0Eh). See also STG

-STG2 (address 0Bh).

0

pins are situated on adjacent pins.

Bias

Transmit and receive filter gains are controlled by the TxFG

-TxFG2 and RxFG0-RxFG2 control bits respectively.

0

These are located in the FCODEC Gain Control Register 1 (address 0Ah). Transmit filter gain is adjustable from

0 dB to +7 dB and receive filter gain from 0 dB to -7 dB, both in 1 dB increments.

Side-tone filter gain is controlled by the STG

-STG2 control bits located in the FCODEC Gain Control Register 2

0

(address 0Bh). Side-tone gain is adjustable from -9.96 dB to +9.96 dB in 3.32 dB increments.

Law selection for the Filter/CODEC is provided by the A/µ companding control bit while the coding scheme is

controlled by the sign-mag/CCITT

bit. Both of these reside in the General Control Register (address 0Fh).

Digital Signal Processor

The DSP block is located, functionally, between the serial ST-BUS port and the Filter/CODEC block. Its main

purpose is to provide both a digital gain control and a half-duplex handsfree switching function. The DSP will also

generate the digital patterns required to produce standard DTMF signalling tones as well as single tones and a tone

ringer output. A programmable (ON/OFF) offset null routine may also be performed on the transmit PCM data

stream. The DSP can generate a ringer tone to be applied to the speakerphone speaker during normal handset

operation so that the existing call is not interrupted.

The main functional control of the DSP is through two hardware registers which are accessible at any time via the

microport. These are the Receive Gain Control Register at address 1Dh and the DSP Control Register at address

1Eh. In addition, other functional control is accomplished via multiple RAM-based registers which are accessible

only while the DSP is held in a reset state. This is accomplished with the DRESET

bit of the DSP Control Register.

Ram-based registers are used to store transmit gain levels (20h for transmit PCM and 21h for transmit DTMF

levels), the coefficients for tone and ringer generation (addresses 23h and 24h), and tone ringer warble rates

(address 26h). All undefined addresses below 20h are reserved for the temporary storage of interim variables

calculated during the execution of the DSP algorithms. These undefined addresses should not be written to via the

microprocessor port. The DSP can be programmed to execute the following micro-programs which are stored in

instruction ROM, (see PS0 to PS2, DSP Control Register, address 1Eh). All program execution begins at the frame

pulse boundary.

PS1 PS0 Micro-program

PS2

0 0 0 Power up reset program

6

Zarlink Semiconductor Inc.

Page 7

MT9094 Data Sheet

0 0 1 Transmit and receive gain control program; with autonulling of the transmit PCM, if the AUTO bit is

set (see address 1Dh)

0 1 0 DTMF generation plus transmit and receive gain control program (autonull available via the AUTO

control bit)

0 1 1 Tone ringer plus transmit and receive gain control program (autonull available via the AUTO control

bit)

1 0 0 handsfree switching program

101

1 1 0 Last three selections reserved

111

Note: For the DSP to function it must be selected to operate, in conjunction with the Filter/Codec, in one of the B-Channels.

Therefore, one of the B-Channel enable bits must be set (see Timing Control, address 15h: bits CH

Power Up Reset Program

A hardware power-up reset (pin 6, PWRST) will initialize the DSP hardware registers to the default values (all

zeros) and will reset the DSP program counter. The DSP will then be disabled and the PCM streams will pass

transparently through the DSP. The RAM-based registers are not reset by the PWRST

their default settings by programming the DSP to execute the power up reset program. None of the micro-programs

actually require the execution of the power up reset program but it is useful for pre-setting the variables to a known

condition. Note that the reset program requires one full frame (125µSec) for execution.

EN and CH3EN).

2

pin but may be initialized to

Gain Control Program

Gain control is performed on converted linear code for both the receive and the transmit PCM. Receive gain control

is set via the hardware register at address 1Dh (see bits B0 - B5) and may be changed at any time. Gain in 1.5 dB

increments is available within a range of +22.5 dB to -72 dB. Normal operation usually requires no more than a +20

to -20 dB range of control. However, the handsfree switching algorithm requires a large attenuation depth to

maintain stability in worst case environments, hence the large (-72 dB) negative limit. Transmit gain control is

divided into two RAM registers, one for setting the network level of transmit speech (address 20h) and the other for

setting the transmit level of DTMF tones into the network (address 21h). Both registers provide gain control in

1.5 dB increments and are encoded in the same manner as the receive gain control register (see address 1Dh, bits

B0 - B5). The power up reset program sets the default values such that the receive gain is set to -72.0 dB, the

transmit audio gain is set to 0.0dB and the transmit DTMF gain is set to -3.0 dB (equivalent to a DTMF output level

of -4 dBm0 into the network).

Optional Offset Nulling

Transmit PCM may contain residual offset in the form of a DC component. An offset of up to ±fifteen linear bits is

acceptable with no degradation of the parameters defined in CCITT G.714. The DPhone-II filter/CODEC

guarantees no more than ±ten linear bits of offset in the transmit PCM when the autonull routine is not enabled. By

enabling autonulling (see AUTO in the Receive Gain Control Register, address 1Dh) offsets are reduced to within

±one bit of zero. Autonulling circuitry was essential in the first generations of Filter/Codecs to remove the large DC

offsets found in the linear technology. Newer technology has made nulling circuitry optional as offered in the

DPhone-II.

7

Zarlink Semiconductor Inc.

Page 8

MT9094 Data Sheet

DTMF and Gain Control Program

The DTMF program generates a dual cosine wave pattern which may be routed into the receive path as comfort

tones or into the transmit path as network signalling. In both cases, the digitally generated signal will undergo gain

adjustment as programmed into the Receive Gain Control and the Transmit DTMF Gain Control registers. The

composite signal output level in both directions is -4 dBm0 when the gain controls are set to 2Eh (-3.0 dB).

Adjustments to these levels may be made by altering the settings of the gain control registers. Pre-twist of 2.0 dB is

incorporated into the composite signal. The frequency of the low group tone is programmed by writing an 8-bit

coefficient into Tone Coefficient Register 1 (address 23h), while the high group tone frequency uses the 8-bit

coefficient programmed into Tone Coefficient Register 2 (address 24h). Both coefficients are determined by the

following equation:

COEFF = 0.128 x Frequency (in Hz)

where COEFF is a rounded off 8 bit binary integer

A single frequency tone may be generated instead of a dual tone by programming the coefficient at address 23h to

a value of zero. In this case the frequency of the single output tone is governed by the coefficient stored at address

24h.

Frequency

(Hz)

697 59h 695.3 -.20%

770 63h 773.4 +.40%

852 6Dh 851.6 -.05%

941 79h 945.3 +.46%

1209 9Bh 1210.9 +.20%

1336 ABh 1335.9 .00%

1477 BDh 1476.6 -.03%

1633 D1h 1632.8 -.01%

COEF

Actual

Frequency%Deviation

Table 1

DTMF Signal to distortion:

The sum of harmonic and noise power in the frequency band from 50 Hz to 3500 Hz is typically more than 30dB below the power in the tone pair.

All individual harmonics are typically more than 40 dB below the level of the low group tone.

Table 1 gives the standard DTMF frequencies, the coefficient required to generate the closest frequency, the actual

frequency generated and the percent deviation of the generated tone from the nominal.

Tone Ringer and Gain Control Program

A locally generated alerting (ringing) signal is used to prompt the user when an incoming call must be answered.

The DSP uses the values programmed into Tone Coefficient Registers 1 and 2 (addresses 23h and 24h) to

generate two different squarewave frequencies in PCM code. The amplitude of the squarewave frequencies is set

to a mid level before being sent to the receive gain control block. From there the PCM passes through the decoder

and receive filter, replacing the normal receive PCM data, on its way to the loudspeaker driver. Both coefficients are

determined by the following equation:

COEFF = 8000/Frequency (Hz)

where COEFF is a rounded off 8 bit binary integer

Zarlink Semiconductor Inc.

8

Page 9

MT9094 Data Sheet

The ringer program switches between these two frequencies at a rate defined by the 8-bit coefficient programmed

into the Tone Ringer Warble Rate Register (address 26h). The warble rate is defined by the equation:

Tone duration (warble frequency

in Hz) = 500/COEFF

where 0 < COEFF < 256, a warble rate of 5-20 Hz is suggested.

An alternate method of generating ringer tones to the speakerphone speaker is available. With this method the

normal receive speech path through the decoder and receive filter is uninterrupted to the handset, allowing an

existing conversation to continue. The normal DSP and Filter/CODEC receive gain control is also retained by the

speech path. When the OPT bit (DSP Control Register address 1Eh) is set high the DSP will generate the new call

tone according to the coefficients programmed into registers 23h, 24h and 26h as before. In this mode the DSP

output is no longer a PCM code but a toggling signal which is routed directly through the New Call Tone gain control

section to the loudspeaker driver. Refer to the section titled ‘New Call Tone’.

Handsfree Program

A half-duplex speakerphone program, fully contained on chip, provides high quality gain switching of the transmit

and receive speech PCM to maintain loop stability under most network and local acoustic environments. Gain

switching is performed in continuous 1.5 dB increments and operates in a complimentary fashion. That is, with the

transmit path at maximum gain the receive path is fully attenuated and vice versa. This implies that there is a mid

position where both transmit and receive paths are attenuated equally during transition. This is known as the idle

state.

Of the 64 possible attenuator states, the algorithm may rest in only one of three stable states; full receive, full

transmit and idle. The maximum gain values for full transmit and full receive are programmable through the

microport at addresses 20h and 1Dh respectively, as is done for normal handset operation. This allows the user to

set the maximum volumes to which the algorithm will adhere. The algorithm determines which path should maintain

control of the loop based upon the relative levels of the transmit and receive audio signals after the detection and

removal of background noise energy. If the algorithm determines that neither the transmit or the receive path has

valid speech energy then the idle state will be sought. The present state of the algorithm plus the result of the Tx vs.

Rx decision will determine which transition the algorithm will take toward its next stable state. The time durations

required to move from one stable state to the next are parameters defined in CCITT Recommendation P.34 and are

used by default by this algorithm (i.e., build-up time, hang-over time and switching time).

Quiet Code

The DSP can be made to send quiet code to the decoder and receive filter path by setting the RxMUTE bit high.

Likewise, the DSP will send quiet code in the transmit (DSTo) path when the TxMUTE bit is high. Both of these

control bits reside in the DSP Control Register at address 1Eh. When either of these bits are low, their respective

paths function normally.

Transducer Interfaces

Four standard telephony transducer interfaces are provided by the DPhone-II. These are:

• The handset microphone inputs (transmitter), pins M+/M- and the speakerphone microphone inputs, pins

MIC+/MIC-. The transmit path is muted/not-muted by the MIC EN control bit. Selection of which input pair is

to be routed to the transmit filter amplifier is accomplished by the MIC/HNSTMIC

reside in the Transducer Control Register (address 0Eh). The nominal transmit path gain may be adjusted to

either 6.1 dB (suggested for µ-Law) or 15.4 dB (suggested for A-Law). Control of this gain is provided by the

MICA/u

programmable gain provided by the transmit filter and DSP.

control bit (General Control Register, address 0Fh). This gain adjustment is in addition to the

control bit. Both of these

9

Zarlink Semiconductor Inc.

Page 10

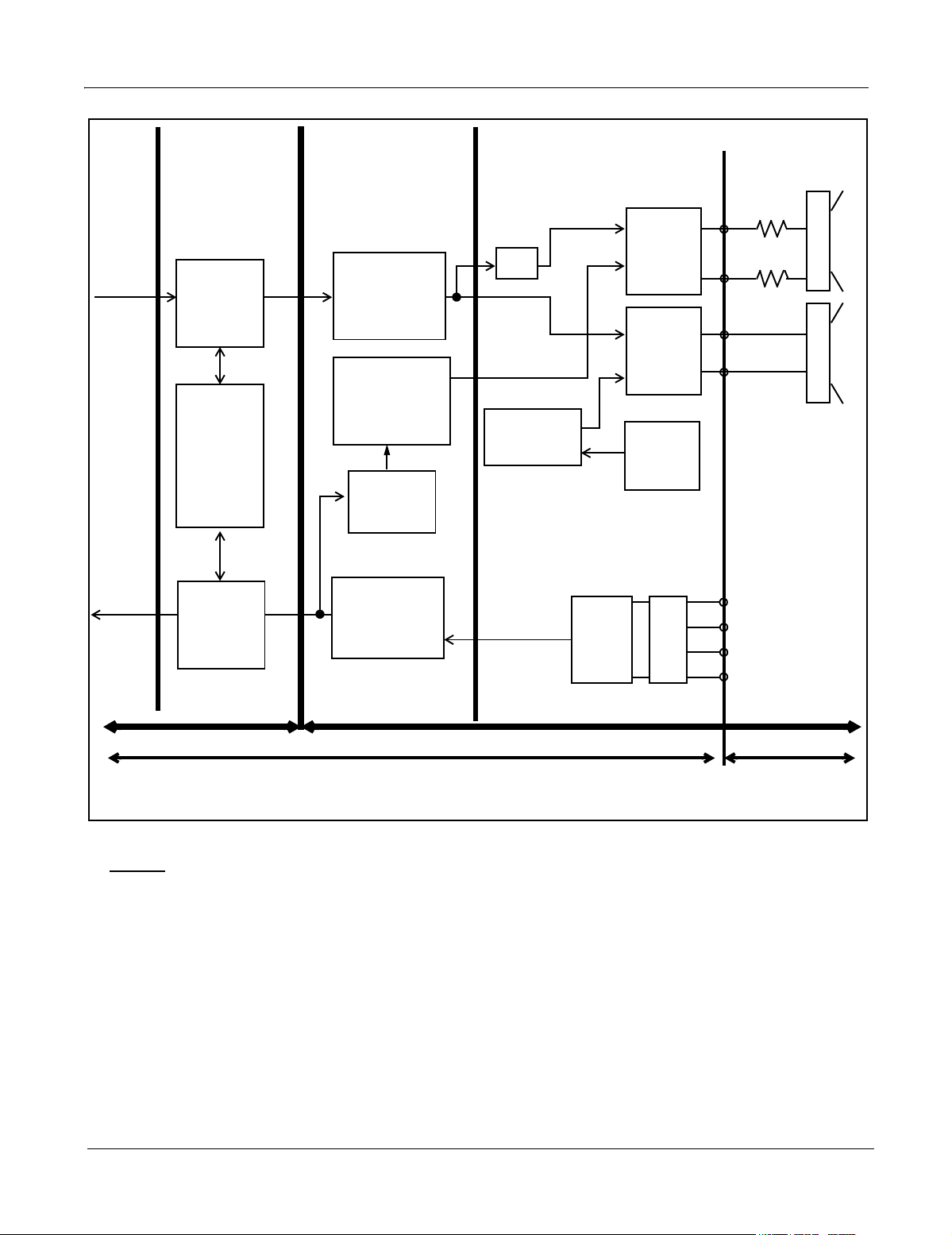

MT9094 Data Sheet

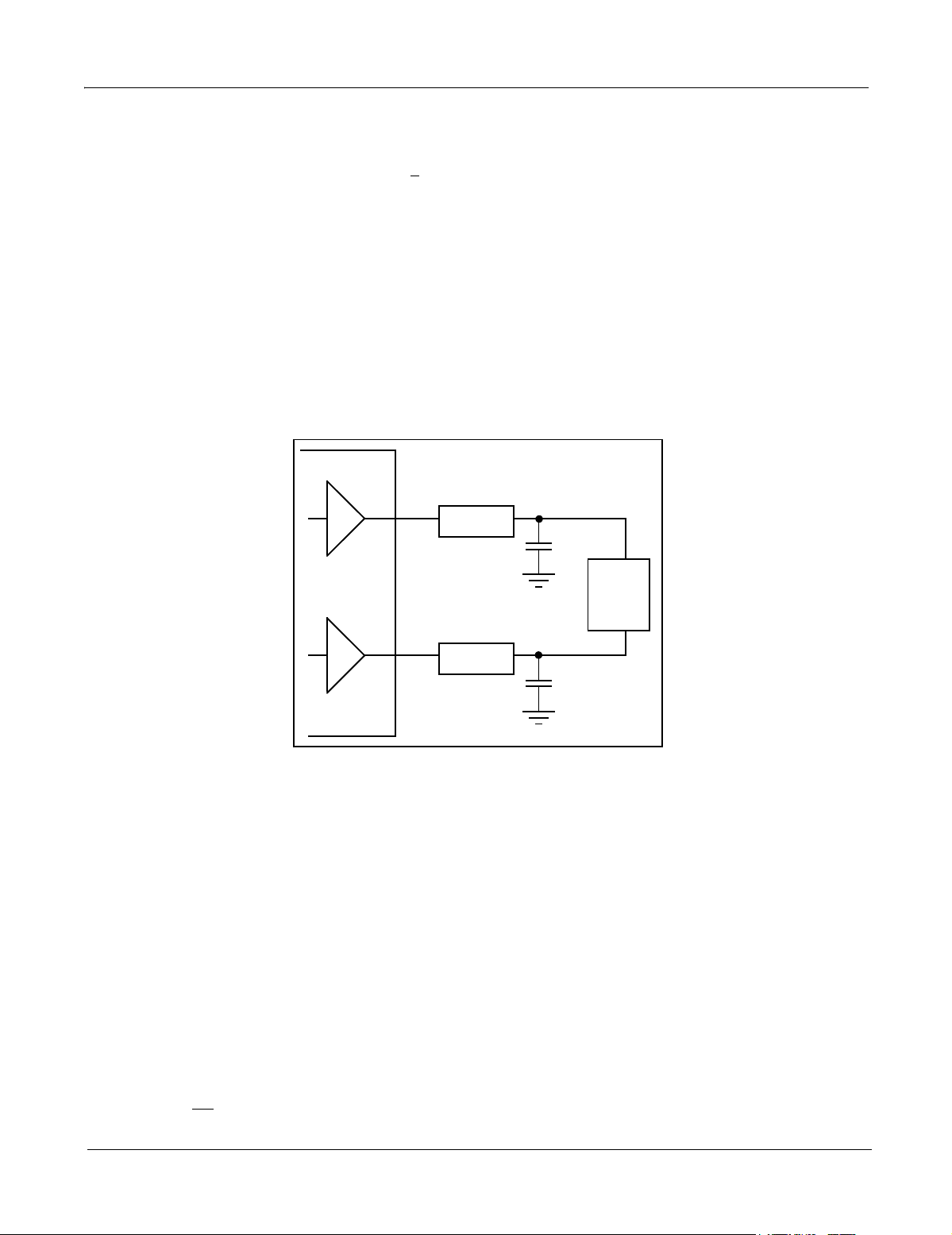

• The handset speaker outputs (receiver), pins HSPKR+/HSPKR-. This internally compensated, fully

differential output driver is capable of driving the load shown in Figure 4. This output is enabled/disabled by

the HSSPKR EN bit residing in the Transducer Control Register (address 0Eh). The nominal handset receive

path gain may be adjusted to either -12.3 dB (suggested for µ-Law) or - 9.7 dB (suggested for A-Law).

Control of this gain is provided by the RxA/u

adjustment is in addition to the programmable gain provided by the receive filter and DSP.

• The loudspeaker outputs, pins SPKR+/SPKR-. This internally compensated, fully differential output driver is

capable of directly driving 6.5vpp into a 40 ohm load. This output is enabled/disabled by the SPKR EN bit

residing in the Transducer Control Register (address 0Eh). The nominal gain for this amplifier is 0.2 dB.

C-Channel

Access to the internal control and status registers of Zarlink basic rate, layer 1, transceivers is through the ST-BUS

Control Channel (C-Channel), since direct microport access is not usually provided, except in the case of the SNIC

(MT8930). The DPhone-II provides asynchronous microport access to the ST-BUS C-Channel information on both

DSTo and DSTi via a double-buffered read/write register (address 14h). Data written to this address is transmitted

on the C-Channel every frame when enabled by CH

HSPKR+

control bit (General Control Register, address 0Fh). This gain

EN (see ST-BUS/Timing Control).

1

75 Ω

1000 pF

1000 pF

ground

150 ohm

load

(speaker)

MT9094

75 Ω

HSPKR-

Figure 4 - Handset Speaker Driver

LCD

A twelve segment, non-multiplexed, LCD display controller is provided for easy implementation of various set status

and call progress indicators. The twelve output pins (S

) are used in conjunction with 12 segment control bits,

n

located in LCD Segment Enable Registers 1&2 (addresses 12h and 13h), and the BackPlane output pin (BP) to

control the on/off state of each segment individually.

The BP pin drives a continuous 62.5 Hz, 50% duty cycle squarewave output signal. An individual segment is

controlled via the phase relationship of its segment driver output pin with respect to the backplane, or common,

driver output. Each of the twelve Segment Enable bits corresponds to a segment output pin. The waveform at each

segment pin is in-phase with the BP waveform when its control bit is set to logic zero (segment off) and is out-ofphase with the BP waveform when its control bit is set to a logic high (segment on). Refer to the LCD Driver

Characteristics for pin loading information.

Microport

A serial microport, compatible with Intel MCS-51 (mode 0) specifications, provides access to all DPhone-II internal

read and write registers. This microport consists of three pins; a half-duplex transmit/receive data pin (DATA1), a

chip select pin (CS

) and a synchronous data clock pin (SCLK).

10

Zarlink Semiconductor Inc.

Page 11

MT9094 Data Sheet

On power-up reset (PWRST) or with a software reset (RST), the DATA1 pin becomes a bidirectional

(transmit/receive) serial port while the DATA2 pin is internally disconnected and tri-stated.

All data transfers through the microport are two-byte transfers requiring the transmission of a Command/Address

byte followed by the data byte written or read from the addressed register. CS

duration of this two-byte transfer. As shown in Figure 5, the falling edge of CS

microport transfer is about to begin. The first 8 clock cycles of SCLK after the falling edge of CS

receive the Command/Address byte from the microcontroller. The Command/Address byte contains information

detailing whether the second byte transfer will be a read or a write operation and of what address. The next 8 clock

cycles are used to transfer the data byte between the DPhone-II and the microcontroller. At the end of the two-byte

transfer CS

DATA1 which will remain tri-stated as long as CS

is brought high again to terminate the session. The rising edge of CS will tri-state the output driver of

is high.

Receive data is sampled and transmit data is made available on DATA1 concurrent with the falling edge of SCLK.

Lastly, provision is made to separate the transmit and receive data streams onto two individual pins. This control is

given by the DATASEL pin in the General Control Register (address 0Fh). Setting DATASEL logic high will cause

DATA1 to become the data receive pin and DATA2 to become the data transmit pin. Only the signal paths are

altered by DATASEL; internal timing remains the same in both cases. Tri-stating on DATA2 follows CS

DATA1 when DATASEL is logic low. Use of the DATASEL bit is intended to help in adapting Motorola (SPI) and

National Semiconductor (Micro-wire) microcontrollers to the DPhone-II. Note that whereas Intel processor serial

ports transmit data LSB first other processor serial ports, including Motorola, transmit data MSB first. It is the

responsibility of the microcontroller to provide LSB first data to the DPhone-II.

must remain asserted for the

indicates to the DPhone-II that a

are always used to

as it does on

COMMAND/ADDRESS DATA INPUT/OUTPUT COMMAND/ADDRESS

DATA 1

Receive

DATA 1 or DATA 2

Tra ns mi t

SCLK

CS

✈✑✉

✈✒ ✉

✈✓✉

✈✔✉

✈✕✉

D0D1D2D3D4D5D6D

(2)

✈✓✉

Delays due to MCS-51 internal timing which are transparent.

The DPhone-II: -latches received data on the falling edge of SCLK

The falling edge of CS

byte is always data followed by CS

A new COMMAND/ADDRESS byte may be loaded only by CS

The COMMAND/ADDRESS byte contains:

-outputs transmit data on the falling edge of SCLK

indicates that a COMMAND/ADDRESS byte will be transmitted from the microprocessor. The subsequent

(5)

✈✑✉

7

returning high.

1 bit - Read/Write

6 bits - Addressing Data

1 bit - Not used, write logic "0"

Figure 5 - Serial Port Relative Timing

D

0D1D2D3D4D5D6D7

D0D1D2D3D4D5D6D

cycling high then low again.

✈✔✉

✈✑✉

D0D1D2D3D4D5D6D

7

D

7

0A5A4A

D0D1D2D3D4D5D6D

✈✔✉

✈✓✉

7

7

D

0

A2A

3

1

A0R/W

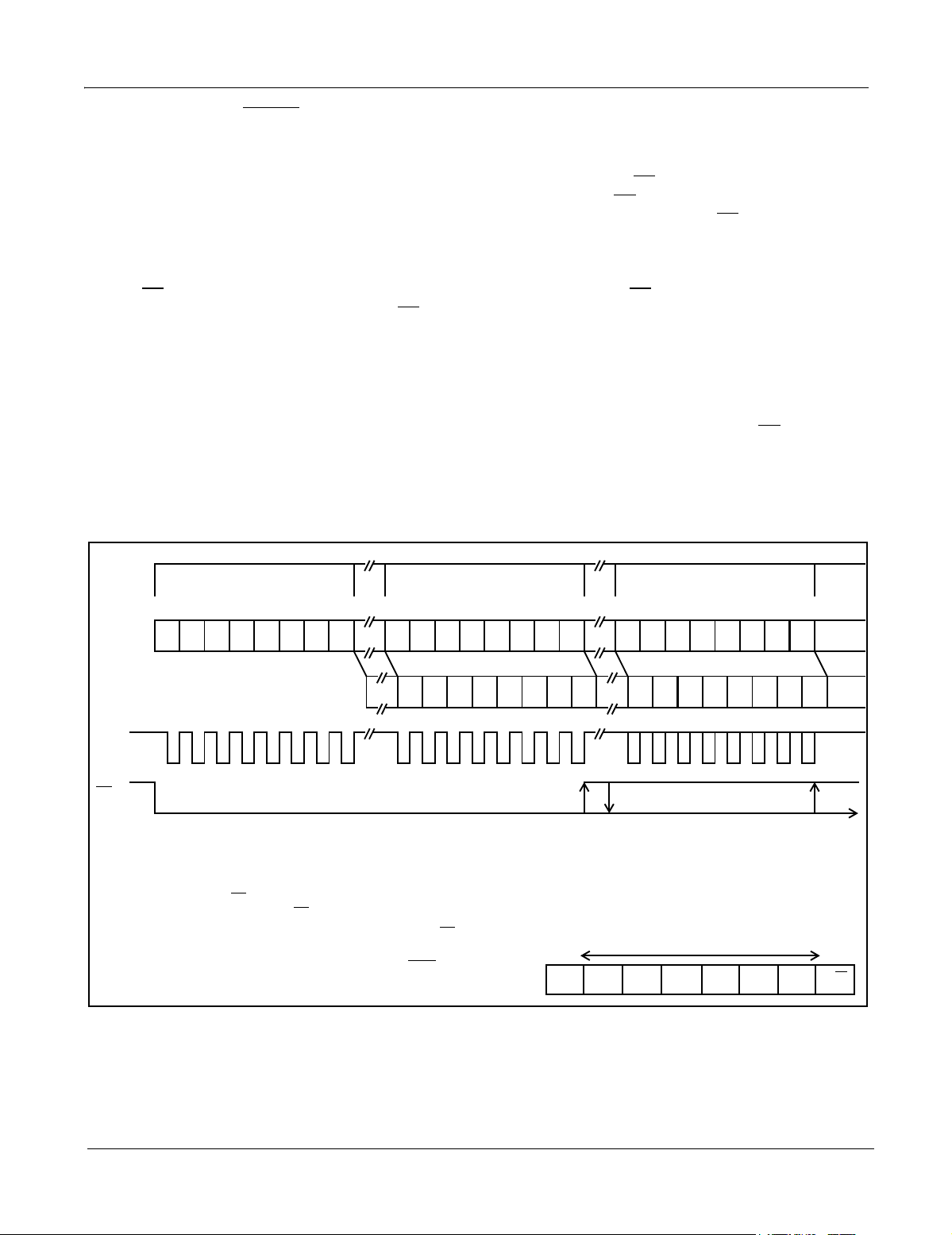

ST-BUS/Timing Control

A serial link is required for the transport of data between the DPhone-II and the external digital transmission device.

The DPhone-II utilizes the ST-BUS architecture defined by Zarlink Semiconductor. Refer to Zarlink Application Note

11

Zarlink Semiconductor Inc.

Page 12

MT9094 Data Sheet

MSAN-126. The DPhone-II ST-BUS consists of output and input serial data streams, DSTo and DSTi respectively,

a synchronous clock signal C4i

The data streams operate at 2048 kb/s and are Time Division Multiplexed into 32 identical channels of 64 kb/s

bandwidth. Frame Pulse (a 244 nSec low going pulse) is used to parse the continuous serial data streams into the

32 channel TDM frames. Each frame has a 125 µSecond period translating into an 8 kHz frame rate. Valid frame

pulse occurs when F0i

is logic low coincident with a falling edge of C4i. C4i has a frequency (4096 MHz) which is

twice the data rate. This clock is used to sample the data at the _ bit-cell position on DSTi and to make data

available on DSTo at the start of the bit-cell. C4i

Filter/CODEC, HDLC) and to provide the channel timing requirements.

The DPhone-II uses channels 1, 2 & 3 of the 32 channel frame. These channels are always defined, beginning with

the first channel after frame pulse, as shown in Figure 6 (DSTi and DSTo channel assignments). Channels are

enabled independently by the three control bits Ch

(address15h).

EN - C-Channel

Ch

1

Channel 1 conveys the control/status information for Zarlink’s layer 1 transceiver. The full 64 kb/s bandwidth is

available and is assigned according to which transceiver is being used. Consult the data sheet for the selected

transceiver for its bit definitions and order of bit transfer. When this bit is high register data is transmitted on DSTo.

When low, this timeslot is tri-stated on DSTo. Receive C-Channel data (DSTi) is always routed to the register

regardless of this control bit's logic state. C-channel data is transferred on the ST-BUS MSB first by the DPhone-II.

Ch

EN and Ch3EN - B1-Channel and B2-Channel

2

Channels 2 and 3 are the B1 and B2 channels, respectively. These bits (Ch

PCM channels from/to the DPhone-II as required.

, and a framing pulse F0i.

is also used to clock the DPhone-II internal functions (i.e., DSP,

En -Ch3En residing in the Timing Control Register

1

EN and Ch3EN) are used to enable the

2

Transmit PCM on DSTo

When high, PCM from the Filter/CODEC and DSP is transmitted on DSTo in the selected ST-BUS channel. When low,

DSTo is forced to logic 0 for the corresponding timeslot. If both Ch

EN and Ch3EN are enabled, default is to channel 2.

2

Receive PCM from DSTi

When high, PCM from DSTi is routed to the DSP and Filter/CODEC in the associated channel. If both Ch2EN and

EN are enabled the default is to channel 2.

Ch

3

New Call Tone

The New Call Tone Generator produces a frequency shifted square-wave used to toggle the speaker driver outputs.

This is intended for use where a ringing signal is required concurrently with an already established voice

conversation in the handset.

Programming of the DSP for New Call generator is exactly as is done for the tone ringer micro-program except that

the OPT bit (DSP Control Register, address 1Eh) is set high. In this mode the DSP does not produce a frequency

shifted squarewave output to the filter CODEC section. Instead the DSP uses the contents of the tone coefficient

registers, along with the tone warble rate register, to produce a gated squarewave control signal output which

toggles between the programmed frequencies. This control signal is routed to the New Call Tone block when the

NCT EN control bit is set (General Control Register, address 0Fh). NCT EN also enables a separate gain control

block, for controlling the loudness of the generated ringing signal. With the gain control block set to 0 dB the output

is at maximum or 6 volts p-p. Attenuation of the applied signal, in three steps of 8 dB, provide the four settings for

New Call tone (0, -8, -16, -24 dB). The NCT gain bits (NCTG

-NCTG1) reside in the FCODEC Gain Control Register

0

2 (address 0Bh).

12

Zarlink Semiconductor Inc.

Page 13

F0i

MT9094 Data Sheet

125 µs

DSTi,

DSTo

Not

Used

CHANNEL 1

C-channel

CHANNEL 2

B1-channel

MSB first for C, B1 - & B2-

Channels

CHANNEL 3

B2-channel

CHANNELS 4 - 31

Not Used

Figure 6 - ST-BUS Channel Assignment

Watchdog

To maintain program integrity an on-chip watchdog timer is provided for connection to the microcontroller reset pin.

The watchdog output WD (pin 17) goes high while the DPhone-II is held in reset via the PWRST

PWRST

clocked on the falling edge of F0i

will cause WD to return low immediately and will also start the watchdog timer. The watchdog timer is

and requires only this input, along with VDD, for operation.

If the watchdog reset word is written to the watchdog register (address 11h) after PWRST

(pin 6). Release of

is released, but before

the timeout period (T=512mSec) expires, a reset of the timer results and WD will remain low. Thereafter, if the reset

word is loaded correctly at intervals less than 'T' then WD will continue low. The first break from this routine, in

which the watchdog register is not written to within the correct interval or it is written to with incorrect data, will result

in a high going WD output after the current interval 'T' expires. WD will then toggle at this rate until the watchdog

register is again written to correctly.

5-BIT WATCHDOG RESET WORD

W4 W3 W2 W1 W0

XXX01010

x=don’t care

DPhone-II Register Map

Address

(Hex)

WRITE READ

00-09 RESERVED RESERVED

0A FCODEC GAIN CONTROL REGISTER 1 VERIFY

0B FCODEC GAIN CONTROL REGISTER 2 VERIFY

0C RESERVED RESERVED

0D RESERVED RESERVED

0E TRANSDUCER CONTROL REGISTER VERIFY

0F GENERAL CONTROL REGISTER VERIFY

10 RESERVED RESERVED

11 WATCHDOG REGISTER NOT USED

12 LCD SEGMENT ENABLE REGISTER 1 VERIFY

13 LCD SEGMENT ENABLE REGISTER 2 VERIFY

14 C-CHANNEL REGISTER (to DSTo) C-CHANNEL REGISTER (from DSTi)

15 TIMING CONTROL REGISTER VERIFY

16 LOOP-BACK REGISTER VERIFY

17-1C RESERVED RESERVED

13

Zarlink Semiconductor Inc.

Page 14

DPhone-II Register Map

MT9094 Data Sheet

Address

(Hex)

WRITE READ

1D RECEIVE GAIN CONTROL REGISTER VERIFY

1E DSP CONTROL REGISTER VERIFY

1F RESERVED RESERVED

20 TRANSMIT AUDIO GAIN REGISTER VERIFY

21 TRANSMIT DTMF GAIN REGISTER VERIFY

22 RESERVED RESERVED

23 TONE COEFFICIENT REGISTER 1 VERIFY

24 TONE COEFFICIENT REGISTER 2 VERIFY

25 RESERVED RESERVED

26 TONE RINGER WARBLE RATE REGISTER VERIFY

27-3F RESERVED RESERVED

Test Loops

Detail LBio and LBoi Loopback Register (address 16h)

LBio Setting this bit causes data on DSTi to be looped back to DSTo directly at the pins. The appropriate channel

enables Ch

EN -Ch3EN must also be set.

1

LBoi Setting this bit causes data on DSTo to be looped back to DSTi directly at the pins.

14

Zarlink Semiconductor Inc.

Page 15

MT9094 Data Sheet

Register Summary

This section contains a complete listing of the DPhone-II register addresses, the control/status bit mapping

associated with each register and a definition of the function of each control/status bit.

The Register Summary may be used for future reference to review each of the control/status bit definitions without

the need to locate them in the text of the functional block descriptions.

ADDRESSES 00h and 09h are RESERVED

FCODEC Gain Control Register 1 ADDRESS = 0Ah WRITE/READ VERIFY

Power Reset Value

-RxFG

RxFG1RxFG

2

0

TxFG2TxFG1TxFG

-

0

76543210

X000 X000

Receive Gain

Setting (dB)

(default) 0

-1

-2

-3

-4

-5

-6

-7

RxFG

RxFG

0

0

0

0

1

1

1

1

= Receive Filter Gain n TxFGn = Transmit Filter Gain n

n

RxFG

2

0

0

1

1

0

0

1

1

RxFG

1

0

0

1

0

1

0

1

0

1

Transmit Gain

Setting (dB)

(default) 0

1

2

3

4

5

6

7

TxFG

0

0

0

0

1

1

1

1

TxFG

2

0

0

1

1

0

0

1

1

TxFG

1

0

0

1

0

1

0

1

0

1

FCODEC Gain Control Register 2 ADDRESS = 0Bh WRITE/READ VERIFY

Power Reset Value

--

NCTG

NCTG

1

0

0

STG2STG1STG

-

0X00 X000

76543210

Gain (dB) NCTG

0 (default)

-8

-16

-24

0

0

1

1

NCTG

1

NCTGn = New Call Tone Gain n

0

0

1

0

1

Side-tone Gain

Setting (dB)

(default) OFF

-9.96

-6.64

-3.32

0

3.32

6.64

9.96

STG

0

0

0

0

1

1

1

1

2

STG

1

0

0

1

1

0

0

1

1

STG

0

1

0

1

0

1

0

1

0

15

Zarlink Semiconductor Inc.

STG

= Side-tone Gain n

n

Page 16

MT9094 Data Sheet

ADDRESSES 0Ch and 0Dh are RESERVED

Note: Bits marked "-" are reserved bits and should be written with logic "0".

Transducer Control Register ADDRESS = 0Eh WRITE/READ VERIFY

PuFC Tfhp

DIAL SIDE

MIC

EN EN EN

MIC/

HNSTMIC

SPKR

EN

HSSPKR

EN

Power Reset Value

0000 0000

76 543 2 1 0

PuFC When high, the Filter/CODEC is powered up. When low, the Filter/CODEC is powered down. If PuFC, SPKR EN and

Tfhp When high, an additional high pass function (passband beginning at 400 Hz) is inserted into the transmit path. When low, this

DIAL EN When high, a first order lowpass filter is inserted into the receive path (3 dB = 1 kHz). When low, this lowpass filter is disabled.

SIDE EN When high, the sidetone path is enabled (assuming STG

MIC EN When high, the selected transmit microphone is enabled to the transmit filter section. When low, the microphone path is muted.

MIC/HNSTMIC

SPKR EN When high, the handsfree loudspeaker driver is powered up. When low, this driver is powered down.

HSSPKR EN When high, the handset speaker driver is powered up. When low, this driver is powered down.

HSSPKR EN are all low then the VRef/VBias circuit is also powered down.

highpass filter is disabled.

are not all low). When low, the sidetone path is disabled.

2-0

When high, the handsfree microphone (pins MIC±) is muxed into the transmit path. When low, the handset microphone (pins

±) is muxed into the transmit path. Both are contingent on "MIC EN".

M

General Control Register ADDRESS = 0Fh WRITE/READ VERIFY

RST

DATA

SEL

A/

µ

Sign-Mag/

CCITT

A/

Rx

MIC

µ

A/

Side

A/

µ

NCT

EN

µ

Power Reset Value

0000 0000

76 543 2 1 0

RST Active high reset. Performs the same function as PWRST but does not affect the microport or the watchdog circuits. To remove

DATASEL When high, the microport transmit and receive are performed on separate pins. DATA1 is receive while DATA2 is transmit.

A/u

Sign-mag/CCITT

RxA/u

MICA/u

SIDEA/u

NCT EN When high, the new call tone generator output from the DSP is selected as the source for the loudspeaker path. When low, the

this reset a PWRST

When low, the microport conforms to Intel MCS-51 mode 0 specifications; DATA1 is a bi-directional (transmit/receive) serial

data pin while DATA2 is internally disconnected and tri-stated.

When high, A-Law (de)coding is selected. When low, µ-Law (de)coding is selected.

When high, sign-magnitude bit coding is selected, When low, true CCITT PCM coding is selected.

When high, the receiver driver nominal gain is set at -9.7 dB. When low this driver nominal gain is set at -12.3 dB.

When high, the transmit amplifier nominal gain is set at 15.4 dB. When low this amplifier nominal gain is set at 6.1 dB.

When high, the side-tone nominal gain is set at -18.8 dB. When low this nominal gain is set at -11 dB.

CODEC output is selected for the loudspeaker path. Note that SPKR EN must also be set high for new call tone to function.

must occur or this bit must be written low.

Note: Bits marked "-" are reserved bits and should be written with logic "0".

16

Zarlink Semiconductor Inc.

ADDRESS 10h is RESERVED

Page 17

MT9094 Data Sheet

Watchdog Register ADDRESS = 11h WRITE

Power Reset Value

---W

W

4

W

3

W

2

W

1

0

76543210

WATCHDOG RESET WORD - XXX01010

LCD Segment Enable Register 1 ADDRESS = 12h WRITE/READ VERIFY

SC

SC

8

SC

7

SC

6

SC

5

SC

4

SC

3

SC

2

1

76543210

Twelve segment control bits used for the LCD outputs. When high the respective segment is on. When low the respective segment is off.

XXX0 1010

Power Reset Value

0000 0000

LCD Segment Enable Register 2 ADDRESS = 13h WRITE/READ VERIFY

Power Reset Value

-

-

--SC

SC

12

SC

11

SC

10

9

XXXX 0000

76543210

Twelve segment control bits used for the LCD outputs. When high the respective segment is on. When low the respective segment is off.

C-Channel Register ADDRESS = 14h WRITE/READ

Power Reset Value

D

D

7

D

6

D

5

D

4

D

3

D

2

D

1

0

Write = 1111 1111

Read = Not Applicable

76543210

Micro-port access to the ST-BUS C-Channel information.

Note: Bits marked "-" are reserved bits and should be written with logic "0".

17

Zarlink Semiconductor Inc.

Page 18

MT9094 Data Sheet

Timing Control Register ADDRESS = 15h WRITE/READ VERIFY

Power Reset Value

-- --CH

EN CH1ENCH2EN

3

-

76543210

All bits active high:

EN and Ch3EN

Ch

2

Channels 2 and 3 are the B1 and B2 channels, respectively. PCM associated with the DSP, Filter/CODEC and transducer audio

paths is conveyed in one of these channels as selected in the timing control register.

Transmit B1 and B2 data on DSTo

When high PCM from the Filter/CODEC and DSP is transmitted on DSTo in the associated channel. When low DSTo is

forced to logic 0 for the corresponding timeslot. If both Ch

Receive B1 and B2 data on DSTi

When enabled PCM from DSTi is routed to the DSP and Filter/CODEC in the associated channel. If both Ch

are enabled, data input defaults to channel 2.

Ch

EN Channel 1 conveys the control/status information for the layer 1 transceiver. The full 64kb/s bandwidth is available and is assigned

1

according to which transceiver is being used. Consult the data sheets for the transceiver selected. When high register data is trans-

mitted on DSTo. When low this timeslot is tri-stated on DSTo. Receive C-Channel data (DSTi) is always routed to the register

regardless of this control bit's logic state.

EN and Ch3EN are enabled, data defaults to channel 2.

2

XX0X 0000

EN and Ch3EN

2

Loop-back Register ADDRESS = 16h WRITE/READ VERIFY

Power Reset Value

- LBio LBoi - - ---

X00X XXXX

76543210

LB

LB

Active high enables data from the ST-BUS input to be looped back to the ST-BUS output directly at the pins. The DSTo tri-state driver

io

must also be enabled using one of the channel enable signals.

Active high enables data from ST-BUS output to be looped back to the ST-BUS input directly at the pins.

oi

ADDRESSES 17h - 1Ch are RESERVED

Note: Bits marked "-" are reserved bits and should be written with logic "0".

18

Zarlink Semiconductor Inc.

Page 19

MT9094 Data Sheet

Receive Gain Control Register ADDRESS = 1Dh WRITE/READ VERIFY

Power Reset Value

-AUTOB5B4 B2B1B0B3

76543210

AUTO When high autonulling of the transmit PCM is enabled. When low, autonulling is disabled. This bit is used in conjunction with the PS2 -

PS0 bits of the DSP Control Register at address 1Eh.

B5-B0 These 6 bits (indicated below in hexadecimal) are decoded to control Rx PCM gain:

B5-B0 Gain Setting (dB) B5-B0 Gain Setting (dB)

3F +22.5 1F -25.5

3E +21.0 1E -27.0

3D +19.5 1D -28.5

3C +18.0 1C -30.0

3B +16.5 1B -31.5

3A +15.0 1A -33.0

39 +13.5 19 -34.5

38 +12.0 18 -36.0

37 +10.5 17 -37.5

36 +9.0 16 -39.0

35 +7.5 15 -40.5

34 +6.0 14 -42.0

33 +4.5 13 -43.5

32 +3.0 12 -45.0

31 +1.5 11 -46.5

30 +0.0 10 -48.0

2F -1.5 0F -49.5

2E -3.0 0E -51.0

2D -4.5 0D -52.5

2C -6.0 0C -54.0

2B -7.5 0B -55.5

2A -9.0 0A -57.0

29 -10.5 09 -58.5

28 -12.0 08 -60.0

27 -13.5 07 -61.5

26 -15.0 06 -63.0

25 -16.5 05 -64.5

24 -18.0 04 -66.0

23 -19.5 03 -67.5

22 -21.0 02 -69.0

21 -22.5 01 -70.5

20 -24.0 00 -72.0

0000 0000

Note: B0-B5 of addresses 20h and 21h are encoded in the same manner

Note: Bits marked "-" are reserved bits and should be written with logic "0".

19

Zarlink Semiconductor Inc.

Page 20

MT9094 Data Sheet

DSP Control Register ADDRESS = 1Eh WRITE/READ VERIFY

Power Reset Value

PS2 PS1 PS0

OPT

RxMUTE -TxMUTE DRESET

76543210

OPT: When high, the tone ringer is in New Call tone mode. When low the normal tone ringer program is executed.

RxMUTE: This bit when high turns off the receive PCM channel, substituting quiet code.

TxMUTE: This bit when high turns off the transmit PCM channel, substituting quiet code.

DRESET

: This bit (when high) enables the DSP. If low, no programs are executed, the master clock is disabled and the program counter is

PS2-PS0: These bits are program select bits for the DSP Rom programs.

reset to zero.

0000 0000

PS2

PS1 PS0 MICRO-PROGRAM

0 0 0 Power up reset program

0 0 1 Gain control program

0 1 0 DTMF & Gain control program

0 1 1 Tone Ringer & Gain control program

1 0 0 Handsfree program

101Reserved

110Reserved

111Reserved

ADDRESS 1Fh is RESERVED

Transmit Audio Gain Register ADDRESS = 20h WRITE/READ VERIFY

Power Reset Value

--B5B4 B2B1B0B3

XX11 0000

76543210

This register controls the transmit speech path gain in 1.5dB steps as in Receive Gain Register (address 1Dh).

Transmit DTMF Gain Register

ADDRESS = 21h WRITE/READ VERIFY

--B5B4 B2B1B0B3

76543210

This register controls the transmit DTMF level in 1.5dB steps as in Receive Gain Register (address 1Dh).

Note: Bits marked "-" are reserved bits and should be written with logic "0".

20

Zarlink Semiconductor Inc.

Power Reset Value

XX10 1110

ADDRESS 22h is RESERVED

Page 21

MT9094 Data Sheet

Tone Coeff Register 1-DTMF or Tone Ringer ADDRESS = 23h WRITE/READ VERIFY

B7 B6 B5 B4 B3 B1B2 B0

Power Reset Value

0000 0000

76543210

This register is used to program the low-group frequency of the DTMF program. The tone coefficient is calculated as follows:

COEF = 0.128 x Frequency

where: Frequency is in Hz (note: COEF must be converted to an 8 bit binary integer)

Highest frequency possible: 1992.2 Hz

Lowest frequency possible: 7.8 Hz

Frequency resolution: 7.8 Hz

Pre-twist: -2.1 dB

This register is used to program the first frequency of the squarewave ringer program. The tone coefficient is calculated as follows:

COEF = 8000 / Frequency

where: Frequency is in Hz (note: COEF must be rounded off and converted to an 8 bit binary integer)

Highest frequency possible: 4000 Hz

Lowest frequency possible: 31.4 Hz

Frequency resolution: non-linear

This tone can be disabled by writing zero to this register for single tone generation.

± 0.2 dB

Tone Coeff Register 2-DTMF or Tone Ringer ADDRESS = 24h WRITE/READ VERIFY

B7 B6 B5 B4 B3 B1B2 B0

Power Reset Value

0000 0000

76543210

This register is used to program the high-group frequency of the DTMF program. The tone coefficient is calculated as follows:

COEF = 0.128 x Frequency

where: Frequency is in Hz (note: COEF must be converted to an 8 bit binary integer)

Highest frequency possible: 1992.2 Hz

Lowest frequency possible: 7.8 Hz

Frequency resolution: 7.8 Hz

Pre-twist: 0 dB

This register is used to program the second frequency of the squarewave program. The tone coefficient is calculated similarly to tone coefficient reg-

ister 1.

21

Zarlink Semiconductor Inc.

ADDRESS 25h is RESERVED

Page 22

MT9094 Data Sheet

Tone Ringer Warble Rate-Tone Ringer ADDRESS = 26h WRITE/READ VERIFY

Power Reset Value

B7 B6 B5 B4 B3 B1B2 B0

76543210

The tone ringer will switch between squarewave frequencies at a warble frequency defined by this register. The relationship between the duration

period of each tone and the 8 bit warble coefficient is as follows:

Tone duration (warble frequency) = 500 / COEF

where: Frequency is in Hz, and 0≤COEF <256

Highest frequency possible: 500 Hz

Lowest frequency possible: 2.0 Hz

Frequency resolution: non-linear

Addresses: 27h to 2Dh are transmit and receive gains and coefficients used by the filters in the handsfree decision cir-

cuit.

2Eh to 3Fh are scratch-pad ram locations used by the DSP algorithms as temporary storage during calcula-

tions.

Applications

0000 0000

To maintain a fully differential topology in the transmit path the suggested connection scheme for the transmit

microphones is shown in Figure 7. However, it is possible to use a single-ended arrangement as shown in Figure 8

for the transmit interface. In this case the dynamic range of the MT9094 is reduced by half. In both figures the

output drivers are connected in a fully differential manner.

The MT9094 is a member of the Zarlink family of digital terminal equipment components. There are two

transmission devices which connect directly with the MT9094 to complete an application; the MT8930 (SNIC) and

the MT8971/72 (DSIC/DNIC). An ISDN 4-wire "TE" function is implemented with the MT8930/MT9094 combination.

A 2-wire digital phone for PABX, key-systems and other proprietary applications is implemented with the

MT8971/72/MT9094 combination.

Figures 9 and 10 show the 4-wire and 2-wire applications, respectively.

22

Zarlink Semiconductor Inc.

Page 23

ST-BUS

Port

Transmission

Device

Serial

Microport

INTEL

MCS-51

to

+5V

DATA2

DATA1

Av = 1+

DSTi

DSTo

C4i

F0i

SCLK

CS

WD

MT9094 Data Sheet

+

-

T

100K

VBias

100K

0.1µF

VBias

MT9094

R

2R

T

R

-

+

0.1µF

6543214443424140

7

8

9

10

11

12

13

14

15

16

17

+5V

0.1µF

0.1µF

330Ω

511Ω

511Ω

Av = 1+

+

2R

T

+

10µF

Electret

Microphone

R

R

39

38

37

36

35

34

33

32

31

30

29

+

-

+

-

75Ω

.1µF

LCD

+5V

T

1000pF

75Ω

100K

VBias

100K

+5V

0.1µF

0.1µF

1000pF

330Ω

511Ω

+

Electret

Microphone

511Ω

+40Ω nom.

32Ω min.

150Ω

1000pF caps

are optional

+

10µF

18 19 20 21 22 23 24 25 26 27 28

LCD

Note: Single-ended configurations reduce

dynamic range by a factor of two.

Figure 7 - Application Circuit - fully differential audio input

23

Zarlink Semiconductor Inc.

Page 24

MT9094 Data Sheet

330Ω

1µF

+5V

1K

+

VBias

–

R

T

+

Electret

+

Microphone

10µF

ST-BUS

Port

Transmission

Device

Serial

Microport

INTEL

MCS-51

to

+5V

DATA2

DATA1

DSTi

DSTo

C4i

F0i

SCLK

CS

WD

0.1µF

6543214443424140

7

8

9

10

11

12

13

14

15

16

17

18 19 20 21 22 23 24 25 26 27 28

0.1µF

VBias

MT9094

VBias

+

–

R

39

38

75Ω

37

36

35

34

33

32

31

30

29

+5V

.1µF

LCD

T

75Ω

1000pF 1000pF

Note: Single-ended configurations reduce

dynamic range by a factor of two.

+5V

1µF

330Ω

1K

Electret

Microphone

40Ω nom.

+

32Ω min.

150Ω

1000pF caps

are optional

+

10µF

+

LCD

Figure 8 - Application Circuit - single-ended audio input

24

Zarlink Semiconductor Inc.

Page 25

MT9094 Data Sheet

CCITT ISDN

Reference

Point S

Interface

DC to DC

Converter

5 Volts

LTx

VBias

LRx

MT8930

SNIC

with

HDLC

Controller

(ALE) (RD

C4b

F0b

DSTo

DSTi

IRQ

)(WR)

AD0-7

C4i

F0i

DSTi

DSTo

IRQ

AD0-7

IRQ

CS

MT9094

DPhone-∏

SCLK

AS

(ALE)E(RD

8051

INTEL

DATA1

)

MCS-

51

HSPKR+

HSPKR-

M+

M-

MIC+

MIC-

SPKR+

SPKR-

R/W

(WR)

Handset

Microphone

Speaker

Figure 9 - CCITT ISDN Voice/Data Terminal Equipment - TE1

25

Zarlink Semiconductor Inc.

Page 26

MT9094 Data Sheet

Twisted Pair

to Central

PBX

DC to DC

CONVERTER

5 volts

Lin

Lout

Z

MT8972

DNIC

T

10.24 MHz

C4

F0

DSTo

DSTi

C4i

F0i

DSTi

DSTo

MT9094

DPhone-∏

SCLK DATA1

CS

INTEL

MCS-51

Figure 10 - Voice/Data Digital Telephone Set Circuit

HSPKR+

HSPKR-

M+

M-

MIC+

MIC-

SPKR+

SPKR-

Handset

Microphone

Speaker

26

Zarlink Semiconductor Inc.

Page 27

MT9094 Data Sheet

Programming Examples

Some examples of the programming steps required to set-up various telephony functions are given. Note that these

steps are from the power-up reset default definition. If some other state is currently true then some programming

steps may be omitted while new ones may be required.

Standard Full-duplex handset call

Description Address DATA

select B-Channel of operation 15h bits 2 or 3 (as required)

reset DSP 1Eh 00h

set Rx gain (ie 0dB with Tx autonull) 1Dh 70h (or as required)

set Tx gain (ie 0dB) 20h 30h (or as required)

start Rx gain program 1Eh 21h

select transducers and turn on

sidetone and filter/CODEC

set sidetone gain 0Bh 04h (for 0dB or as required)

optional:

set CODEC Rx and Tx gain

select A-Law versus µ-Law

Half-Duplex handsfree operation

Description Address DATA

select B-Channel of operation 15h bits 2 or 3 (as required)

reset DSP 1Eh 00h

set Rx g a in (ie 12 dB) 1Dh 38h (or as required)

set Tx gain (ie 0dB) 20h 30 h (or as required)

start handsfree program 1Eh 81h

select transducers and filter/CODEC

and turn off sidetone

optional:

set CODEC Rx and Tx gain

select A-Law versus µ-Law

0Eh 99h

0Ah

0Fh

0Eh 1Eh

0Ah

0Fh

as required (0dB default)

bits 1-5 (as required)

as required (0dB default)

bits 1-5 (as required)

Generate tone ringer

Description Address DATA

select B-Channel of operation 15h bits 2 or 3 (as required)

reset DSP 1Eh 00h

set Rx gain (ie 0 dB with Tx

autonull)

set Tx gain (ie 0dB) 20h 30h (or as required)

write tone coefficient 1 23h as required

write tone coefficient 2 24h as required

write warble tone rate coefficient 26h as required

start tone ringer program 1Eh 61h

select speaker and filter/CODEC

and turn off sidetone

control ringer cadence by toggling

RxMUTE

1Dh 70h (or as required)

0Eh 82h

1Eh 61 (on)

69 (off)

61 (on)

69 (off) etc...

27

Zarlink Semiconductor Inc.

Page 28

MT9094 Data Sheet

Generate DTMF tones

Description Address DATA

select B-Channel of operation 15h bits 2 or 3 (as required)

reset DSP 1Eh 00h

set Rx DTMF gain (ie -20 dBm0) 1Dh 22h (or as required)

set Tx audio gain (ie 0dB) 20h 30h (or as required)

set Tx DTMF gain (ie -4dBm0) 21h 2Eh (or as required)

write tone coefficient 1 23h as required

write tone coefficient 2 24h as required

start DTMF program 1Eh 41h

select transducers and filter/CODEC

(PuFC)

and turn off sidetone

optional:

set CODEC Rx gain 0Ah as required (0dB default)

send tones in only Rx or Tx by

disabling

RxMUTE or TxMUTE appropriately

New Call Tone

Description Address DATA

Assume that a B-Channel of operation has already been selected for the concurrent handset

conversation.

If this is not true select one.

select B-Channel of operation 15h bits 2 or 3 (as required)

reset DSP 1Eh 00h

0Eh as required

1Eh as required

**********************************************************************************

set Rx gain (ie 0 dB with Tx autonull) 1Dh 70h (or as required)

set Tx gain (ie 0dB) 20h 30h (or as required)

Note: these two steps a required for the concurrent conversation only and do not affect new

call tone generation. See Standard Full-duplex handset call for required programming.

**********************************************************************************

write tone coefficient 1 23h as required

write tone coefficient 2 24h as required

write warble rate coefficient 26h as required

start new call tone ringer program 1Eh 71h

set new call tone gain 0Bh NCTG2-1 (as required)

select speaker 0Eh 02h

9Bh (assuming a concurrent handset

call)

enable new call tone 0Fh 01h (assuming all other bits are µ-Law

control ringer cadence by toggling

between gain control and tone ringer

with gain control programs

1Eh 71h (on)

31h (off)

71h (on) etc...

28

Zarlink Semiconductor Inc.

Page 29

Absolute Maximum Ratings

MT9094 Data Sheet

Parameter Symbol Min. Max. Units

1 Supply Voltage V

DD-VSS

2 Voltage on any I/O pin V

3 Current on any I/O pin (transducers excluded) I

4 Storage Temperature T

5 Power Dissipation (package) Plastic P

I/VO

I/IO

S

D

-0.3 7 V

VSS-0.3 VDD+0.3 V

±20 mA

-65 +150 °C

750 mW

6Static Discharge ESD ±2.0 KV

7 Latch-up Current I

Recommended Operating Conditions

- Voltages are with respect to V

LU

unless otherwise stated.

SS

±100 mA

Characteristics Sym. Min. Typ. Max. Units Test Conditions

1 Supply Voltage V

2 Input Voltage (high) * V

3 Input Voltage (low) * V

4 Operating Temperature T

5 Clock Frequency (C4i

* Excluding PWRST

which is a Schmitt Trigger Input.

)f

CLK

4.7555.25V

DD

2.4 V

IH

V

IL

A

SS

-40 +85 °C

DD

0.4 V Noise margin = 400 mV

409240964100 kHz

VNoise margin = 400mV

Power Characteristics

Characteristics Sym. Min. Typ. Max. Units Test Conditions

1 Supply Current (clock enabled, all

I

DDC1

functions off

2 Supply Current by function

Filter/Codec

DSP

Handset Driver (bias only, no signal)

Speaker Driver (bias only, no signal)

Timing Control, C-Channel, ST-BUS,

I

DDF1

I

DDF3

I

DDF4

I

DDF5

I

DDF6

etc.

Total all functions enabled

Note 1: Power delivered to the load is in addition to the bias current requirements.

Note 2: I

is not additive to I

DDFT

DDC1

.

I

DDFT

1.5

1.5

1.5

1.5

1.0

7.0 14

6mA

mA

mA

mA

mA

See Note 1.

See Note 1.

mA

mA

See Note 2.

29

Zarlink Semiconductor Inc.

Page 30

MT9094 Data Sheet

DC Electrical Characteristics

Characteristics Sym. Min. Typ.

1 Input HIGH Voltage TTL inputs V

2 Input LOW Voltage TTL inputs V

3 VBias Voltage Output V

4 Input Leakage Current

5 Positive Going Threshold

Voltage (PWRST

only)

Negative Going Threshold

Voltage (PWRST

only)

6 Output HIGH Current TTL O/P I

7 Output LOW Current TTL O/P I

8 Output Voltage V

9 Output Leakage Current

10 Output Capacitance C

11 Input Capacitance C

† DC Electrical Characteristics are over recommended temperature and range & recommended power supply voltages.

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Note 1 TTL compatible pins only

†

(except LCD Drive Pins) - Voltages are with respect to ground (V

‡

Max. Units Test Conditions

IN

IL

Bias

1

1

.

I

IZ

V

T+

V

T-

OH

OL

Ref

I

OZ

2.0 V

0.8 V

VDD/2 V Max. Load = 100 µA

0.1 10 µAVIN = VDD to V

3.3

1.5

-10 -16 mA VOH = 2.4V DSTo, WD,

510 mAV

(VDD/2)-1.5

0.01 10 µAV

o

i

15 pF

10 pF

VNo load

) unless otherwise stated.

SS

SS

DATA1,

DATA2

= 0.4V DSTo, WD,

OL

DATA1,

DATA2

= VDD and V

OUT

SS

DC Electrical Characteristics

†

- LCD Drive Pins - Voltages are with respect to ground (V

Characteristics Sym. Min. Typ. Max. Units Test Conditions

1 Output High Voltage Both

V

OH

4.8 --- --- Volts Io = 1 mA, V

Segment and Backplane

2 Output Low Voltage Both

V

OL

--- --- 0.2 Volts Io = 1 mA, VDD = 5 V

Segment and Backplane

3 Segment Output Load --- --- 1200 pF

4 Backplane Output Load --- --- 7200 pF

5 Frequency 62 62.5 63 Hz

) unless otherwise stated.

SS

= 5 V

DD

30

Zarlink Semiconductor Inc.

Page 31

MT9094 Data Sheet

AC Characteristics† for A/D (Transmit) Path - 0dBm0 = 1.421V

0.5 volts and V

channel noise.

= 2.5 volts). All parameters pertain exclusively to the Filter/CODEC except absolute half-channel gain and transmit idle

Bias

Characteristics Sym. Min. Typ.

1 Analog input equivalent to

overload decision

2 Absolute half-channel gain.

Transmit filter gain = 0 dB setting

All other transmit filter settings

(1 to 7 dB) are in addition to 0 dB

A

A

Li3.17

Li3.14

G

G

G

G

AX1

AX2

AX1

AX2

5.4

14.7

-0.15

-0.15

setting

3 Gain tracking vs. input level

CCITT G.714 Method 2

G

TX

-0.3

-0.6

-1.6

4 Signal to total Distortion vs. input

level

CCITT G.714 Method 2

D

QX

35

29

24

for µ-Law and 1.477V

rms

‡

Max Units Test Conditions

5.79

6.0

6.1

15.4

6.8

16.1

+0.15

+0.15

0.3

0.6

1.6

for A-Law, at the CODEC. (V

rms

Vp-p

Vp-p

µ-Law

A-Law

Both at CODEC

dB

dB

MICA/u=0*

MICA/u

MIC± or M± to PCM

1020Hz

dB

dB

MICA/u=0*

MICA/u

from nominal

MIC± or M± to PCM

1020 Hz

dB

dB

dB

dB

dB

dB

3 to -40 dBm0

-40 to -50 dBm0

-50 to -55 dBm0

0 to -30dBm0

-40 dBm0

-45 dBm0

=1*

=1*

Ref

=

5 Transmit Idle Channel Noise N

6 Gain relative to gain at 1020 Hz

<50 Hz

60 Hz

200 Hz

300-3000 Hz

3000-3400 Hz

4000 Hz

>4600 Hz

7 Absolute Delay D

8 Group Delay relative to D

AX

CX

N

PX

G

RX

15

-72

-0.25

-0.9

AX

D

DX

360 µs at frequency of minimum

750

380

130

750

17.5

-66

-25

-30

0.0

0.25

0.25

-12.5

-25

dBrnC0

dBrn0p

dB

dB

dB

dB

dB

dB

dB

µs

µs

µs

µs

9 Power Supply Rejection

f=1020 Hz

f=0.3 to 3 kHz

f=3 to 4 kHz

f=4 to 50 kHz

† AC Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

*Note: MICA/u

, refer to General Control Register, address 0Fh.

PSSR

PSSR1

PSSR2

PSSR3

37

40

35

40

dB

dB

dB

dB

µ-Law

A-Law

delay

500-600 Hz

600-1000 Hz

1000-2600 Hz

2600 - 2800 Hz

100mV

rms

signal

µ-Law

PSSR1-3 not production

tested

31

Zarlink Semiconductor Inc.

Page 32

MT9094 Data Sheet

AC Characteristics† for D/A (Receive) Path - 0dBm0 = 1.421V

volts and V

= 2.5 volts). All parameters pertain exclusively to the Filter/CODEC except absolute gain and receive idle channel noise.

Bias

for µ-Law and 1.477V

rms

rms

Characteristics Sym. Min. Typ.‡Max. Units Test Conditions

35

29

24

5.704

5.906

0.2

-12.3

-9.7

0.95

-11.8

-9.1

+0.15

+0.15

+0.15

0.3