Yamaha RXA-720 Service Manual

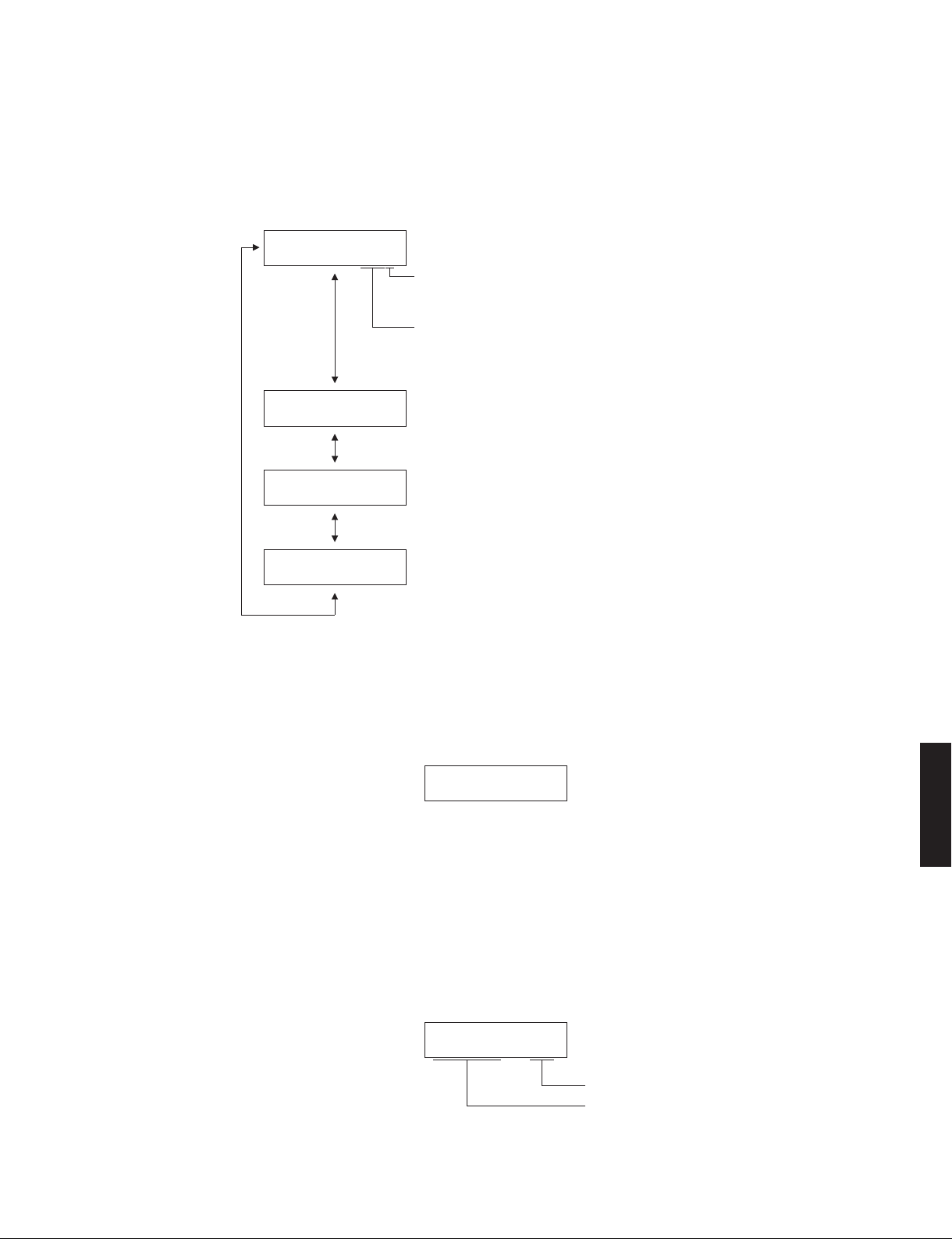

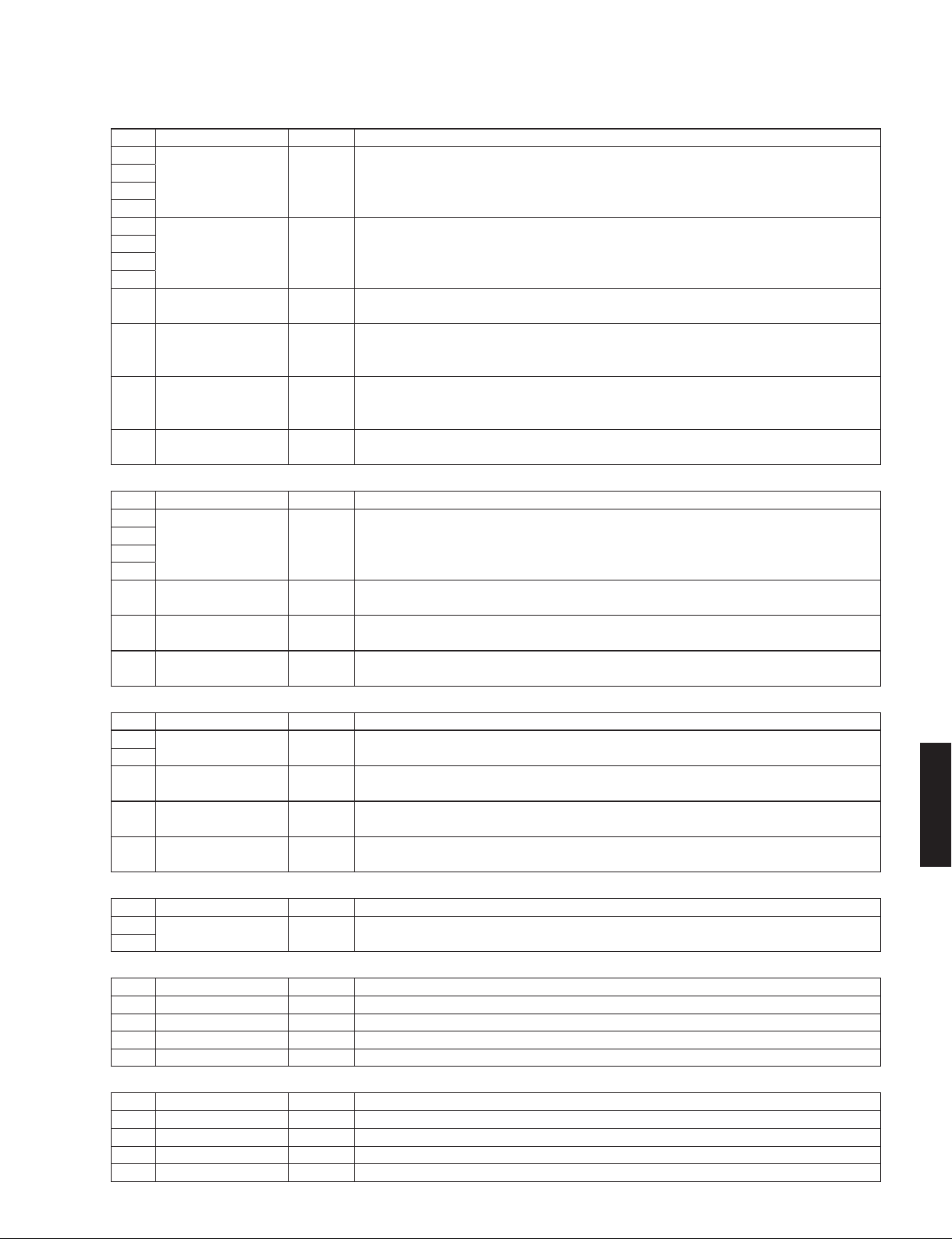

P2. PROTECTION HISTORY

This menu is used to display the history of protection function.

All history of protection function will be erased by pressing the “STRAIGHT” key.

* Numeric values in the figure are given as reference only.

RX-V673/HTR-6065/RX-A720

P2-1

1st:PS2000L

P2-2

2nd:TMP1000L

P2-3

3rd:DC000L

P2-4

NoPrt

P2-1. History 1

H: Displayed when the voltage is HIGHER than upper limit.

L: Displayed when the voltage is LOWER than lower limit.

xxx: A/D conversion value of voltage at the moment when the protection function

worked.

(Reference voltage: 3.3 V=255)

P2-2. History 2

P2-3. History 3

P2-4. History 4

S1. FIRMWARE UPDATE

Not for service.

S1-1

F/WUPDATE?

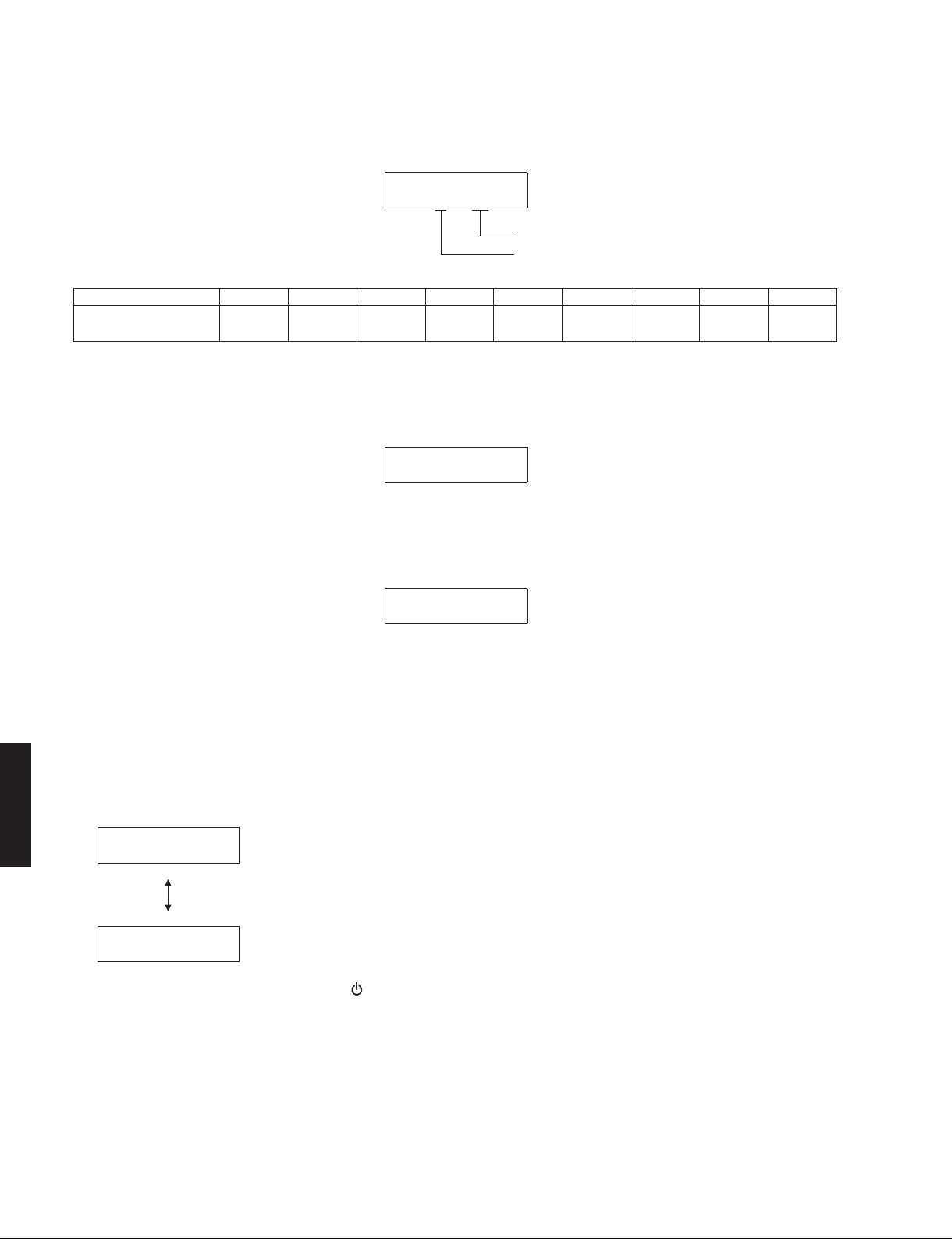

S2. SET INFORMATION

The model name and destination of this unit are displayed.

S2-1. MODEL

The model name of this unit is displayed.

S2-1

MDL:V673255

RX-V673/HTR-6065/

RX-A720

Not for service.

Model name

V673 : RX-V673

6065 : HTR-6065

A720 : RX-A720

61

RX-V673/HTR-6065/RX-A720

S2-2. DESTINATION

The destination of this unit is displayed.

Destination J U C R (R, S) T K A BG (B, G, F) L (L, H)

A/D conversion value

(3.3 V=255)

S2-3. DEBUG

Not for service.

S2-2

DEST:U28

A/D conversion value

Destination

0 − 12 13 − 39 40 − 67 68 − 92 93 − 115 116 − 140 141 − 169 199 − 221 222 − 244

S2-3

DBG:255

S2-4. NET RESTART COUNTER

S3. FACTORY PRESET

This menu is used to reserve/inhibit initialization of the back-up IC (EEPROM: IC82 on DIGITAL P.C.B.).

RX-A720

RX-V673/HTR-6065/

S3-1

PRESET:INH

S3-1

PRESET:RSRV

Not for service.

S2-4

NRC:0

S3-1. PRESET INHIBIT (Initialization inhibited)

Initialization of the back-up IC is not executed. Select this sub-menu to protect the values set by the user.

S3-1. PRESET RESERVED (Initialization reserved)

Initialization of the back-up IC is reserved. (Actual initialization is executed when the power is turned on

next.) To reset to the original factory settings or to reset the backup IC, select this sub-menu and press

the “MAIN ZONE

” key to turn off the power.

62

CAUTION: Before setting to the PRESET RESERVED, write down the existing preset memory content of the tuner. (This

is because setting to the PRESET RESERVED will cause the user memory content to be erased.)

RX-V673/HTR-6065/RX-A720

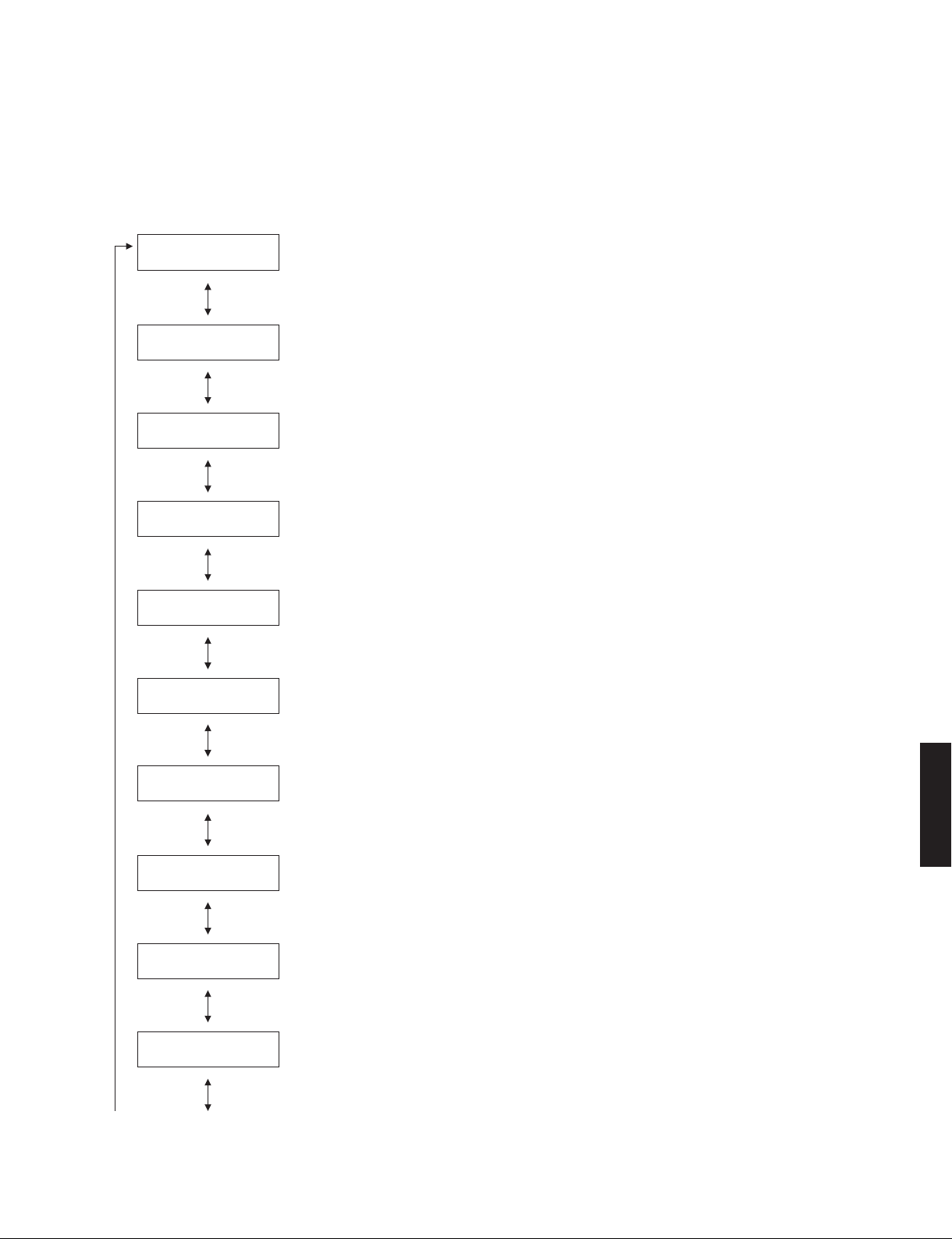

S4. ROM VERSION/CHECKSUM

The firmware version and checksum values are displayed.

The checksum is obtained by adding the data at every 8-bit and expressing the result as a hexadecimal notation.

* Numeric values in the figure are given as reference only.

S4-1

SYS-VER.1.10

S4-2

VER.00040

S4-3

SUM.F0EA

S4-4

FR-V.00029

S4-5

FR-S.D2A0

S4-6

S-VER.0041

S4-1. SYSTEM VERSION

The firmware version is displayed.

S4-2. MICROPROCESSOR VERSION

The firmware version of MICROPROCESSOR (IC83 on DIGITAL P.C.B.) is displayed.

S4-3. MICROPROCESSOR CHECKSUM

The checksum value of MICROPROCESSOR (IC83 on DIGITAL P.C.B.) is displayed.

S4-4. FLASH ROM VERSION

The firmware version of FLASH ROM (IC77 on DIGITAL P.C.B.) is displayed.

S4-5. FLASH ROM CHECKSUM

The checksum value of FLASH ROM (IC77 on DIGITAL P.C.B.) is displayed.

S4-6. NETWORK MICROPROCESSOR VERSION

The firmware version of Network microprocessor (IC951 on DIGITAL P.C.B.) is displayed.

S4-7

S-SUM.992245EF

S4-8

D1-V.1.06r3

S4-9

D1-S.47CD49C3

S4-10

INVALIDITEM

S4-7. NETWORK MICROPROCESSOR CHECKSUM

The checksum value of Network microprocessor (IC951 on DIGITAL P.C.B.) is displayed.

S4-8. DSP1 VERSION

The firmware version of DSP1 (IC921 on DIGITAL P.C.B.) is displayed.

S4-9. DSP1 CHECKSUM

The checksum value of DSP1 (IC921 on DIGITAL P.C.B.) is displayed.

S4-10. INVALID ITEM

Not for service.

RX-V673/HTR-6065/

RX-A720

63

RX-V673/HTR-6065/RX-A720

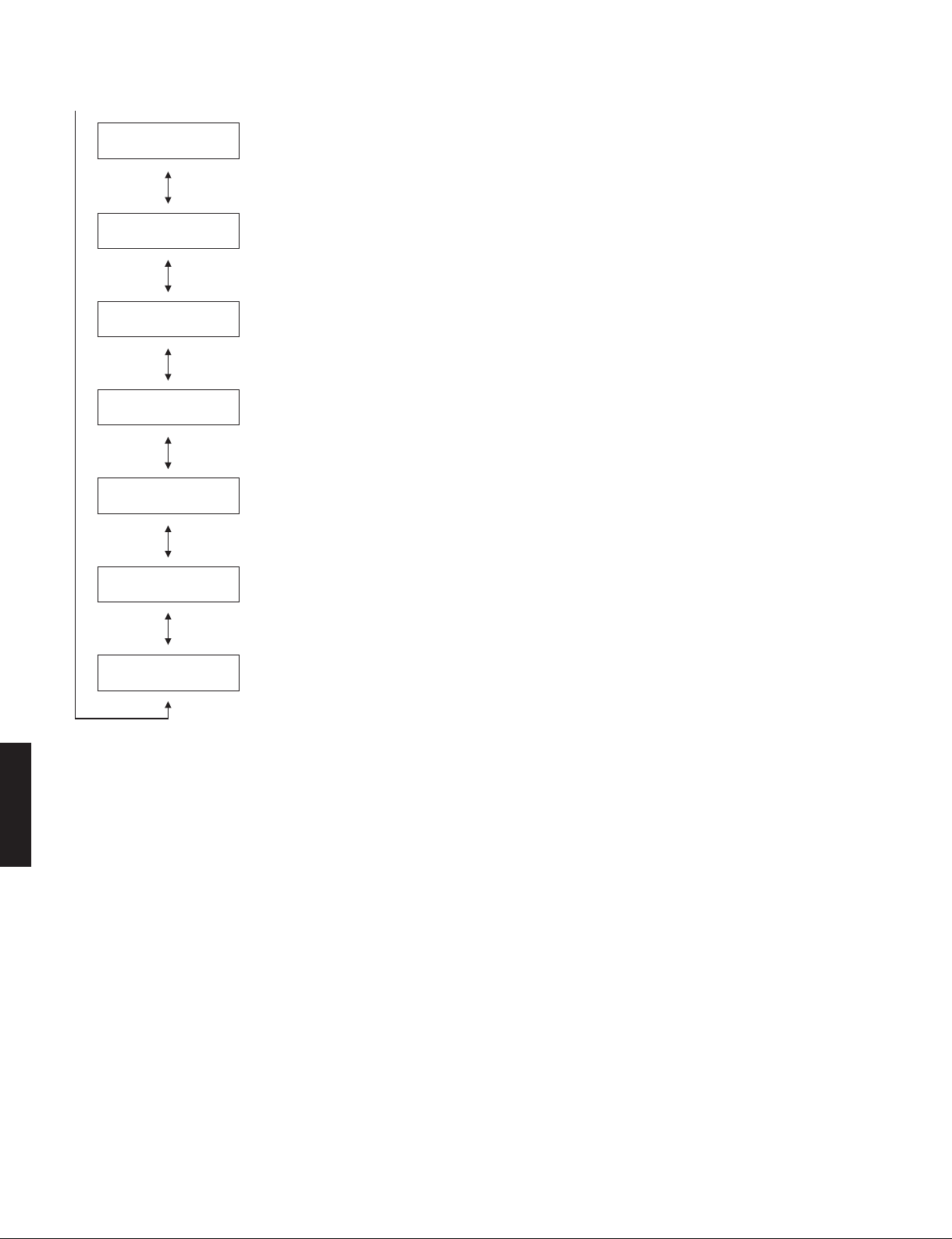

S4-11

INVALIDITEM

S4-12

G-V.000006136

S4-13

FPGA-G-V.18

S4-14

FPGA-S-V.12

S4-15

FPGA-H-V.6

S4-16

INVALIDITEM

S4-11. INVALID ITEM

Not for service.

S4-12. GUI VERSION

The firmware version of GUI data is displayed.

S4-13. FPGA GUI VERSION

The firmware version of GUI section in FPGA (IC50 on DIGITAL P.C.B.) is displayed.

S4-14. FPGA SD (Standard Definition) VERSION

The firmware version of SD I/P scaler section in FPGA (IC50 on DIGITAL P.C.B.) is displayed.

S4-15. FPGA HD (High Definition) VERSION

The firmware version of HD I/P scaler section in FPGA (IC50 on DIGITAL P.C.B.) is displayed.

S4-16. INVALID ITEM

Not for service.

S4-17

INVALIDITEM

RX-A720

RX-V673/HTR-6065/

S4-17. INVALID ITEM

Not for service.

64

RX-V673/HTR-6065/RX-A720

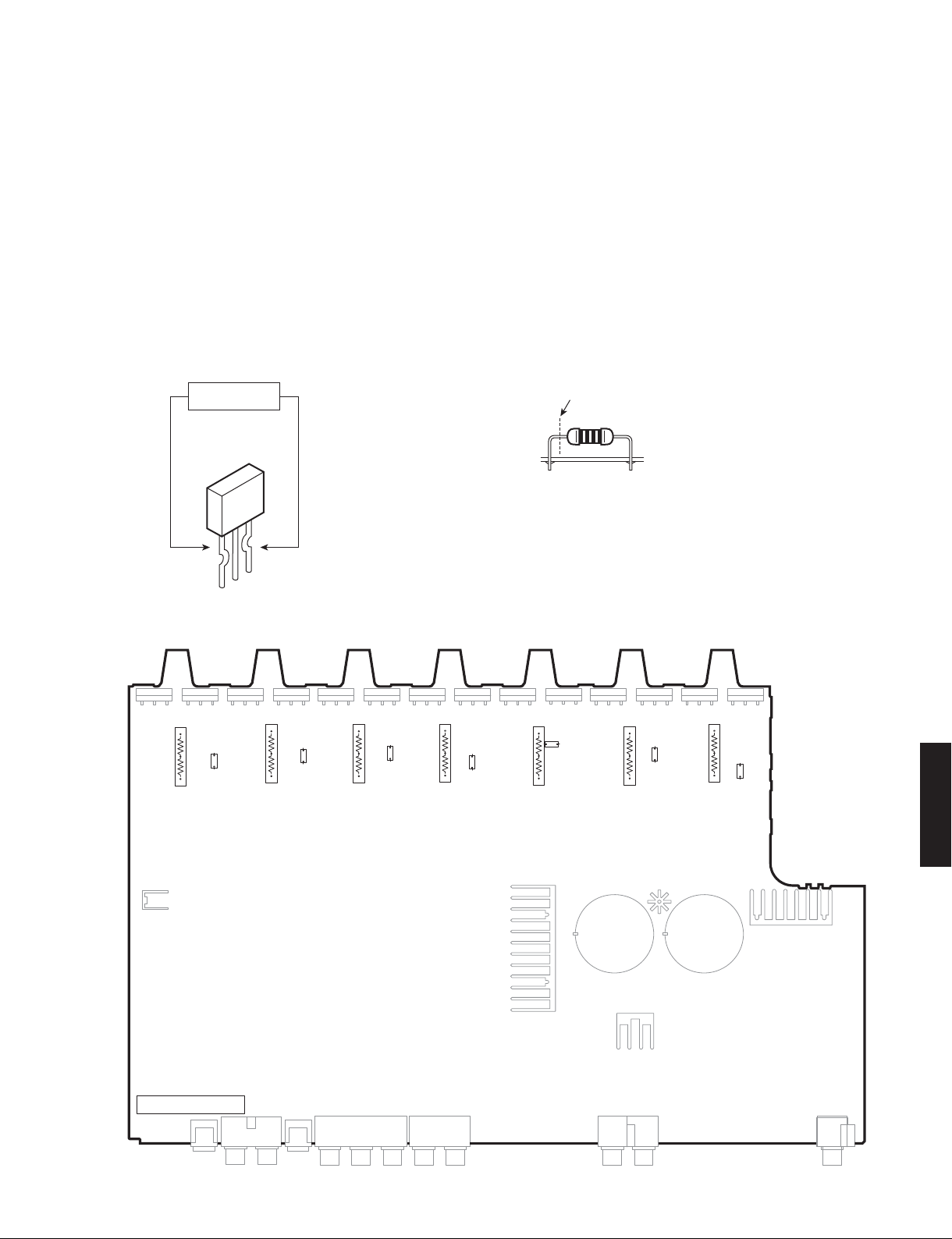

■ POWER AMPLIFIER ADJUSTMENT

1. Right after power is turned on, confirm that the voltage across the terminals of R1152 (SURROUND BACK Rch), R1154

(SURROUND Rch), R1150 (FRONT Rch), R1148 (CENTER), R1149 (FRONT Lch), R1153 (SURROUND Lch) and R1151

(SURROUND BACK Lch) are within the confines of 0.1 mV to 10 mV.

2. If measured voltage exceeds 10 mV, open (cut off) R1104 (SURROUND BACK Rch), R1106 (SURROUND Rch), R1102 (FRONT

Rch), R1100 (CENTER), R1101 (FRONT Lch), R1105 (SURROUND Lch) and R1103 (SURROUND BACK Lch), and then

reconfirm the voltage.

Attention

If the measured voltage exceeds 10 mV after repairing the power amplifier, check other parts again for any possible

defect before cutting the resistor.

3. Confirm that the voltage is within the confines of 0.2 mV to 15 mV after 60 minutes.

0.1 mV – 10 mV

R1154

R1106

(DC)

R1153 R1152

R1105

R1152 (SURROUND BACK Rch)

R1154 (SURROUND Rch)

R1150 (FRONT Rch)

R1148 (CENTER)

R1149 (FRONT Lch)

R1153 (SURROUND Lch)

R1151 (SURROUND BACK Lch)

Front side

R1151

R1104

R1103

Open (cut off)

R1150 R1149

R1102

R1104 (SURROUND BACK Rch)

R1106 (SURROUND Rch)

R1102 (FRONT Rch)

R1100 (CENTER)

R1101 (FRONT Lch)

R1105 (SURROUND Lch)

R1103 (SURROUND BACK Lch)

R1148

R1101

R1100

RX-V673/HTR-6065/

RX-A720

MAIN (1) P.C.B.

65

RX-V673/HTR-6065/RX-A720

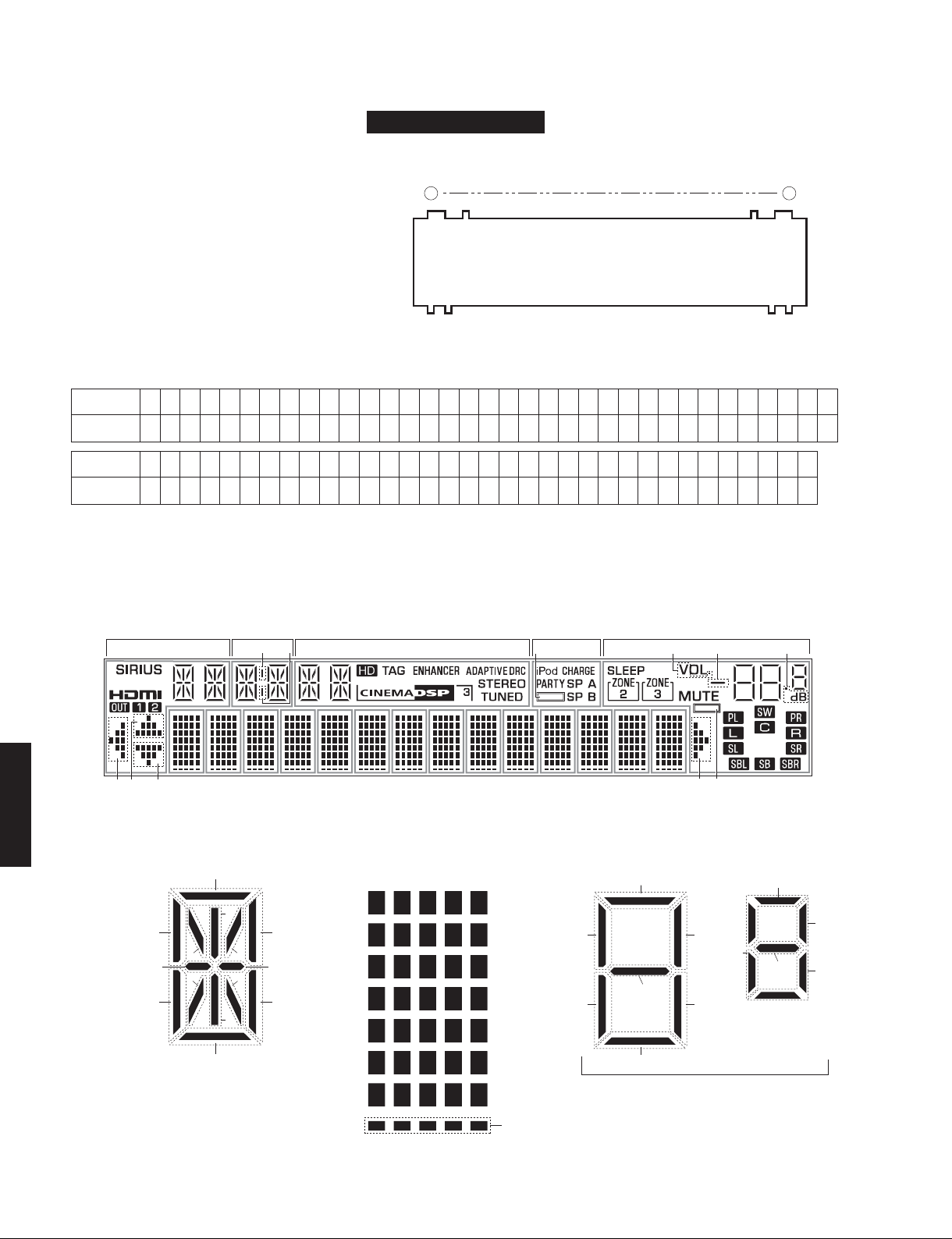

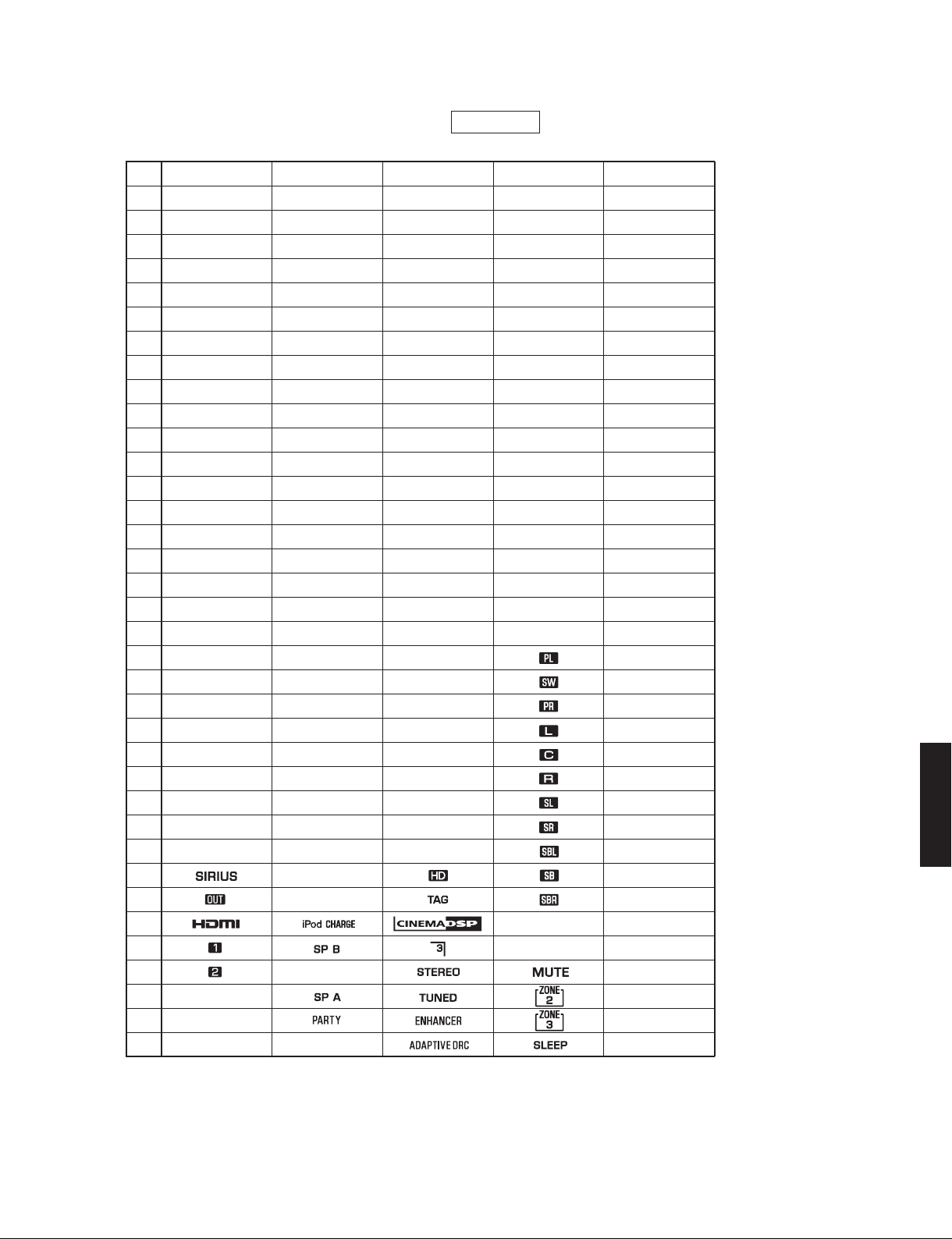

■ DISPLAY DATA

● V4001 : 18-MT-11GNK (OPERATION P.C.B.)

RX-V673/HTR-6065

69

PATTERN AREA

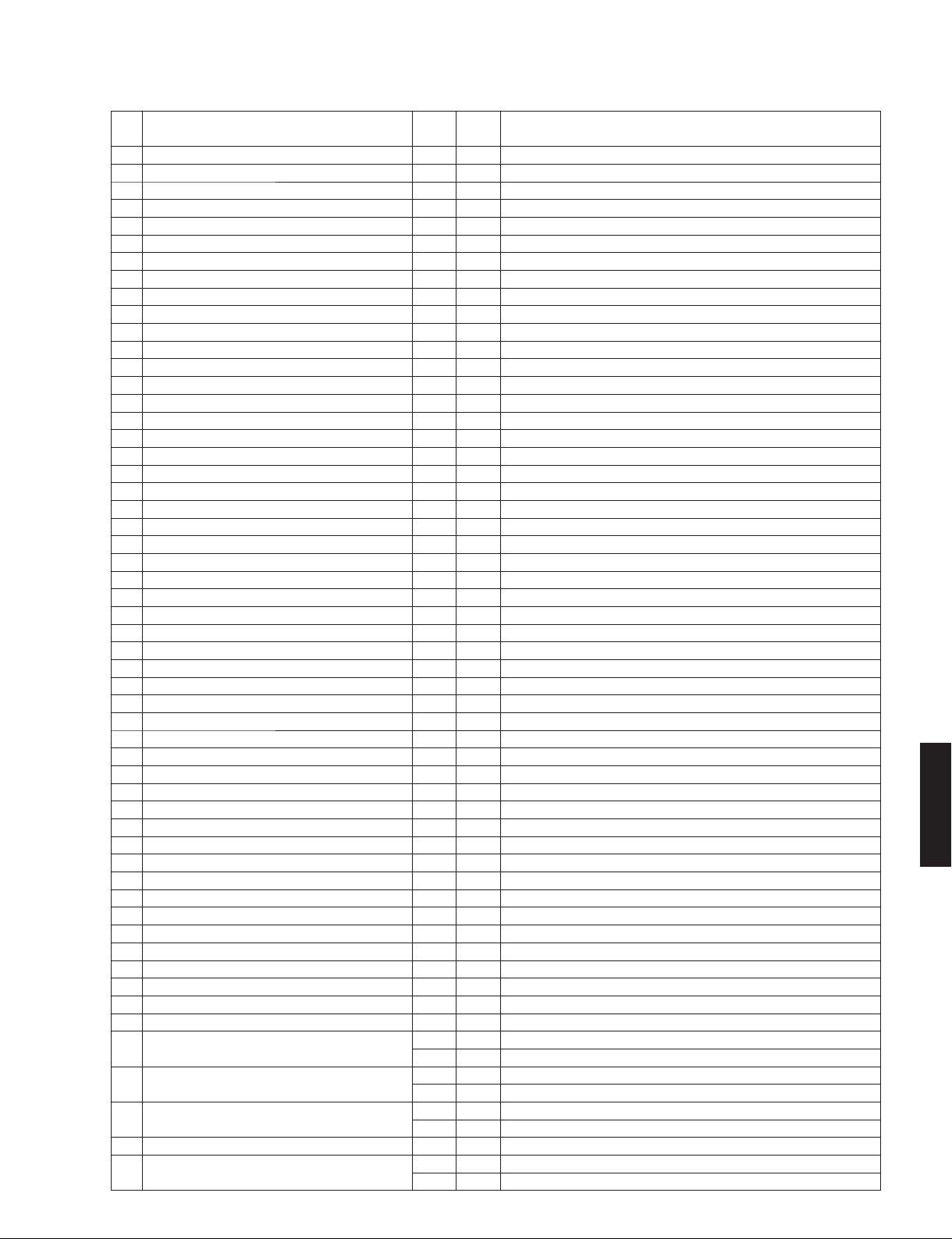

● PIN CONNECTION

Pin No.

Connection

Pin No.

Connection

Note : 1) F1, F2 ..... Filament pin 2) NP ..... No pin 3) NX ..... No extend pin 4) 1G-18G ..... Grid pin

● GRID ASSIGNMENT

69

68 67NP66NP65P164P263P362P461P560P659P758P857P956

F2NX

34

P3233P3332P3431P3530P36

18G

1a 1a1a2a 2a2a 2a1a

29 28

NXNX27NX26NX25NX24NX23NX2218G2117G2016G1915G1814G1713G1612G1511 G1410G139G128G117G106G95G84G73G62G51G4NP3NP

17G

S8 S9

P1055P1154P1253P1352P1451P1550P1649P1748P1847P1946P2045P2144P2243P2342P2441P2540P2639P2738P2837P29

16G

17G

1

36

P3035P31

21

F1NX

15G

S7 S5S15 S5

S12

RX-A720

RX-V673/HTR-6065/

66

S11

S10

f

gm

e

2G1G 3G 4G 5G 6G 7G 11G10G9G8G 12G 13G 14G

a

j

b

h

k

nr

c

p

d

(18G–16G)

1-1 2-1 3-1 4-1 5-1

1- 2

2-2

3-2

1- 3

2-3

3-3

1- 4

2-4

3-4

1- 5

2-5

3-5

1- 6

2-6

3-6

1- 7

2-7

3-7

4-2

4-3

4-4

4-5

4-6

4-7

5-2

5-3

5-4

5-5

5-6

5-7

(1G–14G)

S1

S13

S6

a

f

g

e

d

b

c

S2

S3

S3

S4

S2

(15G)

● ANODE CONNECTION

RX-V673/HTR-6065/RX-A720

RX-V673/HTR-6065

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

P21

P22

P23

P24

P25

P26

P27

P28

P29

P30

P31

P32

P33

P34

P35

P36

18G

1a

1h

1j

1k

1b

1f

1m

1g

1c

1e

1r

1p

1n

1d

2a

2h

2j

2k

2b

2f

2m

2g

2c

2e

2r

2p

2n

2d

S12

S10

S11

17G

1a

1h

1j

1k

1b

1f

1m

1g

1c

1e

1r

1p

1n

1d

2a

2h

2j

2k

2b

2f

2m

2g

2c

2e

2r

2p

2n

2d

S8

S9

S15

–

16G

1a

1h

1j

1k

1b

1f

1m

1g

1c

1e

1r

1p

1n

1d

2a

2h

2j

2k

2b

2f

2m

2g

2c

2e

2r

2p

2n

2d

15G

S5

S7

1d

2d

S2

1e

2e

S3

1c

2c

S4

1g

2g

1f

2f

1b

2b

1a

2a

S6

S13

1G–14G

1-1

2-1

3-1

4-1

5-1

1-2

2-2

3-2

4-2

5-2

1-3

2-3

3-3

4-3

5-3

1-4

2-4

3-4

4-4

5-4

1-5

2-5

3-5

4-5

5-5

1-6

2-6

3-6

4-6

5-6

1-7

2-7

3-7

4-7

5-7

S1

RX-V673/HTR-6065/

RX-A720

67

RX-V673/HTR-6065/RX-A720

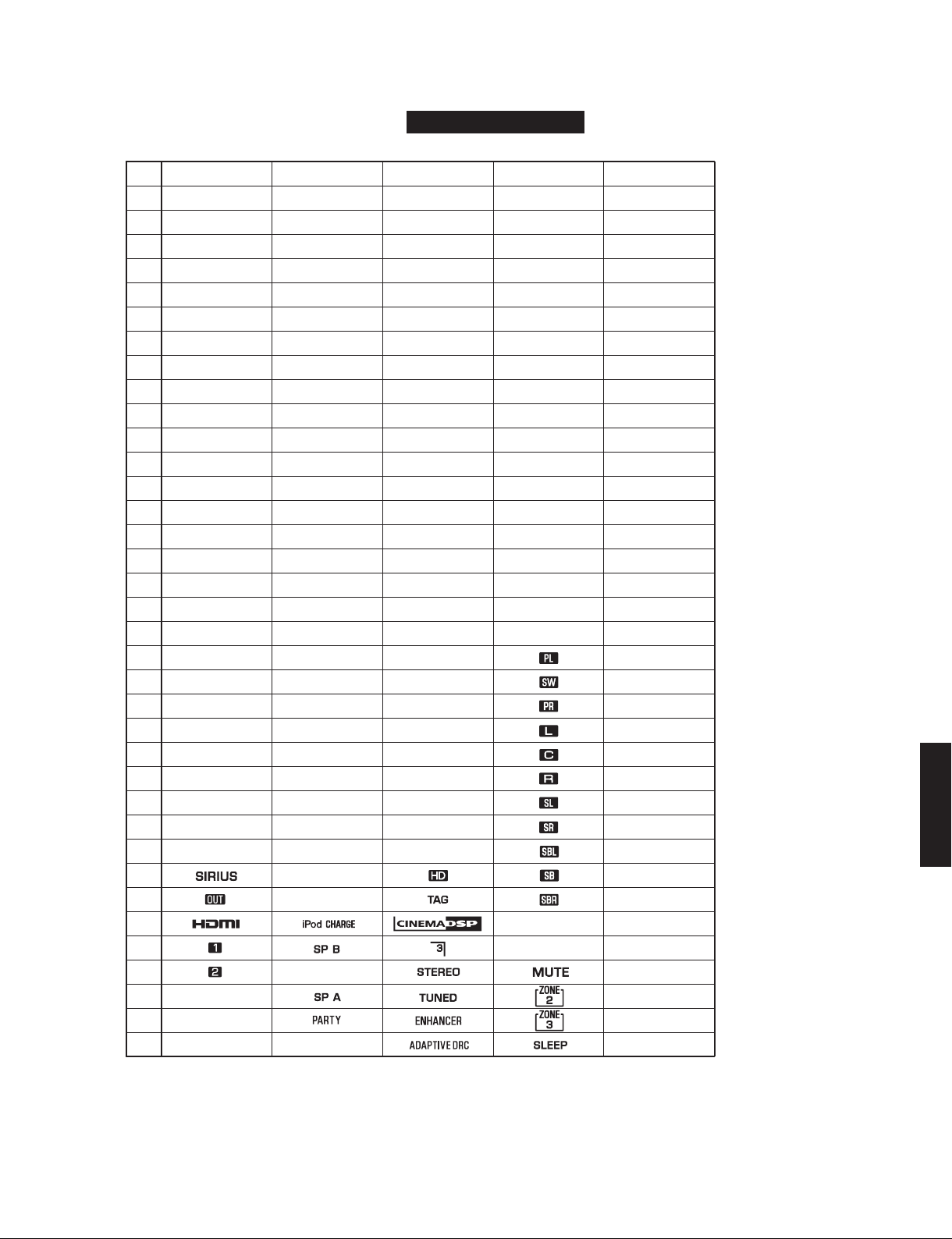

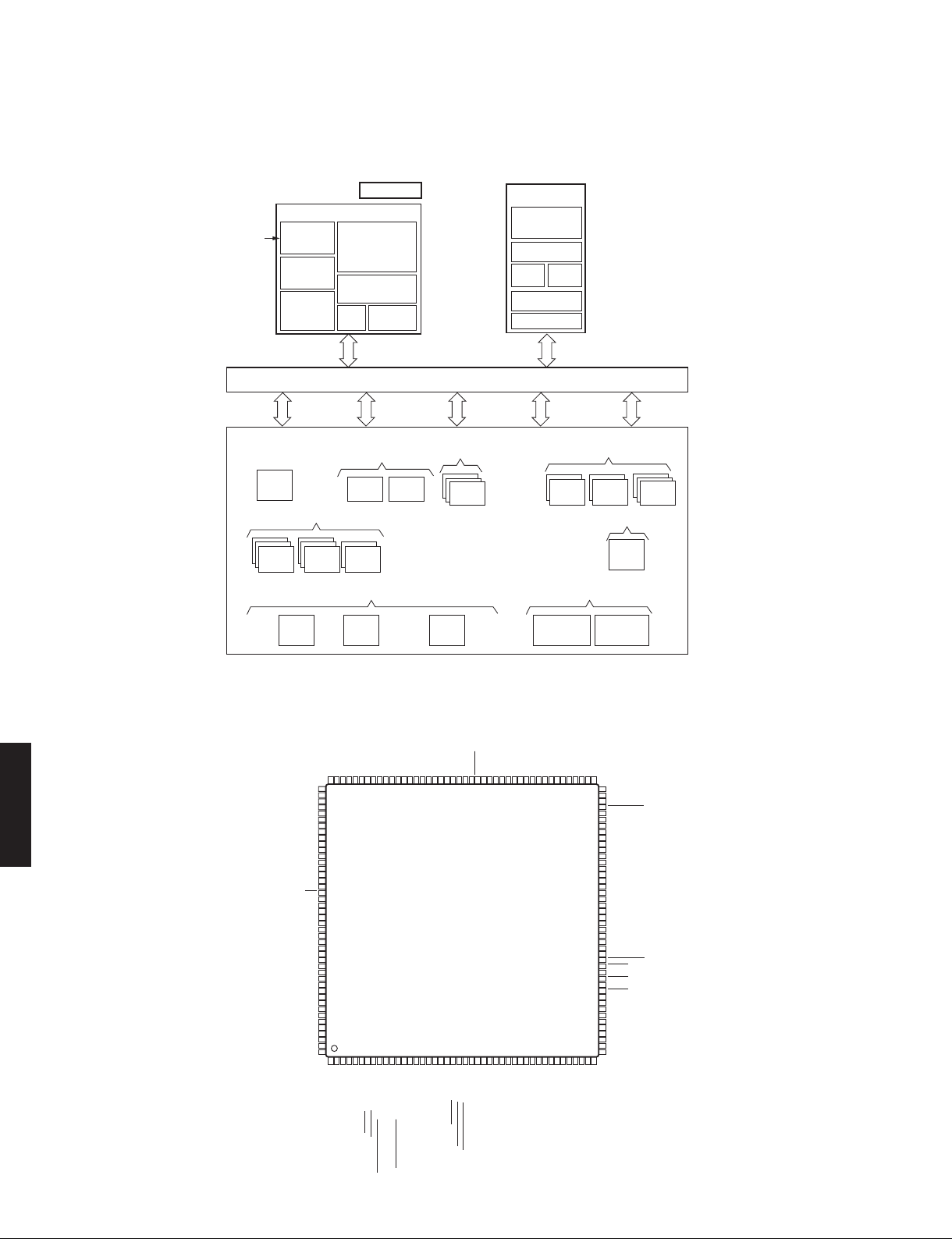

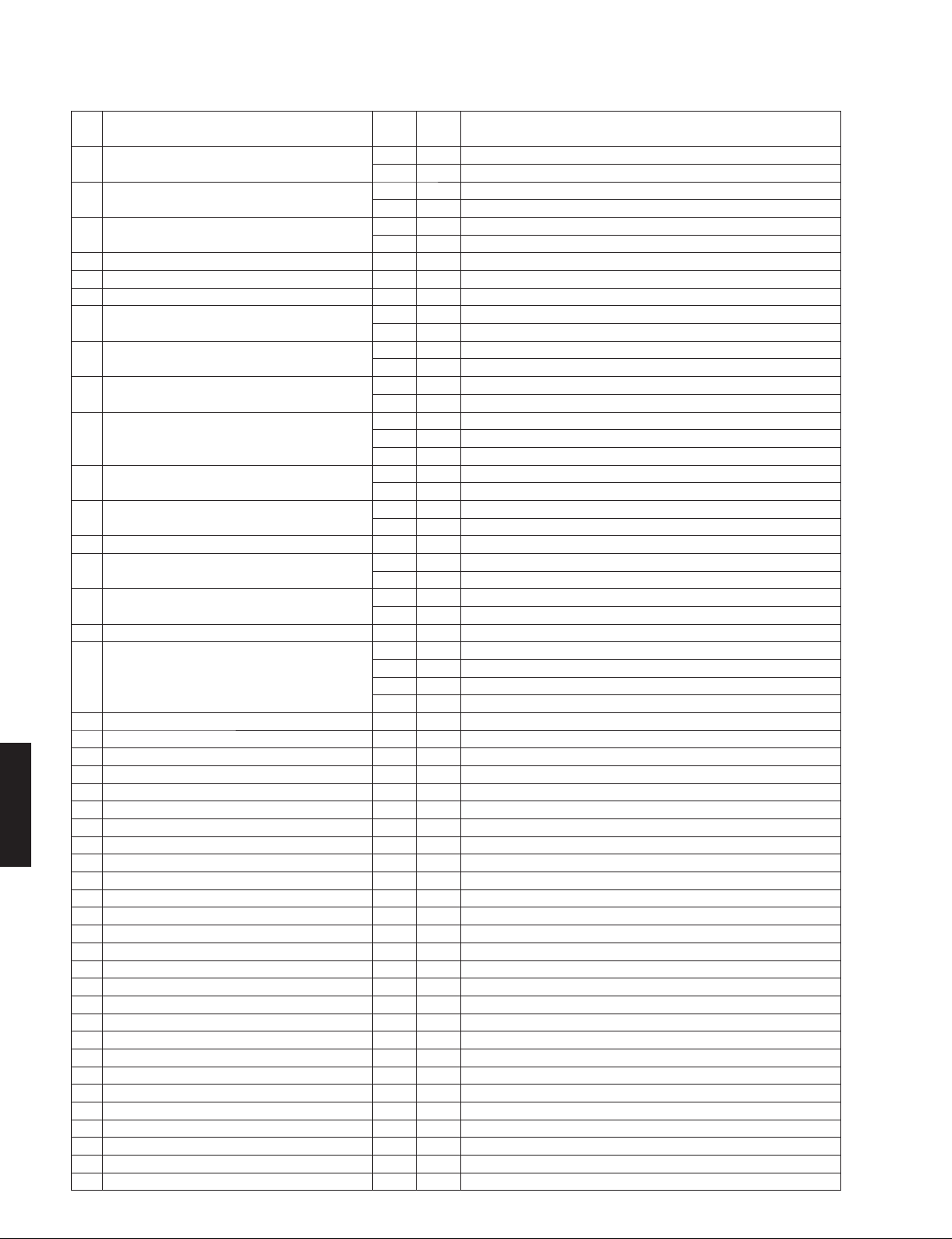

● V4001 : HNA-18MM03T (OPERATION P.C.B.)

RX-A720

69

PATTERN AREA

● PIN CONNECTION

Pin No.

Connection

Pin No.

Connection

Note : 1) F1, F2 ..... Filament pin 2) 1G–18G ..... Grid pin 3) P1–P36 ..... Anode pin 4) NP ..... No pin 5) NX ..... No extended pin

● GRID ASSIGNMENT

69

68 67NP66NP65P164P263P362P461P560P659P758P857P956

F2 F2

34

P3233P3332P3431P3530P36

18G

1a 1a1a2a 2a2a

29 28

NXNX27NX26NX25NX24NX23NX2218G2117G2016G1915G1814G1713G1612G1511 G1410G139G128G117G106G95G84G73G62G51G4NP3NP

17G

3a 3b

P1055P1154P1253P1352P1451P1550P1649P1748P1847P1946P2045P2144P2243P2342P2441P2540P2639P2738P2837P29

16G

17G

15G

1

36

P3035P31

21

F1F1

V1 S1S3 S1

A1

RX-A720

RX-V673/HTR-6065/

f

gm

e

68

A3

A2

a

j

h

p

d

(18G–16G)

2G1G 3G 4G 5G 6G 7G 11G10G9G8G 12G 13G 14G

1-1 2-1 3-1 4-1 5-1

1- 2

2-2

2-3

2-4

2-5

2-6

2-7

3-2

3-3

3-4

3-5

3-6

3-7

b

k

nr

c

1- 3

1- 4

1- 5

1- 6

1- 7

4-2

4-3

4-4

4-5

4-6

4-7

5-2

5-3

5-4

5-5

5-6

5-7

V2

V7V6V3

V8V1

V4

V5

U1

(1G–14G)

(15G)

V14

V13

V9

V15

V12

V10

V11

S2

A4

V18

V17

V17

V16

V18

● ANODE CONNECTION

RX-V673/HTR-6065/RX-A720

RX-A720

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

P21

P22

P23

P24

P25

P26

P27

P28

P29

P30

P31

P32

P33

P34

P35

P36

18G

1a

1h

1j

1k

1b

1f

1m

1g

1c

1e

1r

1p

1n

1d

2a

2h

2j

2k

2b

2f

2m

2g

2c

2e

2r

2p

2n

2d

A1

A2

A3

17G

1a

1h

1j

1k

1b

1f

1m

1g

1c

1e

1r

1p

1n

1d

2a

2h

2j

2k

2b

2f

2m

2g

2c

2e

2r

2p

2n

2d

3a

3b

S3

–

16G

1a

1h

1j

1k

1b

1f

1m

1g

1c

1e

1r

1p

1n

1d

2a

2h

2j

2k

2b

2f

2m

2g

2c

2e

2r

2p

2n

2d

15G

S1

V1

V5

V12

V18

V6

V13

V17

V4

V11

V16

V8

V15

V7

V14

V3

V10

V2

V9

A4

S2

1G–14G

1-1

2-1

3-1

4-1

5-1

1-2

2-2

3-2

4-2

5-2

1-3

2-3

3-3

4-3

5-3

1-4

2-4

3-4

4-4

5-4

1-5

2-5

3-5

4-5

5-5

1-6

2-6

3-6

4-6

5-6

1-7

2-7

3-7

4-7

5-7

U1

RX-V673/HTR-6065/

RX-A720

69

RX-V673/HTR-6065/RX-A720

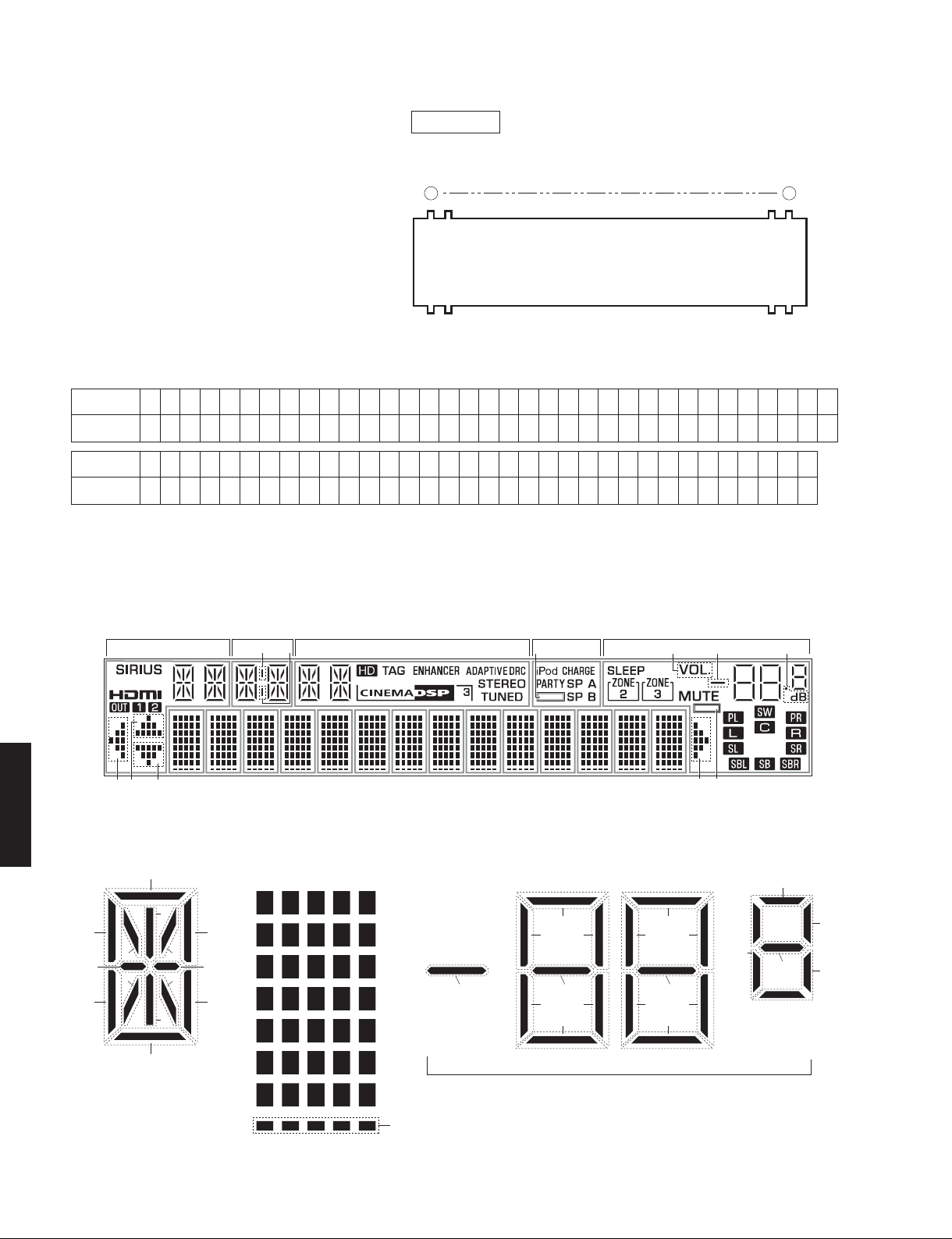

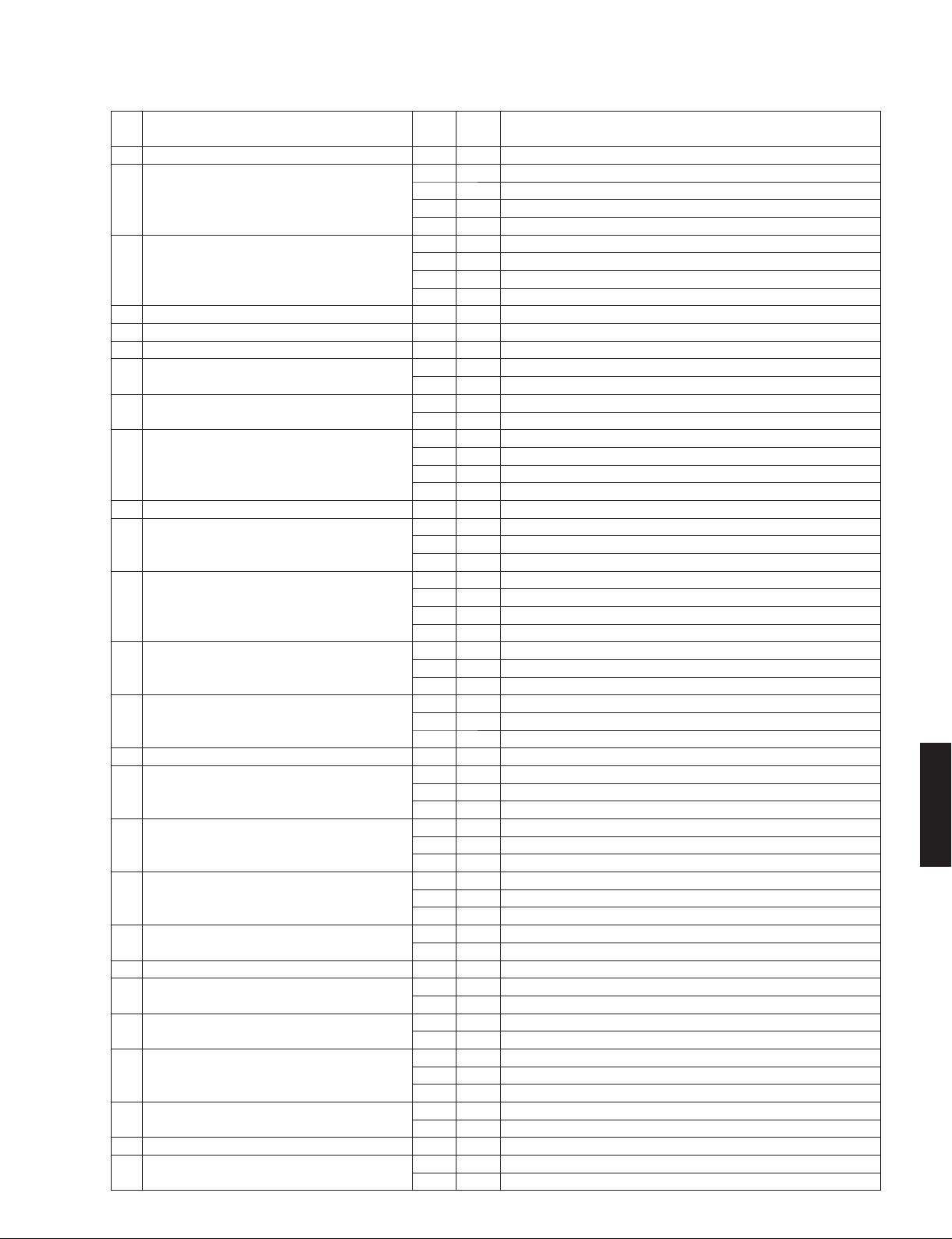

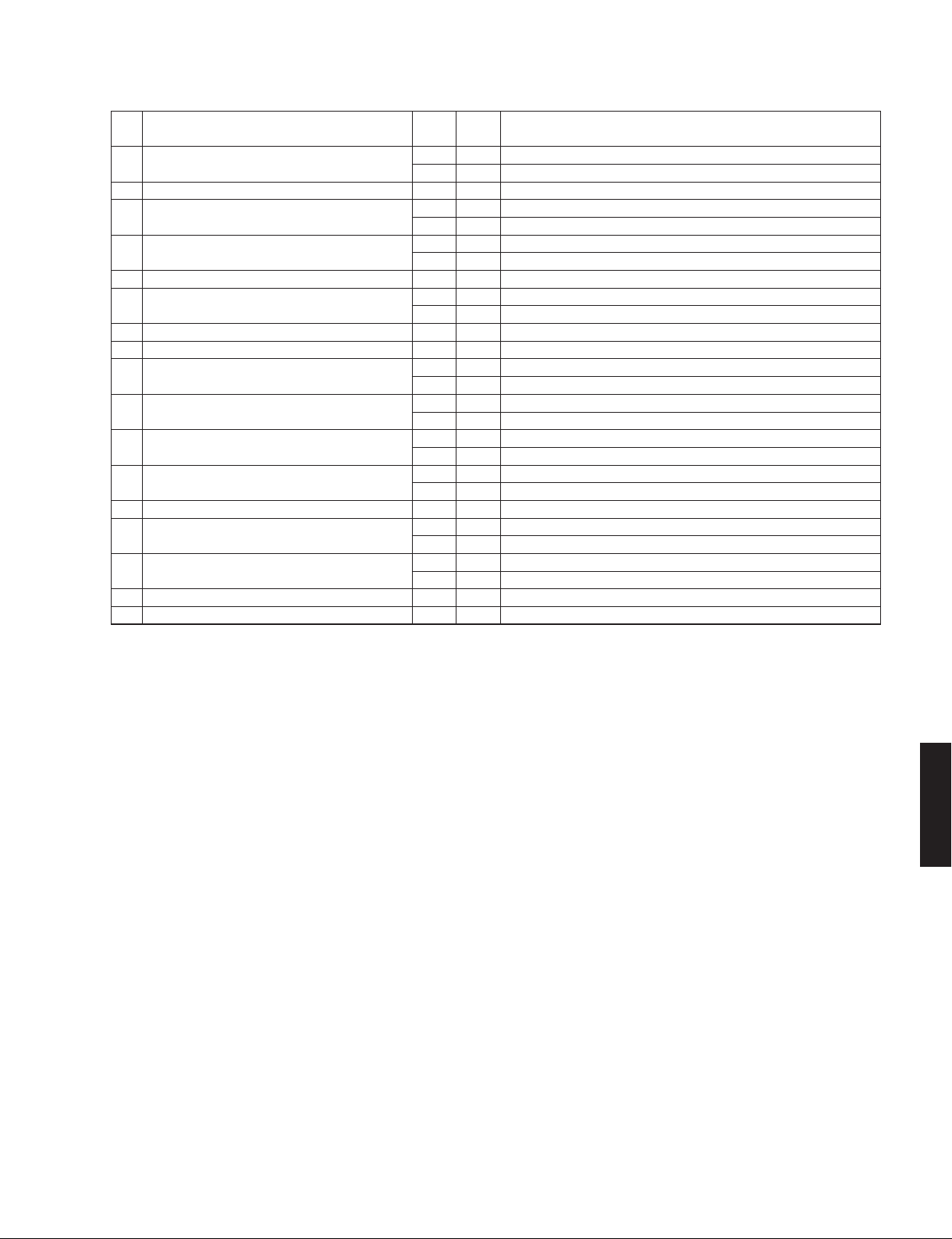

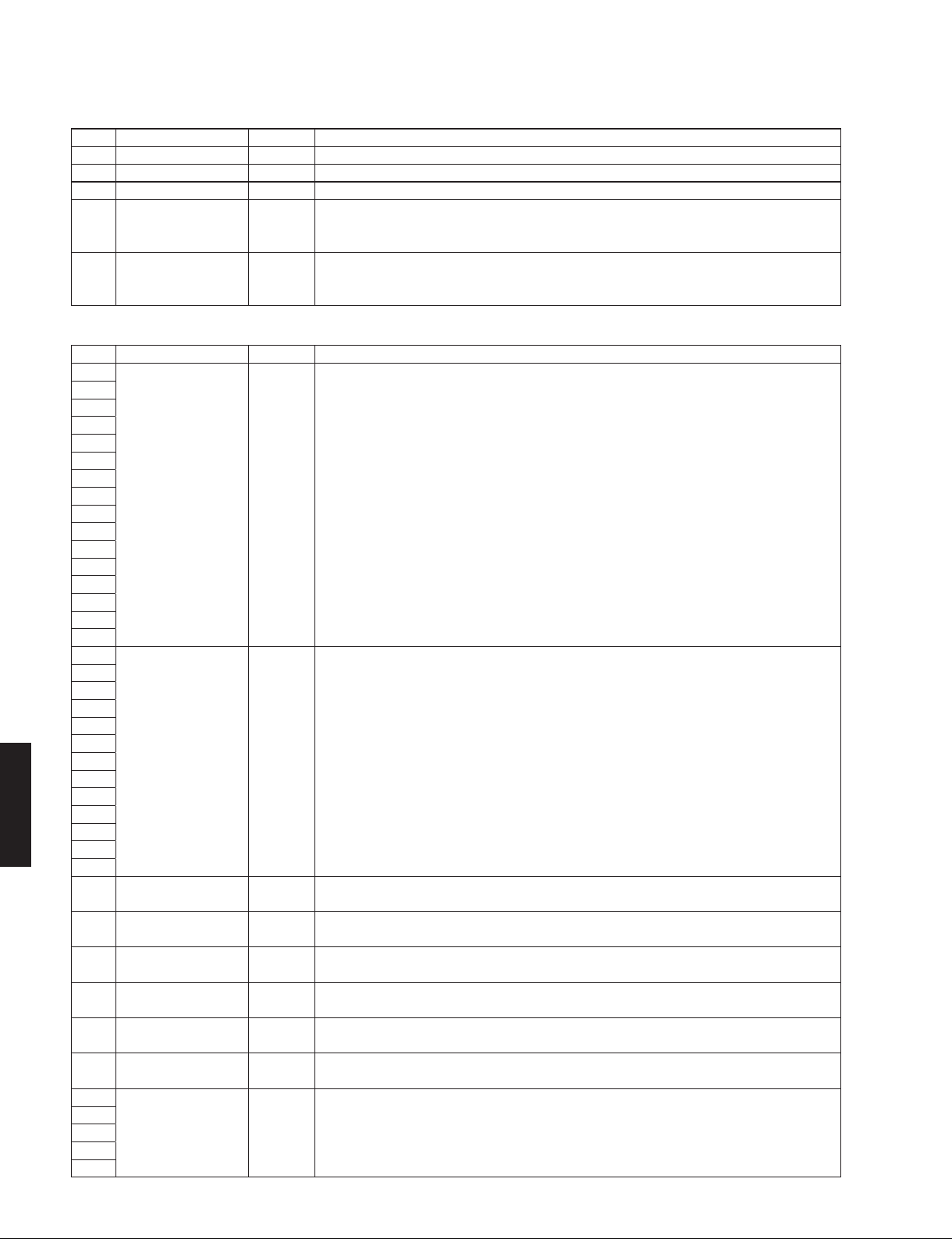

■ IC DATA

IC921: D80YK113CPTP400 (DIGITAL P.C.B.)

Digital signal processor

Input

Clock(s)

Peripherals

System Control

(Watchdog)

GPIO

eHRPWM

USB2.0

OTG Ctlr

PLL/Clock

Generator

w/OSC

GeneralPurpose

Timer

GeneralPurpose

Timer

Control Timers

eCAP

PHY

JTAG Interface

Memory Protection

I/O Protection

Power/Sleep

Controller

RTC/

OSC

Pin

Multiplexing

32-KHz

DMA

EDMA3

eQEP

Connectivity

HPI

Switched Control Resource (SCR)

Audio Ports

MMC/SD

(8b)

McASP

w/FIFO

dMAX

DSP Subsystem

TM

C674x

DSP MICRO-

PROCESSOR

AET

32 KB

32 KB

L1 Pgm

L1 RAM

256 KB L2 RAM

1024 KB L2 ROM

I2C SPI

External Memory Interface

EMIFA(8b/16b)

NAND/Flash

16b SDRAM

Serial Interface

Shared Memory

128 KB

RAM

EMIFB

SDRAM Only

(16b/32b)

UART

RX-A720

RX-V673/HTR-6065/

70

USB0_VDDA12

USB0_VDDA18

USB0_DP

USB0_DM

USB0_VDDA33

PLL0_VDDA

PLL0_VSSA

OSCIN

OSCVSS

OSCOUT

RESET

RTC_XI

RTC_CVDD

GP7[14]

AHCLKX1/EPWMQB/GP3[14]

ACLKX1/EPWMQA/GP3[15]

AFSX1/EPWMSYNCI/EPWMSYNC0/GP4[10]

ACLKR1/ECAP2/APWM2/GP4[12]

AFSR1/GP4[13]

AXR1[8]/EPWM1A/GP4[8]

AXR1[7]/EPWM1B/GP4[7]

AXR1[6]/EPWM2A/GP4[6]

AXR1[5]/EPWM2B/GP4[5]

AXR1[4]/EQEP1B/GP4[4]

AXR1[3]/EQEP1A/GP4[3]

AXR1[2]/GP4[2]

AXR1[1]/GP4[1]

ACLKX0/ECAP0/APWM0/GP2[12]

AFSX0/GP2[13]/BOOT[10]

AHCLKR0/GP2[14]/BOOT[11]

AFSR0/GP3[12]

ACLKR0/ECAP1/APWM1/GP2[15]

AMUTE1/EHRPWMTZ/GP4[14]

DVDD

128

127

126

132

131

130

129

RSV2

133

134

135

NC

136

137

138

NC

139

140

141

142

143

144

145

146

CVDD

147

148

149

TRST

150

DVDD

151

TMS

152

TDI

153

CVDD

154

TCK

155

TDO

156

157

158

DVDD

159

CVDD

160

161

CVDD

162

163

DVDD

164

165

166

CVDD

167

168

169

170

171

DVDD

172

173

174

175

176

123456789

DD

DV

AXR1[0]/GP4[0]

AXR1[10]/GP5[10]

AXR1[11]/GP5[11]

SPI1_ENA/UART2_RXD/GP5[12]

UART0_RXD/I2C0_SDA/TM64P0_IN12/GP5[8]/BOOT[8]

UART0_TXD/I2C0_SCL/TM64P0_OUT12/GP5[9]/BOOT[9]

AXR0[11]/AXR2[0]/GP3[11]

DVDD

CVDD

119

118

117

116

115

125

124

123

122

1011121314151617181920212223242526272829303132333435363738394041424344

DD

CV

SPI1_SCS[0]/UART2_TXD/GP5[13]

SPI0_CLK/EQEP1I/GP5[2]BOOT[2]

SPI0_SCS[0]/UART0_RTS/EQEP0B/GP5[4]/BOOT[4]

114

121

120

DVDD

EMA_WAIT[0]/UHPI_HRDY/GP2[10]

SPI1_CLK/EQEP1S/GP5[7]BOOT[7]

SPI0_SOMI[0]/EQEP0I/GP5[0]BOOT[0]

SPI0_SIMO[0]/EQEP0S/GP5[1]BOOT[1]

SPI1_SOMI[0]/I2C1/SCL/GP5[5]BOOT[5]

SPI1_SIMO[0]/I2C1/SDA/GP5[6]BOOT[6]

SPI0_ENA/UART0_CTS/EQEP0A/GP5[3]/BOOT[3]

EMB_BA[1]/GP7[0]

EMB_BA[0]/GP7[1]

EMB_CS[0]

EMB_RAS

DVDD

113

112

CVDD

EMA_CS[3]/AMUTE2/GP2[6]

CVDD

111

110

109

108

107

106

105

104

DVDD

CVDD

EMA_A[0]/GP1[0]

EMA_A[10]/GP1[10]

EMA_BA[0]/GP1[14]

EMA_BA[1]/UHPI_HHWIL/GP1[13]

EMA_OE/UHPI_HDS1/AXR0[13]/GP2[7]

EMA_CS[2]/UHPI_HCS/GP2[5]/BOOT[15]

EMB_A[2]/GP7[4]

EMB_A[1]/GP7[3]

EMB_A[0]/GP7[2]

DVDD

9998979695949392919089

103

102

101

100

DVDD

EMA_A[3]/GP1[3]

EMA_A[4]/GP1[4]

EMA_A[5]/GP1[5]

EMA_A[6]/GP1[6]

EMA_A[7]/GP1[7]

EMA_A[1]/MMCSD_CLK/UHPI/HCNTL0/GP1[1]

EMA_A[2]/MMCSD_CMD/UHPI/HCNTL1/GP1[2]

EMB_A[7]/GP7[9]

EMB_A[6]/GP7[8]

EMB_A[5]/GP7[7]

EMB_A[4]/GP7[6]

EMB_A[3]/GP7[5]

EMB_A[10]/GP7[12]

AXR0[0]/AFSR2/GP3[0]

AXR0[1]/ACLKX2/GP3[1]

AXR0[2]/AXR2[3]/GP3[2]

AXR0[3]/AXR2[2]/GP3[3]

AXR0[4]/AXR2[1]/GP3[4]

AXR0[5]/AFSX2/GP3[5]

AXR0[6]/ACLKR2/GP3[6]

AXR0[7]/GP3[7]

AXR0[8]/GP3[8]

UART1_RXD/AXR0[9]/GP3[9]

UART1_TXD/AXR0[10]/GP3[10]

AHCLKX0/AHCLKX2/USB_REFCLKIN/GP2[11]

EMB_A[12]/GP3[13]

EMB_A[11]/GP7[13]

EMB_A[9]/GP7[11]

EMB_A[8]/GP7[10]

DVDD

CVDD

88

EMB_SDCKE

87

DVDD

86

EMB_CLK

85

EMB_WE/DQM[1]/GP5[14]

84

EMB_D[8]/GP6[8]

83

EMB_D[9]/GP6[9]

82

EMB_D[10]/GP6[10]

81

DVDD

80

EMB_D[11]/GP6[11]

79

EMB_D[12]/GP6[12]

78

EMB_D[13]/GP6[13]

77

CVDD

76

EMB_D[14]/GP6[14]

75

DVDD

74

EMB_D[15]/GP6[15]

73

EMB_D[0]/GP6[0]

72

EMB_D[1]/GP6[1]

71

DVDD

70

EMB_D[2]/GP6[2]

69

CVDD

68

EMB_D[3]/GP6[3]

67

CVDD

66

EMB_D[4]/GP6[4]

65

DVDD

64

EMB_D[5]/GP6[5]

63

EMB_D[6]/GP6[6]

62

EMB_D[7]/GP6[7]

61

CVDD

60

EMB_WE_DQM[0]/GP5[15]

59

EMB_WE

58

DVDD

57

EMB_CAS

56

CVDD

55

EMA_WE]/UHPI_HRW/AXR0[12]/GP2[3]/BOOT[14]

54

EMA_D[7]/MMCSD_DAT[7]/UHPI_HD[7]/GP0[7]/BOOT[13]

53

DVDD

52

EMA_D[6]/MMCSD_DAT[6]/UHPI_HD[6]/GP0[6]

51

EMA_D[5]/MMCSD_DAT[5]/UHPI_HD[5]/GP0[5]

50

CVDD

49

EMA_D[4]/MMCSD_DAT[4]/UHPI_HD[4]/GP0[4]

48

EMA_D[3]/MMCSD_DAT[3]/UHPI_HD[3]/GP0[3]

47

DVDD

46

EMA_D[2]/MMCSD_DAT[2]/UHPI_HD[2]/GP0[2]

45

EMA_D[1]/MMCSD_DAT[1]/UHPI_HD[1]/GP0[1]

DVDD

CVDD

EMA_A[8]/GP1[8]

EMA_A[9]/GP1[9]

EMA_A[11]/GP1[11]

EMA_A[12]/GP1[12]

EMA_D[0]/MMCSD_DAT[0]/UHPI_HD[0]/GP0[0]/BOOT[12]

RX-V673/HTR-6065/RX-A720

Pin

No. (1) (2)

1 AXR1[0]/GP4[0] I/O IPD McASP1 serial data

2 UART0_RXD/I2C0_SDA/TM64P0_IN12/GP5[8]/ I IPU BOOT[8]

BOOT[8] I IPU UART0 receive data

3 UART0_TXD/I2C0_SCL/TM64P0_OUT12/GP5[9]/ I IPU BOOT[9]

BOOT[9] O IPU UART0 transmit data

4 AXR1[10]/GP5[10] I/O IPU McASP1 serial data

5 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

6 AXR1[11]/GP5[11] I/O IPU McASP1 serial data

7 SPI1_ENA /UART2_RXD/GP5[12] I/O IPU SPI1 enable

8 SPI1_SCS[0] /UART2_TXD/GP5[13] I/O IPU SPI1 chip select

9 SPI0_SCS[0] /UART0_RTS/EQEP0B/GP5[4]/BOOT[4] I/O IPU SPI0 chip select

10 CVDD (Core supply) PWR 1.2-V core supply voltage pins

11 SPI0_CLK/EQEP1I/GP5[2]/BOOT[2] I/O IPD SPI0 clock

12 SPI0_ENA /UART0_CTS/EQEP0A/GP5[3]/BOOT[3] I/O IPU SPI0 enable

13 SPI1_SOMI[0]/I2C1_SCL/GP5[5]/BOOT[5] I/O IPU SPI1 data/slave-out-master-in

14 SPI1_SIMO[0]/I2C1_SDA/GP5[6]/BOOT[6] I/O IPU SPI1 data/slave-in-master-out

15 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

16 SPI1_CLK/EQEP1S/GP5[7]/BOOT[7] I/O IPD SPI1 clock

17 SPI0_SOMI[0]/EQEP0I/GP5[0]/BOOT[0] I/O IPD SPI0 data/slave-out-master-in

18 SPI0_SIMO[0]/EQEP0S/GP5[1]/BOOT[1] I/O IPD SPI0 data/slave-in-master-out

19 EMA_WAIT[0]/ UHPI_HRDY/GP2[10] I IPU EMIFA wait input/interrupt

20 CVDD (Core supply) PWR 1.2-V core supply voltage pins

21 EMA_CS[3] /AMUTE2/GP2[6] O IPU EMIFA Async chip select

22 EMA_OE /UHPI_HDS1/AXR0[13]/GP2[7] O IPU EMIFA output enable

23 EMA_CS[2] /UHPI_HCS/GP2[5]/BOOT[15] O IPU EMIFA Async chip select

24 EMA_OE/UHPI_HDS1/AXR0[13]/GP2[7] I/O IPU McASP0 serial data

DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

25 EMA_BA[0]/ GP1[14] O IPU EMIFA bank address

26 EMA_BA[1]/ UHPI_HHWIL/GP1[13] O IPU EMIFA bank address

Function Name

TYPE PULL

I/O IPU I2C0 serial data

I IPU Timer0 lower input

I/O IPU I2C0 serial clock

O IPU Timer0 lower output

I IPU UART2 receive data

O IPU UART2 transmit data

I IPU eQEP0B quadrature input

I IPU BOOT[4]

O IPU UART0 ready-to-send output

I IPD eQEP1 index

I IPD BOOT[2]

I IPU eQEP0A quadrature input

I IPU BOOT[3]

I IPU UART0 clear-to-send input

I IPU BOOT[5]

I/O IPU I2C1 serial clock

I IPU BOOT[6]

I/O IPU I2C1 serial Data

I IPD eQEP1 strobe

I IPD BOOT[7]

I IPD eQEP0 index

I IPD BOOT[0]

I IPD eQEP0 strobe

I IPD BOOT[1]

I/O IPU UHPI ready

O IPU McASP2 mute output

I/O IPU UHPI data strobe

I IPU BOOT[15]

I/O IPU UHPI chip select

I/O IPU UHPI half-word identification control

Detail of Function

RX-V673/HTR-6065/

RX-A720

71

RX-V673/HTR-6065/RX-A720

Pin

No. (1) (2)

27 EMA_A[10]/ GP1[10] O IPU EMIFA address bus

28 CVDD (Core supply) PWR 1.2-V core supply voltage pins

29 EMA_A[0]/ GP1[0] O IPD EMIFA address bus

30 EMA_A[1]/MMCSD_CLK/UHPI_HCNTL0/GP1[1] O IPU EMIFA address bus

31 EMA_A[2]/MMCSD_CMD/UHPI_HCNTL1/GP1[2] O IPU EMIFA address bus

32 EMA_A[3]/ GP1[3] O IPD EMIFA address bus

33 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

34 EMA_A[4]/ GP1[4] O IPD EMIFA address bus

35 EMA_A[5]/ GP1[5] O IPD EMIFA address bus

36 EMA_A[6]/ GP1[6] O IPD EMIFA address bus

37 EMA_A[7]/ GP1[7] O IPD EMIFA address bus

38 CVDD (Core supply) PWR 1.2-V core supply voltage pins

39 EMA_A[8]/ GP1[8] O IPU EMIFA address bus

40 EMA_A[9]/ GP1[9] O IPU EMIFA address bus

41 EMA_A[11]/ GP1[11] O IPU EMIFA address bus

42 EMA_A[12]/ GP1[12] O IPU EMIFA address bus

43 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

44 EMA_D[0]/MMCSD_DAT[0]/UHPI_HD[0]/GP0[0]/ I/O IPU EMIFA data bus

BOOT[12] I IPU BOOT[12]

45 EMA_D[1]/MMCSD_DAT[1]/UHPI_HD[1]/GP0[1] I/O IPU EMIFA data bus

46 EMA_D[2]/MMCSD_DAT[2]/UHPI_HD[2]/GP0[2] I/O IPU EMIFA data bus

47 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

48 EMA_D[3]/MMCSD_DAT[3]/UHPI_HD[3]/GP0[3] I/O IPU EMIFA data bus

49 EMA_D[4]/MMCSD_DAT[4]/UHPI_HD[4]/GP0[4] I/O IPU EMIFA data bus

RX-A720

RX-V673/HTR-6065/

50 CVDD (Core supply) PWR 1.2-V core supply voltage pins

51 EMA_D[5]/MMCSD_DAT[5]/UHPI_HD[5]/GP0[5] I/O IPU EMIFA data bus

52 EMA_D[6]/MMCSD_DAT[6]/UHPI_HD[6]/GP0[6] I/O IPU EMIFA data bus

53 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

54 EMA_D[7]/MMCSD_DAT[7]/UHPI_HD[7]/GP0[7]/ I/O IPU EMIFA data bus

BOOT[13] I IPU BOOT[13]

55 EMA_WE /UHPI_HRW/AXR0[12]/GP2[3]/BOOT[14] O IPU EMIFA SDRAM write enable

56 CVDD (Core supply) PWR 1.2-V core supply voltage pins

57 EMB_CAS O IPU EMIFB column address strobe

58 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

59 EMB_WE O IPU EMIFB write enable

60 EMB_WE_DQM[0] /GP5[15] O IPU EMIFB write enable/data mask for EMB_D.

72

Function Name

TYPE PULL

I/O IPU UHPI access control

O IPU MMCSD_CLK

I/O IPU UHPI access control

I/O IPU MMCSD_CMD

I/O IPU UHPI data bus

I/O IPU MMC/SD data

I/O IPU UHPI data bus

I/O IPU MMC/SD data

I/O IPU UHPI data bus

I/O IPU MMC/SD data

I/O IPU UHPI data bus

I/O IPU MMC/SD data

I/O IPU UHPI data bus

I/O IPU MMC/SD data

I/O IPU UHPI data bus

I/O IPU MMC/SD data

I/O IPU UHPI data bus

I/O IPU MMC/SD data

I/O IPU UHPI data bus

I/O IPU MMC/SD data

I IPU BOOT[14]

I/O IPU UHPI read/write

I/O IPU McASP0 serial data

Detail of Function

RX-V673/HTR-6065/RX-A720

Pin

No. (1) (2)

61 CVDD (Core supply) PWR 1.2-V core supply voltage pins

62 EMB_D[7]/GP6[7] I/O IPD EMIFB SDRAM data bus

63 EMB_D[6]/GP6[6] I/O IPD EMIFB SDRAM data bus

64 EMB_D[5]/GP6[5] I/O IPD EMIFB SDRAM data bus

65 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

66 EMB_D[4]/GP6[4] I/O IPD EMIFB SDRAM data bus

67 CVDD (Core supply) PWR 1.2-V core supply voltage pins

68 EMB_D[3]/GP6[3] I/O IPD EMIFB SDRAM data bus

69 CVDD (Core supply) PWR 1.2-V core supply voltage pins

70 EMB_D[2]/GP6[2] I/O IPD EMIFB SDRAM data bus

71 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

72 EMB_D[1]/GP6[1] I/O IPD EMIFB SDRAM data bus

73 EMB_D[0]/GP6[0] I/O IPD EMIFB SDRAM data bus

74 EMB_D[15]/GP6[15] I/O IPD EMIFB SDRAM data bus

75 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

76 EMB_D[14]/GP6[14] I/O IPD EMIFB SDRAM data bus

77 CVDD (Core supply) PWR 1.2-V core supply voltage pins

78 EMB_D[13]/GP6[13] I/O IPD EMIFB SDRAM data bus

79 EMB_D[12]/GP6[12] I/O IPD EMIFB SDRAM data bus

80 EMB_D[11]/GP6[11] I/O IPD EMIFB SDRAM data bus

81 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

82 EMB_D[10]/GP6[10] I/O IPD EMIFB SDRAM data bus

83 EMB_D[9]/GP6[9] I/O IPD EMIFB SDRAM data bus

84 EMB_D[8]/GP6[8] I/O IPD EMIFB SDRAM data bus

85 EMB_WE_DQM[1] /GP5[14] O IPU EMIFB write enable/data mask for EMB_D

86 EMB_CLK O IPU EMIF SDRAM clock

87 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

88 EMB_SDCKE I/O IPU EMIFB SDRAM clock enable

89 EMB_A[12]/GP3[13] O IPD EMIFB SDRAM row/column address bus

90 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

91 EMB_A[11]/GP7[13] O IPD EMIFB SDRAM row/column address bus

92 EMB_A[9]/GP7[11] O IPD EMIFB SDRAM row/column address bus

93 CVDD (Core supply) PWR 1.2-V core supply voltage pins

94 EMB_A[8]/GP7[10] O IPD EMIFB SDRAM row/column address bus

95 EMB_A[7]/GP7[9] O IPD EMIFB SDRAM row/column address bus

96 EMB_A[6]/GP7[8] O IPD EMIFB SDRAM row/column address bus

97 EMB_A[5]/GP7[7] O IPD EMIFB SDRAM row/column address bus

98 EMB_A[4]/GP7[6] O IPD EMIFB SDRAM row/column address

99 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

100 EMB_A[3]/GP7[5] O IPD EMIFB SDRAM row/column address

101 EMB_A[2]/GP7[4] O IPD EMIFB SDRAM row/column address

102 EMB_A[1]/GP7[3] O IPD EMIFB SDRAM row/column address

103 EMB_A[0]/GP7[2] O IPD EMIFB SDRAM row/column address

104 CVDD (Core supply) PWR 1.2-V core supply voltage pins

105 EMB_A[10]/GP7[12] O IPD EMIFB SDRAM row/column address bus

106 EMB_BA[1]/GP7[0] O IPU EMIFB SDRAM bank address

107 EMB_BA[0]/GP7[1] O IPU EMIFB SDRAM bank address

108 EMB_CS[0] O IPU EMIFB SDRAM chip select 0

109 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

110 EMB_RAS O IPU EMIFB SDRAM row address strobe

111 AXR0[0]/AFSR2/GP3[0] I/O IPD McASP0 serial data

112 AXR0[1]/ACLKX2/GP3[1] I/O IPD McASP0 serial data

113 AXR0[2]/AXR2[3]/GP3[2] I/O IPD McASP0 serial data

114 CVDD (Core supply) PWR 1.2-V core supply voltage pins

115 AXR0[3]/AXR2[2]/GP3[3] I/O IPD McASP0 serial data

Function Name

TYPE PULL

O IPD McASP2 serial data

O IPD McASP2 transmit bit clock

O IPD McASP2 serial data

O IPD McASP2 serial data

Detail of Function

RX-V673/HTR-6065/

RX-A720

73

RX-V673/HTR-6065/RX-A720

Pin

No. (1) (2)

116 AXR0[4]/ AXR2[1]/GP3[4] I/O IPD McASP0 serial data

117 AXR0[5]/AFSX2/GP3[5] I/O IPD McASP0 serial data

118 AXR0[6]/ACLKR2/GP3[6] I/O IPD McASP0 serial data

119 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

120 AXR0[7]/GP3[7] I/O IPD McASP0 serial data

121 AXR0[8]/GP3[8] I/O IPU McASP0 serial data

122 UART1_RXD/AXR0[9]/GP3[9] I IPD UART1 receive data

123 UART1_TXD/AXR0[10]/GP3[10] O IPD UART1 transmit data

124 AXR0[11]/ AXR2[0]/GP3[11] I/O IPD McASP0 serial data

125 AHCLKX0/AHCLKX2/USB_REFCLKIN/GP2[11] I/O IPD McASP0 transmit master clock

126 ACLKX0/ECAP0/APWM0/GP2[12] I/O IPD Enhanced capture 0/input or auxiliary PWM 0 output

127 AFSX0/GP2[13]/BOOT[10] I IPD BOOT[10]

128 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

129 AHCLKR0/GP2[14]/BOOT[11] I IPD BOOT[11]

130 ACLKR0/ECAP1/APWM1/GP2[15] I/O IPD Enhanced capture 1/input or auxiliary PWM 1 output

131 AFSR0/GP3[12] I/O IPD McASP0 receive frame sync

132 AMUTE1/EPWMTZ/GP4[14] I/O IPD eHRPWM0 trip zone input

133 RSV2 PWR Reserved. For proper device operation, this pin must be tied directly to CVDD

134 USB0_VDDA12 (4) PWR USB0 PHY 1.2-V LDO output for bypass cap

135 USB0_VDDA18 PWR USB0 PHY 1.8-V supply input

136 N C – –

137 USB0_DP A USB0 PHY data plus

RX-A720

RX-V673/HTR-6065/

138 USB0_DM A USB0 PHY data minus

139 N C – –

140 USB0_VDDA33 PWR USB0 PHY 3.3-V supply

141 PLL0_VDDA PWR PLL analog VDD (1.2-V filtered supply)

142 PLL0_VSSA GND PLL analog VSS (for filter)

143 OSCIN I Oscillator input

144 OSCVSS GND Oscillator ground (for filter only)

145 OSCOUT O Oscillator output

146 RESET I Device reset input

147 CVDD (Core supply) PWR 1.2-V core supply voltage pins

148 RTC_XI I Low-frequency (32-kHz) oscillator receiver for real-time clock

149 RTC_CVDD PWR RTC module core power ( isolated from rest of chip CVDD)

150 TRST I IPD JTAG test reset

151 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

152 TMS I IPU JTAG test mode select

153 TDI I IPU JTAG test data input

154 CVDD (Core supply) PWR 1.2-V core supply voltage pins

155 TCK I IPU JTAG test clock

156 TDO O IPD JTAG test data output

157 GP7[14] (5) I/O IPD General-Purpose IO signal

158 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

159 CVDD (Core supply) PWR 1.2-V core supply voltage pins

74

Function Name

TYPE PULL

O IPD McASP2 serial data

O IPD McASP2 transmit frame sync

I/O IPD McASP2 receive bit clock

(3) I/O IPD McASP0 serial data

(3) I/O IPD McASP0 serial data

O IPD McASP2 serial data

O IPD McASP2 transmit master clock

I IPD USB_REFCLKIN. Optional 48 MHz clock input

I/O IPD McASP0 transmit bit clock

I/O IPD McASP0 transmit frame sync

I/O IPD McASP0 receive master clock

I/O IPD McASP0 receive bit clock

I/O IPD eHRPWM1 trip zone input

I/O IPD eHRPWM2 trip zone input

O IPD McASP1 mute output

Detail of Function

RX-V673/HTR-6065/RX-A720

Pin

No. (1) (2)

160 AHCLKX1/EPWM0B/GP3[14] I/O IPD eHRPWM0 B output

161 CVDD (Core supply) PWR 1.2-V core supply voltage pins

162 ACLKX1/EPWM0A/GP3[15] I/O IPD eHRPWM0 A output

163 AFSX1/EPWMSYNCI/EPWMSYNCO/GP4[10] I/O IPD Sync input to eHRPWM0 module or sync output to external PWM

164 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

165 ACLKR1/ECAP2/APWM2/GP4[12] I/O IPD enhanced capture 2/input or auxiliary PWM 2 output

166 AFSR1/GP4[13] I/O IPD McASP1 receive frame sync

167 CVDD (Core supply) PWR 1.2-V core supply voltage pins

168 AXR1[8]/EPWM1A/GP4[8] I/O IPD eHRPWM1 A (with high-resolution)

169 AXR1[7]/EPWM1B/GP4[7] I/O IPD eHRPWM1 B

170 AXR1[6]/EPWM2A/GP4[6] I/O IPD eHRPWM2 A (with high-resolution)

171 AXR1[5]/EPWM2B/GP4[5] I/O IPD eHRPWM2 B

172 DVDD (I/O supply) PWR 3.3-V I/O supply voltage pins

173 AXR1[4]/EQEP1B/GP4[4] I IPD eQEP1B quadrature input

174 AXR1[3]/EQEP1A/GP4[3] I IPD eQEP1A quadrature input

175 AXR1[2]/GP4[2] I/O IPD McASP1 serial data

176 AXR1[1]/GP4[1] I/O IPD McASP1 serial data

Function Name

TYPE PULL

I/O IPD McASP1 transmit master clock

I/O IPD McASP1transmit bit clock

I/O IPD McASP1 transmit frame sync

I/O IPD McASP1 receive bit clock

I/O IPD McASP1 serial data

I/O IPD McASP1 serial data

I/O IPD McASP1 serial data

I/O IPD McASP1 serial data

I/O IPD McASP1 serial data

I/O IPD McASP1 serial data

Detail of Function

(1) I = Input, O = Output, I/O = Bidirectional, Z = High impedance, PWR = Supply voltage, GND = Ground, A = Analog signal.

Note: The pin type shown refers to the input, output or high-impedance state of the pin function when configured as the the signal name highlighted

in bold. All multiplexed signals may enter a high-impedance state when the configured function is input-only or the configured function supports

high-Z operation. All GPIO signals can be used as input or output. For multiplexed pins where functions have different types (ie., input versus

output), the table reflects the pin function direction for that particular peripheral.

(2) IPD = Internal Pulldown resistor, IPU = Internal Pullup resistor

(3) 122, 123 pin: As these signals are internally pulled down while the device is in reset, it is necessary to externally pull them high with resistors if UART1

boot mode is used.

(4) 134 pin: Core power supply LDO output for USB PHY. This pin must be connected via a 0.22-mF capacitor to VSS. When the USB peripheral is not

used, the USB_VDDA12 signal should still be connected via a 1-mF capacitor to VSS.

(5) 157 pin: GP7[14] is initially configured as a reserved function after reset and will not be in a predictable state. This signal will only be stable after

the GPIO configuration for this pin has been completed. Users should carefully consider the system implications of this pin being in an

unknown state after reset.

RX-V673/HTR-6065/

RX-A720

75

RX-V673/HTR-6065/RX-A720

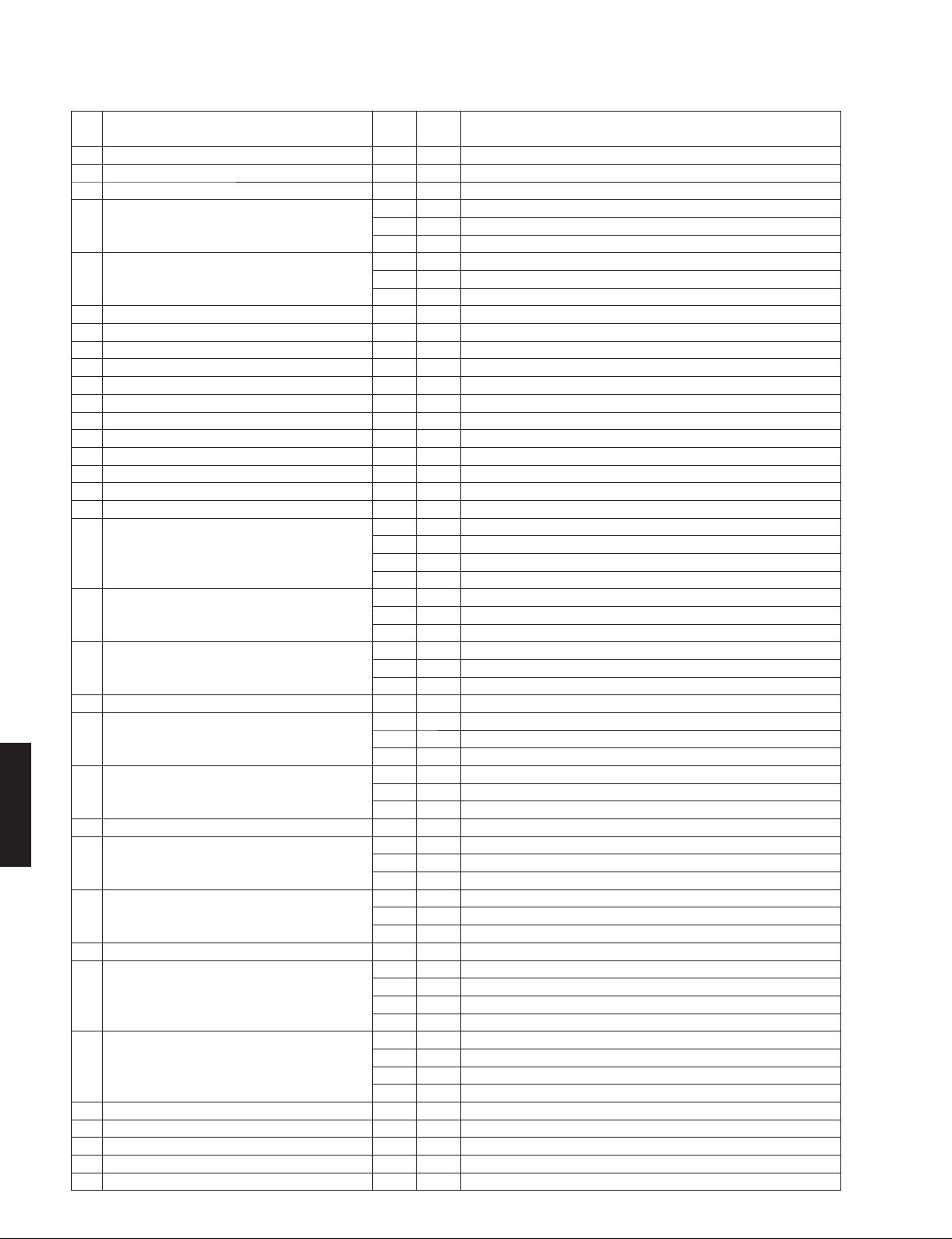

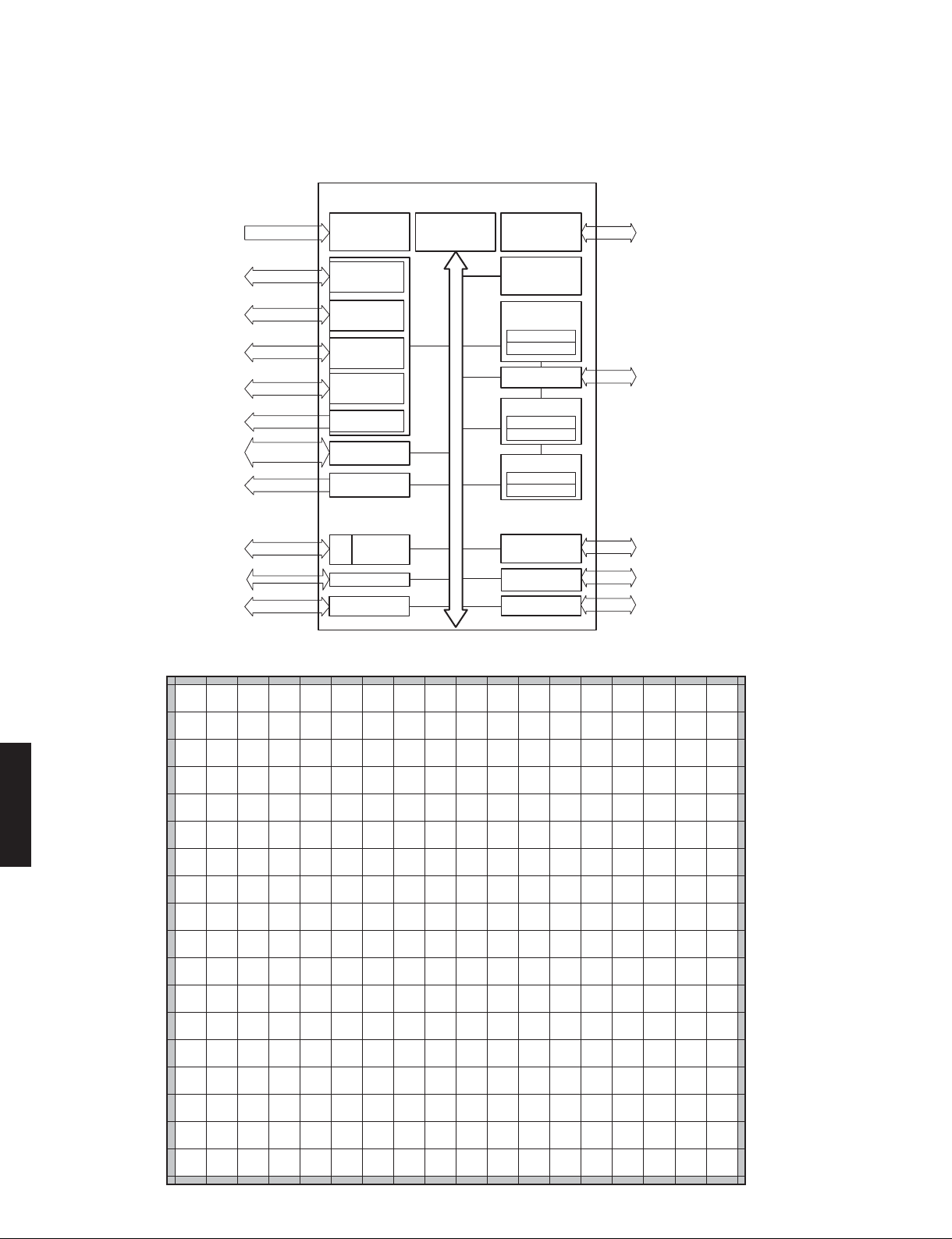

IC951: DM860A (DIGITAL P.C.B.)

Network microprocessor

* No replacement part available.

RESET, BOOT_SEL

4xAudio, 1xVideo

4xAudio

2xAudio

2xAudio

Audio

Memory Bus,

System Extension

LCD

USB

UART

SPI

Security Engine

Reset, Boot, OTP

AV0 Port

2

S, I8S, DSD, video

I

AV2 Port

2

I

S, I8S, DSD

AV3 Port

2

I

S, I8S, DSD,

SPDIF

AV4 Port

2

I

S, I8S, DSD,

SPDIF, ADAT

stereo

PWM-DAC

SD/SRAM and System

Extension Controller

LCD Controller

USB 2.0

USB

OTG

8 kByte RAM

PHY

2 x UART-1

SPI

General Purpose

on-chip RAM

slave

slave

slave

slave

slave

slave

64 kBytes

S

Y

S

T

E

M

B

U

S

master

slave

master

slave

master

slave

master

slave

master

slave

slave

Timing Engine

2 PLLs, 3 DCOs

DMA

2 Forwarding Units

64 Contexts

ARM 926EJ-S

240 MHz

I-cache 16 kByte

D-cache 16 kByte

Interrupt Controller

Watchdog, 2 Timer

RTSP Processor

160 MHz

I-cache 16 kByte

TCM 48 kByte

Audio Engine

160 MHz

I-cache 4 kByte

TCM 10 kByte

Ethernet MAC

10/100 Mbps

NAND FLASH

SSM Controller

CLOCKS

GPIO

(R/SSS)MII

NAND

SSM

RX-A720

RX-V673/HTR-6065/

76

123456789101112131415161718

USBDN

A

USBDP

B

VSS12

C SSMD2

USB

VDD12

D

USB

VSS33

E

RTC

VDD33

F

RTC

VDD12

G

DCO

VSS12

H

DCO

J

PDOUT1

PDOUT0

K

L

AV0CLK

AV0

M D4VSSVSS VSSVSS VSSVSS

CTRL0

AV0

N D8VSSVSS VSSVSS VSSVSS

DATA2

AV1

P

DATA2

AV2CLK

R

AV2

T

CTRL0

AV2

U

DATA0

V NC

123456789101112131415

VDD33

USBC

VDD33

USBT

USBREXT

USBVBUS

USBID

RTCXIN

RTCXOUT

VSS12

PLL

VCO1

VCO0

AOUTLN

AV0

CTRL1

AV0

DATA1

AV1

DATA1

AV2

CTRL1

AV2

DATA1

AV3

CTRL0

AV4

DATA0

VSS33

USBC

VSS33

USBT

USBXO

USBXI

NRES33

USBATST

USBVB

USDRV

VDD33

PLL

VSS33

PLL

VDD12

PLL

XTALO

AOUTLP

XTALI

AOUTRP

AOUTRN

AV0

DATA3

CTRL2

AV0

DATA3

DATA0

AV1

DATA0

DATA3

AV2

AV3CL

DATA2

AV3

CTRL1

DATA0

AV4

LCDD16 LCDD13 LCDD9

DATA1

LCDD17

LCDD15 LCDD12 LCDD8

AV3

OUT

AV0

AV1

AV2

TDO

TDI

HIGHZ

n.c.

VSS RFCLKN SSMD1 SSMD5 TXD1n.c. n.c. RFRXINRFRXQN

NRES12

VSS

OUT

NRES33

NRES12

REF

REF

NC

NC

NC

NC

VDD12

CORE

VDD33IO

VSS

VDD33IO

VDD12

CORE

VDD12

CORE

VSS

VDD33IO

VSS VSS

VDD33IO

VDD12

VSS

CORE

VDD12

VSS

CORE

VDD33IO VDD33IO VDD33IO VDD33IO

AV3

K

LCDD11

DATA1

n.c.

RREF

VDD33

VDD12

CORE

VSSVSS

VSS

VSSVSS

VSSVSS

VSS

VSS

VSS

LCDD7 FD3

LCDD6LCDD14 LCDD10

LCDD5

LCDD4

n.c.

VDD12

SSMWP

VDD33IO VDD33IO

VSSVSS VSSVSS VSSVSS

VSSVSS VSSVSS VSSVSS

VDD12

VDD12

CORE

CORE

LCD

LCDD3

CTRL0

LCD

LCDD2

CTRL1

LCD

LCDD1

CTRL2

LCD

LCDD0

CTRL3

SSMD0 SSMD4 SSMCMDn.c. VDD33 RFCLKP RFRXIPRFRXQP

SSMCLK

SSMCP

VDD12

CORE

VSS A22

VSS

VPP MIITXEN MIITXC LK MIIRXER MIICRS FD2

MIITXD0

SSMD6 TCK

SSMD3

SSMD7

VDD12

CORE

VDD12

CORE

MIITXD2

MIIRXD0

VSSNC

TXD0

NRESET

VDD33IOVDD33IO

VSSVSS

VSSVSS

VDD12

CORE

MIIRXD2

RXD1

RXD0 A2TEST1

SPIDI

VDD12

CORE

VDD12

CORE

VDD33IO

VDD33IO

VDD12

CORE

VDD12

CORE

VDD33IO

VDD33IO

MII

RXDV

MIIMDIO

TMS

SPINCS0

SPIDO A7

A9

A13_RAS A14_CAS

A17_DQ M0A18_DQ

A21

NCS0 NCS1

MEMCLK NWE

D3 D2

D7 D6

D11 D10

FD0 FD1

FD5

NFCE0

MIIPHY

CLK

A0

SPICLK

SPINCS1

A3

A4A1A5

A6 A8

A10

A11 A12

A15_BA0 A16_BA1

A19

M1

A23

NCS2

NOE

D1

D5

D9

D13

FD4

FD7

FD6LCDCLK MIIRXCLK MIICOLMIIITXER

FCLE

NFWE

NFWP

NFREMIITXD1 MIIRXD1 MIIRXD3MIITXD3 FALEMIIMDC

16 17 18

A

B

C

D

E

F

A20

G

NCS3VSSVSS VSS

H

MEMCKEVSSVSS VSSVSS VSS

J

NWAITVSSVSS VSS

K

D0VSSVSS VSSVSS VSSVSS

L

M

N

D12

P

D14

R

D15

T

NFRB

U

V

AV-P or t 0

Pin No. Function Name I/O Detail of Function

M4

N1

N2 Several formats are supported.

N3

N4 Video data, together with AV0DATA[3:0]:

P1

P2 AV1DATA[3:0] = video[7:4]

P3

L1 AV0CLK I/O

M1 AV0CTRL0 I/O • Serial audio formats: LRCK input or output.

M2 AV0CTRL1 I/O • Serial audio formats: Master clock output.

M3 AV0CTRL2 I/O

AV-P or t 2

Pin No. Function Name I/O Detail of Function

P4

R3

T2 Several formats are supported.

U1

R1 AV2CLK I/O

T1 AV2CTRL0 I/O

R2 AV2CTRL1 I/O

AV-P or t 3

Pin No. Function Name I/O Detail of Function

R5

T4 Several formats are supported.

R4 AV3CLK I/O

U2 AV3CTRL0 I/O

T3 AV3CTRL1 I/O

AV-P or t 4

Pin No. Function Name I/O Detail of Function

U3

V2 Several formats are supported.

PWM-DAC

Pin No. Function Name I/O Detail of Function

K4 AOUTLP O Left channel PWM output (positive).

L2 AOUTLN O Left channel PWM output (negative).

L4 AOUTRP O Right channel PWM output (positive).

L3 AOUTRN O Right channel PWM output (negative).

UART Interface

Pin No. Function Name I/O Detail of Function

B14 RXD0 I UART-0 receive signal.

C13 TXD0 O UART-0 transmit signal.

A14 RXD1 I UART-1 receive signal.

B13 TXD1 O UART-1 transmit signal.

AV0DATA[3:0] I/O

AV1DATA[3:0] I/O

AV2DATA[3:0] I/O

AV3DATA[1:0] I/O

AV4DATA[1:0] I/O

Audio/video data.

AV0DATA[3:0] = video[3:0]

Data clock. Depending on the AV-Port 0 configuration, this clock is a bit- or byte-clock which is used to

transmit or receive the AV0DATA[*] synchronously.

Configurable sync signal:

• Video formats: PSYNC input or output.

Configurable sync signal:

• Video formats: DVALID input or output.

Configurable sync signal:

• Video formats: FSYNC input or output.

Audio data.

Data clock. Depending on the AV-Port 2 configuration this clock is a bit-clock which is used to transmit or

receive the AV2DATA[*] synchronously.

Configurable sync signal:

Serial audio formats: LRCK input or output.

Configurable sync signal:

Serial audio formats: Master clock output.

Audio data.

Data clock. Depending on the AV-Port 3 configuration this clock is a bit-clock which is used to transmit or

receive the AV3DATA[*] synchronously.

Configurable sync signal:

Serial audio formats: LRCK input or output.

Configurable sync signal:

Serial audio formats: Master clock output.

Audio data.

RX-V673/HTR-6065/RX-A720

RX-V673/HTR-6065/

RX-A720

77

RX-V673/HTR-6065/RX-A720

Serial Peripheral Interface (SPI)

Pin No. Function Name I/O Detail of Function

D14 SPIDIN I SPI data receive.

D15 SPIDOUT O SPI data transmit.

B16 SPICLK I/O SPI clock.

C15 SPINCS0 I/O Master only mode: Chip-select 1 output.

B17 SPINCS1 I/O Master only mode: Chip-select 2 output.

External Memory Interface

Pin No. Function Name I/O Detail of Function

T18

R18

P17

P18

N15

N16

N17

N18

M15

M16

M17

M18

L15

L16

L17

L18

E18

E17

E16

E15

D18

D17

D16 A[12:0] O Address bus for external memory and peripheral access.

C18

C17

RX-A720

RX-V673/HTR-6065/

C16

B18

A18

A17

F15 A13_RAS O

F16 A14_CAS O

F17 A15_BA0 O

F18 A16_BA1 O

G15 A17_DQM0 O

G16 A18_DQM1 O

H17

H16

H15 A[23:19] O Address bus for external memory and peripheral access.

G18

G17

Multi-master mode: Chip-select input (used to detect bus conflict).

Slave mode: Chip-select input.

Multi-master mode: Chip-select 2 output.

Slave mode: Not used.

D[15:0] I/O Data bus for external memory and peripheral access.

SRAM: Address output

SDRAM: Row access strobe

SRAM: Address output

SDRAM: Column access strobe

SRAM: Address output

SDRAM: Bank select

SRAM: Address output

SDRAM: Bank select

SRAM: Address output

SDRAM: Data mask

SRAM: Address output

SDRAM: Data mask

78

Loading...

Loading...