Page 1

XAUI v12.3

LogiCORE IP Product Guide

Vivado Design Suite

PG053 April 6, 2016

Page 2

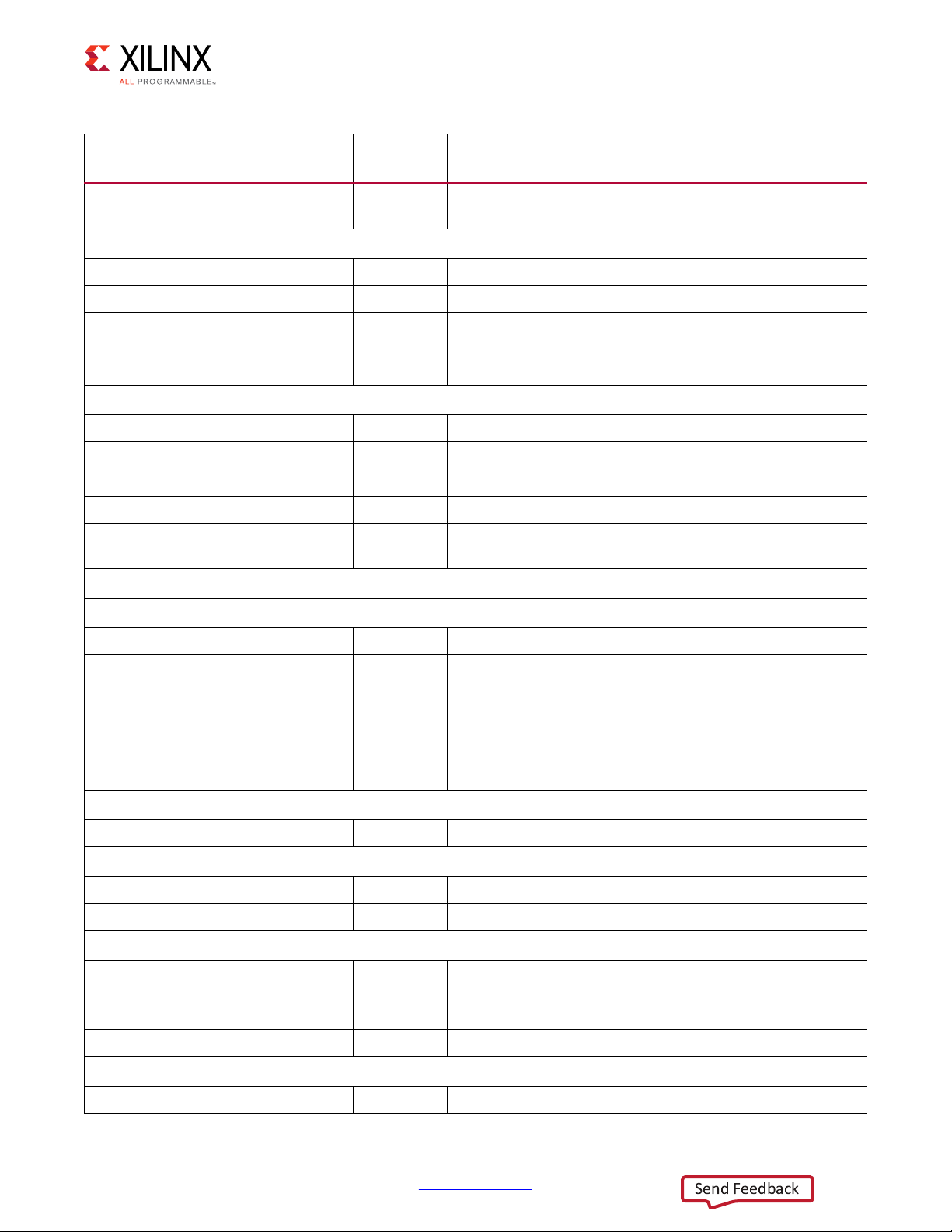

IP Facts

Send Feedback

Chapter 1: Overview

Additional Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

About the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Recommended Design Experience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Licensing and Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Feedback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Chapter 2: Product Specification

Standards Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Chapter 3: Designing with the Core

Use the Example Design as a Starting Point. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Know the Degree of Difficulty. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Keep It Registered . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Recognize Timing Critical Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Use Supported Design Flows. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Make Only Allowed Modifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Chapter 4: Core Architecture

System Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Chapter 5: Interfacing to the Core

Data Interface: Internal XGMII Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Interfacing to the Transmit Client Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Interfacing to the Receive Client Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Configuration and Status Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

MDIO Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Configuration and Status Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Debug Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

XAUI v12.3 Product Guide www.xilinx.com 2

PG053 April 6, 2016

Page 3

Chapter 6: Design Considerations

Send Feedback

Shared Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Clocking: UltraScale Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Clocking: Zynq-7000, Virtex-7, Artix-7, and Kintex-7 Devices. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Multiple Core Instances. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Reset Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Receiver Termination: Virtex-7 and Kintex-7 FPGAs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Transmit Skew . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Chapter 7: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Output Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Chapter 8: Detailed Example Design

Chapter 9: Test Bench

Appendix A: Verification and Interoperability

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Hardware Testing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Appendix B: Migrating and Upgrading

Device Migration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Appendix C: Debugging Designs

Finding Help on xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Simulation Specific Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Appendix D: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Additional Core Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

XAUI v12.3 Product Guide www.xilinx.com 3

PG053 April 6, 2016

Page 4

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Send Feedback

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

XAUI v12.3 Product Guide www.xilinx.com 4

PG053 April 6, 2016

Page 5

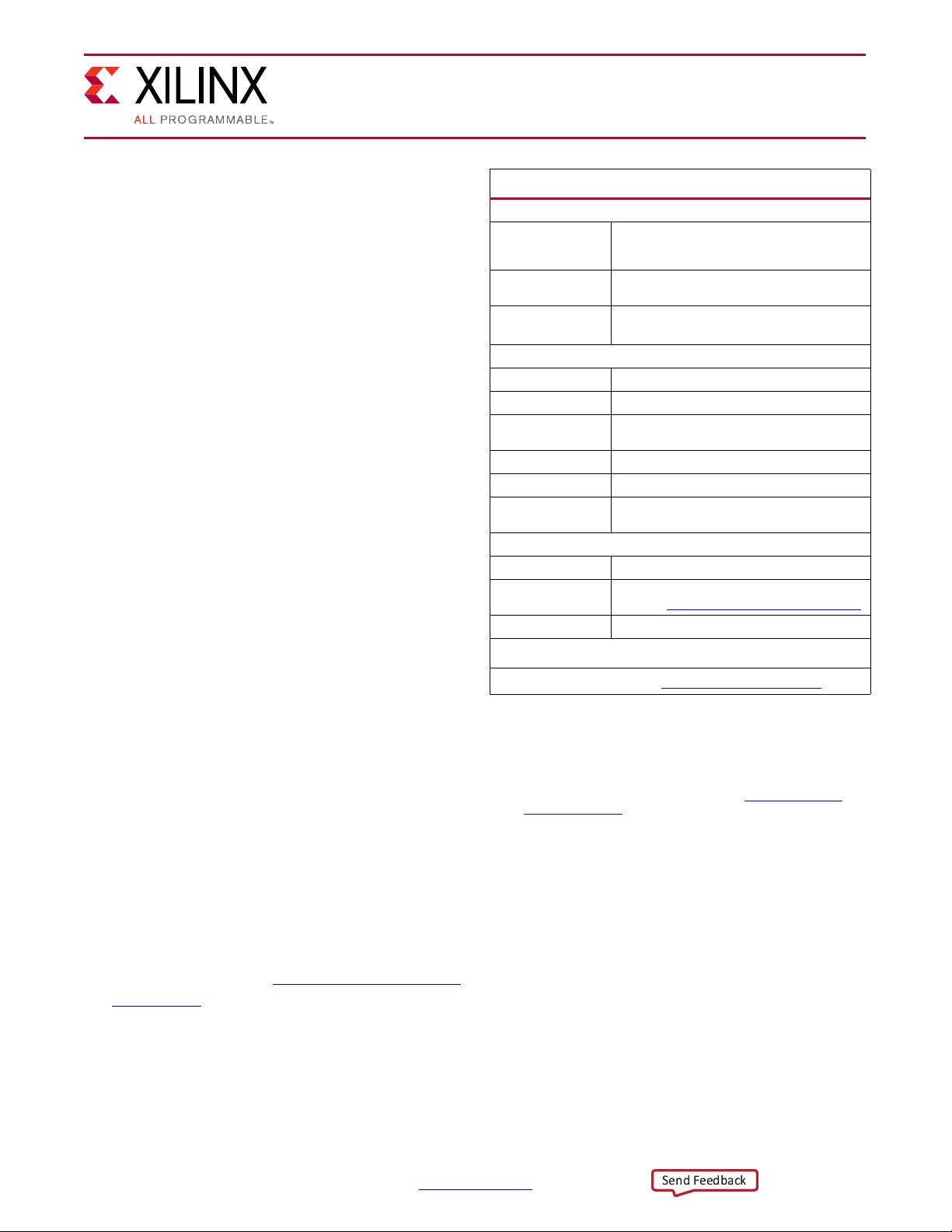

IP Facts

Send Feedback

Introduction

The Xilinx® LogiCORE™ IP eXtended

Attachment Unit Interface (XAUI) core is a

high-performance, low-pin count 10-Gb/s

interface intended to allow physical separation

between the data link layer and physical layer

devices in a 10-Gigabit Ethernet system.

The XAUI core implements a single-speed

full-duplex 10-Gb/s Ethernet eXtended

Attachment Unit Interface (XAUI) solution for

the UltraScale™ architecture, Zynq®-7000 All

Programmable SoC, and 7-series devices.

Features

• Designed to 10-Gigabit Ethernet IEEE

802.3-2012 specification

• Supports 20G double-rate XAUI (Double

XAUI) using four transceivers at 6.25 Gb/s.

For devices and speed grades, see Speed

Grades.

• Uses four transceivers at 3.125 Gb/s line

rate to achieve 10-Gb/s data rate

• Implements Data Terminal Equipment (DTE)

XGMII Extender Sublayer (XGXS), PHY XGXS,

and 10GBASE-X Physical Coding Sublayer

(PCS) in a single netlist

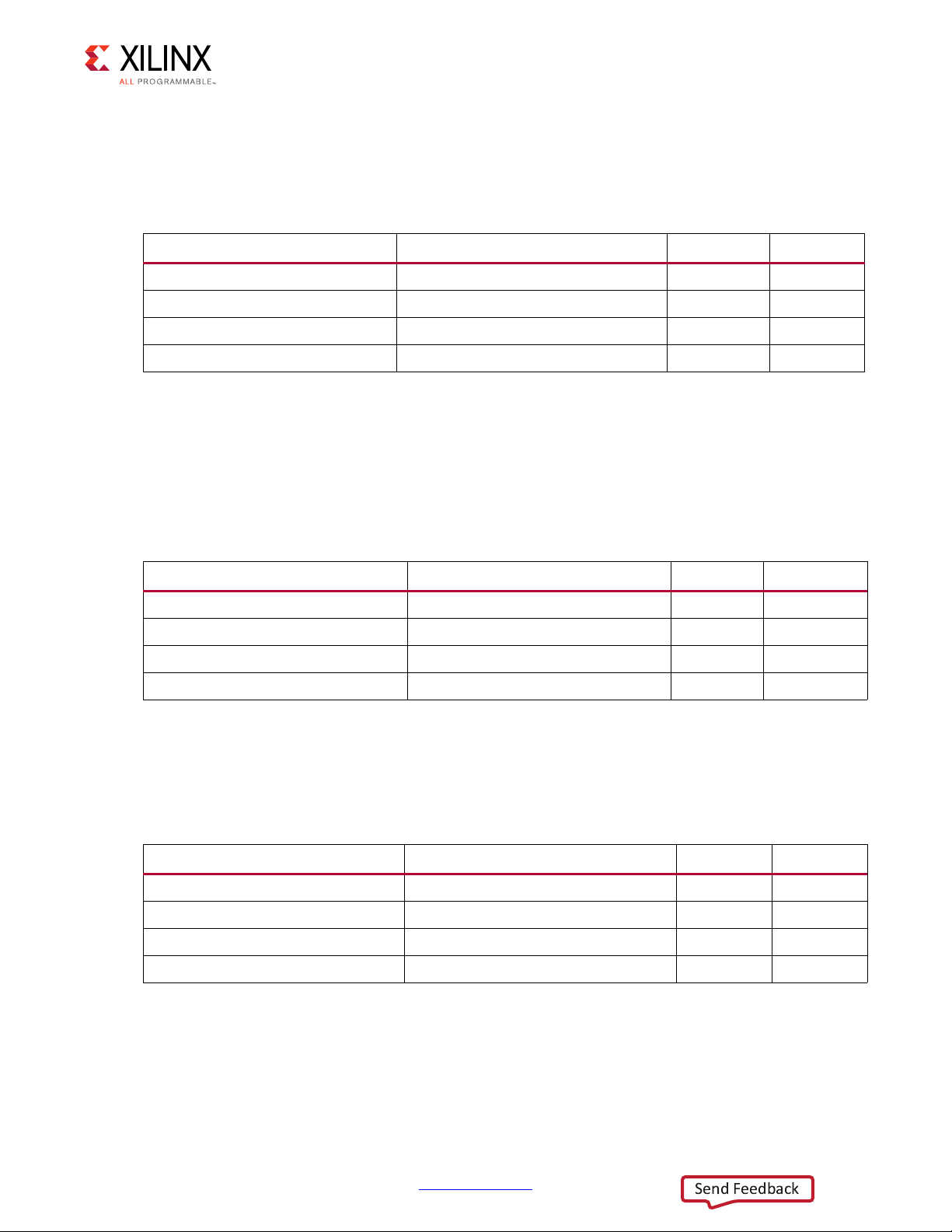

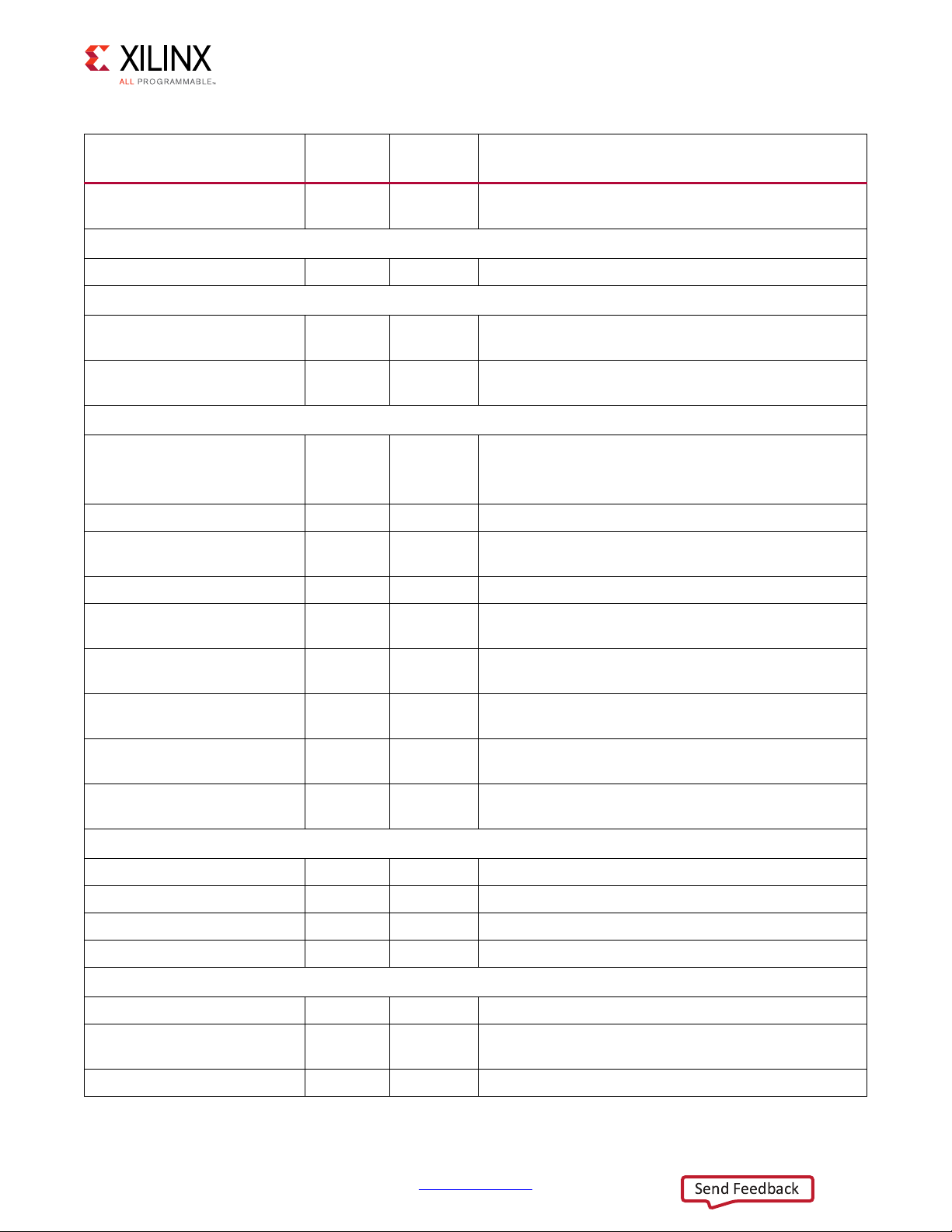

LogiCORE IP Facts

Core Specifics

Supported Device

(1)

Family

Supported User

Interfaces

Resources

Design Files Encrypted RTL

Example Design VHDL and Verilog

Test Bench

Constraints File Xilinx Design Constraints (XDC)

Simulation Model VHDL/Verilog

Supported S/W

Drivers

Design Entry Vivado® Design Suite

Simulation

Synthesis Vivado Synthesis

(2), (3)

UltraScale™ Architecture, Zynq®-7000, 7 Series

See Table 2-2, Table 2-3, Table 2-4, and

Provided with Core

Tested Design Flows

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide

UltraScale+™ Families,

64-bit XG

VHDL Test Bench

Verilog Test Fixture

(4)

Devices

MII Interface

Table 2-5.

NA

Support

Provided by Xilinx, Inc.@ Xilinx Support web page

1.For a complete list of supported devices, see Vivado IP catalog. See

Verification for supported speed grades.

2.Resource utilizations for 20 G are the same as those for 10 G. For

detailed utilization numbers based upon configuration, see

Table 2-2 through Table 2-5.

3.Resource utilization depends on target device and configuration. See

Table 2-2 through Table 2-5 for detailed information.

4.For the supported versions of the tools, see the Xilinx Design Tools:

Release Notes Guide.

.

• IEEE 802.3-2012 clause 45 Management

Data Input/Output (MDIO) interface

(optional)

• IEEE 802.3-2012 clause 48 State Machines

• Available under the Xilinx End User License

Agreement

XAUI v12.3 Product Guide www.xilinx.com 5

PG053 April 6, 2016 Product Specification

Page 6

Overview

Send Feedback

XAUI is a four-lane, 3.125 Gb/s-per-lane serial interface. Each lane is a differential pair

carrying current mode logic (CML) signaling, and the data on each lane is 8B/10B encoded

before transmission. Special code groups are used to allow each lane to synchronize at a

word boundary and to deskew all four lanes into alignment at the receiving end. The XAUI

standard is fully specified in clauses 47 and 48 of the 10-Gigabit Ethernet IEEE 802.3-2012

specification.

The XAUI standard was initially developed as a means to extend the physical separation

possible between Media Access Controller (MAC) and PHY components in a 10-Gigabit

Ethernet system distributed across a circuit board and to reduce the number of interface

signals in comparison with the XGMII (10-Gigabit Ethernet Media Independent Interface).

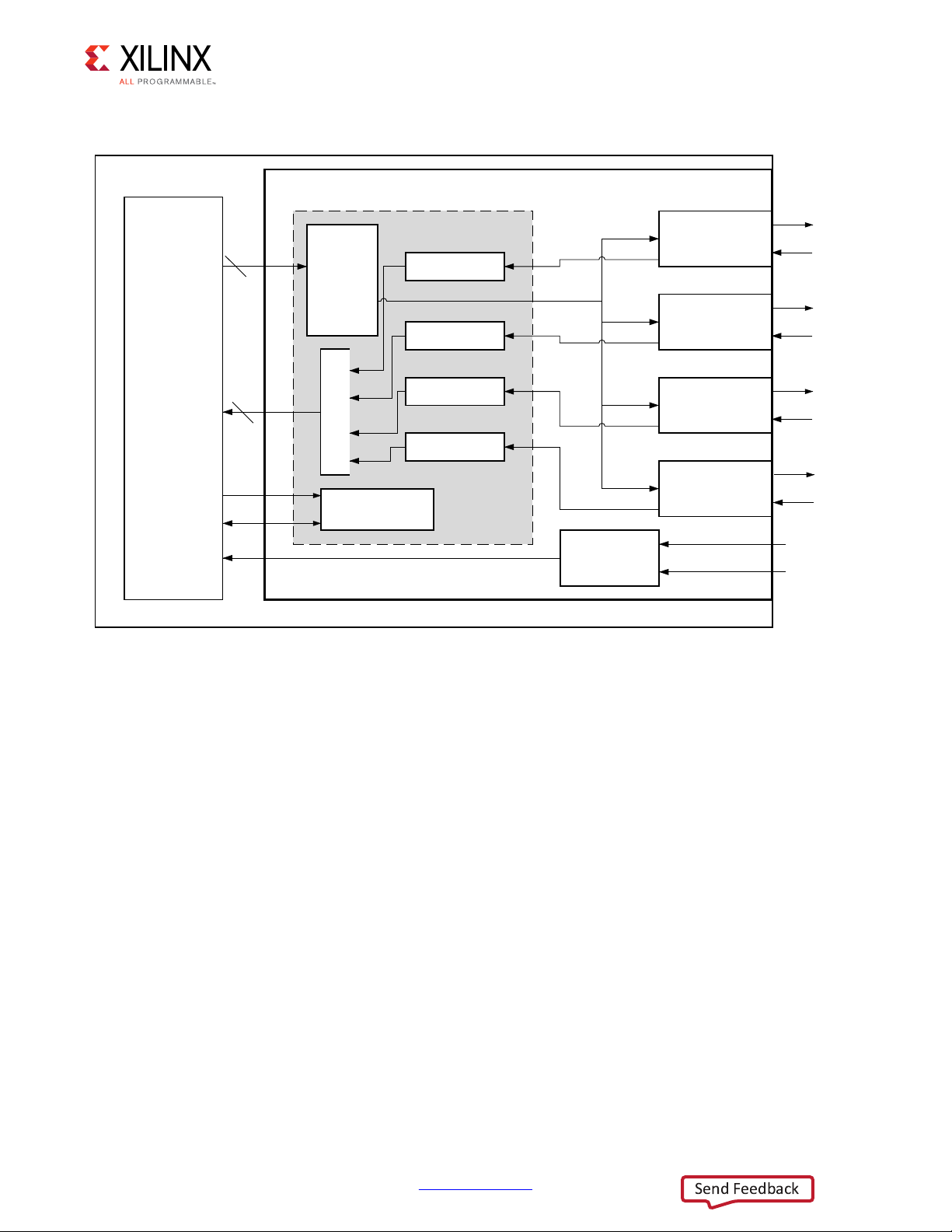

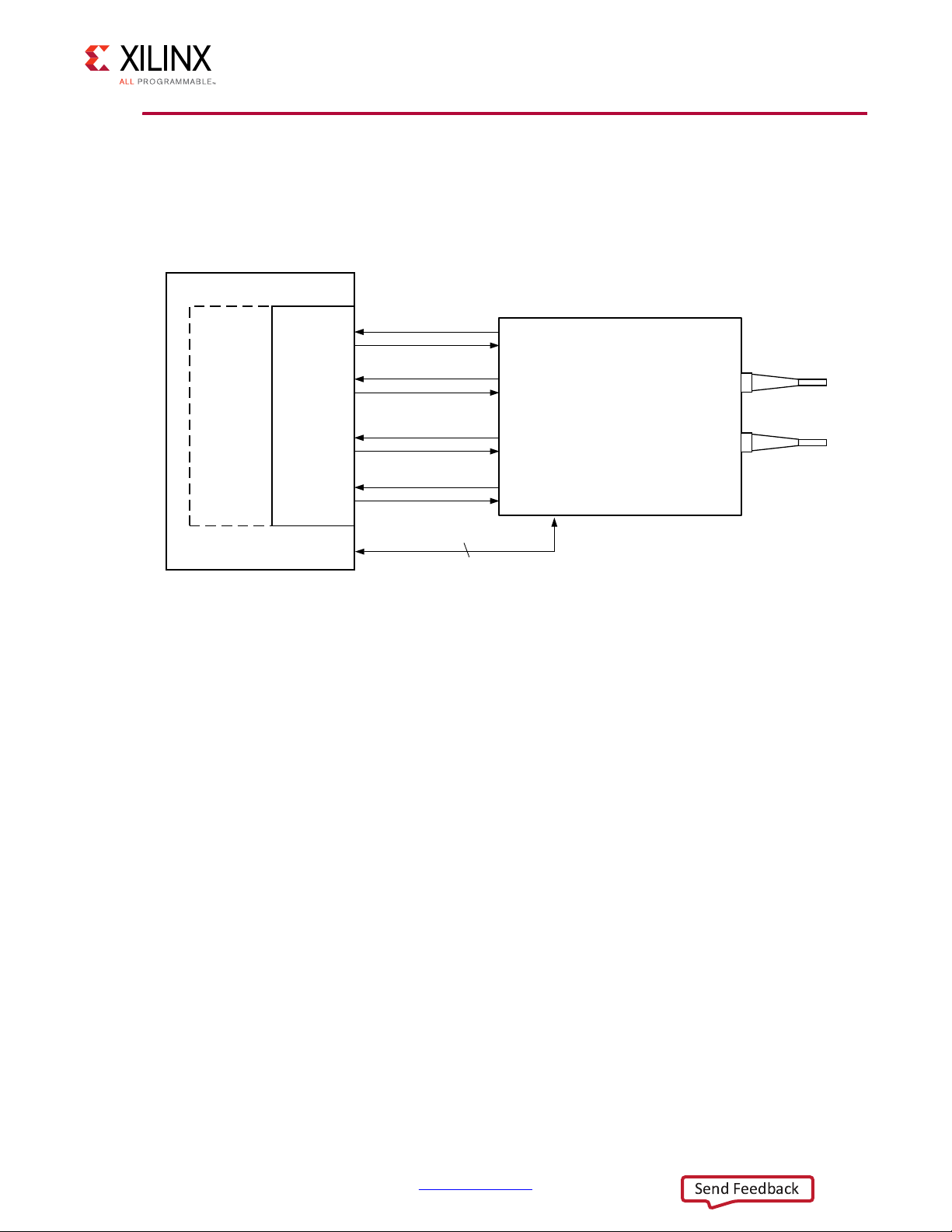

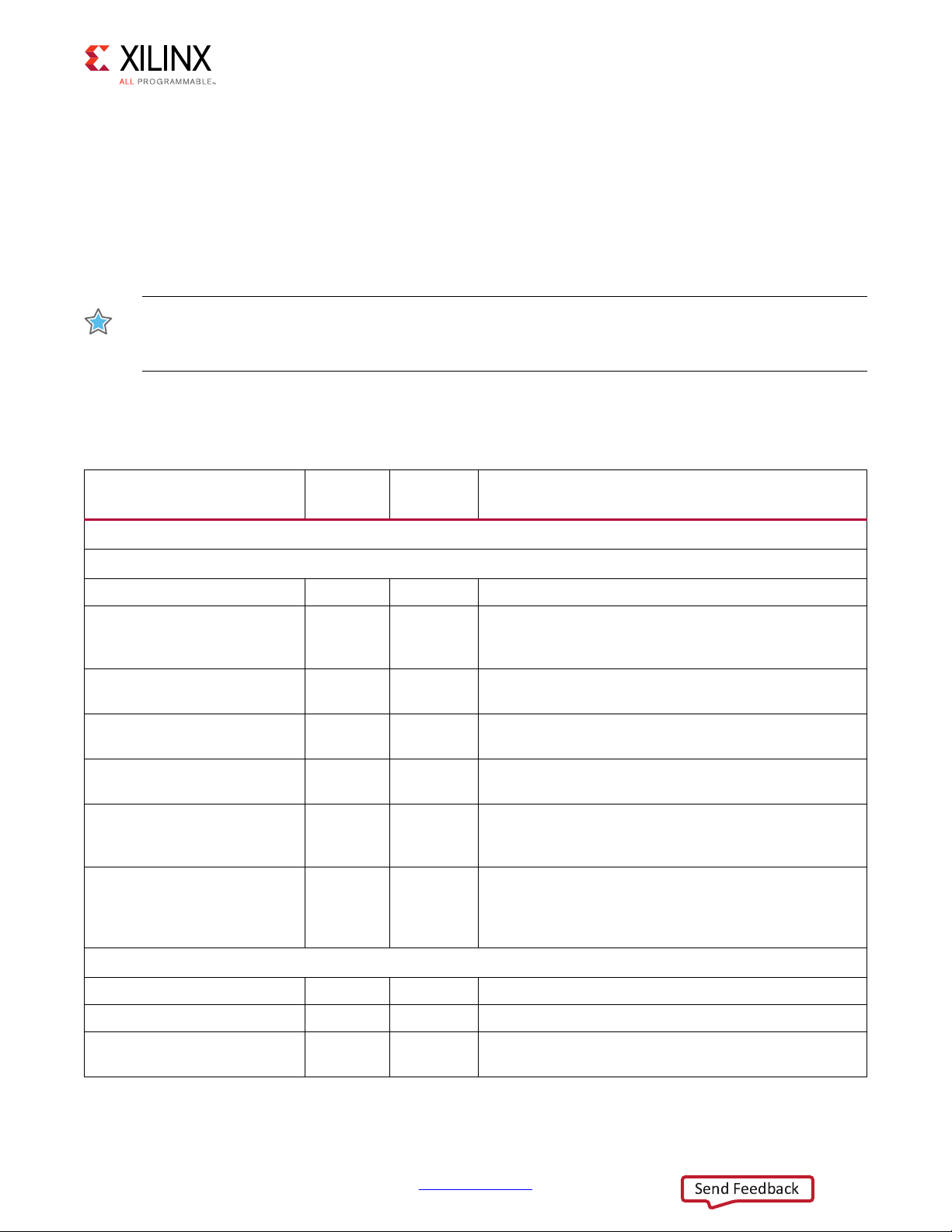

Figure 1-1 shows a block diagram of the XAUI core implementation. The major functional

blocks of the core include the following:

Chapter 1

• Transmit Idle Generation Logic creates the code groups to allow synchronization and

alignment at the receiver.

• Synchronization State Machine (one per lane) identifies byte boundaries in incoming

serial data.

• Deskew State Machine de-skews the four received lanes into alignment.

• Optional MDIO Interface is a two-wire low-speed serial interface used to manage the

core.

• Four Device-Specific Transceivers (integrated in the FPGAs) provide the high-speed

transceivers as well as 8B/10B encode and decode and elastic buffering in the receive

datapath.

XAUI v12.3 Product Guide www.xilinx.com 6

PG053 April 6, 2016

Page 7

X-Ref Target - Figure 1-1

X13667

FPGA

User Logic

Transceiver

Transceiver

Transceiver

Transceiver

Clocks and

Reset

Logic

Idle

Generation

Synchronization

Deskew

Management

Synchronization

Synchronization

Synchronization

Encrypted HDL

Core

64+8

64+8

Reference

clock

Resetclk156_out

Lane 0

Lane 1

Lane 2

Lane 3

mdc

mdio

Core

Send Feedback

Chapter 1: Overview

Figure 1‐1: Architecture of the XAUI IP Core with Client-Side User Logic

XAUI v12.3 Product Guide www.xilinx.com 7

PG053 April 6, 2016

Page 8

Chapter 1: Overview

Send Feedback

Additional Features

20-Gigabit XAUI (Double XAUI) Support

By running the XAUI interface at twice the normal clock and line rates, 20-Gigabit data rate

can be achieved. For devices and speed grades, see Speed Grades. Consult the release notes

for the core for the specific devices supported.

About the Core

The XAUI core is a Xilinx® Intellectual Property (IP) core, included in the latest IP Update on

the Xilinx IP Center. For detailed information about the core, see the XAUI product page

.

Recommended Design Experience

Although the XAUI core is a fully-verified solution, the challenge associated with

implementing a complete design varies depending on the configuration and functionality

of the application. For best results, previous experience building high performance,

pipelined Field Programmable Gate Array (FPGA) designs using Xilinx implementation

software and Xilinx Design Constraints (XDC) is recommended.

Contact your local Xilinx representative for a closer review and estimation for your specific

requirements.

XAUI v12.3 Product Guide www.xilinx.com 8

PG053 April 6, 2016

Page 9

Chapter 1: Overview

User Logic

(Ten Gigabit

Ethernet

MAC)

FPGA

XPAK Optical Module

XAUICore

low speed management signals

X13723

Send Feedback

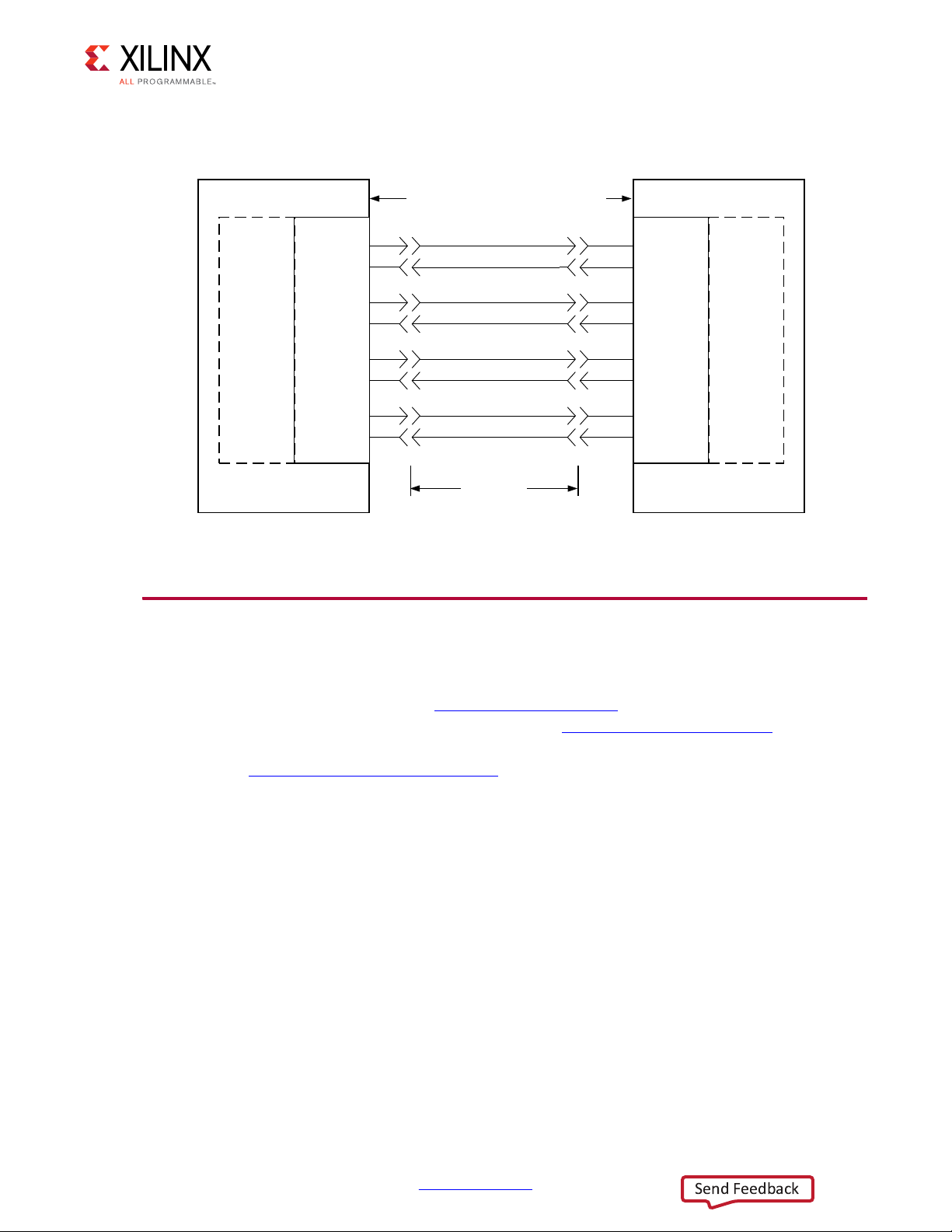

Applications

Figure 1-2 shows the XAUI core connecting a 10-Gigabit Ethernet MAC to a 10-Gigabit

XPAK optical module.

X-Ref Target - Figure 1-2

Figure 1‐2: XAUI Connecting a 10-Gigabit Ethernet MAC to an Optical Module

After its publication, the applications of XAUI have extended beyond 10-Gigabit Ethernet to

the backplane and other general high-speed interconnect applications. Figure 1-3 shows a

typical backplane and other general high-speed interconnect applications.

XAUI v12.3 Product Guide www.xilinx.com 9

PG053 April 6, 2016

Page 10

X-Ref Target - Figure 1-3

XAUI

Core

XAUI

Core

Up to 20in FR-4 plus 2 connectors

User

Logic

User

Logic

Backplane

FPGA FPGA

x13668

Send Feedback

Chapter 1: Overview

Figure 1‐3: Typical Backplane Application for XAUI

Licensing and Ordering Information

This Xilinx LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado®

Design Suite under the terms of the Xilinx End User License

other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property

information about pricing and availability of other Xilinx LogiCORE IP modules and tools,

contact your local Xilinx sales representative

.

. Information about this and

page. For

XAUI v12.3 Product Guide www.xilinx.com 10

PG053 April 6, 2016

Page 11

Chapter 1: Overview

Send Feedback

Feedback

Xilinx welcomes comments and suggestions about the XAUI core and the documentation

supplied with the core.

Core

For comments or suggestions about the XAUI core, submit a webcase from Xilinx Support

web page. Be sure to include the following information:

• Product name

• Core version number

• Explanation of your comments

Document

For comments or suggestions about this document, submit a webcase from

www.xilinx.com/support

• Document title

• Document number

• Page number(s) to which your comments refer

• Explanation of your comments

. Be sure to include the following information:

XAUI v12.3 Product Guide www.xilinx.com 11

PG053 April 6, 2016

Page 12

Product Specification

Send Feedback

Standards Compliance

The XAUI IP core is designed to the standard specified in clauses 47 and 48 of the

10-Gigabit Ethernet specification IEEE Std. 802.3-2012.

Performance

This section contains the following subsections:

• Latency

Chapter 2

• Speed Grades

Latency

These measurements are for the core only; they do not include the latency through the

transceiver. The latency through the transceiver can be obtained from the relevant

transceiver user guide.

Transmit Path Latency

As measured from the input port xgmii_txd[63:0] of the transmitter side XGMII (until

that data appears on the txdata pins on the internal transceiver interface on the

transceiver interface), the latency through the core for the internal XGMII interface

configuration in the transmit direction is four clk periods of the core input usrclk.

Receive Path Latency

Measured from the input into the core encrypted hdl logic from the rxdata pins of the

internal transceiver interface until the data appears on xgmii_rxdata[63:0] of the

receiver side XGMII interface, the latency through the core in the receive direction is equal

to 4

–5 clock cycles of usrclk.

XAUI v12.3 Product Guide www.xilinx.com 12

PG053 April 6, 2016

Page 13

Chapter 2: Product Specification

Send Feedback

If the word appears on the upper half of the two-byte transceiver interface, the latency is

five clock cycles of usrclk and it appears on the lower half of the XGMII interface. If it

appears on the lower half of the two-byte interface, the latency is four clock cycles of

usrclk and it appears on the upper half of the XGMII interface.

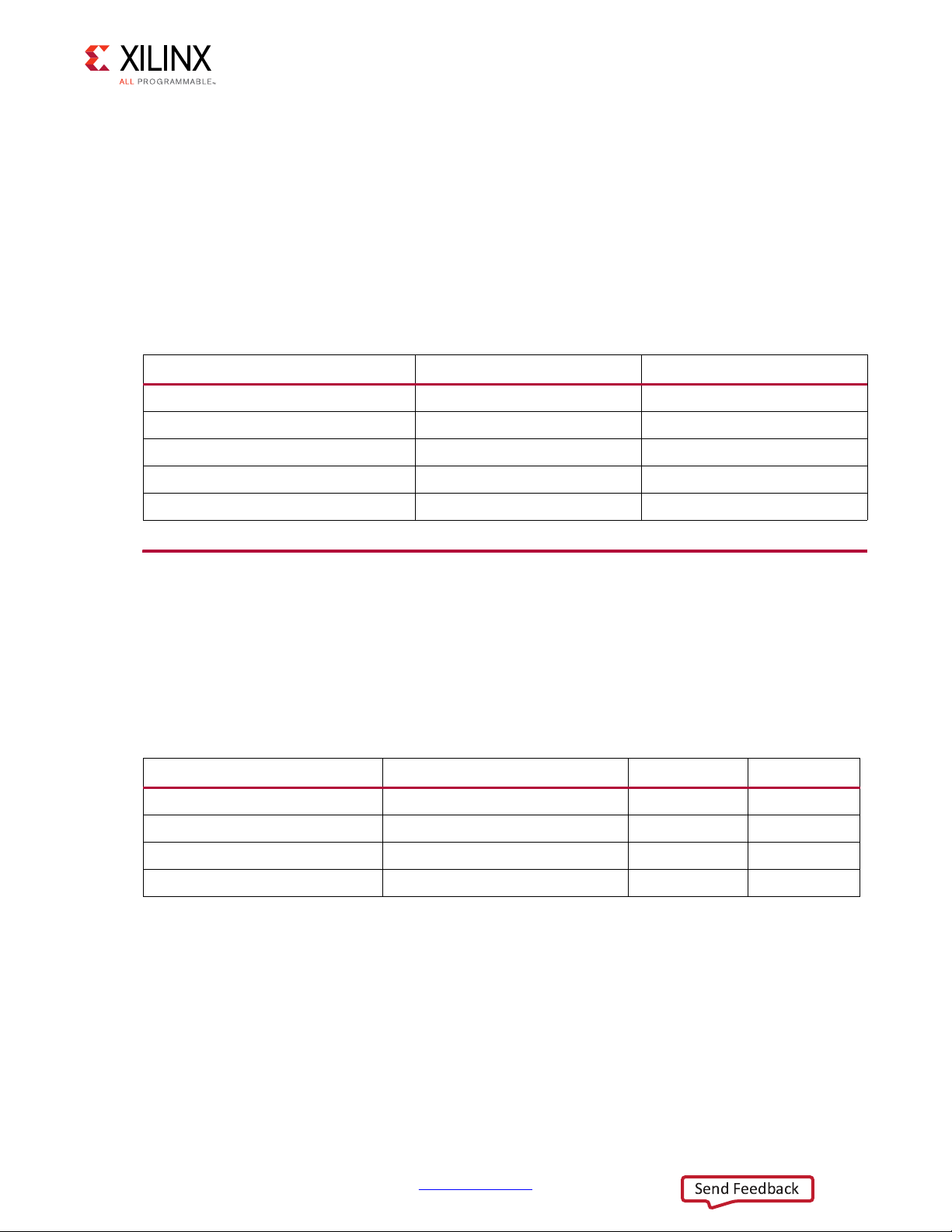

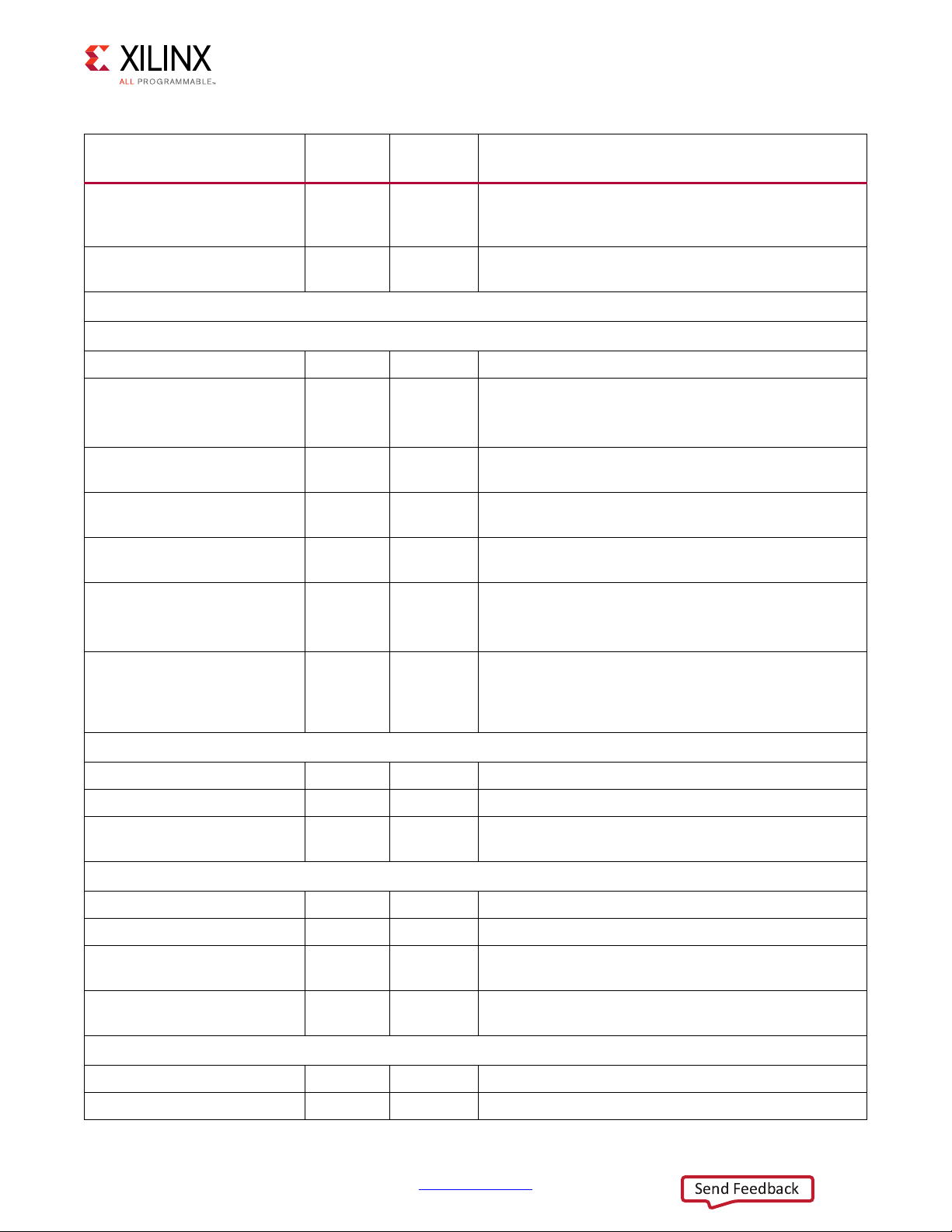

Speed Grades

The minimum device requirements for 10G and 20G operation are listed in the following

table.

Table 2‐1: Speed Grades

Device XAUI (4x3.125G) DXAUI (4x6.25G)

UltraScale Architecture -1 -1

Zynq-7000 –1 –2

Virtex-7 –1 –2

Kintex-7 –1 –2

Artix-7 –1 –2

Resource Utilization

UltraScale Architecture Devices

Table 2-2 provides approximate resource counts for the various core options on

UltraScale™ architecture.

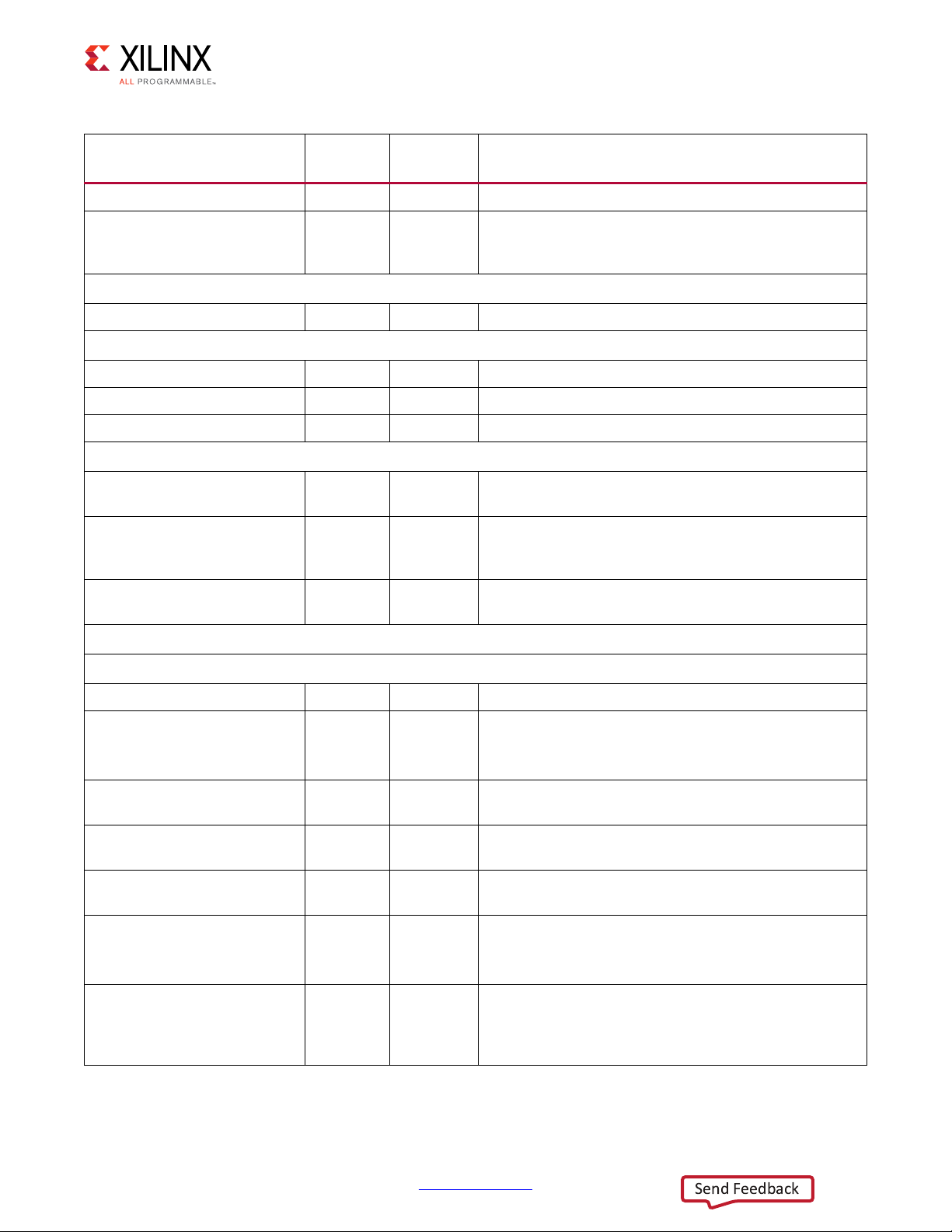

Table 2‐2: Device Utilization – UltraScale Architectures

Shared Logic MDIO Management LUTs FFs

In Example Design FALSE 724 995

In Example Design TRUE 864 1094

In Core FALSE 813 995

In Core TRUE 956 1094

XAUI v12.3 Product Guide www.xilinx.com 13

PG053 April 6, 2016

Page 14

Chapter 2: Product Specification

Send Feedback

Virtex-7 (GTH) FPGAs

Table 2-3 provides approximate resource counts for the various core options on Virtex®-7

FPGAs.

Table 2‐3: Device Utilization – Virtex-7 FPGAs

Shared Logic MDIO Management LUTs FFs

In Example Design FALSE 1036 1193

In Example Design TRUE 1192 1292

In Core FALSE 1114 1193

In Core TRUE 1263 1292

Zynq-7000, Virtex-7 (GTX), and Kintex-7 Devices

Table 2-4 provides approximate resource counts for the various core options Kintex-7

devices.

Note:

.

Zynq®-7000 device results are expected to be similar to Kintex-7 device results.

Table 2‐4: Device Utilization – Kintex-7 Devices

Shared Logic MDIO Management LUTs FFs

In Example Design FALSE 765 945

In Example Design TRUE 877 1044

In Core FALSE 845 945

In Core TRUE 957 1044

Artix-7 FPGAs

Table 2-5 provides approximate resource counts for the various core options on Artix®-7

FPGAs.

Table 2‐5: Device Utilization – Artix-7 FPGAs

Shared Logic MDIO Management LUTs FFs

In Example Design FALSE 1027 1186

In Example Design TRUE 1144 1285

In Core FALSE 1107 1186

XAUI v12.3 Product Guide www.xilinx.com 14

PG053 April 6, 2016

In Core TRUE 1223 1285

Page 15

Chapter 2: Product Specification

Send Feedback

Verification

The XAUI core has been verified using both simulation and hardware testing.

Simulation

A highly parameterizable transaction-based simulation test suite was used to verify the

core. Verification tests include:

• Register access over MDIO

• Loss and regain of synchronization

• Loss and regain of alignment

• Frame transmission

• Frame reception

• Clock compensation

• Recovery from error conditions

Hardware Verification

The core has been used in several hardware test platforms within Xilinx. In particular, the

®

core has been used in a test platform design with the Xilinx

design comprises the MAC, XAUI, a ping loopback First In First Out (FIFO), and a test pattern

generator all under embedded processor control. This design has been used for

conformance and interoperability testing at the University of New Hampshire

Interoperability Lab.

10-Gigabit Ethernet MAC. This

XAUI v12.3 Product Guide www.xilinx.com 15

PG053 April 6, 2016

Page 16

Chapter 2: Product Specification

Send Feedback

Port Descriptions

Client-Side Interface

The signals of the client-side interface are shown in Table 2-6. See Chapter 5, Interfacing to

the Core for more information on connecting to the client-side interface.

Table 2‐6: Client-Side Interface Ports

Signal Name Direction Clock Domain Description

xgmii_txd[63:0] IN clk156_out Transmit data, eight bytes wide

xgmii_txc[7:0] IN clk156_out Transmit control bits, one bit per transmit data byte

xgmii_rxd[63:0] OUT clk156_out Received data, eight bytes wide

xgmii_rxc[7:0] OUT clk156_out Receive control bits, one bit per received data byte

Transceiver I/O

The Transceiver Interface is no longer part of the ports of the core because it includes the

transceiver. Instead there are the following ports.

• Ports Corresponding to the I/O of the transceiver

• Dynamic Reconfiguration Port of the transceiver

See Table 2-7.

Table 2‐7: Ports Corresponding to the I/O of the Transceiver

Signal Name Direction Clock Domain Description

xaui_tx_l0_p, xaui_tx_l0_n,

xaui_tx_l1_p, xaui_tx_l1_n,

xaui_tx_l2_p, xaui_tx_l2_n,

xaui_tx_l3_p, xaui_tx_l3_n

xaui_rx_l0_p, xaui_rx_l0_n,

xaui_rx_l1_p, xaui_rx_l1_n,

xaui_rx_l2_p, xaui_rx_l2_n,

xaui_rx_l3_p, xaui_rx_l3_n

signal_detect[3:0] IN Async

OUT N/A

IN N/A

Differential complements of one another

forming a differential transmit output pair.

One pair for each of the 4 lanes.

Differential complements of one another

forming a differential receiver input pair. One

pair for each of the 4 lanes.

Intended to be driven by an attached

10GBASE-LX4 optical module; they signify

that each of the four optical receivers is

receiving illumination and is therefore not just

putting out noise. If an optical module is not

in use, this four-wire bus should be tied to

1111.

XAUI v12.3 Product Guide www.xilinx.com 16

PG053 April 6, 2016

Page 17

Transceiver Control and Status Ports

Send Feedback

Optional ports that, if enabled, allow the monitoring and control of certain important ports

of the transceivers. When not selected, these ports are tied to their default values. For

information on these ports, see the 7 Series FPGAs GTX/GTH Transceivers User Guide

(UG476) [Ref 1], the 7 Series FPGAs GTP Transceivers User Guide (UG482) [Ref 2], the

UltraScale Architecture GTH Transceivers User Guide (UG576) [Ref 3], and the Ultrascale

Architecture GTY Transceivers User Guide (UG578) [Ref 4]).

IMPORTANT: The ports in the Transceiver Control And Status Interface must be driven in accordance

with the appropriate GT user guide. Using the input signals listed in

unpredictable behavior of the IP core.

Note: The Dynamic Reconfiguration Port is only available if the Transceiver Control and Status Ports

option is selected

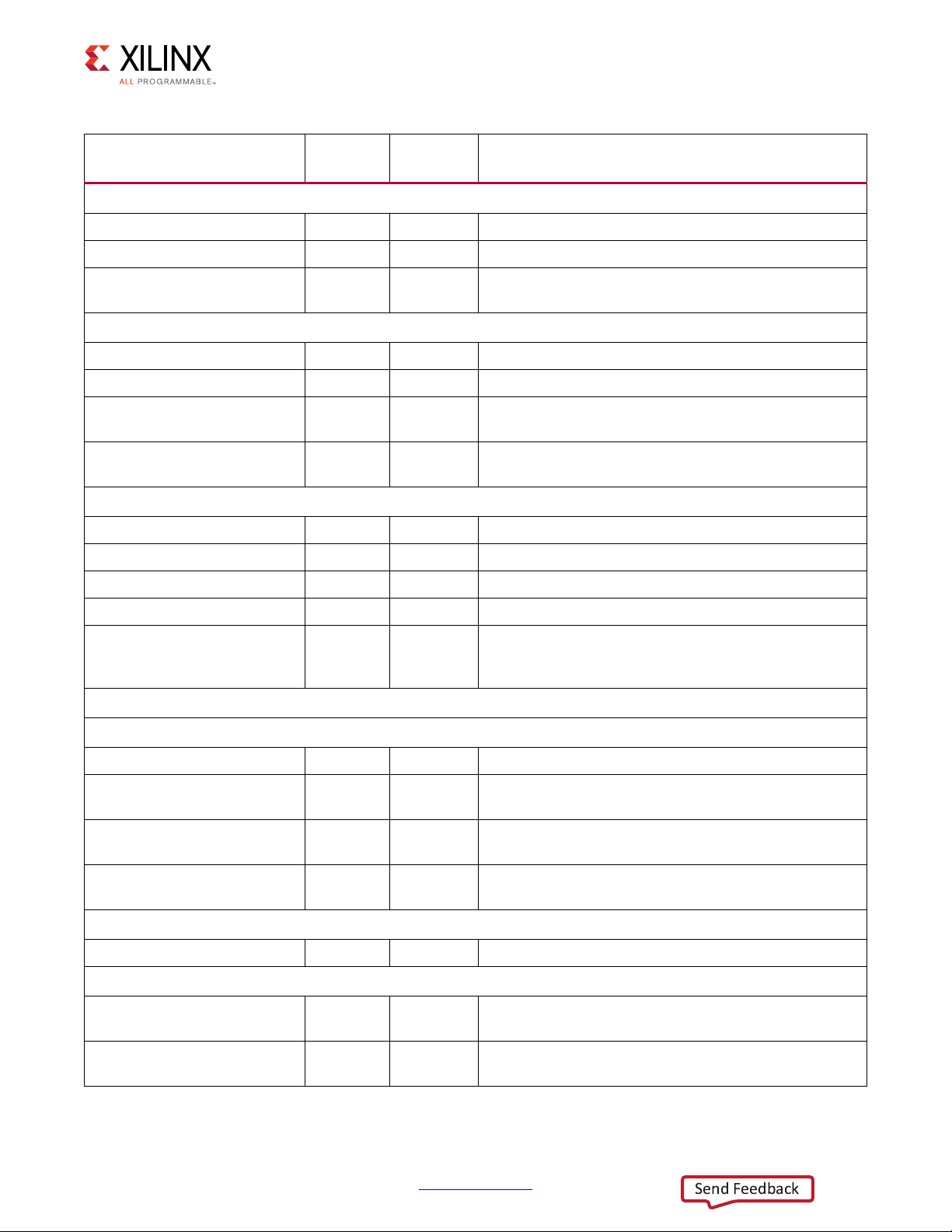

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs

Chapter 2: Product Specification

Table 2-8 may result in

Signal Name Direction

Clock

Domain

Description

CHANNEL 0

GT0 DRP

gt0_drpaddr[8:0] in dclk DRP address bus for channel 0

DRP enable signal.

gt0_drpen in dclk

gt0_drpdi[15:0] in dclk

gt0_drpdo[15:0] out dclk

gt0_drprdy out dclk

gt0_drpwe in dclk

gt0_drp_busy out dclk

0: No read or write operation performed.

1: enables a read or write operation.

Data bus for writing configuration data to the

transceiver for channel 0.

Data bus for reading configuration data from the

transceiver for channel 0.

Indicates operation is complete for write operations

and data is valid for read operations for channel 0.

DRP write enable for channel 0.

0: Read operation when drpen is 1.

1: Write operation when drpen is 1.

(GTPE2 all configurations or GTHE2 10G

configuration). Indicates the DRP interface is being

used internally by the serial transceiver and should not

be driven until this signal is deasserted.

gt0_txpmareset_in in Async Starts the TX PMA reset process.

gt0_txpcsreset_in in Async Starts the TX PCS reset process.

gt0_txresetdone_out out clk156_out

XAUI v12.3 Product Guide www.xilinx.com 17

PG053 April 6, 2016

GT0 TX Reset and Initialization

When asserted the serial transceiver TX has finished

reset and is ready for use.

Page 18

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

Clock

Domain

Description

GT0 RX Reset and Initialization

gt0_rxpmareset_in in Async Starts the RX PMA reset process.

gt0_rxpcsreset_in in Async Starts the RX PCS reset process.

gt0_rxpmaresetdone_out out Async

gt0_rxresetdone_out out clk156_out

(GTHE2 and GTPE2) This active-High signal indicates

RX PMA reset is complete.

When asserted the serial transceiver RX has finished

reset and is ready for use.

GT0 Clocking

gt0_rxbufstatus_out[2:0] out clk156_out RX buffer status.

gt0_txphaligndone_out out Async TX phase alignment done.

gt0_txphinitdone_out out Async TX phase alignment initialization done.

gt0_txdlysresetdone_out out Async TX delay alignment soft reset done.

(GTHE2) This active-High PLL frequency lock signal

gt0_cplllock_out out Async

gt_qplllock_out out Async

indicates that the PLL frequency is within

predetermined tolerance.

(GTXE2 and GTPE2) This active-High PLL frequency lock

signal indicates that the PLL frequency is within

predetermined tolerance.

Signal Integrity and Functionality

GT0 Eye scan

gt0_eyescantrigger_in in clk156_out Causes a trigger event.

gt0_eyescanreset_in in Async

gt0_eyescandataerror_out out Async

gt0_rxrate_in[2:0] in Reserved

This port is driven High and then deasserted to start

the EYESCAN reset process.

Asserts High for one rec_clk cycle when an

(unmasked) error occurs while in the COUNT or ARMED

state.

This port dynamically controls the setting for the RX

serial clock divider.

GT0 Loopback

gt0_loopback_in[2:0] in Async Determines the loopback mode.

GT0 Polarity

gt0_rxpolarity_in in clk156_out

gt0_txpolarity_in in clk156_out

The rxpolarity port can invert the polarity of incoming

data.

The txpolarity port can invert the polarity of outgoing

data.

GT0 RX Decision Feedback Equalizer (DFE)

gt0_rxlpmen_in in Async

(GTXE2 and GTHE2) RX datapath.

0: DFE. 1: LPM.

XAUI v12.3 Product Guide www.xilinx.com 18

PG053 April 6, 2016

Page 19

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

gt0_rxdfelpmreset_in in Async (GTXE2 and GTHE2) Reset for LPM and DFE datapath.

gt0_rxmonitorsel_in[1:0] in Reserved

gt0_rxmonitorout_out[6:0] out Async (GTXE2 and GTHE2) Monitor output.

gt0_rxlpmreset_in in clk156_out

gt0_rxlpmhfhold_in in Async

gt0_rxlpmhfovrden_in in Async

gt0_rxlpmlfhold_in in Async

gt0_rxlpmlfovrden_in in Async

Clock

Domain

Description

(GTXE2 and GTHE2) Select signal for

gt0_rxmonitorout_out.

(GTPE2) This port is driven High and then deasserted to

start the LPM reset process.

(GTPE2) Determines whether the value of the

high-frequency boost is either held or adapted.

(GTPE2) Determines whether the high-frequency boost

is controlled by an attribute or a signal.

(GTPE2) Determines whether the value of the

low-frequency boost is either held or adapted.

(GTPE2) Determines whether the low-frequency boost

is controlled by an attribute or a signal.

GT0 TX Driver

gt0_txpostcursor_in[4:0] in Async Transmitter post-cursor TX post-emphasis control.

gt0_txprecursor_in[4:0] in Async Transmitter post-cursor TX pre-emphasis control.

gt0_txdiffctrl_in[3:0] in Async Driver Swing Control.

gt0_txinhibit_in in clk156_out When High, this signal blocks the transmission of data.

GT0 PRBS

gt0_rxprbscntreset_in in clk156_out Resets the PRBS error counter.

gt0_rxprbserr_out out clk156_out

gt0_rxprbssel_in[2:0] in clk156_out Receiver PRBS checker test pattern control.

gt0_txprbssel_in[2:0] in clk156_out Transmitter PRBS generator test pattern control.

gt0_txprbsforceerr_in in clk156_out

This non-sticky status output indicates that PRBS

errors have occurred.

When this port is driven High, errors are forced in the

PRBS transmitter. While this port is asserted, the

output data pattern contains errors.

GT0 RX CDR

gt0_rxcdrhold_in in Async Hold the CDR control loop frozen.

GT0 Digital Monitor

gt0_dmonitorout_out[7:0] out Async (GTXE2) Digital Monitor Output Bus

gt0_dmonitorout_out[14:0] out Async (GTHE2) Digital Monitor Output Bus

gt0_dmonitorout_out[14:0] out Async (GTPE2) Digital Monitor Output Bus

GT0 Status

gt0_rxdisperr_out[3:0] out clk156_out

XAUI v12.3 Product Guide www.xilinx.com 19

PG053 April 6, 2016

Active-High indicates the corresponding byte of the

received data has a disparity error

Page 20

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

gt0_rxnotintable_out[3:0] out clk156_out

gt0_rxcommadet_out out clk156_out

Clock

Domain

Description

Active-High indicates the corresponding byte of the

received data was not a valid character in the 8B/10B

table.

This signal is asserted when the comma alignment

block detects a comma.

CHANNEL 1

GT1 DRP

gt1_drpaddr[8:0] in dclk DRP address bus for channel 1.

DRP enable signal.

gt1_drpen in dclk

gt1_drpdi[15:0] in dclk

gt1_drpdo[15:0] out dclk

gt1_drprdy out dclk

gt1_drpwe in dclk

0: No read or write operation performed.

1: enables a read or write operation.

Data bus for writing configuration data to the

transceiver for channel 1.

Data bus for reading configuration data from the

transceiver for channel 1.

Indicates operation is complete for write operations

and data is valid for read operations for channel 1.

DRP write enable for channel 1.

0: Read operation when drpen is 1.

1: Write operation when drpen is 1.

(GTPE2 all configurations or GTHE2 10G

gt1_drp_busy out dclk

configuration). Indicates the DRP interface is being

used internally by the serial transceiver and should not

be driven until this signal is deasserted.

GT1 TX Reset and Initialization

gt1_txpmareset_in in Async Starts the TX PMA reset process.

gt1_txpcsreset_in in Async Starts the TX PCS reset process.

gt1_txresetdone_out out clk156_out

When asserted the serial transceiver TX has finished

reset and is ready for use.

GT1 RX Reset and Initialization

gt1_rxpmareset_in in Async Starts the RX PMA reset process.

gt1_rxpcsreset_in in Async Starts the RX PCS reset process.

gt1_rxpmaresetdone_out out Async

gt1_rxresetdone_out out clk156_out

(GTHE2 and GTPE2) This active-High signal indicates

RX PMA reset is complete.

When asserted the serial transceiver RX has finished

reset and is ready for use.

GT1 Clocking

gt1_rxbufstatus_out[2:0] out clk156_out RX buffer status.

gt1_txphaligndone_out out Async TX phase alignment done.

XAUI v12.3 Product Guide www.xilinx.com 20

PG053 April 6, 2016

Page 21

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

gt1_txphinitdone_out out Async TX phase alignment initialization done.

gt1_txdlysresetdone_out out Async TX delay alignment soft reset done.

gt1_cplllock_out out Async

Clock

Domain

Description

(GTHE2) This active-High PLL frequency lock signal

indicates that the PLL frequency is within

predetermined tolerance.

Signal Integrity and Functionality

GT1 Eye scan

gt1_eyescantrigger_in in clk156_out Causes a trigger event.

gt1_eyescanreset_in in Async

gt1_eyescandataerror_out out Async

gt1_rxrate_in[2:0] in Reserved

This port is driven High and then deasserted to start

the EYESCAN reset process.

Asserts High for one rec_clk cycle when an

(unmasked) error occurs while in the COUNT or ARMED

state.

This port dynamically controls the setting for the RX

serial clock divider.

GT1 Loopback

gt1_loopback_in[2:0] in Async Determines the loopback mode.

GT1 Polarity

gt1_rxpolarity_in in clk156_out

gt1_txpolarity_in in clk156_out

The rxpolarity port can invert the polarity of incoming

data.

The txpolarity port can invert the polarity of outgoing

data.

GT1 RX Decision Feedback Equalizer (DFE)

gt1_rxlpmen_in in Async

gt1_rxdfelpmreset_in in Async (GTXE2 and GTHE2) Reset for LPM and DFE datapath.

gt1_rxmonitorsel_in[1:0] in Reserved

gt1_rxmonitorout_out[6:0] out Async (GTXE2 and GTHE2) Monitor output.

gt1_rxlpmreset_in in clk156_out

gt1_rxlpmhfhold_in in Async

gt1_rxlpmhfovrden_in in Async

gt1_rxlpmlfhold_in in Async

(GTXE2 and GTHE2) RX datapath.

0: DFE. 1: LPM.

(GTXE2 and GTHE2) Select signal for

gt1_rxmonitorout_out.

(GTPE2) This port is driven High and then deasserted to

start the LPM reset process.

(GTPE2) Determines whether the value of the

high-frequency boost is either held or adapted.

(GTPE2) Determines whether the high-frequency boost

is controlled by an attribute or a signal.

(GTPE2) Determines whether the value of the

low-frequency boost is either held or adapted.

gt1_rxlpmlfovrden_in in Async

XAUI v12.3 Product Guide www.xilinx.com 21

PG053 April 6, 2016

(GTPE2) Determines whether the low-frequency boost

is controlled by an attribute or a signal.

Page 22

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

Clock

Domain

Description

GT1 TX Driver

gt1_txpostcursor_in[4:0] in Async Transmitter post-cursor TX post-emphasis control.

gt1_txprecursor_in[4:0] in Async Transmitter post-cursor TX pre-emphasis control.

gt1_txdiffctrl_in[3:0] in Async Driver Swing Control.

gt1_txinhibit_in in clk156_out When High, this signal blocks the transmission of data.

GT1 PRBS

gt1_rxprbscntreset_in in clk156_out Resets the PRBS error counter.

gt1_rxprbserr_out out clk156_out

gt1_rxprbssel_in[2:0] in clk156_out Receiver PRBS checker test pattern control.

gt1_txprbssel_in[2:0] in clk156_out Transmitter PRBS generator test pattern control.

gt1_txprbsforceerr_in in clk156_out

This non-sticky status output indicates that PRBS

errors have occurred.

When this port is driven High, errors are forced in the

PRBS transmitter. While this port is asserted, the

output data pattern contains errors.

GT1 RX CDR

gt1_rxcdrhold_in in Async Hold the CDR control loop frozen.

GT1 Digital Monitor

gt1_dmonitorout_out[7:0] out Async (GTXE2) Digital Monitor Output Bus

gt1_dmonitorout_out[14:0] out Async (GTHE2) Digital Monitor Output Bus

gt1_dmonitorout_out[14:0] out Async (GTPE2) Digital Monitor Output Bus

GT1 Status

gt1_rxdisperr_out[3:0] out clk156_out

gt1_rxnotintable_out[3:0] out clk156_out

gt1_rxcommadet_out out clk156_out

Active-High indicates the corresponding byte of the

received data has a disparity error

Active-High indicates the corresponding byte of the

received data was not a valid character in the 8B/10B

table.

This signal is asserted when the comma alignment

block detects a comma.

CHANNEL 2

GT2 DRP

gt2_drpaddr[8:0] in dclk DRP address bus for channel 2.

DRP enable signal.

gt2_drpen in dclk

gt2_drpdi[15:0] in dclk

0: No read or write operation performed.

1: enables a read or write operation.

Data bus for writing configuration data to the

transceiver for channel 2.

XAUI v12.3 Product Guide www.xilinx.com 22

PG053 April 6, 2016

Page 23

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

gt2_drpdo[15:0] out dclk

gt2_drprdy out dclk

gt2_drpwe in dclk

gt2_drp_busy out dclk

Clock

Domain

Description

Data bus for reading configuration data from the

transceiver for channel 2.

Indicates operation is complete for write operations

and data is valid for read operations for channel 2.

DRP write enable for channel 2.

0: Read operation when drpen is 1.

1: Write operation when drpen is 1.

(GTPE2 all configurations or GTHE2 10G

configuration). Indicates the DRP interface is being

used internally by the serial transceiver and should not

be driven until this signal is deasserted.

GT2 TX Reset and Initialization

gt2_txpmareset_in in Async Starts the TX PMA reset process.

gt2_txpcsreset_in in Async Starts the TX PCS reset process.

gt2_txresetdone_out out clk156_out

When asserted the serial transceiver TX has finished

reset and is ready for use.

GT2 RX Reset and Initialization

gt2_rxpmareset_in in Async Starts the RX PMA reset process.

gt2_rxpcsreset_in in Async Starts the RX PCS reset process.

gt2_rxpmaresetdone_out out Async

gt2_rxresetdone_out out clk156_out

(GTHE2 and GTPE2) This active-High signal indicates

RX PMA reset is complete.

When asserted the serial transceiver RX has finished

reset and is ready for use.

GT2 Clocking

gt2_rxbufstatus_out[2:0] out clk156_out RX buffer status.

gt2_txphaligndone_out out Async TX phase alignment done.

gt2_txphinitdone_out out Async TX phase alignment initialization done.

gt2_txdlysresetdone_out out Async TX delay alignment soft reset done.

(GTHE2) This active-High PLL frequency lock signal

gt2_cplllock_out out Async

indicates that the PLL frequency is within

predetermined tolerance.

Signal Integrity and Functionality

GT2 Eye Scan

gt2_eyescantrigger_in in clk156_out Causes a trigger event.

gt2_eyescanreset_in in Async

gt2_eyescandataerror_out out Async

This port is driven High and then deasserted to start

the EYESCAN reset process.

Asserts High for one rec_clk cycle when an (unmasked)

error occurs while in the COUNT or ARMED state.

XAUI v12.3 Product Guide www.xilinx.com 23

PG053 April 6, 2016

Page 24

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

gt2_rxrate_in[2:0] in Reserved

Clock

Domain

Description

This port dynamically controls the setting for the RX

serial clock divider.

GT2 Loopback

gt2_loopback_in[2:0] in Async Determines the loopback mode.

GT2 Polarity

gt2_rxpolarity_in in clk156_out

gt2_txpolarity_in in clk156_out

The rxpolarity port can invert the polarity of incoming

data.

The txpolarity port can invert the polarity of outgoing

data.

GT2 RX Decision Feedback Equalizer (DFE)

(GTXE2 and GTHE2) RX datapath.

gt2_rxlpmen_in in Async

gt2_rxdfelpmreset_in in Async (GTXE2 and GTHE2) Reset for LPM and DFE datapath.

gt2_rxmonitorsel_in[1:0] in Reserved

gt2_rxmonitorout_out[6:0] out Async (GTXE2 and GTHE2) Monitor output.

0: DFE.

1: LPM.

(GTXE2 and GTHE2) Select signal for

gt2_rxmonitorout_out.

gt2_rxlpmreset_in in clk156_out

gt2_rxlpmhfhold_in in Async

gt2_rxlpmhfovrden_in in Async

gt2_rxlpmlfhold_in in Async

gt2_rxlpmlfovrden_in in Async

(GTPE2) This port is driven High and then deasserted to

start the LPM reset process.

(GTPE2) Determines whether the value of the

high-frequency boost is either held or adapted.

(GTPE2) Determines whether the high-frequency boost

is controlled by an attribute or a signal.

(GTPE2) Determines whether the value of the

low-frequency boost is either held or adapted.

(GTPE2) Determines whether the low-frequency boost

is controlled by an attribute or a signal.

GT2 TX Driver

gt2_txpostcursor_in[4:0] in Async Transmitter post-cursor TX post-emphasis control.

gt2_txprecursor_in[4:0] in Async Transmitter post-cursor TX pre-emphasis control.

gt2_txdiffctrl_in[3:0] in Async Driver Swing Control.

gt2_txinhibit_in in clk156_out When High, this signal blocks the transmission of data.

GT2 PRBS

gt2_rxprbscntreset_in in clk156_out Resets the PRBS error counter.

gt2_rxprbserr_out out clk156_out

This non-sticky status output indicates that PRBS

errors have occurred.

gt2_rxprbssel_in[2:0] in clk156_out Receiver PRBS checker test pattern control.

XAUI v12.3 Product Guide www.xilinx.com 24

PG053 April 6, 2016

Page 25

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

gt2_txprbssel_in[2:0] in clk156_out Transmitter PRBS generator test pattern control.

gt2_txprbsforceerr_in in clk156_out

Clock

Domain

Description

When this port is driven High, errors are forced in the

PRBS transmitter. While this port is asserted, the

output data pattern contains errors.

GT2 RX CDR

gt2_rxcdrhold_in in Async Hold the CDR control loop frozen.

GT2 Digital Monitor

gt2_dmonitorout_out[7:0] out Async (GTXE2) Digital Monitor Output Bus

gt2_dmonitorout_out[14:0] out Async (GTHE2) Digital Monitor Output Bus

gt2_dmonitorout_out[14:0] out Async (GTPE2) Digital Monitor Output Bus

GT2 Status

gt2_rxdisperr_out[3:0] out clk156_out

gt2_rxnotintable_out[3:0] out clk156_out

gt2_rxcommadet_out out clk156_out

Active-High indicates the corresponding byte of the

received data has a disparity error

Active-High indicates the corresponding byte of the

received data was not a valid character in the 8B/10B

table.

This signal is asserted when the comma alignment

block detects a comma.

CHANNEL 3

GT3 DRP

gt3_drpaddr[8:0] in dclk DRP address bus for channel 3.

DRP enable signal.

gt3_drpen in dclk

gt3_drpdi[15:0] in dclk

gt3_drpdo[15:0] out dclk

gt3_drprdy out dclk

gt3_drpwe in dclk

gt3_drp_busy out dclk

0: No read or write operation performed.

1: enables a read or write operation.

Data bus for writing configuration data to the

transceiver for channel 3.

Data bus for reading configuration data from the

transceiver for channel 3.

Indicates operation is complete for write operations

and data is valid for read operations for channel 3.

DRP write enable for channel 3.

0: Read operation when drpen is 1.

1: Write operation when drpen is 1.

(GTPE2 all configurations or GTHE2 10G

configuration). Indicates the DRP interface is being

used internally by the serial transceiver and should not

be driven until this signal is deasserted.

XAUI v12.3 Product Guide www.xilinx.com 25

PG053 April 6, 2016

Page 26

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

Clock

Domain

Description

GT3 TX Reset and Initialization

gt3_txpmareset_in in Async Starts the TX PMA reset process.

gt3_txpcsreset_in in Async Starts the TX PCS reset process.

gt3_txresetdone_out out clk156_out

When asserted the serial transceiver TX has finished

reset and is ready for use.

GT3 RX Reset and Initialization

gt3_rxpmareset_in in Async Starts the RX PMA reset process.

gt3_rxpcsreset_in in Async Starts the RX PCS reset process.

gt3_rxpmaresetdone_out out Async

gt3_rxresetdone_out out clk156_out

(GTHE2 and GTPE2) This active-High signal indicates

RX PMA reset is complete.

When asserted the serial transceiver RX has finished

reset and is ready for use.

GT3 Clocking

gt3_rxbufstatus_out[2:0] out clk156_out RX buffer status.

gt3_txphaligndone_out out Async TX phase alignment done.

gt3_txphinitdone_out out Async TX phase alignment initialization done.

gt3_txdlysresetdone_out out Async TX delay alignment soft reset done.

(GTHE2) This active-High PLL frequency lock signal

gt3_cplllock_out out Async

indicates that the PLL frequency is within

predetermined tolerance.

Signal Integrity and Functionality

GT3 Eye Scan

gt3_eyescantrigger_in in clk156_out Causes a trigger event.

gt3_eyescanreset_in in Async

gt3_eyescandataerror_out out Async

gt3_rxrate_in[2:0] in Reserved

This port is driven High and then deasserted to start

the EYESCAN reset process.

Asserts High for one rec_clk cycle when an (unmasked)

error occurs while in the COUNT or ARMED state.

This port dynamically controls the setting for the RX

serial clock divider.

GT3 Loopback

gt3_loopback_in[2:0] in Async Determines the loopback mode.

GT3 Polarity

gt3_rxpolarity_in in clk156_out

gt3_txpolarity_in in clk156_out

The rxpolarity port can invert the polarity of incoming

data.

The txpolarity port can invert the polarity of outgoing

data.

XAUI v12.3 Product Guide www.xilinx.com 26

PG053 April 6, 2016

Page 27

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

Clock

Domain

Description

GT3 RX Decision Feedback Equalizer (DFE)

gt3_rxlpmen_in in Async

gt3_rxdfelpmreset_in in Async (GTXE2 and GTHE2) Reset for LPM and DFE datapath.

gt3_rxmonitorsel_in[1:0] in Reserved

gt3_rxmonitorout_out[6:0] out Async (GTXE2 and GTHE2) Monitor output.

gt3_rxlpmreset_in in clk156_out

gt3_rxlpmhfhold_in in Async

gt3_rxlpmhfovrden_in in Async

gt3_rxlpmlfhold_in in Async

gt3_rxlpmlfovrden_in in Async

(GTXE2 and GTHE2) RX datapath.

0: DFE. 1: LPM.

(GTXE2 and GTHE2) Select signal for

gt3_rxmonitorout_out.

(GTPE2) This port is driven High and then deasserted to

start the LPM reset process.

(GTPE2) Determines whether the value of the

high-frequency boost is either held or adapted.

(GTPE2) Determines whether the high-frequency boost

is controlled by an attribute or a signal.

(GTPE2) Determines whether the value of the

low-frequency boost is either held or adapted.

(GTPE2) Determines whether the low-frequency boost

is controlled by an attribute or a signal.

GT3 TX Driver

gt3_txpostcursor_in[4:0] in Async Transmitter post-cursor TX post-emphasis control.

gt3_txprecursor_in[4:0] in Async Transmitter post-cursor TX pre-emphasis control.

gt3_txdiffctrl_in[3:0] in Async Driver Swing Control.

gt3_txinhibit_in in clk156_out When High, this signal blocks the transmission of data.

GT3 PRBS

gt3_rxprbscntreset_in in clk156_out Resets the PRBS error counter.

gt3_rxprbserr_out out clk156_out

gt3_rxprbssel_in[2:0] in clk156_out Receiver PRBS checker test pattern control.

gt3_txprbssel_in[2:0] in clk156_out Transmitter PRBS generator test pattern control.

gt3_txprbsforceerr_in in clk156_out

This non-sticky status output indicates that PRBS

errors have occurred.

When this port is driven High, errors are forced in the

PRBS transmitter. While this port is asserted, the

output data pattern contains errors.

GT3 RX CDR

gt3_rxcdrhold_in in Async Hold the CDR control loop frozen.

GT3 Digital Monitor

gt3_dmonitorout_out[7:0] out Async (GTXE2) Digital Monitor Output Bus

gt3_dmonitorout_out[14:0] out Async (GTHE2) Digital Monitor Output Bus

gt3_dmonitorout_out[14:0] out Async (GTPE2) Digital Monitor Output Bus

XAUI v12.3 Product Guide www.xilinx.com 27

PG053 April 6, 2016

Page 28

Chapter 2: Product Specification

Send Feedback

Table 2‐8: Transceiver Control and Status Ports —7 Series FPGAs (Cont’d)

Signal Name Direction

Clock

Domain

Description

GT3 Status

gt3_rxdisperr_out[3:0] out clk156_out

gt3_rxnotintable_out[3:0] out clk156_out

gt3_rxcommadet_out out clk156_out

Active-High indicates the corresponding byte of the

received data has a disparity error

Active-High indicates the corresponding byte of the

received data was not a valid character in the 8B/10B

table.

This signal is asserted when the comma alignment

block detects a comma.

Table 2‐9: Transceiver Control and Status Ports — UltraScale Architectures

Signal Name Direction

Clock

Domain

Description

GT0 DRP

gt0_drpaddr[8:0] in dclk DRP address bus for channel 0

DRP enable signal.

gt0_drpen in dclk

gt0_drpdi[15:0] in dclk

0: No read or write operation performed.

1: enables a read or write operation.

Data bus for writing configuration data to the transceiver

for channel 0.

gt0_drpdo[15:0] out dclk

gt0_drprdy out dclk

gt0_drpwe in dclk

Data bus for reading configuration data from the

transceiver for channel 0.

Indicates operation is complete for write operations and

data is valid for read operations for channel 0.

DRP write enable for channel 0.

0: Read operation when drpen is 1.

1: Write operation when drpen is 1.

GT1 DRP

gt1_drpaddr[8:0] in dclk DRP address bus for channel 1

DRP enable signal.

gt1_drpen in dclk

gt1_drpdi[15:0] in dclk

gt1_drpdo[15:0] out dclk

gt1_drprdy out dclk

0: No read or write operation performed.

1: enables a read or write operation.

Data bus for writing configuration data to the transceiver

for channel 1.

Data bus for reading configuration data from the

transceiver for channel 1.

Indicates operation is complete for write operations and

data is valid for read operations for channel 1.

XAUI v12.3 Product Guide www.xilinx.com 28

PG053 April 6, 2016

Page 29

Chapter 2: Product Specification

Send Feedback

Table 2‐9: Transceiver Control and Status Ports — UltraScale Architectures (Cont’d)

Signal Name Direction

gt1_drpwe in dclk

Clock

Domain

Description

DRP write enable for channel 1.

0: Read operation when drpen is 1.

1: Write operation when drpen is 1.

GT2 DRP

gt2_drpaddr[8:0] in dclk DRP address bus for channel 2

DRP enable signal.

gt2_drpen in dclk

gt2_drpdi[15:0] in dclk

gt2_drpdo[15:0] out dclk

gt2_drprdy out dclk

gt2_drpwe in dclk

0: No read or write operation performed.

1: enables a read or write operation.

Data bus for writing configuration data to the transceiver

for channel 2.

Data bus for reading configuration data from the

transceiver for channel 2.

Indicates operation is complete for write operations and

data is valid for read operations for channel 2.

DRP write enable for channel 2.

0: Read operation when drpen is 1.

1: Write operation when drpen is 1.

GT3 DRP

gt3_drpaddr[8:0] in dclk DRP address bus for channel 3

DRP enable signal.

gt3_drpen in dclk

gt3_drpdi[15:0] in dclk

gt3_drpdo[15:0] out dclk

gt3_drprdy out dclk

gt3_drpwe in dclk

0: No read or write operation performed.

1: enables a read or write operation.

Data bus for writing configuration data to the transceiver

for channel 3.

Data bus for reading configuration data from the

transceiver for channel 3.

Indicates operation is complete for write operations and

data is valid for read operations for channel 3.

DRP write enable for channel 3.

0: Read operation when drpen is 1.

1: Write operation when drpen is 1.

DRP Reset

Bits 2, 18, 34 and 50 are connected to port pcsrsvdin[2] of

gt_pcsrsvdin[63:0] in Async

GT lanes 0, 1, 2 and 3 respectively. See the appropriate

transceiver user guide for more details.

TX Reset and Initialization

gt_txpmareset[3:0] in Async Starts the TX PMA reset process.

gt_txpcsreset[3:0] in Async Starts the TX PCS reset process.

XAUI v12.3 Product Guide www.xilinx.com 29

PG053 April 6, 2016

Page 30

Chapter 2: Product Specification

Send Feedback

Table 2‐9: Transceiver Control and Status Ports — UltraScale Architectures (Cont’d)

Signal Name Direction

gt_txresetdone[3:0] out clk156_out

Clock

Domain

Description

When asserted the serial transceiver TX has finished reset

and is ready for use.

RX Reset and Initialization

gt_rxpmareset[3:0] in Async Starts the RX PMA reset process.

gt_rxpcsreset[3:0] in Async Starts the RX PCS reset process.

gt_rxpmaresetdone[3:0] out Async

gt_rxresetdone[3:0] out clk156_out

When asserted the serial transceiver RX has finished reset

and is ready for use.

Clocking

gt_rxbufstatus[11:0] out clk156_out RX buffer status.

gt_txphaligndone[3:0] out Async TX phase alignment done.

gt_txphinitdone[3:0] out Async TX phase alignment initialization done.

gt_txdlysresetdone[3:0] out Async TX delay alignment soft reset done.

gt_qplllock out Async

This active-High PLL frequency lock signal indicates that the

PLL frequency is within predetermined tolerance.

Signal Integrity and Functionality

Eye Scan

gt_eyescantrigger[3:0] in clk156_out Causes a trigger event.

gt_eyescanreset[3:0] in Async

gt_eyescandataerror[3:0] out Async

gt_rxrate[11:0] in clk156_out

This port is driven High and then deasserted to start the

EYESCAN reset process.

Asserts High for one rec_clk cycle when an (unmasked) error

occurs while in the COUNT or ARMED state.

This port dynamically controls the setting for the RX serial

clock divider.

Loopback

gt_loopback[11:0] in Async Determines the loopback mode.

Polarity

gt_rxpolarity[3:0] in clk156_out The rxpolarity port can invert the polarity of incoming data.

gt_txpolarity[3:0] in clk156_out The txpolarity port can invert the polarity of outgoing data.

RX Decision Feedback Equalizer (DFE)

RX datapath.

gt_rxlpmen[3:0] in Async

gt_rxdfelpmreset[3:0] in Async Reset for LPM and DFE datapath.

0: DFE.

1: LPM.

gt_txpostcursor[19:0] in Async Transmitter post-cursor TX post-emphasis control.

XAUI v12.3 Product Guide www.xilinx.com 30

PG053 April 6, 2016

TX Driver

Page 31

Chapter 2: Product Specification

Send Feedback

Table 2‐9: Transceiver Control and Status Ports — UltraScale Architectures (Cont’d)

Signal Name Direction

gt_txprecursor[19:0] in Async Transmitter post-cursor TX pre-emphasis control.

gt_txdiffctrl[19:0 or 15:0] in Async

gt_txinhibit3:0] in clk156_out When High, this signal blocks the transmission of data.

Clock

Domain

Description

Driver Swing Control. The bus size is 20 bits for GTYE3 and

16 bits for GTHE3.

PRBS

gt_rxprbscntreset[3:0] in clk156_out Resets the PRBS error counter.

gt_rxprbserr[3:0] out clk156_out

gt_rxprbssel[15:0] in clk156_out Receiver PRBS checker test pattern control.

gt_txprbssel[15:0] in clk156_out Transmitter PRBS generator test pattern control.

gt_txprbsforceerr[3:0] in clk156_out

This non-sticky status output indicates that PRBS errors

have occurred.

When this port is driven High, errors are forced in the PRBS

transmitter. While this port is asserted, the output data

pattern contains errors.

RX CDR

gt_rxcdrhold[3:0] in Async Hold the CDR control loop frozen.

Digital Monitor

gt_dmonitorout[67:0] out Async Digital Monitor Output Bus

Status

gt_rxdisperr[7:0] out clk156_out

gt_rxnotintable[7:0] out clk156_out

gt_rxcommadet[3:0] out clk156_out

If you are migrating from a 7 series to an UltraScale device, the prefixes of the optional transceiver debug ports for

single-lane cores are changed from “gt0”, “gt1” to “gt”, and the suffix “_in” and “_out” are dropped. For multi-lane

cores, the prefixes of the optional transceiver debug ports gt(n) are aggregated into a single port. See Device Migration

for more information.

Active-High indicates the corresponding byte of the

received data has a disparity error.

Active-High indicates the corresponding byte of the

received data was not a valid character in the 8B/10B table.

This signal is asserted when the comma alignment block

detects a comma.

MDIO Interface

The MDIO Interface signals are shown in Table 2-10. More information on using this

interface can be found in Chapter 5, Interfacing to the Core.

Table 2‐10: MDIO Management Interface Ports

Signal Name Direction

Clock

Domain

Description

mdc in Async Management clock

mdio_in in Async MDIO input

XAUI v12.3 Product Guide www.xilinx.com 31

PG053 April 6, 2016

Page 32

Table 2‐10: MDIO Management Interface Ports (Cont’d)

Send Feedback

Chapter 2: Product Specification

Signal Name Direction

mdio_out out clk156_out MDIO output

mdio_tri out clk156_out

type_sel[1:0] in Tie-off Type select

prtad[4:0] in Tie-off

Clock

Domain

Description

MDIO 3-state; ‘1’ disconnects the output driver from the MDIO

bus.

MDIO port address; you should set this to provide a unique ID

on the MDIO bus.

Configuration and Status Signals

The Configuration and Status Signals are shown in Table 2-11. See Configuration and Status

Interfaces for more information on these signals, including a breakdown of the

configuration and status vectors.

Table 2‐11: Configuration and Status Ports

Signal Name Direction

configuration_ vector[6:0] in clk156_out Configuration information for the core.

status_vector[7:0] out clk156_out Status information from the core.

Clock

Domain

Description

debug[5] out clk156_out

debug[4:1] out clk156_out

debug[0] out clk156_out

align_status: 1 when the XAUI receiver is

aligned across all four lanes, 0 otherwise.

sync_status: Each pin is 1 when the respective

XAUI lane receiver is synchronized to byte

boundaries, 0 otherwise.

Indicates when the TX phase alignment of the

transceiver has been completed.

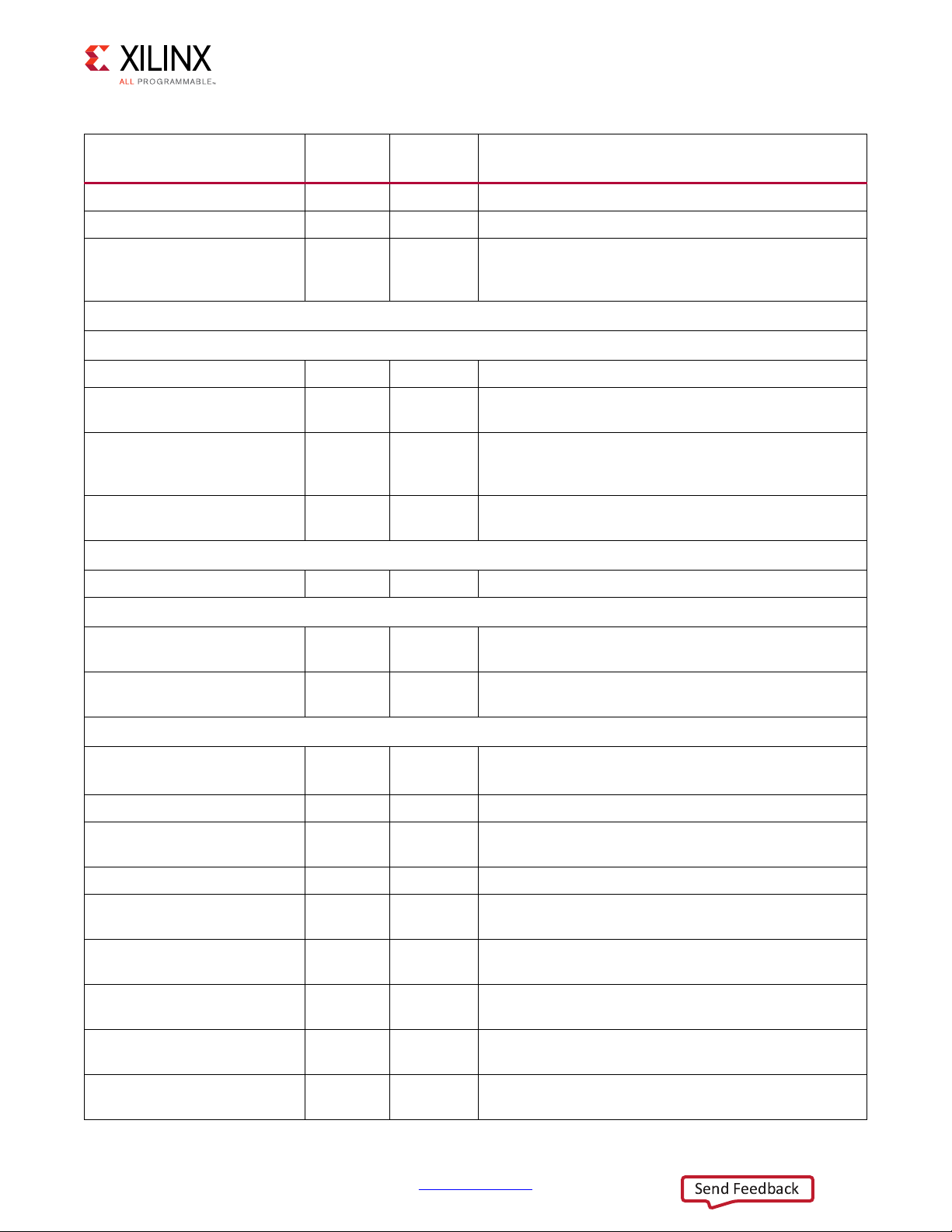

Clocking and Reset Signals and Module

Included in the example design top-level sources are circuits for clock and reset

management. These can include Digital Clock Managers (DCMs), Mixed-Mode Clock

Managers (MMCMs), reset synchronizers, or other useful utility circuits that might be useful

in your particular application.

XAUI v12.3 Product Guide www.xilinx.com 32

PG053 April 6, 2016

Page 33

Chapter 2: Product Specification

Send Feedback

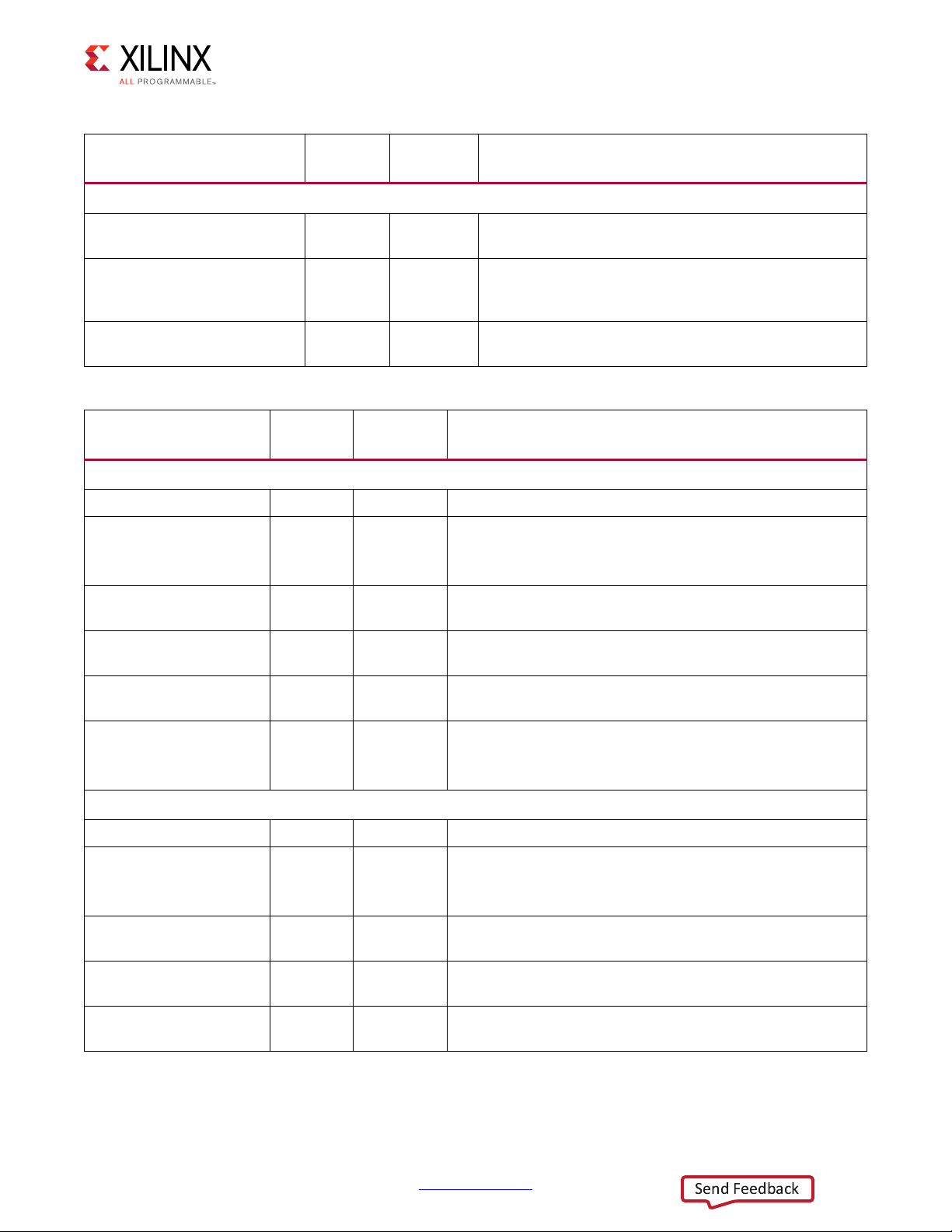

Table 2-12 shows the ports that are associated with system clocks and resets.

Table 2‐12: Clock and Reset Ports with Shared Logic in the Example Design

Signal Name Direction Description

Clock used as the DRP clock, and also as a stable reference clock for the

detection of the feedback and reference clock signals to the QPLL. The

dclk in

input reference clock to the QPLL or any output clock generated from

the QPLL (for example, TXOUTCLK) must not be used to drive this clock.

For UltraScale devices, this clock is also used in the internal state

machines for the configuration of the transceiver.

refclk_p/refclk_n in

refclk in

clk156_out out

clk156_lock out

reset in Asynchronous external reset

Transceiver differential reference clock to the core when shared logic is

included in the core.

Transceiver reference clock to the core when shared logic is included in

the example design.

System clock for the encrypted HDL logic and for the device-specific

transceiver logic ports. This clock must have a frequency of 156.25 MHz

for 10G XAUI operation. 312.5 MHz for 20G XAUI operation.

This active-High PLL frequency lock signal indicates that the PLL

frequency is within predetermined tolerance. The transceiver and its

clock outputs are not reliable until this condition is met.

Table 2-13 shows the ports that are associated with system clocks and resets.

Table 2‐13: Clock and Reset Ports with Shared Logic in Core

Signal Name Direction Description

Clock used as the DRP clock, and also as a stable reference clock for the

detection of the feedback and reference clock signals to the QPLL. The

dclk in

input reference clock to the QPLL or any output clock generated from

the QPLL (for example, TXOUTCLK) must not be used to drive this clock.

For UltraScale devices this clock is also used in the internal state

machines for the configuration of the transceiver.

XAUI v12.3 Product Guide www.xilinx.com 33

PG053 April 6, 2016

refclk_p in Differential transceiver reference clock “p.”

refclk_n in Differential transceiver reference clock “n.”

System clock for the encrypted HDL logic and for the device-specific

clk156_out out

clk156_lock out

reset in Asynchronous external reset

transceiver logic ports. This clock must have a frequency of 156.25 MHz

for 10G XAUI operation. 312.5 MHz for 20G XAUI operation.

This active-High PLL frequency lock signal indicates that the PLL

frequency is within predetermined tolerance. The transceiver and its

clock outputs are not reliable until this condition is met.

Page 34

Chapter 2: Product Specification

Send Feedback

Register Space

MDIO Management Registers

The XAUI core, when generated with an MDIO interface, implements an MDIO Interface

Register block. The core responds to MDIO transactions as either a 10GBASE-X PCS, a DTE

XS, or a PHY XS depending on the setting of the type_sel port (see Table 2-10).

10GBASE-X PCS/PMA Register Map

When the core is configured as a 10GBASE-X Physical Coding Sublayer/Physical Medium

Attachment (PCS/PMA), it occupies MDIO Device Addresses 1 and 3 in the MDIO register

address map, as shown in Table 2-14.

Table 2‐14: 10GBASE-X PCS/PMA MDIO Registers

Register Address Register Name

1.0

1.1 PMA/PMD Status 1

1.2,1.3 PMA/PMD Device Identifier

1.4 PMA/PMD Speed Ability

1.5, 1.6 PMA/PMD Devices in Package

1.7 10G PMA/PMD Control 2

1.8 10G PMA/PMD Status 2

1.9 Reserved

1.10 10G PMD Receive Signal OK

1.11 TO 1.13 Reserved

1.14, 1.15 PMA/PMD Package Identifier

1.16 to 1.65 535 Reserved

3.0 PCS Control 1

3.1 PCS Status 1

3.2, 3.3 PCS Device Identifier

3.4 PCS Speed Ability

Physical Medium Attachment/Physical Medium Dependent (PMA/PMD)

Control 1

XAUI v12.3 Product Guide www.xilinx.com 34

PG053 April 6, 2016

3.5, 3.6 PCS Devices in Package

3.7 10G PCS Control 2

3.8 10G PCS Status 2

3.9 to 3.13 Reserved

3.14, 3.15 Package Identifier

Page 35

Table 2‐14: 10GBASE-X PCS/PMA MDIO Registers (Cont’d)

RESET

RSVD

RSVD

RSVD

RSVD

POWER DOWN

LOOPBACK

SPEED

SPEED

SPEED

15 14 13 12 11 10 7 6 5 2 1 0

Reg 1.0

X13682

Send Feedback

Register Address Register Name

3.16 to 3.23 Reserved

3.24 10GBASE-X PCS Status

3.25 10GBASE-X Test Control

3.26 to 3.65 535 Reserved

MDIO Register 1.0: PMA/PMD Control 1

Figure 2-1 shows the MDIO Register 1.0: PMA/PMD Control 1.

X-Ref Target - Figure 2-1

Chapter 2: Product Specification

Figure 2‐1: PMA/PMD Control 1 Register

Table 2-15 shows the PMA Control 1 register bit definitions.

Table 2‐15: PMA/PMD Control 1 Register Bit Definitions

Bit Name Description Attributes

1 = Block reset

0 = Normal operation

1.0.15 Reset

1.0.14 Reserved

1.0.13

Speed

Selection

1.0.12 Reserved

1.0.11

Power

down

The XAUI block is reset when this bit is set to 1. It

returns to 0 when the reset is complete. The

soft_reset pin is connected to this bit. This can be

connected to the reset of any other MMDs.

The block always returns 0 for this bit and ignores

writes.

The block always returns 1 for this bit and ignores

writes.

The block always returns 0 for this bit and ignores

writes.

1 = Power down mode

0 = Normal operation

When set to 1, the serial transceivers are placed in

a low-power state. Set to 0 to return to normal

operation

R/W

Self-clearing

R/O 0

R/O 1

R/O 0

R/W 0

Default

Value

0

The block always returns 0 for these bits and

ignores writes.

R/O All 0s

1.0.10:7 Reserved

XAUI v12.3 Product Guide www.xilinx.com 35

PG053 April 6, 2016

Page 36

Table 2‐15: PMA/PMD Control 1 Register Bit Definitions (Cont’d)

RSVD

RSVD

RSVD

LOCAL FAULT

POWERDOWN ABILITY

RX LINK STATUS

15 876 3210

Reg 1.1

X13683

Send Feedback

Chapter 2: Product Specification

Bit Name Description Attributes

1.0.6

1.0.5:2

Speed

Selection

Speed

Selection

1.0.1 Reserved

1.0.0 Loopback

The block always returns 1 for this bit and ignores

writes.

The block always returns 0s for these bits and

ignores writes.

The block always returns 0 for this bit and ignores

writes.

1 = Enable loopback mode

0 = Disable loopback mode

The XAUI block loops the signal in the serial

transceivers back into the receiver.

R/O 1

R/O All 0s

R/O All 0s

R/W 0

MDIO Register 1.1: PMA/PMD Status 1

Figure 2-2 shows the MDIO Register 1.1: PMA/PMD Status 1.

X-Ref Target - Figure 2-2

Default

Value

Table 2-16 shows the PMA/PMD Status 1 register bit definitions.

Table 2‐16: PMA/PMD Status 1 Register Bit Definitions

Bit Name Description Attributes

1.1.15:8 Reserved The block always returns 0 for this bit. R/O 0

1.1.7 Local Fault The block always returns 0 for this bit. R/O 0

1.1.6:3 Reserved The block always returns 0 for this bit. R/O 0

1.1.2

1.1.1

1.1.0 Reserved The block always returns 0 for this bit. R/O 0

Receive Link

Status

Power Down

Ability

Figure 2‐2: PMA/PMD Status 1 Register

The block always returns 1 for this bit. R/O 1

The block always returns 1 for this bit. R/O 1

Default

Val ue

XAUI v12.3 Product Guide www.xilinx.com 36

PG053 April 6, 2016

Page 37

Chapter 2: Product Specification

PMA/PMD

IDENTIFIER

15 0

Reg 1.2

PMA/PMD

IDENTIFIER

15

0

Reg 1.3

X13684

RSVD

10G CAPABLE

15 0

Reg 1.4

X13685

Send Feedback

MDIO Registers 1.2 and 1.3: PMA/PMD Device Identifier

Figure 2-3 shows the MDIO Registers 1.2 and 1.3: PMA/PMD Device Identifier.

X-Ref Target - Figure 2-3

Figure 2‐3: PMA/PMD Device Identifier Registers

Table 2-17 shows the PMA/PMD Device Identifier registers bit definitions.

Table 2‐17: PMA/PMD Device Identifier Registers Bit Definitions

Bit Name Description Attributes

1.2.15:0

1.3.15:0

PMA/PMD

Identifier

PMA/PMD

Identifier

The block always returns 0 for these bits and

ignores writes.

The block always returns 0 for these bits and

ignores writes.

R/O All 0s

R/O All 0s

MDIO Register 1.4: PMA/PMD Speed Ability

Figure 2-4 shows the MDIO Register 1.4: PMA/PMD Speed Ability.

X-Ref Target - Figure 2-4

Figure 2‐4: PMA/PMD Speed Ability Register

Default

Val ue

XAUI v12.3 Product Guide www.xilinx.com 37

PG053 April 6, 2016

Page 38

Chapter 2: Product Specification

VENDOR2 PRESENT

VENDOR1 PRESENT

RSVD

15 14 13 0

Reg 1.6

RSVD

DTE XS PRESENT

PHY XS PRESENT

PCS PRESENT

WIS PRESENT

PMD/PMA PRESENT

CLAUSE 22 PRESENT

15

01

23456

Reg 1.5

X13686

Send Feedback

Table 2-18 shows the PMA/PMD Speed Ability register bit definitions.

Table 2‐18: PMA/PMD Speed Ability Register Bit Definitions

Bit Name Description Attribute Default Value

1.4.15:1 Reserved

1.4.0 10G Capable

The block always returns 0 for these bits

and ignores writes.

The block always returns 1 for this bit

and ignores writes.

R/O All 0s

R/O 1

MDIO Registers 1.5 and 1.6: PMA/PMD Devices in Package

Figure 2-5 shows the MDIO Registers 1.5 and 1.6: PMA/PMD devices in package.

X-Ref Target - Figure 2-5

Figure 2‐5: PMA/PMD Devices in Package Registers

Table 2-19 shows the PMA/PMD Device in Package registers bit definitions.

Table 2‐19: PMA/PMD Devices in Package Registers Bit Definitions

Bit Name Description Attributes

1.6.15

1.6.14

1.6.13:0 Reserved

1.5.15:6 Reserved

Vendor- specific

Device 2 Present

Vendor-specific

Device 1 Present

The block always returns 0 for this bit. R/O 0

The block always returns 0 for this bit. R/O 0

The block always returns 0 for these

bits.

The block always returns 0 for these

bits.

R/O All 0s

R/O All 0s

Default

Value

XAUI v12.3 Product Guide www.xilinx.com 38

PG053 April 6, 2016

Page 39

Chapter 2: Product Specification

RSVD

PMA/PMD TYPE SELECTION

15 0

23

Reg 1.7

X13687

Send Feedback

Table 2‐19: PMA/PMD Devices in Package Registers Bit Definitions (Cont’d)

Bit Name Description Attributes

DTE Extender

1.5.5

1.5.4 PHY XS Present The block always returns 0 for this bit. R/O 0

1.5.3 PCS Present The block always returns 1 for this bit. R/O 1

1.5.2 WIS Present The block always returns 0 for this bit. R/O 0

1.5.1 PMA/PMD Present The block always returns 1 for this bit. R/O 1

1.5.0

Sublayer (XS)

Present

Clause 22 Device

Present

The block always returns 0 for this bit. R/O 0

The block always returns 0 for this bit. R/O 0

MDIO Register 1.7: 10G PMA/PMD Control 2

Figure 2-6 shows the MDIO Register 1.7: 10G PMA/PMD Control 2.

X-Ref Target - Figure 2-6

Default

Value

Figure 2‐6: 10G PMA/PMD Control 2 Register

Table 2-20 shows the PMA/PMD control 2 register bit definitions.

Table 2‐20: 10G PMA/PMD Control 2 Register Bit Definitions

Bit Name Description Attributes

1.7.15:3 Reserved

1.7.2:0

PMA/PMD Type

Selection

The block always returns 0 for these bits

and ignores writes.

The block always returns 100 for these

bits and ignores writes. This corresponds

to the 10GBASE-X PMA/PMD.

R/O All 0s

R/O 100

Default

Value

XAUI v12.3 Product Guide www.xilinx.com 39

PG053 April 6, 2016

Page 40

Chapter 2: Product Specification

DEVICE PRESENT

TX FAULT ABILITY

RX FAULT ABILITY

TX FAULT

RX FAULT

RSVD

PMD TX DISABLE ABILITY

10GBASE-SR ABILITY

10GBASE-LR ABILITY

10GBASE-ER ABILITY

10GBASE-SW ABILITY

10GBASE-LW ABILITY

10GBASE-EW ABILITY

PMA LOOPBACK ABILITY

10GBASE-LX4 ABILITY

15 14 587613 12 11 10 9 243 10

Reg 1.8

X13688

Send Feedback

MDIO Register 1.8: 10G PMA/PMD Status 2

Figure 2-7 shows the MDIO Register 1.8: 10G PMA/PMD Status 2.

X-Ref Target - Figure 2-7

Figure 2‐7: 10G PMA/PMD Status 2 Register

Table 2-21 shows the PMA/PMD status 2 register bit definitions.

Table 2‐21: 10G PMA/PMD Status 2 Register Bit Definitions

Bit Name Description Attributes Default Value

1.8.15:14 Device Present

1.8.13

1.8.12

Transmit Local

Fault Ability

Receive Local

Fault Ability

1.8.11 Transmit Fault

1.8.10 Receive Fault

1.8.9 Reserved

1.8.8

1.8.7

1.8.6

1.8.5

PMD Transmit

Disable Ability

10GBASE-SR

Ability

10GBASE-LR

Ability

10GBASE-ER

Ability

The block always returns 10 for

these bits.

The block always returns 0 for this

bit.

The block always returns 0 for this

bit.

The block always returns 0 for this

bit.

The block always returns 0 for this

bit.

The block always returns 0 for this

bit.

The block always returns 0 for this

bit.

The block always returns 0 for this

bit.

The block always returns 0 for this

bit.

The block always returns 0 for this

bit.

R/O 10

R/O 0

R/O 0