Page 1

Virtex-6 FPGA

www.BDTIC.com/XILINX

System Monitor

User Guide

UG370 (v1.1) June 14, 2010

Page 2

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development

www.BDTIC.com/XILINX

of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the

Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise,

without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves

the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors

contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with

technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER

WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY

RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL

DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2009–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx

in the United States and other countries. All other trademarks are the property of their respective owners.

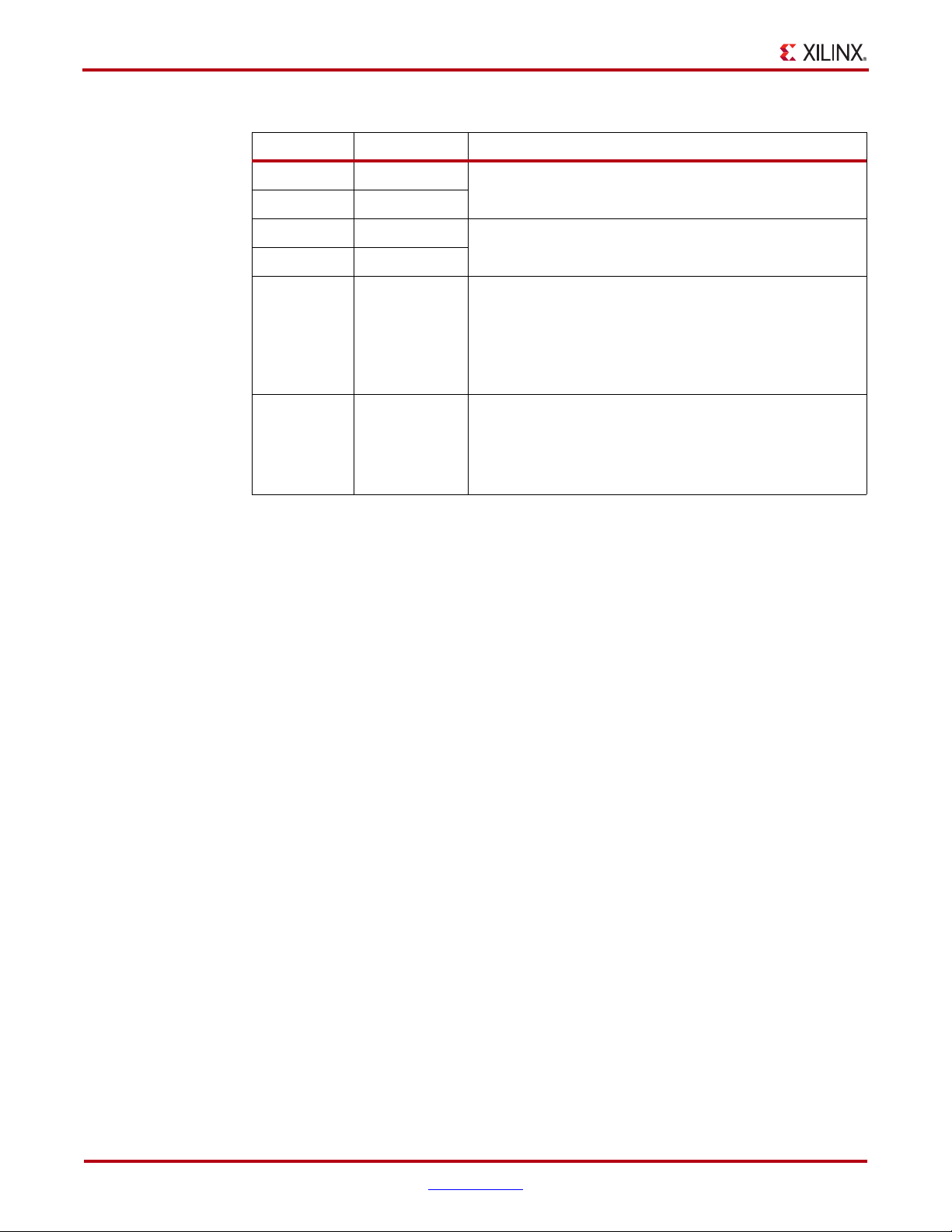

Revision History

The following table shows the revision history for this document.

Version Revision

06/24/09 1.0 Initial Xilinx release.

06/14/10 1.1 Updated V

with MAX6018.

values in Tab le 7 , Ta bl e 13 ,and Tab le 1 5. In Figure 24, replaced MAX6120

REFP

Virtex-6 FPGA System Monitor www.xilinx.com UG370 (v1.1) June 14, 2010

Page 3

Table of Contents

www.BDTIC.com/XILINX

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Preface: About This Guide

Additional Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Additional Support Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Virtex-6 FPGA System Monitor

System Monitor Primitive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

System Monitor Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

User Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Pre-Configuration Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Analog-to-Digital Converter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Temperature Sensor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Power Supply Sensor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Register File Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Flag Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Configuration Registers (40h to 42h). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Test Registers (43h to 47h). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Channel Sequencer Registers (48h to 4Fh). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Alarm Registers (50h to 57h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

DRP JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

System Monitor DRP JTAG Write Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

System Monitor JTAG DRP Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

JTAG DRP Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

DRP Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

JTAGBUSY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

JTAGMODIFIED. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

JTAGLOCKED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

System Monitor Control Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Channel Sequencer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

ADC Channel Selection (48h and 49h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

ADC Channel Averaging (4Ah and 4Bh) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

ADC Channel Analog-Input Mode (4Ch and 4Dh). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

ADC Channel Acquisition Time (4Eh and 4Fh) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Maximum and Minimum Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Automatic Alarms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Supply Sensor Alarms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Thermal Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Thermal Diode (DXP and DXN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

System Monitor Calibration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Calibration Coefficients. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Calibration Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

System Monitor Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Virtex-6 FPGA System Monitor www.xilinx.com 3

UG370 (v1.1) June 14, 2010

Page 4

Continuous Sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

www.BDTIC.com/XILINX

Acquisition Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Conversion Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Event-Driven Sampling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Analog Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Auxiliary Analog Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Adjusting the Acquisition Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Analog Input Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Unipolar Input Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Bipolar Input Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Application Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Reference Inputs (VREFP and VREFN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Analog Power Supply and Ground (AVDD and AVSS) . . . . . . . . . . . . . . . . . . . . . . . . 45

External Analog Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Anti-Alias Filters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

PC Board Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Example Instantiation of SYSMON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

SYSMON I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

SYSMON Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Simulation of the SYSMON Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

EDK Support for System Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

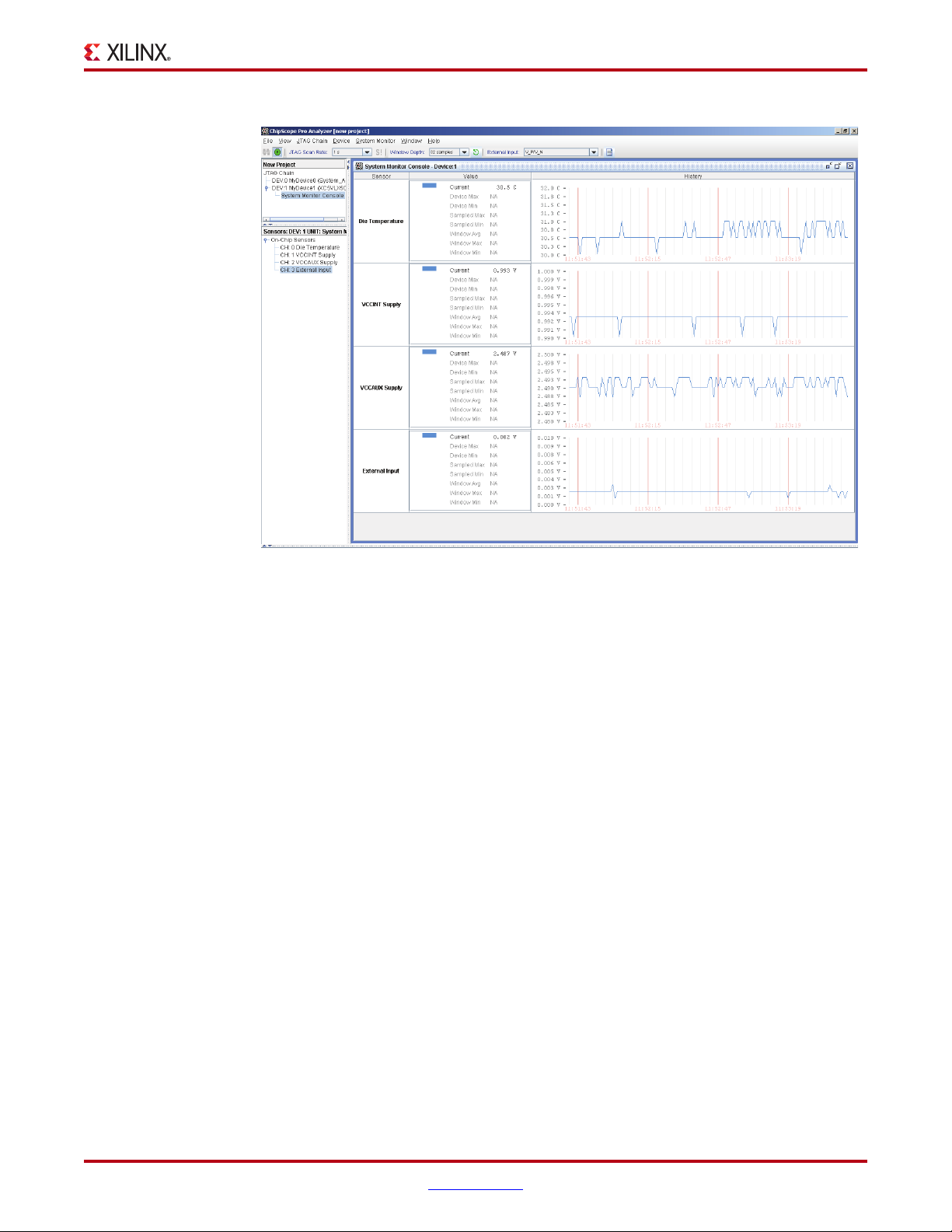

ChipScope Pro Tool and System Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

4 www.xilinx.com Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Page 5

About This Guide

www.BDTIC.com/XILINX

This user guide describes the features and functionalities of the Virtex®-6 FPGA

System Monitor. Complete and up-to-date documentation of the Virtex-6 family of FPGAs

is available on the Xilinx website.

Additional Documentation

The following documents are also available for download at

http://www.xilinx.com/support/documentation/virtex-6.htm

• Virtex-6 Family Overview

The features and product selection of the Virtex-6 family are outlined in this overview.

• Virtex-6 FPGA Data Sheet: DC and Switching Characteristics

This data sheet contains the DC and Switching Characteristic specifications for the

Virtex-6 family.

Preface

.

• Virtex-6 FPGA Packaging and Pinout Specifications

This specification includes the tables for device/package combinations and maximum

I/Os, pin definitions, pinout tables, pinout diagrams, mechanical drawings, and

thermal specifications.

• Virtex-6 FPGA Configuration Guide

This all-encompassing configuration guide includes chapters on configuration

interfaces (serial and SelectMAP), bitstream encryption, boundary-scan and JTAG

configuration, reconfiguration techniques, and readback through the SelectMAP and

JTAG interfaces.

• Virtex-6 FPGA SelectIO Resources User Guide

This guide describes the SelectIO™ resources available in all Virtex-6 devices.

• Virtex-6 FPGA Clocking Resources User Guide

This guide describes the clocking resources available in all Virtex-6 devices, including

the MMCM and PLLs.

• Virtex-6 FPGA Memory Resources User Guide

The functionality of the block RAM and FIFO are described in this user guide.

• Virtex-6 FPGA Configurable Logic Blocks User Guide

This guide describes the capabilities of the configurable logic blocks (CLBs) available

in all Virtex-6 devices.

Virtex-6 FPGA System Monitor www.xilinx.com 5

UG370 (v1.1) June 14, 2010

Page 6

Preface: About This Guide

www.BDTIC.com/XILINX

• Virtex-6 FPGA GTH Transceivers User Guide

This guide describes the GTH transceivers available in all Virtex-6 HXT FPGAs except

the XC6VHX250T and the XC6VHX380T in the FF1154 package.

• Virtex-6 FPGA GTX Transceivers User Guide

This guide describes the GTX transceivers available in all Virtex-6 FPGAs except the

XC6VLX760.

• Virtex-6 FPGA Embedded Tri-Mode Ethernet MAC User Guide

This guide describes the dedicated Tri-Mode Ethernet Media Access Controller

available in all Virtex-6 FPGAs except the XC6VLX760.

• Virtex-6 FPGA DSP48E1 Slice User Guide

This guide describes the architecture of the DSP48E1 slice in Virtex-6 FPGAs and

provides configuration examples.

• Virtex-6 FPGA PCB Design Guide

This guide provides information on PCB design for Virtex-6 devices, with a focus on

strategies for making design decisions at the PCB and interface level.

Additional Support Resources

To search the database of silicon and software questions and answers or to create a

technical support case in WebCase, see the Xilinx website at:

http://www.xilinx.com/support

For the most up to date support information including software updates, reference

designs, tutorials, and FAQs please got to:

http://www.xilinx.com/systemmonitor

.

6 www.xilinx.com Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Page 7

Virtex-6 FPGA System Monitor

MUX

17 External

Analog Inputs

(Measurement Results)

External

Reference Inputs

FPGA Logic Port

On-chip

Sensors

On-chip

1.25V

Reference

ADC

10-bit/ 200kSPS

On-chip Sensors for

Power Supplies and

Temperature Monitoring

Status Registers

DRP

Arbitrator

JTAG Port

Alarms

UG370_01_060709

System Monitor

Control Registers

(User Defined Operation)

www.BDTIC.com/XILINX

Every member of the Virtex®-6 FPGA family contains a single System Monitor, which is

located in the center of every die. The System Monitor function is built around a 10-bit,

200-kSPS (kilosamples per second) Analog-to-Digital Converter (ADC). When combined

with a number of on-chip sensors, the ADC is used to measure FPGA physical operating

parameters like on-chip power supply voltages and die temperatures. Access to external

voltages is provided through a dedicated analog-input pair (V

selectable analog inputs, known as auxiliary analog inputs (V

The external analog inputs allow the ADC to monitor the physical environment of the

board or enclosure. System Monitor is fully functional on power up, and measurement

data can be accessed via the JTAG port pre-configuration.

Figure 1 shows the System Monitor block diagram. The System Monitor control logic

implements some common monitoring features. For example, an automatic channel

sequencer allows a user-defined selection of parameters to be automatically monitored,

and user-programmable averaging is enabled to ensure robust noise-free measurements.

System Monitor also provides user-programmable alarm thresholds for the on-chip

sensors. Thus, if an on-chip monitored parameter moves outside the user-specified

operating range, an alarm logic output becomes active.

X-Ref Target - Figure 1

P/VN

AUXP

) and 16 user-

[15:0], V

AUXN

[15:0]).

Virtex-6 FPGA System Monitor www.xilinx.com 7

UG370 (v1.1) June 14, 2010

Figure 1: System Monitor Simplified Block Diagram

A register-file-based interface allows easy access to the measured data and the System

Monitor control registers. The measured values for both on-chip sensors and external

channels are available after End of Conversion (EOC) or End of Sequence (EOS) is asserted

High at the end of an ADC conversion (see System Monitor Timing, page 33). The output

Page 8

System Monitor Primitive

www.BDTIC.com/XILINX

data registers also store the maximum and minimum measurements for each of the on-chip

sensors recorded since power up or the last user reset.

In addition to monitoring the on-chip temperature for user-defined applications, System

Monitor issues a special alarm called Over-Temperature (OT) if the FPGA temperature

exceeds a user specified temperature e.g., 100°C. By default the over temperature limit is

set to 125°C. The over-temperature signal is deactivated when the device temperature falls

below a user-specified lower limit. If the FPGA power down feature is enabled, the FPGA

enters power down when the OT signal becomes active. The FPGA powers up again when

the alarm is deactivated (see Automatic Alarms, page 29).

All System Monitor features are customizable at run time through the Dynamic

Reconfiguration Port (DRP) and the System Monitor control registers. These control

registers can also be initialized at design time when System Monitor is instantiated in a

design (see Register File Interface, page 14). For the latest information, including FAQs,

software updates, and tutorials, refer to http://www.xilinx.com/systemmonitor

System Monitor Primitive

System Monitor Ports

.

Figure 2 illustrates the ports on the primitive (SYSMON) used to instantiate System

Monitor in a design. A description of the ports is given in Ta bl e 1.

X-Ref Target - Figure 2

SYSMON

DO[15:0]

DI[15:0]

Dynamic

Reconfiguration Port

(DRP)

CONTROL

and CLOCK

External

Analog

Inputs

DADDR[6:0]

DEN

DWE

DCLK

DRDY

RESET

CONVST

CONVSTCLK

VP

VN

VAUXP[15:0]

VAUXN[15:0]

ALM[2:0]

OT

CHANNEL[4:0]

EOC

EOS

BUSY

JTAGLOCKED

JTAGMODIFIED

JTAGBUSY

ALARMS

STATUS

8 www.xilinx.com Virtex-6 FPGA System Monitor

UG370_02_060709

Figure 2: System Monitor Ports

UG370 (v1.1) June 14, 2010

Page 9

Table 1: System Monitor I/O

www.BDTIC.com/XILINX

Port I/O Description

DI[15:0] Inputs Input data bus for the dynamic reconfiguration port.

DO[15:0] Outputs Output data bus for dynamic reconfiguration port.

DADDR[6:0] Input Address bus for the dynamic reconfiguration port.

(1)

DEN

DWE

(1)

Input Enable signal for the dynamic reconfiguration port.

Input Write enable for the dynamic reconfiguration port.

DCLK Input Clock input for the dynamic reconfiguration port.

(1)

DRDY

(1)

RESET

CONVST

(3)

Output Data ready signal for the dynamic reconfiguration port.

Input Reset signal for the System Monitor control logic.

Input Convert start input. This input is used to control the sampling instant on the ADC input

and is only used in Event Mode Timing (see Event-Driven Sampling, page 36). This

input comes from the general-purpose interconnect in the FPGA logic.

CONVSTCLK

(3)

Input Convert start input. This input is connected to a global clock input. Like CONVST, this

input is used to control the sampling instant on the ADC inputs and is only used in

Event Mode Timing. This input comes from the local clock distribution network in the

FPGA logic. Thus for the best control over the sampling instant (delay and jitter), a

global clock input can be used as the CONVST source.

System Monitor Primitive

(2)

(2)

(2)

(2)

(2)

(2)

V

, V

P

N

Input One dedicated analog-input pair. System Monitor has one pair of dedicated analog-

input pins that provide a differential analog input. When designing with the System

V

AUXP

V

AUXN

[15:0],

[15:0]

Monitor feature, but not using the dedicated external channel of V

should connect both V

Inputs Sixteen auxiliary analog

input, System Monitor uses 16 differential digital

and VN to the analog ground.

P

-input pairs. In addition to the dedicated differential analog

-input pairs as low-bandwidth

and VN, the user

P

differential analog inputs. These inputs are configured as analog during FPGA

configuration. These inputs can also be enabled pre-configuration via the JTAG port.

See DRP JTAG Interface, page 21 and Auxiliary Analog Inputs, page 40.

ALM[0]

ALM[1]

ALM[2]

(1)

(1)

(1)

Output System Monitor temperature-sensor alarm output.

Output System Monitor V

Output System Monitor V

-sensor alarm output.

CCINT

-sensor alarm output.

CCAUX

OT Output Over-Temperature alarm output.

CHANNEL[4:0] Outputs Channel selection outputs. The ADC input MUX channel selection for the current ADC

conversion is placed on these outputs at the end of an ADC conversion.

(1)

EOC

Output End of Conversion signal. This signal transitions to an active High at the end of an ADC

conversion when the measurement is written to the status registers (see System Monitor

Timing, page 33).

(1)

EOS

Output End of Sequence. This signal transitions to an active High when the measurement data

from the last channel in the auto sequence is written to the status registers (see System

Monitor Timing, page 33).

(1)

BUSY

Output ADC busy signal. This signal transitions High during an ADC conversion. This signal

also transitions High for an extended period during an ADC or Supply Sensor

calibration.

Virtex-6 FPGA System Monitor www.xilinx.com 9

UG370 (v1.1) June 14, 2010

Page 10

Pre-Configuration Operation

www.BDTIC.com/XILINX

Table 1: System Monitor I/O (Cont’d)

Port I/O Description

(1)

(1)

Output Used to indicate that a DRP port lock request has been made by the Joint Test Action

Group (JTAG) interface (see DRP Arbitration, page 24).

(1)

Output Used to indicate that a JTAG Write to the DRP has occurred.

Output Used to indicate that a JTAG DRP transaction is in progress.

JTAGLOCKED

JTAGMODIFIED

JTAGBUSY

Notes:

1. Active-High signal.

2. For some details on the timing for these DRP signals, consult Figure 16, page 38 and Table 19, page 39 or Chapter 5 (Dynamic

Reconfiguration Port) in the Virtex-6 FPGA Configuration Guide.

3. Rising edge triggered signal.

User Attributes

System Monitor functionality is configured by the Control registers (see Register File

Interface, page 14). These Control registers can be initialized at design, using the Attributes

listed in Ta bl e 2 and through the DRP at run time (see Control Registers, page 17).

Table 2: System Monitor Attributes

Control

Attribute Name

INIT_40 Configuration register 0 40h

INIT_41 Configuration register 1 41h

INIT_42 Configuration register 2 42h

INIT_43 to

INIT_47

INIT_48 to

INIT_4F

INIT_50 to

INIT_57

Test r e gi st er s 43h to 47h System Monitor Test registers for factory use only. The default

Sequence registers 48h to 4Fh Sequence registers used to program the Channel Sequencer

Alarm Limit registers 50h to 57h Alarm threshold registers for the System Monitor alarm function

Register

Address

Pre-Configuration Operation

System Monitor starts operating in a safe mode of operation shortly after the FPGA is

powered-up without performing a configuration.

Note:

Monitor is available as soon as the Clear Configuration Memory step is complete, which is normally

indicated by INIT_B going High. See the “Configuration Sequence” section in the Virtex-6 FPGA

Configuration Guide for more information.

Holding INIT_B or PROG Low to delay configuration has no effect on System Monitor. System

Description

System Monitor configuration registers (see Configuration

Registers (40h to 42h), page 17).

initialization is 0000h.

function in System Monitor (see Channel Sequencer, page 25).

(see Automatic Alarms, page 29).

In this mode of operation, System Monitor operates in a sequence mode (see Channel

Sequencer, page 25

), monitoring the on-chip sensors: temperature, V

When operating in safe mode, System Monitor is not affected by any change in the FPGA’s

configuration. System Monitor operates in safe mode prior to any configuration and

during configuration (full and partial). It is possible to customize the System Monitor

operation pre-configuration using the JTAG TAP. However, System Monitor only operates

in safe mode during configuration and the contents of the System Monitor control registers

10 www.xilinx.com Virtex-6 FPGA System Monitor

, and V

CCINT

UG370 (v1.1) June 14, 2010

CCAUX

.

Page 11

are overwritten when a full chip configuration is carried out. To enable auxiliary analog

000

001

003

004

3FF

Output Code

Full Scale

Transition

3FE

3FD

002

123 999

Full Scale Input = 1V

1 LSB = 1V / 1024 = 977 μV

10-Bit Output Code (Hex)

UG370_03_060709

Input Voltage (mV)

www.BDTIC.com/XILINX

input channels during preconfiguration, see DRP JTAG Interface, page 21.

Because no system clock is available, System Monitor uses an internal clock oscillator

pre-configuration. The full functionality of System Monitor is accessed pre-configuration

through the JTAG Test Access Port (JTAG TAP) (see DRP JTAG Interface, page 21).

The JTAG interface provides full Read/Write access to the System Monitor register file

interface. After power-up, the System Monitor functionality is customized, if required,

through the JTAG TAP. The System Monitor functionality is also available through the

JTAG TAP post configuration even if System Monitor has not been instantiated in a design.

It is possible to access the System Monitor registers at any time using the JTAG TAP.

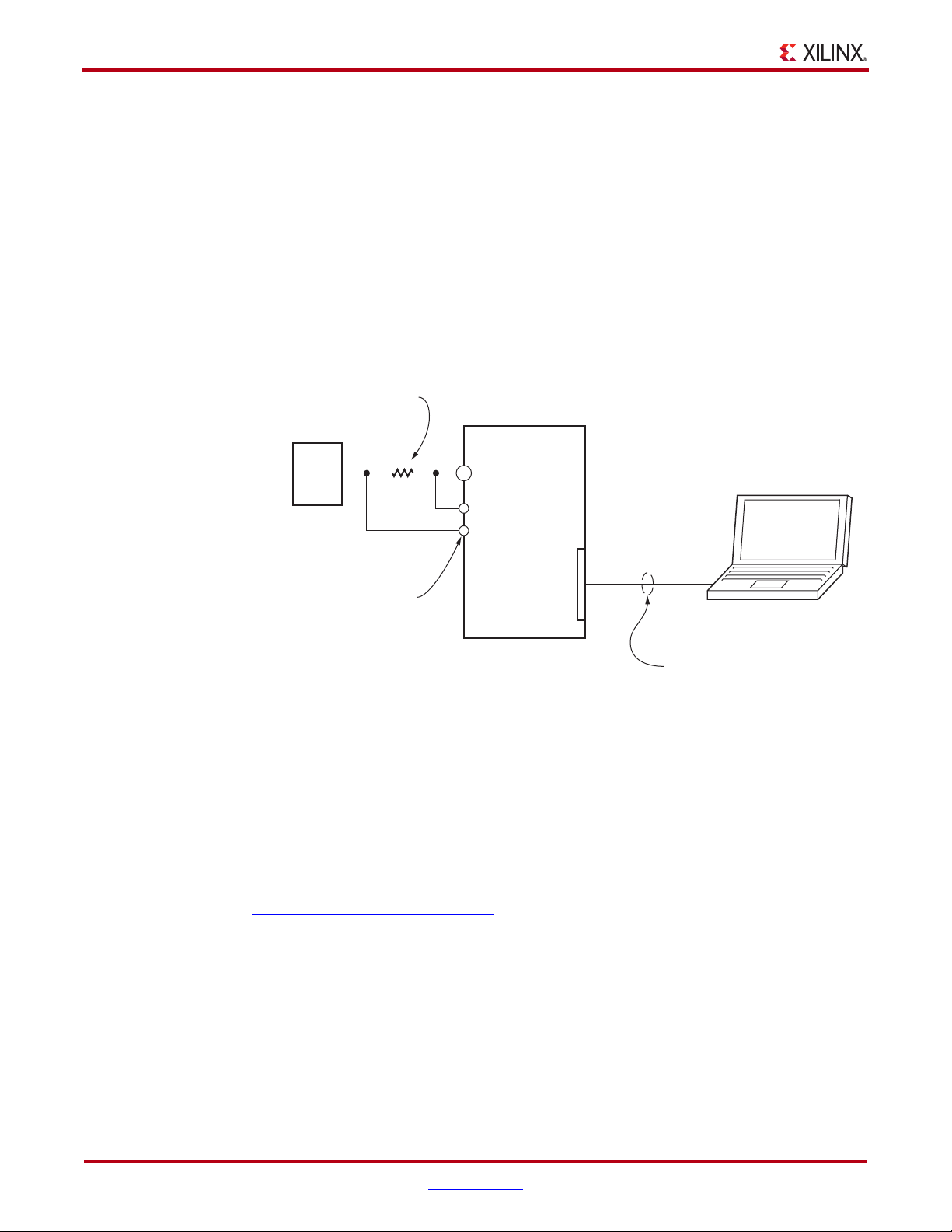

The basic connection requirements that ensure the System Monitor functionality is enabled

are shown in Figure 4. For more information regarding power supply requirements, see

Application Guidelines, page 45.

Analog-to-Digital Converter

The ADC is used to digitize the output of the on-chip sensors and voltages connected to

the external analog inputs. The ADC specifications are listed in the Virtex-6 FPGA Data

Sheet.

Analog-to-Digital Converter

The System Monitor ADC carries out a 16-bit resolution conversion of all sensor and

external analog input voltages. However, only 10-bit performance is specified and

guaranteed in the Virtex-6 FPGA Data Sheet. These additional conversion bits are accessable

to improve the resolution of a measurement on an external channel. A more detailed

discussion can be found in Application Guidelines, page 45. Since the ADC has a specified

performance of 10-bits and to simplify the discussion, a 10-bit transfer function is used in

this guide to illustrate operation.

The 10-bit full scale output code of 3FFh is produced when a 1V differential voltage is

placed on an external analog input (see Figure 3).

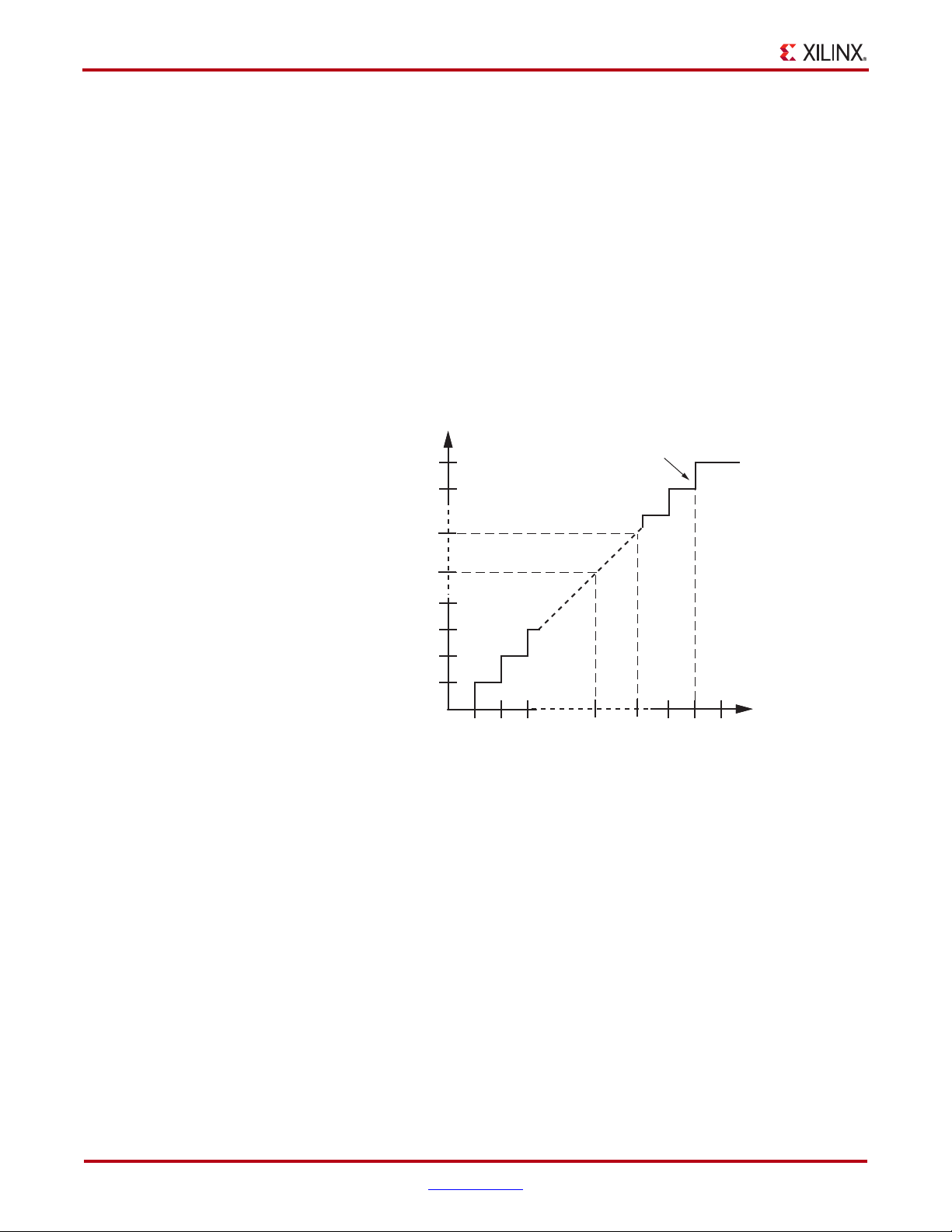

X-Ref Target - Figure 3

Virtex-6 FPGA System Monitor www.xilinx.com 11

UG370 (v1.1) June 14, 2010

Figure 3: ADC Transfer Function

Page 12

Analog-to-Digital Converter

ADC

1.25V ±0.2%

50 ppm/°C

2.5V – 5V

AV

DD

AV

SS

V

REFP

V

P

V

N

V

REFN

V

CCAUX

(2.5V ±5%)

V

CCAUX

(2.5V ±5%)

UG370_04_061009

External Reference

ADC

AV

DD

AV

SS

V

REFP

V

P

V

N

V

REFN

On-Chip Reference

GND

Ferrite for HF noise isolation

10nF 10nF

GND

Ferrite for HF noise isolation

Package Pins

10nF

www.BDTIC.com/XILINX

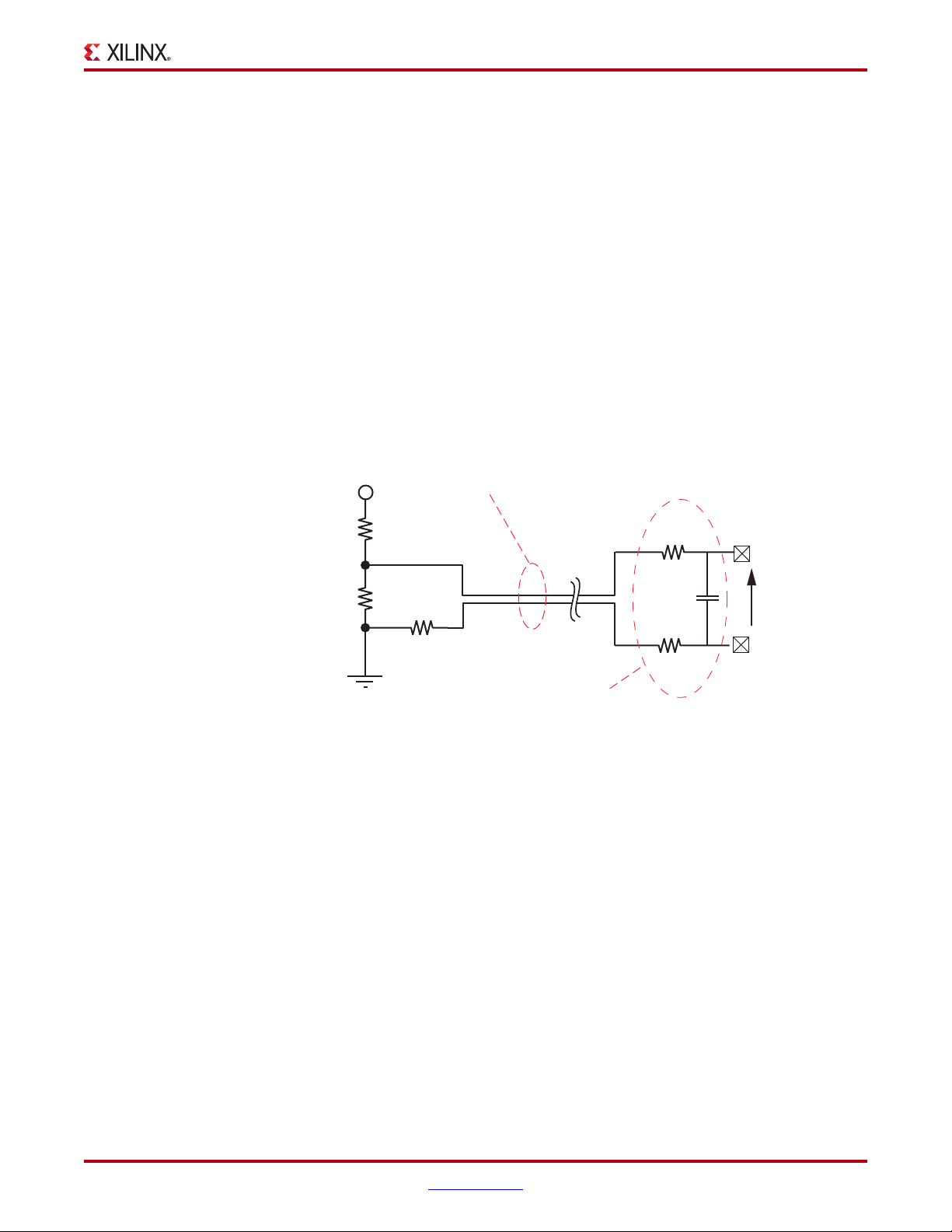

The System Monitor ADC has six dedicated pins (see Figure 4). Two of these pins provide

a dedicated high-bandwidth, differential analog-input channel (V

pins are used to access an external reference voltage (V

reference device, a reference voltage with a low-temperature coefficient (< 50 ppm/°C) can

be supplied. This voltage is used to provide stable and accurate measurements over a wide

temperature range. An internal reference circuit can also be selected by connecting V

and V

a wide temperature range than an external reference. Performance using the internal

reference circuit is specified in the Virtex-6 FPGA Data Sheet. For the most accurate

measurements, an external reference IC is recommended.

, VN). Another two

P

, V

REFP

to analog ground (AGND). This internal reference is typically less accurate over

REFP

). By using an external

REFN

REFN

X-Ref Target - Figure 4

The remaining analog pins (AV

and AVSS) are used to decouple the power supply for

DD

the ADC analog circuits and provide a local AGND return for the ADC circuitry. The

System Monitor connection diagrams (using the on-chip and external reference) are shown

in Figure 4. For a more detailed discussion of required power supply connections and PC

Board layout, see Application Guidelines, page 45.

Figure 4: System Monitor Dedicated Pins

In addition to on-chip sensors, the ADC is used to digitize external analog signals. There is

one dedicated analog-input pin pair and 16 user-programmable analog-input pairs

supplied for this purpose. The ADC has a true differential-sampling analog-input scheme,

allowing the ADC to achieve a high degree of accuracy when digitizing both on-chip and

external channels.

The ADC accommodates both unipolar and bipolar analog input signals (see Analog

Inputs, page 39). The analog-input mode is selected by writing to the System Monitor

configuration registers (see Configuration Registers (40h to 42h), page 17). In Single

Channel mode, the configuration registers are also used to select the sampling modes of

the ADC and the analog input channels such as, on-chip sensors and external analog-input

channels.

12 www.xilinx.com Virtex-6 FPGA System Monitor

Temperature Sensor

System Monitor contains a temperature sensor that produces a voltage output that is

proportional to the die temperature.

Equation 1 shows the output voltage of the temperature sensor.

UG370 (v1.1) June 14, 2010

Page 13

Analog-to-Digital Converter

Voltage 10

kT()

q

-----------

10()ln××=

Temperature °C()

ADCcode 503.975×

1024

-------------------------------------------------- -

273.15–=

000h

001h

003h

004h

3FFh

10-bit Output Code

Full Scale

Transition

3FEh

3FDh

002h

102 3 605

10231022

Temperature (°C)

+230.5°C

+24.76°C

-273°C

-272.5°C

-272°C

-271.5°C

1LSB ≅ 0.49°C

UG370_05_060709

www.BDTIC.com/XILINX

Equation 1

Where:

k = Boltzman’s constant = 1.38 x 10

-23

T = Temperature K (Kelvin) = °C + 273.1

-19

q = Charge on an electron = 1.6 x 10

C

The output voltage of this sensor is digitized by the ADC to produce a 10-bit digital output

code (ADC code). Figure 5 illustrates the digital output transfer function for this

temperature sensor.

For simplification, the temperature sensor plus the ADC transfer function is rewritten in

Equation 2.

Equation 2

System Monitor also provides a digital averaging function that allows a user to average up

to 256 individual temperature-sensor measurements to produce a reading (see ADC

Channel Averaging (4Ah and 4Bh), page 27). Averaging the sensor measurements helps

generate a noise-free and repeatable measurement. The result of a temperature reading is

placed in the output data registers at address 00h on the DRP (see Register File Interface,

page 14). The full ADC transfer function describes temperatures outside the FPGA

operating temperature range. This does not mean that the FPGA is operational at these

temperatures (refer to Virtex-6 FPGA Data Sheet for temperature specifications). System

Monitor is operational over a temperature range of –40°C to +125°C on all parts

irrespective of grade.

X-Ref Target - Figure 5

Virtex-6 FPGA System Monitor www.xilinx.com 13

UG370 (v1.1) June 14, 2010

The on-chip temperature sensor has a maximum-measurement error of ±4°C over a range

of –40°C to +125°C. Monitoring FPGA on-chip temperature avoids functional and

irreversible failures by ensuring critical operating temperatures are not exceeded.

Figure 5: Ideal Temperature Sensor Transfer Function

Page 14

Register File Interface

www.BDTIC.com/XILINX

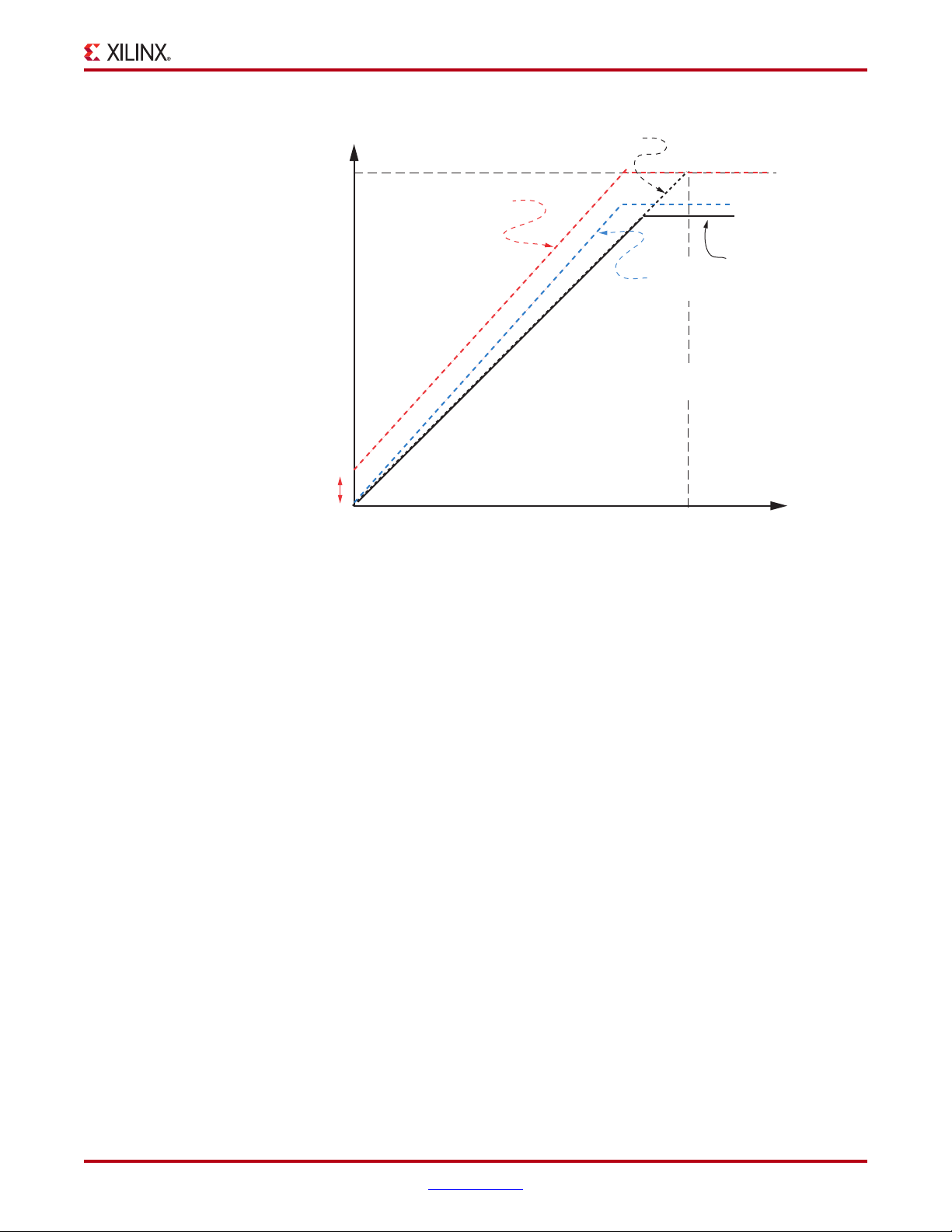

Power Supply Sensor

System Monitor also includes on-chip sensors allowing a user to monitor the FPGA powersupply voltages using the ADC. The sensors sample and attenuate (by a factor of three) the

power supply voltages V

shows the power-supply sensor transfer function after digitizing by the ADC. The Power

Supply sensor can be used to measure voltages in the range 0V to V

resolution of approximately 3 mV:

Supply Voltage (Volts) = (ADC Code / 1024) x 3V Equation 3

Similar to the temperature sensor, System Monitor provides a digital-averaging function

for the power supply measurements. Thus, up to 256 measurements of a sensor output are

used to generate a single reading. The power-supply measurement results for V

V

Status Registers, page 15).

X-Ref Target - Figure 6

are stored in the data registers at DRP addresses 01h and 02h, respectively (see

CCAUX

Output Code

CCINT

and V

on the package power supply balls. Figure 6

CCAUX

CCAUX

+5% with a

and

CCINT

Register File Interface

3FFh

3FEh

355h

155h

004h

003h

002h

10-Bit Output Code

001h

000h

Figure 6: Ideal Power Supply Transfer Function

1 LSB = 2.93 mV

2.93 mV

5.86 mV

8.79 mV

Supply Voltage (Volts)

Full Scale

Transition

1.00V

2.50V

2.997V

2.994V

UG370_06_060709

Figure 7 illustrates the System Monitor register file interface. All registers in the register

file interface are accessible through the DRP. The DRP can be accessed via a fabric port or

the JTAG TAP. Access is governed by an arbitrator (see DRP Arbitration, page 24). The

DRP allows the user to access up to 128 16-bit registers (DADDR[6:0] = 00h to 7Fh) from

the FPGA logic. The first 64 access locations (DADDR[6:0] = 00h to 3Fh) are read-only and

contain the status registers (see Status Registers). The Control registers are located at

addresses 40h to 7Fh (see Control Registers, page 17) and are readable or writable via the

DRP. The DRP timing is shown in Figure 16, page 38. For a detailed description of the DRP

timing please refer to the Virtex-6 FPGA Configuration Guide. For more information on the

JTAG DRP interface, see DRP JTAG Interface, page 21.

14 www.xilinx.com Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Page 15

X-Ref Target - Figure 7

DI[15:0]

DO[15:0]

DADDR[6:0]

DCLK

JTAGBUSY

JTAGLOCKED

JTAGMODIFIED

DWE

DEN

DRDY

Config Reg. #0 (40h)

Config Reg. #1 (41h)

Config Reg. #2 (42h)

Test Reg. #1 (44h)

Test Reg. #0 (43h)

Test Reg. #4 (47h)

Test Reg. #2 (45h)

Test Reg. #3 (46h)

Alarm Reg. #0 (50h)

Alarm Reg. #1 (51h)

Alarm Reg. #2 (52h)

Alarm Reg. #4 (54h)

Alarm Reg. #3 (53h)

Alarm Reg. #7 (57h)

Alarm Reg. #5 (55h)

Alarm Reg. #6 (56h)

Undefined (58h)

Undefined (59h)

Undefined (5Ah)

Undefined (7Fh)

Undefined (7Dh)

Undefined (7Eh)

Sequence Reg. #0 (48h)

Sequence Reg. #1 (49h)

Sequence Reg. #2 (4Ah)

Sequence Reg. #4 (4Ch)

Sequence Reg. #3 (4Bh)

Sequence Reg. #7 (4Fh)

Sequence Reg. #5 (4Dh)

Sequence Reg. #6 (4Eh)

Temp (00h)

Vccint (01h)

Vccaux (02h)

VP/VN (03h)

Undefined (0Fh)

VAUXP[1]/VAUXN[1] (11h)

V

CCINT

Max (21h)

V

CCAUX

Max (22h)

Undefined (23h)

Temp Max (20h)

V

CCINT

Min (25h)

V

CCAUX

Min (26h)

Undefined (27h)

Temp Min (24h)

VAUXP[0]/VAUXN[0] (10h)

Undefined (0Eh)

Undefined (0Dh)

Control Registers (40h–7Fh)

Read & WriteRead Only

Status Registers (00h–3Fh)

Dynamic Reconfiguration Port - JTAG Arbitrator

Undefined (28h)

Undefined (29h)

Undefined (2Ah)

Flag (3Fh)

Undefined (3Eh)

Undefined (3Dh)

VAUXP[13]/VAUXN[13] (1Dh)

VAUXP[12]/VAUXN[12] (1Ch)

VAUXP[14]/VAUXN[14] (1Eh)

VAUXP[15]/VAUXN[15] (1Fh)

DRP

JTAG TAP

Controller

UG370_07_060709

www.BDTIC.com/XILINX

Register File Interface

Status Registers

The first 64 address locations (DADDR[6:0] = 00h to 3Fh) contain the status registers that

are Read-Only and cannot be initialized when System Monitor is instantiated in a design.

The status registers contain the results of an analog-to-digital conversion of the on-chip

sensors and external channels. All sensors and external analog-input channels have a

unique channel address (see Tabl e 7, pa ge 1 9). The measurement result from each channel

is stored in a status register with the same address on the DRP.

For example, the result from an Analog-to-Digital Conversion on ADC multiplexer

channel 0 (temperature sensor) is stored in the Status Register at address 00h. The result

from ADC mux channel 1 (V

The status registers also store the maximum and minimum measurements recorded for the

on-chip sensors from the chip power-up or the last user reset of the System Monitor logic.

See Tab le 3 for a list of the status registers and definitions.

Figure 7: System Monitor Register Interface

) is stored at address 01h.

CCINT

Virtex-6 FPGA System Monitor www.xilinx.com 15

UG370 (v1.1) June 14, 2010

Page 16

Register File Interface

www.BDTIC.com/XILINX

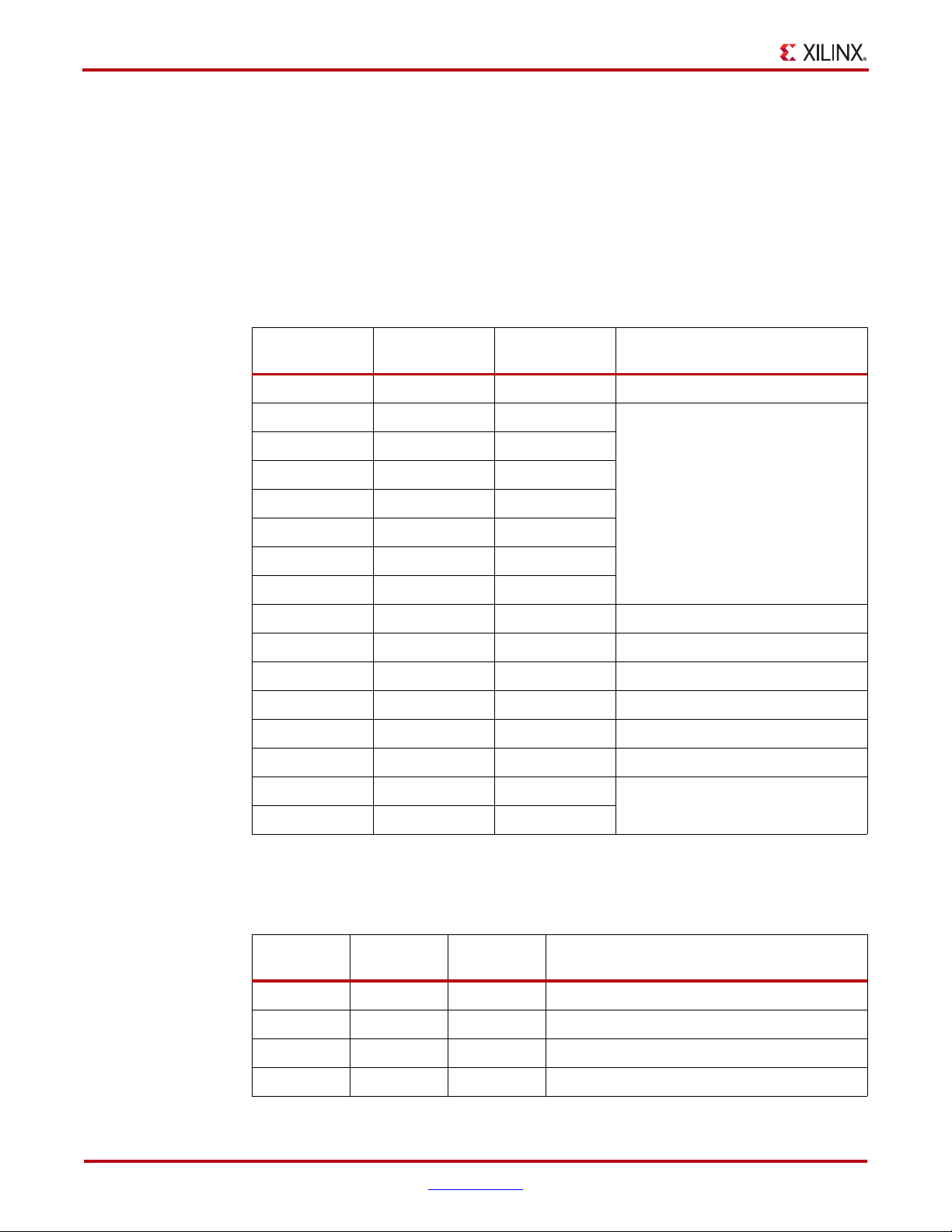

Table 3: Status Registers (Read-Only)

Name Address Description

Temperature 00h The result of the on

data is MSB justified in the 16

-chip temperature sensor measurement is stored in this location. The

-bit register. The ten MSBs correspond to the temperature

sensor transfer function shown in Figure 5, page 13.

V

01h The result of the on-chip V

CCINT

The data is MSB justified in the 16

supply monitor measurement is stored at this location.

CCINT

-bit register. The 10 MSBs correspond to the supply

sensor transfer function shown in Figure 6.

V

CCAUX

02h The result of the on-chip V

location. The data is MSB justified in the 16

Data supply monitor measurement is stored at this

CCAUX

-bit register. The ten MSBs correspond to the

supply sensor transfer function shown in Figure 6.

V

P/VN

03h The result of a conversion on the dedicated analog input channel is stored in this register.

The ten MSBs correspond to the ADC transfer functions shown in Figure 20, page 43 or

Figure 23, page 44 depending on the ADC input configuration.

V

REFP

04h The result of a conversion on the reference input V

REFP

10 MSBs correspond to the ADC transfer function shown in Figure 6. The supply sensor

is used when measuring V

.This channel is also used during a calibration (see System

REFP

Monitor Calibration, page 31).

V

REFN

05h The result of a conversion on the reference input V

REFP

10 MSBs correspond to the ADC transfer function shown in Figure 6. The supply sensor

is used when measuring V

. This channel is also used during a calibration (see System

REFP

Monitor Calibration, page 31).

Undefined 06h to 07h These locations are unused and contain invalid data.

is stored in this register. The

is stored in this register. The

Supply Offset 08h The calibration coefficient for the supply sensor offset is stored at this location

(see System

Monitor Calibration, page 31).

ADC Offset 09h The calibration coefficient for the ADC offset calibration is stored at this location

System Monitor Calibration, page 31).

Undefined 0Ah to 0Fh These locations are unused and contain invalid data.

V

AUXP

V

AUXN

[15:0]/

[15:0]

10h to 1Fh The results of 10

these locations. The data is MSB justified in the 16

Max Temp 20h Maximum temperature measurement recorded since power

10

-bit data MSB justified.

Max V

Max V

CCINT

CCAUX

21h Maximum V

10

-bit data MSB justified.

22h Maximum V

10

-bit data MSB justified.

-bit A/D conversions on the auxiliary analog inputs 0 to 15 are stored at

-bit register

-up or the last SYSMON reset.

measurement recorded since power-up or the last SYSMON reset.

CCINT

measurement recorded since power-up or the last SYSMON reset.

CCAUX

Undefined 23h This location contains invalid data.

Min Temp 24h Minimum temperature measurement recorded since power

10

-bit data MSB justified.

Min V

Min V

CCINT

CCAUX

25h Minimum V

10

-bit data MSB justified.

26h Minimum V

10

-bit data MSB justified.

measurement recorded since power-up or the last SYSMON reset.

CCINT

measurement recorded since power-up or the last SYSMON reset.

CCAUX

-up or the SYSMON reset.

(see

16 www.xilinx.com Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Page 17

Table 3: Status Registers (Read-Only) (Cont’d)

Flag Register

DADDR [6:0] = 3Fh

DI0DI1DI2DI3DI4DI5DI6DI7DI8DI9DI10DI11DI12DI13DI14DI15

XOTDIS X X XXXXX X REFXX

X

X

UG370_08_060709

www.BDTIC.com/XILINX

Name Address Description

Undefined 27h to 3Eh These locations are unused and contain invalid data.

Flag 3Fh This register contains general status information - see Figure 8.

Flag Register

The Flag Register is shown in Figure 8. The bit definitions are described in Ta bl e 4.

X-Ref Target - Figure 8

Figure 8: Flag Register

Table 4: Flag Register Definitions

Name Description

Register File Interface

OT This bit reflects the status of the Over Temperature logic output

DIS When this bit is a logic 1, the System Monitor is disabled by connecting the supplies and reference

inputs to AGND.

REF When this bit is a logic 1, the System Monitor ADC is using the internal voltage reference. When it is

a logic 0, then the external reference is being used.

Control Registers

The System Monitor control registers (Ta b le 5 ) are located at addresses 40h to 7Fh. These

registers are used to configure the System Monitor operation. System Monitor

functionality (ADC operating modes, Channel Sequencer, and Alarm limits) is controlled

through these registers. System Monitor functionality is explained in System Monitor

Control Logic, page 25.

The control registers are initialized using the SYSMON attributes when System Monitor is

instantiated in a design. This means that System Monitor can be configured to start in a

predefined mode after FPGA configuration.

Configuration Registers (40h to 42h)

The first three registers in the control register block are used to configure the System

Monitor operating modes. These registers are known as System Monitor configuration

registers. The configuration registers bit definitions are illustrated in Figure 9. The Xs in

Figure 9 define these bit positions as don’t cares. Bits 0, 1, and 2 in configuration register 2

(42h) should always be set to 0.

The configuration registers are modifiable through the DRP after the FPGA has been

configured. For example, a soft microprocessor or state machine can be used to alter the

contents of the System Monitor control registers at any time during normal operation.

Virtex-6 FPGA System Monitor www.xilinx.com 17

UG370 (v1.1) June 14, 2010

Page 18

Register File Interface

www.BDTIC.com/XILINX

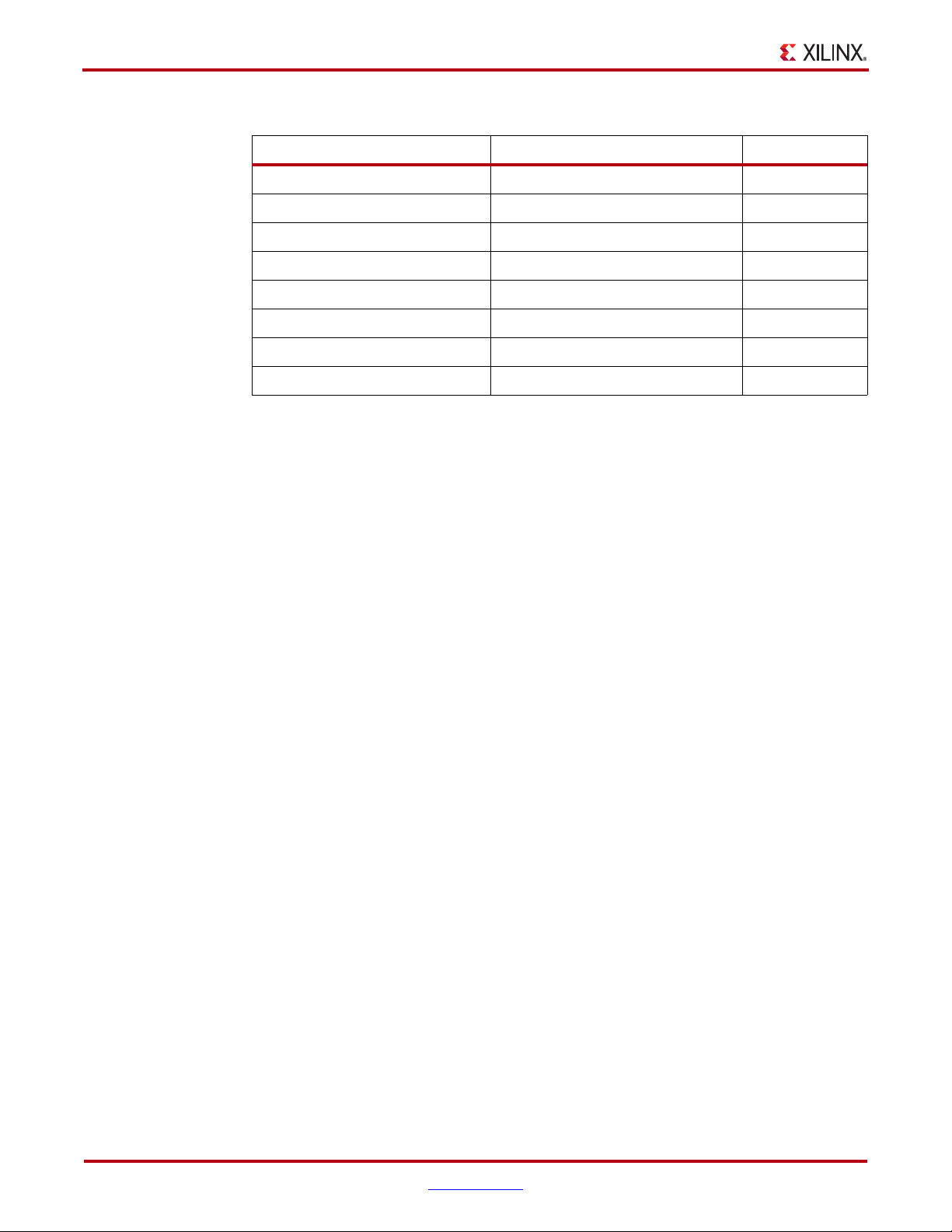

Table 5: Control Registers (Read and Write)

Name Address SW Attribute Description

Configuration register 0 40h INIT_40

Configuration register 1 41h INIT_41

Configuration register 2 42h INIT_42

These are System Monitor configuration registers (see

Figure 9).

Test registers 0 to 4 43h to 47h INIT_43 to

INIT_47

These are System Monitor Test registers. The default

initialization is 0000h. These registers are used for

factory test and should be left at the default

initialization.

Sequence registers 48h to 4Fh INIT_48 to

INIT_4F

These registers are used to program the Channel

Sequencer function in System Monitor (see Channel

Sequencer, page 25).

Alarm registers 50h to 57h INIT_50 to

INIT_57

These are the alarm threshold registers for the System

Monitor alarm function (see Automatic Alarms,

page 29).

Undefined 58h to 7Fh no attribute Do not read or write these registers.

X-Ref Target - Figure 9

DI0DI1DI2DI3DI4DI5DI6DI7DI8DI9DI10DI11DI12DI13DI14DI15

CH4 CH3 CH2 CH1 CH0ACQ X XXXXCAVG AVG1 AVG 0 BU EC

DI12DI13DI14DI15

SEQ1 SEQ0

DI12DI13DI14DI15

XXXXXX

CD3CD4CD5CD6CD7 X X

CD0 0 0CD1CD2 XXX0

CAL0CAL1CAL2CAL3

DI0DI1DI2DI3DI4DI5DI6DI7DI8DI9DI10DI11

ALM0ALM1ALM2 OT

DI0DI1DI2DI3DI4DI5DI6DI7DI8DI9DI10DI11

Config Reg #0

DADDR [6:0] = 40h

Config Reg #1

DADDR [6:0] = 41h

Config Reg #2

DADDR [6:0] = 42h

UG370_09_060809

Figure 9: Configuration Register Bit Definitions

Ta bl e 6 describes the bit-position functionality in configuration registers 0 to 2.

Table 6: Configuration Bit Definitions

Name Description

CH0 to CH4 When operating in Single Channel mode, these bits are used to select the ADC input channel (refer

to Channel Sequencer, page 25 for more details). This channel could be an internal voltage or an

external (off

-chip) transducer. Ta bl e 7 shows the channel assignments.

ACQ This bit is used in Single Channel mode to increase the acquisition time available for external analog

inputs in Continuous Sampling mode by 6 ADCCLK cycles (see Acquisition Phase, page 34). The

acquisition time is increased by setting this bit to logic 1.

BU

This bit is used in Single Channel mode to select either Unipolar or Bipolar operating mode for

the ADC analog inputs (see Analog Inputs, page 39). A logic High places the ADC in differential

mode and logic 0 places the ADC in unipolar mode.

18 www.xilinx.com Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Page 19

Register File Interface

www.BDTIC.com/XILINX

Table 6: Configuration Bit Definitions (Cont’d)

Name Description

EC This bit is used in Single Channel Mode to select either Continuous or Event driven sampling mode

for the ADC

(see System Monitor Timing, page 33). A logic High places the ADC in event driven

sampling mode and logic 0 places the ADC in continuous sampling mode. Event Mode should only

be used with external analog input channels.

AVG1, AVG0 These bits are used to set the amount of sample averaging on selected channels in both Single Channel

and Sequence mode (see Ta bl e 8).

CAVG This bit is used to enable averaging for the calculation of the calibration coefficients. Averaging is

enabled by default (logic 0). To disable, set this bit to logic 1. Averaging is fixed at 16 samples.

OT This bit is used to disable the Over

-Temperature signal. Alarm is disabled by setting this bit to logic

1 (see Thermal Management, page 30).

ALM0 to ALM2 These bits are used to disable individual alarm outputs for Temperature, V

CCINT

, and V

CCAUX

logic 1 disables an alarm output (see Automatic Alarms, page 29).

SEQ0, SEQ1 These bits are used to enable the channel-sequencer function for the bit assignments (see Ta bl e 9).

CAL0 to CAL3 These bits are used to enable the application of the calibration coefficients to the ADC and on

supply sensor measurements (

see System Monitor Calibration, page 31). A logic 1 enables calibration

-chip

and a logic 0 disables calibration. For bit assignments, see Ta bl e 10 .

CD0 to CD7 These bits are used to select the division ratio between the

frequency ADC clock (ADCCLK) used for the ADC

DRP clock (DCLK) and the lower

(see System Monitor Timing, page 33). For bit

assignments, see Ta bl e 11 .

Table 7: Channel Selection

ADC Channel CH4 CH3 CH2 CH1 CH0 Description

000000On

1 0 0 0 0 1 Average on

2 0 0 0 1 0 Average on-chip V

300011V

400100V

500101V

-chip temperature

-chip V

, VN—Dedicated analog inputs

P

(1.25V)

REFP

(1)

(0V)

REFN

CCINT

CCAUX

(1)

600110

Invalid channel selection

700111

. A

8 0 1 0 0 0 Carry out a System Monitor calibration

9.....15 ... ... ... ... ... Invalid channel selection

16 1 0 0 0 0 V

17 1 0 0 0 1 V

18....31 ... ... ... ... ... V

Notes:

1. These channel selection options are used for System Monitor self-check and calibration operations. When these channels are

selected, the supply sensor is connected to V

Virtex-6 FPGA System Monitor www.xilinx.com 19

UG370 (v1.1) June 14, 2010

REFP

and V

REFN

[0], V

AUXP

[1], V

AUXP

[2:15], V

AUXP

.

[0]—Auxiliary channel 1

AUXN

[1]—Auxiliary channel 2

AUXN

[2:15]—Auxiliary channels 3 to 16

AUXN

Page 20

Register File Interface

www.BDTIC.com/XILINX

Table 8: Averaging Filter

AVG1 AVG0 Function

0 0 No averaging

0 1 Average 16 samples

1 0 Average 64 samples

1 1 Average 256 samples

Table 9: Channel Sequencer Operation

SEQ1 SEQ0 Function

0 0 Default safe mode

0 1 One pass through sequence

1 0 Continuous cycling of sequence

1 1 Single Channel mode (Sequencer Off)

Table 10: Calibration Enables

Name Description

CAL0 ADC offset correction enable

CAL1 ADC offset and gain correction enable

CAL2 Supply Sensor offset correction enable

CAL3 Supply Sensor offset and gain correction enable

Table 11: DCLK Division Selection

CD7 CD6 CD5 CD4 CD3 CD2 CD1 CD0 Division

00000000 2

00000001 2

00000010 2

(see Pre-Configuration Operation, page 10)

(1)

00000011 3

00000100 4

––––––––

11111110 254

11111111 255

Notes:

1. Minimum division ratio is 2, for example, ADCCLK = DCLK/2.

Test Registers (43h to 47h)

These registers are intended for factory test purposes only and have a default status of

zero. The user must not write to these registers.

20 www.xilinx.com Virtex-6 FPGA System Monitor

.

.

.

UG370 (v1.1) June 14, 2010

Page 21

Channel Sequencer Registers (48h to 4Fh)

www.BDTIC.com/XILINX

These registers are used to program the channel sequencer functionality (see Channel

Sequencer, page 25).

Alarm Registers (50h to 57h)

These registers are used to program the alarm thresholds for the automatic alarms on the

internally monitored channels, temperature, V

page 29).

DRP JTAG Interface

System Monitor uses a full JTAG interface extension to the System Monitor DRP interface.

This allows Read/Write access to the System Monitor DRP through the existing on-chip

JTAG infrastructure. No instantiation is required to access the System Monitor DRP

interface over JTAG. A Boundary-Scan instruction (10-bit instruction = 1111110111)

called SYSMON has been added to Virtex-6 devices to allow access to the System Monitor

DRP through the JTAG TAP. All System Monitor JTAG instructions are 32-bits in length.

For more information on the Virtex-6 FPGA Boundary-Scan instructions and usage, see the

Virtex-6 FPGA Configuration Guide. Read and Write operations using the System Monitor

JTAG DRP interface are described in the next sections. Users unfamiliar with basic JTAG

functionality should understand the JTAG standard (IEEE1149.1) before proceeding.

CCINT

, and V

CCAUX

Register File Interface

(see Automatic Alarms,

System Monitor DRP JTAG Write Operation

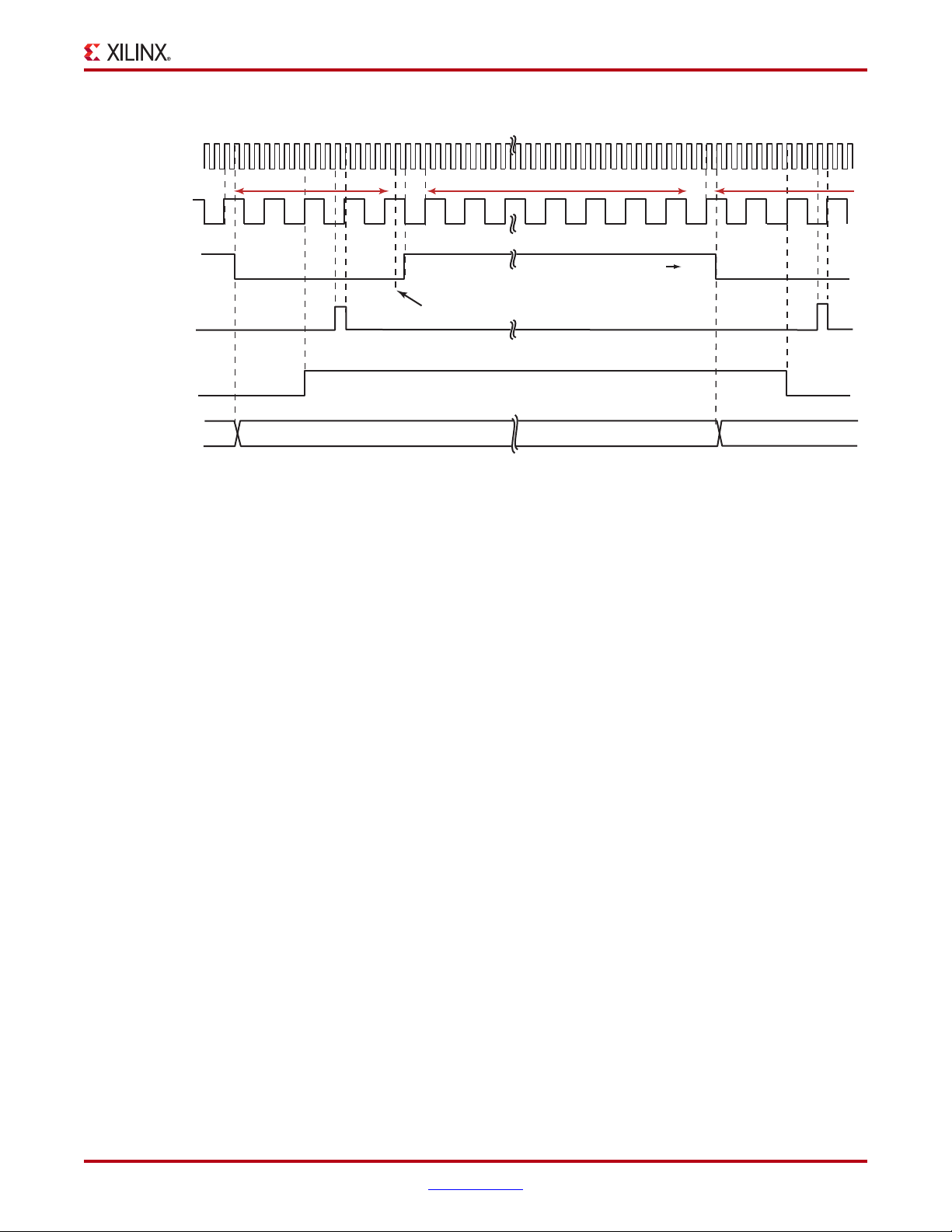

Figure 10 shows a timing diagram for a Write operation to the SYSMON DRP through the

JTAG TAP. The DRP is accessed through the System Monitor Data register (SYSMON DR).

Before the SYSMON DR is accessed, the instruction register (IR) must first be loaded with

the SYSMON instruction. The Controller is first placed in the IR-scan mode, and the

SYSMON instruction is shifted to the IR.

After the SYSMON instruction is loaded, all data register (DR)-scan operations are carried

out on the SYSMON DR. When the data shifted into SYSMON DR is a JTAG DRP Write

command, the SYSMON DRP arbitrator carries out a DRP write. The format of this Write

command is described in JTAG DRP Commands, page 23. The SYSMON DR contents are

transferred to the SYSMON DRP arbitrator (see DRP Arbitration, page 24) during the

Update-DR state. After the Update-DR state, the arbitrator manages the new data transfer

to the System Monitor DRP register. This takes up to six DRP Clock (DCLK) cycles if a DRP

access from the fabric is already in progress.

During the Capture-DR phase (just before data is shifted into the SYSMON DR), DRP data

is captured from the arbitrator. Depending on the last JTAG DRP command, this data could

be old data, previously written to the DRP or requested new Read data (see System

Monitor JTAG DRP Read Operation, page 22). This captured data is shifted out (LSB first)

on DO as the new JTAG DRP command is shifted in. The 16 LSBs of this 32-bit word

contain the JTAG DRP data. The 16 MSBs are set to zero.

If multiple writes to the SYSMON DR are taking place, it might be necessary to idle the

TAP Controller for several TCK cycles before advancing to the next write operation. This is

illustrated in Figure 10. The idle cycles allow the arbitrator to complete the Write operation

to the System Monitor DRP register. If DCLK is running approximately 6 x TCK, these idle

states are not necessary. However, inserting ten or so idle states ensures all transfers are

inherently safe.

Virtex-6 FPGA System Monitor www.xilinx.com 21

UG370 (v1.1) June 14, 2010

Page 22

Register File Interface

www.BDTIC.com/XILINX

X-Ref Target - Figure 10

TLR TLR RTI RTI RTI RTIDRS DRSDRSIRS CIR CDR CDRSIR SIR SIR SIR SDR SDR SDRSDR SDREIR EDR UDRUIR

TCK

TMS

TDI

TAP Controller States

09 0 3130

LSB

MSB MSB

LSB

TDO

Load IR with

SYSMON insructions

LSB

MSB

Write DRP Command shifted into

SYSMON DR

LSB

Old DRP Write or New

Read Data shifted out

MSB

Idle between successive

Writes to allow DRP Write

operation to finish

Figure 10: System Monitor JTAG DRP Write Operation

System Monitor JTAG DRP Read Operation

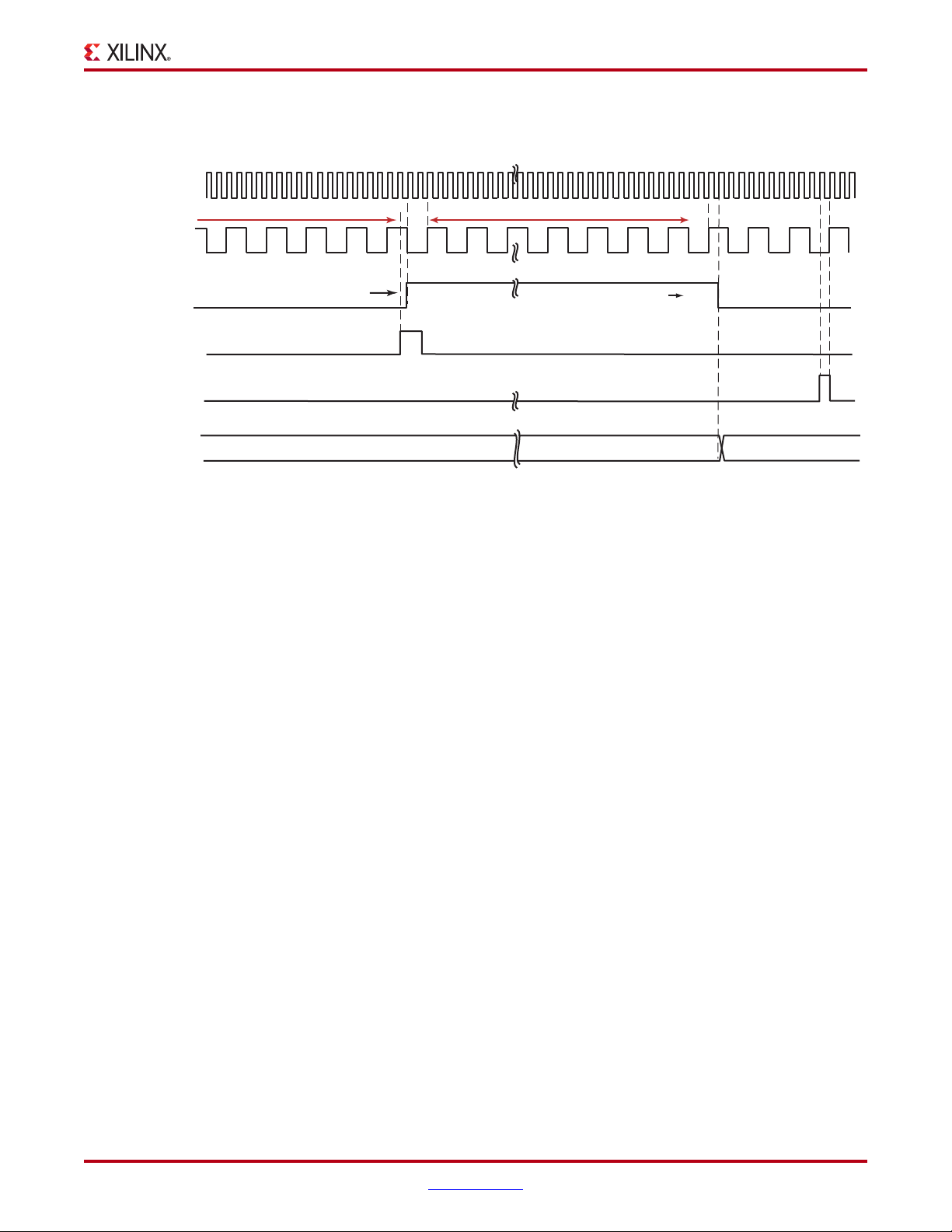

Figure 11 shows the timing for a SYSMON DR Read operation. The IR should contain the

DR-scan operation SYSMON instruction. A JTAG Read from the System Monitor DRP is a

two-step operation.

• First, the SYSMON DR is loaded with the Read DRP instruction. This instruction is

transferred to the arbitrator during the Update-DR state and then the arbitrator reads

the selected DRP register and stores the newly read 16-bit data. This operation takes

several DCLK cycles to complete.

• During the DR-Capture phase of the next DR-scan, newly read data is transferred

from the arbitrator to the SYSMON DR. This 16-bit data (stored in the 16 LSBs of the

32-bit word) is then shifted out on TDO during the subsequent shift operation (see

Figure 11). The timing diagram shows a number of idle states at the end of the first

DR-scan operation, allowing the arbitrator enough time to fetch the System Monitor

DRP data.

UG370_10_

060809

As mentioned previously, if the DCLK frequency is significantly faster than the TCK, these

idle states might not be required.

Note:

operation results in old DRP data being transferred to the SYSMON DR during the DR-capture

phase.

Implementing a DR-scan operation before the arbitrator has completed the DRP-read

To ensure reliable operation over all operating clock frequencies, a minimum of ten RunTest-Idle (RTI) states should be inserted. Multiple Read operations can be pipelined, as

shown in Figure 11. Thus, as the result of a read operation is being shifted out of the

SYSMON DR, an instruction for the next read can be shifted in.

22 www.xilinx.com Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Page 23

X-Ref Target - Figure 11

www.BDTIC.com/XILINX

TCK

TMS

Register File Interface

TAP Controller States

RTIUIR RTI RTI RTI RTI RTI RTIDRS CDR SDR SDR SDRSDR SDR EDR UDR RTI DRS CDR SDR SDR SDRSDR SDR EDR UDR

TDI

TDO

03130

LSB

Read Command shifted into

SYSMON DR

LSB

Old DRP Write or New

Read Data shfited out

Monitor DRP instructions

previously shifted into IR

Figure 11: System Monitor JTAG DRP Read Operation

JTAG DRP Commands

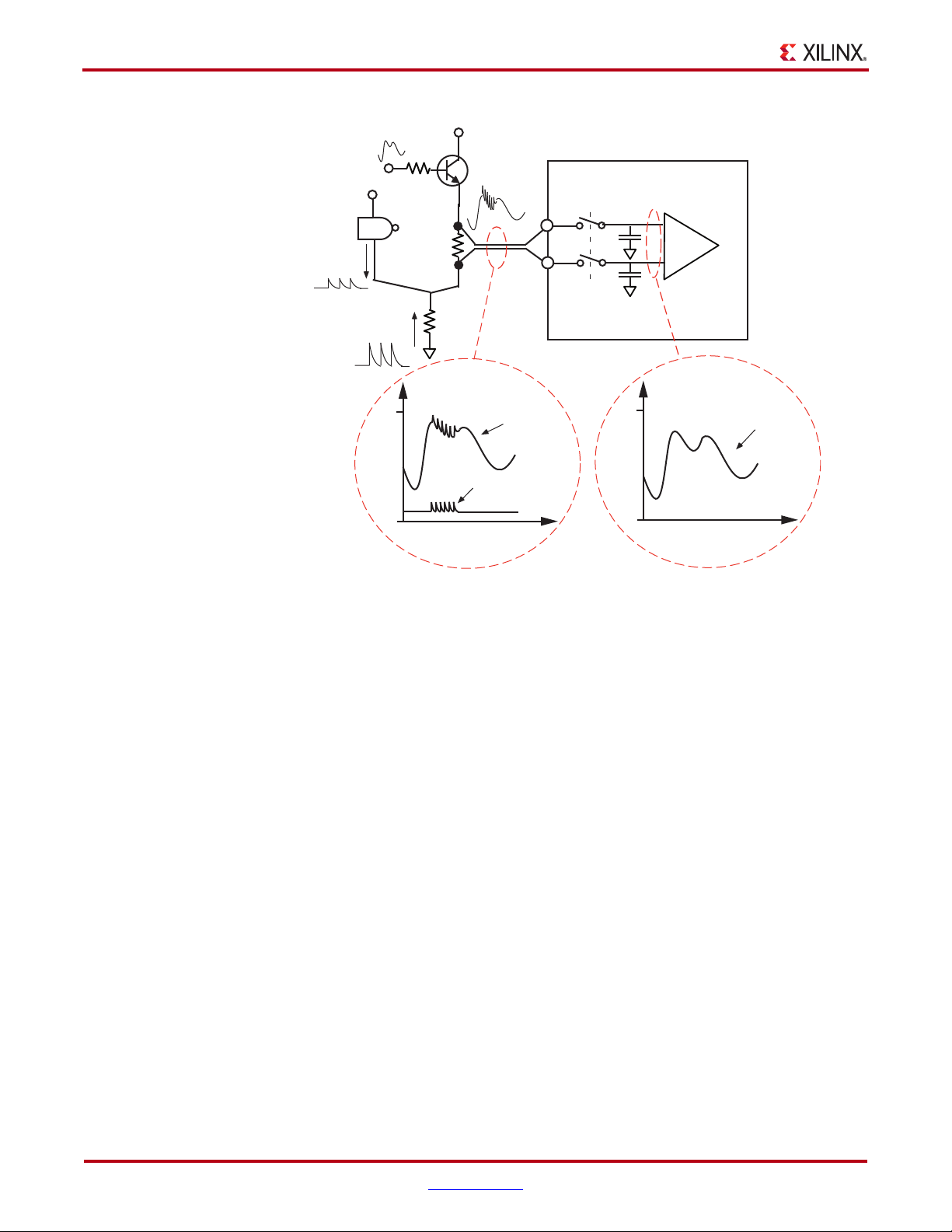

The data shifted into the 32-bit SYSMON DR during a DR-scan operation instructs the

arbitrator to carry out a Write, Read, or no operation on the System Monitor DRP. Figure 12

shows the data format of the JTAG DRP command loaded into the SYSMON DR. The first

16 LSBs of SYSMON DR [15:0] contain the DRP register data. For both Read/Write

operations, the address bits SYSMON DR [25:16] hold the DRP target register address. The

command bits SYSMON DR [29:26] are used to specify a Read/Write or no operation (see

Ta bl e 12 ).

X-Ref Target - Figure 12

31 30

MSB

MSB

Idle to allow DRP Read

to complete before

shifting out result

03130

LSB

Read Command shifted into

SYSMON DR

LSB

New DRP Read Data

shifted out

1516252629

MSB

MSB

Idle to allow DRP Read

to complete before

shifting out result

UG370_11_

060809

0

XX

MSB LSB

DRP Address [9:0]

System Monitor Data Register (SYSMON DR)

Figure 12: SYSMON JTAG DRP Command

Table 12: JTAG DRP Commands

CMD[3:0] Operation

0 0 0 0 No operation

0 0 0 1 DRP Read

0010DRP Write

––––Not defined

Virtex-6 FPGA System Monitor www.xilinx.com 23

UG370 (v1.1) June 14, 2010

DRP Data [15:0]CMD [3:0]

UG370_12_

060809

Page 24

Register File Interface

www.BDTIC.com/XILINX

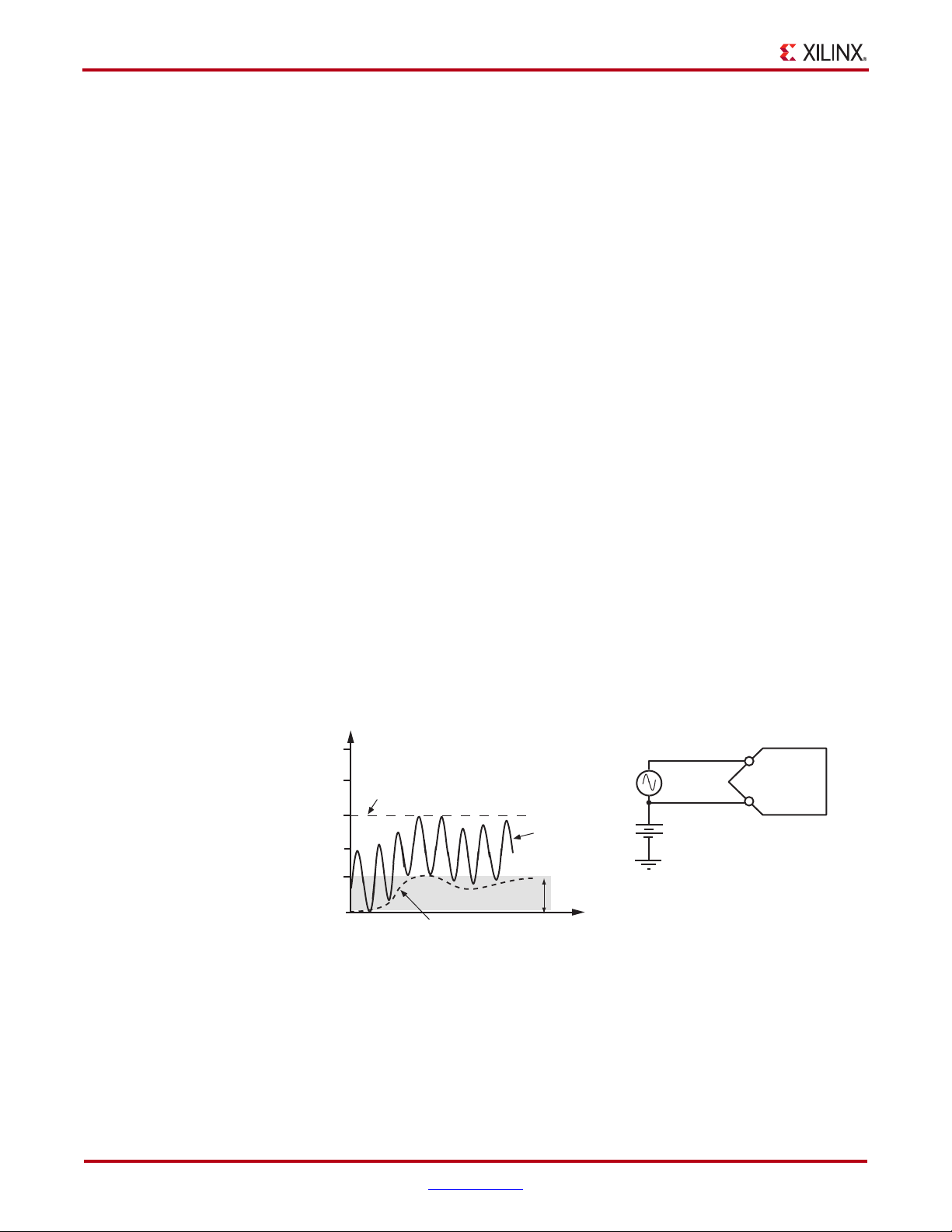

It is also possible to enable the auxiliary analog input channel pre-configuration of the

FPGA, allowing external analog voltages (on the PCB) to be monitored using the JTAG

TAP before configuration. The auxiliary channels are enabled by writing 0001h to DRP

address 02h. This address lies within the read-only status register address space and

normally holds the result of a V

enables the auxiliary inputs.

CCAUX

measurement. However, a write to this address

Note:

explicitly instantiated in the design.

This function only works prior to configuration. Post configuration, these inputs must be

DRP Arbitration

Because the DRP registers are accessed from two different ports (interconnect and JTAG

TAP) access must be carefully managed. An arbitrator has been implemented to manage

potential conflicts between the fabric and JTAG port. Arbitration is managed on a per

transaction basis (a transaction is a single Read/Write operation to the DRP). The

arbitration rules are as follows:

• A JTAG transaction cannot be interrupted by the fabric. The fabric transaction is

queued by the arbitrator until the JTAG transaction has finished, and then the fabric

transaction is completed.

• A JTAG transaction cannot interrupt a fabric transaction already in progress. As soon

as the fabric transaction is finished, then the JTAG transaction is completed.

Three status signals are provided to help manage access through the interconnect when the

JTAG port is also being used.

JTAGBUSY

This signal becomes active during the update phase of a DRP transaction through the JTAG

TAP. The signal resets when the JTAG SYSMON DR transaction is completed. Each

Read/Write to the SYSMON DR is treated as an individual transaction. If DRP access

initiates through the interconnect port when JTAGBUSY is High, then the arbitrator

queues this request for a Read/Write through the fabric. DRDY does not go active until

JTAGBUSY transitions Low and the interconnect transaction is completed. A second DRP

access through the fabric must not be initiated until the DRDY for the initial access

becomes active and indicates the Read/Write was successful. If an interconnect access is in

progress when a JTAG DRP transaction initiates, the interconnect access is completed

before the JTAG transaction.

JTAGMODIFIED

Whenever there is a JTAG Write (JTAG Reads typically occur more often) to any register in

the DRP, the application (FPGA) must be notified about the potential change of

configuration. Thus, a signal called JTAGMODIFIED transitions High after a JTAG Write.

A subsequent DRP Read/Write resets the signal.

JTAGLOCKED

In some cases, it is simpler for the JTAG user to take DRP ownership for a period by

locking out access through the interconnect. This is useful in a diagnostic situation where

a large number of DRP registers are modified through the JTAG TAP. When a

JTAGLOCKED request is made, the JTAGLOCKED signal transitions to an active High.

The signal remains High until the port is unlocked again. No read or write access is

possible via the DRP fabric port when the JTAGLOCKED signal is High. The

24 www.xilinx.com Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Page 25

JTAGLOCKED signal is activated by writing 0001h to DRP address 00h. The

www.BDTIC.com/XILINX

JTAGLOCKED signal is reset again by writing 0000h to DRP address 00h.

System Monitor Control Logic

Many of the most commonly used system monitoring functions are implemented in the

System Monitor control logic. Common functions include:

• Channel sequencer

• Measurement averaging

• Maximum and minimum internal sensor measurements

• Automatic alarms on internal sensors

• Sensor and ADC calibration

The control logic also decodes the configuration registers to configure the ADC sampling

modes (see System Monitor Timing, page 33) and external analog-input configuration (see

Analog Inputs, page 39).

Channel Sequencer

System Monitor Control Logic

When bits SEQ1 and SEQ0 in Control Register 41h are set to logic 1 (see Tab le 9 , p age 20 ),

System Monitor operates in Single Channel mode. In this mode, the user must select the

channel for Analog-to-Digital conversion by writing to the bit locations CH0 to CH4 in

control register 40h. Operating modes for Single Channel mode, such as analog input

mode (B

40h. In applications where many channels need to be monitored, this can mean a

significant overhead for the microprocessor or other controller. To automate this task, a

function called the Channel Sequencer is provided.

The Channel Sequencer provides a method for the user to set up a predefined sequence of

channels (both internal and external) to be automatically monitored. The Channel

Sequencer function is implemented using eight control registers from address 48h to 4Fh

on the DRP (see Control Registers, page 17). These eight registers can be viewed as four

pairs of 16-bit registers. Each pair of registers controls one aspect of the sequencer

functionality. I ndividual bits in e ach pair of registers (32 bits) enable a specific functionality

for a particular ADC channel. The four pairs of registers are:

• ADC channel selection (48h and 49h)

• ADC channel averaging enables (4Ah and 4Bh)

• ADC channel analog-input mode (4Ch and 4Dh)

• ADC channel acquisition time (4Eh and 4Fh)

System Monitor only operates in Continuous Sampling mode (see Continuous Sampling,

page 34) when the automatic channel sequencer is enabled. Sequencer mode is enabled by

using bits SEQ1 and SEQ0 in Configuration register 1 (see Configuration Registers (40h to

42h), page 17). The Channel Sequencer registers should be initialized by the user when

System Monitor is instantiated in a design (see System Monitor Primitive, page 8). The

Channel Sequencer can also be reconfigured via the DRP at run time. The Sequencer must

first be disabled by writing to bits SEQ1 and SEQ0 before writing to any of the Channel

Sequencer registers. It is recommended the System Monitor is placed in safe mode by

writing zeros to SEQ0 and SEQ1 while updating the Control Registers. System Monitor is

automatically reset whenever SEQ1 and SEQ0 are changed. The current status register

U) and acquisition time (ACQ), must also be set by writing to Control Register

Virtex-6 FPGA System Monitor www.xilinx.com 25

UG370 (v1.1) June 14, 2010

Page 26

System Monitor Control Logic

www.BDTIC.com/XILINX

contents are not reset at this time. Restarting the sequencer by writing to bits SEQ1 and

SEQ0 resets all channel averaging (see ADC Channel Averaging (4Ah and 4Bh), page 27).

ADC Channel Selection (48h and 49h)

The ADC channel selection registers enable and disable a channel in the automatic

monitoring sequence. The bit definitions for these registers are described in Tabl e 13 and

Ta bl e 1 4 . The two 16-bit registers are used to enable or disable the associated channels. A

logic 1 enables a particular channel in the sequence. The sequence order is fixed starting

from the LSB (bit 0) of register 48h and ending with the MSB (bit 15) of register 49h.

Table 13: Sequencer ADC Channel Selection, Control Register 48h

Sequence

Number

1 0 8 System Monitor calibration

280On

391Average On

4102Average On

5113V

6124V

7135V

Bit

19

210

311

412

513

614

715

14 6

15 7

ADC

Channel

Description

Invalid channel selection

-Chip temperature

-Chip V

-Chip V

, V

—Dedicated analog inputs

P

N

(1.25V)

REFP

(0V)

REFN

Invalid channel selection

CCINT

CCAUX

(1)

Notes:

1. See the ADC Channel Averaging (4Ah and 4Bh) section for further details on how calibration is done

in an averaged sequence.

Table 14: Sequencer ADC Channel Selection, Control Register 49h

Sequence

Number

8 0 16 VAUXP[0],VAUXN[0]—Auxiliary channel 1

9 1 17 VAUXP[1],VAUXN[1]—Auxiliary channel 2

10 2 18 VAUXP[2],VAUXN[2]—Auxiliary channel 3

11 3 19 VAUXP[3],VAUXN[3]—Auxiliary channel 4

26 www.xilinx.com Virtex-6 FPGA System Monitor

Bit

ADC

Channel

Description

UG370 (v1.1) June 14, 2010

Page 27

System Monitor Control Logic

www.BDTIC.com/XILINX

Table 14: Sequencer ADC Channel Selection, Control Register 49h (Cont’d)

Sequence

Number

12 4 20 VAUXP[4],VAUXN[4]—Auxiliary channel 5

13 5 21 VAUXP[5],VAUXN[5]—Auxiliary channel 6

14 6 22 VAUXP[6],VAUXN[6]—Auxiliary channel 7

15 7 23 VAUXP[7],VAUXN[7]—Auxiliary channel 8

16 8 24 VAUXP[8],VAUXN[8]—Auxiliary channel 9

17 9 25 VAUXP[9],VAUXN[9]—Auxiliary channel 10

18 10 26 VAUXP[10],VAUXN[10]—Auxiliary channel 11

19 11 27 VAUXP[11],VAUXN[11]—Auxiliary channel 12

20 12 28 VAUXP[12],VAUXN[12]—Auxiliary channel 13

21 13 29 VAUXP[13],VAUXN[13]—Auxiliary channel 14

22 14 30 VAUXP[14],VAUXN[14]—Auxiliary channel 15

23 15 31 VAUXP[15],VAUXN[15]—Auxiliary channel 16

Bit

ADC

Channel

Description

ADC Channel Averaging (4Ah and 4Bh)

The ADC channel averaging registers enable and disable the averaging of the channel data

in the sequence. The result of a measurement on an averaged channel is generated by using

16, 64, or 256 samples. The amount of averaging is selected by using the AVG1 and AVG0

bits in Configuration register 0 (see Configuration Registers (40h to 42h), page 17). Not all

channels in the automatic sequence have an averaging feature. The bit definitions for these

registers are described in Ta bl e 15 and Ta bl e 1 6 . Each bit in the two 16-bit registers is used

to enable or disable the averaging for its associated channel. A logic 1 enables averaging

for a particular channel in the sequence. All channels have the same amount of averaging

applied as defined by AVG1 and AVG0 (see Tab le 8, p ag e 20).

Averaging can be independently selected for each channel in the sequence. When

averaging is enabled for some of the channels of the sequence, the EOS will only be pulsed

after the sequence has completed the amount of averaging selected by using AVG1 and

AVG0. If a channel in the sequence does not have averaging enabled, its status register will

be updated for every pass through the sequencer. When a channel has averaging enabled,

its status register is only updated after the averaging is complete. An example sequence is

Temperature and V

Temperature, V

AUX

[1] and averaging of 16 is enabled on V

AUX

[1], Temperature, V

conversions where the temperature status register is updated. The V

is updated after the averaging of the 16 conversions.

If averaging is enabled for the calibration channel (by setting CAVG logic Low), the

coefficients will be updated after the first pass through the sequence. Subsequent updates

to coefficient registers will require 16 conversions before the coefficients are updated.

Virtex-6 FPGA System Monitor www.xilinx.com 27

UG370 (v1.1) June 14, 2010

[1], ... Temperature, V

AUX

[1]. The sequence will be

AUX

[1] for each of the

AUX

[1] status register

AUX

Page 28

System Monitor Control Logic

www.BDTIC.com/XILINX

Table 15: Sequencer ADC Channel Averaging, Control Register 4Ah

Bit ADC Channel Description

08

19

210

311

412

513

614

715

8 0 Enable averaging—On

9 1 Enable averaging—On

10 2 Enable averaging—On

11 3 Enable averaging—V

12 4 Enable averaging—V

13 5 Enable averaging—V

14 6

15 7

Averaging for the calibration coefficients is

enabled using CAVG in Configuration Register 0.

Invalid channel selection

Invalid channel selection

-Chip temperature

-Chip V

-Chip V

, VN

P

(1.25V)

REFP

REFN

(0V)

CCINT

CCAUX

sensor

sensor

Table 16: Sequencer ADC Channel Averaging, Control Register 4Bh

Bit ADC Channel Description

0 16 Enable averaging—VAUXP[0],VAUXN[0]—Auxiliary channel 1

1 17 Enable averaging—VAUXP[1],VAUXN[1]—Auxiliary channel 2

2 18 Enable averaging—VAUXP[2],VAUXN[2]—Auxiliary channel 3

3 19 Enable averaging—VAUXP[3],VAUXN[3]—Auxiliary channel 4

4 20 Enable averaging—VAUXP[4],VAUXN[4]—Auxiliary channel 5

5 21 Enable averaging—VAUXP[5],VAUXN[5]—Auxiliary channel 6

6 22 Enable averaging—VAUXP[6],VAUXN[6]—Auxiliary channel 7

7 23 Enable averaging—VAUXP[7],VAUXN[7]—Auxiliary channel 8

8 24 Enable averaging—VAUXP[8],VAUXN[8]—Auxiliary channel 9

9 25 Enable averaging—VAUXP[9],VAUXN[9]—Auxiliary channel 10

10 26 Enable averaging—VAUXP[10],VAUXN[10]—Auxiliary channel 11

11 27 Enable averaging—VAUXP[11],VAUXN[11]—Auxiliary channel 12

12 28 Enable averaging—VAUXP[12],VAUXN[12]—Auxiliary channel 13

13 29 Enable averaging—VAUXP[13],VAUXN[13]—Auxiliary channel 14

28 www.xilinx.com Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Page 29

System Monitor Control Logic

www.BDTIC.com/XILINX

Table 16: Sequencer ADC Channel Averaging, Control Register 4Bh (Cont’d)

Bit ADC Channel Description

14 30 Enable averaging—VAUXP[14],VAUXN[14]—Auxiliary channel 15

15 31 Enable averaging—VAUXP[15],VAUXN[15]—Auxiliary channel 16

ADC Channel Analog-Input Mode (4Ch and 4Dh)

These registers are used to configure an ADC channel as either unipolar or bipolar in the

automatic sequence (see Analog Inputs, page 39). The registers have the same bit

assignments as the Channel Sequence and Channel Averaging registers. However, only

external analog-input channels, such as the dedicated-input channels V

Auxiliary Analog inputs V

Setting a bit to logic 1 enables a bipolar input mode for the associated channel. Setting a bit

to logic 0 (default) enables a unipolar input mode. All internal sensors use a unipolar

transfer function.

[15:0], and V

AUXP

[15:0]), can be configured in this way.

AUXN

, and VN, and the

P

ADC Channel Acquisition Time (4Eh and 4Fh)

The default acquisition time for an external channel in Continuous-Sampling mode is four

ADCCLK cycles. However, by setting the corresponding bits to logic 1 in registers 4Eh and 4Fh,

the associated channel can have its acquisition time extended to ten ADCCLK cycles. The bit

definitions (which bits correspond to which external channels) for these registers are the same

as the Channel Sequence registers described in Ta bl e 1 3 and Ta bl e 1 4. For example, to extend the

acquisition time for channel V

AUXP

[1]/V

[1], bit 1 in register 4Fh is set to a logic 1.

AUXN

Maximum and Minimum Status Registers

System Monitor also tracks the minimum and maximum values recorded for the internal

sensors since the last power-up or since the last reset of the System Monitor control logic.

The maximum and minimum values recorded are stored in the DRP Status registers

starting at address 20h (see Status Registers, page 15). On power-up or after reset, all the

minimum registers are set to FFFFh and the maximum registers are set to 0000h. Each

new measurement generated for an on-chip sensor is compared to the contents of its

maximum and minimum registers. If the measured value is greater than the contents of its

maximum registers, then the measured value is written to the maximum register. Similarly,

for the minimum register, if the measured value is less than the contents of its minimum

register, then the measured value is written to the minimum register. This check is carried

out every time a measurement result is written to the status registers.

Automatic Alarms