Page 1

Virtex-6 FPGA

www.BDTIC.com/XILINX

GTX Transceivers

User Guide

UG366 (v2.5) January 17, 2011

Page 2

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development

www.BDTIC.com/XILINX

of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the

Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise,

without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves

the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors

contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with

technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER

WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY

RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL

DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© Copyright 2009–2011 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are

trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All other

trademarks are the property of their respective owners.

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com UG366 (v2.5) January 17, 2011

Page 3

Revision History

www.BDTIC.com/XILINX

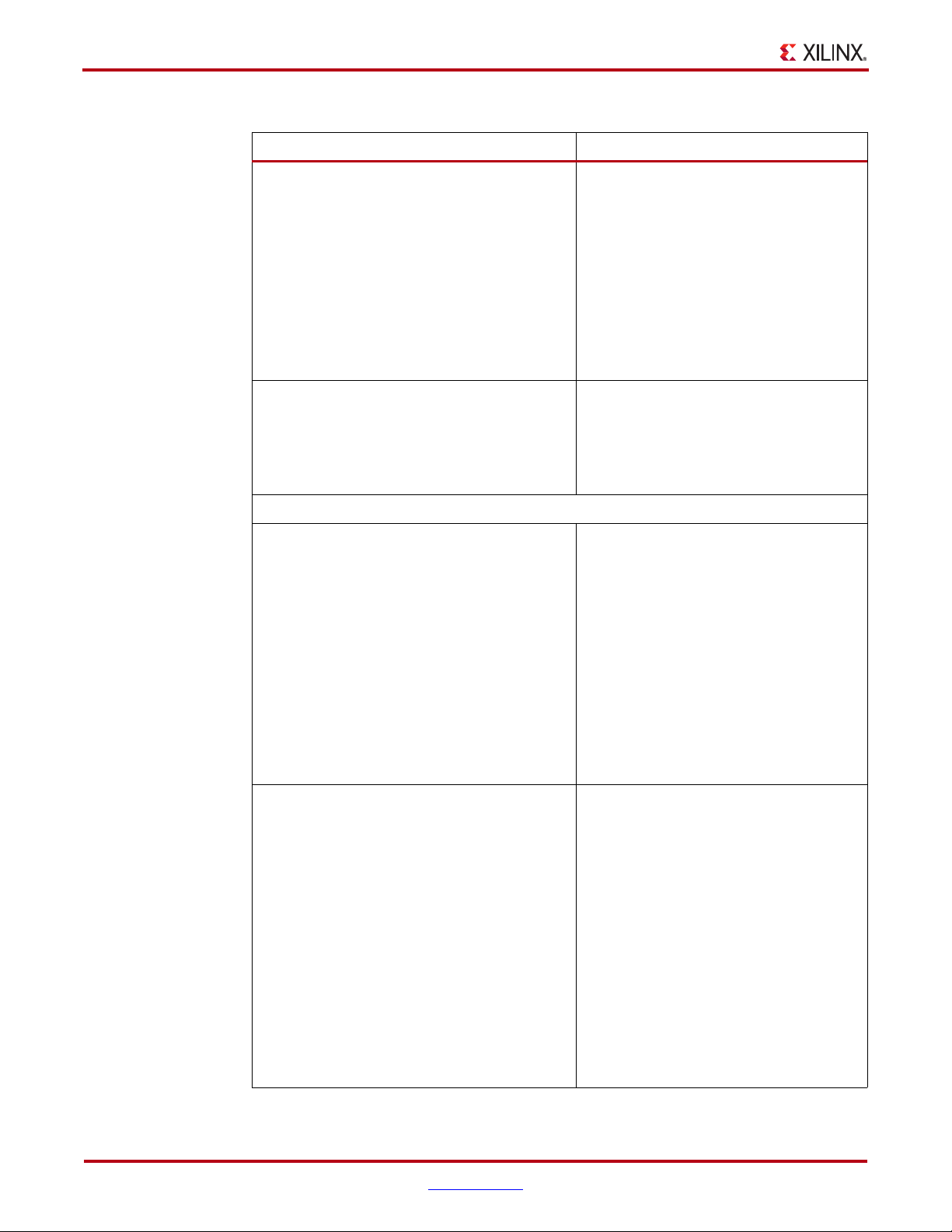

The following table shows the revision history for this document.

Date Version Revision

06/24/09 1.0 Initial Xilinx release.

08/11/09 2.0 Chapter 2:

• Added new sections: Using TXOUTCLK to Drive the GTX TX, page 131, GTX TX Reset in

Response to Completion of Configuration, page 139, GTX TX Reset in Response to

GTXTXRESET Pulse, page 139, GTX TX Component-Level Resets, page 140, After Powerup and Configuration, page 142, After Turning on a Reference Clock to the TX PLL,

page 142, After Changing the Reference Clock to the TX PLL, page 142, After

Assertion/Deassertion of TXPOWERDOWN, page 142, TX Rate Change with the TX

Buffer Enabled, page 142, TX Rate Change with the TX Buffer Bypassed, page 142, TX

Parallel Clock Source Reset, page 142, TX Phase Alignment after Rate Change Use Mode,

page 159, and Rate Change Use Mode for PCI Express 2.0 Operation, page 171.

• Added the RXPLLREFSELDY[2:0] port to Table 2-4, page 106.

• Replaced first sentence of Single External Reference Clock Use Model, page 108.

• Added new section Multiple External Reference Clocks Use Model, page 110.

• Revised PLL nominal operating range and added Tab l e 2-6 , pag e 11 3 .

• Added the PMA_COM_CFG attribute to Tabl e 2 -9, p age 115 .

•Replaced Table 2-10, page 117.

• Added PCI Express mode power conditions to bulleted list in Power-Down Features for

PCI Express Operation, page 123.

• Added note 1 to Table 2-10, page 117 on P1 and P2 power state support.

•In Dynamic Reconfiguration Port, page 125, revised occurrences of DO to DRPDO.

•In Table 2-18, page 126, changed the bus width of the DRP address bus to DADDR[7:0].

Chapter 3:

• Renamed TX Clock Divider Control block to TX Fabric Clock Output Control.

• Revised “GTX Lanes in Channel” values for 2-byte and 4-byte rows in Table 3-3, page 129.

• In the Functional Description of TX Initialization, page 136, revised #2 and added #3.

Added Figure 3-8, page 137 showing the GTX TX reset hierarchy.

• Revised the GTXTEST[12:0] and GTXTXRESET descriptions in Table 3-7, page 138.

• Revised Ease of Use and TX Lane-to-Lane Deskew rows in Table 3-15, page 153.

• Revised the TXDLYALIGNDISABLE, TXDLYALIGNMONITOR[7:0], and TXOUTCLK

descriptions in Table 3-18, page 155.

• Revised steps 2, 5, and 9 in Using t

page 158.

• Changed the width of TXDLYALIGNRESET in Figure 3-21, page 159 to 16 TXUSRCLK2

cycles and revised caption.

• Revised paragraph under Figure 3-23, page 160 on making phase alignment effective.

•In Serial Clock Divider, page 168, provided more details on using the D divider in fixed

line rate and multiple line rate applications.

•In Table 3-28, page 168, removed TXPLL_DIVSEL_OUT = Ignored from all rows in the

Dynamic Control via Ports column.

•In Table 3-29, page 169, added the GTXTEST[1] port and revised the clock domain and

description of TXRATEDONE.

•In Table 3-30, page 170, revised the description of TRANS_TIME_RATE.

• Revised PCI Express Clocking Use Mode, page 170 and added Figure 3-29, page 171 and

Figure 3-30, page 172.

he TX Phase-Alignment Circuit to Bypass the Buffer,

UG366 (v2.5) January 17, 2011 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

Page 4

Date Version Revision

www.BDTIC.com/XILINX

08/11/09

(Cont’d)

2.0 Chapter 3 (Cont’d):

• Changed the widths of TXPREEMPHASIS, TXDIFFCTRL, and TXPOSTEMPHASIS in

Figure 3-31, page 173.

• Revised description of RXPOWERDOWN and TXPOWERDOWN in Table 3-33, page 179.

• Added note to the Functional Description of TX Out-of-Band Signaling, page 180.

•In Table 3-34, page 181, changed TXELECIDLE to one bit and added COMFINISH.

• Updated descriptions of TXELECIDLE and TXPOWERDOWN ports in Table 3-34,

page 181

Chapter 4:

• Added new sections GTX RX Reset in Response to Completion of Configuration, page 263,

GTX RX Reset in Response to GTXRXRESET Pulse, page 263, Link Idle Reset Support,

page 264, GTX RX Component-Level Resets, page 264, After Power-up and Configuration,

page 266, After Turning on a Reference Clock to RX PLL, page 266, After Changing the

Reference Clock to RX PLL, page 267, After Assertion/Deassertion of RXPOWERDOWN,

page 267, RX Rate Change with RX Elastic Buffer Enabled, page 267, RX Rate Change with

RX Elastic Buffer Bypassed, page 267, RX Parallel Clock Source Reset, page 267, After

Remote Power-Up, page 267, Electrical Idle Reset, page 267, After Connecting RXN/RXP,

page 268, After an RX Elastic Buffer Error, page 268, Before Channel Bonding, page 268,

After Changing Channel Bonding Mode on the Fly, page 268, After a PRBS Error, page 268,

After an Oversampler Error, page 268, and After Comma Realignment, page 269.

• Added ESD Diodes label to Figure 4-2, page 184, Figure 4-3, page 187, Figure 4-4,

page 188, Figure 4-5, page 189, Figure 4-6, page 190, and Figure 4-7, page 191.

• Revised captions for Figure 4-9, page 194 and Figure 4-10, page 195.

•In Tab l e 4-2 , pag e 1 85, added sentence about system evaluation purposes to the

de

scriptions of TERMINATION_CTRL[4:0] and TERMINATION_OVRD.

• Added GATERXELECIDLE and IGNORESIGDET ports to Table 4-9, page 192.

•Added Figure 4-8, page 193.

•In Serial Clock Divider, page 208, provided more details on using the D divider in fixed

line rate and multiple line rate applications.

•In Table 4-23, page 208, removed RXPLL_DIVSEL_OUT = Ignored from all rows in the

Dynamic Control via Ports column.

•In Table 4-24, page 209, revised the clock domain and description of RXRATEDONE.

•In Table 4-25, page 209, revised the description of TRANS_TIME_RATE.

• Added RX decoder port and attribute tables (Table 4-38, page 230 and Table 4-39, page 231,

respectively).

• Changed description of RXDLYALIGNMONITOR[7:0] to reserved in Table 4-40, page 233.

• Moved description of RX CDR lock to RX CDR, page 204.

• Revised descriptions of CLK_COR_ADJ_LEN, CLK_COR_DET_LEN,

CLK_COR_MAX_LAT, and CLK_CORRECT_USE attributes in Table 4-47, page 242.

• In the Functional Description of RX Initialization, page 261, revised #2 and added #3.

Added Figure 4-49, page 261 showing the GTX receiver reset hierarchy.

•In Table 4-52, page 261, revised the GTXTEST[12:0] description and added the

PRBSCNTRESET port.

• Added the RX_EN_REALIGN_RESET_BUF2 attribute to Table 4-53, page 262.

• Revised “GTX Lanes in Channel” values for 2-byte and 4-byte rows in Table 4-58, page 270.

Appendix B:

• Added new appendix.

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com UG366 (v2.5) January 17, 2011

Page 5

Date Version Revision

www.BDTIC.com/XILINX

01/19/10 2.1 Updated width of TXBUFSTATUS port in Ta bl e 1 -1. Updated Figure 1-4. Updated description

of SIM_GTXRESET_SPEEDUP in Tab le 1 -2 . Added GTXE1_X0Y1 location for LX75T to

Figure 1-9.

Added new section Reference Clock Input Structure, page 101. Added note after Figure 2-4,

Figure 2-5, Figure 2-6, and Figure 2-7. Updated PLL nominal operation range in Functional

Description. Removed Line Rate Range column and added -1 Line Rate Range and -2/-3 Line

Rate Range columns to Ta bl e 2 -6 . Added note after Figure 2-9. Added description of N1

divider setting after Ta bl e 2 -7 . Updated entries in and removed REFCLK Max and Min

columns from Ta bl e 2 -1 0. Removed Power Down Transition Times section. Updated

Description column of Ta bl e 2 -1 0.

Moved Ports and Attributes, page 130 before Using TXOUTCLK to Drive the GTX TX,

page 131. Updated Using TXOUTCLK to Drive the GTX TX, page 131. Added guideline for

asynchronous GTXTXRESET pulse width in GTX TX Reset in Response to GTXTXRESET

Pulse, page 139. Added TXDLYALIGNMONENB and updated descriptions of

TXDLYALIGNRESET, TXOUTCLK, and TXPMASETPHASE to Tab le 3 -1 8. Updated steps 1d

and 6 in Using the TX Phase-Alignment Circuit to Bypass the Buffer, page 158. Updated TX

Oversampling, page 166. In Ta bl e 3 - 26 , removed PMA_RX_CFG, updated description of

TX_OVERSAMPLE_MODE, and added TXPLL_DIVSEL_OUT. Added note 5 to Figure 3-28.

Updated line rate ranges in Ta bl e 3 -2 8. Changed IBUFDS to IBUFDS_GTXE1 in Figure 3-29

and added a note after the figure. Replaced TXPREEMPHASIS with TXPOSTEMPHASIS in

description of TXDEEMPH in Ta bl e 3- 31 . Changed PCI Express version from 3.0 to 2.0 in note

for Ta bl e 3- 31 . Replaced TXPREEMPHASIS with TXPOSTEMPHASIS in descriptions of

TX_DEEMPH_0/1 in Tab le 3 -3 2. Replaced TXPREEMPHASIS with TXPOSTEMPHASIS in

PCIe Mode, page 178 and Customizable User Presets, page 178.

Added note after Figure 4-2 and Tab l e 4 -3 . Updated Ta bl e 4 -5 and Tabl e 4 -7 . Added

OOBDETECT_THRESHOLD_0/1 to and updated description of SATA_IDLE_VAL in

Ta bl e 4 - 10 .

Figure 4-12. Updated descriptions of DFECLKDLYADJ, DFECLKDLYADJMON, and

DFEDLYOVRD in Ta b le 4 -1 1. Updated descriptions of DFE_CAL_TIME, DFE_CFG, and

RX_EN_IDLE_HOLD_DFE attributes in Ta bl e 4 -1 2. Renamed RX Clock Divider Control

section as RX Fabric Clock Output Control, page 207. Updated MGTREFCLKFAB[1] bit in

and added note 4 to Figure 4-15. Updated line rate ranges in Tab le 4- 23 . Updated RX Margin

Analysis, page 210. Added DFEEYEDACMON port to Tab le 4 -2 6. Replaced

INTDATAWIDTH with R X _ D ATA _W I DTH in and added note to Figure 4-19. Changed

RXOVERSAMPLER to RXOVERSAMPLEERR in Tab l e 4 -2 9 . Updated description of

RX_OVERSAMPLE_MODE in and added RXPLL_DIVSEL_OUT to Tab l e 4 -3 0 . Swapped the

order of the SIPO and Polarity Inversion blocks in Figure 4-20. Updated descriptions of

RX_PRBS_ERR_CNT and RXPRBSERR_LOOPBACK attributes in Tab le 4 -3 2. Replaced

GTXRESET with GTXRXRESET in Use Models, page 216. Changed PCOMMA_ALIGN and

MCOMMA_ALIGN to PCOMMA_DETECT and MCOMMA_DETECT, respectively, in

Alignment Status Signals, page 219 and Ta b le 4 -3 4 . Updated RX Buffer Bypass, page 231 with

restrictions on RX buffer bypass operation. Updated descriptions of

CHAN_BOND_1/2_MAX_SKEW a nd CHAN_BOND_SEQ_LEN attribute in Ta bl e 4 - 49 .

Added guideline for asynchronous GTXTXRESET pulse width in GTX RX Reset in Response

to GTXRXRESET Pulse, page 263. Added description of power supply regulators for

MGTAVCC and VCCINT in Overview, page 283.

In Tab le B -1 , changed attribute encoding 3 in attribute bits 1:0 of DADDRs 7h, 12h, and 13h

to Reserved.

02/23/10 2.2 Updated descriptions of RXDLYALIGNOVERRIDE in Tab le 4 -4 0 and

RX_DLYALIGN_OVRDSETTING in Ta bl e 4 - 41 . Updated Using the RX Phase Alignment

Circuit to Bypass the Buffer, page 235, including Note 2 in Notes for Figure 4-32.. Updated

Figure 4-33.

Updated descriptions of DFETAPOVRD and DFEDLYOVRD ports after

UG366 (v2.5) January 17, 2011 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

Page 6

Date Version Revision

www.BDTIC.com/XILINX

05/24/10 2.3 Added description of buffer bypass mode to Multiple External Reference Clocks Use Model.

Added Power-Down Requirements for TX and RX Buffer Bypass.

Added description of TX buffer bypass to Functional Description, page 136 and Functional

Description, page 155.

Added description of RX buffer bypass to Functional Description, page 231. Updated

Functional Description, page 261 with description of buffer bypass mode. Removed

GTXTEST[12:0] from Tabl e 4 -5 2.

Updated Managing Unused GTX Transceivers. Replaced “group” with “bank” in Ta bl e 5-1 ,

Analog Power Supply Pins, and Partially Unused Quad Column. Added Note 2 to Ta bl e 5- 3

and Tab le 5 -4 . Added note about buffer bypass mode to Reference Clock Checklist. Added

Reference Clock Toggling.

10/01/10 2.4 Updated Functional Description, GTX TX Reset in Response to Completion of Configuration,

and GTX TX Reset in Response to GTXTXRESET Pulse.

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com UG366 (v2.5) January 17, 2011

Page 7

Date Version Revision

www.BDTIC.com/XILINX

01/17/11 2.5 Replaced PMA_COM_CFG with PMA_CFG in Ta bl e 2- 9. Replaced RXRATE with

RXRATE[1:0] in Chapter 4, Receiver. Added note before

TXDLYALIGNMONENB, RXDLYALIGNMONENB, PMA_RXSYNC_CFG,

TXDRIVE_LOOPBACK_HIZ, and TXDRIVE_LOOPBACK_PD to Ta bl e 1 -1. In Ta bl e 1 -1 ,

moved RX_PRBS_ERR_CNT from RX Pattern Checker to Status Registers (Read Only)

section. Added FF1154 Package Placement Diagrams, FF1155 Package Placement

Diagrams, FF1923 Package Placement Diagrams, and FF1924 Package Placement

Diagrams.

Updated Figure 2-1. Added RX_CLK25_DIVIDER and TX_CLK25_DIVIDER to Tab l e 2 -9 and

Tab le 1 -1 . Updated description of TXPDOWNASYNCH in Tab le 2 -11. Added BGTEST_CFG,

BIAS_CFG, and PMA_TX_CFG to Ta bl e 2 -1 2 and

ACJTAG. Updated Ta bl e 3 -1 0. Updated descriptions of TXDIFFCTRL[3:0],

TXPDOWNASYNCH, TXPOSTEMPHASIS[4:0], and TXPREEMPHASIS[3:0] in Ta b le 3 -3 1 .

Updated description of TXPOWERDOWN[1:0] in Tab le 3 -3 4.

Updated description of IGNORESIGDET and changed direction of RXVALID from In to Out

in Tab l e 4 -9 . Updated OOBDETECT_THRESHOLD attribute in Tab l e 4 -1 0 . Added Use Mode

– Fixed Tap Mode and Use Mode – Auto-To-Fix and Use Mode – Auto. Updated descriptions

of PMA_RX_CFG, RX_EN_IDLE_HOLD_CDR, RX_EN_IDLE_RESET_FR, and

RX_EN_IDLE_RESET_PH in Ta bl e 4 - 22 . Updated Eye Outline Scan Mode. Updated

description of RX_EYE_OFFSET in Ta bl e 4 - 27 . Updated description of PMA_RX_CFG in

Ta bl e 4 - 30 . Updated Figure 4-26. Added Manual Alignment, including Figure 4-27. Removed

RX_PRBS_ERR_CNT from Tab le 4 -3 2 and added it to Ta bl e 4 -3 3. Added RXSLIDE to

Ta bl e 4 - 34 and

MCOMMA_10B_VALUE, MCOMMA_DETECT, PCOMMA_10B_VALUE,

PCOMMA_DETECT, SHOW_REALIGN_COMMA, RX_SLIDE_MODE, and

RX_SLIDE_AUTO_WAIT to Ta b le 4 -3 5 and

of RX_LOS_THRESHOLD in Functional Description, page 226. Changed RX_DATA_WIDTH

attribute type in Ta bl e 4 - 39 . Added RXDLYALIGNMONENB to Tab le 4 - 40 . Added

PMA_RXSYNC_CFG to Ta bl e 4 -4 1. Changed direction of RXDATA[31:0] port from In to Out

in Tab le 4 -4 0.

Updated Common Package Power Plane Prioritization. Added Hot Swapping Devices.

Updated 2Ah and 47h rows of Ta ble B -1 . Added Tab le B -2 .

Added Appendix C, Low Latency Design.

Updated POWER_SAVE description in Ta ble 2 -1 2, Ta bl e 3 -1 9, and Ta bl e 4 -4 1. Updated

embedded table title of TXPOSTEMPHASIS[4:0] port in Tab le 3 - 31 . Updated description

of “From TX Parallel Data” in Figure 4-1 and Figure C-3. Updated Tab le 4 -2 . Updated

Use Mode – Auto-To-Fix and Use Mode – Auto. Updated Using the RX Phase Alignment

Circuit to Bypass the Buffer. Updated Figure 4-32 and Figure 4-34. Updated DADDR in

Tab le B -1.

Per XCN11009: Virtex-6: Data-Sheet, User Guides and JTAG ID Updates: Updated TX Buffer

Bypass: TX delay aligner bypassed, additional requirements on interconnect logic clocking

use model; Updated RX Buffer Bypass: RX delay aligner bypassed for lower line rates, higher

line rate support is an advanced feature.

Tab le 1 -1 . Updated description of ALIGN_COMMA_WORD, and added

Tab le 1 -1 . Updated Figure 4-28 and description

Tab le 1 -1 . Added

Tab le 1 -1 . Added Tab le 2 -1 7. Added

UG366 (v2.5) January 17, 2011 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

Page 8

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com UG366 (v2.5) January 17, 2011

www.BDTIC.com/XILINX

Page 9

Table of Contents

www.BDTIC.com/XILINX

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Additional Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Additional References. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Chapter 1: Transceiver and Tool Overview

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Port and Attribute Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Virtex-6 FPGA GTX Transceiver Wizard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

SIM_GTXRESET_SPEEDUP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

SIM_RECEIVER_DETECT_PASS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

SIM_RXREFCLK_SOURCE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

SIM_TXREFCLK_SOURCE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

SIM_VERSION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

SIM_TX_ELEC_IDLE_LEVEL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

FF484 Package Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

FF784 Package Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

FF1156 Package Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

FF1759 Package Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

FF1154 Package Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

FF1155 Package Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

FF1923 Package Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

FF1924 Package Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Chapter 2: Shared Transceiver Features

Reference Clock Input Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Use Modes: Reference Clock Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Reference Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Single External Reference Clock Use Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Multiple External Reference Clocks Use Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 9

UG366 (v2.5) January 17, 2011

Page 10

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

www.BDTIC.com/XILINX

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

PLL Settings for Common Protocols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Power Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Generic Power-Down Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

PLL Power Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

TX and RX Power Down. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Power-Down Requirements for TX and RX Buffer Bypass . . . . . . . . . . . . . . . . . . . . . 122

Power-Down Features for PCI Express Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

ACJTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Dynamic Reconfiguration Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Chapter 3: Transmitter

TX Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

FPGA TX Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Interface Width Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

TXUSRCLK and TXUSRCLK2 Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Using TXOUTCLK to Drive the GTX TX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

TXOUTCLK Driving a GTX TX in 2-Byte Mode (Single Lane) . . . . . . . . . . . . . . . . . . . 131

TXOUTCLK Driving a GTX TX in 4-Byte Mode (Single Lane) . . . . . . . . . . . . . . . . . . . 132

TXOUTCLK Driving a GTX TX in 1-Byte Mode (Single Lane) . . . . . . . . . . . . . . . . . . . 133

TXOUTCLK Driving More Than One GTX TX in 2-Byte Mode (Multiple Lanes). . . . . 133

TXOUTCLK Driving More Than One GTX TX in 4-Byte Mode (Multiple Lanes). . . . . 134

TXOUTCLK Driving More Than One GTX TX in 1-Byte Mode (Multiple Lanes). . . . . 135

TX Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

GTX TX Reset in Response to Completion of Configuration . . . . . . . . . . . . . . . . . . . 139

GTX TX Reset in Response to GTXTXRESET Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

GTX TX Component-Level Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

After Power-up and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

After Turning on a Reference Clock to the TX PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

After Changing the Reference Clock to the TX PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

After Assertion/Deassertion of TXPOWERDOWN . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

TX Rate Change with the TX Buffer Enabled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

TX Rate Change with the TX Buffer Bypassed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

TX Parallel Clock Source Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

TX 8B/10B Encoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

8B/10B Bit and Byte Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

K Characters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

10 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Page 11

Running Disparity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

www.BDTIC.com/XILINX

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Enabling and Disabling 8B/10B Encoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

TX Gearbox . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Enabling the TX Gearbox . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

TX Gearbox Bit and Byte Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

TX Gearbox Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

External Sequence Counter Operating Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Internal Sequence Counter Operating Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

TX Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Using the TX Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Using the TX Buffer for Oversampling Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

TX Buffer Bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Using the TX Phase-Alignment Circuit to Bypass the Buffer . . . . . . . . . . . . . . . . . . . 158

TX Phase Alignment after Rate Change Use Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Using the TX Phase Alignment Circuit to Minimize TX Lane-to-Lane Skew . . . . . . 160

Transmit Fabric Clocking Use Model for TX Buffer Bypass . . . . . . . . . . . . . . . . . . . . 161

TX Pattern Generator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Use Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

TX Oversampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

TX Polarity Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Using TX Polarity Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

TX Fabric Clock Output Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Serial Clock Divider . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Parallel Clock Divider and Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

PCI Express Clocking Use Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Rate Change Use Mode for PCI Express 2.0 Operation . . . . . . . . . . . . . . . . . . . . . . . . 171

TX Configurable Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Use Modes – TX Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

PCIe Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Customizable User Presets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Use Mode – Resistor Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

TX Receiver Detect Support for PCI Express Designs . . . . . . . . . . . . . . . . . . . . . . . 179

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 11

UG366 (v2.5) January 17, 2011

Page 12

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

www.BDTIC.com/XILINX

TX Out-of-Band Signaling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

Chapter 4: Receiver

RX Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

RX Analog Front End. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Use Modes – RX Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Use Mode – Resistor Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

RX Out-of-Band Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

RX Equalizer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Use Mode – Continuous Time RX Linear Equalizer Only . . . . . . . . . . . . . . . . . . . . . . 199

Use Mode – Fixed Tap Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Use Mode – Auto-To-Fix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Use Mode – Auto . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

RX CDR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

RX Fabric Clock Output Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Serial Clock Divider . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Parallel Clock Divider and Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

RX Margin Analysis. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Horizontal Eye Margin Scan. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Eye Outline Scan Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

RX Polarity Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Using RX Polarity Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

RX Oversampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Feature Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

RX Pattern Checker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Use Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

RX Byte and Word Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

Enabling Comma Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

Configuring Comma Patterns. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

12 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Page 13

Activating Comma Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

www.BDTIC.com/XILINX

Alignment Status Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

Alignment Boundaries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

Manual Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

RX Loss-of-Sync State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

RX 8B/10B Decoder. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

8B/10B Decoder Bit and Byte Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

RX Running Disparity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

RX Buffer Bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

Using the RX Phase Alignment Circuit to Bypass the Buffer . . . . . . . . . . . . . . . . . . . 235

RX Elastic Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

Using the RX Elastic Buffer for Channel Bonding or Clock Correction. . . . . . . . . . . 240

RX Clock Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

Using RX Clock Correction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Enabling Clock Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Setting RX Elastic Buffer Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Setting Clock Correction Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Clock Correction Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Monitoring Clock Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

RX Channel Bonding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

Using RX Channel Bonding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

Enabling Channel Bonding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

Channel Bonding Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

Connecting Channel Bonding Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Setting Channel Bonding Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

Setting the Maximum Skew . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

Precedence between Channel Bonding and Clock Correction . . . . . . . . . . . . . . . . . . . 255

RX Gearbox . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Enabling the RX Gearbox . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

RX Gearbox Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

RX Gearbox Block Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

RX Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

GTX RX Reset in Response to Completion of Configuration . . . . . . . . . . . . . . . . . . . 263

GTX RX Reset in Response to GTXRXRESET Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

Link Idle Reset Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 13

UG366 (v2.5) January 17, 2011

Page 14

GTX RX Component-Level Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

www.BDTIC.com/XILINX

After Power-up and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

After Turning on a Reference Clock to RX PLL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

After Changing the Reference Clock to RX PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

After Assertion/Deassertion of RXPOWERDOWN . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

RX Rate Change with RX Elastic Buffer Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

RX Rate Change with RX Elastic Buffer Bypassed . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

RX Parallel Clock Source Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

After Remote Power-Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

Electrical Idle Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

After Connecting RXN/RXP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

After an RX Elastic Buffer Error. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

Before Channel Bonding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

After Changing Channel Bonding Mode on the Fly . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

After a PRBS Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

After an Oversampler Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

After Comma Realignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

FPGA RX Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

Interface Width Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

RXUSRCLK and RXUSRCLK2 Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

Ports and Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

Chapter 5: Board Design Guidelines

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Pin Description and Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

GTX Transceiver Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Termination Resistor Calibration Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

Managing Unused GTX Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

Analog Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

Unused Quad Column . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

Partially Unused Quad Column . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

Partially Used Quad . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Quad Usage Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Reference Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

Reference Clock Checklist. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

Reference Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

LVDS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

LVPECL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

AC Coupled Reference Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Unused Reference Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Reference Clock Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Reference Clock Toggling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Power Supply and Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Power Supply Regulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Linear vs. Switching Regulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Linear Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Switching Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285

Power Supply Distribution Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

Staged Decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

14 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Page 15

Power Supply Decoupling Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

www.BDTIC.com/XILINX

Printed Circuit Board Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

Board Stackup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

GTX Transceiver Power Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

Signal BGA Breakout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

Crosstalk . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

Hot Swapping Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

SelectIO Usage Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

Appendix A: 8B/10B Valid Characters

Appendix B: DRP Address Map of the GTX Transceiver

Appendix C: Low Latency Design

GTX TX Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316

GTX RX Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 15

UG366 (v2.5) January 17, 2011

Page 16

16 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

www.BDTIC.com/XILINX

UG366 (v2.5) January 17, 2011

Page 17

About This Guide

www.BDTIC.com/XILINX

This document shows how to use the GTX transceivers in Virtex®-6 FPGAs. In this

document:

• Virtex-6 FPGA GTX transceiver is abbreviated as GTX transceiver.

• GTXE1 is the name of the instantiation primitive that instantiates one Virtex-6 FPGA

GTX transceiver.

•A Quad or Q is a cluster or set of four GTX transceivers that share two differential

reference clock pin pairs and analog supply pins.

Guide Contents

This manual contains the following chapters:

• Chapter 1, Transceiver and Tool Overview

• Chapter 2, Shared Transceiver Features

• Chapter 3, Transmitter

• Chapter 4, Receiver

• Chapter 5, Board Design Guidelines

• Appendix A, 8B/10B Valid Characters

• Appendix B, DRP Address Map of the GTX Transceiver

• Appendix C, Low Latency Design

Preface

Additional Documentation

The following documents are also available for download at

http://www.xilinx.com/

• Virtex-6 Family Overview

The features and product selection of the Virtex-6 family are outlined in this overview.

• Virtex-6 FPGA Data Sheet: DC and Switching Characteristics

This data sheet contains the DC and Switching Characteristic specifications for the

Virtex-6 family.

• Virtex-6 FPGA Packaging and Pinout Specifications

This specification includes the tables for device/package combinations and maximum

I/Os, pin definitions, pinout tables, pinout diagrams, mechanical drawings, and

thermal specifications.

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 17

UG366 (v2.5) January 17, 2011

products/virtex6.

Page 18

Preface: About This Guide

www.BDTIC.com/XILINX

• Virtex-6 FPGA Configuration User Guide

• Virtex-6 FPGA SelectIO Resources User Guide

• Virtex-6 FPGA Clocking Resources User Guide

• Virtex-6 FPGA Memory Resources User Guide

• Virtex-6 FPGA Configurable Logic Block User Guide

• Virtex-6 FPGA DSP48E1 Slice User Guide

This all-encompassing configuration guide includes chapters on configuration

interfaces (serial and SelectMAP), bitstream encryption, boundary-scan and JTAG

configuration, reconfiguration techniques, and readback through the SelectMAP and

JTAG interfaces.

This guide describes the SelectIO™ resources available in all Virtex-6 devices.

This guide describes the clocking resources available in all Virtex-6 devices, including

the MMCM and PLLs.

The functionality of the block RAM and FIFO are described in this user guide.

This guide describes the capabilities of the configurable logic blocks (CLBs) available

in all Virtex-6 devices.

This guide describes the architecture of the DSP48E1 slice in Virtex-6 FPGAs and

provides configuration examples.

• Virtex-6 FPGA Embedded Tri-Mode Ethernet MAC User Guide

This guide describes the dedicated Tri-Mode Ethernet Media Access Controller

available in all Virtex-6 FPGAs except the XC6VLX760.

• Virtex-6 FPGA System Monitor User Guide

The System Monitor functionality available in all Virtex-6 devices is outlined in this

guide.

• Virtex-6 FPGA PCB Designer’s Guide

This guide provides information on PCB design for Virtex-6 FPGA GTX transceivers,

with a focus on strategies for making design decisions at the PCB and interface level.

Additional Resources

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/support/documentation/index.htm

To search the Answer Database of silicon, software, and IP questions and answers, or to

create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support

Additional References

.

.

The following documents provide additional information useful to this document:

1. High-Speed Serial I/O Made Simple

http://www.xilinx.com/publications/books/serialio/index.htm

18 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Page 19

Transceiver and Tool Overview

www.BDTIC.com/XILINX

Overview

The Virtex®-6 FPGA GTX transceiver is a power-efficient transceiver. The GTX transceiver

is highly configurable and tightly integrated with the programmable logic resources of the

FPGA. It provides the following features to support a wide variety of applications:

• Current Mode Logic (CML) serial drivers/buffers with configurable termination,

voltage swing

• Programmable TX pre-emphasis/post-emphasis, RX equalization, and linear and

decision feedback equalization (DFE) for optimized signal integrity.

• Line rates from 600 Mb/s to 6.6 Gb/s, with optional 5X digital oversampling required

for rates between 480 Mb/s and 600 Mb/s.

• Optional built-in PCS features, such as 8B/10B encoding, comma alignment, channel

bonding, and clock correction.

• Fixed latency modes for minimized, deterministic datapath latency.

• Beacon signaling for PCI Express® designs and Out-of-Band signaling including

COM signal support for SATA designs.

• RX/TX Gearbox provides header insertion and extraction support for 64B/66B and

64B/67B (Interlaken) protocols.

• Receiver eye scan

Horizontal eye scan in the time domain for testing purposes

Chapter 1

The first-time user is recommended to read High-Speed Serial I/O Made Simple [Ref 1], which

discusses high-speed serial transceiver technology and its applications. The

CORE Generator™ tool includes a Wizard to automatically configure GTX transceivers to

support configurations for different protocols or perform custom configuration (see

Virtex-6 FPGA GTX Transceiver Wizard). The GTX transceiver offers a data rate range and

features that allow physical layer support for various protocols.

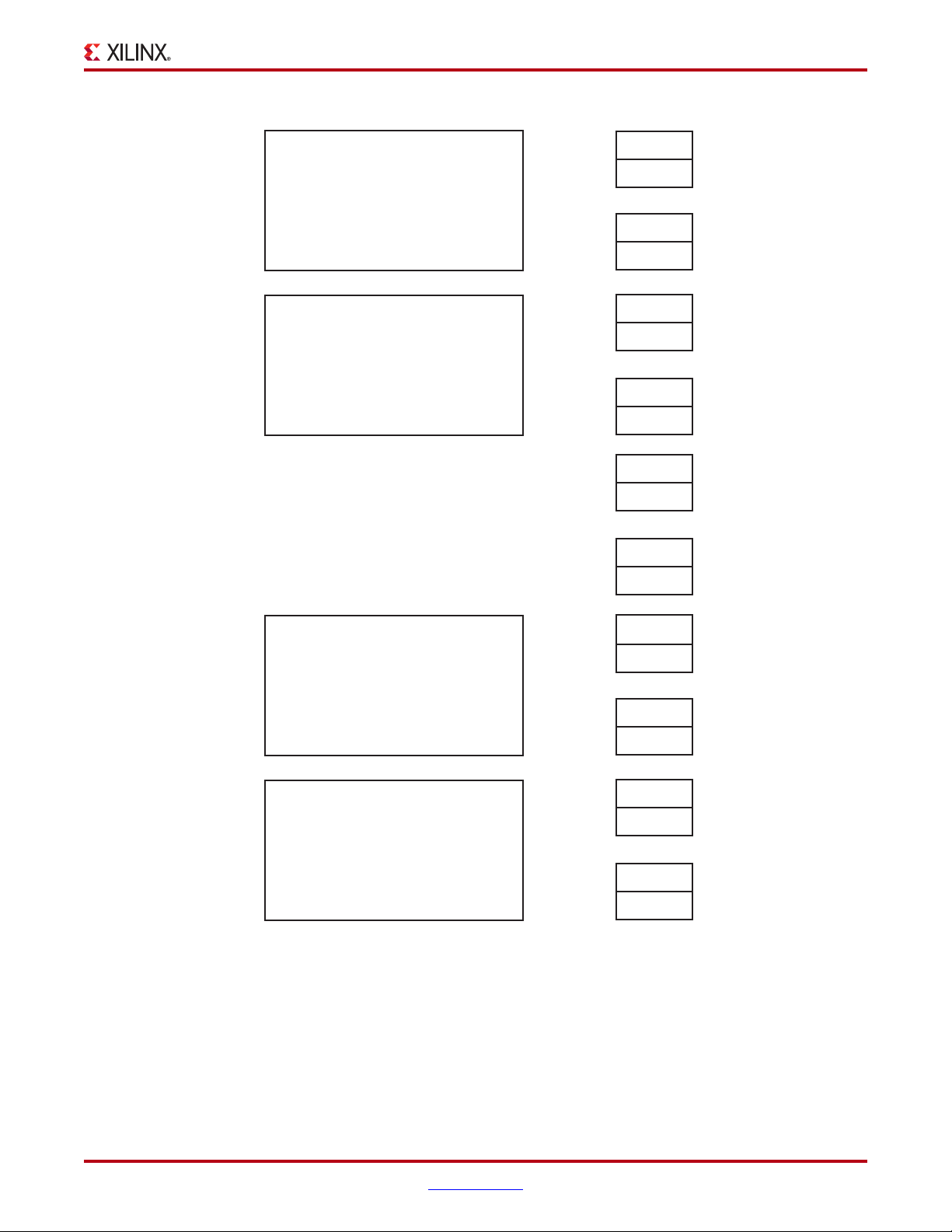

Figure 1-1 illustrates a block view of the Virtex-6 FPGA GTX transceiver.

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 19

UG366 (v2.5) January 17, 2011

Page 20

Chapter 1: Transceiver and Tool Overview

www.BDTIC.com/XILINX

X-Ref Target - Figure 1-1

TX

Gearbox

TX PIPE

Control

FPGA

TX

Interface

8B/

10B

TX

Driver

TX

OOB

and

PCIe

TX

Pre/

Post

emp

PISO

PLL

Polarity

Pattern

Generator

Phase

Adjust

FIFO &

Over-

sampling

PCIe

Beacon

SATA

OOB

TX-PMA TX-PCS

PLL

To RX Parallel

Data (Near-End

PCS Loopback)

Pattern

Checker

From RX Parallel Data

(Far-End PMA Loopback)

Loss of Sync

From RX Parallel Data

(Far-End PCS Loopback)

RX PIPE Control

RX Status Control

RX

Gearbox

FPGA

RX

Interface

RX

EQ

RX OOB

DFE

RX

CDR

SIPO

Polarity

Over-

sampling

Comma

Detect

and

Align

Elastic

Buffer

10B

/8B

RX-PMA RX-PCS

UG366_c1_01_051509

Figure 1-1: Virtex-6 FPGA GTX Transceiver Simplified Block Diagram

Details about the different functional blocks of the transmitter and receiver including their

use models are described in Chapter 3, Transmitter, and Chapter 4, Receiver.

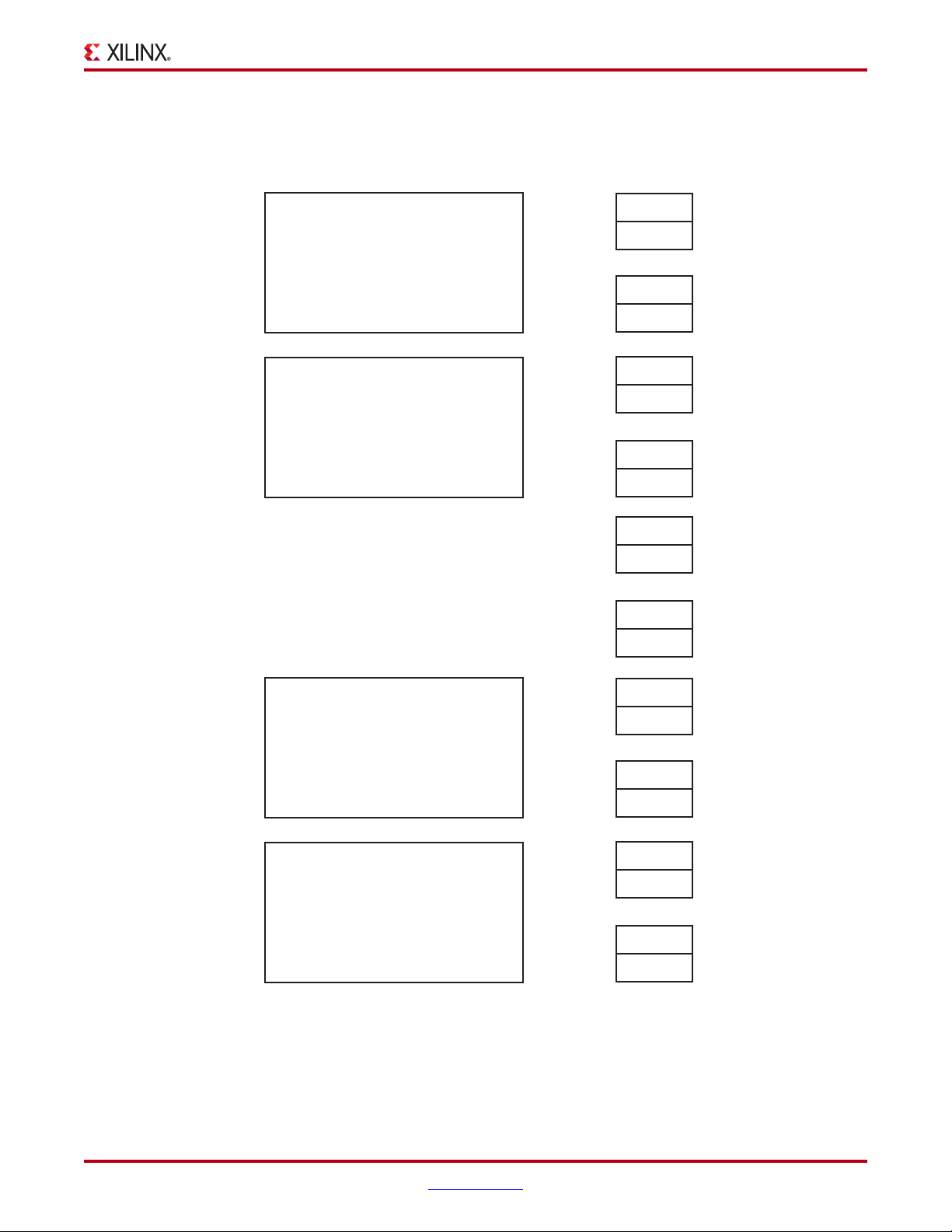

Figure 1-2 shows the GTX transceiver placement in an example Virtex-6 device

(XC6VLX75T).

Additional information on the functional blocks in Figure 1-2 is available in the following

locations:

20 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Page 21

Overview

www.BDTIC.com/XILINX

•The Virtex-6 FPGA Configuration User Guide provides more information on the

Configuration and Clock, MMCM, and I/O blocks.

•The Virtex-6 FPGA Embedded Tri-Mode Ethernet MAC User Guide provides detailed

information on the Ethernet MAC.

Figure 1-2 illustrates the location of the GTX transceiver inside the Virtex-6 XC6VLX75T

FPGA.

X-Ref Target - Figure 1-2

Virtex-6 FPGA (XC6VLX75T)

GTXE1

Column

GTXE1_

X0Y11

MMCM

Ethernet

MAC

GTXE1_

X0Y10

I/O

Column

I/O

Column

Configuration

MMCM

MMCM

I/O

Column

Ethernet

MAC

Integrated

Block for

PCI Express

Operation

Ethernet

MAC

Ethernet

MAC

GTXE1_

X0Y9

GTXE1_

X0Y8

GTXE1_

X0Y7

GTXE1_

X0Y6

GTXE1_

X0Y5

GTXE1_

X0Y4

GTXE1_

X0Y3

GTXE1_

X0Y2

GTXE1_

X0Y1

GTXE1_

X0Y0

Figure 1-2: GTX Transceiver Inside the Virtex-6 XC6VLX75T FPGA

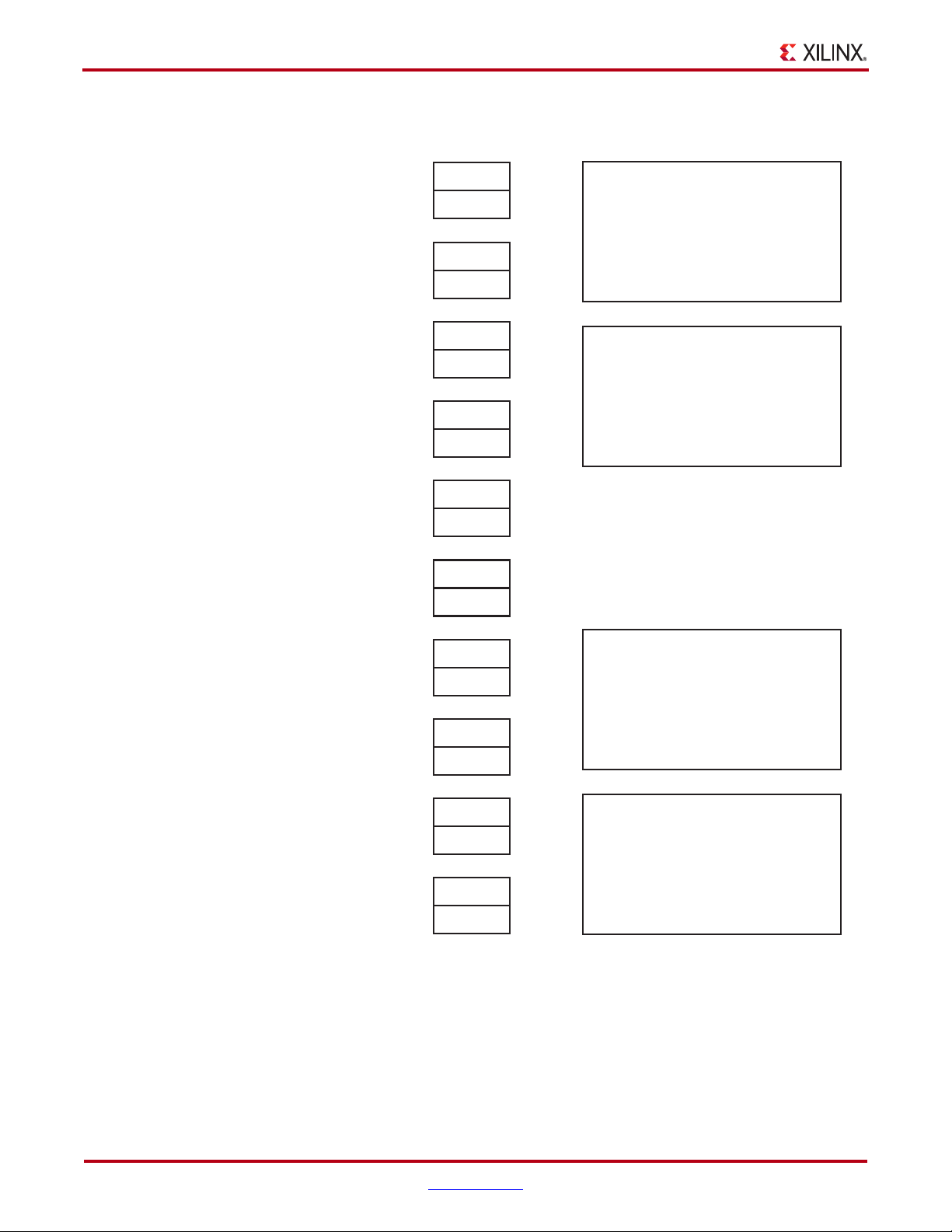

GTX transceivers are clustered together in a set of four called a Quad or Q. Figure 1-3

illustrates the clustering of four GTX transceivers to a Quad. Refer to Implementation,

page 41 for placement information and the mapping of each transceiver into a specific

Quad.

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 21

UG366 (v2.5) January 17, 2011

UG366_c1_02_051509

Page 22

Chapter 1: Transceiver and Tool Overview

From/To Adjacent Quad

From/To Adjacent Quad

UG366_c1_03_051509

TX-P2S

RX0

To FPGA Logic

CLKs TX PLLPCS

RX DFE, CDR, S2P

CLKs RX PLL

From FPGA Logic

TX0

TX-P2S

RX1

To FPGA Logic

CLKs TX PLLPCS

RX DFE, CDR, S2P

CLKs RX PLL

From FPGA Logic

TX1

TX-P2S

RX2

To FPGA Logic

CLKs TX PLLPCS

RX DFE, CDR, S2P

CLKs RX PLL

From FPGA Logic

TX2

TX-P2S

RX3

To FPGA Logic

CLKs TX PLLPCS

RX DFE, CDR, S2P

CLKs RX PLL

From FPGA Logic

TX3

MGTREFCLK0

MGTREFCLK1

www.BDTIC.com/XILINX

X-Ref Target - Figure 1-3

Figure 1-3: Quad Configuration

22 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Page 23

This cluster of four GTX transceivers share two differential reference clock pin pairs and

www.BDTIC.com/XILINX

clock routing. Chapter 2, Shared Transceiver Features, discusses details about reference

clock sources and the routing.

Port and Attribute Summary

The ports and attributes are grouped in tables for each functionality group (e.g., reference

clock selection). If a port or attribute appears in multiple chapters, it is listed in the group

of its first appearance. Ta bl e 1 -1 summarizes the ports and attributes according to

functionality group.

Port and Attribute Summary

Note:

are present in the instantiation primitive or are listed in Appendix B, DRP Address Map of the GTX

Transceiver but not in Ta bl e 1 - 1 .

Table 1-1: Port and Attribute Summary

Ta bl e 1 - 1 lists all the ports and attributes covered in this user guide. Some ports or attributes

Port/Attribute Section, Page

Simulation

Attributes:

• SIM_GTXRESET_SPEEDUP

• SIM_RECEIVER_DETECT_PASS

• SIM_RXREFCLK_SOURCE

• SIM_TX_ELEC_IDLE_LEVEL

• SIM_TXREFCLK_SOURCE

• SIM_VERSION

Clocking

Ports:

• GREFCLKRX

• GREFCLKTX

• MGTREFCLKRX[1:0]

• MGTREFCLKTX[1:0]

• NORTHREFCLKRX[1:0]

• NORTHREFCLKTX[1:0]

• PERFCLKRX

• PERFCLKTX

• RXPLLREFSELDY[2:0]

• SOUTHREFCLKRX[1:0]

• SOUTHREFCLKTX[1:0]

• TXPLLREFSELDY[2:0]

page 38

page 38

page 39

page 39

page 39

page 39

page 106

page 106

page 106

page 106

page 106

page 106

page 106

page 106

page 107

page 107

page 107

page 107

Attributes:

• PMA_CAS_CLK_EN

• SIM_RXREFCLK_SOURCE[2:0]

• SIM_TXREFCLK_SOURCE[2:0]

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 23

UG366 (v2.5) January 17, 2011

page 107

page 107

page 107

Page 24

Chapter 1: Transceiver and Tool Overview

www.BDTIC.com/XILINX

Table 1-1: Port and Attribute Summary (Cont’d)

Port/Attribute Section, Page

PLL

Ports:

• PLLTXRESET

• PLLRXRESET

• TXPLLLKDET

• RXPLLLKDET

• TXPLLLKDETEN

• RXPLLLKDETEN

• TXPLLPOWERDOWN

• RXPLLPOWERDOWN

Attributes:

• PMA_CFG

• TX_CLK_SOURCE

• TX_TDCC_CFG

• TXPLL_COM_CFG

• RXPLL_COM_CFG

• TXPLL_CP_CFG

• RXPLL_CP_CFG

• TXPLL_DIVSEL_FB

• RXPLL_DIVSEL_FB

• TXPLL_DIVSEL_OUT

• RXPLL_DIVSEL_OUT

• TXPLL_DIVSEL_REF

• RXPLL_DIVSEL_REF

• TXPLL_DIVSEL45_FB

• RXPLL_DIVSEL45_FB

• TXPLL_LKDET_CFG

• RXPLL_LKDET_CFG

• TXPLL_SATA

• RX_CLK25_DIVIDER

• TX_CLK25_DIVIDER

page 115

page 115

page 115

page 115

page 115

page 115

page 115

page 115

page 115

page 115

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 116

page 117

page 117

Power Down

Ports:

• RXPLLPOWERDOWN

• RXPOWERDOWN[1:0]

• TXPDOWNASYNCH

• TXPLLPOWERDOWN

• TXPOWERDOWN[1:0]

24 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

page 120

page 120

page 120

page 120

page 120

UG366 (v2.5) January 17, 2011

Page 25

Table 1-1: Port and Attribute Summary (Cont’d)

www.BDTIC.com/XILINX

Port/Attribute Section, Page

Attributes:

• BGTEST_CFG

• BIAS_CFG

• PMA_TX_CFG

• POWER_SAVE

• TRANS_TIME_FROM_P2

• TRANS_TIME_NON_P2

• TRANS_TIME_RATE

• TRANS_TIME_TO_P2

Loopback

Ports:

• LOOPBACK[2:0]

Attributes:

• TXDRIVE_LOOPBACK_HIZ

• TXDRIVE_LOOPBACK_PD

Port and Attribute Summary

page 121

page 121

page 121

page 121

page 121

page 121

page 121

page 121

page 125

page 125

page 125

DRP

Ports:

• DADDR[7:0]

• DCLK

• DEN

• DI[15:0]

• DRPDO[15:0]

• DRDY

• DWE

FPGA TX Interface

Ports:

• MGTREFCLKFAB[1:0]

• TXCHARDISPMODE[3:0]

• TXCHARDISPVAL[3:0]

• TXDATA[31:0]

• TXUSRCLK

• TXUSRCLK2

Attributes:

• GEN_TXUSRCLK

• TX_DATA_WIDTH

page 126

page 126

page 126

page 126

page 126

page 126

page 126

page 130

page 130

page 130

page 130

page 130

page 130

page 131

page 131

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 25

UG366 (v2.5) January 17, 2011

Page 26

Chapter 1: Transceiver and Tool Overview

www.BDTIC.com/XILINX

Table 1-1: Port and Attribute Summary (Cont’d)

Port/Attribute Section, Page

TX Initialization

Ports:

• GTXTEST[12:0]

• GTXTXRESET

• PLLTXRESET

• TSTIN[19:0]

• TXDLYALIGNRESET

• TXRESET

• TXRESETDONE

Attributes:

• TX_EN_RATE_RESET_BUF

TX Encoder

Ports:

• TXBYPASS8B10B[3:0]

• TXCHARDISPMODE[3:0]

• TXCHARDISPVAL[3:0]

• TXCHARISK[3:0]

• TXENC8B10BUSE

• TXKERR[3:0]

• TXRUNDISP[3:0]

page 138

page 138

page 138

page 138

page 138

page 138

page 138

page 138

page 145

page 145

page 145

page 145

page 145

page 146

page 146

TX Gearbox

Ports:

• TXGEARBOXREADY

• TXHEADER[2:0]

• TXSEQUENCE[6:0]

• TXSTARTSEQ

Attributes:

• GEARBOX_ENDEC

• TXGEARBOX_USE

TX Buffer

Ports:

• TXBUFSTATUS[1:0]

• TXRESET

Attributes:

• TX_BUFFER_USE

• TX_OVERSAMPLE_MODE

TX Buffer Bypass

page 147

page 147

page 147

page 147

page 147

page 147

page 154

page 154

page 154

page 154

26 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Page 27

Table 1-1: Port and Attribute Summary (Cont’d)

www.BDTIC.com/XILINX

Port/Attribute Section, Page

Ports:

• TXDLYALIGNDISABLE

• TXDLYALIGNMONENB

• TXDLYALIGNMONITOR[7:0]

• TXDLYALIGNOVERRIDE

• TXDLYALIGNRESET

• TXDLYALIGNUPDSW

• TXENPMAPHASEALIGN

• TXOUTCLK

• TXPLLLKDET

• TXPLLLKDETEN

• TXPMASETPHASE

• TXUSRCLK

Attributes:

• TX_BUFFER_USE

• TX_BYTECLK_CFG[5:0]

• TX_DATA_WIDTH

• TX_DLYALIGN_CTRINC

• TX_DLYALIGN_LPFINC

• TX_DLYALIGN_MONSEL

• TX_DLYALIGN_OVRDSETTING

• TX_PMADATA_OPT

• TX_XCLK_SEL

• TXOUTCLK_CTRL

Port and Attribute Summary

page 155

page 155

page 155

page 155

page 155

page 155

page 156

page 156

page 156

page 156

page 156

page 156

page 157

page 157

page 157

page 157

page 157

page 157

page 157

page 157

page 158

page 158

TX Pattern Generator

Ports:

• TXENPRBSTST[2:0]

• TXPRBSFORCEERR

Attributes:

• RXPRBSERR_LOOPBACK

TX Oversampling

Attributes:

• TX_OVERSAMPLE_MODE

TX Polarity Control

Ports:

• TXPOLARITY

TX Fabric Clock Output Control

page 164

page 164

page 164

page 166

page 166

Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 27

UG366 (v2.5) January 17, 2011

Page 28

Chapter 1: Transceiver and Tool Overview

www.BDTIC.com/XILINX

Table 1-1: Port and Attribute Summary (Cont’d)

Port/Attribute Section, Page

Ports:

• GTXTEST[1]

• MGTREFCLKFAB[0]

• O

• ODIV2

• PHYSTATUS

• TXOUTCLK

• TXOUTCLKPCS

• TXRATE

• TXRATEDONE

Attributes:

• TRANS_TIME_RATE

• TX_EN_RATE_RESET_BUF

• TXOUTCLK_CTRL

• TXPLL_DIVSEL_OUT

page 169

page 169

page 169

page 169

page 169

page 169

page 169

page 170

page 170

page 170

page 170

page 170

page 170

TX Configurable Driver

Ports:

• TXBUFDIFFCTRL[2:0]

• TXDEEMPH

• TXDIFFCTRL[3:0]

• TXELECIDLE

• TXINHIBIT

• TXMARGIN[2:0]

• TXPDOWNASYNCH

• TXPOSTEMPHASIS[4:0]

• TXPREEMPHASIS[3:0]

• TXP TXN

• TXSWING

Attributes:

• TX_DEEMPH_0[4:0]

• TX_DEEMPH_1[4:0]

• TX_DRIVE_MODE

• TX_MARGIN_FULL_0[6:0]

• TX_MARGIN_FULL_1[6:0]

• TX_MARGIN_FULL_2[6:0]

• TX_MARGIN_FULL_3[6:0]

• TX_MARGIN_FULL_4[6:0]

• TX_MARGIN_LOW_0[6:0]

• TX_MARGIN_LOW_1[6:0]

• TX_MARGIN_LOW_2[6:0]

• TX_MARGIN_LOW_3[6:0]

• TX_MARGIN_LOW_4[6:0]

page 173

page 173

page 174

page 174

page 174

page 174

page 175

page 175

page 176

page 176

page 176

page 176

page 176

page 177

page 177

page 177

page 177

page 177

page 177

page 177

page 177

page 178

page 178

page 178

28 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Page 29

Table 1-1: Port and Attribute Summary (Cont’d)

www.BDTIC.com/XILINX

Port/Attribute Section, Page

TX Receiver Detect Support for PCI Express Designs

Ports:

• PHYSTATUS

• RXPOWERDOWN[1:0]

• TXPOWERDOWN[1:0]

• RXSTATUS[2:0]

• TXDETECTRX

TX OOB

Ports:

• COMFINISH

• TXCOMINIT

• TXCOMSAS

• TXCOMWAKE

• TXELECIDLE

• TXPOWERDOWN[1:0]

Port and Attribute Summary

page 179

page 180

page 180

page 180

page 180

page 181

page 181

page 181

page 181

page 181

page 181

Attributes:

• COM_BURST_VAL

• TXPLL_SATA

RX AFE

Ports:

• RXN

• RXP

Attributes:

• AC_CAP_DIS

• CM_TRIM[1:0]