Page 1

ML361 Virtex-II Pro

DDR400/PC3200 Memory

Board User Guide

UG060 (v1.2) November 8, 2007

R

Page 2

R

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development

of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the

Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise,

without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves

the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors

contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with

technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER

WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY

RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL

DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2004–2007 Xilinx, Inc. All rights reserved.

XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks

are the property of their respective owners.

ML361 Virtex-II Pro DDR400/PC3200 Memory Board User Guide

UG060 (v1.2) November 8, 2007

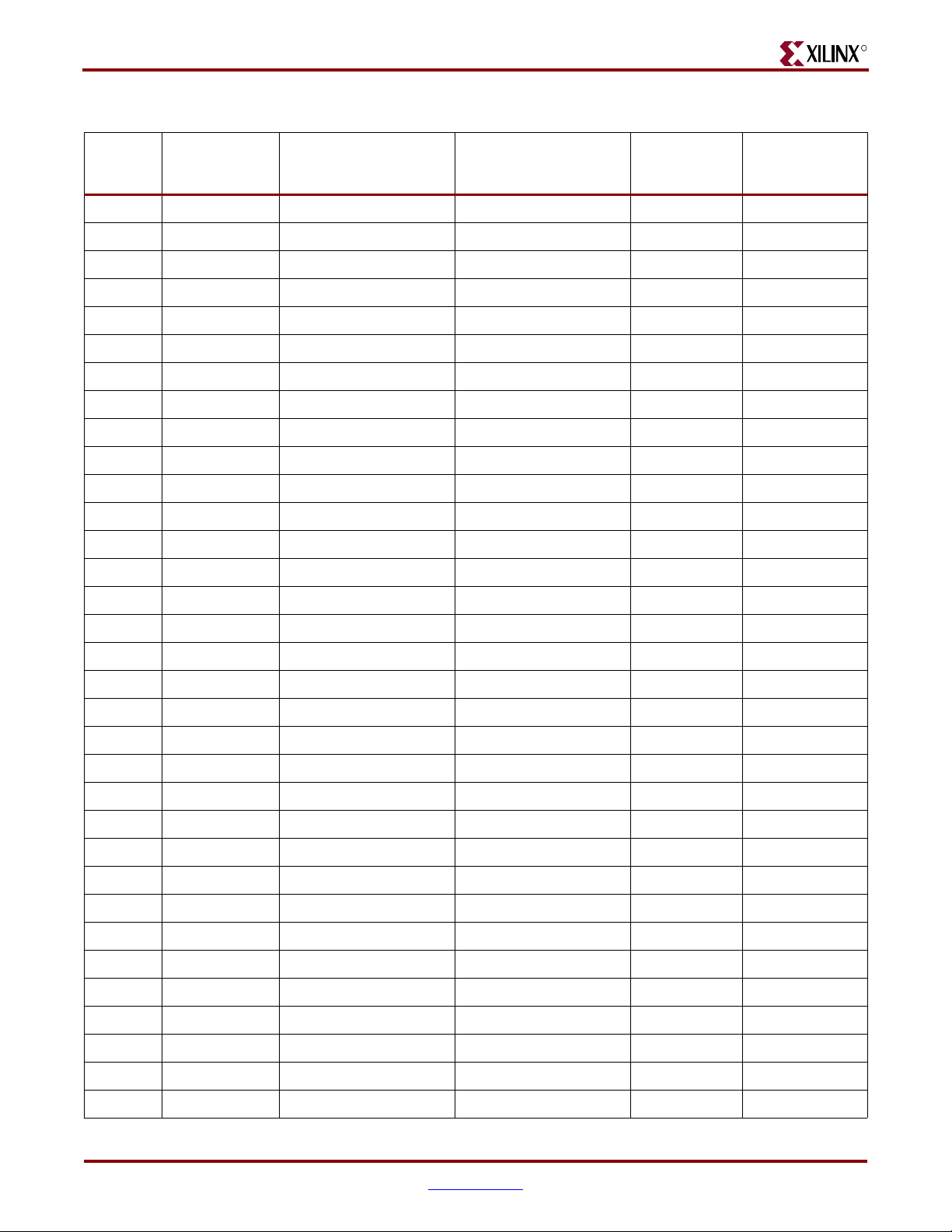

The following table shows the revision history for this document.

Version Revision

01/23/04 1.0 Initial Xilinx release.

03/26/04 1.1 Revised Figure 4-6, Figure 4-7, Figure 4-8, Figure 4-9, Figure 4-26, and Figure 4-27.

11/08/07 1.2

• Ta bl e 5 -1 : Typographical corrections.

• Ta bl e B -1 : Deleted Slice Coordinates column from table.

• Updated copyright notice and legal disclaimer.

ML361 Virtex-II Pro Memory Board www.xilinx.com UG060 (v1.2) November 8, 2007

Page 3

Table of Contents

Schedule of Figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Schedule of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Online Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Chapter 1: Introduction

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Chapter 2: Architecture

ML361 Board Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Block Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Memories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

DDR SDRAM DIMM (Banks 6 and 7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

DDR SDRAM Components (Banks 2 and 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

DDR SDRAM Component (Bank 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

RS232 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

200 MHz LVDS Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

166 MHz LVDS Test Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

SMA Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

User I/Os. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Mictor Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Seven-Segment Displays. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Push Buttons. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Grounded I/Os. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Power Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.3 V Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.6 V Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.5 V Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.3 V Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Linear Regulators for the MGTs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

ML361 Virtex-II Pro Memory Board www.xilinx.com 3

UG060 (v1.2) November 8, 2007

Page 4

FPGA Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

PROMs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Chapter 3: Electrical Requirements

Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

FPGA Internal Power Budget. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Chapter 4: Signal Integrity Recommendations and Simulations

Termination and Transmission Line Summaries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Terminations and Transmission Lines for DDR Components . . . . . . . . . . . . . . . . . . . 26

Data and Clock Signals (DQ, DQS, DM, CLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Address and Control Signals (A, BA, RASn, CASn, WEn, CSn, CKE) . . . . . . . . . . . . . . 26

Terminations and Transmission Lines for the DIMM . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Data and Clock Signals (DQ, DQS, DM, CLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Address and Control Signals (A, BA, RASn, CASn, WEn, CSn, CKE) . . . . . . . . . . . . . . 27

Duty Cycle Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

IBIS Simulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Notes on the Simulation Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Data Signal Simulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Data Signals from the FPGA to Memory (SSTL2_C2 at FPGA). . . . . . . . . . . . . . . . . . . . 32

Data Signals from the Last Memory to the FPGA: Measured at FPGA. . . . . . . . . . . . . . 36

Clock Signal Simulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Address and Control Signal Simulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Simulations with 10% Tolerance on the Transmission Line Impedance . . . . . . . . . . . 56

Data Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Clock Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Address/Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

R

Chapter 5: Board Layout Guidelines

Decoupling Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Providing Additional Ground Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Board Stackup Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Appendix A: Related Documentation

Appendix B: FPGA Pinout

4 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 5

Schedule of Figures

Chapter 1: Introduction

Figure 1-1: Simplified Block Diagram of Memory Board Interfaces . . . . . . . . . . . . . . . . . 11

Chapter 2: Architecture

Figure 2-1: ML361 Board Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Chapter 3: Electrical Requirements

Chapter 4: Signal Integrity Recommendations and Simulations

Figure 4-1: Data Signal Terminations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 4-2: Data Signal from FPGA to Memory (Typical Case) . . . . . . . . . . . . . . . . . . . . . 32

Figure 4-3: Data Signal from FPGA to Memory (Slow Weak Case). . . . . . . . . . . . . . . . . . 33

Figure 4-4: Data Signal from FPGA to Memory (Fast Strong Case) . . . . . . . . . . . . . . . . . . 34

Figure 4-5: Eye Diagram for Data from the FPGA to Last Memory Component. . . . . . . 35

Figure 4-6: Data Signal from Last Memory at FPGA (Typical Case) . . . . . . . . . . . . . . . . . 36

Figure 4-7: Data Signal from Last Memory at FPGA (Slow Weak Corner Case). . . . . . . 37

Figure 4-8: Data Signal from Memory at FPGA (Fast Strong Corner Case) . . . . . . . . . . . 38

Figure 4-9: Eye Diagram for Data at the FPGA to the Last Memory Component . . . . . . 39

Figure 4-10: Clock Signal Terminations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 4-11: Clock Signal from FPGA to Memory (Typical Case) . . . . . . . . . . . . . . . . . . . 41

Figure 4-12: Clock Signal from FPGA to Memory (Slow Weak Case). . . . . . . . . . . . . . . . 42

Figure 4-13: Clock Signal from FPGA to Memory (Fast Strong Case) . . . . . . . . . . . . . . . . 43

Figure 4-14: Eye Diagram for Clock at Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 4-15: Address and Control Signal Terminations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 4-16: Address/Control Signals for All Memories . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 4-17: Address/Control Signals at First DDR Memory (Typical Case). . . . . . . . . . 47

Figure 4-18: Address/Control Signals at First DDR Memory (Slow Weak Case) . . . . . . 48

Figure 4-19: Address/Control Signals at First DDR Memory (Fast Strong Case) . . . . . . 49

Figure 4-20: Address/Control Signals at Last DDR Memory (Typical Case) . . . . . . . . . . 50

Figure 4-21: Address/Control Signals at Last DDR Memory (Slow Weak Case). . . . . . . 51

Figure 4-22: Address/Control Signals at Last DDR Memory (Fast Strong Corner Case) 52

Figure 4-23: Address/Control Signals at Middle DDR Memory (Typical Case) . . . . . . . 53

Figure 4-24: Address/Control Signals at Middle DDR Memory (Slow Weak Corner

Case) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 4-25: Address/Control Signals at Middle DDR Memory (Fast Strong Corner

Case) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 4-26: Data Signals from Last DDR Memory to FPGA (45Ω Impedance) . . . . . . . 56

Figure 4-27: Data Signals from Last DDR Memory to FPGA (55Ω Impedance) . . . . . . . 57

Figure 4-28: Data Signals from FPGA to Last DDR Memory (45Ω Impedance) . . . . . . . 58

ML361 Virtex-II Pro Memory Board www.xilinx.com 5

UG060 (v1.2) November 8, 2007

Page 6

Figure 4-29: Data Signals from Memory to FPGA (55Ω Impedance) . . . . . . . . . . . . . . . . . 59

Figure 4-30: Clock Signals with 45Ω Impedance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 4-31: Clock Signals with 55Ω Impedance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 4-32: Address/Control Signals with 45Ω Impedance Measured at First DDR

Component . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 4-33: Address/Control Signals with 55Ω Impedance Measured at First DDR

Component . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Chapter 5: Board Layout Guidelines

Appendix A: Related Documentation

Appendix B: FPGA Pinout

R

6 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 7

Schedule of Tables

Chapter 1: Introduction

Chapter 2: Architecture

Table 2-1: GPIO Header 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 2-2: GPIO Header 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2-3: DIP Switch Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2-4: Display 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2-5: Display 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 2-6: LED Connections to FPGA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Chapter 3: Electrical Requirements

Table 3-1: ML361 Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 3-2: XC2VP20FF1152 Estimated Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 3-3: XC2VP20FF1152 Temperature Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 3-4: Device Quiescent Power. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 3-5: CLB Logic Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 3-6: Digital Clock Manager Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 3-7: Input/Output Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Chapter 4: Signal Integrity Recommendations and Simulations

Table 4-1: DDR SDRAM Terminations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 4-2: DIMM Terminations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 4-3: Duty Cycle Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Chapter 5: Board Layout Guidelines

Table 5-1: FPGA Decoupling Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 5-2: DDR SDRAM Decoupling Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 5-3: DIMM Decoupling Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 5-4: 16-Layer Board Stackup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Appendix A: Related Documentation

Appendix B: FPGA Pinout

Table B-1: FPGA Pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

ML361 Virtex-II Pro Memory Board www.xilinx.com 7

UG060 (v1.2) November 8, 2007

Page 8

R

8 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 9

R

About This Guide

This document describes the design of the ML361 Virtex-II Pro™ DDR400/PC3200

Memory Board, which connects a Virtex-II Pro FPGA to DDR memories.

Guide Contents

This manual contains the following chapters:

• Chapter 1, “Introduction,” describes the purpose of the ML361 board and provides its

key features.

• Chapter 2, “Architecture,” provides a block diagram of the memory board and

describes the key components.

• Chapter 3, “Electrical Requirements,” lists the electrical specifications for the memory

board.

• Chapter 4, “Signal Integrity Recommendations and Simulations,” provides

information on termination, transmission lines, and duty cycles. It also gives the

results of several IBIS simulations.

• Chapter 5, “Board Layout Guidelines,” provides information on decoupling

capacitors, ground signals, and PCB layout.

• Appendix A, “Related Documentation,” lists data sheet and external website

references specific to the ML361 components.

• Appendix B, “FPGA Pinout,” provides the pinout of the Virtex-II Pro FPGA.

Preface

Additional Resources

For additional information, go to http://support.xilinx.com. The following table lists

some of the resources you can access from this website. You can also directly access these

resources using the provided URLs.

Resource Description/URL

Tutorials Tutorials covering Xilinx design flows, from design entry to verification

and debugging

http://support.xilinx.com/support/techsup/tutorials/index.htm

Answer Browser Database of Xilinx solution records

http://support.xilinx.com/xlnx/xil_ans_browser.jsp

Application Notes Descriptions of device-specific design techniques and approaches

http://support.xilinx.com/apps/appsweb.htm

ML361 Virtex-II Pro Memory Board www.xilinx.com 9

UG060 (v1.2) November 8, 2007

Page 10

Preface: About This Guide

Data Sheets Device-specific information on Xilinx device characteristics, including

Problem Solvers Interactive tools that allow you to troubleshoot your design issues

Tech Tips Latest news, design tips, and patch information for the Xilinx design

Conventions

This document uses the following conventions. An example illustrates each convention.

Typographical

The following typographical conventions are used in this document:

R

Resource Description/URL

readback, boundary scan, configuration, length count, and debugging

http://support.xilinx.com/xlnx/xweb/xil_publications_index.jsp

http://support.xilinx.com/support/troubleshoot/psolvers.htm

environment

http://www.support.xilinx.com/xlnx/xil_tt_home.jsp

Convention Meaning or Use Example

Italic font

Online Document

The following conventions are used in this document:

Convention Meaning or Use Example

Blue text

Blue, underlined text

References to other manuals

Emphasis in text

Cross-reference link to a location

in the current document

Hyperlink to a website (URL)

See the Development System

Reference Guide for more

information.

If a wire is drawn so that it

overlaps the pin of a symbol, the

two nets are not connected.

See the section “Additional

Resources” for details.

Refer to “Title Formats” in

Chapter 1 for details.

Go to http://www.xilinx.com

for the latest speed files.

10 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 11

R

Introduction

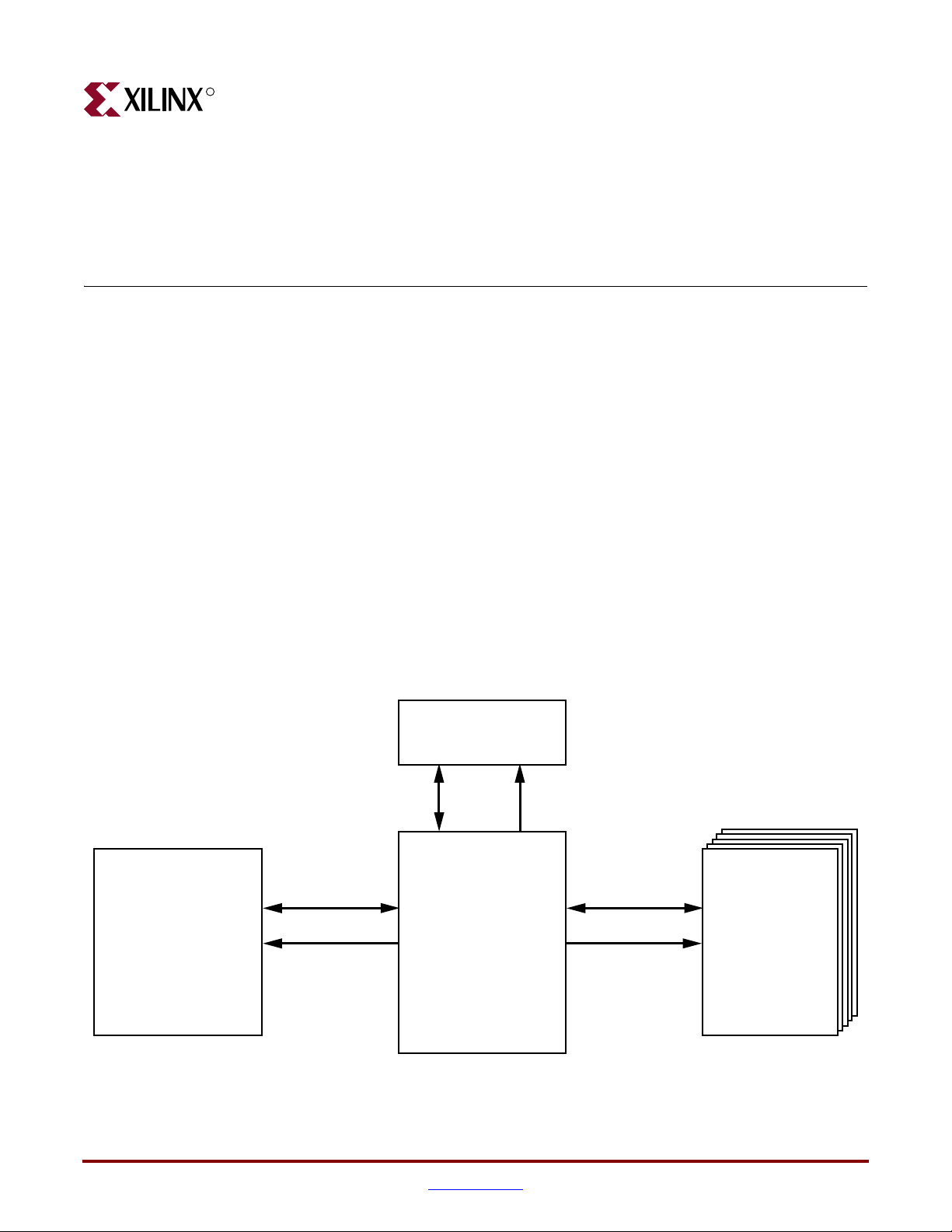

Overview

The ML361 Virtex-II Pro DDR400/PC3200 Memory Board provides a communications

platform between a Virtex-II Pro FPGA and high-speed double-data-rate (DDR) memories

with operating speeds up to 200 MHz. The ML361 has three major functions:

• Tests and verifies the interoperability of Virtex-II Pro devices with high-speed DDR

memories

• Serves as a development platform for Xilinx and its customers to use for building

memory controllers

• Provides a means by which Xilinx can demonstrate high-speed DDR memory

interoperability

Chapter 1

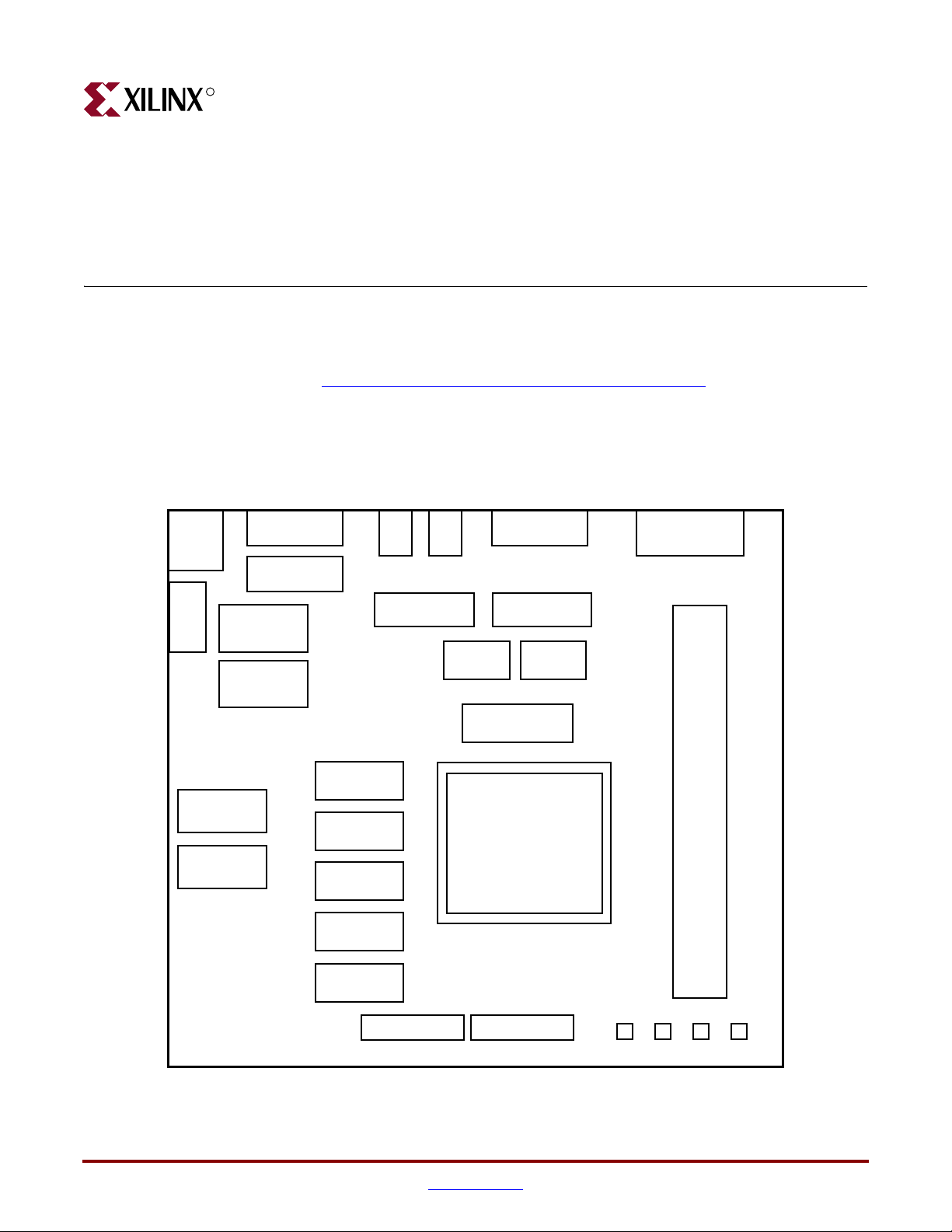

X-Ref Target - Figure 1-1

DDR

SDRAM DIMM

128MB

(MT4VDDT1664-AG-40BC3)

This document describes the functional blocks within the ML361. It also provides various

recommendations and requirements for usage of the board, including electrical

requirements, logic analyzer requirements, and signal integrity issues. Simulation results

using IBIS also are included.

Figure 1-1 shows a simplified block diagram of the ML361 memory interfaces.

DDR SDRAM

(MT46V32M8TG-5B)

Data (8 bits)

Data (72 bits)

Address/Control

Virtex-II Pro FPGA

XC2VP20FF1152-6

Address/Control

Data (72 bits)

Address/Control

DDR

SDRAMs

256Mb

(4 MT46V16M16TG-5B

and

1 MT46V32M8TG-5B)

ug060_c1_01_012104

Figure 1-1: Simplified Block Diagram of Memory Board Interfaces

ML361 Virtex-II Pro Memory Board www.xilinx.com 11

UG060 (v1.2) November 8, 2007

Page 12

Chapter 1: Introduction

Features

R

The ML361 demonstrates a 64-/72-bit interface to a 128 MByte, 200 MHz DDR SDRAM

DIMM, a 72-bit interface to five 256 Mbit, 200 MHz DDR SDRAM components, and an

additional 8-bit interface to a 256 Mbit, 200 MHz DDR SDRAM component on one of the

top banks.

The key features of the ML361 are summarized below:

• One Virtex-II Pro FPGA (XC2VP20FF1152-6)

• One DDR SDRAM DIMM (MT4VDDT1664-AG-40BC3)

♦ 128 MBytes

♦ 64-/72-bit data interface

• Five DDR SDRAMs (four MT46V16M16TG-5B devices and one MT46V32M8TG-5B

device)

♦ 1.28 Gbits

♦ 72-bit data interface

• One DDR SDRAM (MT46V32M8TG-5B)

♦ 256 Mbits

♦ 8-bit data interface

• Two separate controllers for each 72-bit memory interface

• 200 MHz interface

• The memory interfaces are located on the FPGA left/right interface and top I/O

banks (banks 1, 2, 3, 6, and 7)

12 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 13

R

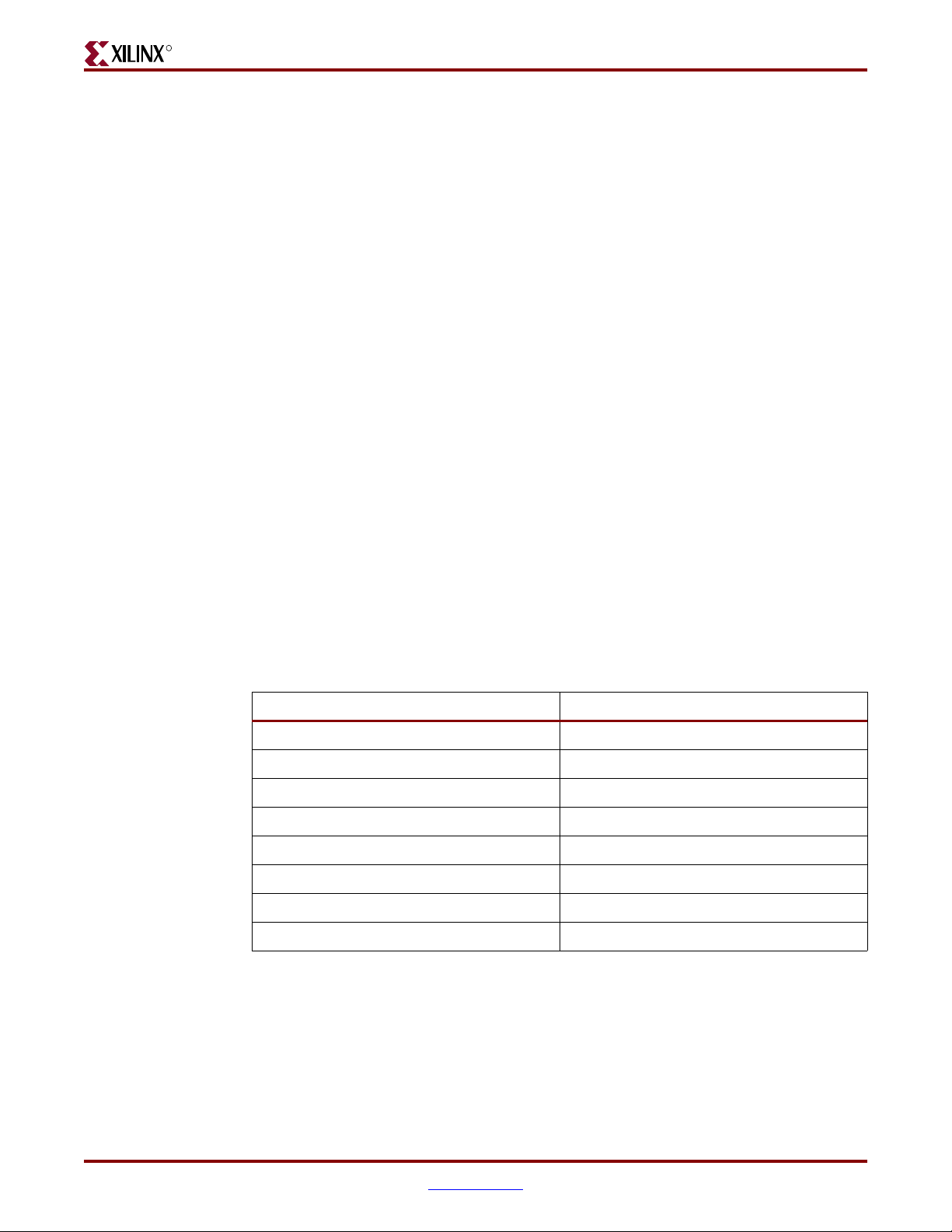

Architecture

This chapter provides functional descriptions of the major blocks within the ML361 board

design. For more detailed information on the design, refer to the schematics, which are

located at http://www.xilinx.com/bvdocs/userguides/ug060.zip

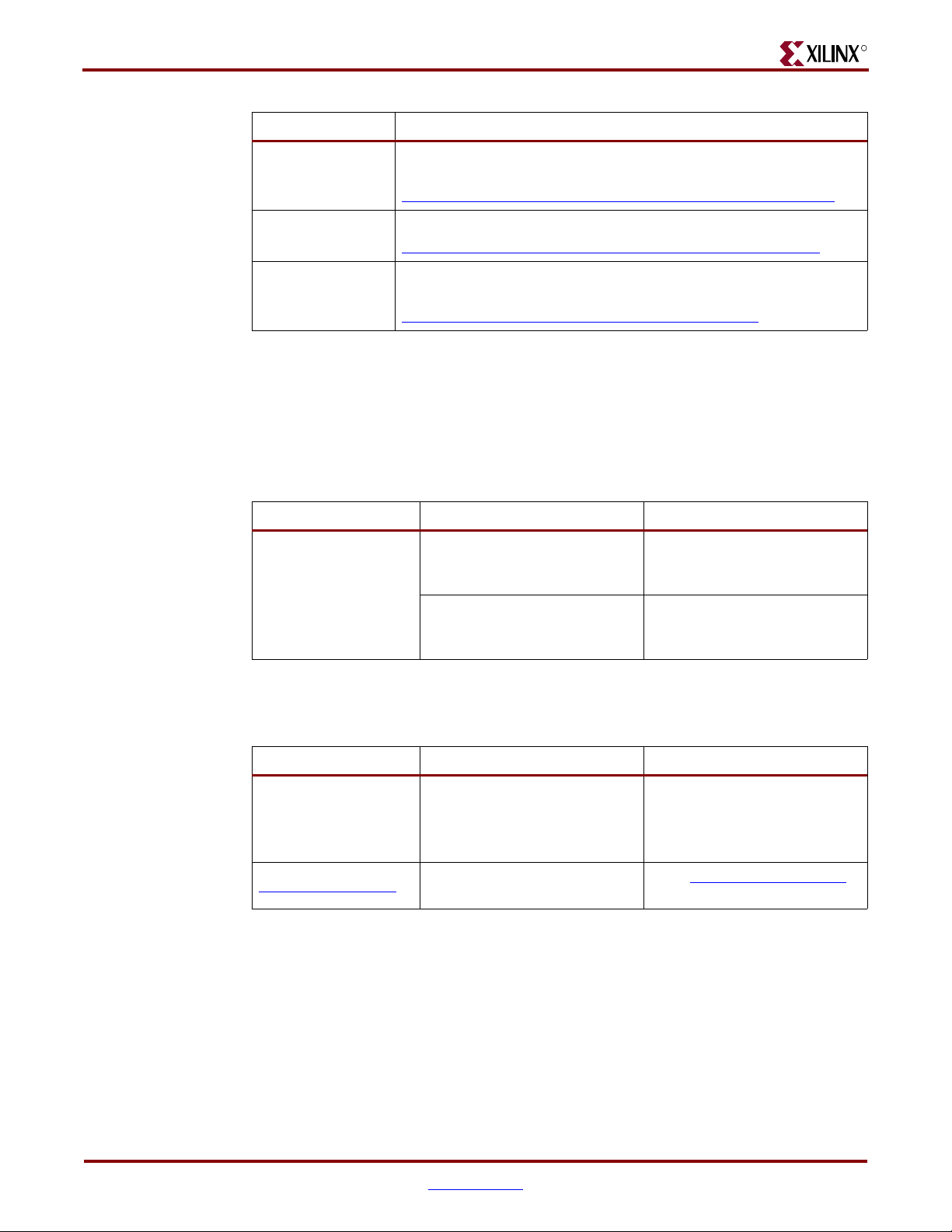

ML361 Board Block Diagram

Figure 2-1 shows a block diagram of the ML361 board. Refer to the following section for

additional information on the major blocks.

X-Ref Target - Figure 2-1

5V

Input

Jack

JTAG Port

PROM

7-Segment Displays

DIP Switch

Chapter 2

.

Serial Port

3.3V Regulator

Switch

1.3V Regulator

2.6V Regulator

(5.5A)

2.6V Regulator

(10A)

(5.5A)

(10A)

GPIO Header GPIO Header

CLOCK

(200 MHz)

DDR SDRAM

(x16)

DDR SDRAM

(x16)

DDR SDRAM

(x16)

DDR SDRAM

(x16)

DDR SDRAM

(x8)

MICTOR (38-pin) MICTOR (38-pin)

XC2VP20FF1152C-6

DDR SDRAM

CLOCK

(166 MHz)

(x8)

Push1 Push2 Prgm Reset

Figure 2-1: ML361 Board Block Diagram

DDR

SDRAM

DIMM

(x64)

ug060_c2_01_121703

ML361 Virtex-II Pro Memory Board www.xilinx.com 13

UG060 (v1.2) November 8, 2007

Page 14

Chapter 2: Architecture

Block Descriptions

This section describes the major blocks of the ML361 board.

FPGA

The ML361 uses a Xilinx XC2VP20FF1152C-6 Virtex-II Pro device. This device is packaged

in a 1152-pin BGA package with a -6 speed grade. Refer to Appendix B, “FPGA Pinout,”for

a complete pinout of the Virtex-II Pro device.

Memories

The ML361 board supports two types of memories: DDR SDRAM DIMM and DDR

SDRAM.

DDR SDRAM DIMM (Banks 6 and 7)

The DDR SDRAM DIMM used on the ML361 board is a 184-pin, 200 MHz, unbuffered,

non-ECC Micron MT4VDDT1664-AG-40BC3 device. This DIMM module has a 64-bit wide

data interface. The board also has provisions to interface to a 72-bit wide DIMM.

R

DDR SDRAM Components (Banks 2 and 3)

DDR SDRAM Component (Bank 1)

RS232

Clocks

200 MHz LVDS Clock

The ML361 board contains five 200 MHz DDR SDRAM components that provide a 72-bit

interface. These devices include four 16-bit Micron MT46V16M16TG-5B devices and one

MT46V32M8TG-5B DDR SDRAM devices. They are packaged in 66-pin TSOP packages.

They share a common address and control bus and have separate clocks and DQS/DQ

signals.

The ML361 board contains one 8-bit Micron MT46V32M8TG-5B device on the top bank of

the FPGA.

The ML361 board provides an RS232 serial interface using a Texas Instruments

MAX3221CDBR device. The maximum speed of this device is 250 Kb/s. The RS232

interface is accessible through a female DB9 RA connector.

The ML361 board contains 166 MHz and 200 MHz LVDS clock oscillators and connectors

for external LVDS clock inputs.

The LVDS clock is a Pletronics LV1145BW-200.0M oscillator with a differential output. The

oscillator runs at 200 MHz ± 50 PPM with an operating voltage of 2.5 V ± 5%. It is

terminated at the FPGA with a 100

CLK_200_LVDSP and CLK_200_LVDSN inputs, respectively.

14 www.xilinx.com ML361 Virtex-II Pro Memory Board

Ω resistor. FPGA pins J17 and H17 in Bank 1 serve as the

UG060 (v1.2) November 8, 2007

Page 15

R

166 MHz LVDS Test Clock

SMA Clock

User I/Os

Mictor Connectors

Block Descriptions

The LVDS test clock is a Pletronics SM7745DW-100.0M clock oscillator with a single-ended

output. This oscillator runs at 166 MHz ± 50 PPM with an operating voltage of 2.5 V ± 5%.

FPGA pins E17 and D17 in Bank 1 serve as the CLK_166_LVDSP and CLK_166_LVDSN

inputs, respectively.

Two SMA connectors are provided for the input of an off-board differential clock. The

traces from the SMAs are run as a pair to the FPGA where they are terminated with a

100 ohm resistor. AK18 serves as the CLK_SMAP input, and AL18 serves as the

CLK_SMAN input for the SMA connector pair.

This subsection describes the devices that connect to the User I/Os of the ML361 board.

The FPGA interfaces to two 38-pin Mictor connectors. They can be used to hook up to a

logic analyzer. All signals from the FPGA to the connectors are matched closely. Refer to

the Xilinx data sheets in Appendix A, “Related Documentation,” for more information.

GPIO

The ML361 board contains 16 general-purpose I/Os (GPIOs), which are accessible through

two 2 x 8 0.100" pin headers (see Ta bl e 2 -1 and Tab le 2 - 2). The even-numbered pins on each

header are connected to ground. The GPIO header pins can be accessed through I/Os in

Bank 0.

Table 2-1: GPIO Header 1

GPIO Pin # FPGA I/O Pin

G00 F22

G01 E22

G02 E25

G03 D25

G04 H21

G05 D22

G06 D23

G07 D24

ML361 Virtex-II Pro Memory Board www.xilinx.com 15

UG060 (v1.2) November 8, 2007

Page 16

Chapter 2: Architecture

DIP Switch

II

Table 2-2: GPIO Header 2

GPIO Pin # FPGA I/O Pin

G08 D30

G09 D29

G10 K23

G11 J23

G12 H22

G13 G22

G14 D26

G15 C26

One eight-position DIP switch is connected to the FPGA I/Os as shown in Ta bl e 2 -3 . These

switches can be used to externally pull up or pull down any signal on the FPGA.

R

Table 2-3: DIP Switch Connections

DIP Switch Input FPGA I/O Pin #

DIP1 G26

DIP2 H25

DIP3 G25

DIP4 J25

DIP5 K24

DIP6 J24

DIP7 F26

DIP8 E26

Seven-Segment Displays

Two seven-segment displays connect to the FPGA I/Os (see Tab le 2- 4 and Ta bl e 2 - 5). The

red displays are active Low. The decimal points are not connected.

Table 2-4: Display 1

DIsplay Input FPGA I/O Pin #

Display1A C21

Display1B E21

Display1C F21

Display1D J20

Display1E K20

16 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 17

R

Block Descriptions

Table 2-4: Display 1

DIsplay Input FPGA I/O Pin #

Display1F C24

Display1G D24

Table 2-5: Display 2

DIsplay Input FPGA I/O Pin #

Display2A D20

Display2B D21

Display2C F20

Display2D G20

Display2E K19

Display2F L19

Display2G C22

LEDs

Four green LEDs connect to the FPGA I/Os as indicated in Ta bl e 2 -6 . The LEDs are active

Low.

Table 2-6: LED Connections to FPGA

LED # FPGA I/O Pin #

LED1 L18

LED2 K18

LED3 G18

LED4 F18

Push Buttons

The ML361 board contains four momentary push buttons. Their functions are as follows:

• Program the FPGA

• Reset the board

• User function 1

• User function 2

Grounded I/Os

Unused I/Os are connected to GND in all FPGA banks. However, all memory banks have

eight unused I/Os connected to GND through 0

Ω resistors. These can be depopulated

when needed for test purposes. Care must be taken to not drive any unused I/Os

connected to GND.

ML361 Virtex-II Pro Memory Board www.xilinx.com 17

UG060 (v1.2) November 8, 2007

Page 18

Chapter 2: Architecture

Power

Power Distribution

Input Voltage

3.3 V Generation

2.6 V Generation

R

The ML361 board uses a 5V input voltage source to generate all the on-board voltages

(1.3V, 1.5V, 2.6V, and 3.3V, and the 2.5V for the MGTs)

The input voltage is specified at 5 V @ 6.5 A. The recommended power supply is a CUI Inc.

DTS050650UTC-PSP-SZ. The jack used is a 4-pin barrel jack, CUI stack PJ-002A-SMT. The

slide switch is a CW Industries G1123-0009. This power input has alternate input solder

pads.

The Texas Instruments PTH05000WAH voltage regulator generates the 3.3 V @ 5.5 A

power. This power input has alternate input solder pads.

The Texas Instruments PTH05010WAS voltage regulator generates the 2.6 V @ 10 A power.

This regulator provides 2.5 Vout with ± 10% trim. This power input has alternate input

solder pads.

1.5 V Generation

The Texas Instruments PTH05000WAH voltage regulator generates the 1.5 V @ 5.5 A

power. This power input has alternate input solder pads.

1.3 V Generation

The Texas Instruments PTH05000WAH voltage regulator generates the 1.3 V @ 1.5 A

power.

Linear Regulators for the MGTs

The Texas Instruments TPS78625 voltage regulator generates 2.5 V @ 1.5 A power for the

Multi Gigabit Transceivers (MGTs).

FPGA Configuration

The Virtex-II Pro FPGA can be programmed through either the JTAG interface or three onboard PROMs.

JTAG

Two headers are used for JTAG: a standard header and a parallel-IV header.

Standard Header

The standard JTAG header is a 1 x 7 0.100" RA header.

Parallel-IV Header

The parallel-IV headers is a 2 x 7 2 mm RA shrouded header.

18 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 19

R

Block Descriptions

PROMs

The ML361 board contains XCF04S PROMs that can be used to program the

Virtex-II Pro FPGA. The PROM operates with a 3.3 V core voltage and a 2.5 V I/O voltage.

ML361 Virtex-II Pro Memory Board www.xilinx.com 19

UG060 (v1.2) November 8, 2007

Page 20

Chapter 2: Architecture

R

20 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 21

R

Electrical Requirements

Power Consumption

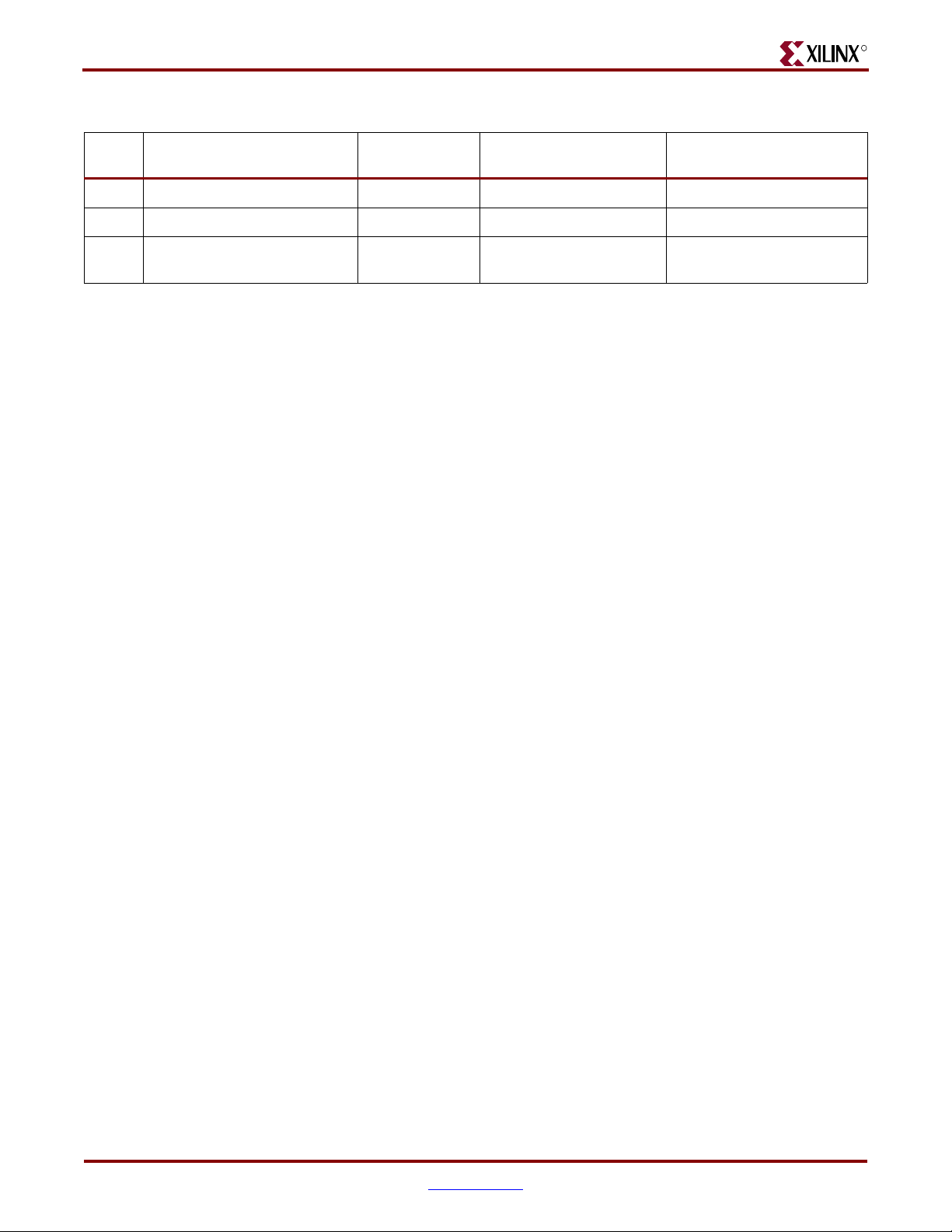

Tab le 3- 1 lists the operating voltages, maximum currents, and power consumption used by

the ML361 board devices. Refer to Appendix A, “Related Documentation,” for more

information on the source material.

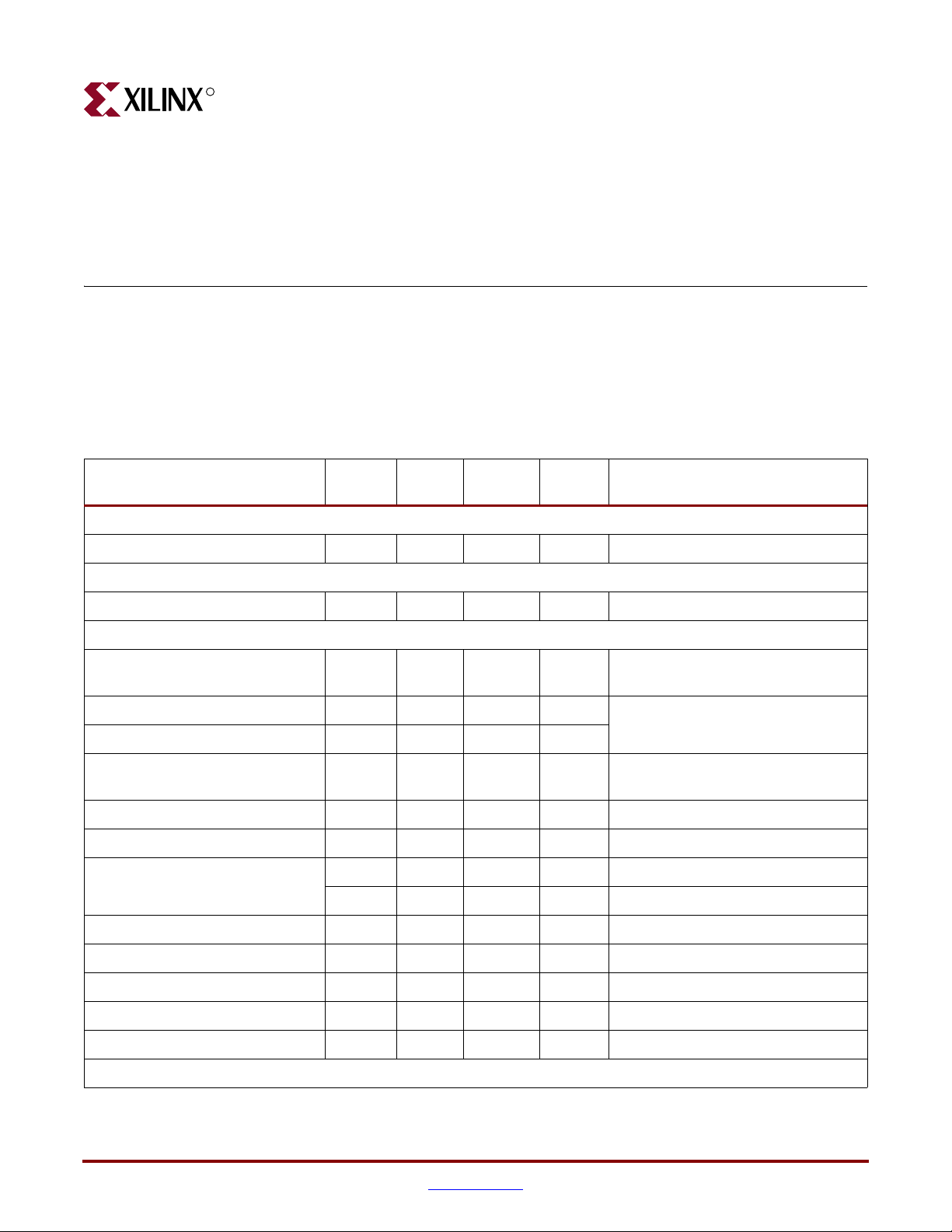

Table 3-1: ML361 Power Consumption

Chapter 3

Device Quantity

Total Available Power

Power Supply 1 5 6500 32.5

FPGA Power (Based on Design)

FPGA (XC2VP20-6 FF1152) 1 6.873 Power Estimator Tool

Board Power

Static Power-on Termination

Resistors (50Ω)

DDR SDRAM (72-bit interface) 5 2.6 260 3.38 Micron DDR SDRAM Data Sheet

DDR SDRAM (8-bit interface) 1 2.6 260 0.676

DDR SDRAM DIMM 1 2.6 1040 2.704 Micron DDR SDRAM DIMM Data

200 MHz LVDS Clock Oscillator 1 3.3 40 0.132 Pletronics LV1145B-200 Data Sheet

166 MHz LVDS Clock Oscillator 1 3.3 40 0.132 Pletronics LV1145B-166 Data Sheet

PROMs (XCF04SV020C) 3 2.6 25 0.2 Estimated

375 1.3 16.2 4.92 Virtex-II Pro User Guide (SSTL2

3 3.3 25 0.25 Estimated

Volt ag e

(V)

Current

(mA)

Power

(W)

Source

current specification)

Sheet

8-pin GPIO Header 2 2.6 160 0.416 Average 10 mA * 16 pins

Seven Segment Display 2 2.6 86 0.224 Fourteen 130Ω loads

LEDs 9 2.6 25 0.585 Nine 130Ω loads

DIP Switch 1 2.6 6 0.016 Eight 3.3 kΩ pull-ups

RS232 Serial Port 1 3.3 40 0.132 TI MAX3221 Data Sheet

Worst Case Power Consumption: 20.64

ML361 Virtex-II Pro Memory Board www.xilinx.com 21

UG060 (v1.2) November 8, 2007

Page 22

Chapter 3: Electrical Requirements

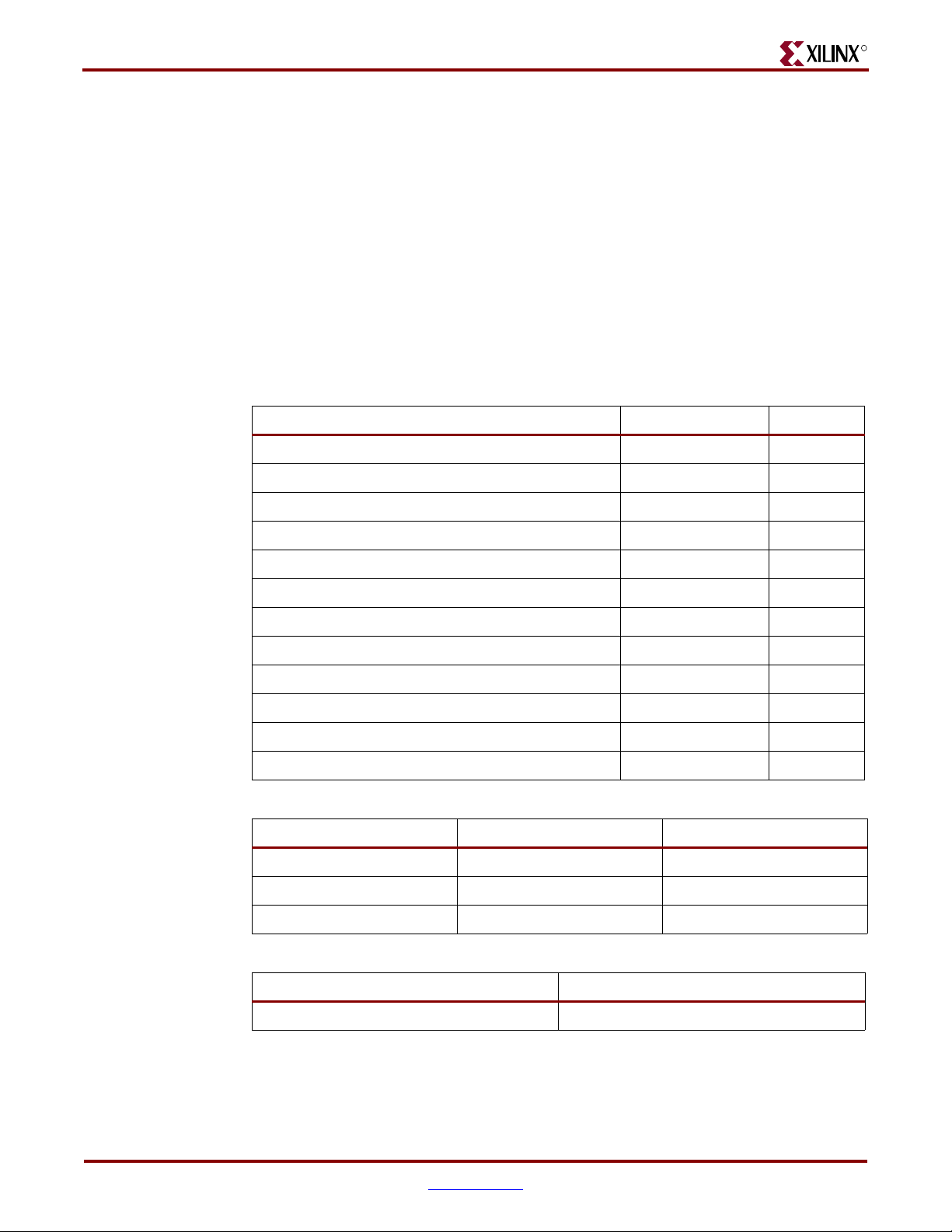

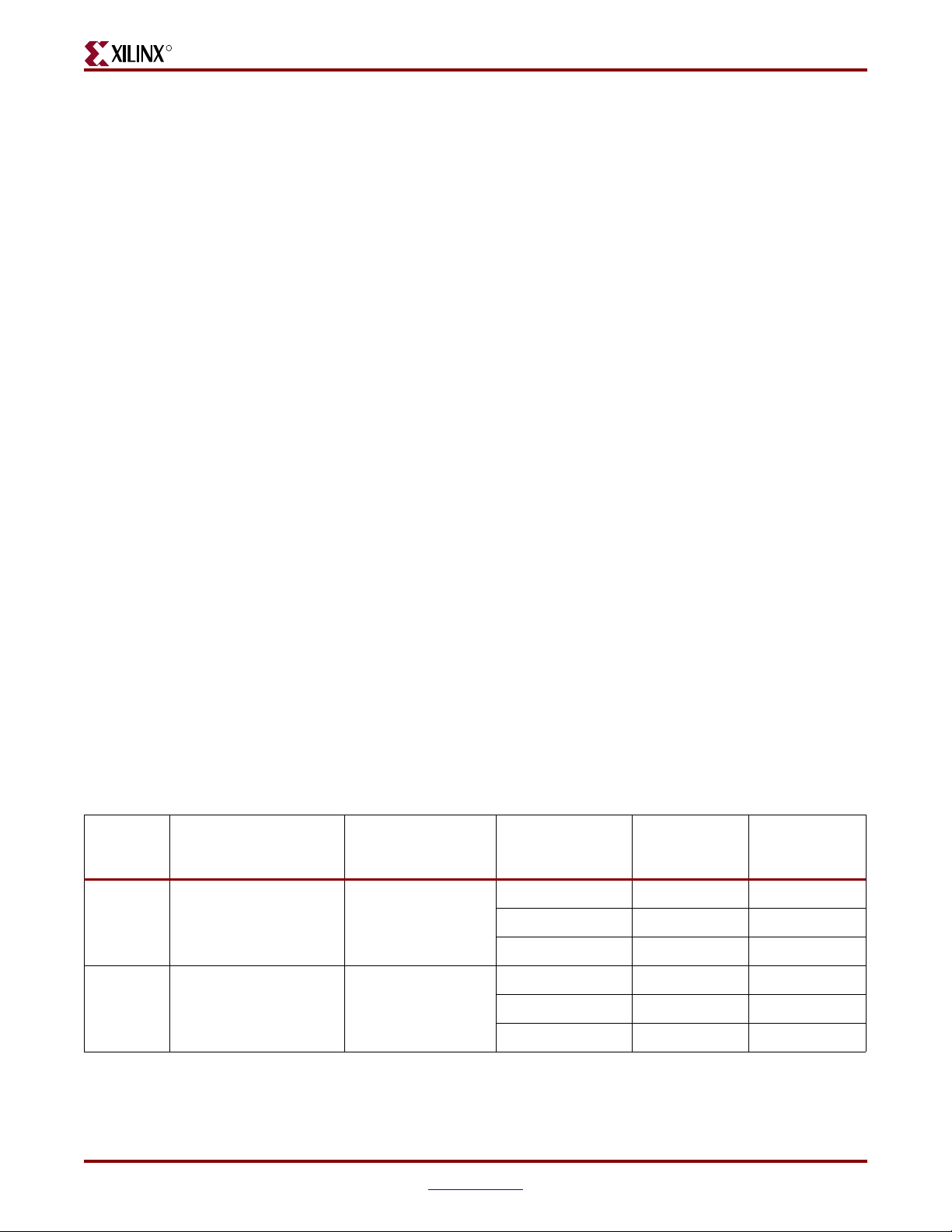

FPGA Internal Power Budget

The following tables show the power consumption values inside the FPGA based on the

complete DDR design. These results are derived using the Xilinx Power Estimator tool.

Block Select RAM, Block Multiplier, Processor, and MGT Power tables are not included in

this section as they are not used in this application.

• Tab le 3- 2, “XC2VP20FF1152 Estimated Power Consumption,” page 22

• Tab le 3- 3, “XC2VP20FF1152 Temperature Specifications,” page 22

• Tab le 3- 4, “Device Quiescent Power,” page 22

• Tab le 3- 5, “CLB Logic Power,” page 23

• Tab le 3- 6, “Digital Clock Manager Power,” page 23

• Tab le 3- 7, “Input/Output Power,” page 24

Table 3-2: XC2VP20FF1152 Estimated Power Consumption

Parameter Value Units

Total Estimated Design Power 6873 mW

R

Estimated Design VCC

Estimated Design VCC

1.5 V Power 3811 mW

INT

2.5 V Power 417 mW

AUX

Estimated Design VCCO 3.3 V Power 0 mW

Estimated Design VCCO 2.5 V Power 2645 mW

Estimated Design VCCO 1.8V Power 0 mW

Estimated Design VCCO 1.5 V Power 0 mW

Estimated Design VCCO 1.2 V Power 0 mW

Estimated Design VCC

Estimated Design VCC

Estimated Design VT

Estimated Design VT

RX 2.5 V Power 0 mW

AUX

TX 2.5 V Power 0 mW

AUX

2.5 V Power 0 mW

RX

2.5 V Power 0 mW

TX

Table 3-3: XC2VP20FF1152 Temperature Specifications

Parameter Value Units

Ambient Temperature 25 •C

Air Flow 0 LFM

Junction Temperature 107 •C

Table 3-4: Device Quiescent Power

VCC

Subtotal (mW) VCC

INT

Subtotal (mW)

AUX

450 417

22 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 23

R

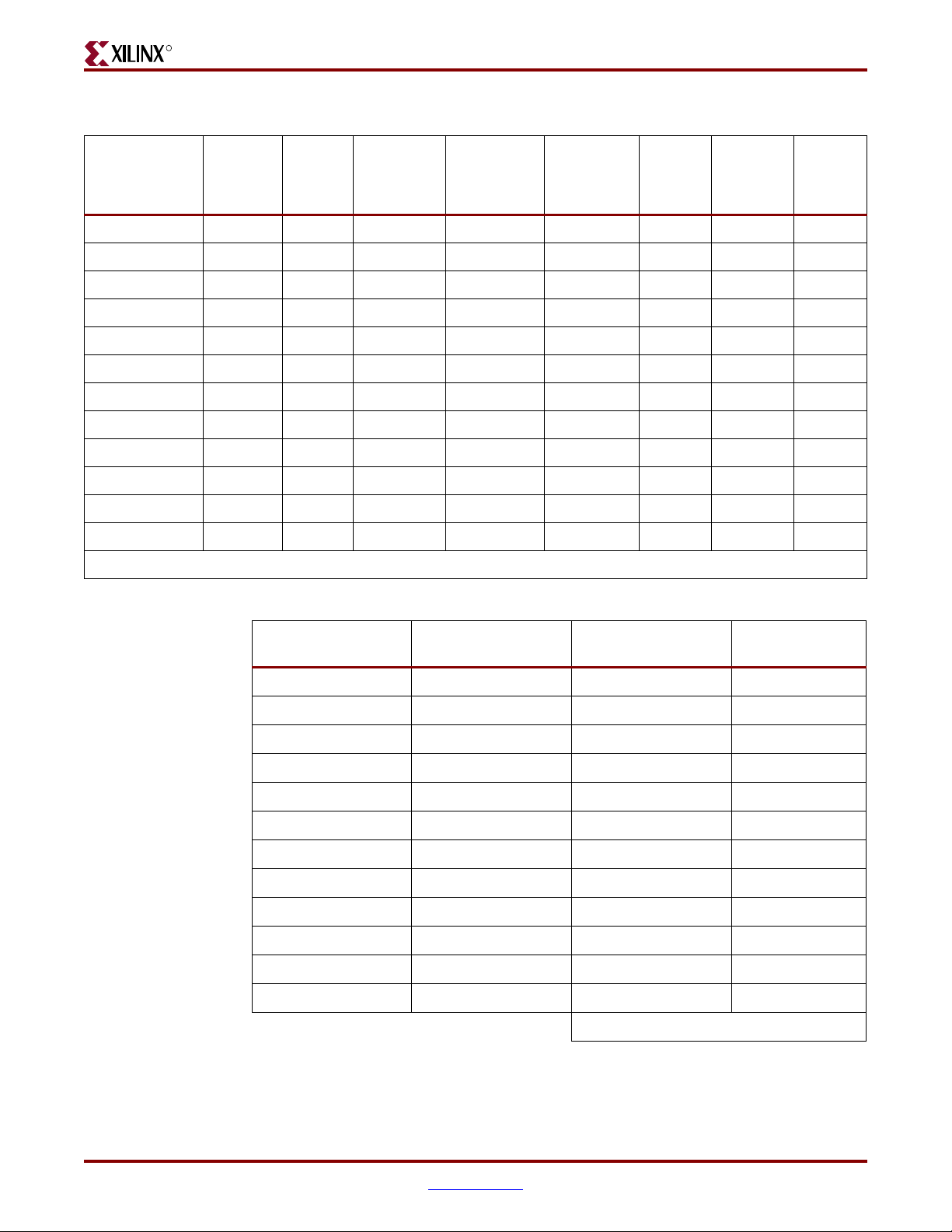

Table 3-5: CLB Logic Power

FPGA Internal Power Budget

Tot al

Name

User Module 1 200 2597 2603 0 1088 40% High 2439

User Module 2 0 0 0 0 0 0% Low 0

User Module 3 0 0 0 0 0 0% Low 0

User Module 4 0 0 0 0 0 0% Low 0

User Module 5 0 0 0 0 0 0% Low 0

User Module 6 0 0 0 0 0 0% Low 0

User Module 7 0 0 0 0 0 0% Low 0

User Module 8 0 0 0 0 0 0% Low 0

User Module 9 0 0 0 0 0 0% Low 0

User Module 10 0 0 0 0 0 0% Low 0

User Module 11 0 0 0 0 0 0% Low 0

User Module 12 0 0 0 0 0 0% Low 0

Frequency

(MHz)

Number

of CLB

Slices

Tot al

Number of

Flip/Flop or

Latches

Tota l N u m be r

of Shift

Register LUTs

Tot al Numbe r

of Select

RAM LUTs

Average

Toggle

Rate

%

Amount of

Routing

Used

Total 2439

VCC

Subtotal

(mW)

INT

Table 3-6: Digital Clock Manager Power

Name

Clock Input

Frequency (MHz)

DCM Frequency Mode

VCC

INT

User DCM 1 200 Low 6

User DCM 2 200 Low 6

User DCM 3 0 Low 0

User DCM 4 0 Low 0

User DCM 5 0 Low 0

User DCM 6 0 Low 0

User DCM 7 0 Low 0

User DCM 8 0 Low 0

User DCM 9 0 Low 0

User DCM 10 0 Low 0

User DCM 11 0 Low 0

User DCM 12 0 Low 0

To t al 1 2

Subtotal

(mW)

ML361 Virtex-II Pro Memory Board www.xilinx.com 23

UG060 (v1.2) November 8, 2007

Page 24

Chapter 3: Electrical Requirements

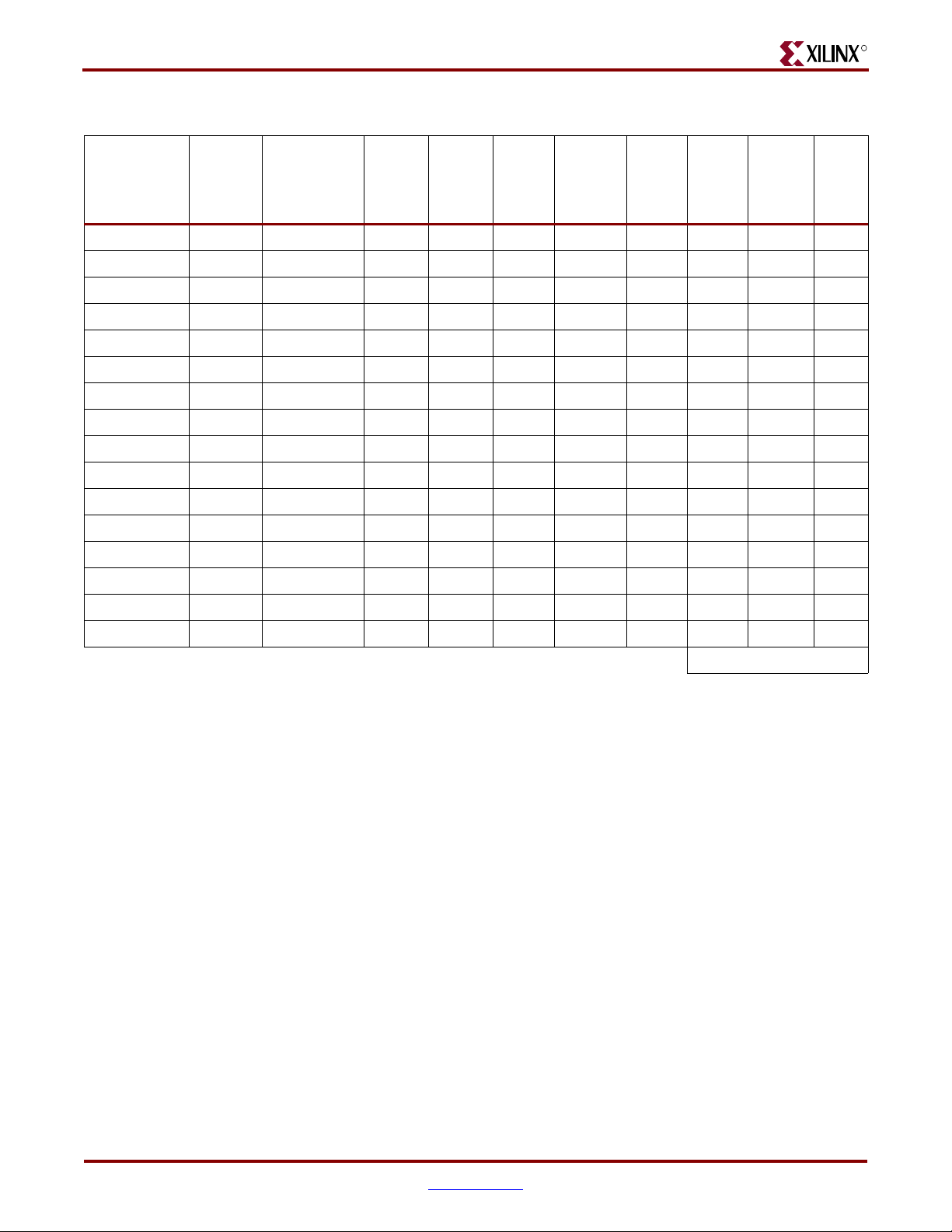

Table 3-7: Input/Output Power

Average

Output

Enable

Rate

%

Average

Output

Load

(pF)

IOB

Registers

VCC

INT

Subtotal

(mW)

VCCO

Subtotal

Name

Frequency

(MHz)

I/O Standard

Typ e

Tot al

Number

of Inputs

Tot al

Number

Outputs

of

Average

IOB

Tog gle

Rate

%

Jpheader 200 LVCMOS25_12 0 16 25% 100% 0 SDR 2 30

ddr_dq 200 SSTL2_II 138 138 80% 50% 5 DDR 462 877

ddr_dqs 2000 SSTL2_II 18 18 80% 50% 5 DDR 335 363

ddr_address 200 SSTL2_II 0 15 25% 100% 3 SDR 1 106

ddr_control 200 SSTL2_II 0 5 25% 100% 3 SDR 0 35

dimm_address 200 SSTL2_I_DCI 0 15 25% 100% 12 SDR 13 157

dimm_control 200 SSTL2_I_DCI 0 4 50% 100% 12 SDR 12 96

ddr_clks 200 SSTL2_II 0 2 100% 100% 3 DDR 0 42

Display 200 LVCMOS25_12 0 14 6% 100% 0 SDR 1 6

dimm_control_1 200 SSTL2_II 0 3 50% 100% 12 SDR 0 28

ddr_dm 200 SSTL2_II 0 17 10% 100% 5 SDR 2 100

R

(mW)

dimm_clks 200 SSTL2_II 0 6 100% 100% 12 SDR 1 82

top_dq 200 SSTL2_II_DCI 8 8 80% 50% 5 DDR 39 366

top_dqs 200 SSTL2_II_DCI 1 1 80% 50% 5 DDR 15 103

top_address 200 SSTL2_I_DCI 0 15 25% 100% 5 SDR 13 153

top_control 200 SSTL2_I_DCI 0 5 25% 100% 5 SDR 12 95

Total 910 2645

24 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 25

R

Chapter 4

Signal Integrity Recommendations and

Simulations

This chapter provides the following information:

• Summary of the termination schemes for various signals (“Termination and

Transmission Line Summaries,” page 25)

• Summary of the observed duty cycles for all signals in the IBIS simulations (“Duty

Cycle Summary,” page 27)

• IBIS simulations and duty cycle measurements (“IBIS Simulations,” page 29)

Termination and Transmission Line Summaries

Tab le 4- 1 summarizes the terminations for the five DDR SDRAM components at the FPGA

and at memory.

Table 4-1: DDR SDRAM Terminations

No. Signal

1 Data (DQ) SSTL2_C2 50Ω pull up to 1.3 V 50Ω pull-up to 1.3 V

2 Data Strobe (DQS) SSTL2_C2 50Ω pull up to 1.3 V 50Ω pull-up to 1.3 V

3 Data Mask (DM) SSTL2_C2 50Ω pull up to 1.3 V 50Ω pull-up to 1.3 V

4 Clock (CK, CKn) SSTL2_C2 50Ω pull up to 1.3 V 50Ω pull-up to 1.3 V

5 Address (A, BA) SSTL2_C2 No termination 50Ω pull-up to 1.3 V after the

6 Control (RASn, CASn, WEn,

CSn, CKE)

Tab le 4- 2 summarizes the terminations for the DIMM at the FPGA and at memory.

Table 4-2: DIMM Terminations

No. Signal

Drivers at the

FPGA

SSTL2_C2 No termination 50Ω pull-up to 1.3 V after the

Drivers at the

FPGA

Termination at FPGA Termination at Memory

last component

last component

Termination at FPGA Termination at Memory

1 Data (DQ) SSTL2_C2 50Ω pull-up to 1.3 V 50Ω pull-up to 1.3 V

2 Data Strobe (DQS) SSTL2_C2 50Ω pull-up to 1.3 V 50Ω pull-up to 1.3 V

3 Data Mask (DM) SSTL2_C2 50Ω pull-up to 1.3 V 50Ω pull-up to 1.3 V

ML361 Virtex-II Pro Memory Board www.xilinx.com 25

UG060 (v1.2) November 8, 2007

Page 26

Chapter 4: Signal Integrity Recommendations and Simulations

Table 4-2: DIMM Terminations

R

No. Signal

4 3 pairs of Clocks (CK, CKn) SSTL2_C2 50Ω pull-up to 1.3 V 50Ω pull-up to 1.3 V

5 Address (A, BA) SSTL2_C2_DCI No termination No termination

6 Control (RASn, CASn, WEn,

CSn, CKE and others)

Drivers at the

FPGA

SSTL2_C2_DCI No termination No termination

Termination at FPGA Termination at Memory

Terminations and Transmission Lines for DDR Components

Data and Clock Signals (DQ, DQS, DM, CLK)

For these DDR signals, the terminations at the FPGA and memory consist of a 50Ω parallel

termination pulled up to 1.3 V.

Use 50

Ω transmission lines with less than ± 1% tolerance on the transmission line

impedance. The recommendations for the transmission line lengths are as follows:

• All these data and clock signals are point-to-point from the FPGA to each DDR

component. All signals going to one individual DDR SDRAM component need to be

matched with respect to each other with a ± 2% tolerance.

• All signals going to the first component are matched to a trace length of 2.8 inches

with a ± 2% tolerance. The 2.5 inch requirement includes the FPGA internal package

skew (available on the pinout table) and the skew between the ball of the FPGA to the

resistor pack as well as the length of the actual trace.

• The trace length variation on these signals across the five DDR components is kept as

small as possible to enable data capture while also ensuring they fall within the

address window. The trace lengths on all five DDR components are: 2.8 inches, 2.8

inches, 3.5 inches, 3.8 inches, and 3.8 inches. All signals corresponding to the same

DDR component are matched as close as ± 1% of the above mentioned trace lengths.

Microstrip is used to model the transmission lines in the IBIS simulations.

Address and Control Signals (A, BA, RASn, CASn, WEn, CSn, CKE)

For the address and control signals, no termination is required at the FPGA. At memory, a

50

Ω resistor pulled up to 1.3 V at the end of the daisy chain is required (after the last DDR

component).

Use 50

Ω transmission lines with ± 5% tolerance from the FPGA to all the memory

components. The recommendations for the transmission line lengths are as follows:

• All the signals are routed in a daisy chain fashion.

• There is a maximum of 2.5 inch trace with ± 2% tolerance from the FPGA to the first

DDR component. The 2.5 inch requirement includes the FPGA internal package skew

(that is available on the pinout table) and the skew between the ball of the FPGA to

the resistor pack as well as the length of the actual trace.

• 0.6 inches of distance with ± 2% tolerance is used in the trace length calculations

below between the individual components. Ideally, straight line routing is desired.

During placement, the components are placed as close as 0.5 inches or lesser by

straight line routing, if possible. The main requirement is that all signals going to each

DDR component must be matched by ± 2% tolerance.

26 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 27

R

• There is a total of 4.9 inches of trace from the FPGA to the last component assuming

the DDR memory components are 0.6 inch apart.

Microstrip is used to model the transmission lines for the first DDR component. All other

DDR components use Buried Microstrip to model the transmission lines.

Terminations and Transmission Lines for the DIMM

Data and Clock Signals (DQ, DQS, DM, CLK)

For these DIMM signals, the terminations at the FPGA and memory consist of a 50Ω

parallel termination pulled up to 1.3 V.

50

Ω transmission lines are used with less than ± 1% tolerance on the transmission line

impedance. The transmission line lengths are as follows:

• There is a 65 mm trace length from FPGA to memory with ± 0.5 mm tolerance.

• A maximum of 1 inch tolerance is allowed to include the FPGA internal package skew

and the skew between the ball of the FPGA to the resistor pack. Package deskew is

necessary if the 1 inch tolerance is not met.

Duty Cycle Summary

Address and Control Signals (A, BA, RASn, CASn, WEn, CSn, CKE)

For the address and control signals, no termination is required at the FPGA or DIMM.

Use 50

Ω transmission lines with less than ± 5% tolerance on the transmission line

impedance. The recommendations for the transmission line lengths are as follows:

• There must be a 65 mm trace length from FPGA to memory with ± 5 mm tolerance.

• Use a maximum of 1 inch tolerance to include the FPGA internal package skew and

the skew between the ball of the FPGA to the resistor pack. Package deskew is

necessary if the 1 inch tolerance is not met.

Duty Cycle Summary

Tab le 4- 3 summarizes the duty cycle measurements taken from prelayout simulations on

50

Ω transmission lines. Refer to “IBIS Simulations,” page 29 for more simulation results.

Table 4-3: Duty Cycle Summary

No. Signal DDR Component Case

1 Address/control Last component

(farthest from FPGA)

Typical 49.22/50.92 NA

Slow weak 49.22/50.63 NA

Duty Cycle

Measured at

Memory(%)

Duty Cycle

Measured at

FPGA (%)

Fast strong 49.22/51.2 NA

2 Address/control First component

(closest to FPGA)

ML361 Virtex-II Pro Memory Board www.xilinx.com 27

UG060 (v1.2) November 8, 2007

Typical 48.94/51.2 NA

Slow weak 49.22/51.48 NA

Fast strong 48.66/51.2 NA

Page 28

Chapter 4: Signal Integrity Recommendations and Simulations

Table 4-3: Duty Cycle Summary

R

No. Signal DDR Component Case

Duty Cycle

Measured at

Memory(%)

Duty Cycle

Measured at

FPGA (%)

3 Address/control Middle component Typical 49.23/51.49 NA

Slow weak 49.22/50.64 NA

Fast strong 48.94/51.2 NA

4 Clock Last component Typical 48.1/52.04 NA

Slow weak 48.66/51.48 NA

Fast strong 48.1/51.48 NA

5 Data Last component Typical 47.24/52.62 48.64/51.78

Slow weak 47.52/52.06 49.52/50.64

Fast strong 46.4/52.9 48.38/51.76

28 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 29

R

IBIS Simulations

This section summarizes various simulations run on the Memory Board using IBIS. It

defines the test conditions and provides color-coded screen captures of the results. The

resulting signal duty cycles are given also.

The simulations have been divided into the following categories:

1. Data Signal Simulations

2. Clock Signal Simulations

3. Address and Control Signal Simulations

4. Typical Case Simulations with 10% Tolerance for:

IBIS Simulations

a. Data Signals from the FPGA to the Last Memory Component

- Typical Case

- Slow Weak Case

- Fast Strong Case

- Eye Diagram

b. Data Signals from the Last Memory Component to the FPGA

- Typical Case

- Slow Weak Case

- Fast Strong Case

- Eye Diagram

a. Clock Signals from the FPGA to the Last Memory Component

- Typical Case

- Slow Weak Case

- Fast Strong Case

- Eye Diagram

a. Address and Control Signals from the FPGA to the First/Last/Middle Memory

Component

- All Memory Components (Typical Case)

- First DDR Component (Typical, Slow Weak, Fast Strong Cases)

- Last DDR Component (Typical, Fast Strong, Slow Weak Cases)

- Middle DDR Component (Typical, Slow Weak, Fast Strong Cases)

a. Data Signals

- Data Signals from the Last DDR Memory to the FPGA with 45

Ω Transmission

Lines (Typical)

- Data Signals from the Last DDR Memory to the FPGA with 55

Ω Transmission

Lines (Typical)

- Data Signals from the FPGA to the Last DDR Memory with 45

Ω Transmission

Lines (Typical)

- Data Signals from Memory to the FPGA with 55

Ω transmission lines (Typical)

b. Clock Signals

- Clock Signals with 45

- Clock Signals with 55

Ω Transmission Lines (Typical)

Ω Transmission Lines (Typical)

ML361 Virtex-II Pro Memory Board www.xilinx.com 29

UG060 (v1.2) November 8, 2007

Page 30

Chapter 4: Signal Integrity Recommendations and Simulations

c. Address and Control Signals

- Address and Control Signals with 45

DDR Component (Typical)

- Address and Control Signals with 55

DDR Component (Typical)

Notes on the Simulation Results

The provided screen captures show the results of each simulation. The signals in these

screen captures are color-coded as follows:

• Red signal – at FPGA

• Yellow signal – at memory

R

Ω Transmission Lines Measured at First

Ω Transmission Lines Measured at First

The two horizontal yellow lines are V

± 100 mV where V

ref

=1.3 V.

ref

30 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 31

R

Data Signal Simulations

All data signal simulations below have the following test conditions for typical, slow

weak, and fast strong cases:

IBIS Simulations

• Topology for data signals: 50

• At memory (yellow signal): 50

• At FPGA (red signal): 50

Ω Transmission lines

Ω parallel termination pulled up to 1.3 V

Ω parallel termination pulled up to 1.3 V (SSTL2C2 drivers at

FPGA).

Figure 4-1 shows the data signal terminations.

X-Ref Target - Figure 4-1

ug060_c5_01_091003

Figure 4-1: Data Signal Terminations

ML361 Virtex-II Pro Memory Board www.xilinx.com 31

UG060 (v1.2) November 8, 2007

Page 32

Chapter 4: Signal Integrity Recommendations and Simulations

Data Signals from the FPGA to Memory (SSTL2_C2 at FPGA)

The simulations in this subsection test the data signals from the FPGA to memory.

Simulations were performed for the following cases: typical, slow weak, fast strong. An

eye diagram is provided also.

Typical Case Simulation for Data Signals from the FPGA to the Last DDR

Component

For the typical case simulation, the resulting duty cycle is 47.24/52.62. Figure 4-2 shows

the simulation screen capture for the typical case.

X-Ref Target - Figure 4-2

R

ug060_c5_02_091003

Figure 4-2: Data Signal from FPGA to Memory (Typical Case)

32 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 33

R

IBIS Simulations

Slow Weak Corner Case for Data from the FPGA to the Last DDR Component

For the slow weak case simulation, the resulting duty cycle is 47.52/52.06. Figure 4-3

shows the simulation screen capture for this case.

X-Ref Target - Figure 4-3

ug060_c5_03_091003

Figure 4-3: Data Signal from FPGA to Memory (Slow Weak Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 33

UG060 (v1.2) November 8, 2007

Page 34

Chapter 4: Signal Integrity Recommendations and Simulations

Fast Strong Case for Data Signals from the FPGA to the Last DDR Component

For the fast strong case simulation, the resulting duty cycle is 46.4/52.9. Figure 4-4 shows

the simulation screen capture for this case.

X-Ref Target - Figure 4-4

R

ug060_c5_04_091003

Figure 4-4: Data Signal from FPGA to Memory (Fast Strong Case)

34 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 35

R

IBIS Simulations

Eye Diagram

Figure 4-5 shows the eye diagram for the data signals from the FPGA to the last memory

component.

X-Ref Target - Figure 4-5

ug060_c5_05_091003

Figure 4-5: Eye Diagram for Data from the FPGA to Last Memory Component

ML361 Virtex-II Pro Memory Board www.xilinx.com 35

UG060 (v1.2) November 8, 2007

Page 36

Chapter 4: Signal Integrity Recommendations and Simulations

Data Signals from the Last Memory to the FPGA: Measured at FPGA

The simulations in this subsection test the data signals from the last memory to the FPGA.

Simulations were performed for the following cases: typical, slow weak, and fast strong.

An eye diagram is provided also.

Typical Case for Data from the Last DDR Memory Device to the FPGA

For the typical case simulation, the resulting duty cycle is 48.64/51.78. Figure 4-6 shows

the simulation screen capture for this case.

X-Ref Target - Figure 4-6

R

ug060_c5_06_031204

Figure 4-6: Data Signal from Last Memory at FPGA (Typical Case)

36 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 37

R

IBIS Simulations

Slow Weak Corner Case for Data Signals from the Last DDR Memory to the FPGA

For the slow weak case simulation, the resulting duty cycle is 49.52/50.64. Figure 4-7

shows the simulation screen capture for this case.

X-Ref Target - Figure 4-7

ug060_c5_07_031204

Figure 4-7: Data Signal from Last Memory at FPGA (Slow Weak Corner Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 37

UG060 (v1.2) November 8, 2007

Page 38

Chapter 4: Signal Integrity Recommendations and Simulations

Fast Strong Corner Case for Data from Memory to the FPGA

For the fast strong case simulation, the resulting duty cycle is 48.38/51.76. Figure 4-8

shows the simulation screen capture for this case.

X-Ref Target - Figure 4-8

R

ug060_c5_08_031204

Figure 4-8: Data Signal from Memory at FPGA (Fast Strong Corner Case)

38 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 39

R

IBIS Simulations

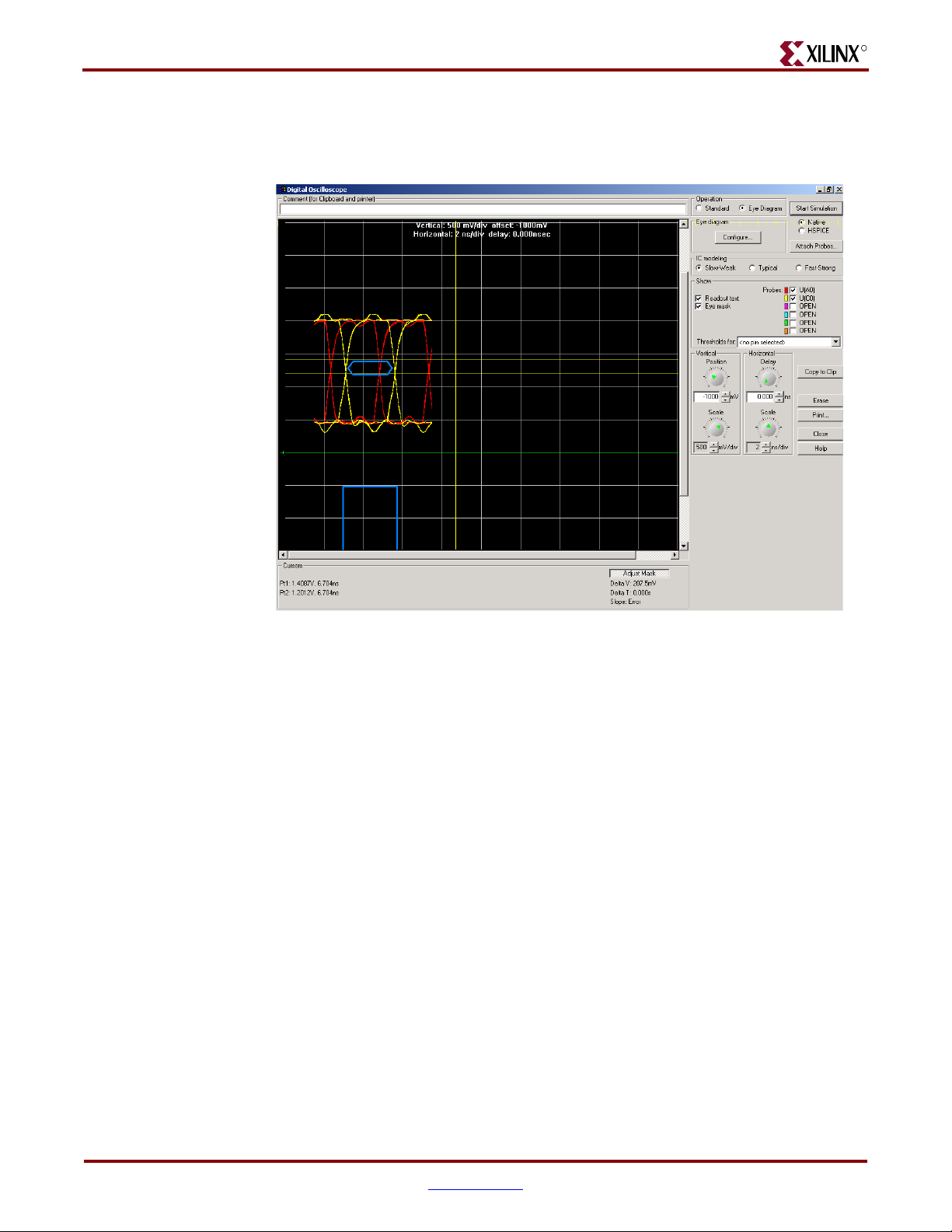

Eye Diagram for Data Signal Measured at the FPGA

Figure 4-9 shows the eye diagram for the data signals from the FPGA to the last memory

component.

X-Ref Target - Figure 4-9

ug060_c5_09_031504

Figure 4-9: Eye Diagram for Data at the FPGA to the Last Memory Component

ML361 Virtex-II Pro Memory Board www.xilinx.com 39

UG060 (v1.2) November 8, 2007

Page 40

Chapter 4: Signal Integrity Recommendations and Simulations

Clock Signal Simulations

The simulations in this subsection test the unidirectional clock signals from the FPGA to

memory. Simulations were performed for the following cases: typical, slow weak, and fast

strong. An eye diagram is provided also.

All clock signal simulations below have the following test conditions for typical, slow

weak, and fast strong cases:

R

• Topology for clock signals: 50

• At memory (yellow signal): 50

• At FPGA (red signal): 50

Ω transmission lines

Ω parallel termination pulled up to 1.3 V

Ω parallel termination pulled up to 1.3 V (SSTL2C2 drivers at

FPGA).

Figure 4-10 shows the clock signal terminations.

X-Ref Target - Figure 4-10

ug060_c5_10_091003

Figure 4-10: Clock Signal Terminations

40 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 41

R

IBIS Simulations

Typical Case for Clock Signals

For the typical case simulation, the resulting duty cycle is 48.1/52.04. Figure 4-11 shows the

simulation screen capture for this case.

X-Ref Target - Figure 4-11

ug060_c5_12_091003

Figure 4-11: Clock Signal from FPGA to Memory (Typical Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 41

UG060 (v1.2) November 8, 2007

Page 42

Chapter 4: Signal Integrity Recommendations and Simulations

Slow Weak Case for Clock Signals

For the slow weak case simulation, the resulting duty cycle is 48.66/51.48. Figure 4-12

shows the simulation screen capture for this case.

X-Ref Target - Figure 4-12

R

ug060_c5_13_091003

Figure 4-12: Clock Signal from FPGA to Memory (Slow Weak Case)

42 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 43

R

IBIS Simulations

Fast Strong Case for Clock Signals

For the fast strong case simulation, the resulting duty cycle is 48.1/51.48. Figure 4-13

shows the simulation screen capture for this case.

X-Ref Target - Figure 4-13

ug060_c5_11_091003

Figure 4-13: Clock Signal from FPGA to Memory (Fast Strong Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 43

UG060 (v1.2) November 8, 2007

Page 44

Chapter 4: Signal Integrity Recommendations and Simulations

Eye Diagram of Clock Signals at Memory

Figure 4-14 shows the eye diagram for the clock signals at memory.

X-Ref Target - Figure 4-14

R

Figure 4-14: Eye Diagram for Clock at Memory

ug060_c5_14_091003

44 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 45

R

Address and Control Signal Simulations

The simulations in this subsection test the unidirectional address and control signals from

the FPGA to five DDR memory components. Simulations were performed on the first,

middle, and last DDR memory component for the following cases: typical, slow weak, and

fast strong.

All clock signal simulations below have the following test conditions for typical, slow

weak, and fast strong cases:

• Topology: The FPGA and the five DDR components are placed in a straight line in a

daisy chain configuration.

♦ The distance between the FPGA and the first DDR component – 2.1 inches

♦ The distance between adjacent DDR components – 0.7 inches

♦ The distance between the FPGA and the last DDR component – 4.8 inches

• At memory (yellow signal): 50

component.

• At FPGA (red signal): 50

Figure 4-15 shows the address and control signal terminations.

X-Ref Target - Figure 4-15

Ω resistor pulled up to 1.3 V after the last DDR SDRAM

Ω transmission line is used (SSTL2C2 drivers at the FPGA).

IBIS Simulations

ug060_c5_15_091003

Figure 4-15: Address and Control Signal Terminations

ML361 Virtex-II Pro Memory Board www.xilinx.com 45

UG060 (v1.2) November 8, 2007

Page 46

Chapter 4: Signal Integrity Recommendations and Simulations

Typical Case Simulation at All Memory Components

Figure 4-16 shows the simulation screen capture for the typical case for all memory

components.

X-Ref Target - Figure 4-16

R

Figure 4-16: Address/Control Signals for All Memories

ug060_c5_16_091003

46 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 47

R

IBIS Simulations

Typical Case Simulation at First DDR Component

For the typical case simulation at the first DDR component, the resulting duty cycle is

48.94/51.2. Figure 4-17 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-17

ug060_c5_17_091003

Figure 4-17: Address/Control Signals at First DDR Memory (Typical Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 47

UG060 (v1.2) November 8, 2007

Page 48

Chapter 4: Signal Integrity Recommendations and Simulations

Slow Weak Corner Case Simulation at First DDR Component

For the slow weak corner case simulation at the first DDR component, the resulting duty

cycle is 49.22/51.48. Figure 4-18 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-18

R

ug060_c5_18_091003

Figure 4-18: Address/Control Signals at First DDR Memory (Slow Weak Case)

48 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 49

R

IBIS Simulations

Fast Strong Corner Case Simulation at First DDR Component

For the fast strong corner case simulation at the first DDR component, the resulting duty

cycle is 48.66/51.2. Figure 4-19 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-19

ug060_c5_19_091003

Figure 4-19: Address/Control Signals at First DDR Memory (Fast Strong Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 49

UG060 (v1.2) November 8, 2007

Page 50

Chapter 4: Signal Integrity Recommendations and Simulations

Typical Case Simulation at Last DDR Component

For the typical case simulation at the last DDR component, the resulting duty cycle is

49.22/50.92. Figure 4-20 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-20

R

ug060_c5_20_091003

Figure 4-20: Address/Control Signals at Last DDR Memory (Typical Case)

50 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 51

R

IBIS Simulations

Slow Weak Case Simulation at Last DDR Component

For the slow weak case simulation at the last DDR component, the resulting duty cycle is

49.22/50.63. Figure 4-21 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-21

ug060_c5_22_091003

Figure 4-21: Address/Control Signals at Last DDR Memory (Slow Weak Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 51

UG060 (v1.2) November 8, 2007

Page 52

Chapter 4: Signal Integrity Recommendations and Simulations

Fast Strong Corner Case Simulation at Last DDR Component

For the fast strong corner case simulation at the last DDR component, the resulting duty

cycle is 49.22/51.2. Figure 4-22 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-22

R

ug060_c5_21_091003

Figure 4-22: Address/Control Signals at Last DDR Memory (Fast Strong Corner

Case)

52 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 53

R

IBIS Simulations

Typical Case Simulation at Middle DDR Component

For the typical case simulation at the middle DDR component, the resulting duty cycle is

49.23/51.49. Figure 4-23 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-23

ug060_c5_23_091003

Figure 4-23: Address/Control Signals at Middle DDR Memory (Typical Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 53

UG060 (v1.2) November 8, 2007

Page 54

Chapter 4: Signal Integrity Recommendations and Simulations

Slow Weak Corner Case Simulation at Middle DDR Component

For the slow weak corner case simulation at the middle DDR component, the resulting

duty cycle is 49.22/50.64. Figure 4-24 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-24

R

ug060_c5_24_091003

Figure 4-24: Address/Control Signals at Middle DDR Memory (Slow Weak Corner

Case)

54 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 55

R

IBIS Simulations

Fast Strong Corner Case Simulation at Middle DDR Component

For the fast strong corner case simulation at the middle DDR component, the resulting

duty cycle is 48.94/51.2. Figure 4-25 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-25

ug060_c5_25_091003

Figure 4-25: Address/Control Signals at Middle DDR Memory (Fast Strong Corner

Case)

ML361 Virtex-II Pro Memory Board www.xilinx.com 55

UG060 (v1.2) November 8, 2007

Page 56

Chapter 4: Signal Integrity Recommendations and Simulations

Simulations with 10% Tolerance on the Transmission Line Impedance

These simulations illustrate the typical cases for data, clock, and address and control

signals.

Data Signals

This subsection provides the data simulation results for the following typical cases:

R

• From the last DDR memory to the FPGA (45

• From the last DDR memory to the FPGA (55

• From the FPGA to the last DDR memory (45

• From the memory to the FPGA (55

Ω transmission line impedance)

Ω transmission line impedance)

Ω transmission line impedance)

Ω transmission line impedance)

Data Signals from the Last DDR Memory to the FPGA with 45Ω Transmission Line

Impedance

For the typical case simulation from the last DDR component to the FPGA, the resulting

duty cycle is 48.66/51.48. Figure 4-26 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-26

ug060_c5_26_031204

Figure 4-26: Data Signals from Last DDR Memory to FPGA (45Ω Impedance)

56 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 57

R

IBIS Simulations

Data Signals from the Last DDR Memory to the FPGA with 55Ω Transmission Line

Impedance

For the typical case simulation from the last DDR component to the FPGA, the resulting

duty cycle is 46.4/52.62. Figure 4-27 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-27

ug060_c5_27_031204

Figure 4-27: Data Signals from Last DDR Memory to FPGA (55Ω Impedance)

ML361 Virtex-II Pro Memory Board www.xilinx.com 57

UG060 (v1.2) November 8, 2007

Page 58

Chapter 4: Signal Integrity Recommendations and Simulations

Data Signals from FPGA to the Last DDR Memory Component with 45Ω

Transmission Line Impedance

For the typical case simulation from the FPGA to the last DDR component, the resulting

duty cycle is 46.96/53.18. Figure 4-28 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-28

R

ug060_c5_28_091003

Figure 4-28: Data Signals from FPGA to Last DDR Memory (45Ω Impedance)

58 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 59

R

IBIS Simulations

Data Signals from Memory to the FPGA with 55Ω Transmission Line Impedance

For the typical case simulation from memory to the FPGA, the resulting duty cycle is

48.66/51.48. Figure 4-29 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-29

ug060_c5_29_091003

Figure 4-29: Data Signals from Memory to FPGA (55Ω Impedance)

ML361 Virtex-II Pro Memory Board www.xilinx.com 59

UG060 (v1.2) November 8, 2007

Page 60

Chapter 4: Signal Integrity Recommendations and Simulations

Clock Signals

This subsection provides the clock simulation results for the following typical cases:

R

• With 45

• With 55

Ω transmission line impedance

Ω transmission line impedance

Clock Signals with 45Ω Transmission Line Impedance

For the typical case simulation with a 45Ω transmission line impedance, the resulting duty

cycle is 48.66/ 52.04. Figure 4-30 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-30

ug060_c5_30_091003

Figure 4-30: Clock Signals with 45Ω Impedance

60 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 61

R

IBIS Simulations

Clock Signals with 55Ω Transmission Line Impedance

For the typical case simulation with a 55Ω transmission line impedance, the resulting duty

cycle is 48.1/51.48. Figure 4-31 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-31

Figure 4-31: Clock Signals with 55Ω Impedance

ug060_c5_31_091003

ML361 Virtex-II Pro Memory Board www.xilinx.com 61

UG060 (v1.2) November 8, 2007

Page 62

Chapter 4: Signal Integrity Recommendations and Simulations

Address/Control Signals

This subsection provides the address and control simulation results for the following

typical cases:

R

• With 45

• With 55

Ω transmission line impedance measured at the first DDR component

Ω transmission line impedance measured at the first DDR component

Address and Control Signals with 45Ω Transmission Lines Measured at the First

DDR Component

For the typical case simulation with a 45Ω transmission line impedance measured at the

first DDR component, the resulting duty cycle is 48.94/51.2. Figure 4-32 shows the

simulation screen capture for this case.

X-Ref Target - Figure 4-32

ug060_c5_32_091003

Figure 4-32: Address/Control Signals with 45Ω Impedance Measured at First DDR

Component

62 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 63

R

IBIS Simulations

Address and Control Signals with 55Ω Transmission Lines Measured at the First

DDR Component

For the typical case simulation with a 55Ω transmission line impedance measured at the

first DDR component, the resulting duty cycle is 48.66/51.48. Figure 4-33 shows the

simulation screen capture for this case.

X-Ref Target - Figure 4-33

ug060_c5_33_091003

Figure 4-33: Address/Control Signals with 55Ω Impedance Measured at First DDR

Component

ML361 Virtex-II Pro Memory Board www.xilinx.com 63

UG060 (v1.2) November 8, 2007

Page 64

Chapter 4: Signal Integrity Recommendations and Simulations

R

64 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 65

R

Board Layout Guidelines

This chapter provides information on decoupling capacitors, ground signals, and PCB

layout.

Decoupling Guidelines

This section lists the decoupling capacitors used with the major components of the ML361

board. Refer to the board schematics for exact placement.

Tab le 5- 1 lists the decoupling capacitors for the Virtex-II Pro FPGA. Refer to the Xilinx

XAPP623

implemented for each bank, VCCI, VAUX, and VREF.

application note for the methodology. A balanced decoupling network is

Chapter 5

Table 5-1: FPGA Decoupling Capacitors

Pin(s) Capacitor Value Distribution

VCCI

1 capacitor per

pin, in a

balanced

decoupling

network.

VA U X

1 capacitor per

pin, in a

balanced

decoupling

network.

Bank 2

39 SSTL2_II

20 SSTL2_I

0.039 µF ceramic capacitor, 0402 10V X7R –20/+20% 10

0.22 µF ceramic capacitor, 0603 10V X7R –20/+20% 5

1 µF ceramic capacitor, 0603 6V X7R –20/+20% 6

10 µF ceramic capacitor, 1206 16V Z5U –20/+20% 3

330 µF solid tantalum capacitor, 6.3V 2

0.039 µF ceramic capacitor, 0402 10V X7R –20/+20% 4

0.22 µF ceramic capacitor, 0603 10V X7R –20/+20% 3

1 µF ceramic capacitor, 0603 6V X7R –20/+20% 3

10 µF ceramic capacitor, 1206 16V Z5U –20/+20% 1

330 µF solid tantalum capacitor, 6.3V 1

Budget = (61/120) = .51 x 12 = 7 caps

0.039 µF ceramic capacitor, 0402 10V X7R –20/+20% 2

0.22 µF ceramic capacitor, 0603 10V X7R –20/+20% 1

1 µF ceramic capacitor, 0603 6V X7R –20/+20% 1

330 µF solid tantalum capacitor, 6.3V 1

ML361 Virtex-II Pro Memory Board www.xilinx.com 65

UG060 (v1.2) November 8, 2007

Page 66

Chapter 5: Board Layout Guidelines

Table 5-1: FPGA Decoupling Capacitors (Cont’d)

Pin(s) Capacitor Value Distribution

R

Bank 2

VREF

7 VREFs used, one capacitor for each VREF

0.039 µF ceramic capacitor, 0402 10V X7R –20/+20% 2

0.22 µF ceramic capacitor, 0603 10V X7R –20/+20% 1

1 µF ceramic capacitor, 0603 6V X7R –20/+20% 1

330 µF solid tantalum capacitor, 6.3V 1, shared with bank 3

Bank 3 Same as Bank 2 for both I/Os and VREFs

Bank 6 Same as Bank 2 for both I/Os and VREFs

Bank 7 Same as Bank 2 for both I/Os and VREFs

Bank 1

1 Reset,

8 GPIO,

4 LED,

8 DIP,

14 DISPLAY

0.033 µF ceramic capacitor, 0402 6V X7R –20/+20% 1

0.22 µF ceramic capacitor, 0603 6V X7R –20/+20% 1

1 µF ceramic capacitor, 0603 6V X7R –20/+20% 1

330 µF solid tantalum capacitor, 6.3V 1

Bank 0 Similar to Bank 1

Bank 4 Similar to Bank 1

Bank 5 Similar to Bank 1

Tab le 5- 2 lists the decoupling capacitors for the DDR SDRAMs.

Table 5-2: DDR SDRAM Decoupling Capacitors

Pin(s) Capacitor Value Quantity Distribution

VDD,

VDDQ,

VREF, VSS,

VSSQ

0.01 µF ceramic capacitor, 0402 6V X7R –20/+20% 8 1 capacitor per pin, in a

0.1 µF ceramic capacitor, 0603 6V X7R –20/+20% 8

balanced decoupling network.

17 total for each component

330 µF solid tantalum capacitor, 6.3V 1

Tab le 5- 3 lists the decoupling capacitors for the DDR DIMM.

Table 5-3: DIMM Decoupling Capacitors

Pin(s) Capacitor Value Distribution

VDD 0.01 µF ceramic capacitor, 0402 6V X7R –20/+20% 1 per VDD pin

0.1 µF ceramic capacitor, 0603 6V X7R –20/+20% 1 per VDD pin

330 µF solid tantalum capacitor, 6.3V 1

VDDQ 0.01 µF ceramic capacitor, 0402 6V X7R –20/+20% 1 per VDDQ pin

0.1 µF ceramic capacitor, 0603 6V X7R –20/+20% 1 per VDDQ pin

330 µF solid tantalum capacitor, 6.3V 2

66 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Page 67

R

Providing Additional Ground Pins

Table 5-3: DIMM Decoupling Capacitors (Cont’d)

Pin(s) Capacitor Value Distribution

VREF 0.01 µF ceramic capacitor, 0402 6V X7R –20/+20% 1 VREF to GND

1 VREF to 2.6V

1 GND to 2.6V

0.1 µF ceramic capacitor, 0603 6V X7R –20/+20% 1 VREF to GND

1 VREF to 2.6V

1 GND to 2.6V

VSS 0.01 µF ceramic capacitor, 0402 6V X7R –20/+20% 8

0.1 µF ceramic capacitor, 0603 6V X7R –20/+20% 4

330 µF solid tantalum capacitor, 6.3V 1

Providing Additional Ground Pins

Additional Ground pins can be added by tying unused and no connect pins to GND.

Board Stackup Guidelines

Tab le 5- 4 shows a suggested stackup of a 16-layer board (8 signals, 8 planes).