Page 1

MicroBlaze

Processor

Reference Guide

Embedded Development Kit

EDK 8.2i

UG081 (v6.0) June 1, 2006

R

Page 2

© 2006 Xilinx, Inc. All Rights Reserved. XILINX, the Xilinx logo, and other designated brandsincludedhereinaretrademarksofXilinx,Inc.

All other trademarks are the property of their respective owners.

NOTICEOFDISCLAIMER:Xilinxis providing this design, code, or information "as is." By providing the design, code, or information as one

possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any

claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any

warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that

this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

MicroBlaze Processor Reference Guide www.xilinx.com UG081 (v6.0) June 1, 2006

1-800-255-7778

Page 3

MicroBlaze Processor Reference Guide

UG081 (v6.0) June 1, 2006

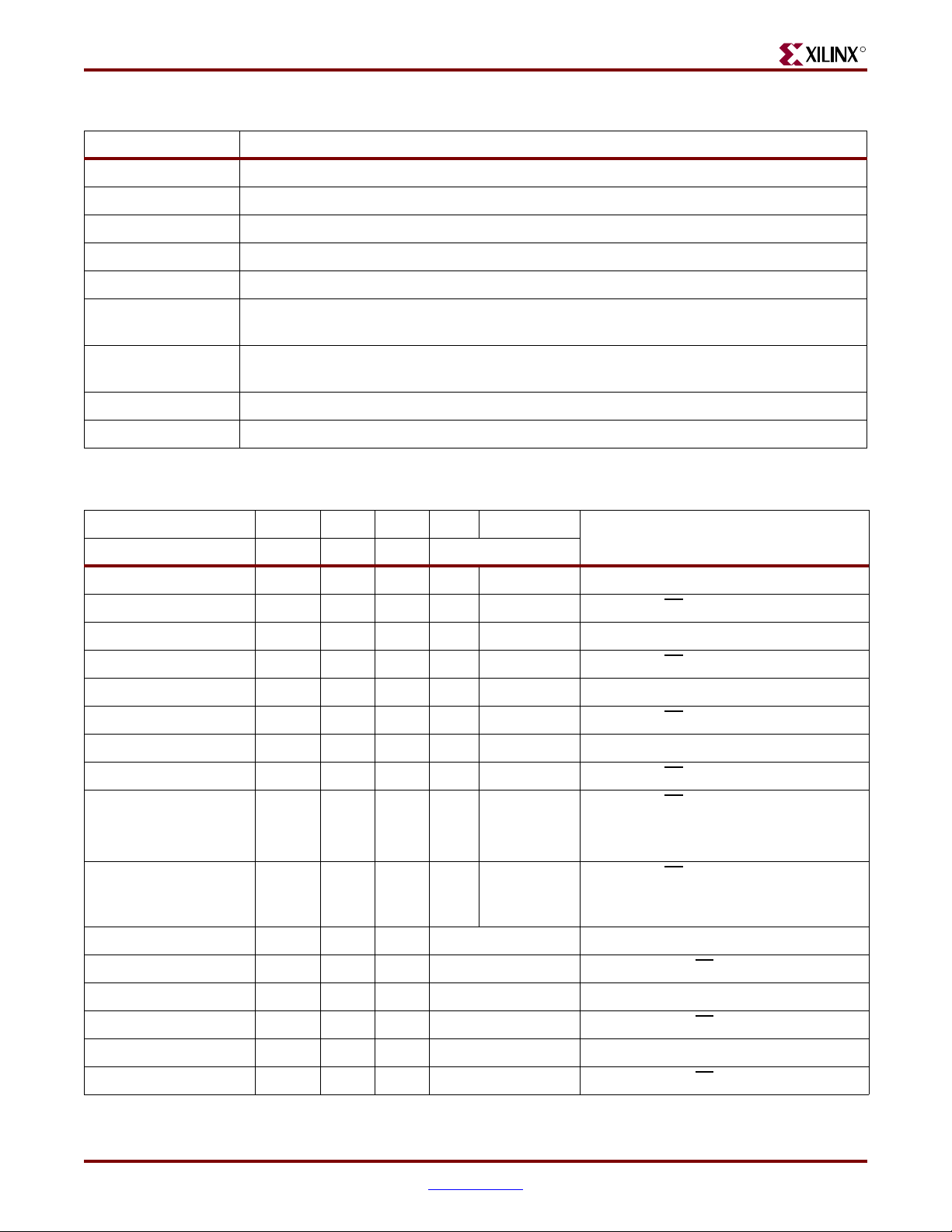

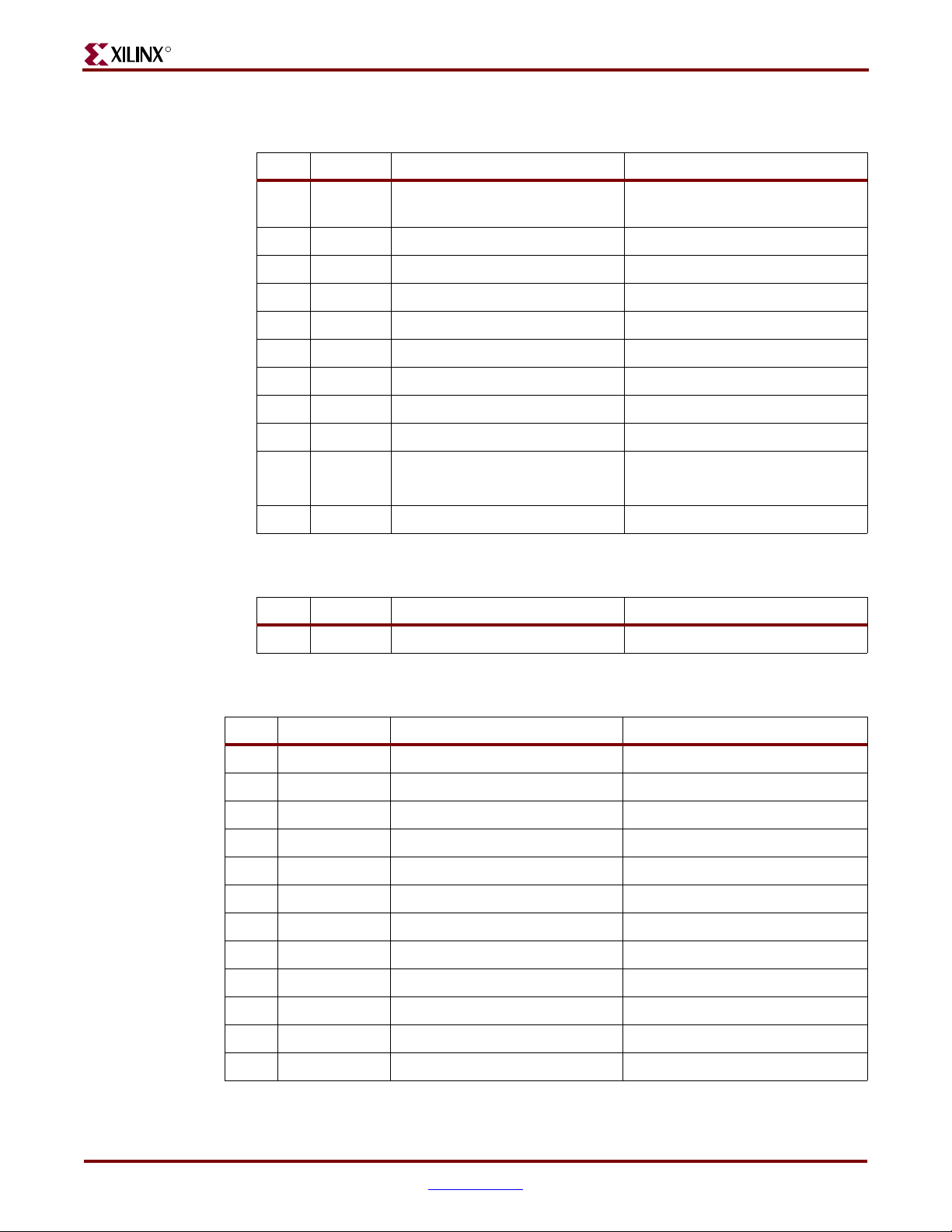

The following table shows the revision history for this document.

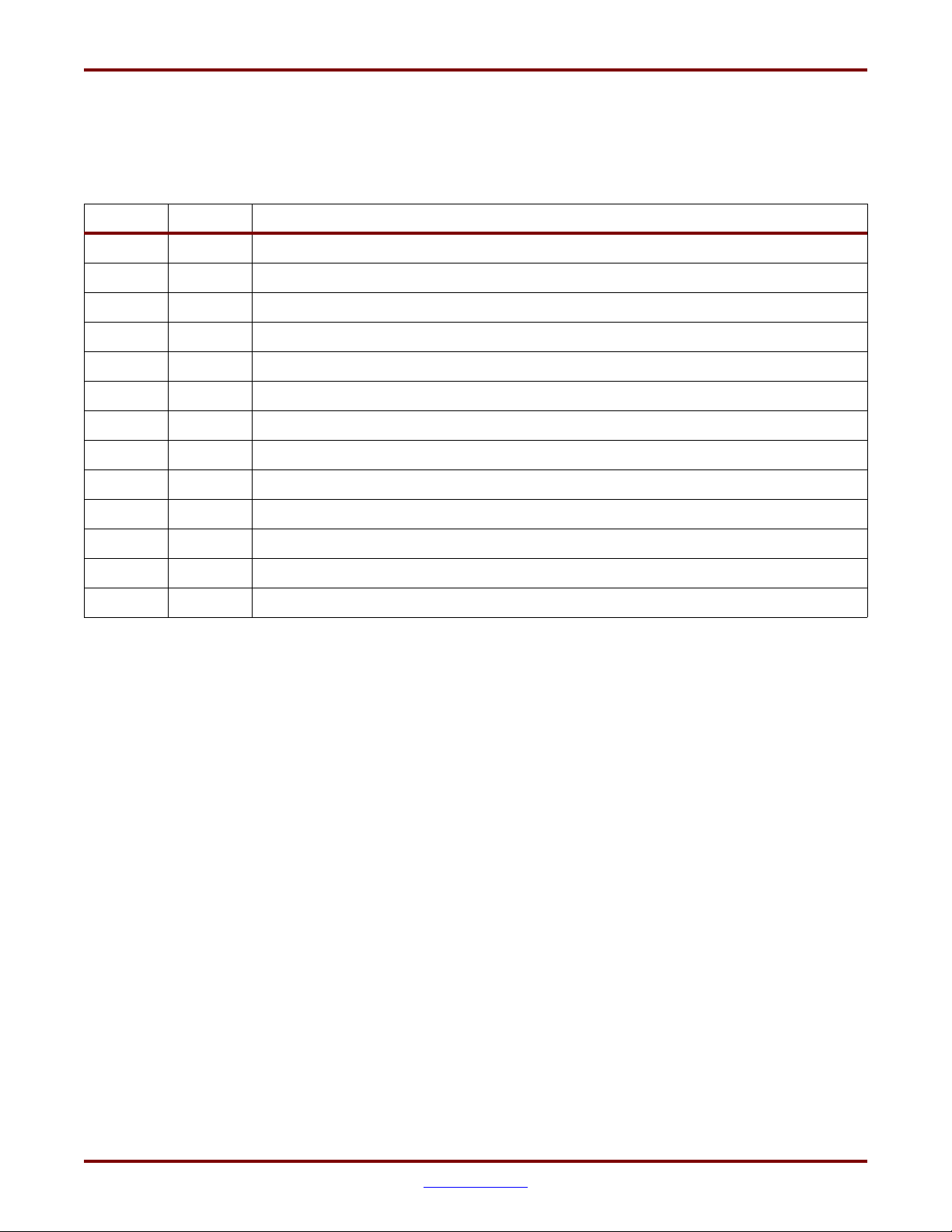

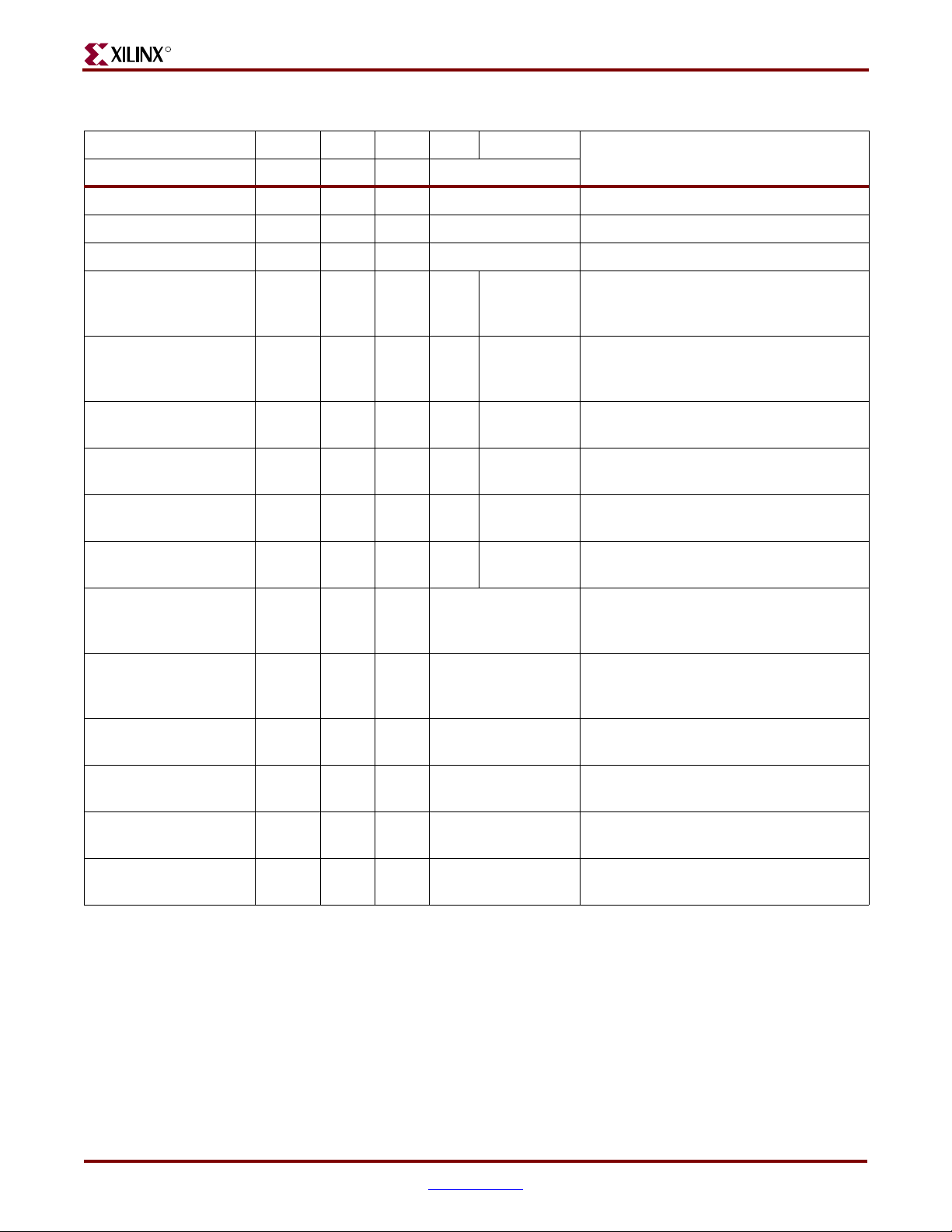

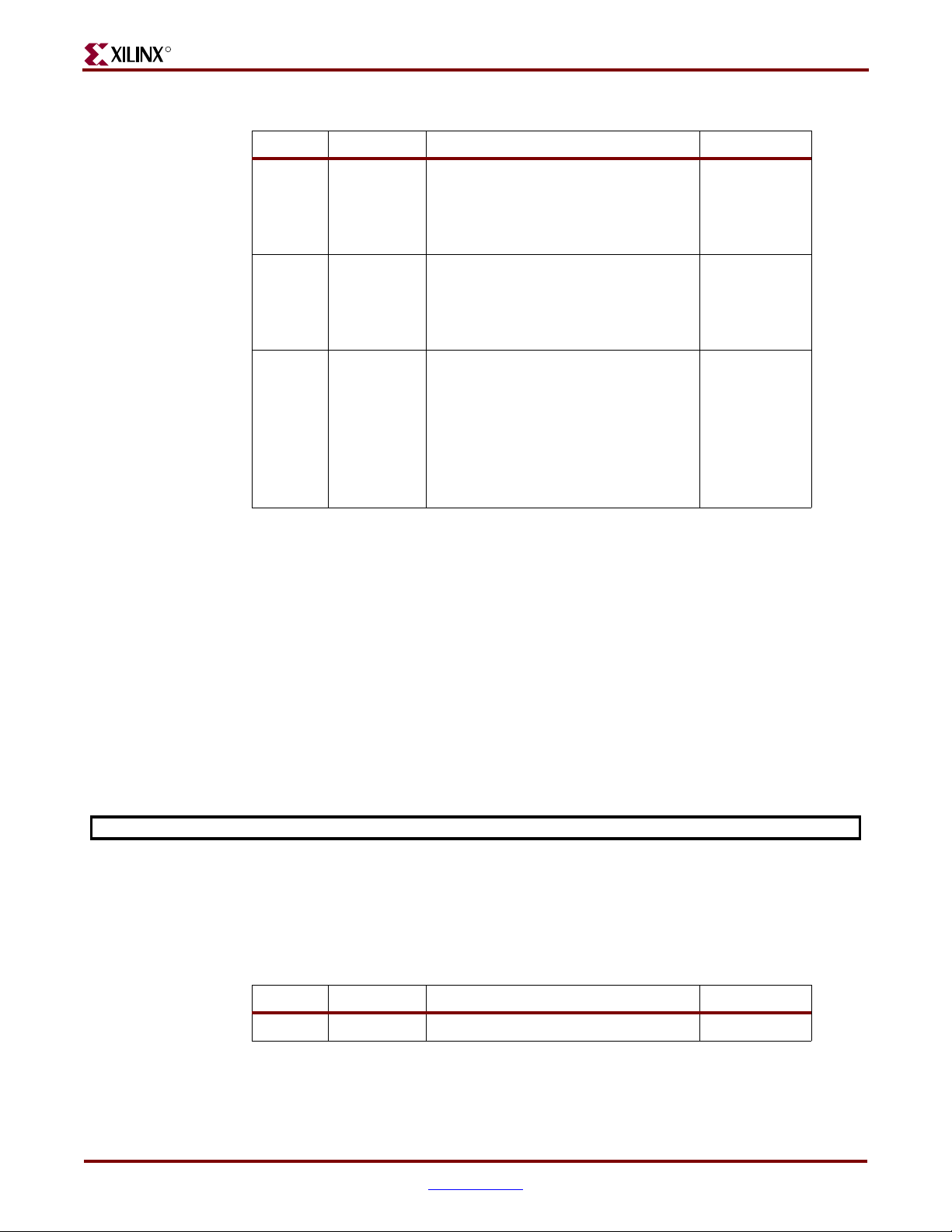

Date Version Revision

10/01/02 1.0 Xilinx EDK 3.1 release

03/11/03 2.0 Xilinx EDK 3.2 release

09/24/03 3.0 Xilinx EDK 6.1 release

02/20/04 3.1 Xilinx EDK 6.2 release

08/24/04 4.0 Xilinx EDK 6.3 release

09/21/04 4.1 Minor corrections for EDK 6.3 SP1 release

11/18/04 4.2 Minor corrections for EDK 6.3 SP2 release

01/20/05 5.0 Xilinx EDK 7.1 release

04/02/05 5.1 Minor corrections for EDK 7.1 SP1 release

05/09/05 5.2 Minor corrections for EDK 7.1 SP2 release

10/05/05 5.3 Minor corrections for EDK 8.1 release

02/21/06 5.4 Corrections for EDK 8.1 SP2 release

06/01/06 6.0 Xilinx EDK 8.2 release

UG081 (v6.0) June 1, 2006 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778

Page 4

MicroBlaze Processor Reference Guide www.xilinx.com UG081 (v6.0) June 1, 2006

1-800-255-7778

Page 5

Preface: About This Guide

Manual Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Online Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 1: MicroBlaze Architecture

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Data Types and Endianness . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

General Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Special Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Pipeline Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Branches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Memory Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Reset, Interrupts, Exceptions, and Break . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Hardware Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Breaks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

User Vector (Exception) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Instruction Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

General Instruction Cache Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Instruction Cache Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Instruction Cache Software Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Data Cache. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

General Data Cache Functionality. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Data Cache Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Data Cache Software Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Floating Point Unit (FPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Rounding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Fast Simplex Link (FSL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Hardware Acceleration using FSL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Debug and Trace. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Debug Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Trace Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Chapter 2: MicroBlaze Signal Interface Description

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

UG081 (v6.0) June 1, 2006 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778

Page 6

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

MicroBlaze I/O Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

On-Chip Peripheral Bus (OPB) Interface Description . . . . . . . . . . . . . . . . . . . . . . . . 48

Local Memory Bus (LMB) Interface Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

LMB Signal Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

LMB Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Read and Write Data Steering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Fast Simplex Link (FSL) Interface Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Master FSL Signal Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Slave FSL Signal Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

FSL Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Xilinx CacheLink (XCL) Interface Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

CacheLink Signal Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

CacheLink Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Debug Interface Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Trace Interface Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

MicroBlaze Core Configurability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Chapter 3: MicroBlaze Application Binary Interface

Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Register Usage Conventions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Stack Convention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Calling Convention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Memory Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Small data area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Data area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Common un-initialized area. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Literals or constants . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Interrupt and Exception Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Chapter 4: MicroBlaze Instruction Set Architecture

Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

UG081 (v6.0) June 1, 2006 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778

Page 7

R

About This Guide

Welcome to the MicroBlaze Processor Reference Guide. This document provides

information about the 32-bit soft processor MicroBlaze, which is part of the Embedded

Processor Development Kit (EDK). The document is intended as a guide to the MicroBlaze

hardware architecture.

Manual Contents

This manual discusses the following topics specific to MicroBlaze soft processor:

• Core Architecture

• Bus Interfaces and Endianness

• Application Binary Interface

• Instruction Set Architecture

Preface

Additional Resources

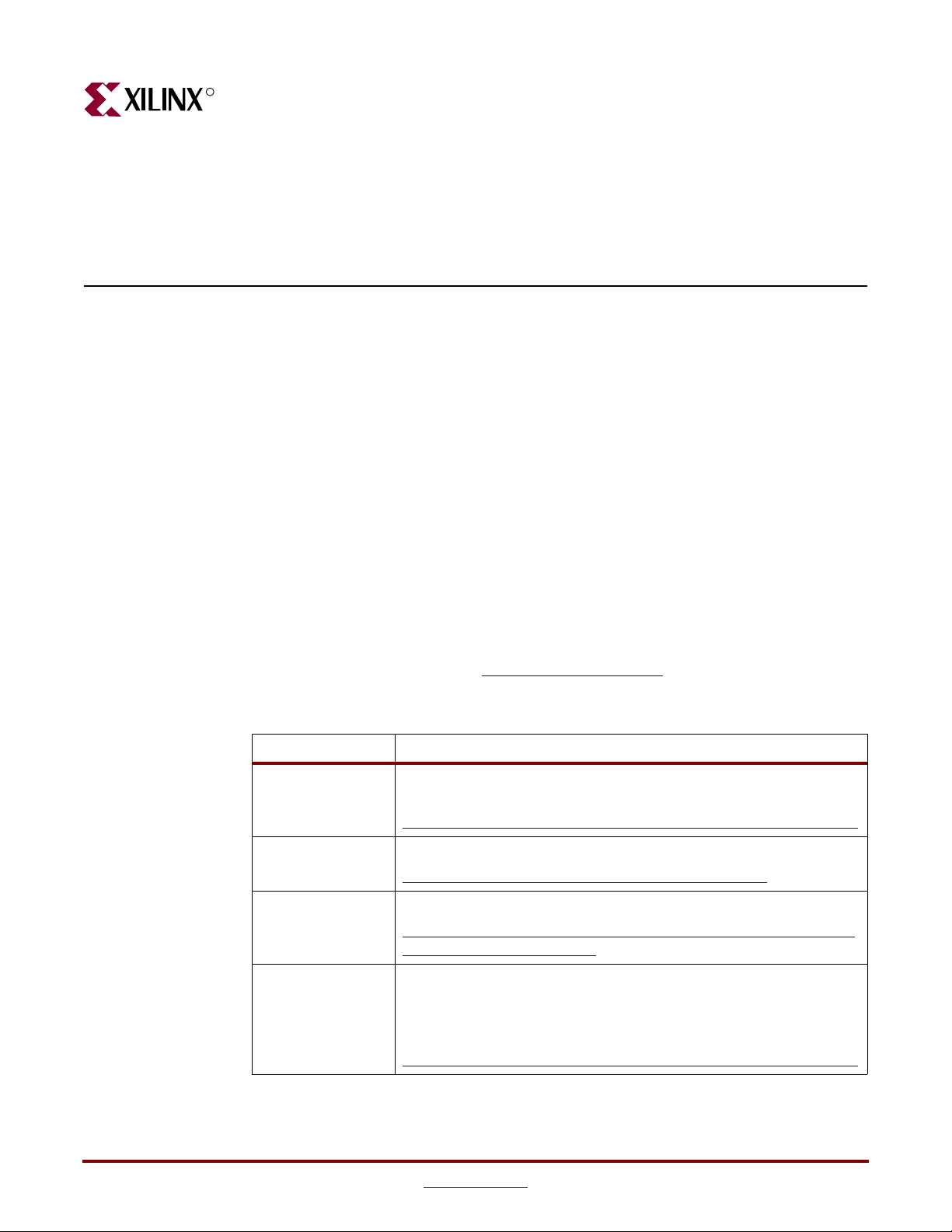

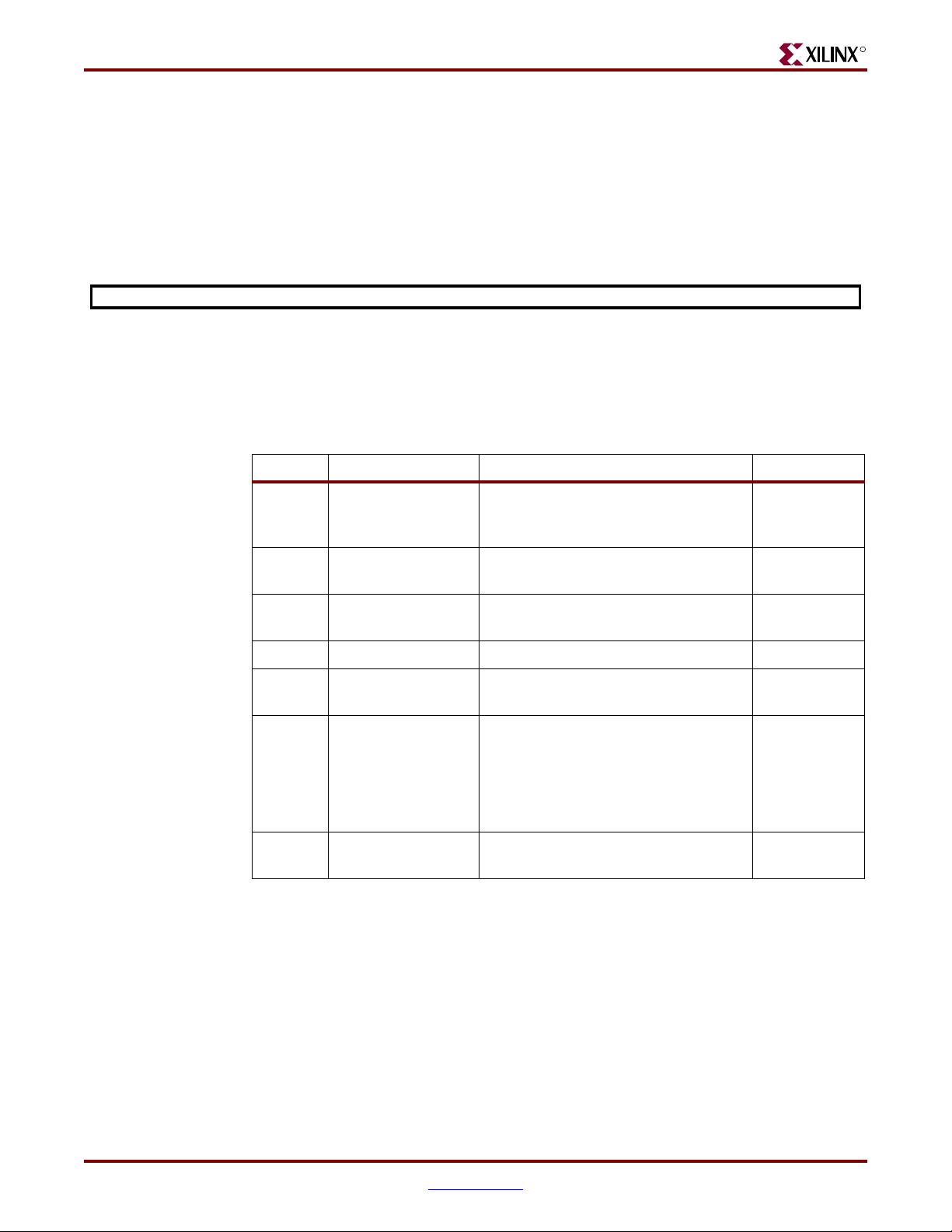

For additional information, go to http://support.xilinx.com. The following table lists

some of the resources you can access from this web-site. You can also directly access these

resources using the provided URLs.

Resource Description/URL

Tutorials Tutorials covering Xilinx design flows, from design entry to

Answer Browser Database of Xilinx solution records

Application Notes Descriptions of device-specific design techniques and approaches

Data Book Pages from The Programmable Logic Data Book, which contains

verification and debugging

http://support.xilinx.com/support/techsup/tutorials/index.htm

http://support.xilinx.com/xlnx/xil_ans_browser.jsp

http://www.xilinx.com/xlnx/xweb/xil_publications_index.jsp?c

ategory=Application+Notes

device-specific information on Xilinx device characteristics,

including readback, boundary scan, configuration, length count,

and debugging

http://support.xilinx.com/xlnx/xweb/xil_publications_index.jsp

MicroBlaze Processor Reference Guide www.xilinx.com 7

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 8

R

Conventions

Typographical

Preface: About This Guide

Resource Description/URL

Problem Solvers Interactive tools that allow you to troubleshoot your design issues

http://support.xilinx.com/support/troubleshoot/psolvers.htm

Tech Tips Latest news, design tips, and patch information for the Xilinx

design environment

http://www.support.xilinx.com/xlnx/xil_tt_home.jsp

GNU Manuals The entire set of GNU manuals

http://www.gnu.org/manual

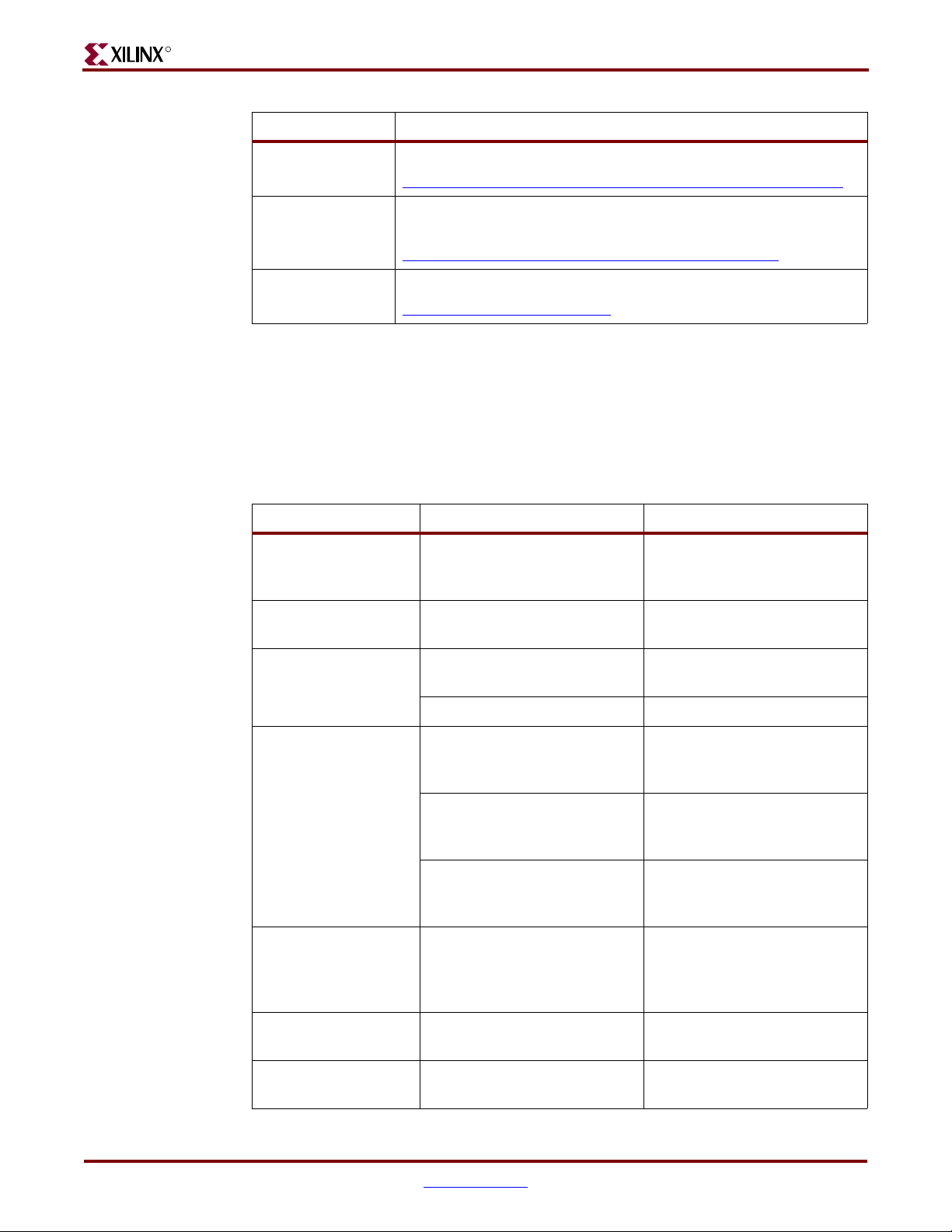

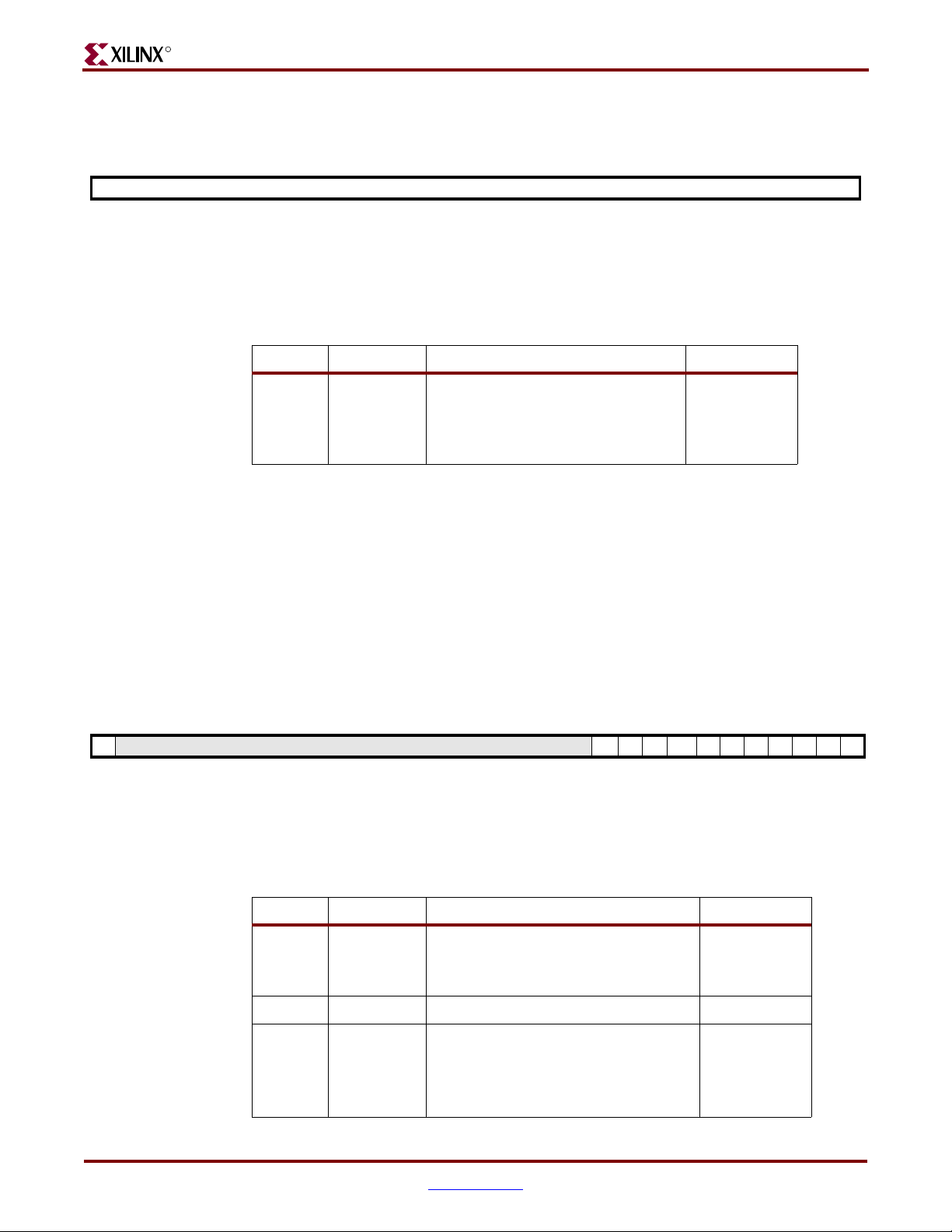

This document uses the following conventions. An example illustrates each convention.

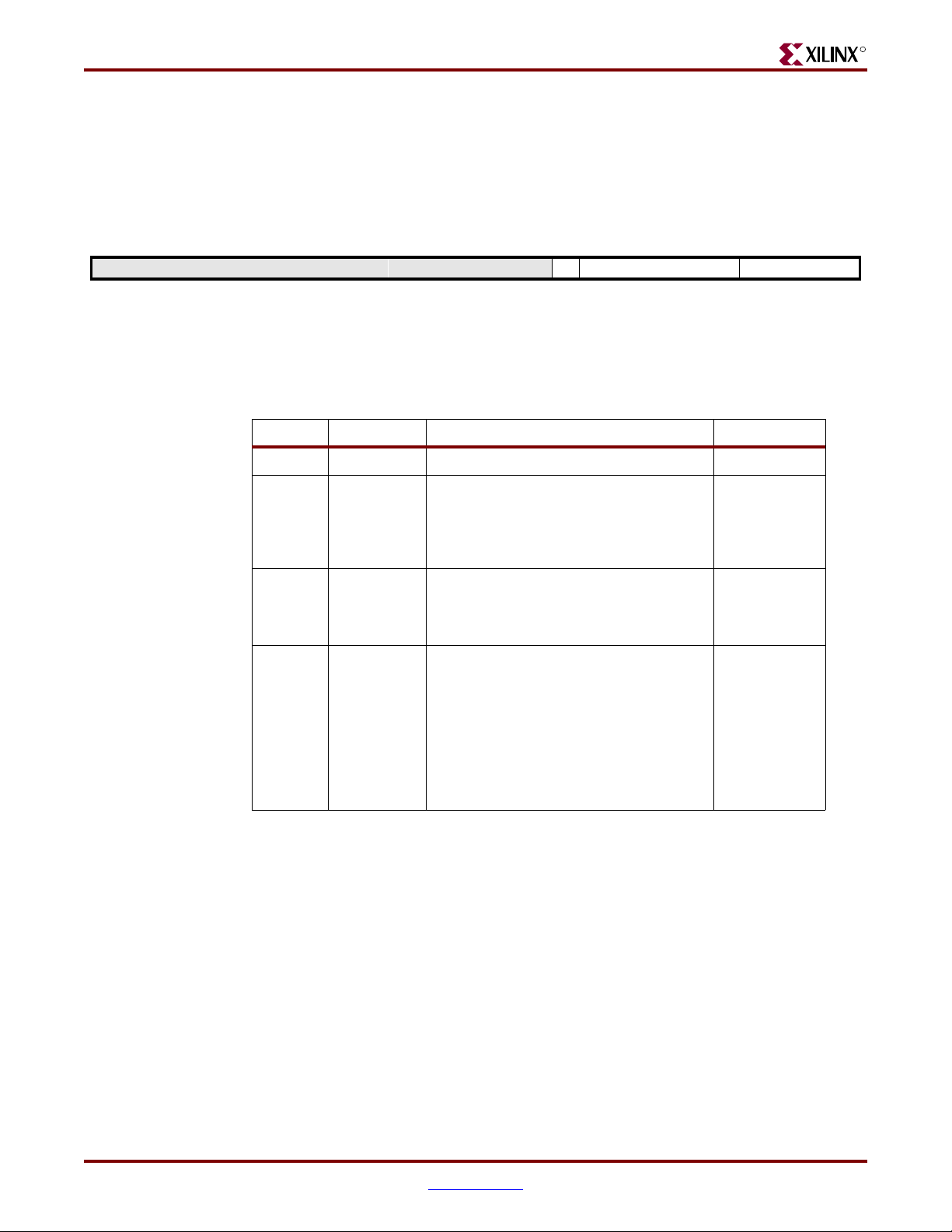

The following typographical conventions are used in this document:

Convention Meaning or Use Example

Messages, prompts, and

Courier font

Courier bold

Helvetica bold

Italic font

Square brackets [ ]

program files that the system

displays

Literal commands that you

enter in a syntactical statement

Commands that you select

from a menu

Keyboard shortcuts Ctrl+C

Variables in a syntax

statement for which you must

supply values

References to other manuals

Emphasis in text

An optional entry or

parameter. However, in bus

specifications, such as

bus[7:0], they are required.

speed grade: - 100

ngdbuild design_name

File → Open

ngdbuild design_name

See the Development System

Reference Guide for more

information.

If a wire is drawn so that it

overlaps the pin of a symbol,

the two nets are not connected.

ngdbuild [option_name]

design_name

Braces { }

Vertical bar |

8 www.xilinx.com MicroBlaze Processor Reference Guide

A list of items from which you

must choose one or more

Separates items in a list of

choices

1-800-255-7778 UG081 (v6.0) June 1, 2006

lowpwr ={on|off}

lowpwr ={on|off}

Page 9

Conventions

R

Convention Meaning or Use Example

Vertical ellipsis

Horizontal ellipsis ...

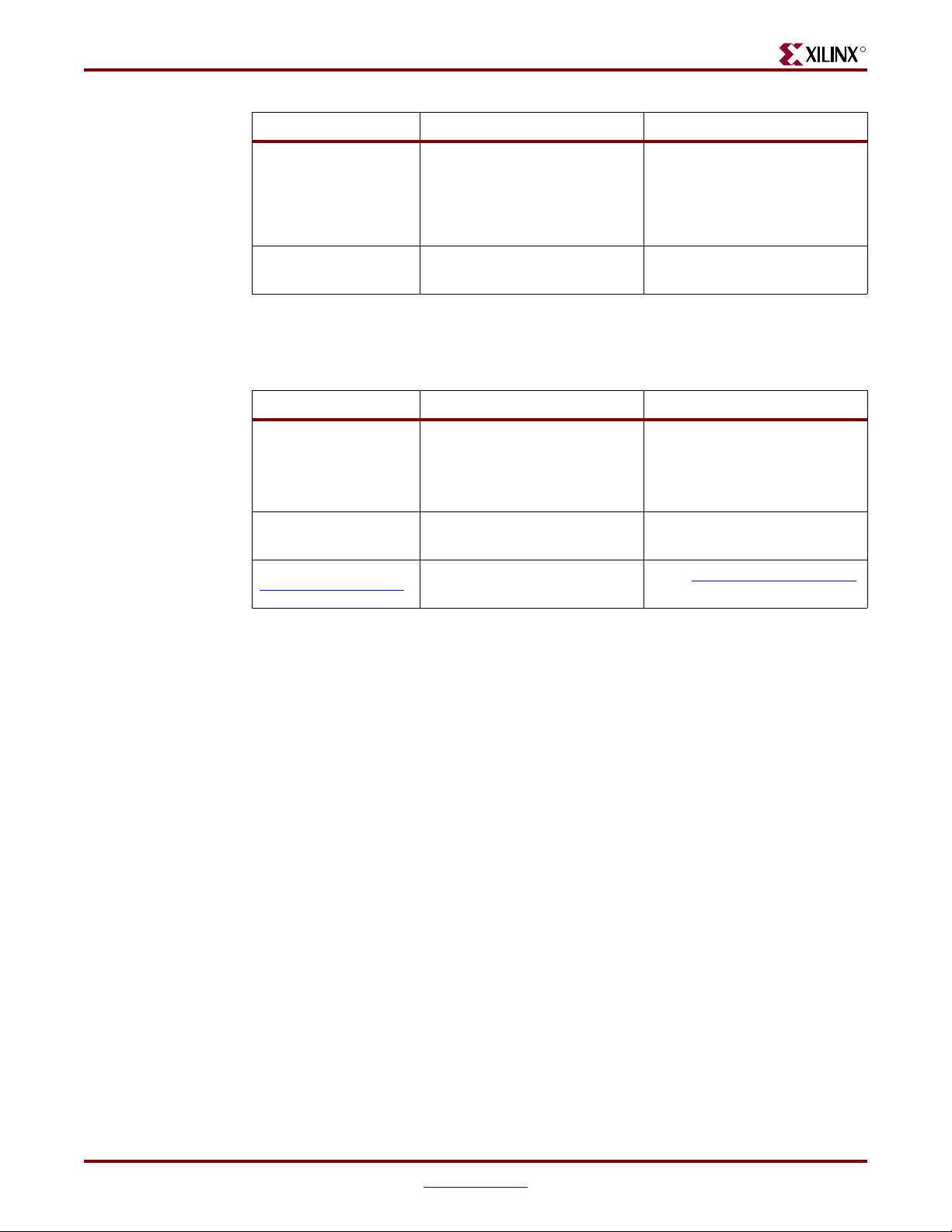

Online Document

The following conventions are used in this document:

Convention Meaning or Use Example

Blue text

Red text

Blue, underlined text Hyperlink to a web-site (URL)

IOB #1: Name = QOUT’

.

.

Repetitive material that has

been omitted

.

Repetitive material that has

been omitted

Cross-reference link to a

location in the current file or

in another file in the current

document

Cross-reference link to a

location in another document

IOB #2: Name = CLKIN’

.

.

.

allow block block_name

loc1 loc2 ... locn;

See the section “Additional

Resources” for details.

Refer to “Title Formats” in

Chapter 1 for details.

See Figure 2-5 in the Virtex-II

Handbook.

Go to http://www.xilinx.com

for the latest speed files.

MicroBlaze Processor Reference Guide www.xilinx.com 9

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 10

R

Preface: About This Guide

10 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 11

R

MicroBlaze Architecture

Overview

The MicroBlaze embedded processor soft core is a reduced instruction set computer (RISC)

optimized for implementation in Xilinx field programmable gate arrays (FPGAs).

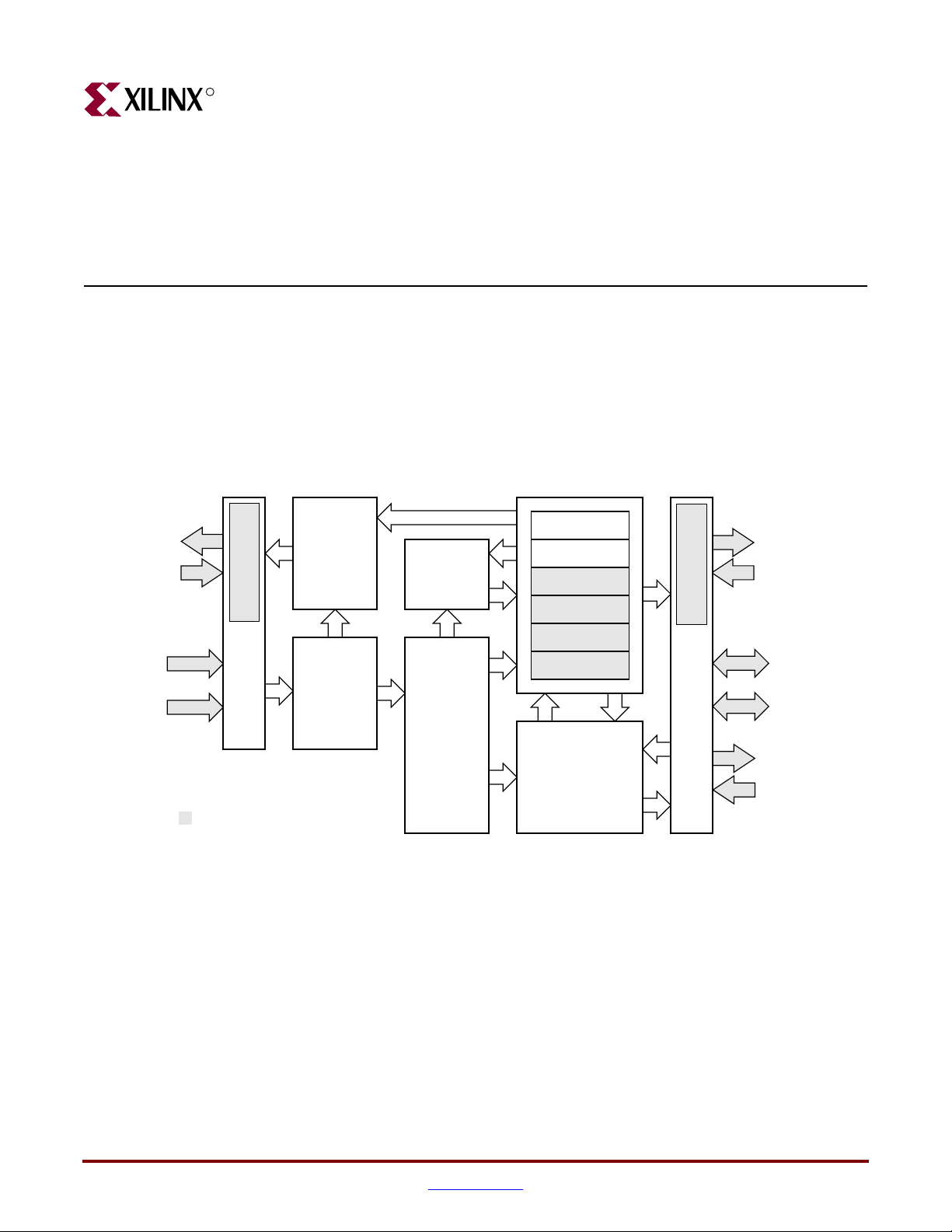

Figure 1-1 shows a functional block diagram of the MicroBlaze core.

Chapter 1

IXCL_M

IXCL_S

Features

bus interface bus interface

I-Cache

IOPB

ILMB

Bus

IF

Optional MicroBlaze feature

Program

Counter

Instruction

Special

Purpose

Registers

Buffer

Instruction

Decode

ALU

Shift

Barrel Shift

Multiplier

Divider

FPU

Register File

32 X 32b

Figure 1-1: MicroBlaze Core Block Diagram

Data-sideInstruction-side

D-Cache

Bus

IF

DXCL_M

DXCL_S

DOPB

DLMB

MFSL 0..7

SFSL 0..7

The MicroBlaze soft core processor is highly configurable, allowing users to select a

specific set of features required by their design.

The processor’s fixed feature set includes:

• Thirty-two 32-bit general purpose registers

• 32-bit instruction word with three operands and two addressing modes

• 32-bit address bus

• Single issue pipeline

MicroBlaze Processor Reference Guide www.xilinx.com 11

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 12

R

Chapter 1: MicroBlaze Architecture

In addition to these fixed features the MicroBlaze processor is parametrized to allow

selective enabling of additional functionality. Older (deprecated) versions of MicroBlaze

support a subset of the optional features described in this manual. Only the latest (active)

version of MicroBlaze (v5.00a) supports all options.

Xilinx recommends that all new designs use the latest active version of the MicroBlaze

processor.

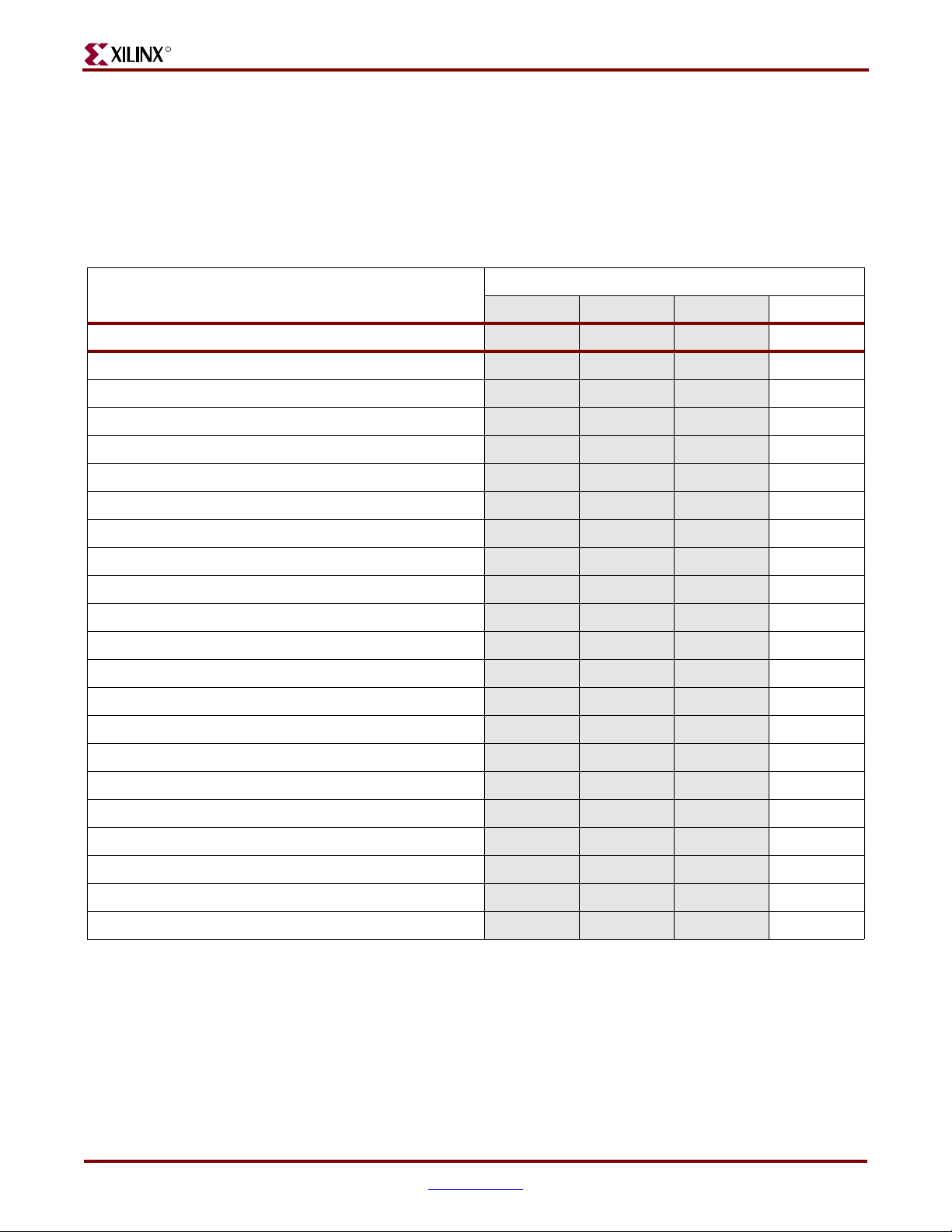

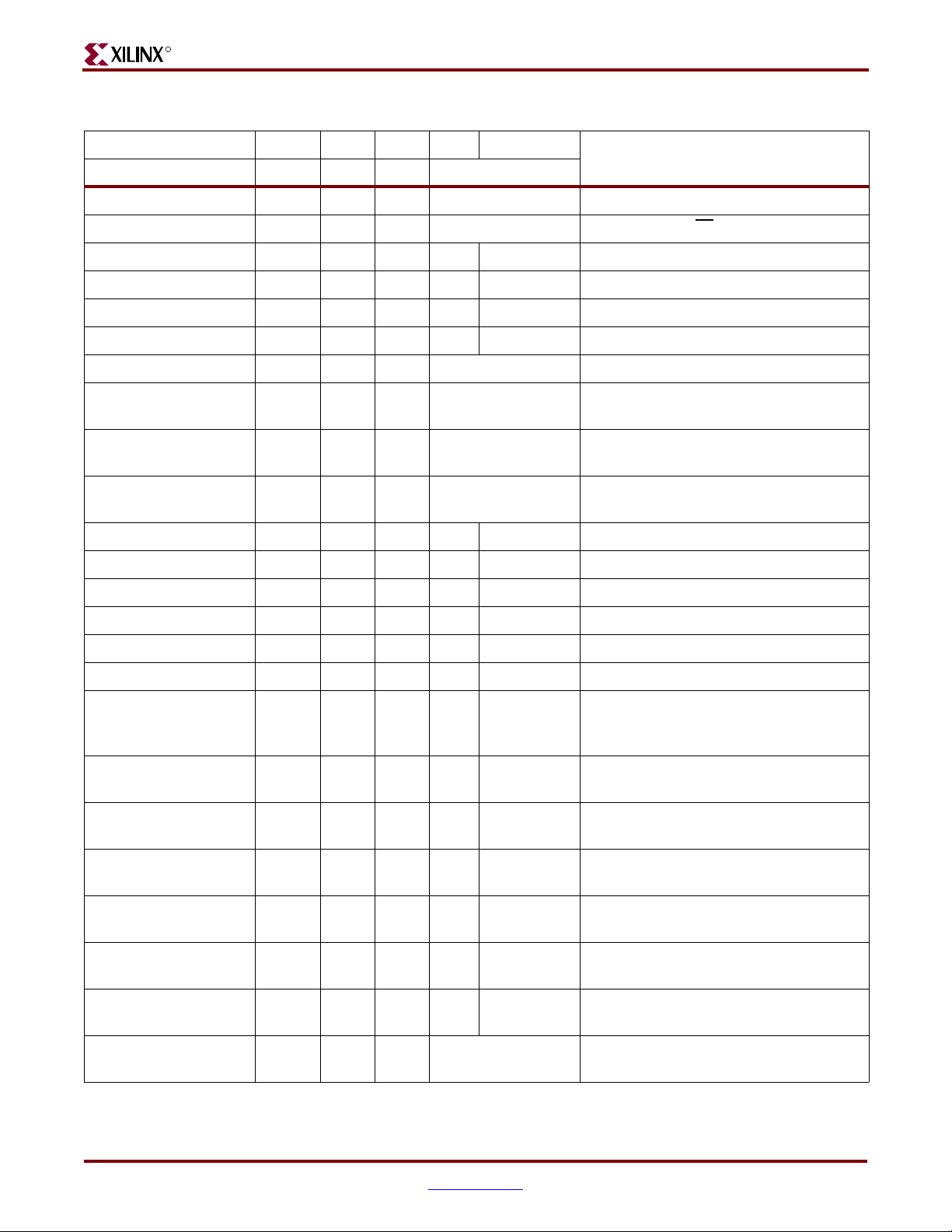

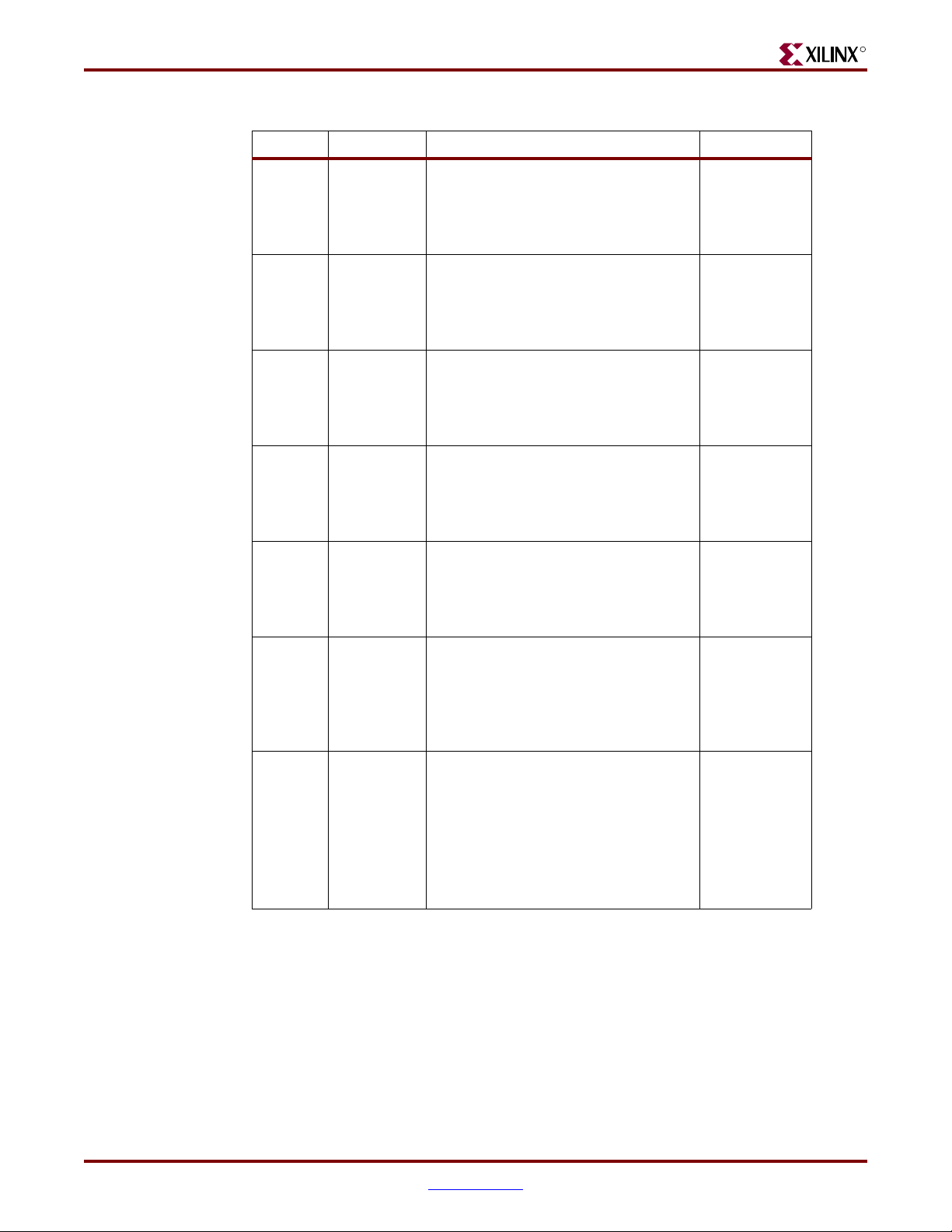

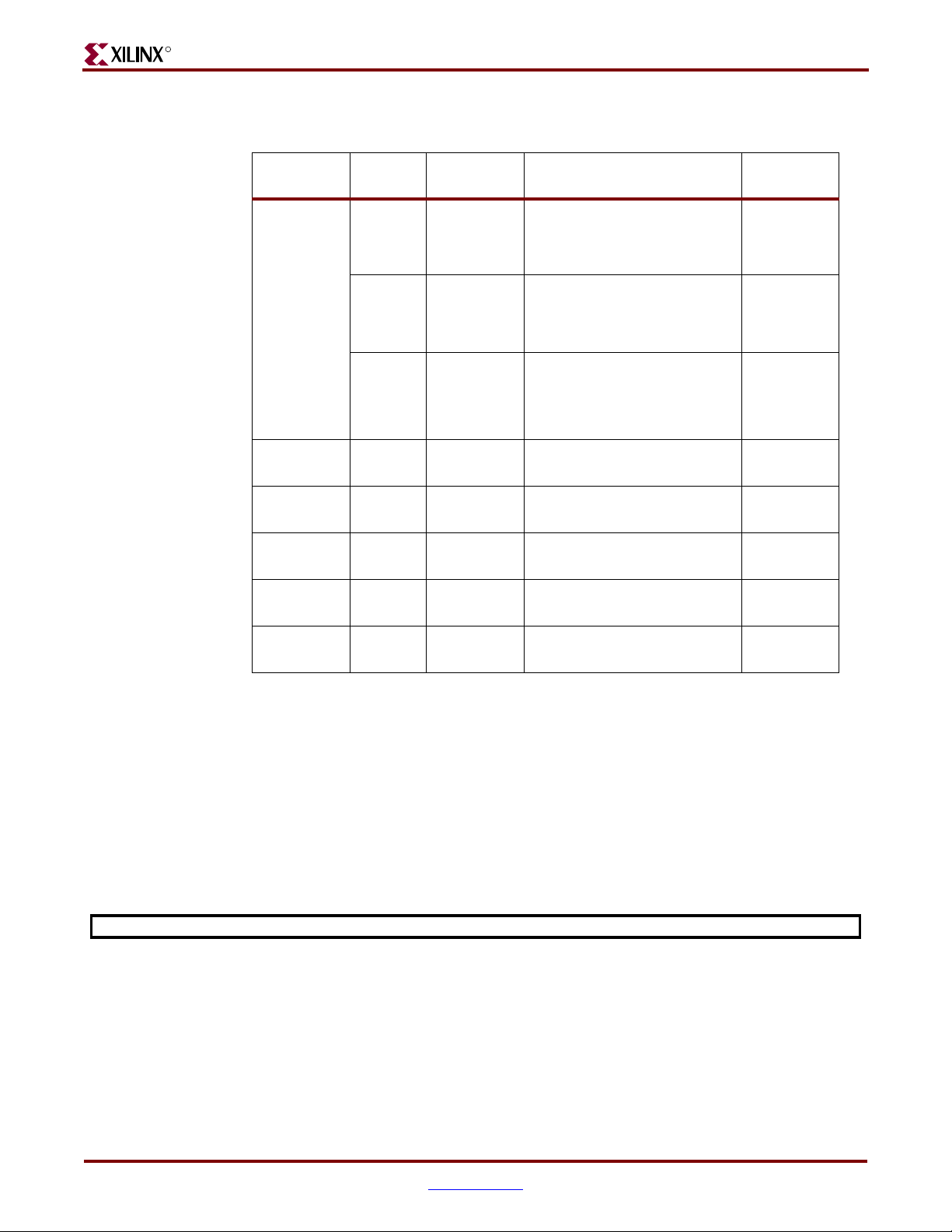

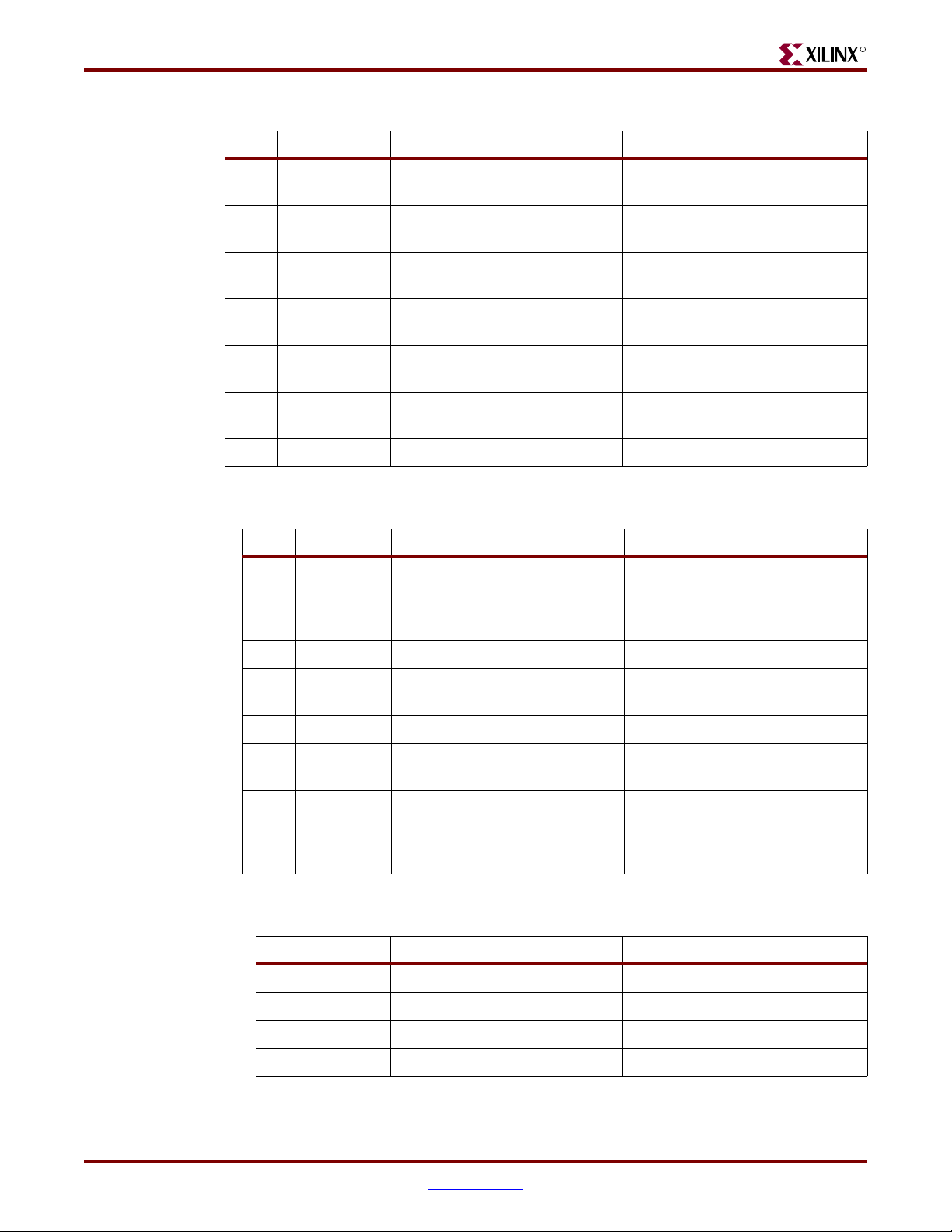

Table 1-1: Configurable Feature Overview by MicroBlaze Version

MicroBlaze Versions

Feature

v2.10a v3.00a v4.00a v5.00a

Version Status deprecated deprecated deprecated active

Processor pipeline depth 3 3 35

On-chip Peripheral Bus (OPB) data side interface option option option option

On-chip Peripheral Bus (OPB) instruction side interface option option option option

Local Memory Bus (LMB) data side interface option option option option

Local Memory Bus (LMB) instruction side interface option option option option

Hardware barrel shifter option option option option

Hardware divider option option option option

Hardware debug logic option option option option

Fast Simplex Link (FSL) interfaces 0-7 0-7 0-7 0-7

Machine status set and clear instructions option option option Yes

Instruction cache over IOPB interface option option option No

Data cache over IOPB interface option option option No

Instruction cache over CacheLink (IXCL) interface - option option option

Data cache over CacheLink (DXCL) interface - option option option

4 or 8-word cache line on XCL - 4 4 option

Hardware exception support - option option option

Pattern compare instructions - - option Yes

Floating point unit (FPU) - - option option

Disable hardware multiplier

1

- - option option

Hardware debug readable ESR and EAR - - Yes Yes

Processor Version Register (PVR) - - - option

1. Used in Virtex-II and subsequent families, for saving MUL18 and DSP48 primitives

12 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 13

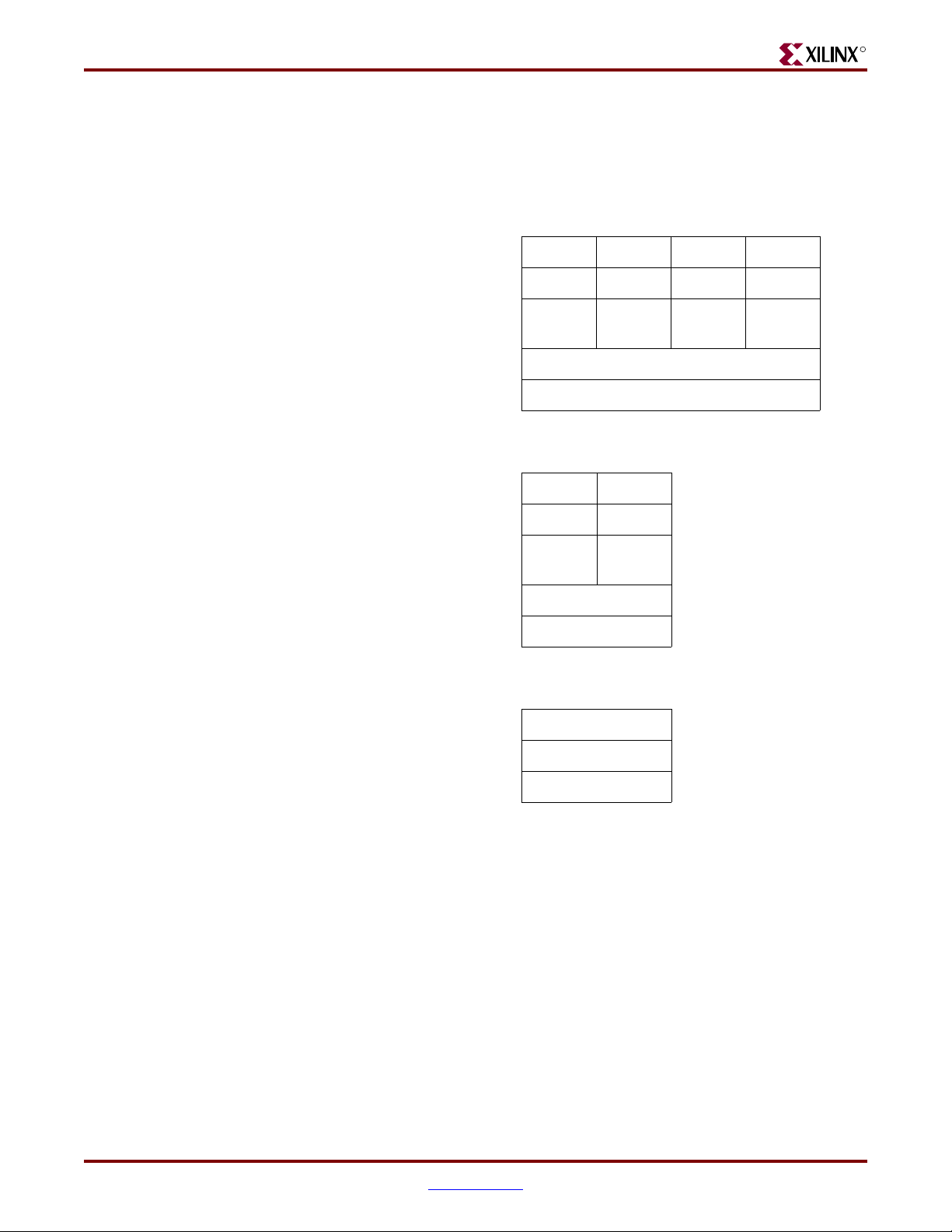

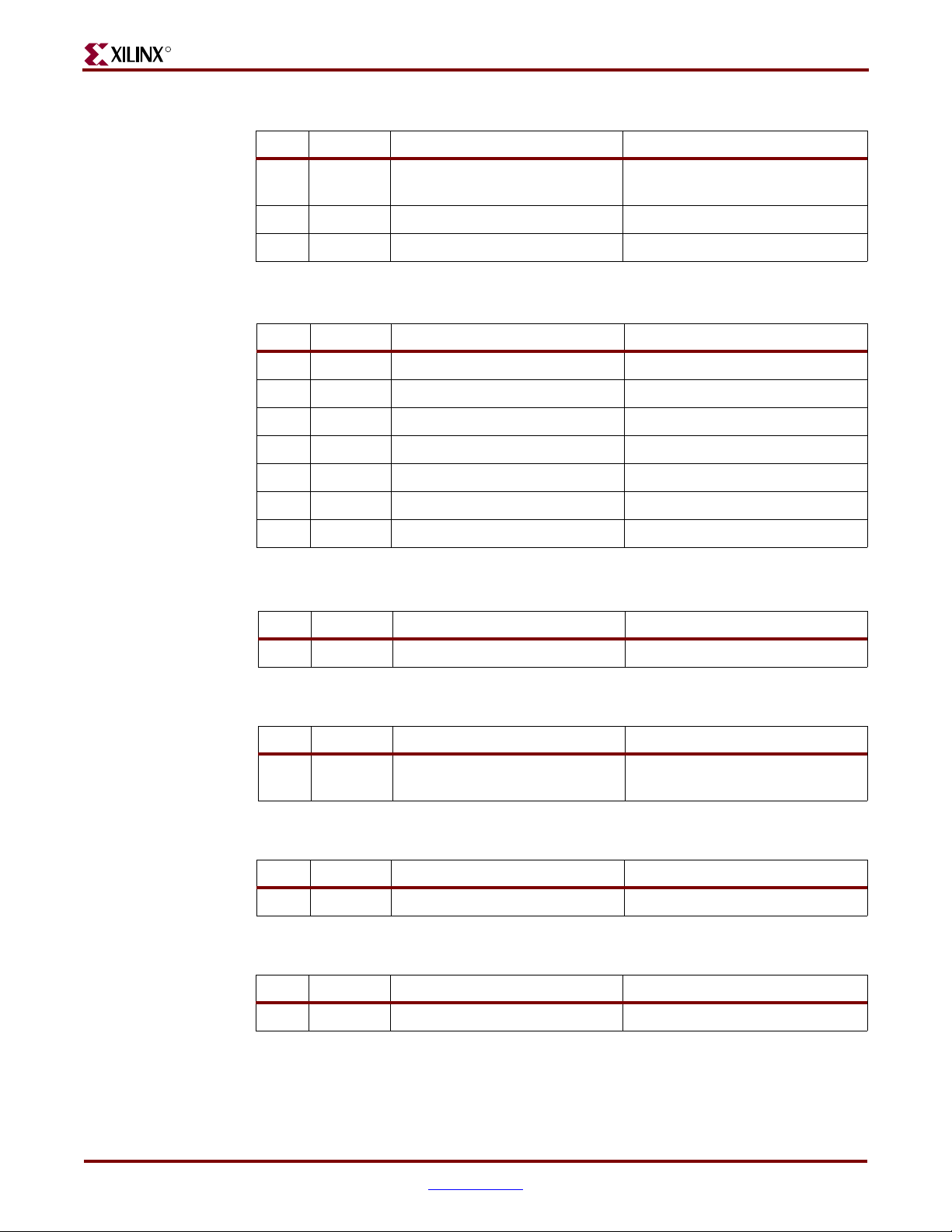

Data Types and Endianness

Data Types and Endianness

MicroBlaze uses Big-Endian, bit-reversed format to represent data. The hardware

supported data types for MicroBlaze are word, half word, and byte. The bit and byte

organization for each type is shown in the following tables.

Table 1-2: Word Data Type

R

Byte address n n+1 n+2 n+3

Byte label 0 1 2 3

Byte

significance

Bit label 0 31

Bit significance MSBit LSBit

Table 1-3: Half Word Data Type

Byte address n n+1

Byte label 0 1

Byte

significance

Bit label 0 15

Bit significance MSBit LSBit

Table 1-4: Byte Data Type

Byte address n

Bit label 0 7

MSByte LSByte

MSByte LSByte

Bit significance MSBit LSBit

Instructions

All MicroBlaze instructions are 32 bits and are defined as either Type A or TypeB. Type A

instructions have up to two source register operands and one destination register operand.

TypeB instructions have one sourceregister and a 16-bit immediate operand (which can be

extended to 32 bits by preceding the Type B instruction with an IMM instruction). Type B

instructions have a single destination register operand. Instructions are provided in the

following functional categories: arithmetic, logical, branch, load/store, and special.

Table 1-6 lists the MicroBlaze instruction set. Refer to Chapter 4, “MicroBlaze Instruction

Set Architecture”, for more information on these instructions. Table 1-5 describes the

instruction set nomenclature used in the semantics of each instruction.

MicroBlaze Processor Reference Guide www.xilinx.com 13

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 14

R

Chapter 1: MicroBlaze Architecture

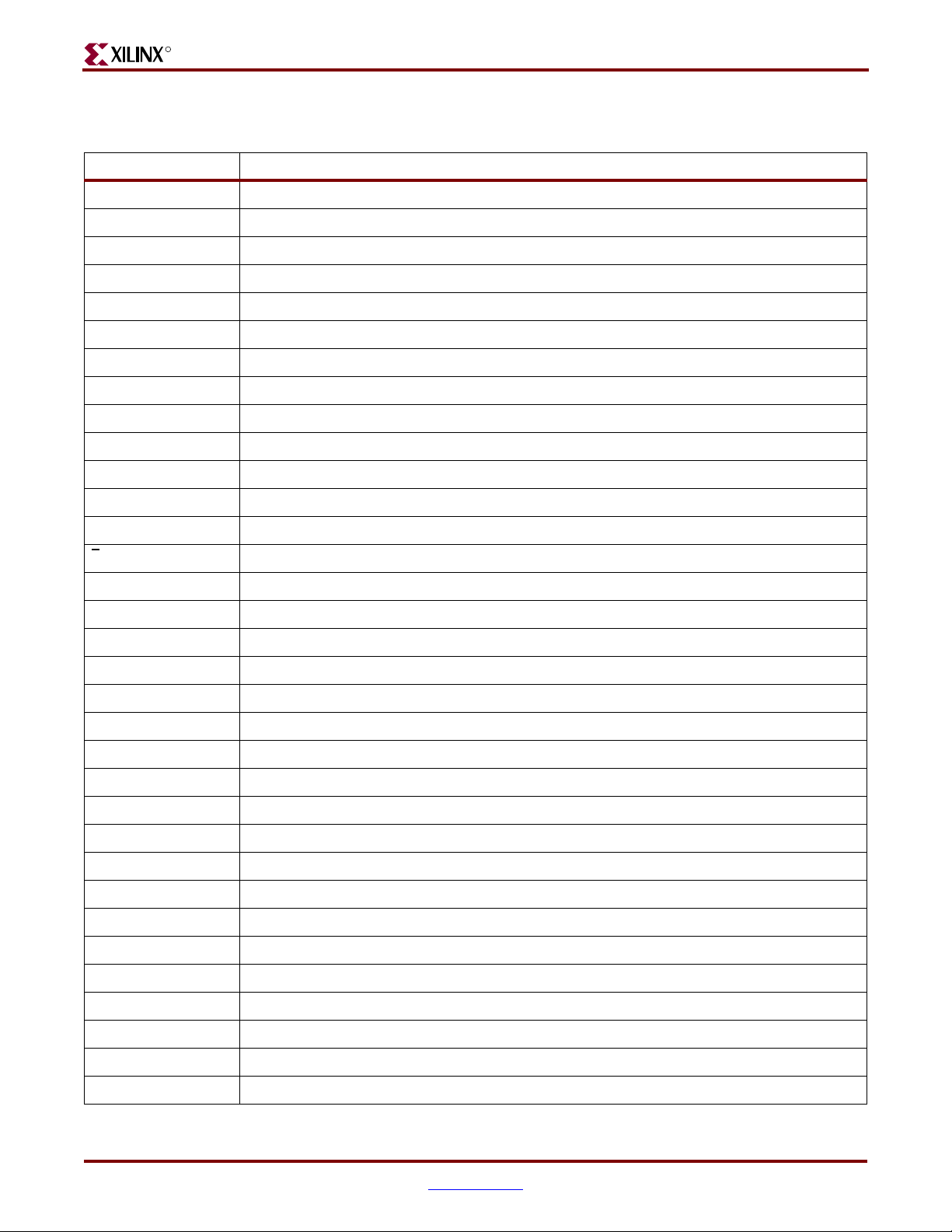

Table 1-5: Instruction Set Nomenclature

Symbol Description

Ra R0 - R31, General Purpose Register, source operand a

Rb R0 - R31, General Purpose Register, source operand b

Rd R0 - R31, General Purpose Register, destination operand

SPR[x] Special Purpose Register number x

MSR Machine Status Register = SPR[1]

ESR Exception Status Register = SPR[5]

EAR Exception Address Register = SPR[3]

FSR Floating Point Unit Status Register = SPR[7]

PVRx Processor Version Register, where x is the register number = SPR[8192 + x]

BTR Branch Target Register = SPR[11]

PC Execute stage Program Counter = SPR[0]

x[y] Bit y of register x

x[y:z] Bit range y to z of register x

x Bit inverted value of register x

Imm 16 bit immediate value

Immxx bit immediate value

FSLx 3 bit Fast Simplex Link (FSL) port designator where x is the port number

C Carry flag, MSR[29]

Sa Special Purpose Register, source operand

Sd Special Purpose Register, destination operand

s(x) Sign extend argument x to 32-bit value

*Addr Memory contents at location Addr (data-size aligned)

:= Assignment operator

= Equality comparison

!= Inequality comparison

> Greater than comparison

>= Greater than or equal comparison

< Less than comparison

<= Less than or equal comparison

+ Arithmetic add

* Arithmetic multiply

/ Arithmetic divide

>> x Bit shift right x bits

14 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 15

Instructions

Table 1-5: Instruction Set Nomenclature

Symbol Description

<< x Bit shift left x bits

and Logic AND

or Logic OR

xor Logic exclusive OR

op1 if cond else op2 Perform op1 if condition cond is true, else perform op2

& Concatenate. E.g. “0000100 & Imm7” is the concatenation of the fixed field “0000100” and

a 7 bit immediate value.

signed Operation performed on signed integer data type. All arithmetic operations are performed

on signed word operands, unless otherwise specified

unsigned Operation performed on unsigned integer data type

float Operation performed on floating point data type

R

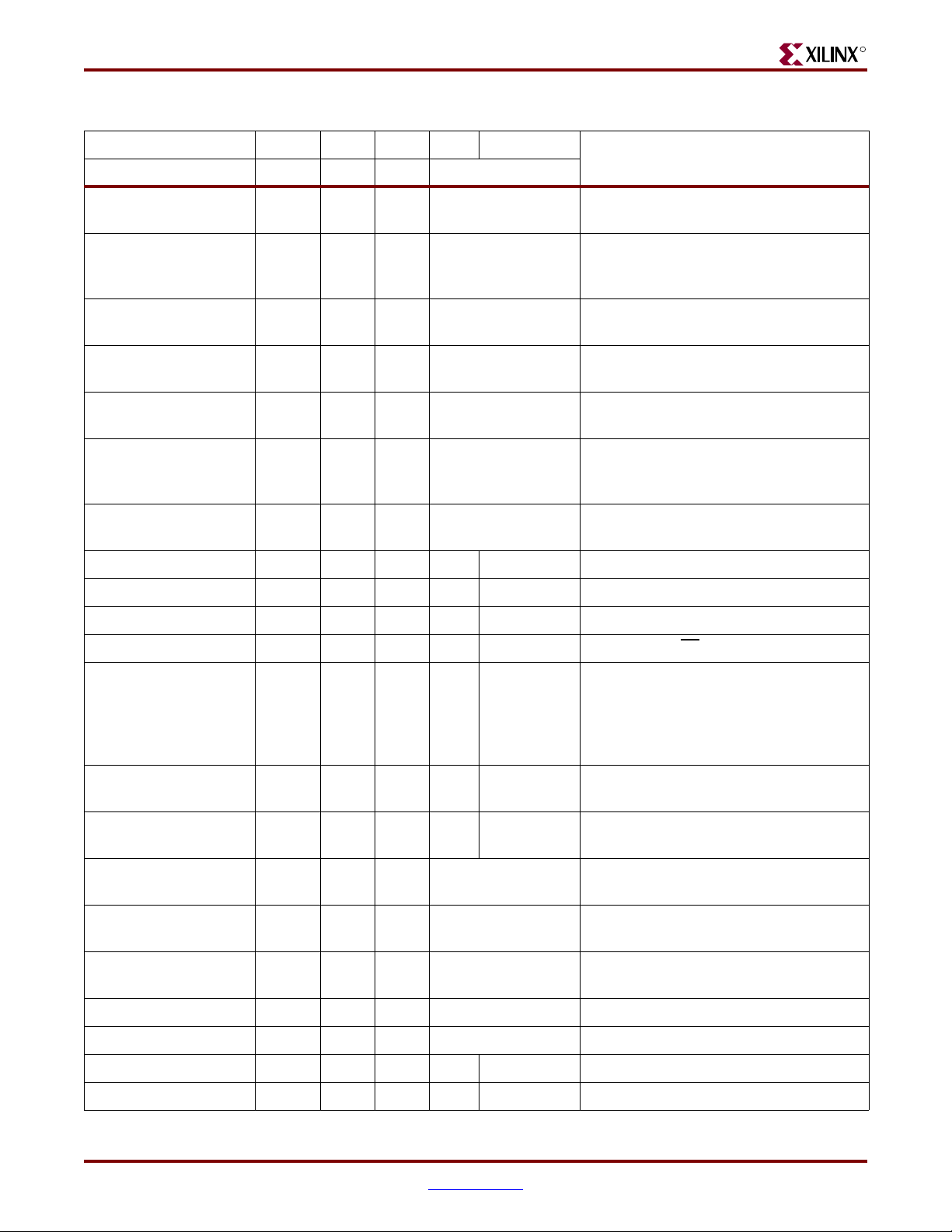

Table 1-6: MicroBlaze Instruction Set Summary

Type A 0-5 6-10 11-15 16-20 21-31

Semantics

Type B 0-5 6-10 11-15 16-31

ADD Rd,Ra,Rb 000000 Rd Ra Rb 00000000000 Rd := Rb + Ra

RSUB Rd,Ra,Rb 000001 Rd Ra Rb 00000000000 Rd := Rb + Ra + 1

ADDC Rd,Ra,Rb 000010 Rd Ra Rb 00000000000 Rd := Rb + Ra + C

RSUBC Rd,Ra,Rb 000011 Rd Ra Rb 00000000000 Rd := Rb + Ra + C

ADDK Rd,Ra,Rb 000100 Rd Ra Rb 00000000000 Rd := Rb + Ra

RSUBK Rd,Ra,Rb 000101 Rd Ra Rb 00000000000 Rd := Rb + Ra + 1

ADDKC Rd,Ra,Rb 000110 Rd Ra Rb 00000000000 Rd := Rb + Ra + C

RSUBKC Rd,Ra,Rb 000111 Rd Ra Rb 00000000000 Rd := Rb + Ra + C

CMP Rd,Ra,Rb 000101 Rd Ra Rb 00000000001 Rd := Rb + Ra + 1

Rd[0] := 0 if (Rb >= Ra) else

Rd[0] := 1

CMPU Rd,Ra,Rb 000101 Rd Ra Rb 00000000011 Rd := Rb + Ra + 1 (unsigned)

Rd[0] := 0 if (Rb >= Ra, unsigned) else

Rd[0] := 1

ADDI Rd,Ra,Imm 001000 Rd Ra Imm Rd := s(Imm) + Ra

RSUBI Rd,Ra,Imm 001001 Rd Ra Imm Rd := s(Imm) + Ra + 1

ADDIC Rd,Ra,Imm 001010 Rd Ra Imm Rd := s(Imm) + Ra + C

RSUBIC Rd,Ra,Imm 001011 Rd Ra Imm Rd := s(Imm) + Ra + C

ADDIK Rd,Ra,Imm 001100 Rd Ra Imm Rd := s(Imm) + Ra

RSUBIK Rd,Ra,Imm 001101 Rd Ra Imm Rd := s(Imm) + Ra + 1

MicroBlaze Processor Reference Guide www.xilinx.com 15

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 16

R

Chapter 1: MicroBlaze Architecture

Table 1-6: MicroBlaze Instruction Set Summary (Continued)

Type A 0-5 6-10 11-15 16-20 21-31

Semantics

Type B 0-5 6-10 11-15 16-31

ADDIKC Rd,Ra,Imm 001110 Rd Ra Imm Rd := s(Imm) + Ra + C

RSUBIKC Rd,Ra,Imm 001111 Rd Ra Imm Rd := s(Imm) +

Ra + C

MUL Rd,Ra,Rb 010000 Rd Ra Rb 00000000000 Rd := Ra * Rb

BSRL Rd,Ra,Rb 010001 Rd Ra Rb 00000000000 Rd : = 0 & (Ra >> Rb)

BSRA Rd,Ra,Rb 010001 Rd Ra Rb 01000000000 Rd := s(Ra >> Rb)

BSLL Rd,Ra,Rb 010001 Rd Ra Rb 10000000000 Rd := (Ra << Rb) & 0

MULI Rd,Ra,Imm 011000 Rd Ra Imm Rd := Ra * s(Imm)

BSRLI Rd,Ra,Imm 011001 Rd Ra 00000000000 &

Rd : = 0 & (Ra >> Imm5)

Imm5

BSRAI Rd,Ra,Imm 011001 Rd Ra 00000010000 &

Rd := s(Ra >> Imm5)

Imm5

BSLLI Rd,Ra,Imm 011001 Rd Ra 00000100000 &

Rd := (Ra << Imm5) & 0

Imm5

IDIV Rd,Ra,Rb 010010 Rd Ra Rb 00000000000 Rd := Rb/Ra

IDIVU Rd,Ra,Rb 010010 Rd Ra Rb 00000000010 Rd := Rb/Ra, unsigned

FADD Rd,Ra,Rb 010110 Rd Ra Rb 00000000000 Rd := Rb+Ra, float

FRSUB Rd,Ra,Rb 010110 Rd Ra Rb 00010000000 Rd := Rb-Ra, float

FMUL Rd,Ra,Rb 010110 Rd Ra Rb 00100000000 Rd := Rb*Ra, float

FDIV Rd,Ra,Rb 010110 Rd Ra Rb 00110000000 Rd := Rb/Ra, float

1

1

1

1

FCMP.UN Rd,Ra,Rb 010110 Rd Ra Rb 01000000000 Rd := 1 if (Rb = NaN or Ra = NaN, float1)

else

Rd := 0

FCMP.LT Rd,Ra,Rb 010110 Rd Ra Rb 01000010000 Rd := 1 if (Rb < Ra, float1) else

Rd := 0

FCMP.EQ Rd,Ra,Rb 010110 Rd Ra Rb 01000100000 Rd := 1 if (Rb = Ra, float1) else

Rd := 0

FCMP.LE Rd,Ra,Rb 010110 Rd Ra Rb 01000110000 Rd := 1 if (Rb <= Ra, float1) else

Rd := 0

FCMP.GT Rd,Ra,Rb 010110 Rd Ra Rb 01001000000 Rd := 1 if (Rb > Ra, float1) else

Rd := 0

FCMP.NE Rd,Ra,Rb 010110 Rd Ra Rb 01001010000 Rd := 1 if (Rb != Ra, float1) else

Rd := 0

FCMP.GE Rd,Ra,Rb 010110 Rd Ra Rb 01001100000 Rd := 1 if (Rb >= Ra, float1) else

Rd := 0

GET Rd,FSLx 011011 Rd 00000 0000000000000 &

FSLx

Rd := FSLx (blocking data read)

MSR[FSL] := 1 if (FSLx_S_Control = 1)

16 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 17

Instructions

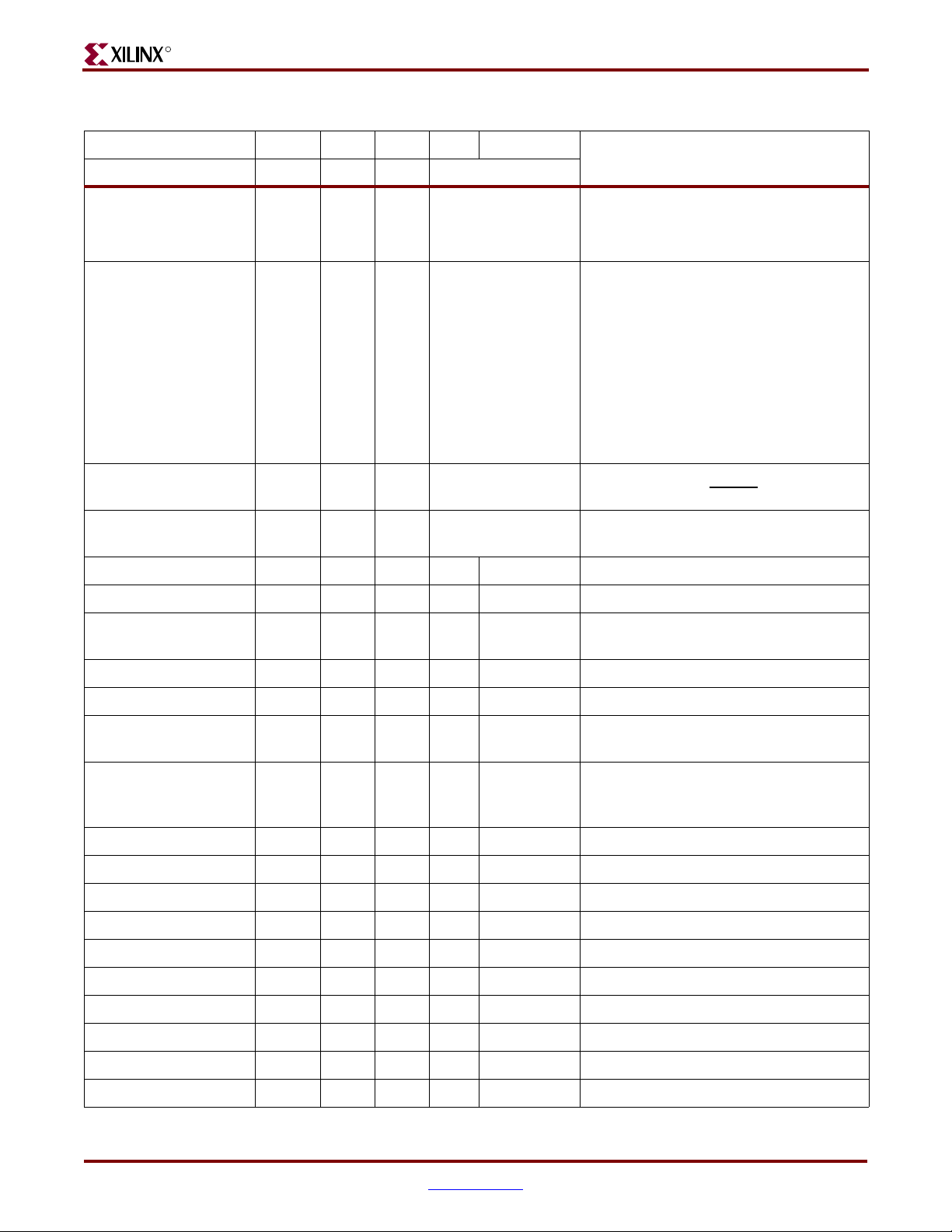

Table 1-6: MicroBlaze Instruction Set Summary (Continued)

Type A 0-5 6-10 11-15 16-20 21-31

Type B 0-5 6-10 11-15 16-31

R

Semantics

PUT Ra,FSLx 011011 00000 Ra 1000000000000 &

FSLx := Ra (blocking data write)

FSLx

NGET Rd,FSLx 011011 Rd 00000 0100000000000 &

FSLx

Rd := FSLx (non-blocking data read)

MSR[FSL] := 1 if (FSLx_S_Control = 1)

MSR[C] := not FSLx_S_Exists

NPUT Ra,FSLx 011011 00000 Ra 1100000000000 &

FSLx

CGET Rd,FSLx 011011 Rd 00000 0010000000000 &

FSLx

CPUT Ra,FSLx 011011 00000 Ra 1010000000000 &

FSLx := Ra (non-blocking data write)

MSR[C] := FSLx_M_Full

Rd := FSLx (blocking control read)

MSR[FSL] := 1 if (FSLx_S_Control = 0)

FSLx := Ra (blocking control write)

FSLx

NCGET Rd,FSLx 011011 Rd 00000 0110000000000 &

FSLx

Rd := FSLx (non-blocking control read)

MSR[FSL] := 1 if (FSLx_S_Control = 0)

MSR[C] := not FSLx_S_Exists

NCPUT Ra,FSLx 011011 00000 Ra 1110000000000 &

FSLx

FSLx := Ra (non-blocking control write)

MSR[C] := FSLx_M_Full

OR Rd,Ra,Rb 100000 Rd Ra Rb 00000000000 Rd := Ra or Rb

AND Rd,Ra,Rb 100001 Rd Ra Rb 00000000000 Rd := Ra and Rb

XOR Rd,Ra,Rb 100010 Rd Ra Rb 00000000000 Rd := Ra xor Rb

ANDN Rd,Ra,Rb 100011 Rd Ra Rb 00000000000 Rd := Ra and

Rb

PCMPBF Rd,Ra,Rb 100000 Rd Ra Rb 10000000000 Rd := 1 if (Rb[0:7] = Ra[0:7]) else

Rd := 2 if (Rb[8:15] = Ra[8:15]) else

Rd := 3 if (Rb[16:23] = Ra[16:23]) else

Rd := 4 if (Rb[24:31] = Ra[24:31]) else

Rd := 0

PCMPEQ Rd,Ra,Rb 100010 Rd Ra Rb 10000000000 Rd := 1 if (Rd = Ra) else

Rd := 0

PCMPNE Rd,Ra,Rb 100011 Rd Ra Rb 10000000000 Rd := 1 if (Rd != Ra) else

Rd := 0

SRA Rd,Ra 100100 Rd Ra 0000000000000001 Rd := s(Ra >> 1)

C := Ra[31]

SRC Rd,Ra 100100 Rd Ra 0000000000100001 Rd := C & (Ra >> 1)

C := Ra[31]

SRL Rd,Ra 100100 Rd Ra 0000000001000001 Rd := 0 & (Ra >> 1)

C := Ra[31]

SEXT8 Rd,Ra 100100 Rd Ra 0000000001100000 Rd := s(Ra[24:31])

SEXT16 Rd,Ra 100100 Rd Ra 0000000001100001 Rd := s(Ra[16:31])

WIC Ra,Rb 100100 00000 Ra Rb 01101000 ICache_Tag := Ra

WDC Ra,Rb 100100 00000 Ra Rb 01100100 DCache_Tag := Ra

MicroBlaze Processor Reference Guide www.xilinx.com 17

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 18

R

Chapter 1: MicroBlaze Architecture

Table 1-6: MicroBlaze Instruction Set Summary (Continued)

Type A 0-5 6-10 11-15 16-20 21-31

Semantics

Type B 0-5 6-10 11-15 16-31

MTS Sd,Ra 100101 00000 Ra 11 & Sd SPR[Sd] := Ra, where:

• SPR[0x0001] is MSR

• SPR[0x0007] is FSR

MFS Rd,Sa 100101 Rd 00000 10 & Sa Rd := SPR[Sa], where:

• SPR[0x0000] is PC

• SPR[0x0001] is MSR

• SPR[0x0003] is EAR

• SPR[0x0005] is ESR

• SPR[0x0007] is FSR

• SPR[0x000B] is BTR

• SPR[0x2000:0x200B] is PVR[0] to

PVR[11]

MSRCLR Rd,Imm 100101 Rd 00001 00 & Imm14 Rd := MSR

MSR := MSR and

Imm14

MSRSET Rd,Imm 100101 Rd 00000 00 & Imm14 Rd := MSR

MSR := MSR or Imm14

BR Rb 100110 00000 00000 Rb 00000000000 PC := PC + Rb

BRD Rb 100110 00000 10000 Rb 00000000000 PC := PC + Rb

BRLD Rd,Rb 100110 Rd 10100 Rb 00000000000 PC := PC + Rb

Rd := PC

BRA Rb 100110 00000 01000 Rb 00000000000 PC := Rb

BRAD Rb 100110 00000 11000 Rb 00000000000 PC := Rb

BRALD Rd,Rb 100110 Rd 11100 Rb 00000000000 PC := Rb

Rd := PC

BRK Rd,Rb 100110 Rd 01100 Rb 00000000000 PC := Rb

Rd := PC

MSR[BIP] := 1

BEQ Ra,Rb 100111 00000 Ra Rb 00000000000 PC := PC + Rb if Ra = 0

BNE Ra,Rb 100111 00001 Ra Rb 00000000000 PC := PC + Rb if Ra != 0

BLT Ra,Rb 100111 00010 Ra Rb 00000000000 PC := PC + Rb if Ra < 0

BLE Ra,Rb 100111 00011 Ra Rb 00000000000 PC := PC + Rb if Ra <= 0

BGT Ra,Rb 100111 00100 Ra Rb 00000000000 PC := PC + Rb if Ra > 0

BGE Ra,Rb 100111 00101 Ra Rb 00000000000 PC := PC + Rb if Ra >= 0

BEQD Ra,Rb 100111 10000 Ra Rb 00000000000 PC := PC + Rb if Ra = 0

BNED Ra,Rb 100111 10001 Ra Rb 00000000000 PC := PC + Rb if Ra != 0

BLTD Ra,Rb 100111 10010 Ra Rb 00000000000 PC := PC + Rb if Ra < 0

BLED Ra,Rb 100111 10011 Ra Rb 00000000000 PC := PC + Rb if Ra <= 0

18 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 19

Instructions

Table 1-6: MicroBlaze Instruction Set Summary (Continued)

Type A 0-5 6-10 11-15 16-20 21-31

Semantics

Type B 0-5 6-10 11-15 16-31

BGTD Ra,Rb 100111 10100 Ra Rb 00000000000 PC := PC + Rb if Ra > 0

BGED Ra,Rb 100111 10101 Ra Rb 00000000000 PC := PC + Rb if Ra >= 0

ORI Rd,Ra,Imm 101000 Rd Ra Imm Rd := Ra or s(Imm)

ANDI Rd,Ra,Imm 101001 Rd Ra Imm Rd := Ra and s(Imm)

XORI Rd,Ra,Imm 101010 Rd Ra Imm Rd := Ra xor s(Imm)

R

ANDNI Rd,Ra,Imm 101011 Rd Ra Imm Rd := Ra and

s(Imm)

IMM Imm 101100 00000 00000 Imm Imm[0:15] := Imm

RTSD Ra,Imm 101101 10000 Ra Imm PC := Ra + s(Imm)

RTID Ra,Imm 101101 10001 Ra Imm PC := Ra + s(Imm)

MSR[IE] := 1

RTBD Ra,Imm 101101 10010 Ra Imm PC := Ra + s(Imm)

MSR[BIP] := 0

RTED Ra,Imm 101101 10100 Ra Imm PC := Ra + s(Imm)

MSR[EE] := 1

MSR[EIP] := 0

ESR := 0

BRI Imm 101110 00000 00000 Imm PC := PC + s(Imm)

BRID Imm 101110 00000 10000 Imm PC := PC + s(Imm)

BRLID Rd,Imm 101110 Rd 10100 Imm PC := PC + s(Imm)

Rd := PC

BRAI Imm 101110 00000 01000 Imm PC := s(Imm)

BRAID Imm 101110 00000 11000 Imm PC := s(Imm)

BRALID Rd,Imm 101110 Rd 11100 Imm PC := s(Imm)

Rd := PC

BRKI Rd,Imm 101110 Rd 01100 Imm PC := s(Imm)

Rd := PC

MSR[BIP] := 1

BEQI Ra,Imm 101111 00000 Ra Imm PC := PC + s(Imm) if Ra = 0

BNEI Ra,Imm 101111 00001 Ra Imm PC := PC + s(Imm) if Ra != 0

BLTI Ra,Imm 101111 00010 Ra Imm PC := PC + s(Imm) if Ra < 0

BLEI Ra,Imm 101111 00011 Ra Imm PC := PC + s(Imm) if Ra <= 0

BGTI Ra,Imm 101111 00100 Ra Imm PC := PC + s(Imm) if Ra > 0

BGEI Ra,Imm 101111 00101 Ra Imm PC := PC + s(Imm) if Ra >= 0

BEQID Ra,Imm 101111 10000 Ra Imm PC := PC + s(Imm) if Ra = 0

BNEID Ra,Imm 101111 10001 Ra Imm PC := PC + s(Imm) if Ra != 0

BLTID Ra,Imm 101111 10010 Ra Imm PC := PC + s(Imm) if Ra < 0

MicroBlaze Processor Reference Guide www.xilinx.com 19

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 20

R

Chapter 1: MicroBlaze Architecture

Table 1-6: MicroBlaze Instruction Set Summary (Continued)

Type A 0-5 6-10 11-15 16-20 21-31

Semantics

Type B 0-5 6-10 11-15 16-31

BLEID Ra,Imm 101111 10011 Ra Imm PC := PC + s(Imm) if Ra <= 0

BGTID Ra,Imm 101111 10100 Ra Imm PC := PC + s(Imm) if Ra > 0

BGEID Ra,Imm 101111 10101 Ra Imm PC := PC + s(Imm) if Ra >= 0

LBU Rd,Ra,Rb 110000 Rd Ra Rb 00000000000 Addr := Ra + Rb

Rd[0:23] := 0

Rd[24:31] := *Addr[0:7]

LHU Rd,Ra,Rb 110001 Rd Ra Rb 00000000000 Addr := Ra + Rb

Rd[0:15] := 0

Rd[16:31] := *Addr[0:15]

LW Rd,Ra,Rb 110010 Rd Ra Rb 00000000000 Addr := Ra + Rb

Rd := *Addr

SB Rd,Ra,Rb 110100 Rd Ra Rb 00000000000 Addr := Ra + Rb

*Addr[0:8] := Rd[24:31]

SH Rd,Ra,Rb 110101 Rd Ra Rb 00000000000 Addr := Ra + Rb

*Addr[0:16] := Rd[16:31]

SW Rd,Ra,Rb 110110 Rd Ra Rb 00000000000 Addr := Ra + Rb

*Addr := Rd

LBUI Rd,Ra,Imm 111000 Rd Ra Imm Addr := Ra + s(Imm)

Rd[0:23] := 0

Rd[24:31] := *Addr[0:7]

LHUI Rd,Ra,Imm 111001 Rd Ra Imm Addr := Ra + s(Imm)

Rd[0:15] := 0

Rd[16:31] := *Addr[0:15]

LWI Rd,Ra,Imm 111010 Rd Ra Imm Addr := Ra + s(Imm)

Rd := *Addr

SBI Rd,Ra,Imm 111100 Rd Ra Imm Addr := Ra + s(Imm)

*Addr[0:7] := Rd[24:31]

SHI Rd,Ra,Imm 111101 Rd Ra Imm Addr := Ra + s(Imm)

*Addr[0:15] := Rd[16:31]

SWI Rd,Ra,Imm 111110 Rd Ra Imm Addr := Ra + s(Imm)

*Addr := Rd

1. Due to the many differentcorner cases involved in floating point arithmetic, only the normal behavior is described. A full description

of the behavior can be found in: Chapter 4, “MicroBlaze Instruction Set Architecture,”

Registers

MicroBlaze has an orthogonal instruction set architecture. It has thirty-two 32-bit general

purpose registers and up to seven 32-bit special purpose registers, depending on

configured options.

20 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 21

Registers

General Purpose Registers

The thirty-two 32-bit General Purpose Registers are numbered R0 through R31. The

register file is reset on bit stream download (reset value is 0x00000000).

Note: The register file is not reset by the external reset inputs: reset and debug_rst.

0 31

↑

R0-R31

Figure 1-2: R0-R31

Table 1-7: General Purpose Registers (R0-R31)

Bits Name Description Reset Value

R

0:31 R0 R0 is defined to always have thevalue

0x00000000

of zero. Anything written to R0 is

discarded.

0:31 R1 through R13 R1 through R13 are 32-bit general

-

purpose registers

0:31 R14 32-bit used to store return addresses

-

for interrupts

0:31 R15 32-bit general purpose register 0:31 R16 32-bit used to store return addresses

-

for breaks

0:31 R17

0:31 R18 through R31 R18 through R31 are 32-bit general

If MicroBlaze is configured to support

hardware exceptions, this register is

loaded with HW exception return

address (see also “Branch Target

Register (BTR)”); if not it is a general

purpose register

-

-

purpose registers.

Please refer to Table 3-2 for software conventions on general purpose register usage.

Special Purpose Registers

Program Counter (PC)

The Program Counter is the 32-bit address of the execution instruction. It can be read with

an MFS instruction, but it can not be written to using an MTS instruction. When used with

the MFS instruction the PC register is specified by setting Sa = 0x0000.

MicroBlaze Processor Reference Guide www.xilinx.com 21

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 22

R

0 31

Chapter 1: MicroBlaze Architecture

↑

PC

Figure 1-3: PC

Table 1-8: Program Counter (PC)

Bits Name Description Reset Value

0:31 PC

Program Counter

0x00000000

Address of executing instruction,

i.e. “mfs r2 0” will store the address

of the mfs instruction itself in R2

Machine Status Register (MSR)

The Machine Status Register contains control and status bits for the processor. It can be

read with an MFS instruction. When reading the MSR, bit 29 is replicated in bit 0 as the

carry copy. MSR can be written using either an MTS instruction or the dedicated MSRSET

and MSRCLR instructions.

When writing to the MSR, some of the bits will takes effect immediately (e.g Carry) and the

remaining bits take effect one clock cycle later. Any value written to bit 0 is discarded.

When used with an MTS or MFS instruction the MSR is specified by setting Sx = 0x0001.

0 21 22 23 24 25 26 27 28 29 30 31

↑ ↑ ↑↑↑↑ ↑↑↑↑↑↑↑

CC RESERVED PVR EIP EE DCE DZ ICE FSL BIP C IE BE

Figure 1-4: MSR

Table 1-9: Machine Status Register (MSR)

Bits Name Description Reset Value

0CC

Arithmetic Carry Copy

0

Copy of the Arithmetic Carry (bit 29).

CC is always the same as bit C.

1:20 Reserved

21 PVR

22 www.xilinx.com MicroBlaze Processor Reference Guide

Processor Version Register exists

0 No Processor Version Register

1 Processor Version Register exists

Read only

1-800-255-7778 UG081 (v6.0) June 1, 2006

Based on

option

C_PVR

Page 23

Registers

R

Table 1-9: Machine Status Register (MSR) (Continued)

Bits Name Description Reset Value

22 EIP

23 EE

24 DCE

25 DZ

26 ICE

Exception In Progress

0 No hardware exception in progress

1 Hardware exception in progress

Read/Write

Exception Enable

0 Hardware exceptions disabled

1 Hardware exceptions enabled

Read/Write

Data Cache Enable

0 Data Cache is Disabled

1 Data Cache is Enabled

Read/Write

Division by Zero

1

0 No division by zero has occurred

1 Division by zero has occurred

Read/Write

Instruction Cache Enable

0 Instruction Cache is Disabled

1 Instruction Cache is Enabled

Read/Write

0

0

0

0

0

27 FSL

28 BIP

FSL Error

0 FSL get/put had no error

1 FSL get/put had mismatch in

control type

Read/Write

Break in Progress

0 No Break in Progress

1 Break in Progress

Source of break can be software break

instruction or hardware break from

Ext_Brk or Ext_NM_Brk pin.

Read/Write

0

0

MicroBlaze Processor Reference Guide www.xilinx.com 23

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 24

R

Chapter 1: MicroBlaze Architecture

Table 1-9: Machine Status Register (MSR) (Continued)

Bits Name Description Reset Value

29 C

Arithmetic Carry

0

0 No Carry (Borrow)

1 Carry (No Borrow)

Read/Write

30 IE

Interrupt Enable

0

0 Interrupts disabled

1 Interrupts enabled

Read/Write

31 BE

Buslock Enable

2

0

0 Buslock disabled on data-side OPB

1 Buslock enabled on data-side OPB

Buslock Enable does not affect

operation of IXCL, DXCL, ILMB,

DLMB, or IOPB.

Read/Write

1. This bit is only used for integer divide-by-zero signaling. There is a floating point equivalent

in the FSR. The DZ-bit will flag divide by zero conditions regardless if the processor is

configured with exception handling or not.

2. For a details on the OPB protocol, please refer to the IBM CoreConnect specification: 64-Bit

On-Chip Peripheral Bus, Architectural Specifications, Version 2.0.

Exception Address Register (EAR)

The Exception Address Register stores the full load/store address that caused the

exception. For an unaligned access exception that means the unaligned access address,and

for an DOPB exception, the failing OPB data access address. The contents of this register is

undefined for all other exceptions. When read with the MFS instruction the EAR is

specified by setting Sa = 0x0003.

0 31

↑

EAR

Figure 1-5: EAR

Table 1-10: Exception Address Register (EAR)

Bits Name Description Reset Value

0:31 EAR Exception Address Register 0x00000000

24 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 25

Registers

Exception Status Register (ESR)

The Exception Status Register contains status bits for the processor. When read with the

MFS instruction the ESR is specified by setting Sa = 0x0005.

19 20 26 27 31

↑↑↑↑

RESERVED

Figure 1-6: ESR

Table 1-11: Exception Status Register (ESR)

Bits Name Description Reset Value

0:18 Reserved

DS

ESS EC

R

19 DS

20:26 ESS

27:31 EC

Exception in delay slot.

0 not caused by delay slot instruction

1 caused by delay slot instruction

Read-only

Exception Specific Status

For details refer to Table 1-12.

Read-only

Exception Cause

00001 = Unaligned data access exception

00010 = Illegal op-code exception

00011 = Instruction bus error exception

00100 = Data bus error exception

00101 = Divide by zero exception

00110 = Floating point unit exception

Read-only

0

See Table 1-12

0

MicroBlaze Processor Reference Guide www.xilinx.com 25

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 26

R

Chapter 1: MicroBlaze Architecture

Table 1-12: Exception Specific Status (ESS)

Exception

Cause

Bits Name Description Reset Value

Unaligned

Data Access

Illegal

Instruction

Instruction

bus error

Data bus

error

Divide by

zero

Floating

point unit

20 W

Word Access Exception

0 unaligned halfword access

1 unaligned word access

21 S Store Access Exception

0 unaligned load access

1 unaligned store access

22:26 Rx

Source/Destination Register

General purpose register used

as source (Store) or destination

(Load) in unaligned access

20:26 Reserved 0

20:26 Reserved 0

20:26 Reserved 0

20:26 Reserved 0

20:26 Reserved 0

0

0

0

Branch Target Register (BTR)

The Branch Target Register only exists if the MicroBlaze processor is configured to use

exceptions. The register stores the branch target address for all delay slot branch

instructions executed while MSR[EIP] = 0. If an exception is caused by an instruction in a

delay slot (i.e. ESR[DS]=1) then the exception handler should return execution to the

address stored in BTR instead of the normal exception return address stored in r17. When

read with the MFS instruction the BTR is specified by setting Sa = 0x000B.

0 31

↑

BTR

Figure 1-7: BTR

26 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 27

Registers

R

Table 1-13: Branch Target Register (BTR)

Bits Name Description Reset Value

0:31 BTR Branch target address used by handler

0x00000000

when returning from an exception

caused by an instruction in a delay slot

Read-only

Floating Point Status Register (FSR)

The Floating Point Status Register contains status bits for the floating point unit. It can be

read with an MFS, and written with an MTS instruction. When read or written, the register

is specified by setting Sa = 0x0007.

27 28 29 30 31

↑ ↑↑↑↑↑

RESERVED IO DZ OF UF DO

Figure 1-8: FSR

Table 1-14: Floating Point Status Register (FSR)

Bits Name Description Reset Value

0:26 Reserved undefined

27 IO

28 DZ

29 OF

30 UF

31 DO

Invalid operation

Divide-by-zero

Overflow

Underflow

Denormalized operand error

0

0

0

0

0

Processor Version Register (PVR)

The Processor Version Register is controlled by the C_PVR configuration option on

MicroBlaze. When C_PVR is set to 0 the processor does not implement any PVR and

MSR[PVR]=0. If C_PVR is set to 1 then MicroBlaze implements only the first register:

PVR0, and if set to 2 all 12 PVR registers (PVR0 to PVR11) are implemented.

When read with the MFS instruction the PVR is specified by setting Sa = 0x200x, with x

being the register number between 0x0 and 0xB.

MicroBlaze Processor Reference Guide www.xilinx.com 27

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 28

R

Chapter 1: MicroBlaze Architecture

Table 1-15: Processor Version Register 0 (PVR0)

Bits Name Description Value

0 CFG PVR implementation: 0=basic,

Based on C_PVR

1=full

1 BS Use barrel shifter C_USE_BARREL

2 DIV Use divider C_USE_DIV

3 MUL Use hardware multiplier C_USE_HW_MUL

4 FPU Use FPU C_USE_FPU

5 EXC Use any type of exceptions Based on C_*_EXCEPTION

6 ICU Use instruction cache C_USE_ICACHE

7 DCU Use data cache C_USE_DCACHE

8:15 Reserved 0

16:23 MBV MicroBlaze release version code

Release Specific

0x1 = v5.00.a

24:31 USR1 User configured value 1 C_PVR_USER1

Table 1-16: Processor Version Register 1 (PVR1)

Bits Name Description Value

0:31 USR2 User configured value 2 C_PVR_USER2

Table 1-17: Processor Version Register 2 (PVR2)

Bits Name Description Value

0 DOPB Data side OPB in use C_D_OPB

1 DLMB Data side LMB in use C_D_LMB

2 IOPB Instruction side OPB in use C_I_OPB

3 IOPB Instruction side OPB in use C_I_LMB

4 IRQEDGE Interrupt is edge triggered C_INTERRUPT_IS_EDGE

5 IRQPOS Interrupt edge is positive C_EDGE_IS_POSITIVE

6:16 Reserved

17 BS Use barrel shifter C_USE_BARREL

18 DIV Use divider C_USE_DIV

19 MUL Use hardware multiplier C_USE_HW_MUL

20 FPU Use FPU C_USE_FPU

21:24 Reserved

28 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 29

Registers

Table 1-17: Processor Version Register 2 (PVR2) (Continued)

Bits Name Description Value

R

25 OP0EXEC Generate exception for 0x0

illegal opcode

26 UNEXEC Generate exception for

unaligned data access

27 OPEXEC Generate exception for any

illegal opcode

28 IOPBEXEC Generate exception for IOPB

error

29 DOPBEXEC Generate exception for DOPB

error

30 DIVEXEC Generate exception for division

by zero

31 FPUEXEC Generate exceptions from FPU C_FPU_EXCEPTION

Table 1-18: Processor Version Register 3 (PVR3)

Bits Name Description Value

0 DEBUG Use debug logic C_DEBUG_ENABLED

1:2 Reserved

C_OPCODE_0x0_ILLEGAL

C_UNALIGNED_EXCEPTION

C_ILL_OPCODE_EXCEPTION

C_IOPB_BUS_EXCEPTION

C_DOPB_BUS_EXCEPTION

C_DIV_ZERO_EXCEPTION

3:6 PCBRK Number of PC breakpoints C_NUMBER_OF_PC_BRK

7:9 Reserved

10:12 RDADDR Number of read address

breakpoints

C_NUMBER_OF_RD_ADDR_B

RK

13:15 Reserved

16:18 WRADDR Number of write address

breakpoints

C_NUMBER_OF_WR_ADDR_B

RK

19:21 Reserved

22:24 FSL Number of FSLs C_FSL_LINKS

25:31 Reserved

Table 1-19: Processor Version Register 4 (PVR4)

Bits Name Description Value

0 ICU Use instruction cache C_USE_ICACHE

1:5 ICTS Instruction cache tag size C_ADDR_TAG_BITS

6 Reserved 1

7 ICW Allow instruction cache write C_ALLOW_ICACHE_WR

MicroBlaze Processor Reference Guide www.xilinx.com 29

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 30

R

Chapter 1: MicroBlaze Architecture

Table 1-19: Processor Version Register 4 (PVR4) (Continued)

Bits Name Description Value

8:10 ICLL Instruction cache line length

C_ICACHE_LINE_LEN

2^n

11:15 ICBS Instruction cache byte size 2^n C_CACHE_BYTE_SIZE

16:31 Reserved 0

Table 1-20: Processor Version Register 5 (PVR5)

Bits Name Description Value

0 DCU Use data cache C_USE_DCACHE

1:5 DCTS Data cache tag size C_DCACHE_ADDR_TAG

6 Reserved 1

7 DCW Allow data cache write C_ALLOW_DCACHE_WR

8:10 DCLL Data cache line length 2^n C_DCACHE_LINE_LEN

11:15 DCBS Data cache byte size 2^n C_DCACHE_BYTE_SIZE

16:31 Reserved 0

Table 1-21: Processor Version Register 6 (PVR6)

Bits Name Description Value

0:31 ICBA InstructionCache Base Address C_ICACHE_BASEADDR

Table 1-22: Processor Version Register 7 (PVR7)

Bits Name Description Value

0:31 ICHA Instruction Cache High

C_ICACHE_HIGHADDR

Address

Table 1-23: Processor Version Register 8 (PVR8)

Bits Name Description Value

0:31 DCBA Data Cache Base Address C_DCACHE_BASEADDR

Table 1-24: Processor Version Register 9 (PVR9)

Bits Name Description Value

0:31 DCHA Data Cache High Address C_DCACHE_HIGHADDR

30 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 31

Pipeline Architecture

R

Table 1-25: Processor Version Register 10 (PVR10)

Bits Name Description Value

0:7 ARCH Target architecture:

8:31 Reserved 0

Table 1-26: Processor Version Register 11 (PVR11)

Bits Name Description Value

0:20 DO Reset value for MSR 0

21:31 RSTMSR Reset value for MSR C_RESET_MSR

Pipeline Architecture

MicroBlaze instruction execution is pipelined. The pipeline is divided into five stages:

Fetch (IF), Decode (OF), Execute (EX), Access Memory (MEM), and Writeback (WB).

Defined by option C_TARGET

0x4 = Virtex2

0x5 = Virtex2Pro

0x6 = Spartan3

0x7 = Virtex4

0x8 = Virtex5

0x9 = Spartan3E

For most instructions, each stage takes one clock cycle to complete. Consequently, it takes

five clock cycles for a specific instruction to complete, and one instruction is completed on

every cycle. A few instructions require multiple clock cycles in the execute stage to

complete. This is achieved by stalling the pipeline.

cycle1cycle2cycle3cycle4cycle5cycle6cycle7cycle8cycle

9

instruction 1 IF OF EX MEM WB

instruction 2 IF OF EX MEM MEM MEM WB

instruction 3 IF OF EX Stall Stall MEM WB

When executing from slower memory, instruction fetches may take multiple cycles. This

additional latency will directly affect the efficiency of the pipeline. MicroBlaze implements

an instruction prefetch buffer that reduces the impact of such multi-cycle instruction

memory latency. While the pipeline is stalled by a multi-cycle instruction in the execution

stage the prefetch buffer continues to load sequential instructions. Once the pipeline

resumes execution the fetch stage can load new instructions directly from the prefetch

buffer rather than having to wait for the instruction memory access to complete.

MicroBlaze Processor Reference Guide www.xilinx.com 31

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 32

R

Branches

Delay Slots

Chapter 1: MicroBlaze Architecture

Normally the instructions in the fetch and decode stages (as well as prefetch buffer) are

flushed when executing a taken branch. The fetch pipeline stage is then reloaded with a

new instruction from the calculated branch address. A taken branch in MicroBlaze takes

three clock cycles to execute, two of which are required for refilling the pipeline. To reduce

this latency overhead, MicroBlaze supports branches with delay slots.

When executing a taken branch with delay slot, only the fetch pipeline stage in MicroBlaze

is flushed. The instruction in the decode stage (branch delay slot) is allowed to complete.

This technique effectively reduces the branch penalty from two clock cycles to one. Branch

instructions with delay slots have a D appended to the instruction mnemonic. For

example, the BNE instruction will not execute the subsequent instruction (does not have a

delay slot), whereas BNED will execute the next instruction before control is transferred to

the branch location.

A delay slot must not contain the following instructions: IMM, branch, or break. Interrupts

and external hardware breaks are deferred until after the delay slot branch has been

completed.

Instructions that could cause recoverable exceptions (e.g. unaligned word or halfword

load and store) are allowed in the delay slot. If an exception is caused in a delay slot the

ESR[DS] bit will be set, and the exception handler is responsible for returning the

execution to the branch target (stored in the special purpose register BTR) rather than the

sequential return address stored in R17.

Memory Architecture

MicroBlaze is implemented with a Harvard memory architecture, i.e. instruction and data

accesses are done in separate address spaces. Each address space has a 32 bit range (i.e.

handles up to 4 GByte of instructions and data memory respectively). The instruction and

data memory ranges can be made to overlap by mapping them both to the same physical

memory. The latter is useful e.g. for software debugging.

Both instruction and data interfaces of MicroBlaze are 32 bit wide and use big endian, bitreversed format. MicroBlaze supports word, halfword, and byte accesses to data memory.

Data accesses must be aligned (i.e. word accesses must be on word boundaries, halfword

on halfword bounders), unless the processor is configured to support unaligned

exceptions. All instruction accesses must be word aligned.

MicroBlaze does not separate between data accesses to I/O and memory (i.e. it uses

memory mapped I/O). The processor has up to three interfaces for memory accesses: Local

Memory Bus (LMB), On-Chip Peripheral Bus (OPB), and Xilinx CacheLink (XCL). The

LMB memory address range must not overlap with OPB or XCL ranges.

MicroBlaze has a single cycle latency for accesses to local memory (LMB) and for cache

read hits. A data cache write normally has two cycles of latency (more if the posted-write

buffer in the memory controller is full).

For details on the different memory interfaces please refer to Chapter 2, “MicroBlaze

Signal Interface Description”.

32 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 33

Reset, Interrupts, Exceptions, and Break

Reset, Interrupts, Exceptions, and Break

MicroBlaze supports reset, interrupt, user exception, break, and hardware exceptions. The

following section describes the execution flow associated with each of these events.

The relative priority starting with the highest is:

1. Reset

2. Hardware Exception

3. Non-maskable Break

4. Break

5. Interrupt

6. User Vector (Exception)

Table 1-27 defines the memory address locations of the associated vectors and the

hardware enforced register file locations for return address. Each vector allocates two

addresses to allow full address range branching (requires an IMM followed by a BRAI

instruction). The address range 0x28 to 0x4F is reserved for future software support by

Xilinx. Allocating these addresses for user applications is likely to conflict with future

releases of EDK support software.

R

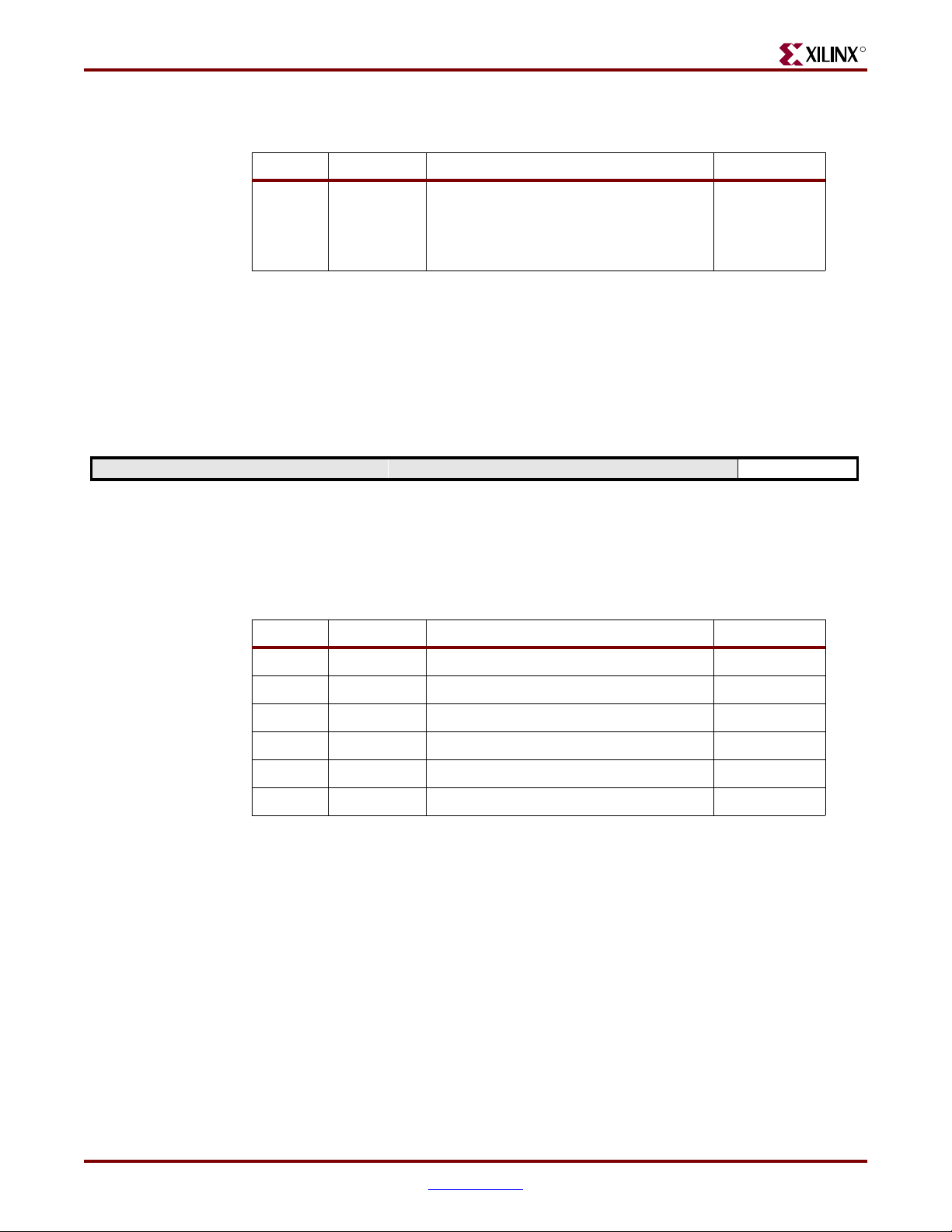

Table 1-27: Vectors and Return Address Register File Location

Register File

Event Vector Address

Reset 0x00000000 -

0x00000004

User Vector (Exception) 0x00000008 -

0x0000000C

Interrupt 0x00000010 -

0x00000014

Return Address

-

-

R14

Break: Non-maskable

hardware

Break: Hardware

0x00000018 -

0x0000001C

R16

Break: Software

Hardware Exception 0x00000020 -

0x00000024

Reserved by Xilinx for

future use

0x00000028 -

0x0000004F

R17 or BTR

-

MicroBlaze Processor Reference Guide www.xilinx.com 33

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 34

R

Reset

Chapter 1: MicroBlaze Architecture

When a Reset or Debug_Rst

instructions from the reset vector (address 0x0). Both external reset signals are active high, and

should be asserted for a minimum of 16 cycles.

Equivalent Pseudocode

PC ← 0x00000000

MSR

← C_RESET_MSR (see “MicroBlaze Core Configurability” in Chapter 2)

EAR

← 0

ESR

← 0

FSR

← 0

Hardware Exceptions

MicroBlaze can be configured to trap the following internal error conditions: illegal

instruction, instruction and data bus error, and unaligned access. The divide by zero

exception can only be enabled if the processor is configured with a hardware divider

(C_USE_DIV=1). When configured with a hardwarefloating point unit (C_USE_FPU=1), it

can also trap the following floating point specific exceptions: underflow, overflow, float

division-by-zero, invalid operation, and denormalized operand error.

A hardware exception will cause MicroBlaze to flush the pipeline and branch to the

hardware exception vector (address 0x20). The exception will also load the decode stage

program counter value into the general purpose register R17. The execution stage

instruction in the exception cycle is not executed. If the exception is caused by an

instruction in a branch delay slot, then the ESR[DS] bit will be set. In this case the exception

handler should resume execution from the branch target address, stored in BTR.

(1)

occurs, MicroBlaze will flush the pipeline and start fetching

The EE and EIP bits in MSR are automatically reverted when executing the RTED

instruction.

Exception Causes

• Instruction Bus Exception

The instruction On-chip Peripheral Bus exception is caused by an active error signal

from the slave (IOPB_errAck) or timeout signal from the arbiter (IOPB_timeout). The

instructions side local memory (ILMB) and CacheLink (IXCL) interfaces can not cause

instruction bus exceptions.

• Illegal Opcode Exception

The illegal opcode exception is caused by an instruction with an invalid major opcode

(bits 0 through 5 of instruction). Bits 6 through 31 of the instruction are not checked.

Optional processor instructions are detected as illegal if not enabled.

• Data Bus Exception

The data On-chip Peripheral Bus exception is caused by an active error signal from the

slave (DOPB_errAck) or timeout signal from the arbiter (DOPB_timeout). The data

side local memory (DLMB) and CacheLink (DXCL) interfaces can not cause data bus

exceptions.

1. Reset input controlled by the XMD debugger via MDM

34 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 35

Reset, Interrupts, Exceptions, and Break

• Unaligned Exception

The unaligned exception is caused by a word access where the address to the data bus

has bits 30 or 31 set, or a half-word access with bit 31 set.

• Divide by Zero Exception

The divide-by-zero exception is causes by an integer division (idiv or idivu) where the

divisor is zero.

• FPU Exception

An FPU exception is caused by an underflow, overflow, divide-by-zero, illegal

operation, or denormalized operand occurring with a floating point instruction.

♦ Underflow occurs when the result is denormalized.

♦ Overflow occurs when the result is not-a-number (NaN).

♦ The divide-by-zero FPU exception is caused by the rA operand to fdiv being zero

when rB is not infinite.

♦ Illegal operation is caused by a signaling NaN operand or by illegal infinite or

zero operand combinations.

Equivalent Pseudocode

R

Breaks

Hardware Breaks

r17 ← PC

PC

← 0x00000020

MSR[EE]

MSR[EIP]

ESR[DS]

ESR[EC]

ESR[ESS]

EAR

FSR

← 0

← 1

← exception in delay slot

← exception specific value

← exception specific value

← exception specific value

← exception specific value

There are two kinds of breaks:

• Hardware (external) breaks

• Software (internal) breaks

Hardware breaks are performed by asserting the external break signal (i.e. the Ext_BRK

and Ext_NM_BRK input ports). On a break the instruction in the execution stage will

complete, while the instruction in the decode stage is replaced by a branch to the break

vector (address 0x18). The break return address (the PC associated with the instruction in

the decode stage at the time of the break) is automatically loaded into general purpose

register R16. MicroBlaze also sets the Break In Progress (BIP) flag in the Machine Status

Register (MSR).

A normal hardware break (i.e the Ext_BRK input port) is only handled when there is no

break in progress (i.e MSR[BIP] is set to 0). The Break In Progress flag disables interrupts.

A non-maskable break (i.e the Ext_NM_BRK input port) will always be handled

immediately.

The BIP bit in the MSR is automatically cleared when executing the RTBD instruction.

MicroBlaze Processor Reference Guide www.xilinx.com 35

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 36

R

Software Breaks

Latency

Equivalent Pseudocode

Interrupt

Chapter 1: MicroBlaze Architecture

To perform a software break, use the brk and brki instructions. Refer to Chapter 4,

“MicroBlaze Instruction Set Architecture” for detailed information on software breaks.

The time it will take MicroBlaze to enter a break service routine from the time the break

occurs, depends on the instruction currently in the execution stage and the latency to the

memory storing the break vector.

r16 ← PC

PC

← 0x00000018

MSR[BIP]

MicroBlaze supports one external interrupt source (connecting to the Interrupt input

port). The processor will only react to interrupts if the Interrupt Enable (IE) bit in the

Machine Status Register (MSR) is set to 1. On an interrupt the instruction in the execution

stage will complete, while the instruction in the decode stage is replaced by a branch to the

interrupt vector (address 0x10). The interrupt return address (the PC associated with the

instruction in the decode stage at the time of the interrupt) is automatically loaded into

general purpose register R14. In addition, the processor also disables future interrupts by

clearing the IE bit in the MSR. The IE bit is automatically set again when executing the

RTID instruction.

← 1

Interrupts are ignored by the processor if either of the break in progress (BIP) or exception

in progress (EIP) bits in the MSR are set to 1.

Latency

The time it will take MicroBlaze to enter an Interrupt Service Routine (ISR) from the time

an interrupt occurs depends on the configuration of the processor and the latency of the

memory controller storing the interrupt vectors. If MicroBlaze is configured to have a

hardware divider, the largest latency will happen when an interrupt occurs during the

execution of a division instruction.

Equivalent Pseudocode

r14 ← PC

PC

← 0x00000010

MSR[IE]

← 0

User Vector (Exception)

The user exception vector is located at address 0x8. A user exception is caused by inserting

a ‘BRALID Rx,0x8’ instruction in the software flow. Although Rx could be any general

purpose register Xilinx recommends using R15 for storing the user exception return

address, and to use the RTSD instruction to return from the user exception handler.

Pseudocode

rx ← PC

36 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 37

Instruction Cache

PC ← 0x00000008

Instruction Cache

Overview

MicroBlaze may be used with an optional instruction cache for improved performance

when executing code that resides outside the LMB address range.

The instruction cache has the following features:

• Direct mapped (1-way associative)

• User selectable cacheable memory address range

• Configurable cache and tag size

• Caching over CacheLink (XCL) interface

• Option to use 4 or 8 word cache-line

• Cache on and off controlled using a bit in the MSR

• Optional WIC instruction to invalidate instruction cache lines

R

General Instruction Cache Functionality

When the instruction cache is used, the memory address space in split into two segments:

a cacheable segment and a non-cacheable segment. The cacheable segment is determined

by two parameters: C_ICACHE_BASEADDR and C_ICACHE_HIGHADDR. All

addresses within this range correspond to the cacheable address segment. All other

addresses are non-cacheable.

Instruction Address Bits

0 3031

Tag Address

Line Addr

Word Addr

Tag

BRAM

Instruction

BRAM

Tag

Valid (word and line)

Cache Address

=

Cache_instruction_data

-

Cache_Hit

-

Figure 1-9: Instruction Cache Organization

The cacheable instruction address consists of two parts: the cache address, and the tag

address. The MicroBlaze instruction cache can be configured from 2kB to 64 kB. This

correspondsto a cache address of between 11and 16 bits. The tag addresstogether with the

cache address should match the full address of cacheable memory.

MicroBlaze Processor Reference Guide www.xilinx.com 37

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 38

R

For example: in a MicroBlaze configured with C_ICACHE_BASEADDR= 0x00300000,

C_ICACHE_HIGHADDR=0x0030ffff, C_CACHE_BYTE_SIZE=4096, and

C_ICACHE_LINELEN=8; the cacheable memory of 64 kB uses 16 bits of byte address, and

the 4 kB cache uses 12 bits of byte address, thus the required address tag width is: 16-12=4

bits. The total number of block RAM primitives required in this configuration is: 2

RAMB16 for storing the 1024 instruction words, and 1 RAMB16 for 128 cache line entries,

each consisting of: 4 bits of tag, 8 word-valid bits, 1 line-valid bit. In total 3 RAMB16

primitives.

Instruction Cache Operation

For every instruction fetched, the instruction cache detects if the instruction address

belongs to the cacheable segment. If the address is non-cacheable, the cache controller

ignores the instruction and lets the OPB or LMB complete the request. If the address is

cacheable, a lookup is performed on the tag memory to check if the requested address is

currently cached. The lookup is successful if: the word and line valid bits are set, and the

tag address matches the instruction address tag segment. On a cache miss, the cache

controllerwill requestthe new instruction over the instruction CacheLink (IXCL) interface,

and wait for the memory controller to return the associated cache line.

Chapter 1: MicroBlaze Architecture

Instruction Cache Software Support

Data Cache

Overview

MSR Bit

The ICE bit in the MSR provides software control to enable and disable caches.

The contents of the cache are preserved by default when the cache is disabled. The user can

invalidate cache lines using the WIC instruction or using the hardware debug logic of

MicroBlaze.

WIC Instruction

The optional WIC instruction (C_ALLOW_ICACHE_WR=1) is used to invalidate cache

lines in the instruction cache from an application. For a detailed description, please refer to

Chapter 4, “MicroBlaze Instruction Set Architecture”. The cache must be disabled

(MSR[ICE]=0) when the instruction is executed.

MicroBlaze may be used with an optional data cache for improved performance. The

cached memory range must not include addresses in the LMB address range.

The data cache has the following features

• Direct mapped (1-way associative)

• Write-through

• User selectable cacheable memory address range

• Configurable cache size and tag size

• Caching over CacheLink (XCL) interface

• Option to use 4 or 8 word cache-lines

38 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Page 39

Data Cache

• Cache on and off controlled using a bit in the MSR

• Optional WDC instruction to invalidate data cache lines

General Data Cache Functionality

When the data cache is used, the memory address space in split into two segments: a

cacheable segment and a non-cacheable segment. The cacheable area is determined by two

parameters: C_DCACHE_BASEADDR and C_DCACHE_HIGHADDR. All addresses

within this range correspond to the cacheable address space. All other addresses are noncacheable.

0 3031

Tag Address

Data Address Bits

Cache Word Address

R

-

-

Addr

Tag

BRAM

Tag

Valid

=

Cache_Hit

Load_Instruction

Addr

Data

Cache_data

BRAM

Figure 1-10: Data Cache Organization

The cacheable data address consists of two parts: the cache address, and the tag address.

The MicroBlaze data cache can be configured from 2kB to 64 kB. This corresponds to a

cache address of between 11 and 16 bits. The tag address together with the cache address

should match the full address of cacheable memory.

For example: in a MicroBlaze configured with C_ICACHE_BASEADDR= 0x00400000,

C_ICACHE_HIGHADDR=0x00403fff, C_CACHE_BYTE_SIZE=2048, and

C_ICACHE_LINELEN=4; the cacheable memory of 16 kB uses 14 bits of byte address, and

the 2 kB cache uses 11bits of byte address, thus the required address tag width is: 14-11=3

bits. The total number of block RAM primitives required in this configuration is: 1

RAMB16 for storing the 512 instruction words, and 1 RAMB16 for 128 cache line entries,

each consisting of: 3 bits of tag, 4 word-valid bits, 1 line-valid bit. In total 2 RAMB16

primitives.

Data Cache Operation

The MicroBlaze data cache implements a write-through protocol. A store to an address

within the cacheable range will, provided that the cache is enabled, generate an equivalent

byte, halfword, or word write over the data CacheLink (DXCL) to external memory. The

write will also update the cached data if the target address word is in the cache (i.e. the

write is a cache-hit). A write cache-miss does not load the associated cache line into the

cache.

MicroBlaze Processor Reference Guide www.xilinx.com 39

UG081 (v6.0) June 1, 2006 1-800-255-7778

Page 40

R

A load from an address within the cacheable range will, provided that the cache is enabled,

trigger a check to determine if the requested data is currently cached. If it is (i.e. on a cachehit) the requested data is retrieved from the cache. If not (i.e. on a cache-miss) the address

is requested over data CacheLink (DXCL), and the processor pipeline will stall until the

cache line associated to the requested address is returned from the external memory

controller.

Data Cache Software Support

MSR Bit

The DCE bit in the MSR controls whether or not the cache is enabled. When disabling

caches the user must ensure that all the prior writes within the cacheable range has been

completed in external memory before reading back over OPB. This can be done by writing

to a semaphore immediately before turning off caches, and then in a loop poll the

semaphore until it has been written.

The contents of the cache is preserved when the cache is disabled.

WDC Instruction

Chapter 1: MicroBlaze Architecture

The optional WDC instruction (C_ALLOW_DCACHE_WR=1) is used to invalidate cache

lines in the data cache from an application. For a detailed description, please refer to

Chapter 4, “MicroBlaze Instruction Set Architecture”.

Floating Point Unit (FPU)

Overview

The MicroBlaze floating point unit is based on the IEEE 754 standard:

• Uses IEEE 754 single precision floating point format, including definitions for infinity,

not-a-number (NaN), and zero

• Supports addition, subtraction, multiplication, division, and comparison instructions

• Implements round-to-nearest mode

• Generates sticky status bits for: underflow, overflow, and invalid operation

For improved performance, the following non-standard simplifications are made:

• Denormalized

a denormalized number will return a quiet NaN and set the denormalized operand

error bit in FSR; see "Floating Point Status Register (FSR)" on page 27

• A denormalized result is stored as a signed 0 with the underflow bit set in FSR. This

method is commonly referred to as Flush-to-Zero (FTZ)

• An operation on a quiet NaN will return the fixed NaN: 0xFFC00000, rather than one

of the NaN operands

• Overflow as a result of a floating point operation will always return signed ∞, even

when the exception is trapped.

(1)

operands are not supported. A hardware floating point operation on

1. Numbers that are so close to 0, that they cannot be represented with full precision, i.e. any number n that falls

in the following ranges: ( 1.17549*10