Page 1

0

R

DS610 July 16, 2007

0 0

Module 1:

Introduction and Ordering Information

DS610-1 (v2.0) July 16, 2007

• Introduction

• Features

• Architectural Overview

• Configuration Overview

• General I/O Capabilities

• Supported Packages and Package Marking

• Ordering Information

Module 2:

Functional Description

DS610-2 (v2.0) July 16, 2007

The functionality of the Spartan™-3A DSP FPGA family is

described in the following documents.

• UG331:

- Clocking Resources

- Digital Clock Managers (DCMs)

-Block RAM

- Configurable Logic Blocks (CLBs)

-I/O Resources

- Programmable Interconnect

-ISE

- Embedded Processing and Control Solutions

- Pin Types and Package Overview

- Package Drawings

- Powering FPGAs

- Power Management

• UG431

User Guide

- DSP48A Slice Design Considerations

- DSP48A Architecture Highlights

- DSP48A Application Examples

Spartan-3 Generation FPGA User Guide

· Distributed RAM

· SRL16 Shift Registers

· Carry and Arithmetic Logic

TM

Software Design Tools and IP Cores

:

XtremeDSP™ DSP48A for Spartan-3A DSP FPGAs

· 18 x 18-Bit Multipliers

· 48-Bit Accumulator

· 18-bit Pre-Adder

Spartan-3A DSP FPGA Family:

Data Sheet

Product Specification

:

• UG332

- Configuration Overview

- Configuration Pins and Behavior

- Bitstream Sizes

- Detailed Descriptions by Mode

- ISE iMPACT Programming Examples

- MultiBoot Reconfiguration

- Design Authentication using Device DNA

Module 3:

DC and Switching Characteristics

DS610-3 (v2.0) July 16, 2007

• DC Electrical Characteristics

- Absolute Maximum Ratings

- Supply Voltage Specifications

- Recommended Operating Conditions

• Switching Characteristics

- I/O Timing

- Configurable Logic Block (CLB) Timing

- Digital Clock Manager (DCM) Timing

-Block RAM Timing

- XtremeDSP Slice Timing

- Configuration and JTAG Timing

Module 4:

Pinout Descriptions

DS610-4 (v2.0) July 16, 2007

• Pin Descriptions

• Package Overview

• Pinout Tables

• Footprint Diagrams

Spartan-3 Generation Configuration User Guide

· Master Serial Mode using Platform Flash PROM

· Master SPI Mode using Commodity Serial Flash

· Master BPI Mode using Commodity Parallel Flash

· Slave Parallel (SelectMAP) using a Processor

· Slave Serial using a Processor

· JTAG Mode

SPARTAN-3A DSP

SPARTAN-3A DSP

www.xilinx.com/spartan3adsp

© 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

DS610 July 16, 2007 www.xilinx.com 1

Product Specification

All other trademarks are the proper ty of their respective owners. All specifications are subject to change without notice.

Page 2

Data Sheet

R

This page intentionally left blank.

2 www.xilinx.com DS610 July 16, 2007

Product Specification

Page 3

<

R

B

L

B

Spartan-3A DSP FPGA Family:

Introduction and Ordering Information

DS610-1 (v2.0) July 16, 2007 Product Specification

Introduction

The Spartan™-3A DSP family of Field-Programmable Gate Arrays

(FPGAs) solves the design challenges in most high-volume,

cost-sensitive, high-performance DSP applications.

two-member family offers densities ranging from

system gates, as shown in Table 1.

The Spartan-3A DSP family builds on the success of the

Spartan-3A FPGA family by increasing the amount of memory per

logic and adding XtremeDSP™ DSP48A slices. New features

improve system performance and reduce the cost of configuration.

These Spartan-3A DSP FPGA enhancements, combined with

proven 90 nm process technology, deliver more functionality and

bandwidth per dollar than ever before, setting the new standard in

the programmable logic

and DSP processing

Spartan-3A and Spartan-3A DSP FPGA Differences

The Spartan-3A DSP FPGAs extend and enhance the Spartan-3A

FPGA family. The XC3SD1800A and the XC3SD3400A devices

are tailored for DSP applications and have additional block RAM

and XtremeDSP DSP48A slices. The XtremeDSP DSP48A slices

replace the 18x18 multipliers found in the Spartan-3A devices and

are based on the DSP48 blocks found in the Virtex™-4 devices.

The block RAMs are also enhanced to run faster by adding an

output register. Both the block RAM and DSP48A slices in the

Spartan-3A DSP devices run at 250 MHz in the lowest cost,

standard -4 speed grade.

Because of their exceptional DSP price/performance ratio,

Spartan-3A DSP FPGAs are ideally suited to a wide range of

consumer electronics applications, including broadband access,

home networking, display/projection, and digital television

equipment.

The Spartan-3A DSP family is a superior alternative to mask

programmed ASICs. FPGAs avoid the high initial cost, lengthy

development cycles, and the inherent inflexibility of conventional

ASICs. Also, FPGA programmability permits design upgrades in

the field with no hardware replacement necessary, an impossibility

with ASICs.

1.8 to 3.4

industry.

The

million

♦ Available pipeline stages for enhanced performance of at least

250 MHz in the standard -4 speed grade

♦ 48-bit accumulator for multiply-accumulate (MAC) operation

♦ Integration added for complex multiply or multiply-add operation

♦ Integrated 18-bit pre-adder

♦ Optional cascaded Multiply or MAC

• Hierarchical SelectRAM™ memory architecture

♦

Up to 2268 Kbits of fast block RAM with byte write enables for

processor applications

♦ Up to 373 Kbits of efficient distributed RAM

♦ Registered outputs on the block RAM with operation of at least

280 MHz in the standard -4 speed grade

• Dual-range V

supply simplifies 3.3V-only design

CCAUX

• Suspend, Hibernate modes reduce system power

• Low-power option reduces quiescent current

• Multi-voltage, multi-standard SelectIO™ interface pins

♦

Up to 519 I/O pins or 227 differential signal pairs

♦ LVCMOS, LVTTL, HSTL, and SSTL single-ended I/O

♦ 3.3V, 2.5V, 1.8V, 1.5V, and 1.2V signaling

♦ Selectable output drive, up to 24 mA per pin

♦ QUIETIO standard reduces I/O switching noise

♦ Full 3.3V ± 10% compatibility and hot swap compliance

♦ 622+ Mb/s data transfer rate per differential I/O

♦ LVDS, RSDS, mini-LVDS, HSTL/SSTL differential I/O with

integrated differential termination resistors

♦ Enhanced Double Data Rate (DDR) support

♦ DDR/DDR2 SDRAM support up to 333 Mb/s

♦ Fully compliant 32-/64-bit, 33/66 MHz PCI suppor t

• Abundant, flexible logic resources

♦

Densities up to 53712 logic cells, including optional shift register

♦ Efficient wide multiplexers, wide logic

♦ Fast look-ahead carry logic

♦ IEEE 1149.1/1532 JTAG programming/debug port

• Eight Digital Clock Managers (DCMs)

♦

Clock skew elimination (delay locked loop)

♦ Frequency synthesis, multiplication, division

♦ High-resolution phase shifting

♦ Wide frequency range (5 MHz to over 320 MHz)

• Eight low-skew global clock networks, eight additional clocks

per half device, plus abundant low-skew routing

• Configuration interface to industry-standard PROMs

♦

Low-cost, space-saving SPI serial Flash PROM

♦ x8 or x8/x16 parallel NOR Flash PROM

Features

• Very low cost, high-performance DSP solution for

high-volume, cost-conscious applications

• 250 MHz XtremeDSP DSP48A Slices

Dedicated 18-bit by 18-bit multiplier

♦

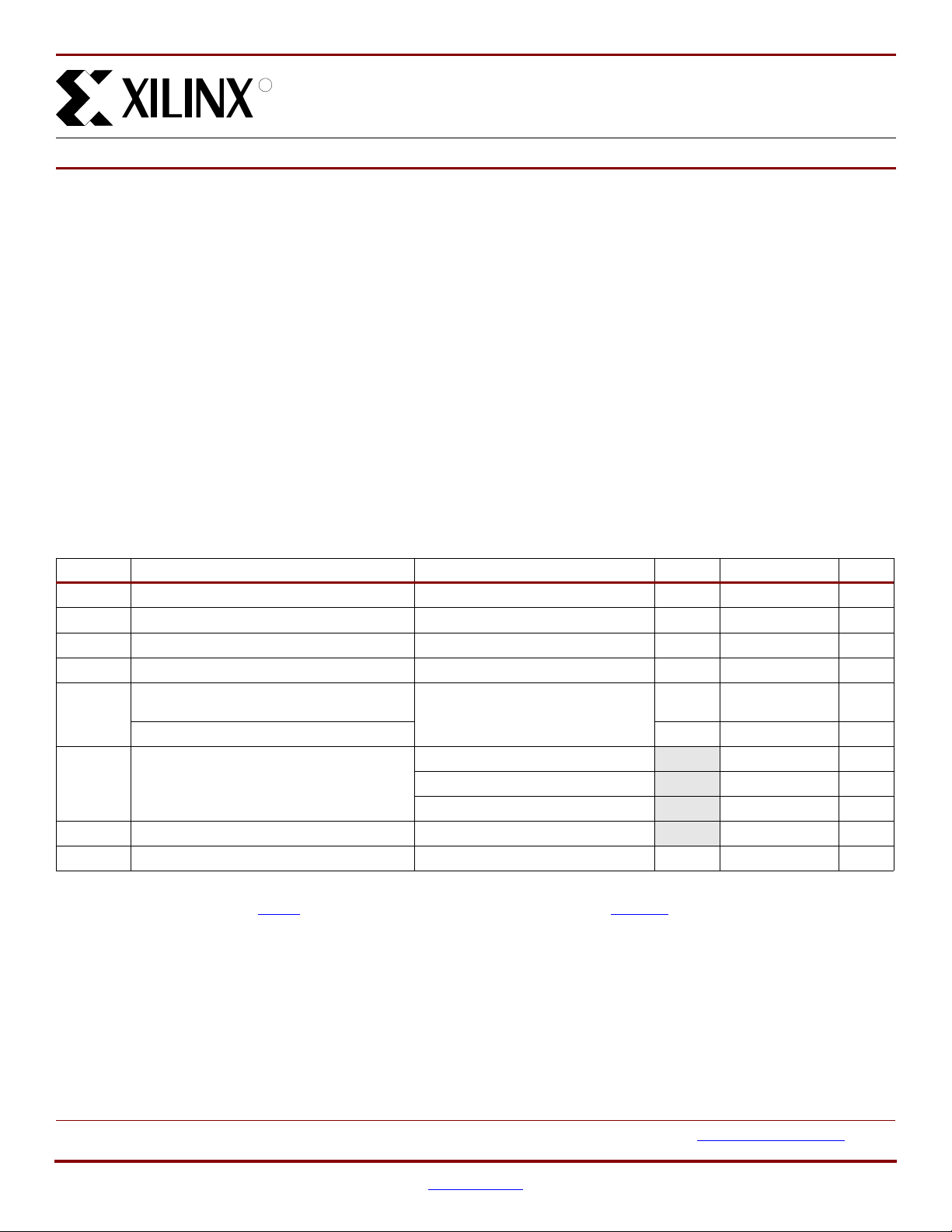

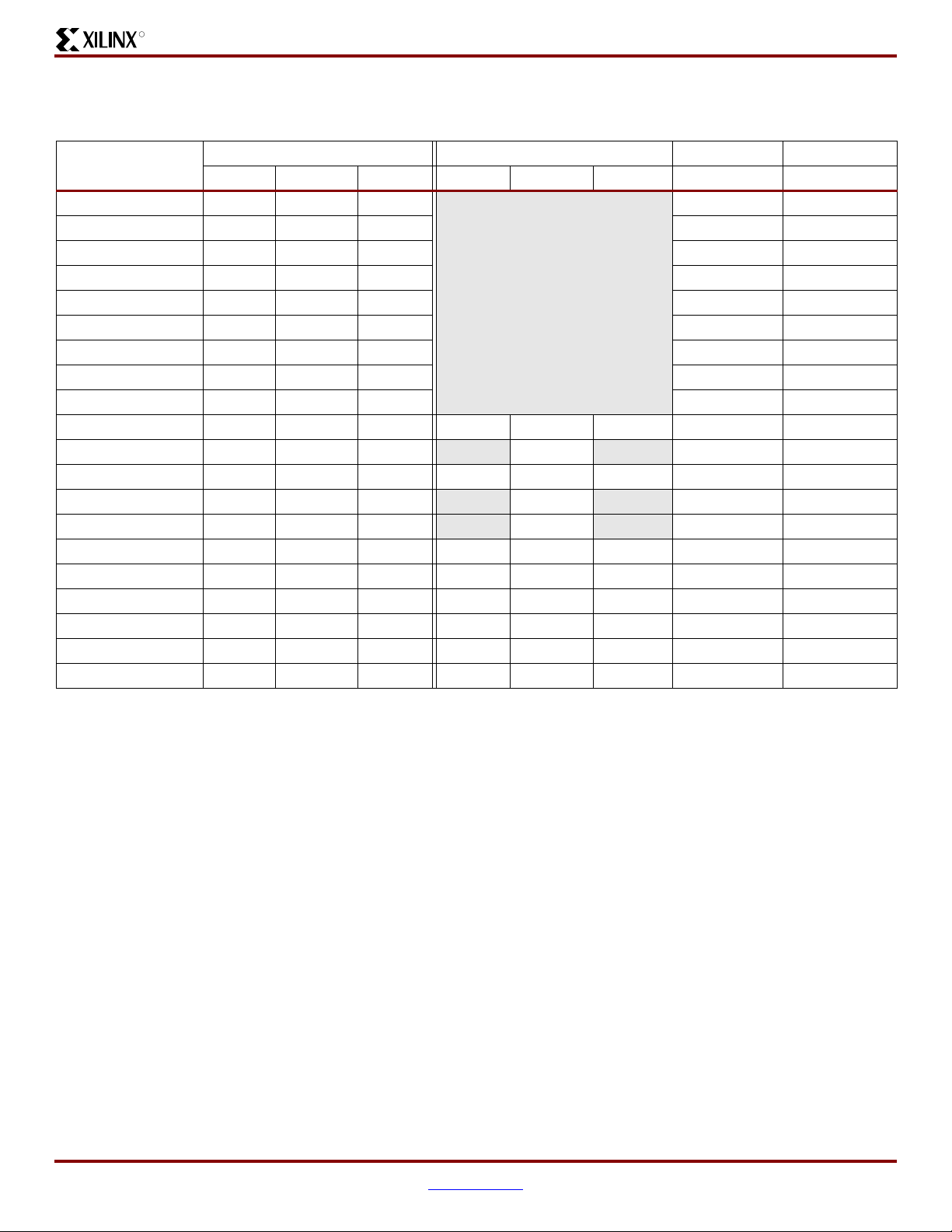

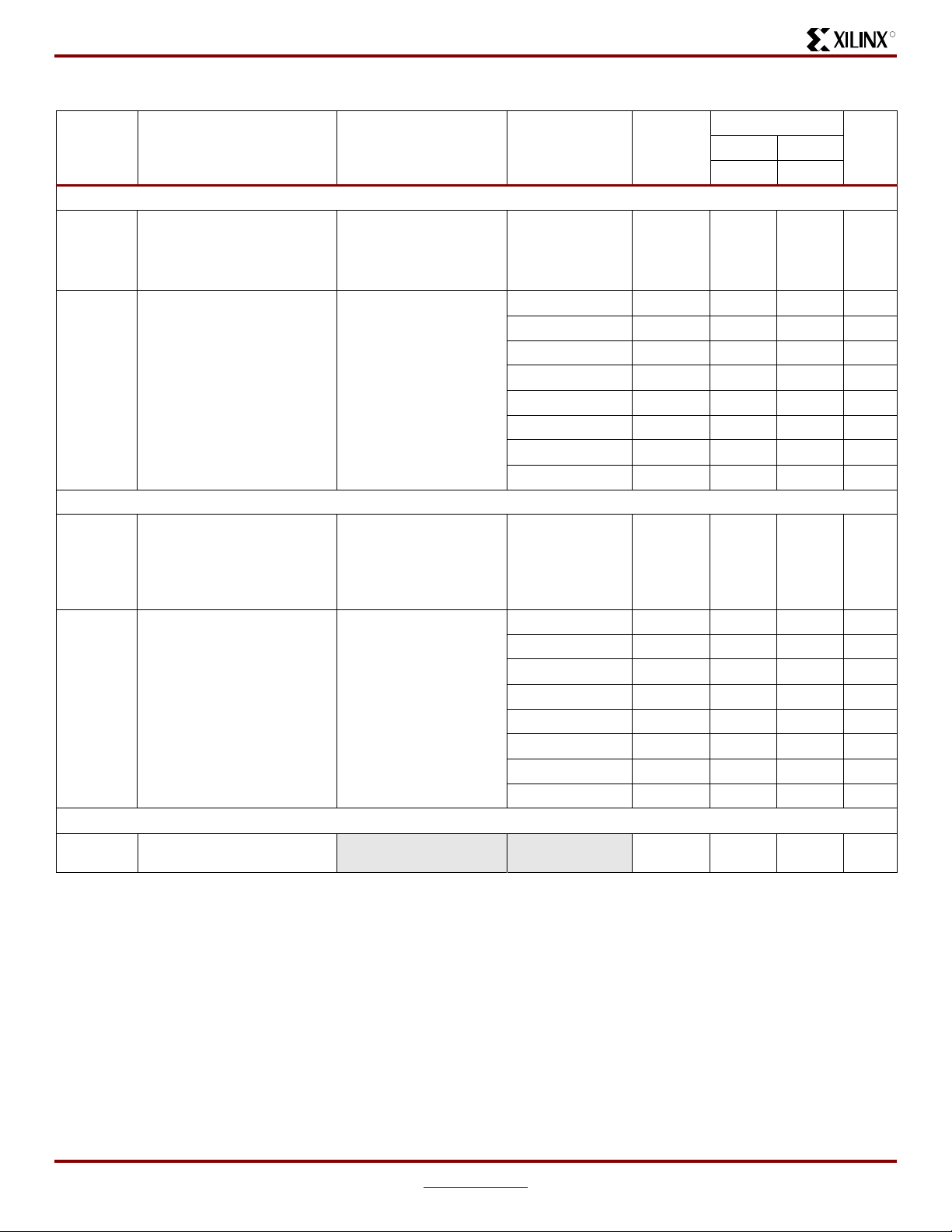

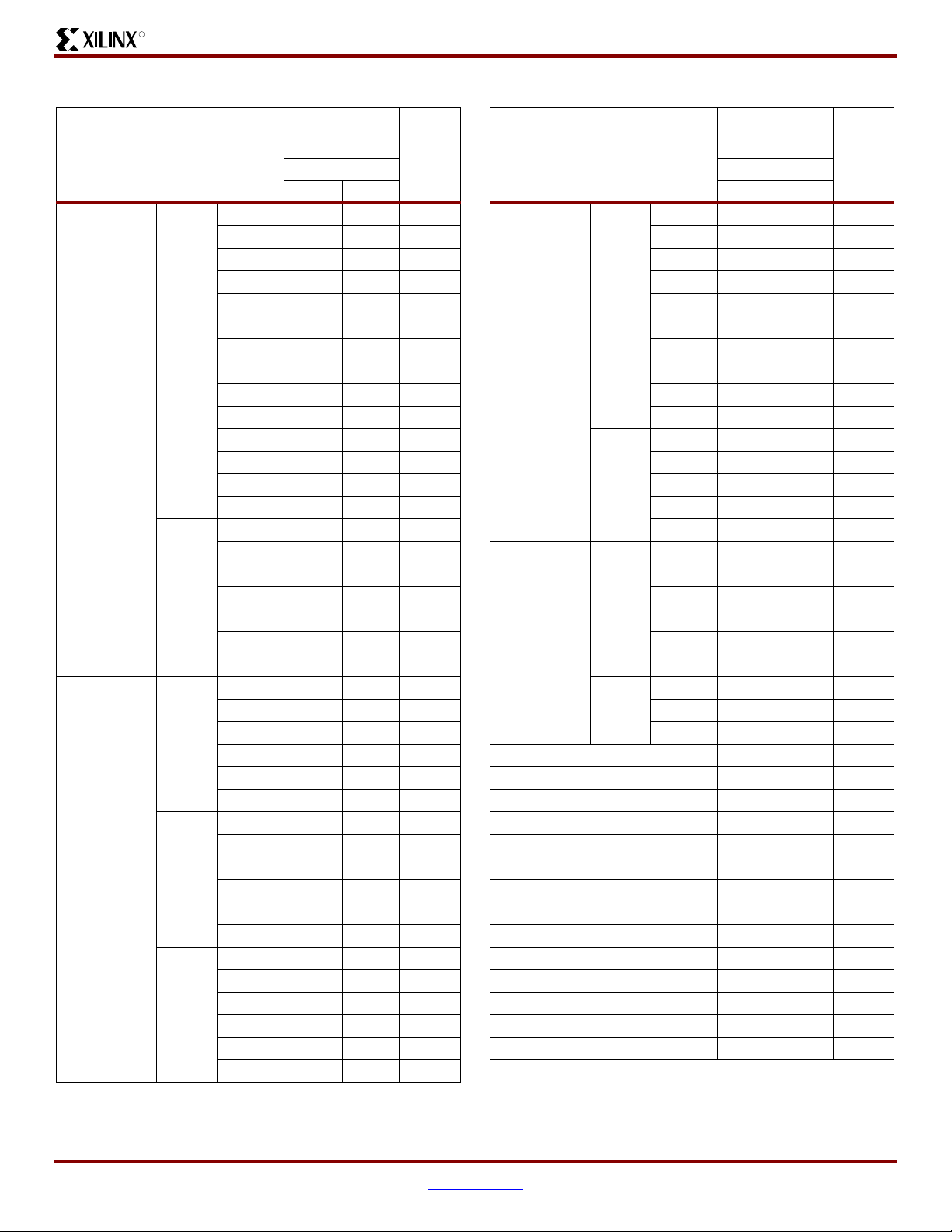

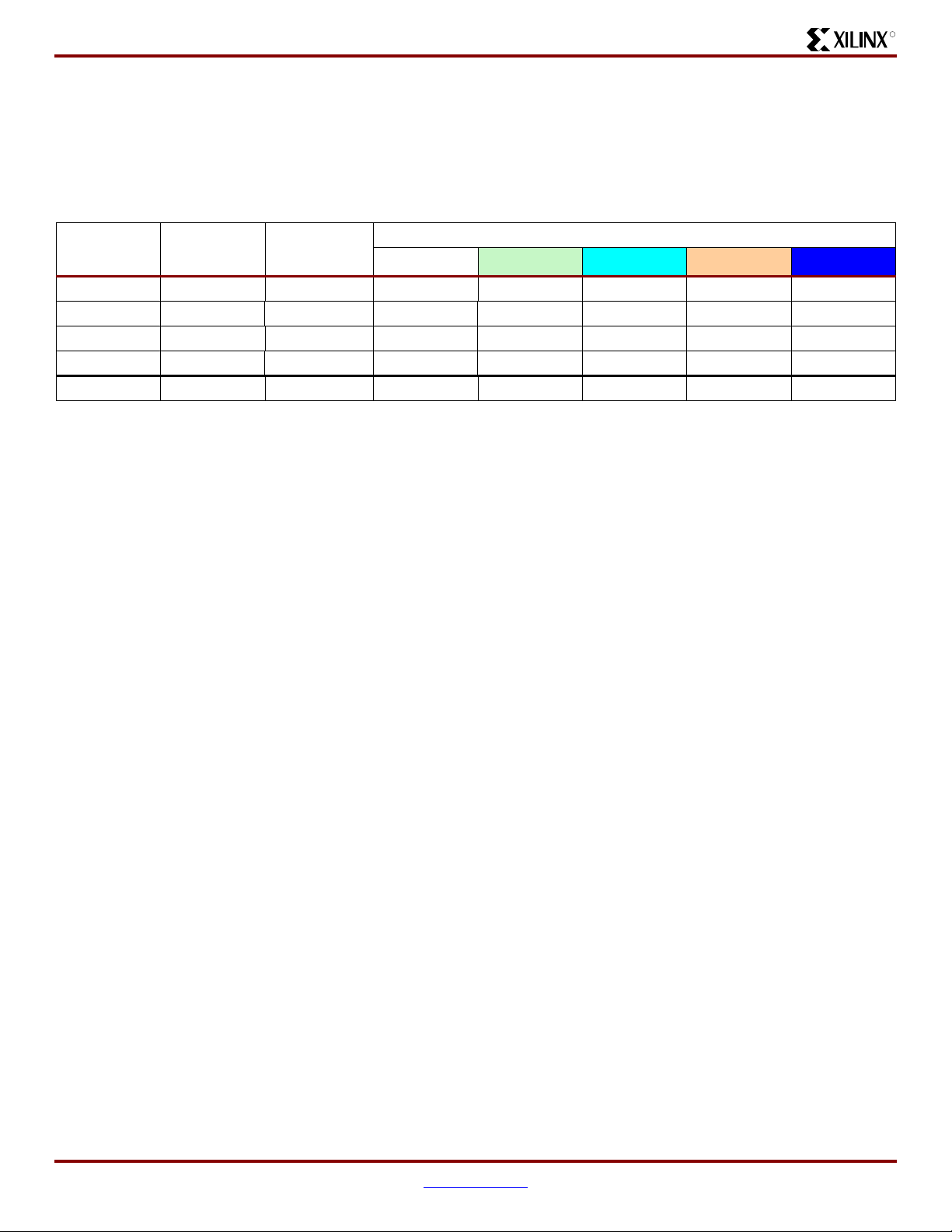

Table 1:

XC3SD1800A 1800K 37,440 88 48 4160 16640 260K 1512K 84 8 519 227

XC3SD3400A 3400K 53,712 104 58 5968 23872 373K 2268K 126 8 469 213

Notes: 1. By convention, one Kb is equivalent to 1,024 bits.

Summary of Spartan-3A DSP FPGA Attributes

CLB Array (One CLB = Four Slices)

Device

System

Gates

Equivalent

Logic Cells

Tota l

CLBs

Tota l

Slices

♦ Low-cost Xilinx Platform Flash with JTAG

♦ Unique Device DNA identifier for design authentication

♦ Load multiple bitstreams under FPGA control

• MicroBlaze™ and PicoBlaze™ embedded processor cores

• BGA and CSP packaging with Pb-free options

♦

Common footprints support easy density migration

Distributed

RAM

(1)

Bits

Block

RAM

(1)

Bits

DSP48As DCMs

Maximum

User I/O

Maximum

Differential

I/O PairsRows Columns

© 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks are the proper ty of their respective owners. All specifications are subject to change without notice.

DS610-1 (v2.0) July 16, 2007 www.xilinx.com 3

Product Specification

Page 4

Introduction and Ordering Information

Architectural Overview

R

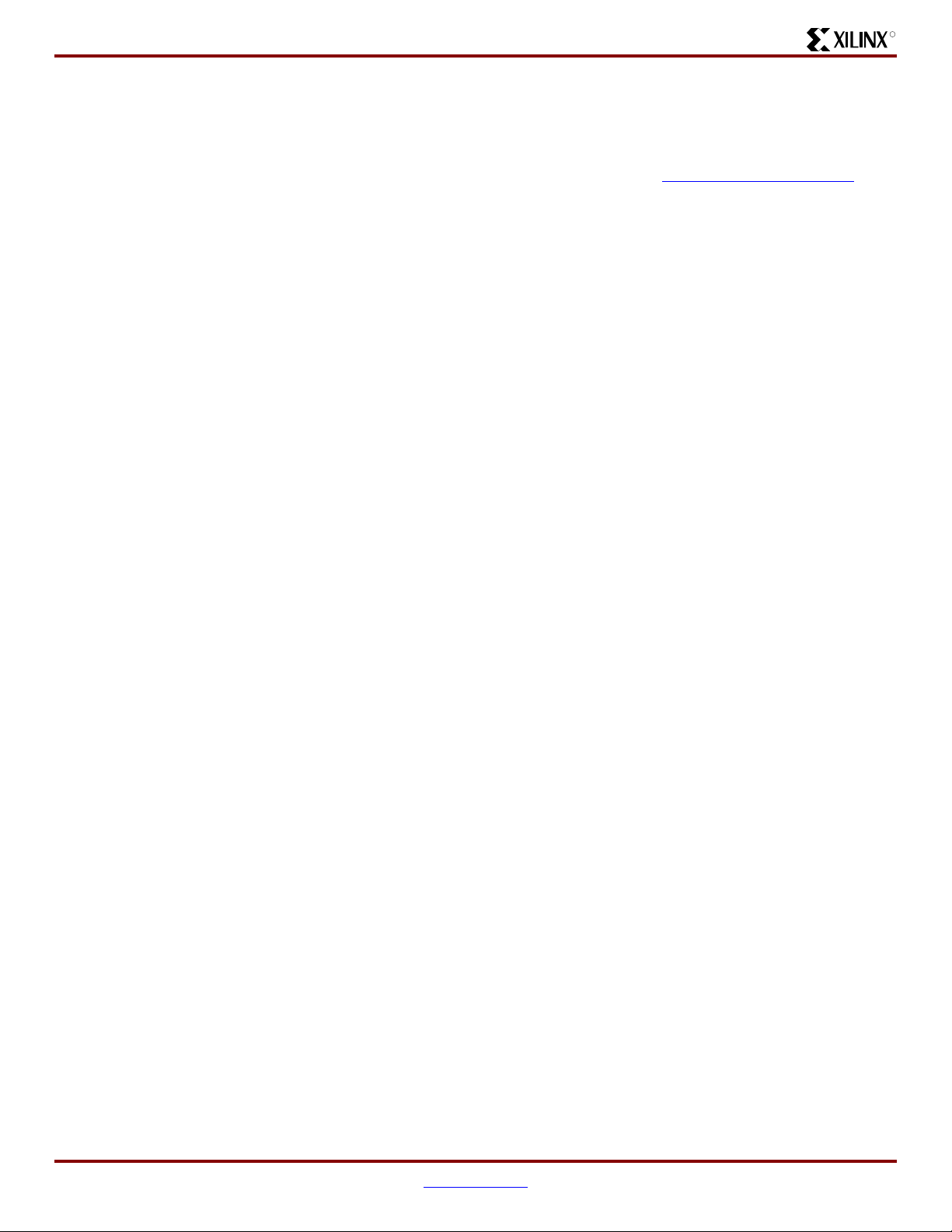

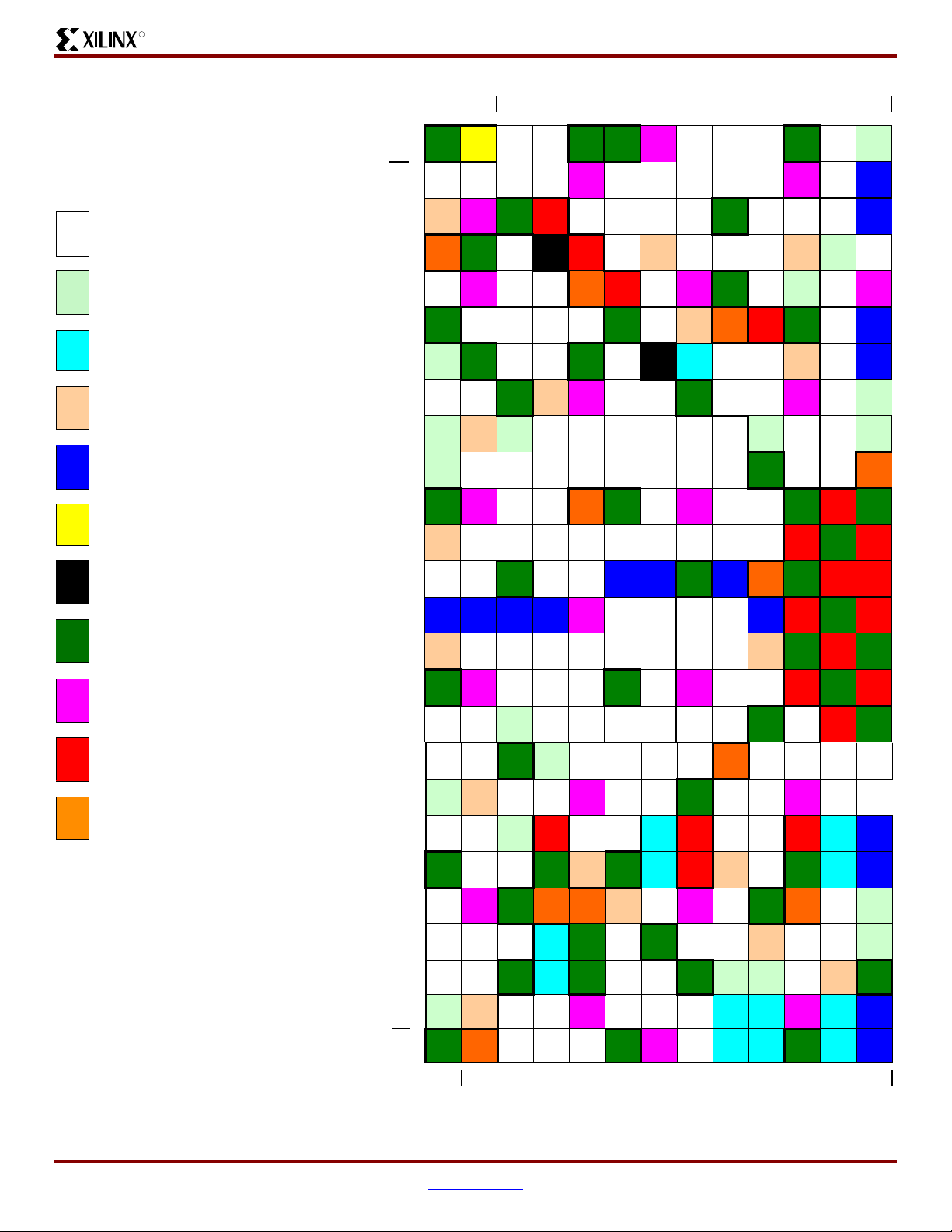

The Spartan-3A DSP family architecture consists of five

fundamental programmable functional elements:

• XtremeDSP DSP48A Slice provides an 18-bit x 18-bit

multiplier, 18-bit pre-adder, 48-bit

post-adder/accumulator, and cascade capabilities for

various DSP applications.

• Block RAM provides data storage in the form of

18-Kbit dual-port blocks.

• Configurable Logic Blocks (CLBs) contain flexible

Look-Up Tables (LUTs) that implement logic plus

storage elements used as flip-flops or latches. CLBs

perform a wide variety of logical functions as well as

store data.

• Input/Output Blocks (IOBs) control the flow of data

between the I/O pins and the internal logic of the

device. IOBs support bidirectional data flow plus

3-state operation. Supports a variety of signal

standards, including several high-performance

differential standards. Double Data-Rate (DDR)

registers are included.

• Digital Clock Manager (DCM) Blocks provide

self-calibrating, fully digital solutions for distributing,

delaying, multiplying, dividing, and phase-shifting clock

signals.

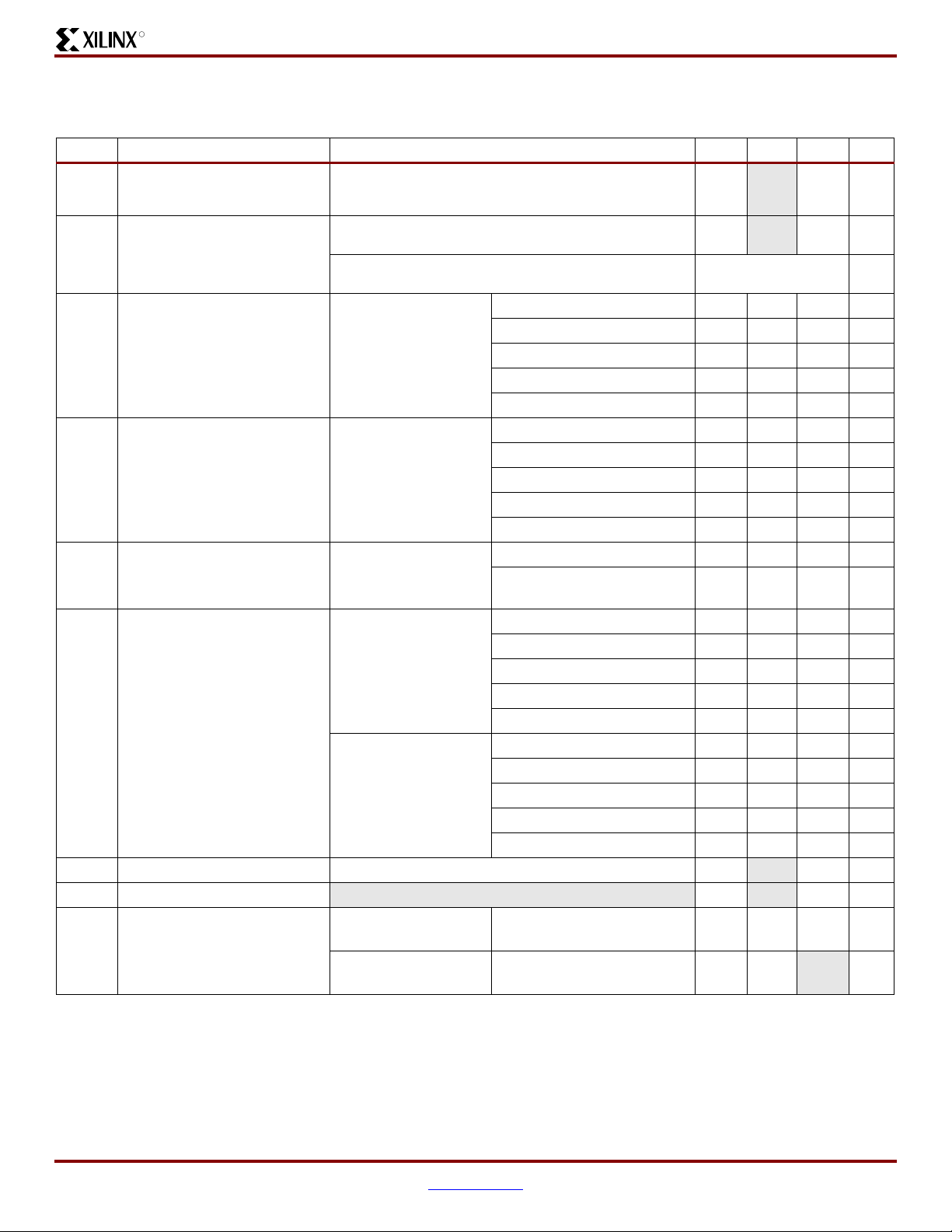

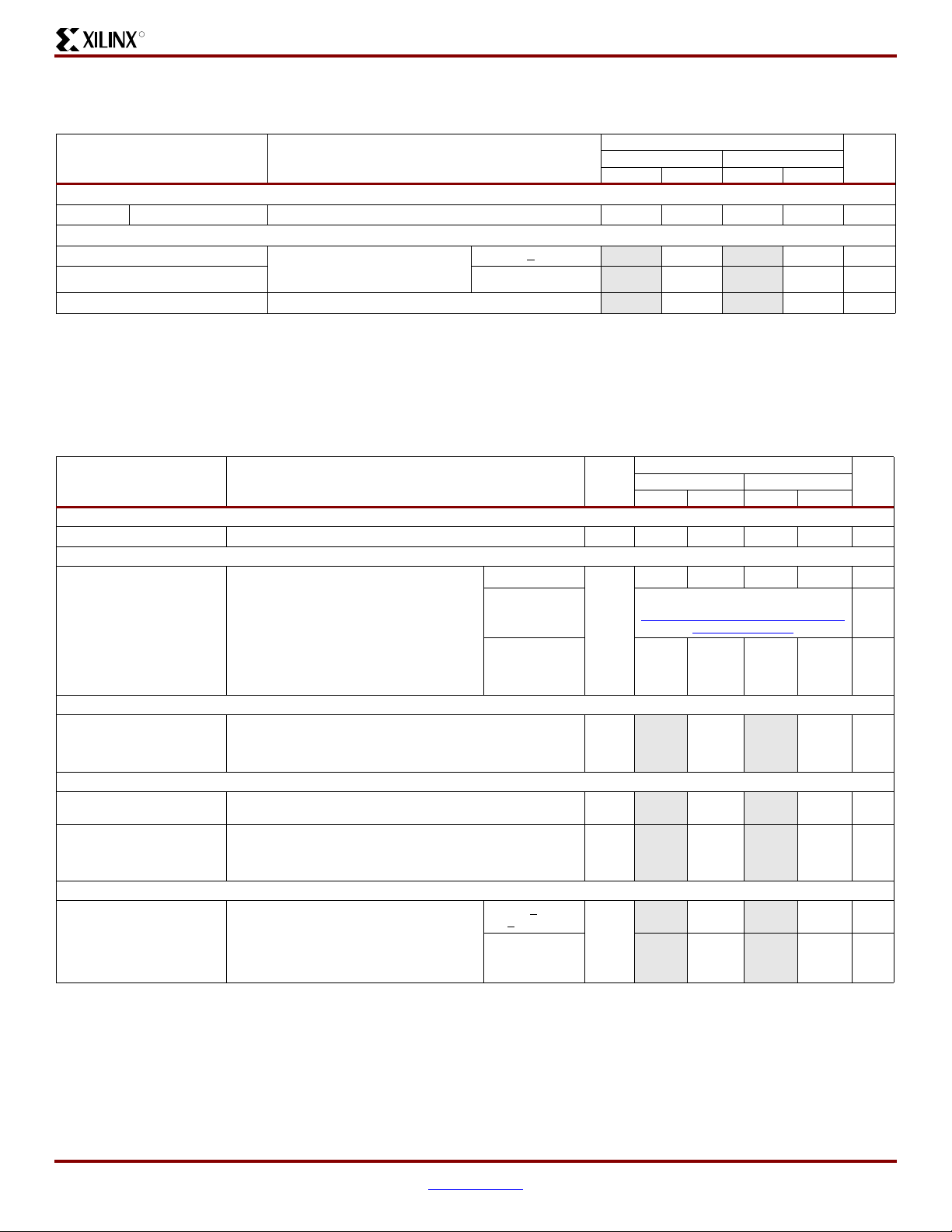

These elements are organized as shown in Figure 1. A dual

ring of staggered IOBs surrounds a regular array of CLBs.

The XC3SD1800A has four columns of DSP48As, and the

XC3SD3400A has five columns of DSP48As. Each

DSP48A has an associated block RAM. The DCMs are

positioned in the center with two at the top and two at the

bottom of the device and in the two outer columns of the 4 or

5 columns of block RAM and DSP48As.

The Spartan-3A DSP family features a rich network of

routing that interconnect all five functional elements,

transmitting signals among them. Each functional element

has an associated switch matrix that permits multiple

connections to the routing.

Configuration

Spartan-3A DSP FPGAs are programmed by loading

configuration data into robust, reprogrammable, static

CMOS configuration latches (CCLs) that collectively control

all functional elements and routing resources. The FPGA’s

configuration data is stored externally in a PROM or some

other non-volatile medium, either on or off the board.

After applying power, the configuration data is written to the

FPGA using any of seven different modes:

• Master Serial from a Xilinx Platform Flash PROM

• Serial Peripheral Interface (SPI) from an

industry-standard SPI serial Flash

• Byte Peripheral Interface (BPI) Up from an

industry-standard x8 or x8/x16 parallel NOR Flash

• Slave Serial, typically downloaded from a processor

• Slave Parallel, typically downloaded from a processor

• Boundary Scan (JTAG), typically downloaded from a

processor or system tester

Furthermore, Spartan-3A DSP FPGAs support MultiBoot

configuration, allowing two or more FPGA configuration

bitstreams to be stored in a single SPI serial Flash or a

parallel NOR Flash. The FPGA application controls which

configuration to load next and when to load it.

Additionally, each Spartan-3A DSP FPGA contains a

unique, factory-programmed Device DNA identifier useful

for tracking purposes, anti-cloning designs, or IP protection.

I/O Capabilities

The Spartan-3A DSP FPGA SelectIO interface supports

many popular single-ended and differential standards.

Tab le 2 shows the number of user I/Os as well as the

number of differential I/O pairs available for each

device/package combination. Some of the user I/Os are

unidirectional input-only pins as indicated in Ta bl e 2 .

Spartan-3A DSP FPGAs support the following single-ended

standards:

• 3.3V low-voltage TTL (LVTTL)

• Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V,

1.5V, or 1.2V

• 3.3V PCI at 33 MHz or 66 MHz

• HSTL I, II, and III at 1.5V and 1.8V, commonly used in

memory applications

• SSTL I and II at 1.8V, 2.5V, and 3.3V, commonly used

for memory applications

Spartan-3A DSP FPGAs support the following differential

standards:

• LVDS, mini-LVDS, RSDS, and PPDS I/O at 2.5V or

3.3V

• Bus LVDS I/O at 2.5V

• TMDS I/O at 3.3V

• Differential HSTL and SSTL I/O

• LVPECL inputs at 2.5V or 3.3V

4 www.xilinx.com DS610-1 (v2.0) July 16, 2007

Product Specification

Page 5

R

Introduction and Ordering Information

IOBs

CLB

DCM

Block RAM

DSP48A Slice

IOBs

DCM

CLBs

DCM

IOBs

IOBs

IOBs

Block RAM / DSP48A Slice

DS610-1_01_031207

Notes:

1. The XC3SD1800A and XC3SD3400A have two DCMs on both the left and right sides, as well as the two DCMs at the top and

bottom of the devices. The two DCMs on the left and right of the chips are in the middle of the outer Block RAM/DSP48A

columns of the 4 or 5 columns in the selected device, as shown in the diagram above.

G431:

2. A detailed diagram of the DSP48A can be found in U

XtremeDSP DSP48A for Spartan-3A DSP FPGAs User Guide.

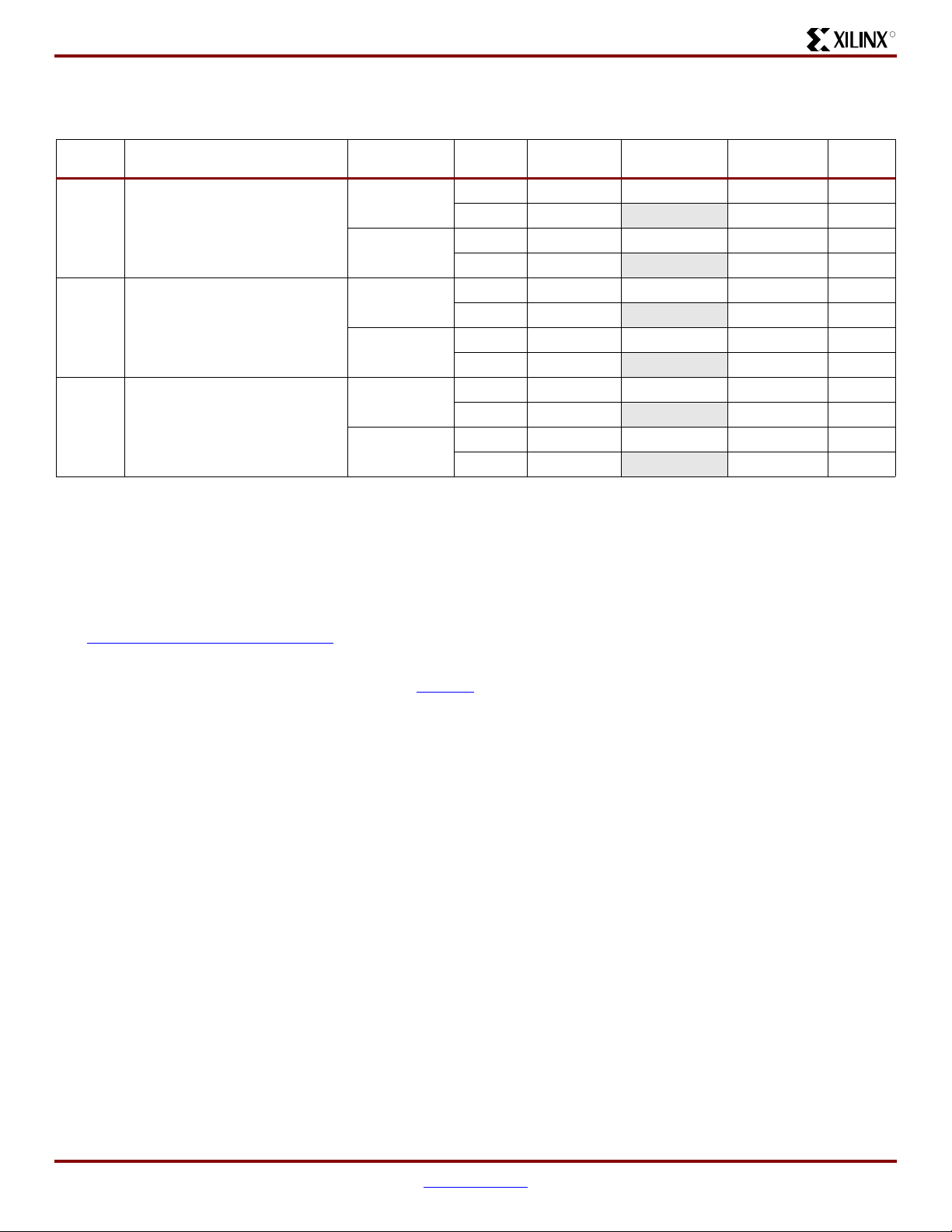

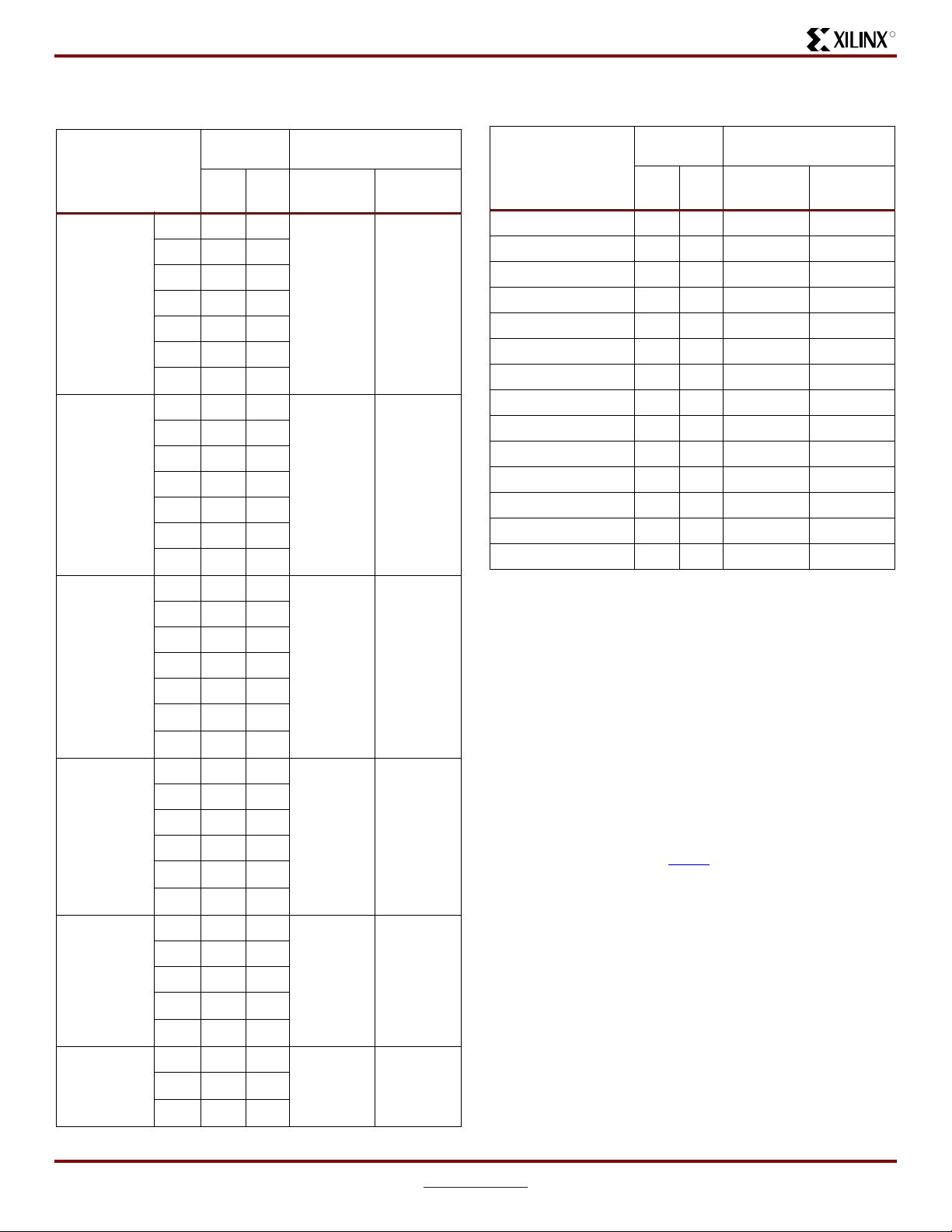

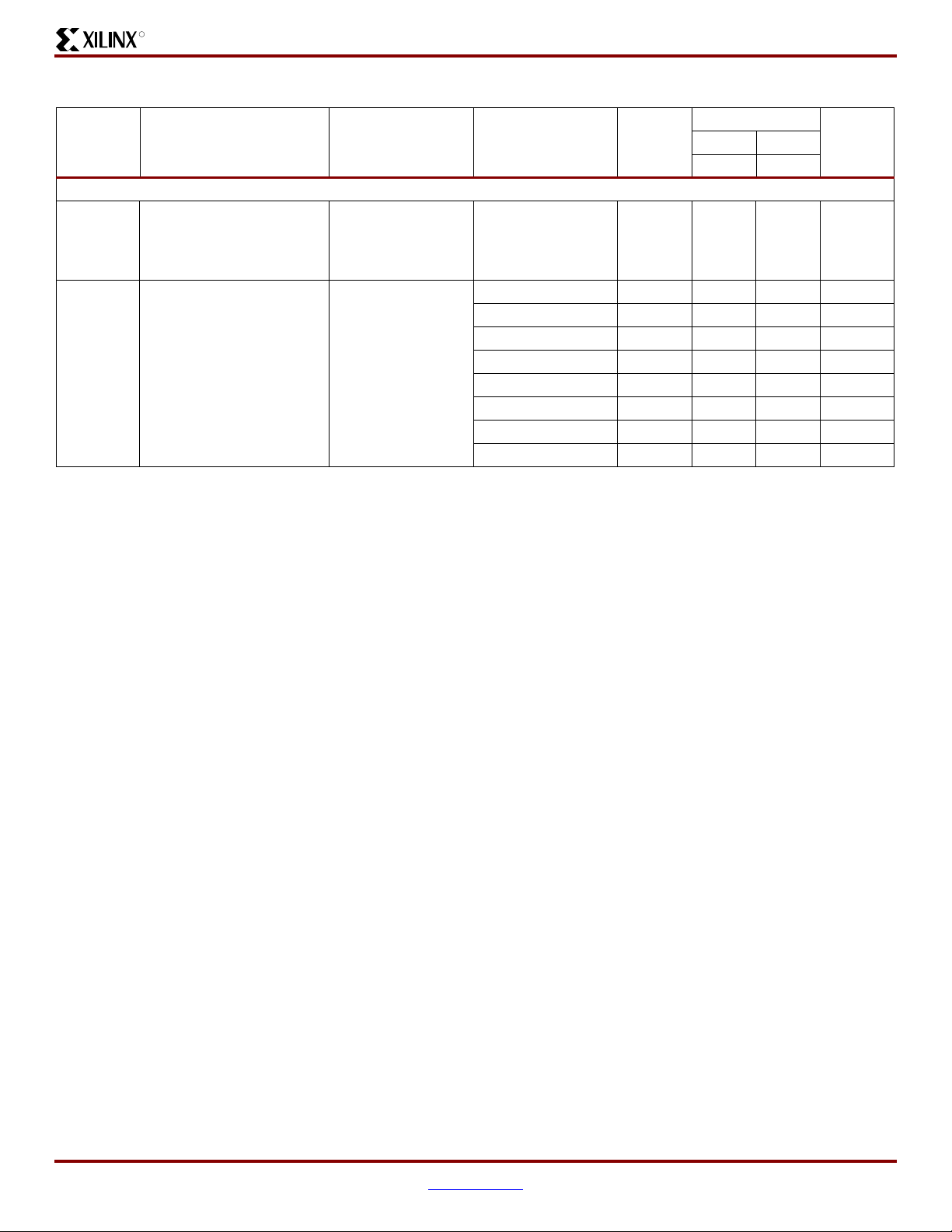

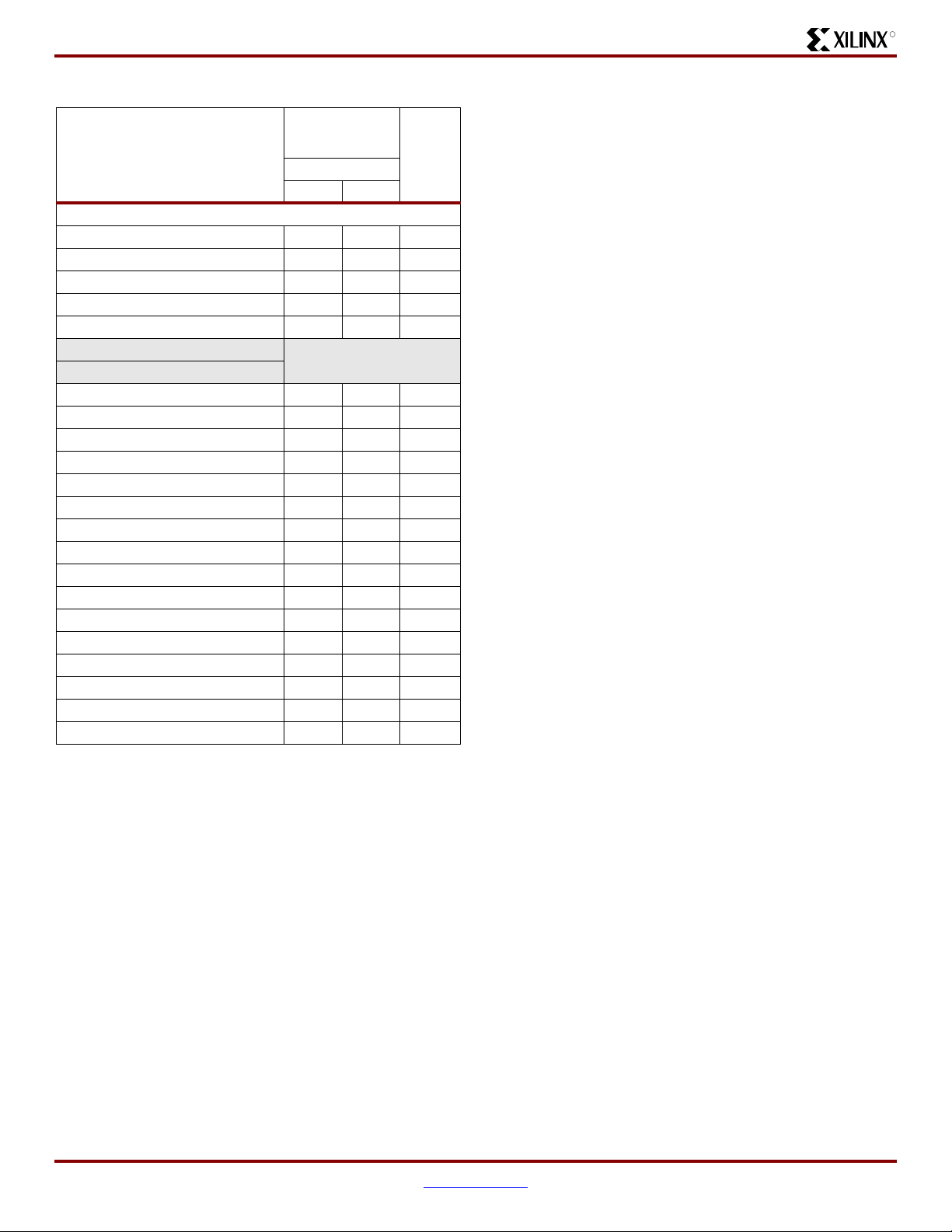

Table 2:

Figure 1:

Available User I/Os and Differential (Diff) I/O Pairs

Device

Spartan-3A DSP Family Architecture

CS484

CSG484

FG676

FGG676

User Diff User Diff

XC3SD1800A

XC3SD3400A

309

(60)

309

(60)

(78)

140

(78)

519

(110)

469

(60)

227

(131)

213

(117)

140

Notes:

1. The number shown in bold indicates the maximum number of I/O and input-only pins. The number shown in (

input-only pins. The differential (Diff) input-only pin count includes both differential pairs on input-only pins and differential pairs on I/O pins within I/O

banks that are restricted to differential inputs.

italics

) indicates the number of

DS610-1 (v2.0) July 16, 2007 www.xilinx.com 5

Product Specification

Page 6

Introduction and Ordering Information

0

Package Marking

R

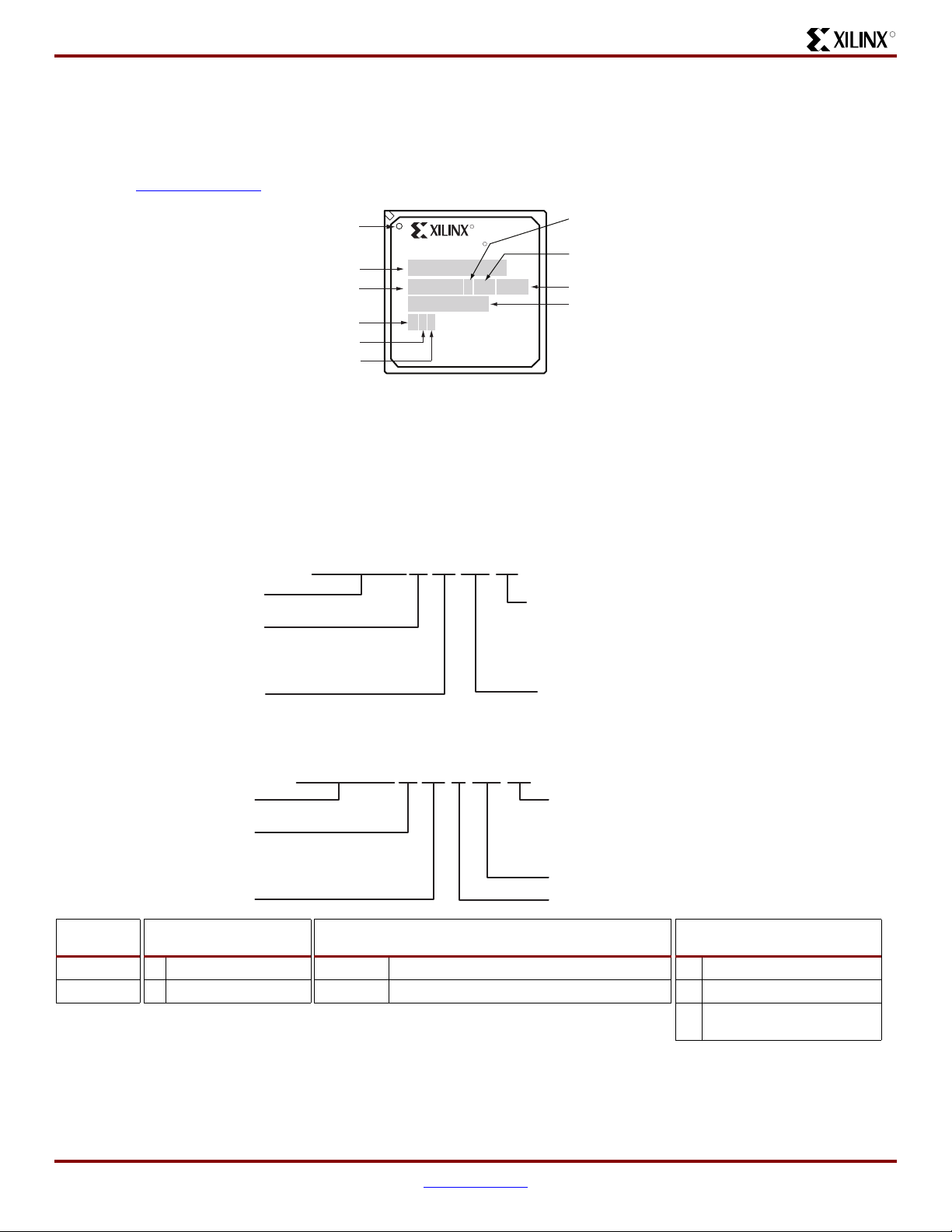

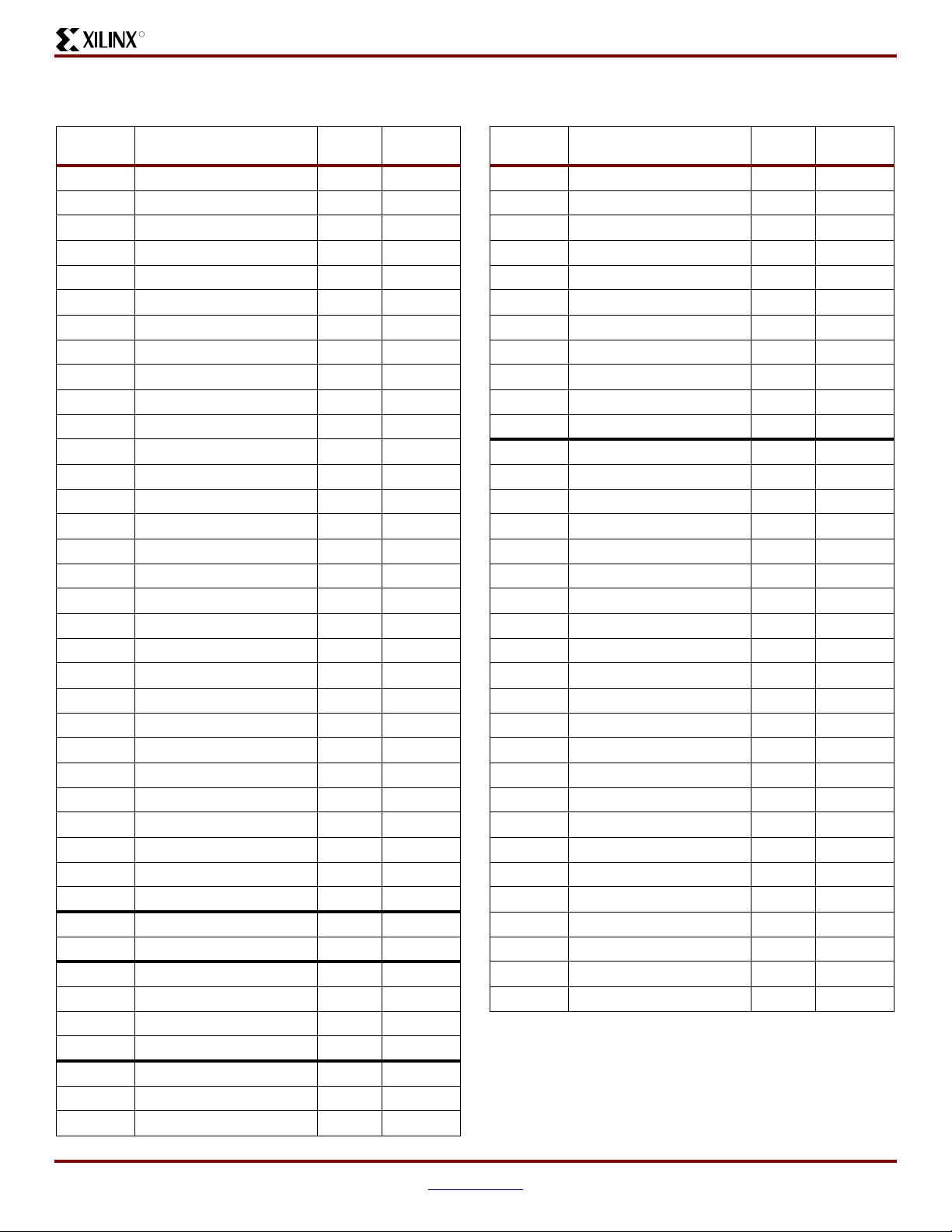

Figure 2 shows the top marking for Spartan-3A DSP

FPGAs. Use the seven digits of the Lot Code to access

The “5C” and “4I” Speed Grade/Temperature Range part

combinations may be dual marked as “5C/4I”.

additional information for a specific device using the Xilinx

web-based G

enealogy Viewer.

BGA Ball A1

Device Type

Package

Low-Power

(optional)

Speed Grade

Operating Range

Figure 2:

Spartan-3A DSP FPGA Package Marking Example

R

SPARTAN

R

XC3SD1800A

CSG484XGQ####

X#######X

L4 I

Mask Revision

Fabrication/

Process Code

Date Code

Lot Code

DS610-1_02_070607

Ordering Information

Spartan-3A DSP FPGAs are available in both standard and Pb-free packaging options for all device/package combinations.

The Pb-free packages include a ‘G’ character in the ordering code.

Standard Packaging

Example:

XC3SD1800A

-4 CS 484LI

Device Type

Speed Grade

-4: Standard Performance

-5: High Performance (Commercial only)

Package Type

Power/Temperature Range:

C = Commercial

I = Industrial

LI = Low-power Industrial (CS484 only)

Number of Pins

Pb-Free Packaging

Example:

XC3SD1800A -4 CS 484LI

Device Type

Speed Grade

-4: Standard Performance

-5: High Performance (Commercial only)

Package Type

Device Speed Grade Package Type / Number of Pins

XC3SD1800A

XC3SD3400A

–4 Standard Performance CS(G)484 484-ball Chip-Scale Ball Grid Array (CSBGA) C Commercial (0°C to 85°C)

–5 High Performance FG(G)676 676-ball Fine-Pitch Ball Grid Array (FBGA) I Industrial (–40°C to 100°C)

G

DS610-1_05_070607

Power/Temperature Range:

C = Commercial

I = Industrial

LI = Low-power Industrial (CSG484 on

Number of Pins

Pb-free

DS610-1_04_07

Power/Temperature Range

( T

LI Low-power Industrial

(–40°C to 100°C)

)

J

Notes:

1. The –5 speed grade is exclusively available in the Commercial temperature range.

2. The L Low-power option is exclusively available in the CS(G)484 package and Industrial temperature range.

6 www.xilinx.com DS610-1 (v2.0) July 16, 2007

Product Specification

Page 7

R

Revision History

The following table shows the revision history for this document.

Date Version Revision

04/02/07 1.0 Initial Xilinx release.

05/25/07 1.0.1 Minor edits.

06/18/07 1.2 Updated for Production release.

07/16/07 2.0 Added Low-power options.

Introduction and Ordering Information

DS610-1 (v2.0) July 16, 2007 www.xilinx.com 7

Product Specification

Page 8

Introduction and Ordering Information

R

This page intentionally left blank.

8 www.xilinx.com DS610-1 (v2.0) July 16, 2007

Product Specification

Page 9

<BL

R

Blue

>

Spartan-3A DSP FPGA Family:

Functional Description

DS610-2 (v2.0) July 16, 2007

Introduction

The functionality of the Spartan™-3A DSP FPGA family is

described in the following documents. The topics covered in

each guide are listed below.

• UG431

FPGAs User Guide

♦ XtremeDSP DSP48A Slices

♦ XtremeDSP DSP48A Pre-Adder

• UG331

♦ Clocking Resources

♦ Digital Clock Managers (DCMs)

♦ Block RAM

♦ Configurable Logic Blocks (CLBs)

♦ I/O Resources

♦ Programmable Interconnect

♦ ISE™ Software Design Tools

♦ IP Cores

♦ Embedded Processing and Control Solutions

♦ Pin Types and Package Overview

♦ Package Drawings

♦ Powering FPGAs

♦ Power Management

:

XtremeDSP DSP48A for Spartan-3A DSP

:

Spartan-3 Generation FPGA User Guide

- Distributed RAM

- SRL16 Shift Registers

- Carry and Arithmetic Logic

0

• UG332

:

Spartan-3 Generation Configuration User

Product Specification

Guide

♦ Configuration Overview

- Configuration Pins and Behavior

- Bitstream Sizes

♦ Detailed Descriptions by Mode

- Master Serial Mode using Xilinx Platform Flash

PROM

- Master SPI Mode using Commodity SPI Serial

Flash PROM

- Master BPI Mode using Commodity Parallel

NOR Flash PROM

- Slave Parallel (SelectMAP) using a Processor

- Slave Serial using a Processor

- JTAG Mode

♦ ISE iMPACT Programming Examples

♦ MultiBoot Reconfiguration

♦ Design Authentication using Device DNA

Create a Xilinx MySupport user account and sign up to

receive automatic E-mail notification whenever this data

sheet or the associated user guides are updated.

Revision History

The following table shows the revision history for this document.

Date Version Revision

04/02/07 1.0 Initial Xilinx release.

05/25/07 1.0.1 Minor edits.

06/18/07 1.2 Updated for Production release.

07/16/07 2.0 Added Low-power options; no changes to this module.

© 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

DS610-2 (v2.0) July 16, 2007 www.xilinx.com 9

Product Specification

All other trademarks are the proper ty of their respective owners. All specifications are subject to change without notice.

Page 10

Functional Description

R

This page intentionally left blank.

10 www.xilinx.com DS610-2 (v2.0) July 16, 2007

Product Specification

Page 11

<BL

R

Blue

>

Spartan-3A DSP FPGA Family:

DC and Switching Characteristics

DS610-3 (v2.0) July 16, 2007

0

Product Specification

DC Electrical Characteristics

In this section, specifications may be designated as

Advance, Preliminary, or Production. These terms are

defined as follows:

Advance: Initial estimates are based on simulation, early

characterization, and/or extrapolation from the

characteristics of other families. Values are subject to

change. Use as estimates, not for production.

Preliminary: Based on characterization. Further changes

are not expected.

Production: These specifications are approved once the

silicon has been characterized over numerous production

lots. Parameter values are considered stable with no future

changes expected.

Table 3:

Symbol Description Conditions Min Max Units

V

V

V

Notes:

1. For soldering guidelines, see UG112:

Absolute Maximum Ratings

CCINT

CCAUX

CCO

V

REF

V

V

ESD

T

T

STG

Guidelines for Pb-Free Packages

Internal supply voltage –0.5 1.32 V

Auxiliary supply voltage –0.5 3.75 V

Output driver supply voltage –0.5 3.75 V

Input reference voltage –0.5 V

Voltage applied to all User I/O pins and

IN

Dual-Purpose pins

Voltage applied to all Dedicated pins –0.5 4.6 V

Electrostatic Discharge Voltage Human body model – ±2000 V

Junction temperature –125°C

J

Storage temperature –65 150 °C

Driver in a high-impedance state

Charged device model

Machine model

Device Packaging and Thermal Characteristics

.

All parameter limits are representative of worst-case supply

voltage and junction temperature conditions. Unless

otherwise noted, the published parameter values apply

to all Spartan™-3A DSP devices. AC and DC

characteristics are specified using the same numbers

for both commercial and industrial grades.

Absolute Maximum Ratings

Stresses beyond those listed under Ta b l e 3 : Absolute

Maximum Ratings may cause permanent damage to the

device. These are stress ratings only; functional operation

of the device at these or any other conditions beyond those

listed under the Recommended Operating Conditions is not

implied. Exposure to absolute maximum conditions for

extended periods of time adversely affects device reliability.

+ 0.5 V

CCO

–0.95 4.6 V

– ±500 V

– ±200 V

and XAPP427:

Implementation and Solder Reflow

© 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 11

Product Specification

All other trademarks are the proper ty of their respective owners. All specifications are subject to change without notice.

Page 12

DC and Switching Characteristics

Power Supply Specifications

R

Table 4:

Supply Voltage Thresholds for Power-On Reset

Symbol Description Min Max Units

V

CCINTT

V

CCAUXT

V

CCO2T

Threshold for the V

Threshold for the V

Threshold for the V

supply 0.4 1.0 V

CCINT

supply 0.8 2.0 V

CCAUX

Bank 2 supply 0.8 2.0 V

CCO

Notes:

1. V

CCINT

, V

CCAUX

, and V

supplies to the FPGA can be applied in any order. However, the FPGA’s configuration source (Platform Flash,

CCO

SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration

source. Apply V

last for lowest overall power consumption (see the UG331 chapter titled "Powering Spartan-3 Generation FPGAs" for

CCINT

more information).

2. To ensure successful power-on, V

no dips at any point.

Table 5:

Supply Voltage Ramp Rate

CCINT

Bank 2, and V

CCO

supplies must rise through their respective threshold-voltage ranges with

CCAUX

, V

Symbol Description Min Max Units

V

CCINTR

V

CCAUXR

V

CCO2R

Ramp rate from GND to valid V

Ramp rate from GND to valid V

Ramp rate from GND to valid V

supply level 0.2 100 ms

CCINT

supply level 0.2 100 ms

CCAUX

Bank 2 supply level 0.2 100 ms

CCO

Notes:

1. V

CCINT

, V

CCAUX

, and V

supplies to the FPGA can be applied in any order. However, the FPGA’s configuration source (Platform Flash,

CCO

SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration

source. Apply V

last for lowest overall power consumption (see the UG331 chapter titled "Powering Spartan-3 Generation FPGAs" for

CCINT

more information).

2. To ensure successful power-on, V

no dips at any point.

CCINT

, V

CCO

Bank 2, and V

supplies must rise through their respective threshold-voltage ranges with

CCAUX

Table 6:

Supply Voltage Levels Necessary for Preserving CMOS Configuration Latch (CCL) Contents and RAM

Data

Symbol Description Min Units

V

V

DRINT

V

DRAUX

level required to retain CMOS Configuration Latch (CCL) and RAM data 1.0 V

CCINT

V

level required to retain CMOS Configuration Latch (CCL) and RAM data 2.0 V

CCAUX

General Recommended Operating Conditions

Table 7:

Notes:

1. This V

2. Measured between 10% and 90% V

General Recommended Operating Conditions

Symbol Description Min Nominal Max Units

T

J

V

CCINT

(1)

V

CCO

V

range specific to each of the single-ended I/O standards, and Ta b l e 1 2 lists that specific to the differential standards.

Auxiliary supply voltage V

CCAUX

T

IN

range spans the lowest and highest operating voltages for all supported I/O standards. Table 10 lists the recommended V

CCO

Junction temperature Commercial 0 -85°C

Industrial –40

-100°C

Internal supply voltage 1.140 1.200 1.260 V

Output driver supply voltage 1.100 -3.600V

= 2.5 2.250 2.500 2.750 V

CCAUX

Input signal transition time

.

CCO

V

(2)

= 3.3 3.000 3.300 3.600 V

CCAUX

- - 500 ns

CCO

12 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 13

R

General DC Characteristics for I/O Pins

DC and Switching Characteristics

Table 8:

General DC Characteristics of User I/O, Dual-Purpose, and Dedicated Pins

Symbol Description Test Conditions Min Typ Max Units

I

I

RPU

R

I

RPD

R

I

R

I

HS

PU

PD

REF

C

Leakage current at User I/O,

L

Input-only, Dual-Purpose, and

Dedicated pins, FPGA powered

Leakage current on pins during

hot socketing, FPGA unpowered

(2)

Current through pull-up resistor

at User I/O, Dual-Purpose,

Input-only, and Dedicated pins.

Dedicated pins are powered by

V

(2)

Equivalent pull-up resistor value

CCAUX

.

at User I/O, Dual-Purpose,

Input-only, and Dedicated pins

(based on I

(2)

Current through pull-down

per Note 2)

RPU

resistor at User I/O,

Dual-Purpose, Input-only, and

Dedicated pins

(2)

Equivalent pull-down resistor

value at User I/O, Dual-Purpose,

Input-only, and Dedicated pins

(based on I

V

current per pin All V

REF

Input capacitance -3-10pF

IN

Resistance of optional differential

DT

termination circuit within a

per Note 2)

RPD

differential I/O pair. Not available

on Input-only pairs.

Driver is in a high-impedance state,

VIN = 0V or V

max, sample-tested

CCO

All pins except INIT_B, PROG_B, DONE, and JTAG pins

when PUDC_B = 1.

INIT_B, PROG_B, DONE, and JTAG pins or other pins

when PUDC_B = 0.

VIN = GND V

VIN = GND V

V

CCAUX

V

CCAUX

V

VIN = V

CCO

CCO

= 3.0V to 3.6V VIN = 3.0V to 3.6V 5.5 10.4 20.8 kΩ

= 2.25V to 2.75V VIN = 3.0V to 3.6V 7.9 16.0 35.0 kΩ

= 3.3V ± 10%

or V

CCO

or V

V

CCO

V

CCO

V

CCO

V

CCO

CCO

V

CCO

V

CCO

V

CCO

V

CCO

V

CCAUX

V

CCAUX

V

IN

V

IN

V

IN

V

= 1.14V to 1.26V 2.4 4.5 8.1 kΩ

IN

V

IN

V

IN

V

IN

V

= 1.14V to 1.26V 3.0 6.0 12.5 kΩ

IN

levels –10 -+10μA

CCO

= 3.0V to 3.6V –151 –315 –710 μA

CCAUX

= 2.3V to 2.7V –82 –182 –437 μA

CCAUX

= 1.7V to 1.9V –36 –88 –226 μA

= 1.4V to 1.6V –22 –56 –148 μA

= 1.14V to 1.26V –11 –31 –83 μA

= 3.0V to 3.6V 5.1 11.4 23.9 kΩ

= 2.3V to 2.7V 6.2 14.8 33.1 kΩ

= 1.7V to 1.9V 8.4 21.6 52.6 kΩ

= 1.4V to 1.6V 10.8 28.4 74.0 kΩ

= 1.14V to 1.26V 15.3 41.1 119.4 kΩ

= 3.0V to 3.6V 167 346 659 μA

= 2.25V to 2.75V

= 2.3V to 2.7V 4.1 7.8 15.7 kΩ

= 1.7V to 1.9V 3.0 5.7 11.1 kΩ

= 1.4V to 1.6V 2.7 5.1 9.6 kΩ

= 2.3V to 2.7V 5.9 12.0 26.3 kΩ

= 1.7V to 1.9V 4.2 8.5 18.6 kΩ

= 1.4V to 1.6V 3.6 7.2 15.7 kΩ

LVDS_33, MINI_LVDS_33,

RSDS_33

= 2.5V ± 10%

V

CCO

LVDS_25, MINI_LVDS_25,

–10 -+10μA

–10

Add IHS + I

-+10μA

RPU

μA

100 225 457 μA

90 100 115 Ω

90 110 – Ω

RSDS_25

Notes:

1. The numbers in this table are based on the conditions set forth in Ta bl e 7 .

2. This parameter is based on characterization. The pull-up resistance R

PU

= V

CCO/IRPU

. The pull-down resistance RPD = VIN / I

RPD

.

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 13

Product Specification

Page 14

DC and Switching Characteristics

Quiescent Current Requirements

R

Table 9:

Symbol Description Device Power Typical

I

CCINTQ

Quiescent Supply Current Characteristics

Quiescent V

supply current XC3SD1800A C,I 55 390 500 mA

CCINT

LI 45

(2)

Commercial

Maximum

(2)

Industrial

Maximum

- 175 mA

(2)

Units

XC3SD3400A C,I 80 550 725 mA

I

CCOQ

Quiescent V

LI 70

supply current XC3SD1800A C,I 0.4 4 5 mA

CCO

LI 0.2

- 300 mA

-5mA

XC3SD3400A C,I 0.4 4 5 mA

LI 0.2 -5mA

I

CCAUXQ

Quiescent V

supply current XC3SD1800A C,I 42 90 110 mA

CCAUX

LI 38

-72mA

XC3SD3400A C,I 70 130 160 mA

LI 65

- 105 mA

Notes:

1. The numbers in this table are based on the conditions set forth in Tab le 7 .

2. Quiescent supply current is measured with all I/O drivers in a high-impedance state and with all pull-up/pull-down resistors at the I/O pads

disabled. Typical values are characterized using typical devices at ambient room temperature (T

= 2.5V). The maximum limits are tested for each device at the respective maximum specified junction temperature and at maximum

V

CCAUX

voltage limits with V

is, a design with no functional elements instantiated). For conditions other than those described above (for example, a design including

functional elements), measured quiescent current levels will be different than the values in the table.

3. There are two recommended ways to estimate the total power consumption (quiescent plus dynamic) for a specific design: a) The

Spartan-3A DSP

XPower Analyzer uses a netlist as input to provide maximum estimates as well as more accurate typical estimates.

4. The maximum numbers in this table indicate the minimum current each power rail requires in order for the FPGA to power-on successfully.

5. For information on the power-saving Suspend mode, see XAPP480

typically saves 40% total power consumption compared to quiescent current.

= 1.26V, V

CCINT

FPGA XPower Estimator provides quick, approximate, typical estimates, and does not require a netlist of the design. b)

= 3.6V, and V

CCO

= 3.6V. The FPGA is programmed with a “blank” configuration data file (that

CCAUX

:

Using Suspend Mode in Spartan-3 Generation FPGAs

of 25°C at V

A

CCINT

= 1.2V, V

= 3.3V, and

CCO

. Suspend mode

14 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 15

R

Single-Ended I/O Standards

DC and Switching Characteristics

Table 10:

Recommended Operating Conditions for User I/Os Using Single-Ended Standards

IOSTANDARD

Attribute

for Drivers

V

CCO

Min (V) Nom (V) Max (V) Min (V) Nom (V) Max (V) Max (V) Min (V)

(2)

V

REF

LVTTL 3.0 3.3 3.6

LV CM O S 33

LV CM O S 25

LV CM O S 18

LV CM O S 15

LV CM O S 12

(4)

(4,5)

(4)

(4)

(4)

3.0 3.3 3.6 0.8 2.0

2.3 2.5 2.7 0.7 1.7

1.65 1.8 1.95 0.38 0.8

V

is not used for

1.4 1.5 1.6 0.38 0.8

REF

these I/O standards

1.1 1.2 1.3 0.38 0.8

PCI33_3 3.0 3.3 3.6 0.3 • V

PCI66_3 3.0 3.3 3.6 0.3 • V

PCIX 3.0 3.3 3.6 0.35 • V

HSTL_I 1.4 1.5 1.6 0.68 0.75 0.9 V

HSTL_III 1.4 1.5 1.6

-0.9 -V

HSTL_I_18 1.7 1.8 1.9 0.8 0.9 1.1 V

HSTL_II_18 1.7 1.8 1.9

HSTL_III_18 1.7 1.8 1.9

-0.9 -V

-1.1 -V

SSTL18_I 1.7 1.8 1.9 0.833 0.900 0.969 V

SSTL18_II 1.7 1.8 1.9 0.833 0.900 0.969 V

SSTL2_I 2.3 2.5 2.7 1.15 1.25 1.38 V

SSTL2_II 2.3 2.5 2.7 1.15 1.25 1.38 V

SSTL3_I 3.0 3.3 3.6 1.3 1.5 1.7 V

SSTL3_II 3.0 3.3 3.6 1.3 1.5 1.7 V

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

Notes:

1. Descriptions of the symbols used in this table are as follows:

– the supply voltage for output drivers

V

CCO

– the reference voltage for setting the input switching threshold

V

REF

– the input voltage that indicates a Low logic level

V

IL

– the input voltage that indicates a High logic level

V

IH

2. In general, the V

and for PCI I/O standards.

rails supply only output drivers, not input circuits. The exceptions are for LVCMOS25 inputs when V

CCO

3. For device operation, the maximum signal voltage (VIH max) can be as high as VIN max. See Tab l e 3 .

4. There is approximately 100 mV of hysteresis on inputs using LVCMOS33 and LVCMOS25 I/O standards.

5. All Dedicated pins (PROG_B, DONE, SUSPEND, TCK, TDI, TDO, and TMS) draw power from the V

LVCMOS33 standard depending on V

When using these pins as part of a standard 2.5V configuration interface, apply 2.5V to the V

well as throughout configuration.

. The Dual-Purpose configuration pins use the LVCMOS25 standard before the User mode.

CCAUX

lines of Banks 0, 1, and 2 at power-on as

CCO

rail and use the LVCMOS25 or

CCAUX

V

IL

V

0.8 2.0

CCO

CCO

CCO

- 0.1 V

- 0.1 V

- 0.1 V

- 0.1 V

- 0.1 V

- 0.125 V

- 0.125 V

- 0.150 V

- 0.150 V

- 0.2 V

- 0.2 V

0.5 • V

0.5 • V

0.5 • V

REF

REF

REF

REF

CCAUX

REF

REF

REF

REF

REF

+ 0.125

+ 0.125

+ 0.150

+ 0.150

REF

REF

= 3.3V range

IH

CCO

CCO

CCO

+ 0.1

+ 0.1

+ 0.1

+ 0.1

+ 0.1

+ 0.2

+ 0.2

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 15

Product Specification

Page 16

DC and Switching Characteristics

R

Table 11:

DC Characteristics of User I/Os Using

Single-Ended Standards

Conditions

I

IOSTANDARD

Attribute

(3)

LVTTL

LV CM O S 33

LV CM O S 25

LV CM O S 18

LV CM O S 15

LV CM O S 12

12 12 –12

16 16 –16

24 24 –24

(3)

12 12 –12

16 16 –16

24

(3)

12 12 –12

16

24

(3)

12

16

(3)

8

12

(3)

4

6

OL

(mA)

22–2 0.4 2.4

44–4

66–6

88–8

22–2 0.4 V

44–4

66–6

88–8

(4)

24 –24

22–2 0.4 V

44–4

66–6

88–8

(4)

16 –16

(4)

24 –24

2 2 –2 0.45 V

44–4

66–6

88–8

(4)

12 –12

(4)

16 –16

2 2 –2 0.25 • V

44–4

66–6

(4)

8–8

(4)

12 –12

22–2 0.4 V

(4)

4–4

(4)

6–6

Test

I

OH

(mA)

Logic Level

Characteristics

V

OL

Max (V)

CCO

V

OH

Min (V)

– 0.4

CCO

– 0.4

CCO

– 0.45

CCO

0.75 • V

– 0.4

CCO

CCO

Table 11:

Single-Ended Standards

IOSTANDARD

PCI33_3

PCI66_3

PCIX 1.5 –0.5 10% V

HSTL_I

HSTL_III

HSTL_I_18 8 –8 0.4 V

HSTL_II_18

HSTL_III_18 24 –8 0.4 V

SSTL18_I 6.7 –6.7

SSTL18_II

SSTL2_I 8.1 –8.1 V

SSTL2_II

SSTL3_I 8 –8 V

SSTL3_II

DC Characteristics of User I/Os Using

(Continued)

Test

Attribute

(5)

(5)

(4)

(4)

(4)

(4)

(4)

(4)

Conditions

I

I

OL

(mA)

OH

(mA)

1.5 –0.5 10% V

1.5 –0.5 10% V

8–8 0.4 V

24 –8 0.4 V

16 –16 0.4 V

13.4 –13.4

16.2 –16.2 VTT – 0.80 VTT + 0.80

16 –16 VTT – 0.8 VTT + 0.8

Characteristics

V

OL

Max (V)

V

– 0.475 VTT + 0.475

TT

V

– 0.475 VTT + 0.475

TT

– 0.61 VTT + 0.61

TT

– 0.6 VTT + 0.6

TT

Logic Level

V

Min (V)

90% V

CCO

90% V

CCO

90% V

CCO

CCO

CCO

CCO

CCO

CCO

OH

CCO

CCO

CCO

- 0.4

- 0.4

- 0.4

- 0.4

- 0.4

Notes:

1. The numbers in this table are based on the conditions set forth in

Tab l e 7 and Table 10.

2. Descriptions of the symbols used in this table are as follows:

I

– the output current condition under which V

OL

– the output current condition under which V

I

OH

V

– the output voltage that indicates a Low logic level

OL

– the output voltage that indicates a High logic level

V

OH

V

– the input voltage that indicates a Low logic level

IL

– the input voltage that indicates a High logic level

V

IH

V

– the supply voltage for output drivers

CCO

– the reference voltage for setting the input switching threshold

V

REF

V

– the voltage applied to a resistor termination

TT

is tested

OL

is tested

OH

3. For the LVCMOS and LVTTL standards: the same VOL and VOH

limits apply for both the Fast and Slow slew attributes.

4. These higher-drive output standards are supported only on

FPGA banks 1 and 3. Inputs are unrestricted. See the chapter

"Using I/O Resources" in UG331

.

5. Tested according to the relevant PCI specifications.

16 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 17

R

Differential I/O Standards

Internal

Logic

GND level

V

INN

V

INP

50%

V

ICM

V

= Input common mode voltage =

ICM

V

= Differential input voltage =

ID

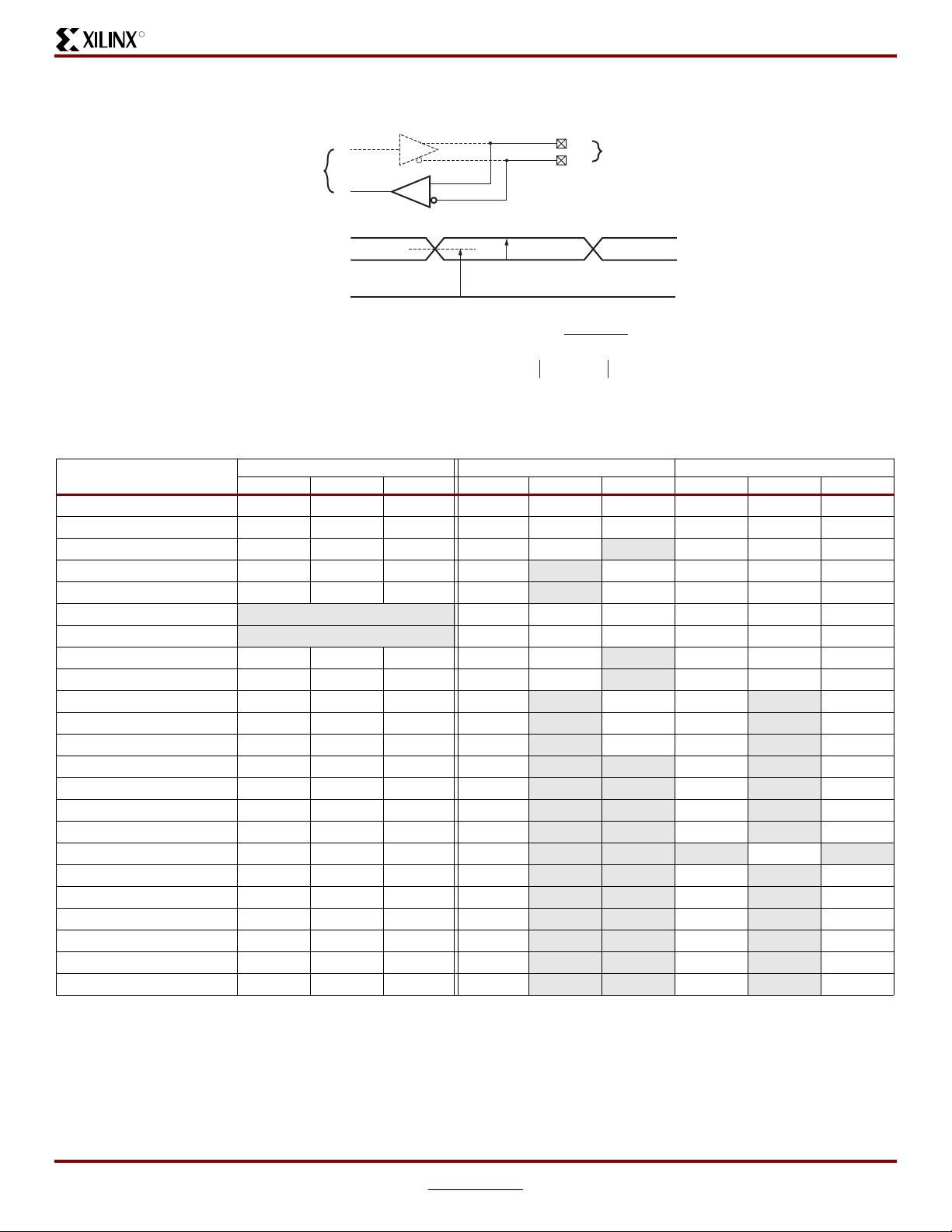

Figure 3:

Differential Input Voltages

DC and Switching Characteristics

V

INP

V

INN

V

ID

V

V

INP

P

N

INP

- V

+ V

2

INN

Differential

I/O Pair Pins

INN

DS610-3_03_061507

Table 12:

IOSTANDARD Attribute

LV DS _2 5

LV DS _3 3

BLVDS_25

MINI_LVDS_25

MINI_LVDS_33

LVPECL_25

LVPECL_33

RSDS_25

RSDS_33

TMDS_33

PPDS_25

PPDS_33

DIFF_HSTL_I_18

DIFF_HSTL_II_18

DIFF_HSTL_III_18

DIFF_HSTL_I

DIFF_HSTL_III

DIFF_SSTL18_I

DIFF_SSTL18_II

DIFF_SSTL2_I

DIFF_SSTL2_II

DIFF_SSTL3_I

DIFF_SSTL3_II

Recommended Operating Conditions for User I/Os Using Differential Signal Standards

(1)

V

ID

– –0.8–1.1

– –0.8–1.1

– –0.68–0.9

– – –0.9–

– –0.7–1.1

– –1.0–1.5

– –1.1–1.9

– –1.1–1.9

(3)

(3)

(4)

(3)

(3)

(3,4,7)

(3)

(3)

(5)

(5)

(3)

(3)

(8)

(8)

(8)

V

for Drivers

CCO

Min (V) Nom (V) Max (V) Min (mV) Nom (mV) Max (mV) Min (V) Nom (V) Max (V)

2.25 2.5 2.75 100 350 600 0.3 1.25 2.35

3.0 3.3 3.6 100 350 600 0.3 1.25 2.35

2.25 2.5 2.75 100 300 – 0.3 1.3 2.35

2.25 2.5 2.75 200 – 600 0.3 1.2 1.95

3.0 3.3 3.6 200 – 600 0.3 1.2 1.95

Inputs Only 100 800 1000 0.3 1.2 1.95

Inputs Only 100 800 1000 0.3 1.2 2.8

2.25 2.5 2.75 100 200 – 0.3 1.2 1.5

3.0 3.3 3.6 100 200 – 0.3 1.2 1.5

3.14 3.3 3.47 150 – 1200 2.7 –3.23

2.25 2.5 2.75 100 –4000.2 –2.3

3.0 3.3 3.6 100 –4000.2 –2.3

1.7 1.8 1.9 100

1.7 1.8 1.9 100 – –0.8–1.1

1.7 1.8 1.9 100

1.4 1.5 1.6 100

1.4 1.5 1.6 100

1.7 1.8 1.9 100

1.7 1.8 1.9 100 – –0.7–1.1

2.3 2.5 2.7 100

2.3 2.5 2.7 100 – –1.0–1.5

3.0 3.3 3.6 100

3.0 3.3 3.6 100

(2)

V

ICM

Notes:

1. The V

2. V

3. These true differential output standards are supported only on FPGA banks 0 and 2. Inputs are unrestricted. See the chapter "Using I/O Resources" in UG331.

4. See "External Termination Requirements for Differential I/O."

5. LVPECL is supported on inputs only, not outputs. Requires V

6. LVPECL_33 maximum V

7. Requires V

8. These higher-drive output standards are supported only on FPGA banks 1 and 3. Inputs are unrestricted. See the chapter "Using I/O Resources" in UG331.

9. V

standards do not use V

rails supply only differential output drivers, not input circuits.

CCO

must be less than V

ICM

= 3.3V ± 10%. (V

CCAUX

inputs are used for the DIFF_SSTL and DIFF_HSTL standards. The V

REF

REF

CCAUX

ICM

.

= V

.

CCAUX

– (VID/2).

CCAUX

- 300 mV) ≤V

ICM

CCAUX

≤ (V

ICM

=3.3V ± 10%.

- 37 mV).

REF

settings are the same as for the single-ended versions in Table 11. Other differential

(6)

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 17

Product Specification

Page 18

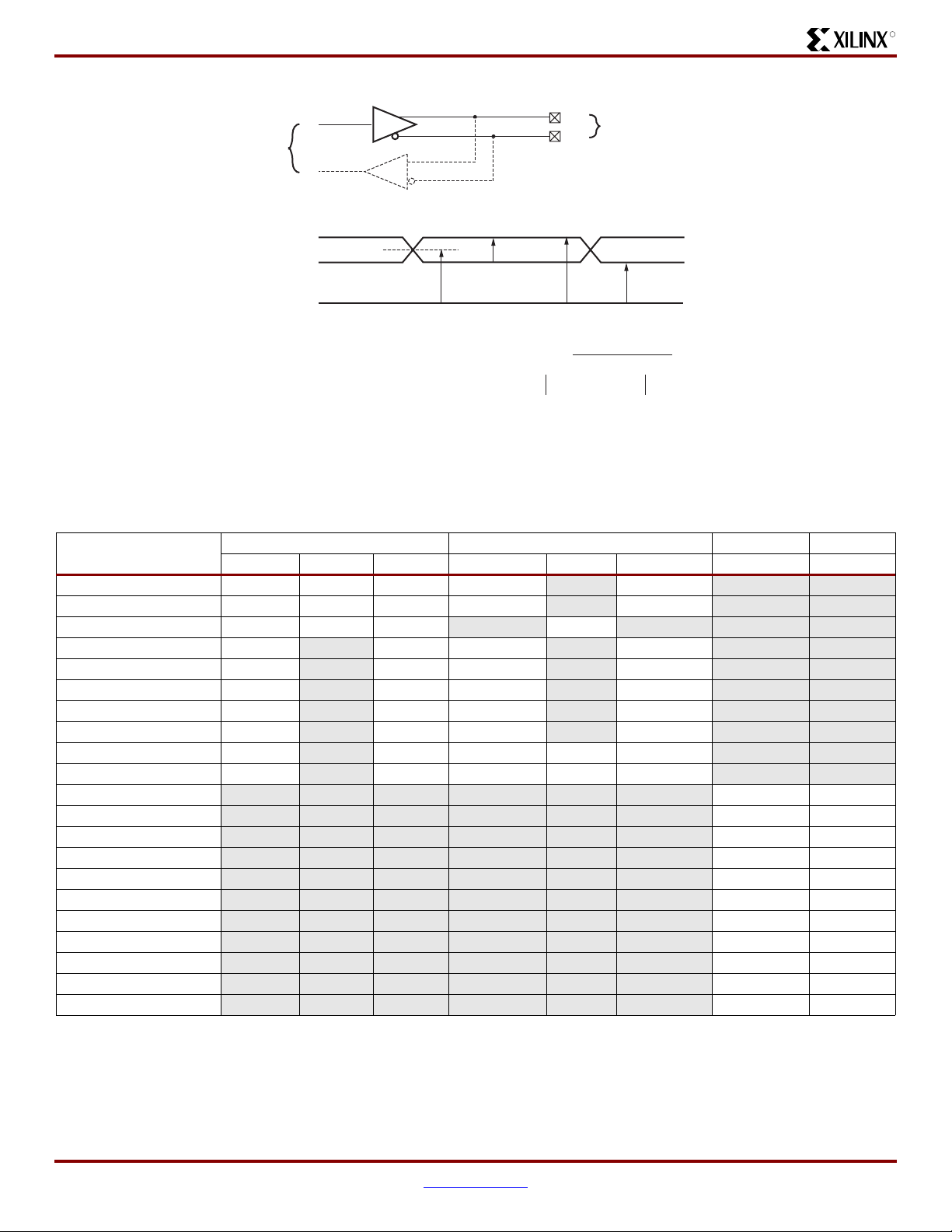

DC and Switching Characteristics

Internal

Logic

V

OUTN

V

OUTP

GND level

V

OUTP

V

OUTN

50%

V

OCM

V

= Output common mode voltage =

OCM

V

= Output differential voltage =

OD

V

= Output voltage indicating a High logic level

OH

= Output voltage indicating a Low logic level

V

OL

Figure 4:

Differential Output Voltages

V

OD

V

V

OUTP

OH

P

N

V

OUTP

- V

Differential

I/O Pair Pins

V

OL

+ V

OUTN

2

OUTN

DS312-3_03_102406

R

Table 13:

IOSTANDARD Attribute

LVDS_25 247 350 454 1.125

LVDS_33 247 350 454 1.125

BLVDS_25 240 350 460

MINI_LVDS_25 300

MINI_LVDS_33 300

RSDS_25 100

RSDS_33 100

TMDS_33 400

PPDS_25 100

PPDS_33 100

DIFF_HSTL_I_18

DIFF_HSTL_II_18

DIFF_HSTL_III_18

DIFF_HSTL_I

DIFF_HSTL_III

DIFF_SSTL18_I

DIFF_SSTL18_II

DIFF_SSTL2_I

DIFF_SSTL2_II

DIFF_SSTL3_I

DIFF_SSTL3_II

DC Characteristics of User I/Os Using Differential Signal Standards

V

OD

Min (mV) Typ (mV) Max (mV) Min (V) Typ (V) Max (V) Min (V) Max (V)

–

–

–

–

–

–

–

–

– – – – – –

– – – – – –

– – – – – –

– – – – – –

– – – – – –

– – – – – –

– – – – – –

– – – – – –

– – – – – –

– – – – – –

– – – – – –

600 1.0

600 1.0

400 1.0

400 1.0

800 V

– 0.405 –V

CCO

400 0.5 0.8 1.4

400 0.5 0.8 1.4

V

1.30

OCM

–

–

–

–

–

–

V

OH

1.375

1.375

– – –

1.4

1.4

1.4

1.4

– 0.190

CCO

– –

– –

– –

– –

– –

– –

– –

– –

– –

V

– 0.4 0.4

CCO

V

– 0.4 0.4

CCO

V

– 0.4 0.4

CCO

V

– 0.4 0.4

CCO

V

– 0.4 0.4

CCO

VTT + 0.475 VTT – 0.475

VTT + 0.475 VTT – 0.475

VTT + 0.61 VTT – 0.61

VTT + 0.81 VTT – 0.81

V

+ 0.6 VTT - 0.6

TT

V

+ 0.8 VTT - 0.8

TT

V

OL

Notes:

1. The numbers in this table are based on the conditions set forth in Ta bl e 7 and Ta bl e 1 2 .

2. See "External Termination Requirements for Differential I/O."

3. Output voltage measurements for all differential standards are made with a termination resistor (RT) of 100Ω across the N and P pins of the

differential signal pair.

4. At any given time, no more than two of the following differential output standards can be assigned to an I/O bank: LVDS_25, RSDS_25,

MINI_LVDS_25, PPDS_25 when V

=2.5V, or LVDS_33, RSDS_33, MINI_LVDS_33, TMDS_33, PPDS_33 when V

CCO

CCO

= 3.3V

18 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 19

R

External Termination Requirements for Differential I/O

LVDS, RSDS, MINI_LVDS, and PPDS I/O Standards

Bank 0 and 2 Any Bank

Bank 0

VCCO = 3.3V

LVD S_33,

MINI_LVDS_33,

RSDS_33,

PPDS_33

VCCO = 3.3V

LVD S_33,

MINI_LVDS_33,

RSDS_33,

PPDS_33

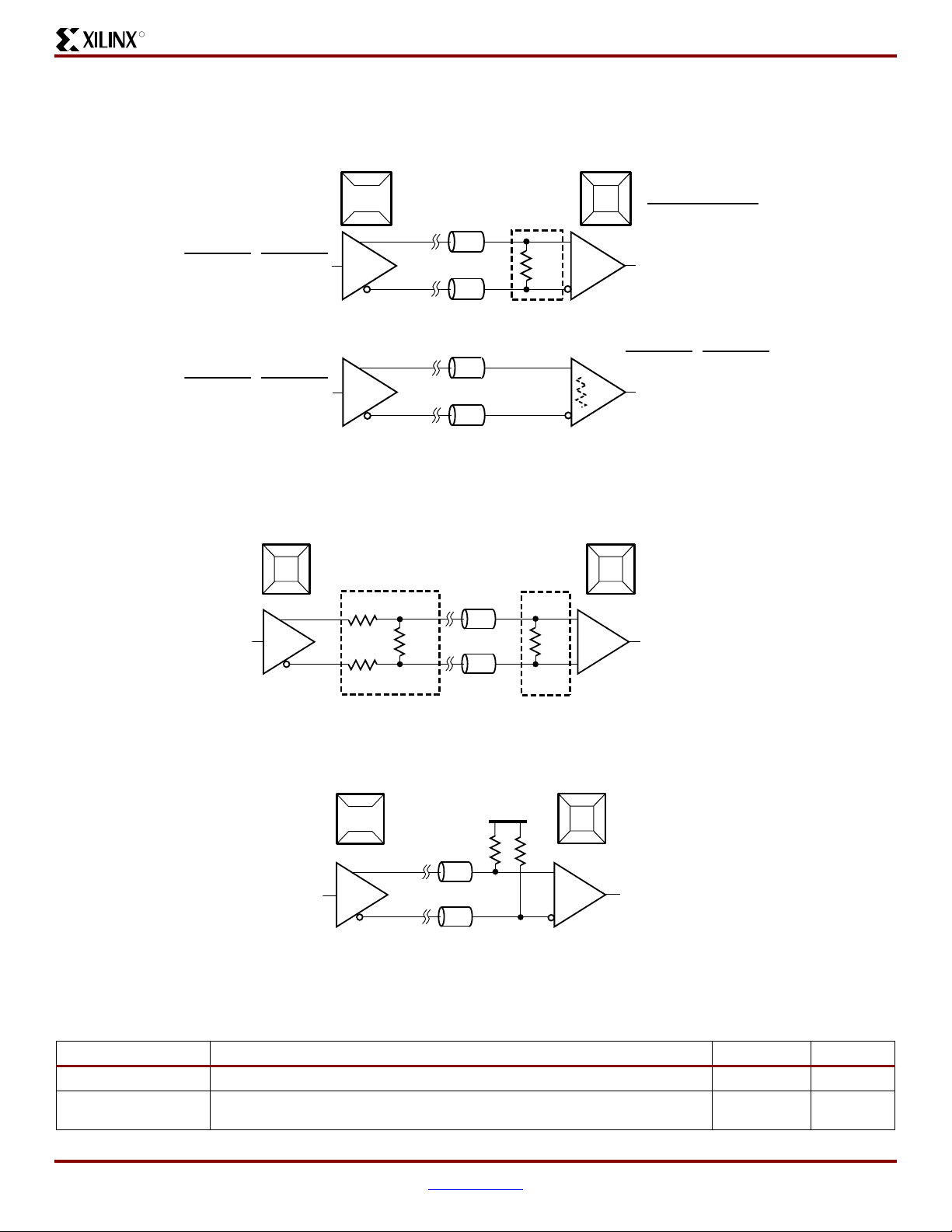

Figure 5:

Bank 2

VCCO = 2.5V

LVD S_25,

MINI_LVDS_25,

RSDS_25,

PPDS_25

a) Input-only differential pairs or pairs not using DIFF_TERM=Yes constraint

VCCO = 2.5V

LVD S_25,

MINI_LVDS_25,

RSDS_25,

PPDS_25

b) Differential pairs using DIFF_TERM=Yes constraint

External Input Termination for LVDS, RSDS, MINI_LVDS, and PPDS I/O Standards

Z0 = 50Ω

Z

0 = 50Ω

Z0 = 50Ω

Z

0 = 50Ω

1

/ th of Bourns

4

Part Number

CAT16-PT4F4

100Ω

DIFF_TERM=No

DIFF_TERM=Yes

Bank 0

Bank 3

Bank 2

R

DT

DC and Switching Characteristics

Bank 1

No VCCO Restrictions

LVD S_33, LVDS_25,

MINI_LVDS_33,

MINI_LVDS_25,

RSDS_33, RSDS_25,

PPDS_33, PPDS_25

VCCO = 3.3V

LVD S_33,

MINI_LVDS_33,

RSDS_33,

PPDS_33

VCCO = 2.5V

LVD S_25,

MINI_LVDS_25,

RSDS_25,

PPDS_25

DS529-3_09_020107

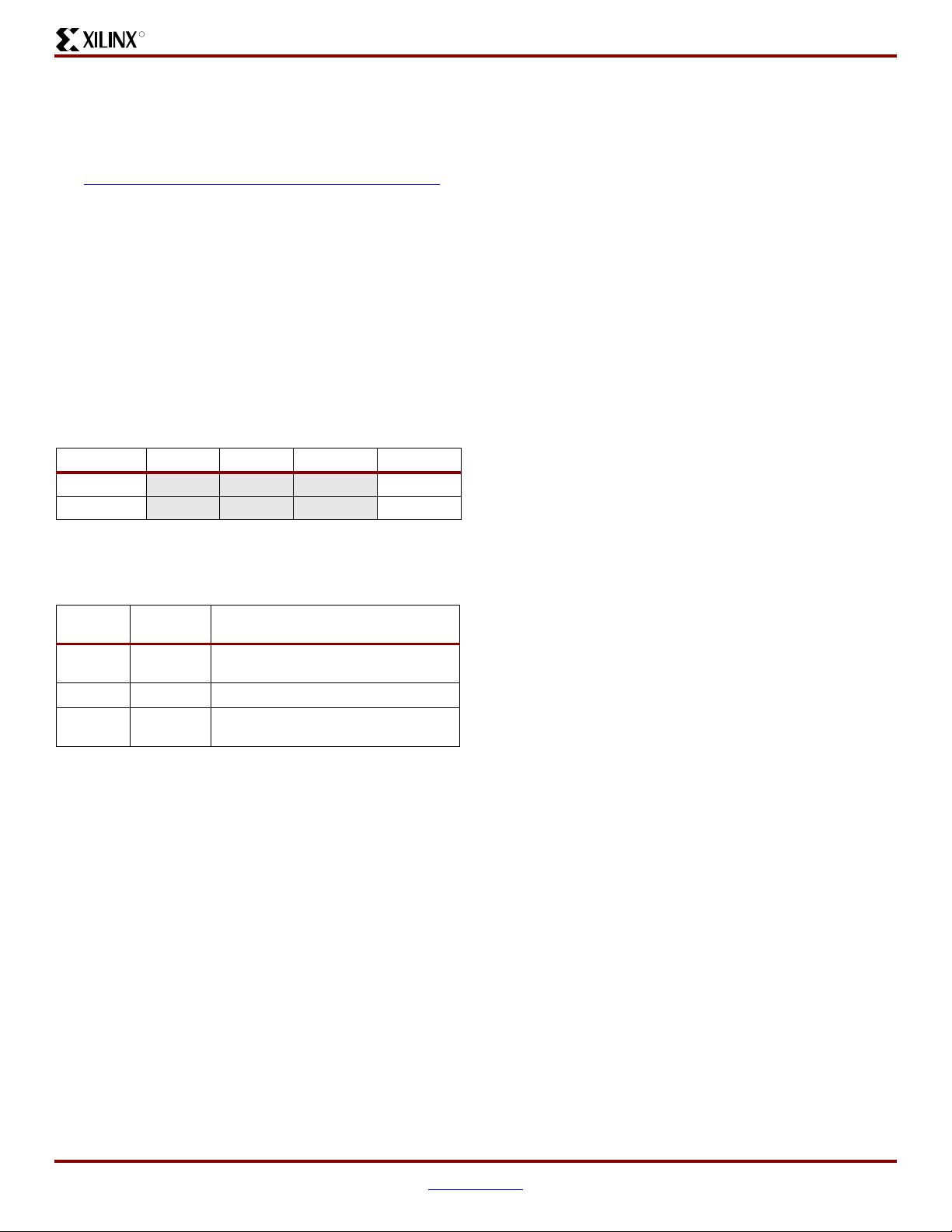

BLVDS_25 I/O Standard

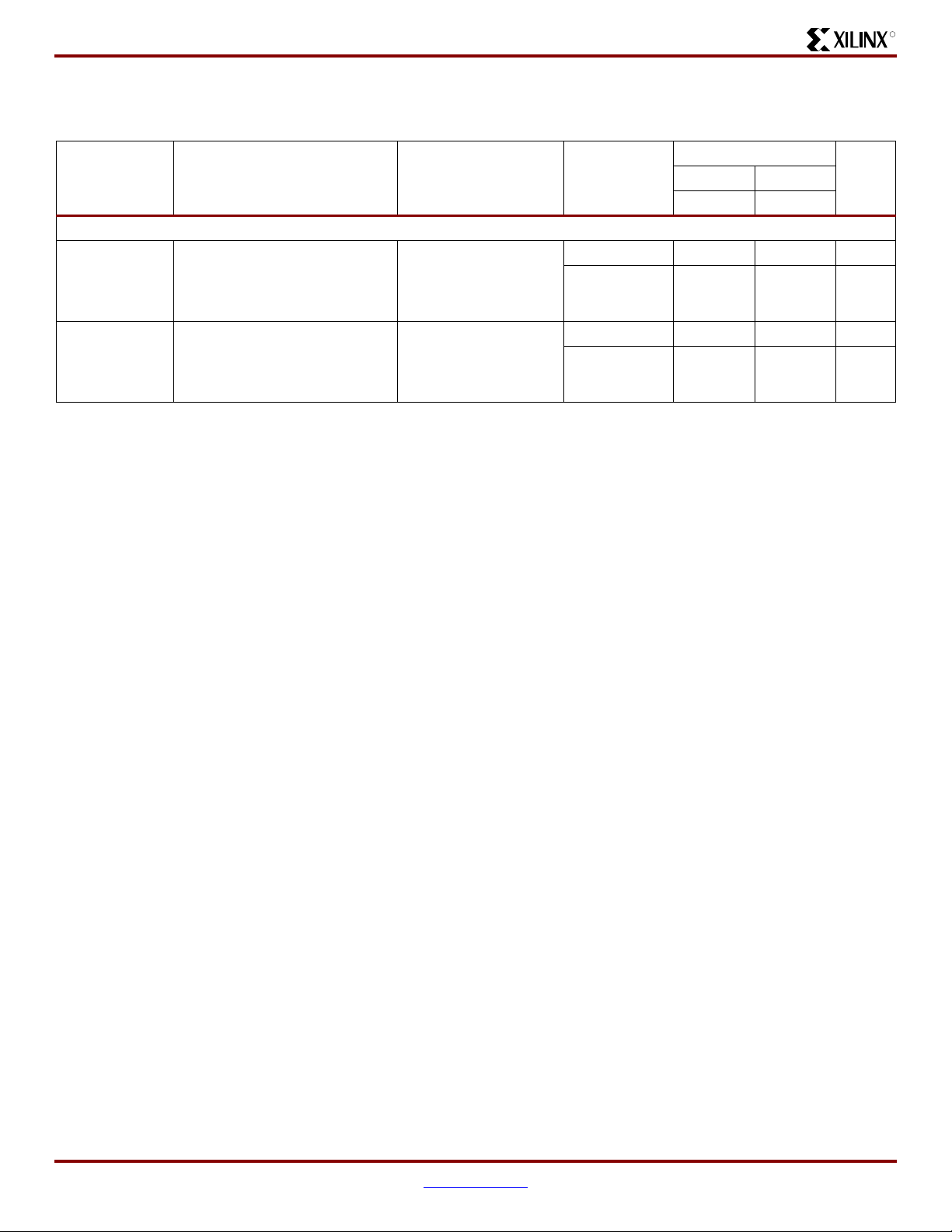

TMDS_33 I/O Standard

Any Bank

Bank 0

Bank 3

Bank 2

VCCO = 2.5V

BLVDS_25

Figure 6:

Figure 7:

Any Bank

Bank 1

1

/ th of Bourns

4

Part Number

CAT16-LV4F12

165Ω

140Ω

Z0 = 50Ω

Z

0 = 50Ω

1

/ th of Bourns

4

Part Number

CAT16-PT4F4

100Ω

Bank 0

Bank 1

Bank 3

Bank 2

No VCCO Requirement

BLVDS_25

165Ω

DS529-3_07_020107

External Termination Resistors for BLVDS_25 I/O Standard

50Ω

Any Bank

Bank 0

Bank 3

Bank 2

V

CCAUX

DS529-3_08_020107DVI/HDMI cable

Bank 1

= 3.3V

Bank 0 and 2

Bank 0

3.3V

Bank 2

V

CCO

= 3.3V

TMDS_33 TMDS_33

50Ω

External Input Resistors Required for TMDS_33 I/O Standard

Device DNA Data Retention, Read Endurance

Table 14:

DNA_RETENTION Data retention, continuous usage 10 Years

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 19

Product Specification

Device DNA Identifier Memory Characteristics

Symbol Description Minimum Units

DNA_CYCLES

Number of READ operations or JTAG ISC_DNA read operations. Unaffected by

HOLD or SHIFT operations.

30,000,000

Read

cycles

Page 20

DC and Switching Characteristics

Switching Characteristics

R

All Spartan-3A DSP FPGAs ship in two speed grades: –4

and the higher performance –5. Switching characteristics in

this document are designated as Preview, Advance,

Preliminary, or Production, as shown in Tab le 1 5 . Each

category is defined as follows:

Preview: These specifications are based on estimates only

and should not be used for timing analysis.

Advance: These specifications are based on simulations

only and are typically available soon after establishing

FPGA specifications. Although speed grades with this

designation are considered relatively stable and

conservative, some under-reporting might still occur.

Preliminary: These specifications are based on complete

early silicon characterization. Devices and speed grades

with this designation are intended to give a better indication

of the expected performance of production silicon. The

probability of under-reporting preliminary delays is greatly

reduced compared to Advance data.

Production: These specifications are approved once

enough production silicon of a particular device family

member has been characterized to provide full correlation

between speed files and devices over numerous production

lots. There is no under-reporting of delays, and customers

receive formal notification of any subsequent changes.

Typically, the slowest speed grades transition to Production

before faster speed grades.

Software Version Requirements

Production-quality systems must use FPGA designs

compiled using a speed file designated as PRODUCTION

status. FPGAs designs using a less mature speed file

designation should only be used during system prototyping

or pre-production qualification. FPGA designs with speed

files designated as Preview, Advance, or Preliminary should

not be used in a production-quality system.

Whenever a speed file designation changes, as a device

matures toward Production status, rerun the latest Xilinx

ISE™ software on the FPGA design to ensure that the

FPGA design incorporates the latest timing information and

software updates.

Production designs will require updating the Xilinx ISE

development software with a future version and/or Service

Pack.

All parameter limits are representative of worst-case supply

voltage and junction temperature conditions. Unless

otherwise noted, the published parameter values apply

to all Spartan-3A DSP devices. AC and DC

characteristics are specified using the same numbers

for both commercial and industrial grades.

20 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 21

R

To create a Xilinx MySupport user account and sign up for

automatic E-mail notification whenever this data sheet is

updated:

• Sign Up for Alerts on Xilinx MySupport

www.xilinx.com/xlnx/xil_ans_display.jsp?getPagePath=19380

Timing parameters and their representative values are

selected for inclusion below either because they are

important as general design requirements or they indicate

fundamental device performance characteristics. The

Spartan-3A DSP FPGA speed files (v1.29), part of the

Xilinx Development Software, are the original source for

many but not all of the values. The speed grade

designations for these files are shown in Ta b l e 1 5 . For more

complete, more precise, and worst-case data, use the

values reported by the Xilinx static timing analyzer (TRACE

in the Xilinx development software) and back-annotated to

the simulation netlist.

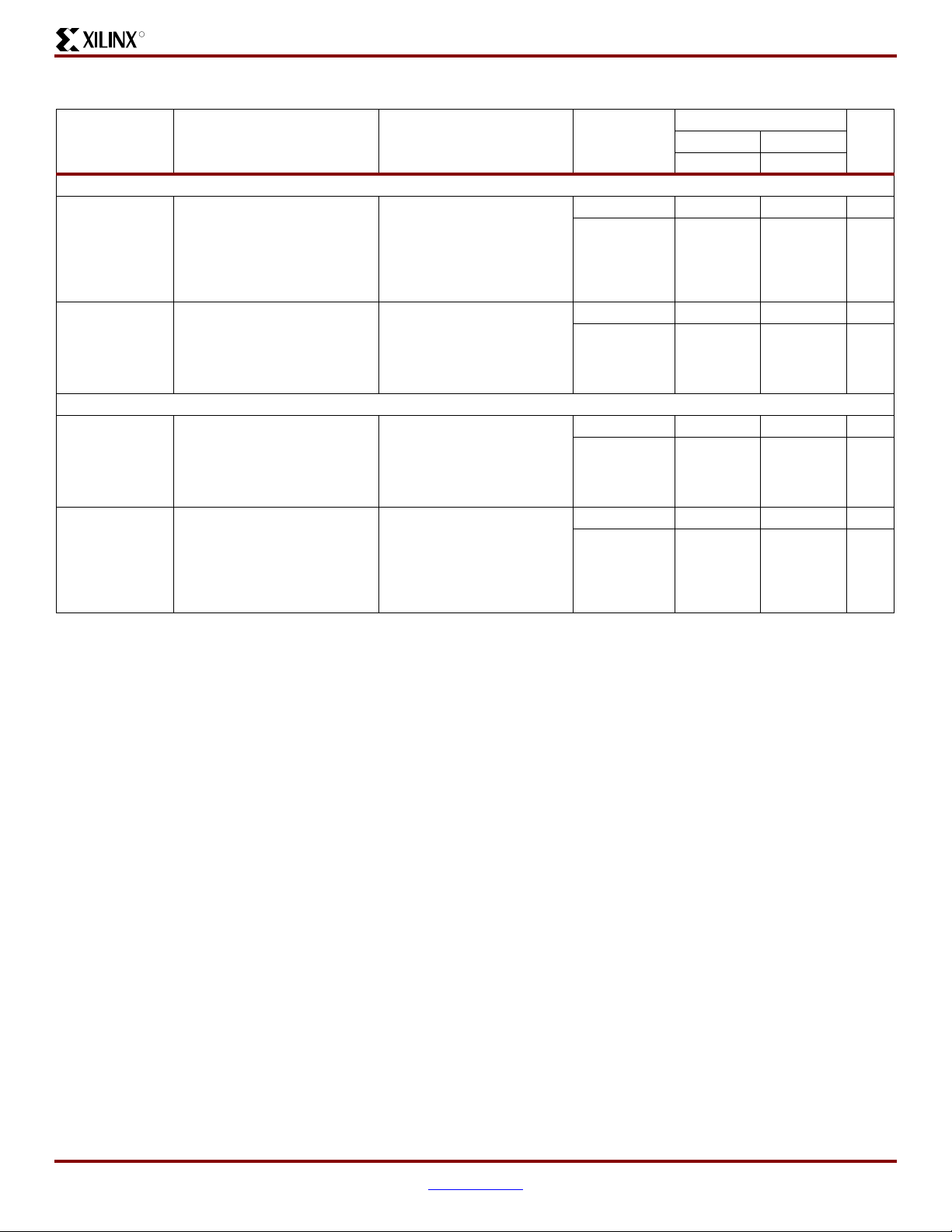

Table 15:

XC3SD1800A

XC3SD3400A

Spartan-3A DSP v1.29 Speed Grade Designations

Device Preview Advance Preliminary Production

-4, -5

-4, -5

DC and Switching Characteristics

Tab le 1 6 provides the recent history of the Spartan-3A DSP

FPGA speed files.

Table 16:

Version

1.29 ISE 9.2.01i

1.28 ISE 9.2i Minor updates

1.27 ISE 9.1.03i

Spartan-3A DSP Speed File Version History

ISE

Release Description

Production Speed Files for -4 and -5

speed grades

Advance Speed Files for -4 speed

grade

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 21

Product Specification

Page 22

DC and Switching Characteristics

I/O Timing

R

Table 17:

Pin-to-Pin Clock-to-Output Times for the IOB Output Path

Speed Grade

-5 -4

Symbol Description Conditions Device

Max Max

Units

Clock-to-Output Times

T

ICKOFDCM

When reading from the Output

Flip-Flop (OFF), the time from the

active transition on the Global

LV CM O S 25

output drive, Fast slew

rate, with DCM

(2)

, 12mA

(3)

XC3SD1800A 3.28 3.51 ns

XC3SD3400A 3.36 3.82 ns

Clock pin to data appearing at the

Output pin. The DCM is in use.

T

ICKOF

When reading from OFF, the time

from the active transition on the

Global Clock pin to data appearing

LV CM O S 25

output drive, Fast slew

rate, without DCM

(2)

, 12mA

XC3SD1800A 5.23 5.58 ns

XC3SD3400A 5.51 6.13 ns

at the Output pin. The DCM is not

in use.

Notes:

1. The numbers in this table are tested using the methodology presented in Table 25 and are based on the operating conditions set forth in

Tab l e 7 and Table 10.

2. This clock-to-output time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or a

standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. If the former is true,

Input adjustment from Table 21. If the latter is true,

3. DCM output jitter is included in all measurements.

add

the appropriate Output adjustment from Ta b l e 2 4 .

add

the appropriate

22 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 23

R

DC and Switching Characteristics

Table 18:

Pin-to-Pin Setup and Hold Times for the IOB Input Path (System Synchronous)

Speed Grade

-5 -4

Symbol Description Conditions Device

Min Min

Units

Setup Times

(4)

(2)

,

XC3SD1800A 2.65 3.11 ns

XC3SD3400A 2.25 2.49 ns

T

PSDCM

When writing to the Input

Flip-Flop (IFF), the time from

the setup of data at the Input

LV CM OS 25

IFD_DELAY_VALUE = 0,

with DCM

pin to the active transition at a

Global Clock pin. The DCM is in

use. No Input Delay is

programmed.

T

PSFD

When writing to IFF, the time

from the setup of data at the

Input pin to an active transition

LV CM OS 25

IFD_DELAY_VALUE = 6,

without DCM

(2)

,

XC3SD1800A 2.98 3.39 ns

XC3SD3400A 2.78 3.08 ns

at the Global Clock pin. The

DCM is not in use. The Input

Delay is programmed.

Hold Times

(4)

(3)

,

XC3SD1800A -0.38 -0.38 ns

XC3SD3400A -0.26 -0.26 ns

T

PHDCM

When writing to IFF, the time

from the active transition at the

Global Clock pin to the point

LV CM OS 25

IFD_DELAY_VALUE = 0,

with DCM

when data must be held at the

Input pin. The DCM is in use.

No Input Delay is programmed.

T

PHFD

When writing to IFF, the time

from the active transition at the

Global Clock pin to the point

LV CM OS 25

IFD_DELAY_VALUE = 6,

without DCM

(3)

,

XC3SD1800A -0.71 -0.71 ns

XC3SD3400A -0.65 -0.65 ns

when data must be held at the

Input pin. The DCM is not in

use. The Input Delay is

programmed.

Notes:

1. The numbers in this table are tested using the methodology presented in Table 25 and are based on the operating conditions set forth in

Ta b l e 7 and Table 10.

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data

Input. If this is true of the Global Clock Input, subtract the appropriate adjustment from Table 21. If this is true of the data Input, add the

appropriate Input adjustment from the same table.

3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data

Input. If this is true of the Global Clock Input, add the appropriate Input adjustment from Tab l e 21 . If this is true of the data Input, subtract

the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock’s

active edge.

4. DCM output jitter is included in all measurements.

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 23

Product Specification

Page 24

DC and Switching Characteristics

R

Table 19:

Setup and Hold Times for the IOB Input Path

Symbol Description Conditions

Setup Times

T

IOPICK

Time from the setup of data at

the Input pin to the active

LV CM O S 25

(2)

transition at the ICLK input of

the Input Flip-Flop (IFF). No

Input Delay is programmed.

T

IOPICKD

Time from the setup of data at

the Input pin to the active

LV CM O S 25

(2)

transition at the ICLK input of

the Input Flip-Flop (IFF). The

Input Delay is programmed.

Hold Times

T

IOICKP

Time from the active transition

at the ICLK input of the Input

LV CM O S 25

(2)

Flip-Flop (IFF) to the point

where data must be held at the

Input pin. No Input Delay is

programmed.

T

IOICKPD

Time from the active transition

at the ICLK input of the Input

LV CM O S 25

(2)

Flip-Flop (IFF) to the point

where data must be held at the

Input pin. The Input Delay is

programmed.

Set/Reset Pulse Width

T

RPW_IOB

Minimum pulse width to SR

control input on IOB

Speed Grade

IFD_DELAY_

VALUE Device

-5 -4

Min Min

0 All 1.36 1.74 ns

1 All 1.79 2.17 ns

2 All 2.55 2.92 ns

3 All 3.38 3.76 ns

4 All 3.75 4.32 ns

5 All 3.81 4.19 ns

6 All 4.39 5.09 ns

7 All 5.16 5.98 ns

8 All 5.69 6.57 ns

0All-0.71-0.71ns

1All-1.60-1.60ns

2All-2.06-2.06ns

3All-2.46-2.46ns

4All-2.86-2.86ns

5All-2.88-2.88ns

6All-3.24-3.24ns

7All-3.55-3.55ns

8All-3.89-3.89ns

All 1.33 1.61 ns

Units

Notes:

1. The numbers in this table are tested using the methodology presented in Table 25 and are based on the operating conditions set forth in

Tab l e 7 and Table 10.

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, add the

appropriate Input adjustment from Table 21.

3. These hold times require adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, subtract

the appropriate Input adjustment from Table 21. When the hold time is negative, it is possible to change the data before the clock’s active

edge.

24 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 25

R

DC and Switching Characteristics

Table 20:

Propagation Times for the IOB Input Path

Speed Grade

-5 -4

Symbol Description Conditions IFD_Delay_Value Device

Max Max

Units

Propagation Times

T

IOPLI

The time it takes for data to

travel from the Input pin

LV CM OS 25

(2)

0 All 1.50 1.97 ns

through the IFF latch to the I

output with no input delay

programmed

T

IOPLID

The time it takes for data to

travel from the Input pin

through the IFF latch to the I

output with the input delay

programmed

LV CM OS 25

(2)

1 All 1.93 2.40 ns

2 All 2.69 3.15 ns

3 All 3.52 3.99 ns

4 All 3.89 4.55 ns

5 All 3.95 4.42 ns

6 All 4.53 5.32 ns

7 All 5.30 6.21 ns

8 All 5.83 6.80 ns

Notes:

1. The numbers in this table are tested using the methodology presented in Table 25 and are based on the operating conditions set forth in

Tab l e 7 and Table 10.

2. This propagation time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. When this is

true,

add

the appropriate Input adjustment from Table 21.

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 25

Product Specification

Page 26

DC and Switching Characteristics

R

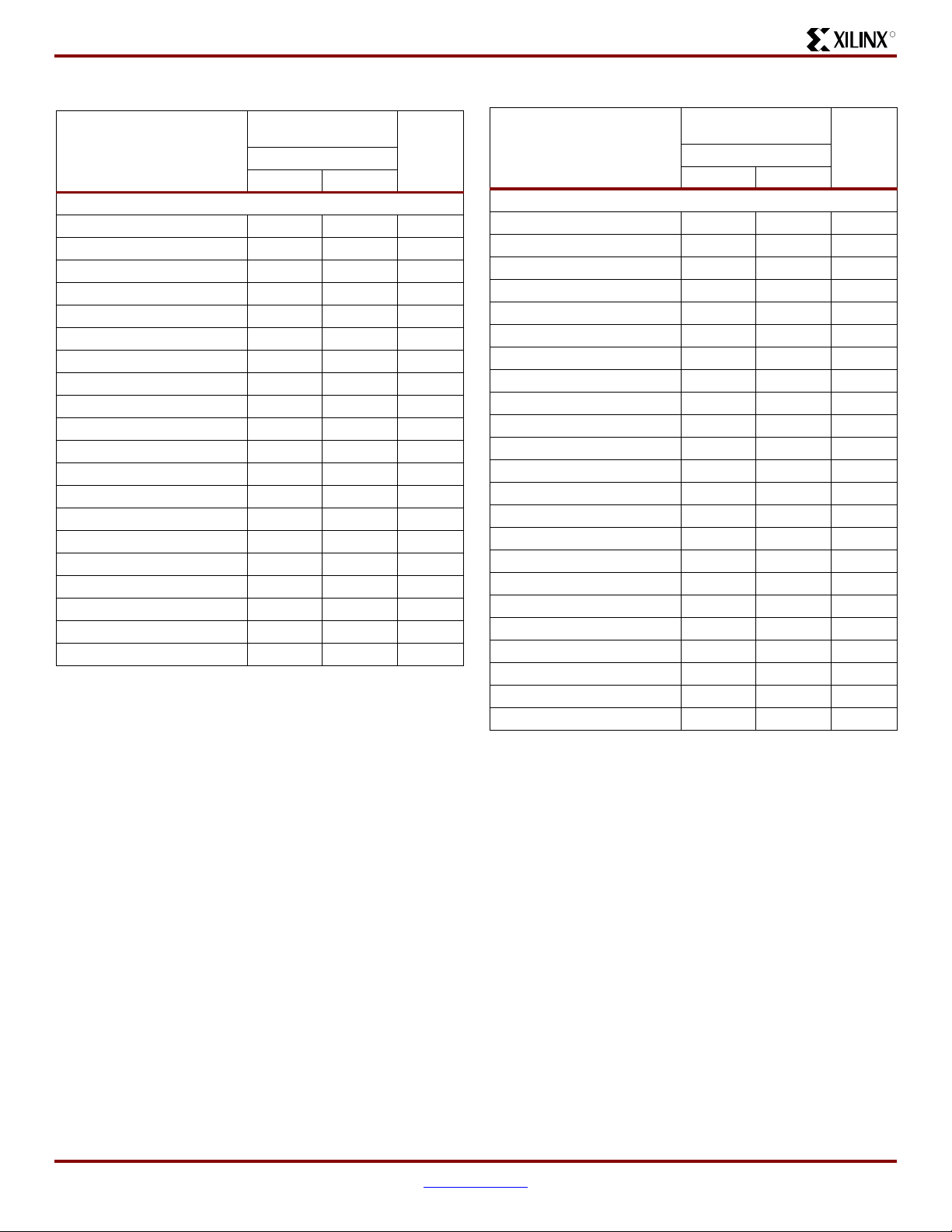

Table 21:

Input Timing Adjustments by IOSTANDARD

Add the

Convert Input Time from

LVCMOS25 to the Following

Signal Standard

(IOSTANDARD)

Adjustment Below

Speed Grade

-5 -4

Units

Single-Ended Standards

LVTTL 0.62 0.62 ns

LVCMOS33 0.54 0.54 ns

LVCMOS25 0.00 0.00 ns

LVCMOS18 0.83 0.83 ns

LVCMOS15 0.60 0.60 ns

LVCMOS12 0.31 0.31 ns

PCI33_3 0.41 0.41 ns

PCI66_3 0.41 0.41 ns

PCIX 0.41 0.41 ns

HSTL_I 0.72 0.72 ns

HSTL_III 0.77 0.77 ns

HSTL_I_18 0.69 0.69 ns

HSTL_II_18 0.69 0.69 ns

HSTL_III_18 0.79 0.79 ns

SSTL18_I 0.71 0.71 ns

SSTL18_II 0.71 0.71 ns

SSTL2_I 0.68 0.68 ns

SSTL2_II 0.68 0.68 ns

SSTL3_I 0.78 0.78 ns

SSTL3_II 0.78 0.78 ns

Table 21:

Input Timing Adjustments by IOSTANDARD

Add the

Convert Input Time from

LVCMOS25 to the Following

Signal Standard

(IOSTANDARD)

Adjustment Below

Speed Grade

-5 -4

Units

Differential Standards

LVDS_25 0.76 0.76 ns

LVDS_33 0.79 0.79 ns

BLVDS_25 0.79 0.79 ns

MINI_LVDS_25 0.78 0.78 ns

MINI_LVDS_33 0.79 0.79 ns

LVPECL_25 0.78 0.78 ns

LVPECL_33 0.79 0.79 ns

RSDS_25 0.79 0.79 ns

RSDS_33 0.77 0.77 ns

TMDS_33 0.79 0.79 ns

PPDS_25 0.79 0.79 ns

PPDS_33 0.79 0.79 ns

DIFF_HSTL_I_18 0.74 0.74 ns

DIFF_HSTL_II_18 0.72 0.72 ns

DIFF_HSTL_III_18 1.05 1.05 ns

DIFF_HSTL_I 0.72 0.72 ns

DIFF_HSTL_III 1.05 1.05 ns

DIFF_SSTL18_I 0.71 0.71 ns

DIFF_SSTL18_II 0.71 0.71 ns

DIFF_SSTL2_I 0.74 0.74 ns

DIFF_SSTL2_II 0.75 0.75 ns

DIFF_SSTL3_I 1.06 1.06 ns

DIFF_SSTL3_II 1.06 1.06 ns

Notes:

1. The numbers in this table are tested using the methodology

presented in Ta bl e 2 5 and are based on the operating conditions

set forth in Ta b le 7 , Table 10, and Ta b le 1 2 .

2. These adjustments are used to convert input path times originally

specified for the LVCMOS25 standard to times that correspond to

other signal standards.

26 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 27

R

DC and Switching Characteristics

Table 22:

Timing for the IOB Output Path

Symbol Description Conditions Device

Clock-to-Output Times

T

IOCKP

When reading from the Output

Flip-Flop (OFF), the time from the

LV CM OS 2 5

drive, Fast slew rate

(2)

, 12 mA output

active transition at the OCLK input to

data appearing at the Output pin

Propagation Times

T

T

IOOLP

IOOP

The time it takes for data to travel from

the IOB’s O input to the Output pin

The time it takes for data to travel from

the O input through the OFF latch to

LV CM OS 2 5

drive, Fast slew rate

(2)

, 12 mA output

the Output pin

Set/Reset Times

T

IOSRP

Time from asserting the OFF’s SR

input to setting/resetting data at the

LV CM OS 2 5

drive, Fast slew rate

(2)

, 12 mA output

Output pin

T

IOGSRQ

Time from asserting the Global Set

Reset (GSR) input on the

STARTUP_SPARTAN3A primitive to

setting/resetting data at the Output pin

Speed Grade

-5 -4

Max Max

Units

All 2.87 3.13 ns

All 2.78 2.91 ns

2.70 2.85 ns

All 3.63 3.89 ns

8.62 9.65 ns

Notes:

1. The numbers in this table are tested using the methodology presented in Table 25 and are based on the operating conditions set forth in

Tab l e 7 and Table 10.

2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data

Output. When this is true,

Table 23:

Timing for the IOB Three-State Path

add

the appropriate Output adjustment from Table 24.

Speed Grade

-5 -4

Symbol Description Conditions Device

Max Max

Units

Synchronous Output Enable/Disable Times

T

IOCKHZ

T

IOCKON

(2)

Time from the active transition at the OTCLK

input of the Three-state Flip-Flop (TFF) to when

the Output pin enters the high-impedance state

Time from the active transition at TFF’s OTCLK

input to when the Output pin drives valid data

LVCMOS25, 12 mA

output drive, Fast slew

rate

All 1.13 1.39 ns

All 3.08 3.35 ns

Asynchronous Output Enable/Disable Times

T

GTS

Time from asserting the Global Three State

(GTS) input on the STARTUP_SPARTAN3A

primitive to when the Output pin enters the

LVCMOS25, 12 mA

output drive, Fast slew

rate

All 9.47 10.36 ns

high-impedance state

Set/Reset Times

T

IOSRHZ

T

IOSRON

(2)

Time from asserting TFF’s SR input to when

the Output pin enters a high-impedance state

Time from asserting TFF’s SR input at TFF to

when the Output pin drives valid data

LVCMOS25, 12 mA

output drive, Fast slew

rate

All 1.61 1.86 ns

All 3.57 3.82 ns

Notes:

1. The numbers in this table are tested using the methodology presented in Table 25 and are based on the operating conditions set forth in

Ta b l e 7 and Table 10.

2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the

data Output. When this is true,

add

the appropriate Output adjustment from Table 24.

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 27

Product Specification

Page 28

DC and Switching Characteristics

R

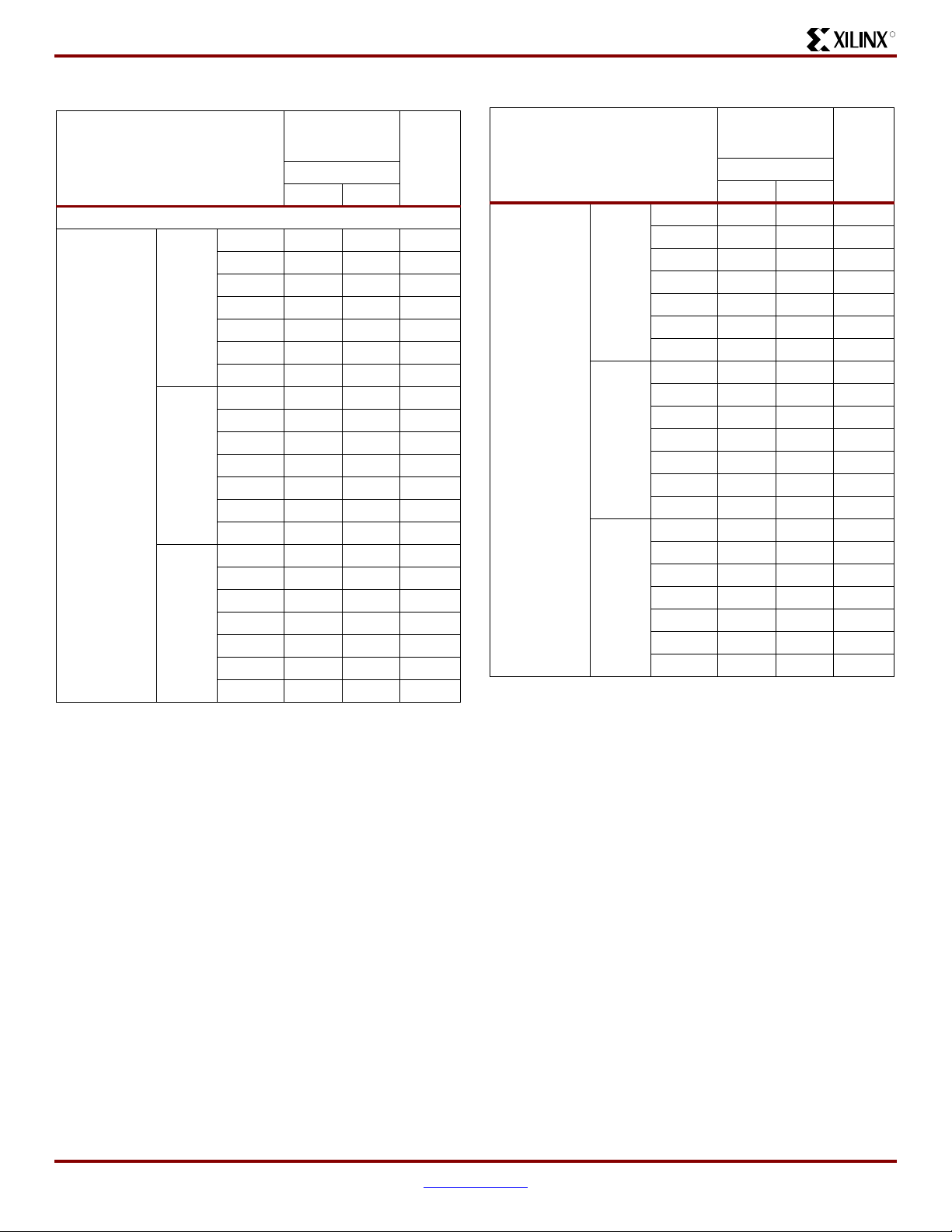

Table 24:

Output Timing Adjustments for IOB

Add the

Adjustment

Convert Output Time from

LVCMOS25 with 12mA Drive and

Fast Slew Rate to the Following

Signal Standard (IOSTANDARD)

Below

Speed Grade

-5 -4

Units

Single-Ended Standards

LVTTL Slow 2 mA 5.58 5.58 ns

4 mA 3.16 3.16 ns

6 mA 3.17 3.17 ns

8 mA 2.09 2.09 ns

12 mA 1.62 1.62 ns

16 mA 1.24 1.24 ns

24 mA 2.74 2.74 ns

Fast 2 mA 3.03 3.03 ns

4 mA 1.71 1.71 ns

6 mA 1.71 1.71 ns

8 mA 0.53 0.53 ns

12 mA 0.53 0.53 ns

16 mA 0.59 0.59 ns

24 mA 0.60 0.60 ns

QuietIO 2 mA 27.67 27.67 ns

4 mA 27.67 27.67 ns

6 mA 27.67 27.67 ns

8 mA 16.71 16.71 ns

12 mA 16.67 16.67 ns

16 mA 16.22 16.22 ns

24 mA 12.11 12.11 ns

Table 24:

Output Timing Adjustments for IOB

(Continued)

Add the

Adjustment

Convert Output Time from

LVCMOS25 with 12mA Drive and

Fast Slew Rate to the Following

Signal Standard (IOSTANDARD)

Below

Speed Grade

-5 -4

Units

LV CM O S 33 Slow 2 mA 5.58 5.58 ns

4 mA 3.17 3.17 ns

6 mA 3.17 3.17 ns

8 mA 2.09 2.09 ns

12 mA 1.24 1.24 ns

16 mA 1.15 1.15 ns

24 mA 2.55 2.55 ns

Fast 2 mA 3.02 3.02 ns

4 mA 1.71 1.71 ns

6 mA 1.72 1.72 ns

8 mA 0.53 0.53 ns

12 mA 0.59 0.59 ns

16 mA 0.59 0.59 ns

24 mA 0.51 0.51 ns

QuietIO 2 mA 27.67 27.67 ns

4 mA 27.67 27.67 ns

6 mA 27.67 27.67 ns

8 mA 16.71 16.71 ns

12 mA 16.29 16.29 ns

16 mA 16.18 16.18 ns

24 mA 12.11 12.11 ns

28 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 29

R

DC and Switching Characteristics

Table 24:

Output Timing Adjustments for IOB

(Continued)

Add the

Adjustment

Convert Output Time from

LVCMOS25 with 12mA Drive and

Fast Slew Rate to the Following

Signal Standard (IOSTANDARD)

Below

Speed Grade

-5 -4

Units

LV CM O S 25 Slow 2 mA 5.33 5.33 ns

4 mA 2.81 2.81 ns

6 mA 2.82 2.82 ns

8 mA 1.14 1.14 ns

12 mA 1.10 1.10 ns

16 mA 0.83 0.83 ns

24 mA 2.26 2.26 ns

Fast 2 mA 4.36 4.36 ns

4 mA 1.76 1.76 ns

6 mA 1.25 1.25 ns

8 mA 0.38 0.38 ns

12 mA 0.00 0.00 ns

16 mA 0.01 0.01 ns

24 mA 0.01 0.01 ns

QuietIO 2 mA 25.92 25.92 ns

4 mA 25.92 25.92 ns

6 mA 25.92 25.92 ns

8 mA 15.57 15.57 ns

12 mA 15.59 15.59 ns

16 mA 14.27 14.27 ns

24 mA 11.37 11.37 ns

LV CM O S 18 Slow 2 mA 4.48 4.48 ns

4 mA 3.69 3.69 ns

6 mA 2.91 2.91 ns

8 mA 1.99 1.99 ns

12 mA 1.57 1.57 ns

16 mA 1.19 1.19 ns

Fast 2 mA 3.96 3.96 ns

4 mA 2.57 2.57 ns

6 mA 1.90 1.90 ns

8 mA 1.06 1.06 ns

12 mA 0.83 0.83 ns

16 mA 0.63 0.63 ns

QuietIO 2 mA 24.97 24.97 ns

4 mA 24.97 24.97 ns

6 mA 24.08 24.08 ns

8 mA 16.43 16.43 ns

12 mA 14.52 14.52 ns

16 mA 13.41 13.41 ns

Table 24:

Output Timing Adjustments for IOB

(Continued)

Add the

Adjustment

Convert Output Time from

LVCMOS25 with 12mA Drive and

Fast Slew Rate to the Following

Signal Standard (IOSTANDARD)

Below

Speed Grade

-5 -4

Units

LV CM O S 15 Slow 2 mA 5.82 5.82 ns

4 mA 3.97 3.97 ns

6 mA 3.21 3.21 ns

8 mA 2.53 2.53 ns

12 mA 2.06 2.06 ns

Fast 2 mA 5.23 5.23 ns

4 mA 3.05 3.05 ns

6 mA 1.95 1.95 ns

8 mA 1.60 1.60 ns

12 mA 1.30 1.30 ns

QuietIO 2 mA 34.11 34.11 ns

4 mA 25.66 25.66 ns

6 mA 24.64 24.64 ns

8 mA 22.06 22.06 ns

12 mA 20.64 20.64 ns

LV CM O S 12 Slow 2 mA 7.14 7.14 ns

4 mA 4.87 4.87 ns

6 mA 5.67 5.67 ns

Fast 2 mA 6.77 6.77 ns

4 mA 5.02 5.02 ns

6 mA 4.09 4.09 ns

QuietIO 2 mA 50.76 50.76 ns

4 mA 43.17 43.17 ns

6 mA 37.31 37.31 ns

PCI33_3 0.34 0.34 ns

PCI66_3 0.34 0.34 ns

PCIX 0.34 0.34 ns

HSTL_I 0.78 0.78 ns

HSTL_III 1.16 1.16 ns

HSTL_I_18 0.35 0.35 ns

HSTL_II_18 0.30 0.30 ns

HSTL_III_18 0.47 0.47 ns

SSTL18_I 0.40 0.40 ns

SSTL18_II 0.30 0.30 ns

SSTL2_I 0.00 0.00 ns

SSTL2_II -0.05 -0.05 ns

SSTL3_I 0.00 0.00 ns

SSTL3_II 0.17 0.17 ns

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 29

Product Specification

Page 30

DC and Switching Characteristics

R

Table 24:

Output Timing Adjustments for IOB

(Continued)

Add the

Adjustment

Convert Output Time from

LVCMOS25 with 12mA Drive and

Fast Slew Rate to the Following

Signal Standard (IOSTANDARD)

Below

Speed Grade

-5 -4

Units

Differential Standards

LVDS_25 1.16 1.16 ns

LVDS_33 0.46 0.46 ns

BLVDS_25 0.11 0.11 ns

MINI_LVDS_25 0.75 0.75 ns

MINI_LVDS_33 0.40 0.40 ns

LVPECL_25

LVPECL_33

Inputs Only

RSDS_25 1.42 1.42 ns

RSDS_33 0.58 0.58 ns

TMDS_33 0.46 0.46 ns

PPDS_25 1.07 1.07 ns

PPDS_33 0.63 0.63 ns

DIFF_HSTL_I_18 0.43 0.43 ns

DIFF_HSTL_II_18 0.41 0.41 ns

DIFF_HSTL_III_18 0.36 0.36 ns

DIFF_HSTL_I 1.01 1.01 ns

DIFF_HSTL_III 0.54 0.54 ns

DIFF_SSTL18_I 0.49 0.49 ns

DIFF_SSTL18_II 0.41 0.41 ns

DIFF_SSTL2_I 0.82 0.82 ns

DIFF_SSTL2_II 0.09 0.09 ns

DIFF_SSTL3_I 1.16 1.16 ns

DIFF_SSTL3_II 0.28 0.28 ns

Notes:

1. The numbers in this table are tested using the methodology

presented in Table 25 and are based on the operating conditions

set forth in Table 7 , Table 10, and Table 12.

2. These adjustments are used to convert output- and

three-state-path times originally specified for the LVCMOS25

standard with 12 mA drive and Fast slew rate to times that

correspond to other signal standards. Do not adjust times that

measure when outputs go into a high-impedance state.

30 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

Page 31

R

Timing Measurement Methodology

DC and Switching Characteristics

When measuring timing parameters at the programmable

I/Os, different signal standards call for different test

conditions. Ta bl e 2 5 lists the conditions to use for each

open connection, and V

measurement point (V

used at the Output.

is set to zero. The same

T

) that was used at the Input is also

M

standard.

V

(V

The method for measuring Input timing is as follows: A

signal that swings between a Low logic level of V

High logic level of V

is applied to the Input under test.

H